# **SPT5510**

# 16-BIT, 200 MWPS ECL D/A CONVERTER

#### **FEATURES**

- 16-Bit, 200 MWPS digital-to-analog converter

- Differential linearity of ±0.6 LSB (typical)

- Integral linearity of ±0.75 LSB (typical)

- Fast settling time: 35 ns to 0.0008%; 25 ns to 0.01%

- · Low glitch energy

- On-chip voltage reference

- ECL compatibility

## **GENERAL DESCRIPTION**

The SPT5510 is a 16-bit, 200 MWPS digital-to-analog converter designed for high-resolution waveform synthesis for test and measurement instrumentation applications. It features true 16-bit linearity, with differential non-linearity of typically  $\pm 0.6$  LSB and integral non-linearity of  $\pm 0.75$  LSB. It

# **APPLICATIONS**

- High-precision arbitrary waveform generation

- Test and measurement instrumentation

- · Digital waveform synthesis

- · Microwave and satellite modems

- Disk drive test equipment

- · Industrial process control

- Military applications

has a very high-speed update rate of up to 200 MHz and is ECL compatible. It has an ultrafast settling time of 25 ns to 0.01% and 35 ns to 0.0008%.

The SPT5510 operates over an industrial temperature range of –40 °C to +85 °C and is available in a 10 x 10 mm, 44-lead metric quad flat pack (MQFP) plastic package.

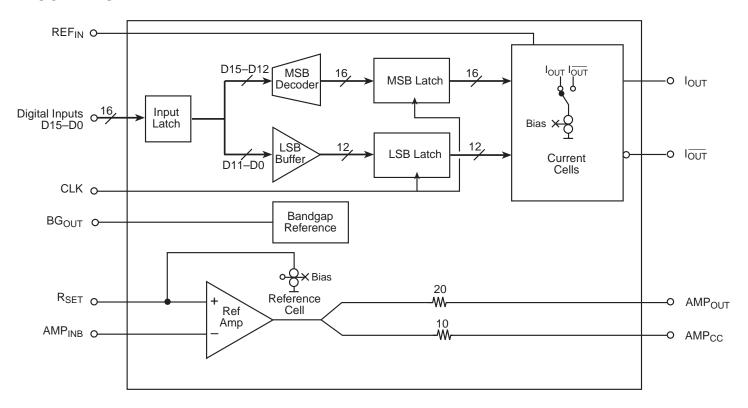

# **BLOCK DIAGRAM**

# Signal Processing Technologies, Inc.

# ABSOLUTE MAXIMUM RATINGS (Beyond which damage may occur)<sup>1</sup>

# Supply VoltagesNegative supply voltage (VEE)—7 VA/D ground voltage differential—0.5 VInput VoltagesTemperatureDigital input voltage (D15–D0, Clock)—2.5 to 0 VRef amp input voltage range—2.5 to 0 VReference input voltage range (Ref In)VEE to -2.5 V Output Currents Bandgap reference output current Emperature Operating temperature Junction temperature —40 to +85 °C Junction temperature Lead, soldering (10 seconds) —65 to +150 °C Storage —65 to +150 °C

**Note**: 1. Operation at any Absolute Maximum Rating is not implied. See Electrical Specifications for nominal operating conditions.

# **ELECTRICAL SPECIFICATIONS**

$T_{A}\text{=-}25~^{\circ}\text{C},\,V_{EE}\text{=-}5.2~\text{V}~\pm5\%,\,50\%$  duty cycle clock, unless otherwise specified.

|                                            | TEST                               | TEST  |       | SPT5510 |      |           |

|--------------------------------------------|------------------------------------|-------|-------|---------|------|-----------|

| PARAMETERS                                 | CONDITIONS                         | LEVEL | MIN   | TYP     | MAX  | UNITS     |

| DC Performance <sup>1</sup>                |                                    |       |       |         |      |           |

| Resolution                                 |                                    |       |       | 16      |      | Bits      |

| Differential Linearity                     |                                    | VI    | -1.95 | ±0.6    | 1.95 | LSB       |

| Differential Linearity                     | T <sub>MIN</sub> -T <sub>MAX</sub> | IV    | -4.0  | ±1.0    | 4.0  | LSB       |

| Integral Linearity                         |                                    | VI    | -1.95 | ±0.75   | 1.95 | LSB       |

| Integral Linearity                         | T <sub>MIN</sub> -T <sub>MAX</sub> | IV    | -4.0  | ±1.5    | 4.0  | LSB       |

| Integral Linearity Drift                   |                                    | IV    | -0.2  |         | 0.2  | LSB/°C    |

| Offset Drift                               | T <sub>MIN</sub> -T <sub>MAX</sub> | IV    | -2.5  |         | 2.5  | ppm FS/°C |

| Monotonicity                               |                                    | V     | 15    |         |      | Bits      |

| Output Capacitance                         |                                    | V     |       | 10      |      | pF        |

| Gain Error                                 |                                    | I     | -2    | 0.4     | 2    | % FS      |

| Gain Error Tempco                          | With Ext Reference                 | V     |       | 50      |      | ppm FS/°C |

| Gain Error Tempco                          | With Internal Bandgap Ref          | V     |       | 50      |      | ppm FS/°C |

| Offset Error                               |                                    | 1     | -4    |         | 4    | μΑ        |

| Compliance Voltage                         |                                    | IV    | -1.2  |         | 2    | V         |

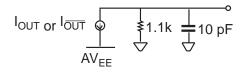

| Output Resistance                          |                                    | IV    | 0.88  | 1.1     | 1.32 | kΩ        |

| Dynamic Performance                        |                                    |       |       |         |      |           |

| Conversion Rate                            |                                    | IV    | 200   |         |      | MHz       |

| Settling Time t <sub>ST</sub> <sup>2</sup> |                                    |       |       |         |      |           |

|                                            | Settling to ±0.01%                 | V     |       | 25      |      | ns        |

|                                            | Settling to ±0.0008%               | V     |       | 35      |      | ns        |

| Delay Time t <sub>D</sub>                  |                                    | V     |       | 2       |      | ns        |

| Glitch Energy                              |                                    | V     |       | 30      |      | pV-s      |

| Full Scale Output Current                  | With On-Chip References            | V     |       | 19      |      | mA        |

| Rise Time/Fall Time                        | $R_L = 50 \Omega$                  | V     |       | 2       |      | ns        |

| Spurious Free Dynamic Range                |                                    |       |       |         |      |           |

| $f_{OUT}$ =5 MHz; $f_{CLOCK}$ =30 MHz      | 10 MHz Span                        | V     |       | 84      |      | dB        |

| $f_{OUT}$ =10 MHz; $f_{CLOCK}$ =100 MHz    | 10 MHz Span                        | V     |       | 76      |      | dB        |

<sup>&</sup>lt;sup>1</sup>Measured at 0 V output using I-V.

SPT5510

<sup>&</sup>lt;sup>2</sup>Measured as voltage settling for mid-scale transition;  $R_L$  = 50  $\Omega$ .

# **ELECTRICAL SPECIFICATIONS**

T<sub>A</sub>= 25 °C, V<sub>EE</sub>=–5.2 V  $\pm$ 5%, 50% duty cycle clock, unless otherwise specified.

|                                                                                                                                                                                                                     | TEST                                                                                | TEST                           |                           | SPT5510                               |                   |                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------|---------------------------|---------------------------------------|-------------------|--------------------------------------|

| PARAMETERS                                                                                                                                                                                                          | CONDITIONS                                                                          | LEVEL                          | MIN                       | TYP                                   | MAX               | UNITS                                |

| Power Supply Requirements Negative Supply Current (–5.2 V) Nominal Power Dissipation Power Supply Rejection Ratio                                                                                                   | $T_{MIN} - T_{MAX}$ $\Delta V \text{ Supply} = \pm 5 \%$                            | VI<br>V<br>I                   | -0.6                      | 115<br>600<br>±0.002                  | 150<br>800<br>0.6 | mA<br>mW<br>% FS                     |

| Voltage Input and Control Bandgap Reference Voltage Bandgap Output Current Ref Amp Bandwidth <sup>3</sup> Ref Amp Input Current Ref Amp Output Current Ref In Operating Voltage                                     | T <sub>A</sub> =25 °C ±10 °C                                                        | V<br>IV<br>V<br>V              | -110                      | -1.2<br>16<br>40<br>16<br>200<br>-3.4 | 220               | V<br>μA<br>MHz<br>μA<br>μA<br>V      |

| Digital Inputs  Logic 1 Voltage  Logic 0 Voltage  Logic 1 Current  Logic 0 Current  Input Capacitance  Input Setup Time (t <sub>S</sub> )  Input Hold Time (t <sub>H</sub> )  Clock Pulse Width (t <sub>PWH</sub> ) | T <sub>MIN</sub> -T <sub>MAX</sub> T <sub>MIN</sub> -T <sub>MAX</sub> -0.8 V -1.8 V | VI<br>VI<br>V<br>V<br>IV<br>IV | -1.0<br>3.0<br>0.5<br>1.5 | -0.8<br>-1.7<br>2.5<br>0<br>3         | -1.5              | V<br>V<br>μA<br>μA<br>pF<br>ns<br>ns |

<sup>&</sup>lt;sup>3</sup>Ref Amp Bandwidth is limited by its compensation network

| TEST LEVEL CODES                                                                                                      | TEST LEVEL | TEST PROCEDURE                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------|

| All electrical characteristics are subject to the following conditions:                                               | 1          | 100% production tested at the specified temperature.                                                |

| All parameters having min/max specifi-                                                                                | II         | 100% production tested at $T_A$ = +25 °C, and sample tested at the specified temperatures.          |

| cations are guaranteed. The Test Level column indicates the specific device                                           | III        | QA sample tested only at the specified temperatures.                                                |

| testing actually performed during pro-<br>duction and Quality Assurance inspec-                                       | IV         | Parameter is guaranteed (but not tested) by design and characterization data.                       |

| tion. Any blank section in the data column indicates that the specification is not tested at the specified condition. | V          | Parameter is a typical value for information purposes only.                                         |

|                                                                                                                       | VI         | 100% production tested at $T_A$ = +25 °C. Parameter is guaranteed over specified temperature range. |

SPT5510 9/27/00

## THEORY OF OPERATION

The SPT5510 is a segmented 16-bit current-output DAC. The four MSBs, D15–D12, are decoded to fifteen unit cells (current sinks). The remaining bits (D11–D0) are binary; bits D9–D0 are derived from an R-2R ladder. All cells are laser trimmed for maximum accuracy. The block diagram shows the basic architecture.

All output cells are always on, with the data determining whether a given cell's current is routed from  $I_{OUT}$  or  $I_{\overline{OUT}}$ . This provides nearly constant power dissipation independent of data and clock rate. It also reduces noise transients on power and ground lines.

The reference loop utilizes an MSB-weighted cell and provides a gain of about 16 to the output. The on-chip reference amplifier has very high open-loop gain and is offset trimmed to provide a very low temperature drift (typically <10 ppm/°C gain drift).

#### POWER SUPPLY AND GROUNDING

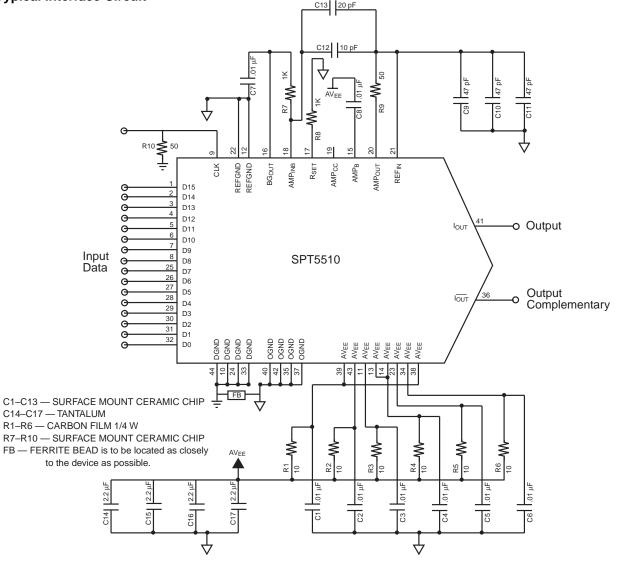

The SPT5510 requires a single –5.2V power supply. All supply pins attach to a common on-chip power bus and should be treated as analog supplies. For best settling performance, each supply pin should be decoupled as shown in figure 1 – typical interface circuit.

There are three separate on-chip ground busses. DGND pins should be tied together and connected to system ground through a ferrite bead. REFGND and OGND pins should be tied directly to the SPT5510's ground plane and connected to system ground through a ferrite bead. It is critical that REFGND and OGND are very tightly coupled, as any differential signal (dc offset, noise, etc.) will be transmitted to the output. Two of the OGND pins can be disconnected from the ground plane and used as sense lines for a current-to-voltage converter, as shown in the OUTPUTS section.

Figure 1 - Typical Interface Circuit

4

SPT5510

Wideband decoupling is required for optimum settling performance. This may require several capacitors in parallel, and series resistors when appropriate, to reduce resonance effects. Some applications may need only a single capacitor; however, decoupling influences both long- and shortterm settling, so caution is urged. Your application may require some research to determine the optimum power supply decoupling network.

#### **DIGITAL INPUTS AND TIMING**

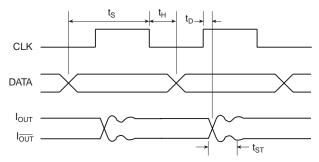

Each digital input is buffered, decoded, and then latched into D flip-flops which drive the output switches. Master-slave flip-flops are not used; thus, there is only a 1/2 clock period delay (max) from data change to output change. In this architecture, clock and data edge speeds (i.e., rise/fall times) may affect data feedthrough. Using a data edge of approximately 0.8 ns will cause data feedthrough of about 10 pV-s, while a 5 ns data edge will reduce the feedthrough to about 4 pV-s. Data lines may include series resistors or RC filters for edge control if desired.

The clock signal controls when the data is latched into the flip-flops. When the CLK is high, the DAC is in track mode. A negative going CLK latches the data. If CLK is held low, the DAC is in hold mode. See figure 2.

Figure 2 - Timing Diagram

$t_H = hold time$

t<sub>D</sub> = time to output valid

$t_S$  = setup time

t<sub>ST</sub> = settling time

Figure 3 – Equivalent Output Circuit

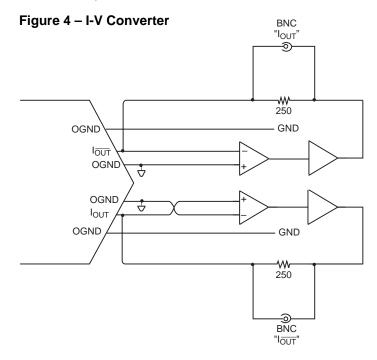

#### **OUTPUTS**

The output is comprised of current sinks, R-2R ladder, and associated parasitics. See figure 3 for an equivalent output circuit.

The DAC's full-scale output current when using the internal reference amplifier is determined by the voltage at pin AMP<sub>INB</sub> and the R<sub>SET</sub> resistance. It can be found (to within an LSB) by using the following formula:

$$I_{OUT}$$

FS = (AMP<sub>INB</sub>/R<sub>SET</sub>) x 16

The inputs determine whether the current from each sink comes from  $I_{OUT}$  or  $I_{\overline{OUT}}$  as follows:

| Code (D15 is MSB)  | I <sub>OUT</sub>               | Ι <sub>ουτ</sub>                    |

|--------------------|--------------------------------|-------------------------------------|

| 0 (zero scale)     | No current                     | All current                         |

| 32768 (mid-scale)  | $I_{OUT} = I_{\overline{OUT}}$ | I <sub>OUT</sub> = I <sub>OUT</sub> |

| 65535 (full-scale) | All current                    | No current                          |

Differential outputs facilitate maximum noise rejection and signal swing. The DAC is trimmed using a current to voltage (I-V) converter which provides a virtual ground at the outputs and includes sense lines to mitigate the impact of bus drops. Operating into a load other than a virtual ground will introduce a slight bow at the output. This bow is related to the current sinks' finite output impedance and ladder impedance.

An example circuit using an I-V converter is shown in figure 4. Note that resistor and op-amp self heating over the DAC's full-scale range will introduce additional temperature dependence. The op-amp and feedback resistor must both have very low tempcos if the DAC's intrinsic gain drift is to be maintained. A sense line helps reduce wire effects – both IR loss and temperature drift.

SPT5510

9/27/00

The feedback resistor should be matched to  $R_{SET}$  to reduce gain drift. Also, the op amp's ground reference should be the same as  $R_{SET}$ 's to reduce gain and offset errors. A composite amplifier may be required to obtain optimal dc performance. A differential circuit may be used; a common heat sink covering both sides (op amps and resistors) will help reduce temperature effects.

Achieving good settling performance requires careful board layout with multiple decoupling circuits and very clean power and ground routing. It is important that digital switching currents do not flow across analog input (REF<sub>IN</sub>) and output signals. Terminations must be broadband and near the device. Measuring settling performance is quite challenging and requires several test systems to ensure settling errors from the instruments are not included.

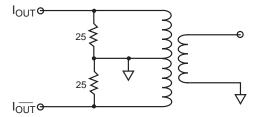

Dynamic performance characteristics (e.g., settling, rise and fall times, etc.) were measured with the outputs terminated to ground through 50  $\Omega$  resistors. SFDR was determined using a transformer to convert the output from differential to single-ended as shown in figure 5. The SPT5510 is designed primarily for step and settle or narrowband RF applications. The second harmonic generally dominates wideband SFDR measurements, although close-in spurs are very small.

Figure 5 - Transformer Output Circuit

Figure 6 – Reference Amplifier Circuit

#### **BANDGAP VOLTAGE REFERENCE**

The on-chip bandgap voltage reference is designed to bias the non-inverting input of the reference amplifier (AMP<sub>INB</sub>) through a resistor equal to R<sub>SET</sub> to help compensate the reference amplifier (see the following section). If the bandgap voltage is required by another DAC, or elsewhere in the system, it must be buffered with a precision op amp configured as a high impedance (e.g., unity gain follower) buffer. A resistor, or RC filter, plus a ferrite bead will help isolate the output from the reference amplifier's compensation and high-frequency charge pulses produced during operation. The output should always be very carefully checked for oscillations using a sensitive, wideband oscilloscope and spectrum analyzer.

#### **REFERENCE AMPLIFIER**

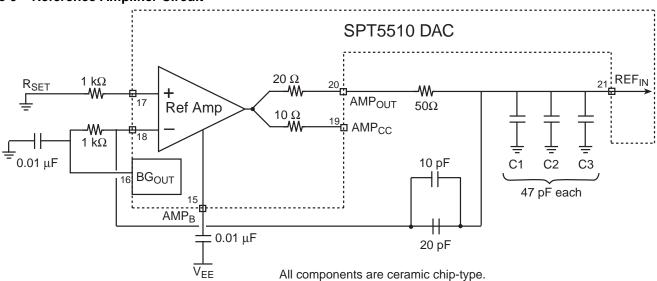

The reference amplifier is a highly temperature-stable driver to bias the precision current sinks. The reference amplifier should only be used to drive REF<sub>IN</sub>. Additional loads will change the amplifier's compensation, which can lead to instability and other settling issues.

There are two reference amplifier outputs:  $AMP_{OUT}$  and  $AMP_{CC}$ .  $AMP_{OUT}$  has a 20 ohm series resistor between the output of the reference amplifier and the  $AMP_{OUT}$  pin;  $AMP_{CC}$  has a 10 ohm resistor. These parallel outputs aide compensation and decoupling. The open-loop output impedance is approximately 1200 ohms.

Reference amplifier compensation is key to achieving high performance. Without proper compensation, oscillations that affect accuracy and settling time will occur. Figure 6 shows a typical reference amplifier compensation circuit. Note that several small value capacitors are used from REF<sub>IN</sub> to ground. This is to provide suitably low impedance

6

SPT5510

9/27/00

around 300 MHz, the amplifier's phase crossover point. The unity-gain bandwidth is roughly 700 MHz. Larger value capacitors exhibit lower self-resonance frequency and thus may not adequately compensate the reference amplifier. Large capacitors may also introduce low frequency tails which increase settling time. The DAC itself exhibits very broadband switching spikes (charge kickback) at the  $R_{\text{SET}}$  node, which can contribute to amplifier instability if not suppressed. Note that the AMP\_INB input must not be directly bypassed, as this will short all feedback to ground, leading to severe oscillation.

Compensation must be optimized for each application. As with any high-speed, high-resolution design, attention must be paid to grounding, decoupling, and parasitic elements that may cause instability. It may be wise to use a guard ring, and/or clear the board ground, around the reference amplifier's inputs. All traces must be short, and capacitors with high self-resonance must be used.

Compensation is perhaps the most challenging aspect of setting up the SPT5510. By slowly switching a full-scale data input (generating a low-frequency square wave), with appropriate clock timing, the DAC's output can be observed using a suitable oscilloscope and spectrum analyzer to observe and suppress any oscillations caused by board and decoupling parasitics. Consult SPT Applications for further assistance if required.

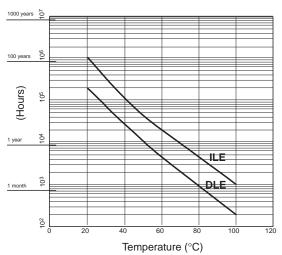

# LONG-TERM STABILITY VERSUS TEMPERATURE

As with all high-speed, high-resolution digital-to-analog converters, the initial accuracy of the device will degrade with both time and temperature. The graph shown in figure 7 can be used to determine the expected change in linearity performance over time when the device is operated at various ambient temperatures. This graph shows how long it will take for the SPT5510 linearity to change by 8 ppm (or 1/2 LSB) at any operating temperature. The top curve shown represents integral nonlinearity (ILE) changes; the bottom curve shows differential nonlinearity (DLE) changes.

Figure 7 - Linearity Performance over Time

Expected time required to produce an 8 ppm (1/2 LSB) linearity (ILE or DLE) shift as a function of temperature.

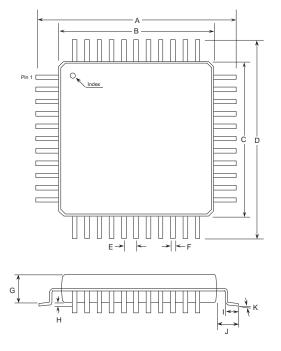

#### PACKAGE OUTLINE

#### 44-Lead MQFP

|        | INCHES     |        | MILLIMETERS |       |  |

|--------|------------|--------|-------------|-------|--|

| SYMBOL | MIN        | MAX    | MIN         | MAX   |  |

| Α      | 0.5098     | 0.5295 | 12.95       | 13.45 |  |

| В      | 0.3917     | 0.3957 | 9.95        | 10.05 |  |

| С      | 0.3917     | 0.3957 | 9.95        | 10.05 |  |

| D      | 0.5098     | 0.5295 | 12.95       | 13.45 |  |

| Е      | 0.0311     | 0.0319 | 0.79        | 0.81  |  |

| F      | 0.0118     | 0.0177 | 0.30        | 0.45  |  |

| G      | 0.0768     | 0.0827 | 1.95        | 2.10  |  |

| Н      | 0.0039     | 0.0098 | 0.10        | 0.25  |  |

| Ī      | 0.0287     | 0.0406 | 0.73        | 1.03  |  |

| J      | 0.0630 REF |        | 1.60 REF    |       |  |

| K      | 0°         | 7°     | 0°          | 7°    |  |

SPT5510

7 9/27/00

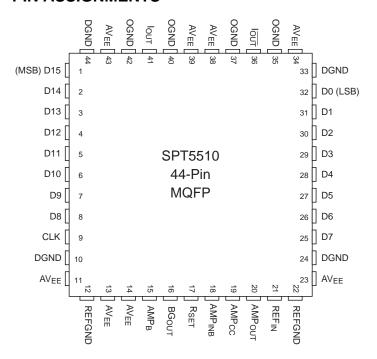

### **PIN ASSIGNMENTS**

# **PIN FUNCTIONS**

| NAME               | FUNCTION                                                                                                                            |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| D15-D0             | Digital Input Bits – all inputs high sends all current to I <sub>OUT</sub> , none to I <sub>OUT</sub>                               |  |

| CLK                | Clock – latches D flip-flops                                                                                                        |  |

| I <sub>OUT</sub>   | Analog Current Output                                                                                                               |  |

| lout               | Complementary Analog Current Output                                                                                                 |  |

| BG <sub>OUT</sub>  | Bandgap Voltage Reference                                                                                                           |  |

| AMP <sub>INB</sub> | Ref Amp's Inverting Input                                                                                                           |  |

| R <sub>SET</sub>   | Ref Amp's Non-Inverting Input – connection for reference-current-setting resistor, nominally $1k\Omega$ to ground                   |  |

| AMP <sub>OUT</sub> | Bias Voltage for Output Current Switches – drives REF $_{\mbox{\footnotesize{IN}}}$ (on-chip 20 $\Omega$ resistor for compensation) |  |

| REF <sub>IN</sub>  | Bias Voltage Node for Output Current Switches – driven by AMP <sub>OUT</sub>                                                        |  |

| AMP <sub>B</sub>   | Used to Decouple Ref Amp's Circuits to AV <sub>EE</sub>                                                                             |  |

| AMP <sub>CC</sub>  | $\mbox{AMP}_{\mbox{OUT}}$ plus on-chip 10 $\Omega$ series resistor for compensation                                                 |  |

| AV <sub>EE</sub>   | Negative Supply – -5.2 V                                                                                                            |  |

| DGND               | Digital Ground Return                                                                                                               |  |

| OGND               | Output Ground Return                                                                                                                |  |

| REFGND             | Reference Amplifier Ground Return                                                                                                   |  |

|                    |                                                                                                                                     |  |

## ORDERING INFORMATION

| PART NUMBER | TEMPERATURE RANGE | PACKAGE  |

|-------------|-------------------|----------|

| SPT5510SIM  | −40 to +85 °C     | 44L MQFP |

Signal Processing Technologies, Inc. reserves the right to change products and specifications without notice. Permission is hereby expressly granted to copy this literature for informational purposes only. Copying this material for any other use is strictly prohibited.

WARNING – LIFE SUPPORT APPLICATIONS POLICY – SPT products should not be used within Life Support Systems without the specific written consent of SPT. A Life Support System is a product or system intended to support or sustain life which, if it fails, can be reasonably expected to result in significant personal injury or death.

Signal Processing Technologies believes that ultrasonic cleaning of its products may damage the wire bonding, leading to device failure. It is therefore not recommended, and exposure of a device to such a process will void the product warranty.

SPT5510