# austriamicrosystems AG

is now

# ams AG

The technical content of this austriamicrosystems datasheet is still valid.

#### **Contact information:**

## **Headquarters:**

ams AG

Tobelbaderstrasse 30

8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0

e-Mail: ams\_sales@ams.com

Please visit our website at www.ams.com

# AS1339 650mA RF Step-Down DC-DC for PA, with two LDOs

# 1 General Description

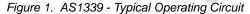

The AS1339 is a high-frequency step-down converter optimized for dynamically powering the power amplifier (PA) in WCDMA or NCDMA handsets. The device uses a  $110 \text{m}\Omega$  typical bypass FET to power the PA directly from the battery during high-power transmission. The IC integrates two 10mA low-noise, low-dropout regulators (LDOs) for PA biasing.

With a switching frequency of 2MHz, the device allows optimization for smallest solution size or highest efficiency. The AS1339 supports fast switching using small ceramic  $10\mu F$  input and  $4.7\mu F$  output capacitors to maintain low ripple voltage.

The AS1339 uses an analog input driven by an external DAC to control the output voltage linearly for continuous PA power adjustment. The gain from REFIN to OUT is 2.5V/V. At high-duty cycle, the device automatically switches to a bypass mode, connecting the input to the output through a low-impedance MOSFET. The LDOs are designed for low-noise operation, wherein each LDO in the device is individually enabled through its own logic control interface. The device is available in a 16-pin WLP (2x2mm) package.

# 2 Key Features

- Fixed Switching Frequency: 2MHz

- PA Step-Down Converter

- Low Dropout Voltage

- Low Output-Voltage Ripple

- Dynamic Output Voltage Control (0.8V to 3.75V)

- 30µs Settling Time for 0.8V to 3.4V Output Voltage Change

- 650mA Output Drive Capability

- Two 10mA Low-Noise LDOs

- Low Shutdown Current

- Supply Voltage Range: 2.7V to 5.5V

- Thermal Shutdown

- 16-pin WLP (2x2mm) package

# 3 Applications

The AS1339 is ideal for WCDMA/NCDMA cellular handsets, Wireless PDAs, and Smartphones.

# 4 Pinout

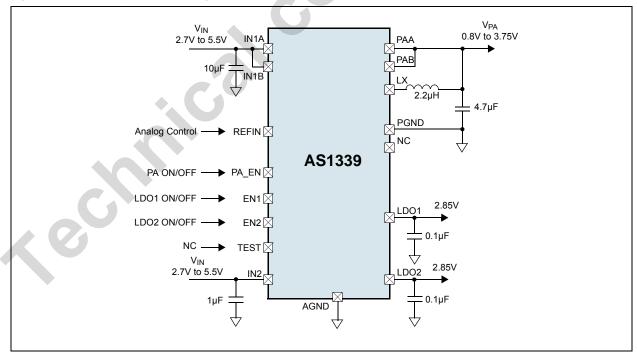

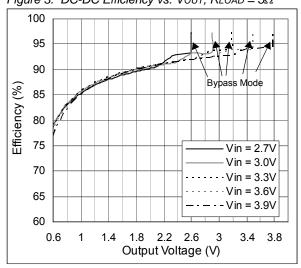

Figure 2. Pin Assignments (Top View)

## **Pin Description**

Table 1. Pin Description

| Pin Name | Pin Number | Description                                                                                                                                                                                                                |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       | A1         | <b>Not Connected.</b> Free, high impedance for normal operation. Used for internal test purpose.                                                                                                                           |

| AGND     | A2         | Low-Noise Analog Ground                                                                                                                                                                                                    |

| REFIN    | A3         | <b>DAC-Controlled Input.</b> Reference voltage for buck converter. The output of the PA step-down converter is regulated to 2.5 x VREFIN. Bypass mode is enabled when $VIN \le 2.69V$ x VREFIN.                            |

| PGND     | A4         | Power Ground for PA Step-Down Converter                                                                                                                                                                                    |

| LDO2     | B1         | <b>10mA LDO Regulator 2 Output.</b> Connect LDO2 with a $0.1\mu F$ ceramic capacitor as close as possible to LDO2 and AGND. LDO2 is internally pulled down through a $100\Omega$ resistor when this regulator is disabled. |

| PA_EN    | B2         | <b>PA Step-Down Converter Enable Input.</b> For normal operation, connect to logic-high. For shutdown mode, connect to logic-low. The pin is internally pulled down through a $110k\Omega$ resistor.                       |

| EN2      | ВЗ         | Enable Input for LDO2. For normal operation, connect to logic-high. For shutdown mode, connect to logic-low. The pin is internally pulled down through a $110k\Omega$ resistor.                                            |

| LX       | B4         | <b>Inductor Connection.</b> Connect an inductor from LX to the output of the PA step-down converter.                                                                                                                       |

Table 1. Pin Description

| Pin Name   | Pin Number | Description                                                                                                                                                                                                                                                                                          |

|------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN2        | C1         | Supply Voltage Input for LDO1 and LDO2. Connect IN2 to a battery or supply voltage from 2.7V to 5.5V. Decouple IN2 with a 1µF ceramic capacitor as close as possible to IN2 and AGND. Connect IN2 to the same source as IN1A and IN1B.                                                               |

| TEST       | C2         | <b>NC.</b> Used for internal test purpose. The pin is internally pulled down with a $110k\Omega$ resistor.                                                                                                                                                                                           |

| IN1B, IN1A | C3, C4     | Supply Voltage Input for PA Step-Down Converter. Connect IN1A/B to a battery or supply voltage from 2.7V to 5.5V. Decouple IN1A/B with a 10µF ceramic capacitor as close as possible to IN1A/B, and PGND. IN1A and IN1B are internally connected together. Connect IN1A/B to the same source as IN2. |

| LDO1       | D1         | <b>10mA LDO Regulator 1 Output.</b> Decouple LDO1 with a $0.1\mu F$ ceramic capacitor as close as possible to LDO1 and AGND. LDO1 is internally pulled down through a $100\Omega$ resistor when this regulator is disabled.                                                                          |

| EN1        | D2         | Enable Input for LDO1. For normal operation, connect to logic-high. For shutdown mode, connect to logic-low. The pin is internally pulled down through a $110k\Omega$ resistor.                                                                                                                      |

| PAB, PAA   | D3, D4     | PA Connection for Bypass Mode. Internally connected to IN1A/B using the internal bypass MOSFET during bypass mode. Connect PAA/B with a 4.7µF ceramic capacitor as close as possible to PAA/B and PGND.                                                                                              |

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 5 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                    | Min  | Max                      | Units | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------|------|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN1A, IN1B, IN2 to AGND                      | -0.3 | +7                       | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PAA, PAB, PA_EN, TEST, REFIN, NC to AGND     | -0.3 | VIN1A/<br>VIN1B +<br>0.3 | >     | .2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| LDO1, LDO2, EN1, EN2 to AGND                 | -0.3 | V <sub>IN2</sub> + 0.3   | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| REFIN Common-Mode Range                      | 0    | VIN                      | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| IN2 to IN1B/IN1A                             | -0.3 | +0.3                     | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PGND to AGND                                 | -0.3 | +0.3                     | V     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| LX Current                                   |      | 0.8                      | ARMS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Bypass Current                               |      | 1.6                      | ARMS  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Human Body Model                             |      | 1                        | kV    | HBM MIL-Std. 883E 3015.7 methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Storage Temperature Range                    | -65  | +150                     | °C    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Package Body Temperature                     | 8    | +260                     | °     | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020D "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".                                                                                                                                                                                                                                                                                                                                                                                |

| Continuous Power Dissipation PD-MAX          |      | 0.75                     | W     | Ta = +65°C; derate 12.5mW/°C above +65°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Junction Temperature (T <sub>J</sub> ) Range | -40  | +125                     | °C    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Ambient Temperature (T <sub>A</sub> ) Range  | -40  | +85                      | °C    | In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated.  Maximum ambient temperature ( $T_{A-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125^{\circ}C$ ), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to ambient thermal resistance of the part/package in the application ( $\theta_{JA}$ ), as given by the following equation: $T_{A-MAX} = T_{J-MAX-OP} - (\theta_{JA} \times P_{D-MAX})$ . |

# **6 Electrical Characteristics**

$V_{IN1A} = V_{IN1B} = V_{IN2} = V_{PA\_EN} = V_{EN1} = V_{EN2} = 3.6V$ ,  $T_{A} = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . Typical values are at  $T_{A} = +25^{\circ}\text{C}$ , (unless otherwise specified), for external components refer to Table 5 on page 7.

Table 3. Electrical Characteristics

| Symbol             | Parameter                                     | Condition                                                               | Min   | Тур  | Max   | Unit |

|--------------------|-----------------------------------------------|-------------------------------------------------------------------------|-------|------|-------|------|

| Input Su           | pply                                          |                                                                         |       |      |       |      |

| VIN                | Input Voltage Range                           |                                                                         | 2.7   |      | 5.5   | V    |

| ISHDN              | Shutdown Supply Current                       | VPA_EN = VEN1 = VEN2 = 0V <sup>1</sup>                                  |       | 0.1  | 1     | μA   |

| IQ                 | DC-DC No-Load Supply<br>Current               | VEN1 = VEN2 = 0V, ILOAD(DCDC) = 0mA, switching, VIN = 4.5V, VOUT = 3.4V |       | 4.5  | 6     | mA   |

| DCDC O             | utput Voltage                                 |                                                                         |       |      | 4     | 1    |

| ILOAD              | Load Current                                  |                                                                         |       |      | 650   | mA   |

|                    | Output Voltage Range                          | PWM Mode                                                                | 0.8   |      | 3.85  | V    |

| M                  |                                               | VREFIN = 0.32V, VIN = 3.9V                                              | 0.75  | 0.8  | 0.85  | V    |

| V <sub>OUT</sub>   | Output Voltage                                | VREFIN = 0.84V, <i>VIN</i> = 3.9V                                       | 2.05  | 2.1  | 2.15  | V    |

|                    |                                               | VREFIN = 1.36V, VIN = 3.9V                                              | 3.319 | 3.4  | 3.481 | V    |

| Thermal            | Protection                                    |                                                                         |       |      |       |      |

|                    | Thermal Shutdown                              | TA rising, 10°C typical hysteresis                                      |       | +140 |       | °C   |

| Logic Co           | ontrol                                        |                                                                         |       | •    |       |      |

|                    | PA_EN, EN1, EN2, Logic-<br>Input High Voltage | 2.7V ≤ VIN ≤ 5.5V                                                       | 1.4   |      |       | V    |

|                    | PA_EN, EN1, EN2, Logic-<br>Input Low Voltage  | 2.7V ≤ VIN ≤ 5.5V                                                       |       |      | 0.5   | V    |

|                    | Logic-Input Current                           | VIL = 0V                                                                | -1    |      | +1    | μΑ   |

|                    | (PA_EN, EN1, EN2)                             | VIH = VIN = 5.5V                                                        |       | 50   | 75    | μΑ   |

| REFIN              |                                               |                                                                         | 1     |      |       |      |

|                    | REFIN Operating Common-Mode Range             |                                                                         | 0.32  |      | 1.5   | V    |

|                    | 2                                             | VREFIN = 0.32V                                                          | 2.35  | 2.50 | 2.65  | V/V  |

|                    | REFIN gain Vout/VREFIN <sup>2</sup>           | VREFIN = 0.84V, 1.36V                                                   | 2.44  | 2.50 | 2.56  | V/V  |

|                    | REFIN Current                                 | VREFIN = VIN = 5.5V                                                     | -1    |      | +1    | μΑ   |

| LX                 |                                               |                                                                         |       |      |       |      |

| Procue             | Pin-Pin Resistance for PFET                   | I <sub>SW</sub> = 200mA; T <sub>A</sub> = +25°C                         |       | 110  | 200   | m()  |

| R <sub>DSONP</sub> | FIII-FIII RESISIANCE IUI PFE I                | I <sub>SW</sub> = 200mA                                                 |       |      | 230   | mΩ   |

| D                  | Pin-Pin Resistance for NFET                   | I <sub>SW</sub> = -200mA; T <sub>A</sub> = +25°C                        |       | 230  | 415   | m0   |

| R <sub>DSONN</sub> | FIII-PIII RESISIANCE IOI NEET                 | I <sub>SW</sub> = -200mA                                                |       |      | 485   | mΩ   |

|                    | PFET Leakage Current                          | VIN = 5.5V, VLX = 0V                                                    |       | 0.1  | 3     | μA   |

| 1                  | NFET Leakage Current                          | VIN = VLX = 5.5V                                                        |       | 0.1  | 3     | μΑ   |

|                    | PFET Peak Current Limit                       | VLX = 0V                                                                |       | 1100 |       | mA   |

Table 3. Electrical Characteristics (Continued)

| Symbol | Parameter                          | Condition                                      | Min           | Тур  | Max  | Unit |     |

|--------|------------------------------------|------------------------------------------------|---------------|------|------|------|-----|

| fosc   | Internal Oscillator Frequency      |                                                |               | 1.8  | 2    | 2.2  | MHz |

| BYPASS |                                    |                                                |               |      |      |      |     |

|        | Bypass Activation Factor           | VREFIN rising, 50mV hyst                       | teresis       | 2.56 | 2.69 | 2.78 | V/V |

|        | On Registance Bypage DEET          | I <sub>SW</sub> = 200mA; T <sub>A</sub> = +25° | С             |      | 110  | 200  | m() |

|        | On-Resistance Bypass PFET          | I <sub>SW</sub> = 200mA                        |               |      |      | 230  | mΩ  |

|        | PFET Bypass Off-Leakage<br>Current | <i>VIN</i> = 5.5V,<br>VPAA = VPAB = 0V         |               | 0.1  | 3    | μΑ   |     |

| LDO1/2 |                                    |                                                |               | I    |      |      | 750 |

|        | Output Voltage                     | IOUT = 0mA, 10mA;                              |               | 2.75 | 2.85 | 2.95 | V   |

|        | Quiescent Current                  | one LDO enabled                                | LOUIT - Omn A |      | 25   | 50   |     |

|        | Quiescent Current                  | both LDOs enabled                              | IOUT = 0mA    |      | 40   | 80   | μA  |

|        | Output Current                     |                                                | •             | 10   |      |      | A   |

|        | Current Limit                      | Vout = 0V                                      |               | 20   | 35   | 50   | mA  |

|        | Dropout Voltage <sup>3</sup>       | IOUT = 10mA                                    |               |      | 20   | 50   | mV  |

| Roff   | Shutdown Output Impedance          | VEN1/2 = 0V                                    |               |      | 100  |      | Ω   |

- 1. Current into supply pins without leakage of DCDC switches.

- 2. Limited by the 50mV output voltage accuracy for VREFIN < 0.84V

- 3. The dropout voltage is the input to output difference at which the output is 100mV below its nominal value.

## **System Characteristics**

$V_{IN1A} = V_{IN1B} = V_{IN2} = V_{PA\_EN} = V_{EN1} = V_{EN2} = 3.9V$ ,  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . Typical values are at  $T_A = +25^{\circ}\text{C}$ , (unless otherwise specified), for external components refer to Table 5 on page 7. The following parameters are verified by characterisation and are not production tested.

Table 4. System Characteristics

| Symbol  | Parameter                                             | Condition                                                                              | Min  | Тур | Max | Unit  |

|---------|-------------------------------------------------------|----------------------------------------------------------------------------------------|------|-----|-----|-------|

| REFIN   |                                                       |                                                                                        |      |     |     |       |

|         | REFIN gain variation; relative linearity <sup>1</sup> | 0.32V ≤ VREFIN ≤ 1.4V                                                                  |      |     | 3   | %     |

|         | REFIN gain variation;                                 | 0.84V ≤ VREFIN ≤ 1.4V                                                                  | -2.4 |     | 2.4 | %     |

|         | absolute linearity <sup>2</sup>                       | 0.32V ≤ VREFIN ≤ 0.84V                                                                 | -50  | ±10 | 50  | mV    |

| LX      |                                                       |                                                                                        |      |     |     |       |

|         | Ripple voltage, PWM mode <sup>3</sup>                 | Vout = 0.8 to 3.4V, RLOAD = $8\Omega$ , no bypass mode, no pulse-skip condition        |      | 10  | 25  |       |

| Line_tr | Line transient response                               | VIN = 3.4 to 3.9V, VOUT = 3.0V,<br>IOUT = 300mA, VIN increase 300mV in<br>10µs         |      | 30  | 50  | mVp-p |

| Load_tr | Load transient response                               | VIN = 3.4 to 4.2V, VOUT = 3.0V, $T_{RISE} = T_{FALL} = 10 \mu s$ , IOUT = 100 to 300mA |      | 50  | 70  |       |

Table 4. System Characteristics (Continued)

| Symbol | Parameter                     | Condition                                                                                       | Min | Тур | Max | Unit  |

|--------|-------------------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

|        | Start-Up Time                 | From PA_EN switch from 0V to 1.7V,<br>VOUT = 3.4V, ILOAD = 0mA, within 50mV<br>regulation error |     | 100 | 150 |       |

|        | Regulation Time; Rise Time    | Vout from 0.8V to 3.4V, RLOAD = $8\Omega$ , within 50mV regulation error                        |     | 30  | 50  | μs    |

|        | Regulation Time; Fall Time    | Vout from 3.4V to 0.8V, RLOAD = 8Ω, within 50mV regulation error                                |     |     |     |       |

| LDO    |                               |                                                                                                 |     |     |     |       |

|        | Start-Up Time                 | IOUT=10mA, within 100mV of VOUT                                                                 |     | 30  | 50  | 7     |

|        | Shut-Down Time                | IOUT=0mA, within 100mV of GND                                                                   |     | 50  | 100 | μs    |

|        | Line Regulation <sup>4</sup>  | VIN = 4V to 3.5V; IOUT = 10mA;                                                                  |     |     | 10  | mV    |

|        | Load Regulation               | IOUT stepped from 50μA to 10mA                                                                  |     |     | 25  | 1114  |

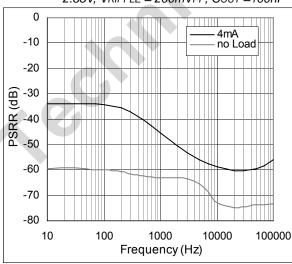

|        | D D 5                         | IOUT = 4mA, VIN = 3.2V, f = 100kHz                                                              | 45  |     |     | ٩D    |

|        | Ripple Rejection <sup>5</sup> | IOUT = 4mA, VIN = 3.2V, f = 2MHz                                                                | 45  |     |     | dB    |

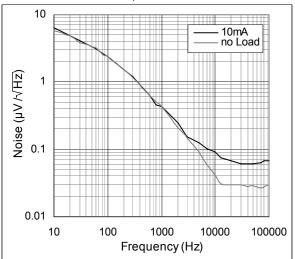

|        | Output Noise <sup>6</sup>     | 10Hz to 100kHz, IOUT = 10mA                                                                     | 9   | 50  | 100 | μVRMS |

- 1. The relative linearity is defined as the difference of the minimum to the maximum gain over the entire REFIN range.

- 2. The absolute linearity is defined as the actual gain error (AE) of every applied VREFIN voltage between 0.32V and 1.4V.

$$AE = \left(\frac{V_{OUT}}{2, 5 \times V_{REFIN}} - 1\right) \times 100$$

- The ripple voltage should measured at C<sub>OUT</sub> electrode on good layout PC board and under condition using suggested inductors and capacitors.

- 4. For dynamic change in Vout (Line transient response) when VIN drops 500mV from 4V (see Figure 48 on page 15); Slew rate= 40mV/µs.

- 5. VRIPPLE = 200mVpp; TA = +25°C; CIN1, CIN2 removed; PA EN = 0V;

- 6. VIN = 3.2V; TA = +25°C; PA\_EN = 3.2V;

Table 5. External Components used for Characterisation

| Name         | Part Number        | Value | Rating | Туре  | Size          | Manufacturer             |

|--------------|--------------------|-------|--------|-------|---------------|--------------------------|

| CIN1         | GRM21BR60J106KE01  | 10μF  | 6.3V   | X5R   | 0805          | Murata                   |

| CIN2         | GRM155R61A105KE15  | 1µF   | 10V    | X5R   | 0402          | www.murata.com           |

| Соит         | C0603C475K8PAC7867 | 4.7µF | 10V    | X5R   | 0603          | KEMET                    |

| CLDO1, CLDO2 | C0402C104K4RAC     | 100nF | 16V    | X7R   | 0402          | www.kemet.com            |

| L            | MLP2520S3R3S       | 3.3µH | 1A     | 110mΩ | 2.2x2.0x1.4mm | TDK<br>www.coilcraft.com |

# 7 Typical Operation Characteristics

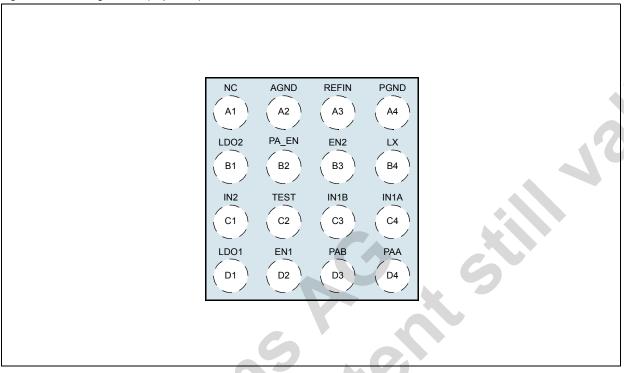

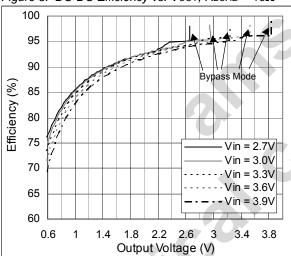

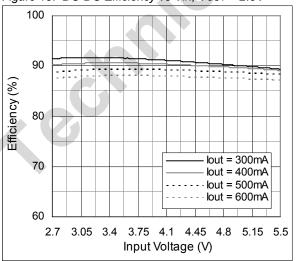

Figure 3. DC-DC Efficiency vs. Vout; RLOAD =  $5\Omega$

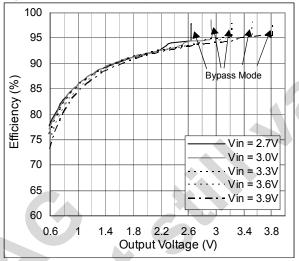

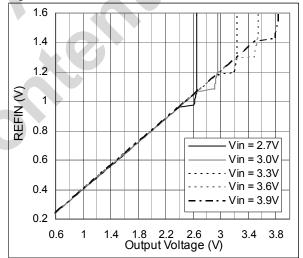

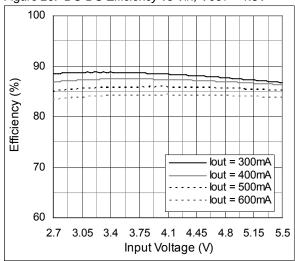

Figure 5. DC-DC Efficiency vs. Vout; RLOAD =  $10\Omega$

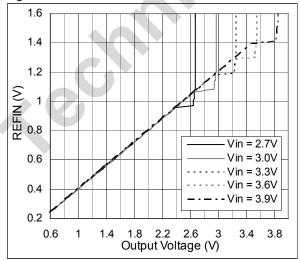

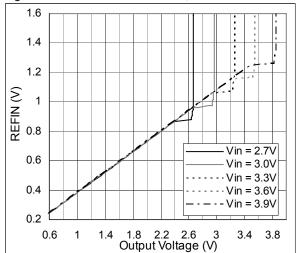

Figure 7. DC-DC REFIN vs. Vout; RLOAD =  $7.5\Omega$

Figure 4. DC-DC Efficiency vs. Vout; RLOAD =  $7.5\Omega$

Figure 6. DC-DC REFIN vs. Vout; RLOAD =  $5\Omega$

Figure 8. DC-DC REFIN vs. Vout; RLOAD =  $10\Omega$

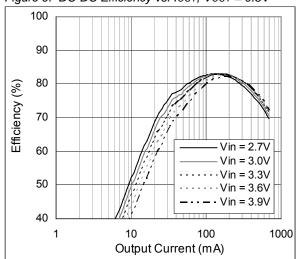

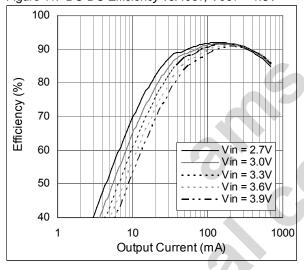

Figure 9. DC-DC Efficiency vs. IOUT; VOUT = 0.8V

Figure 10. DC-DC Efficiency vs. IOUT; VOUT = 1.2V

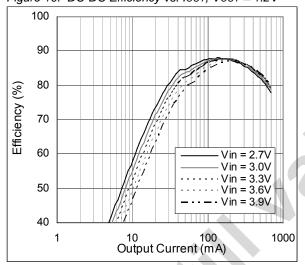

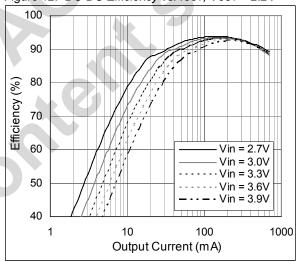

Figure 11. DC-DC Efficiency vs. IOUT; VOUT = 1.8V

Figure 12. DC-DC Efficiency vs. IOUT; VOUT = 2.2V

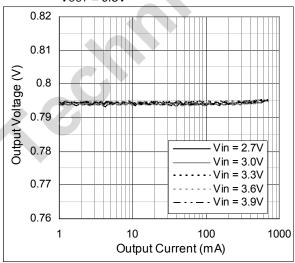

Figure 13. DC-DC Load Regulation, Vout vs. IOUT; VOUT = 0.8V

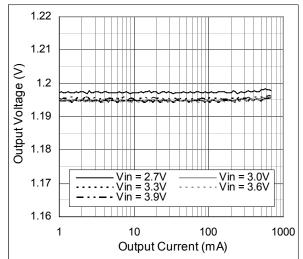

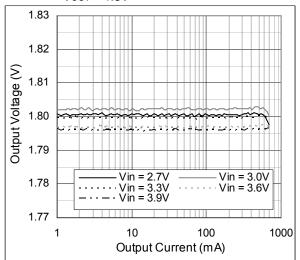

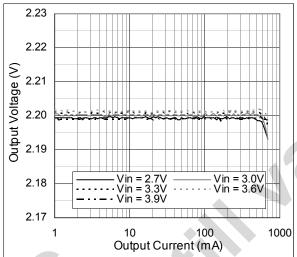

Figure 14. DC-DC Load Regulation, Vout vs. Iout; Vout = 1.2V

Figure 15. DC-DC Load Regulation, Vout vs. Iout; Vout = 1.8V

Figure 16. DC-DC Load Regulation, Vout vs. Iout; Vout = 2.2V

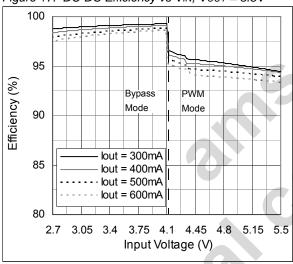

Figure 17. DC-DC Efficiency vs VIN; Vout = 3.8V

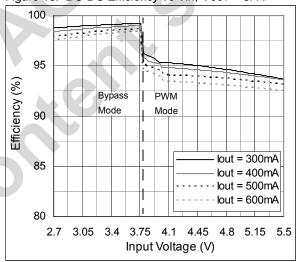

Figure 18. DC-DC Efficiency vs VIN; Vout = 3.4V

Figure 19. DC-DC Efficiency vs VIN; VOUT = 2.0V

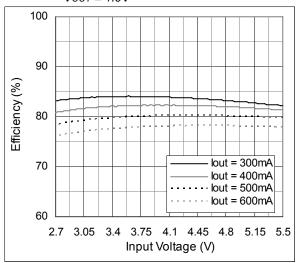

Figure 20. DC-DC Efficiency vs VIN; VOUT = 1.5V

Figure 21. DC-DC Efficiency vs Input Voltage; Vout = 1.0V

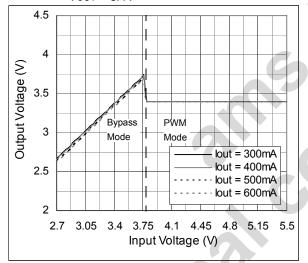

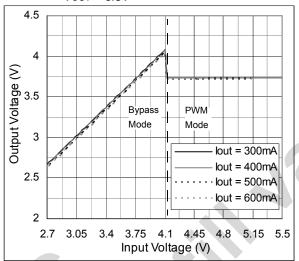

Figure 23. DC-DC Line Regulation, Vout vs. VIN; Vout = 3.4V

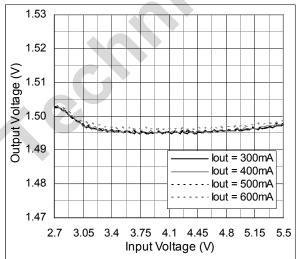

Figure 25. DC-DC Line Regulation, Vout vs. Vin; Vout = 1.5V

Figure 22. DC-DC Line Regulation, Vout vs. VIN; Vout = 3.8V

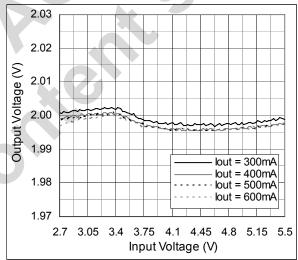

Figure 24. DC-DC Line Regulation, Vout vs. VIN; Vout = 2.0V

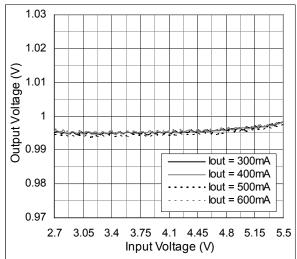

Figure 26. DC-DC Line Regulation, Vout vs.  $V_{IN}$ ;  $V_{OUT} = 1.0V$

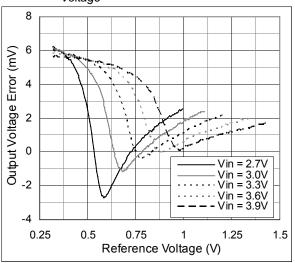

Figure 27. DC-DC Output Voltage Error vs. Reference Voltage

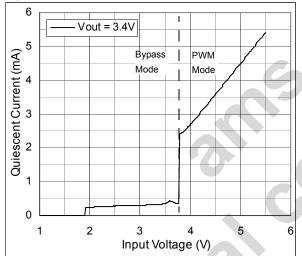

Figure 29. DC-DC No-Load Supply Current vs. VIN

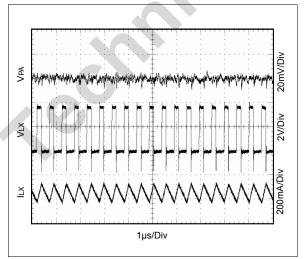

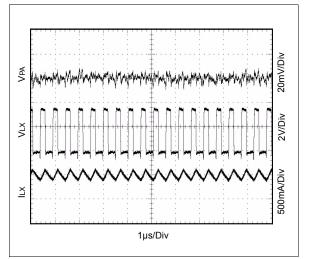

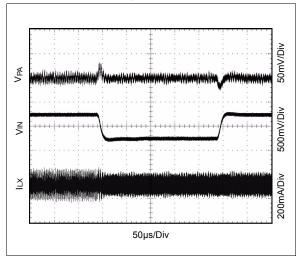

Figure 31. DC-DC Switching; VIN=3.6V, VPA=1.2V, IOUT=50mA

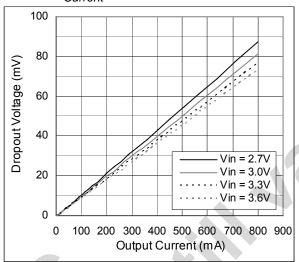

Figure 28. DC-DC Bypass Dropout Voltage vs. Output Current

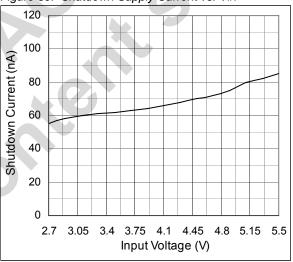

Figure 30. Shutdown Supply Current vs. VIN

Figure 32. DC-DC Switching; VIN=3.6V, VPA=1.2V, IOUT=500mA

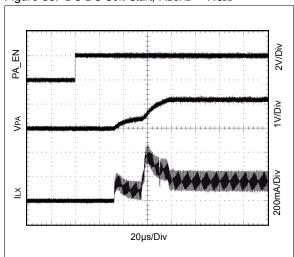

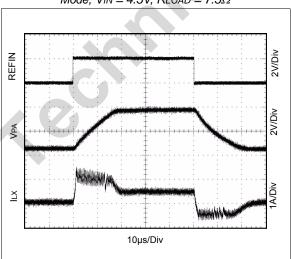

Figure 33. DC-DC Soft-Start;  $RLOAD = 7.5\Omega$

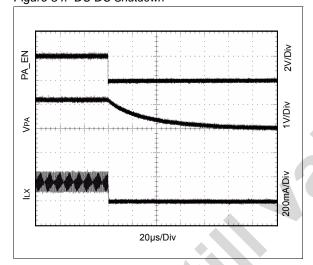

Figure 34. DC-DC Shutdown

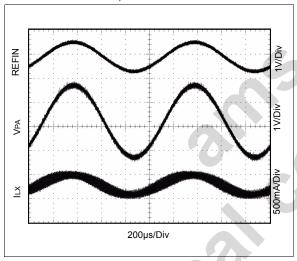

Figure 35. DC-DC Sine Wave Output in PWM Mode; VIN = 4.5V,  $RLOAD = 7.5\Omega$

Figure 36. DC-DC Sine Wave Output in Bypass Mode;  $VIN = 3.6V, RLOAD = 7.5\Omega$

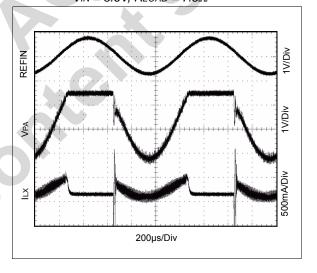

Figure 37. DC-DC Rectangular Wave Output in PWM Mode;  $V_{IN} = 4.5V$ ,  $R_{LOAD} = 7.5\Omega$

Figure 38. DC-DC Rectangular Wave Output in Bypass Mode; VIN = 3.6V,  $RLOAD = 7.5\Omega$

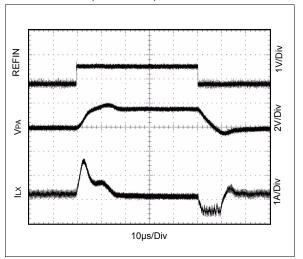

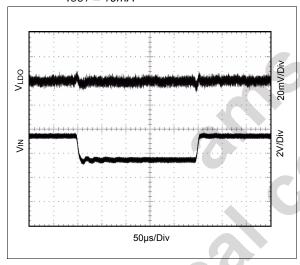

Figure 39. DC-DC Line Transient; VIN = 4.0V to 3.5V, VOUT = 1.2V, RLOAD = 10 $\Omega$

Figure 40. DC-DC Load Transient; IOUT = 0mA to 500mA, VIN = 3.6V, VOUT = 2.5V

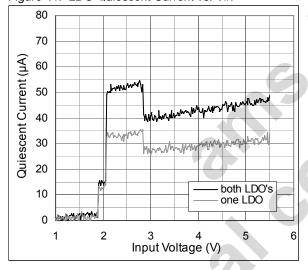

Figure 41. LDO Quiescent Current vs. VIN

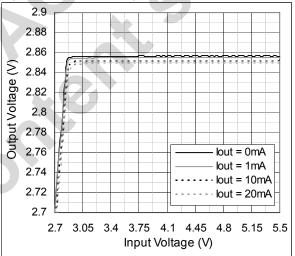

Figure 42. LDO Line Regulation, Vout vs. VIN

Figure 43. LDO PSRR vs. Freq.; VIN = 3.2V, VOUT = 2.85V, VRIPPLE = 200mVPP, COUT = 100nF

Figure 44. LDO Output Noise vs. Freq.; VIN = 3.2V, VOUT = 2.85V, COUT = 100nF

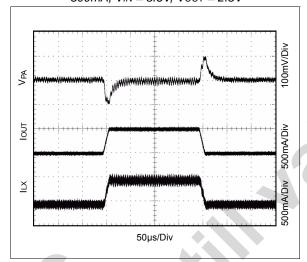

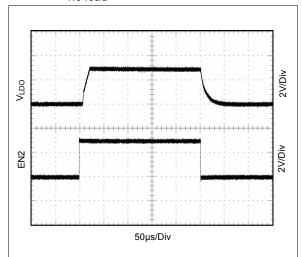

Figure 45. LDO Turn ON/OFF Response; VIN = 3.6V, no load

Figure 46. LDO Load Transient; IOUT = 0mA to 10mA, VIN = 3.6V

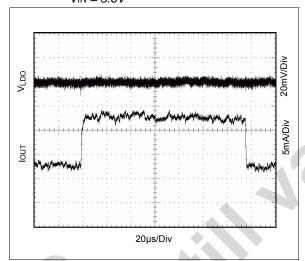

Figure 47. LDO Line Transient; VIN = 5.5V to 3.5V, IOUT = 10mA

Figure 48. LDO Line Transient; VIN = 4.0V to 3.5V, IOUT = 10mA

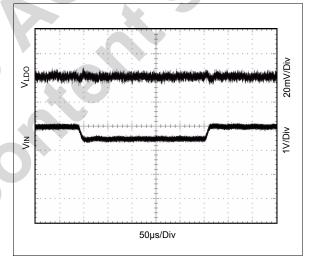

# 8 Detailed Description

The AS1339 is designed to dynamically power the PA in WCDMA and NCDMA handsets. The device is empowered with a high-frequency, high-efficiency step-down converter, and two LDOs. The step-down converters are capable of delivering 650mA. The PWM control scheme provides fast transient response, while 2MHz switching frequency allows the trade-off between efficiency and small external components. A  $110m\Omega$  bypass FET connects the PA directly to the battery during high-power transmission.

Figure 49. AS1339 - Block Diagram

## **Operating the AS1339**

The AS1339's control block turns on the internal PFET (P-channel MOSFET) switch during the first part of each switching cycle, thus allowing current to flow from the input through the inductor to the output filter capacitor and load. The inductor limits the current to a ramp with a slope of (VIN - VOUT) / L, by storing energy in a magnetic field.

During the second part of each cycle, the controller turns the PFET switch off, blocking current flow from the input, and then turns the NFET (N-channel MOSFET) synchronous rectifier on. As a result, the inductor's magnetic field collapses, generating a voltage that forces current from ground through the synchronous rectifier to the output filter capacitor and load.

While the stored energy is transferred back into the circuit and depleted, the inductor current ramps down with a slope of Vout / L. The output filter capacitor stores charge when the inductor current is high, and releases it when low, smoothing the voltage across the load. The output voltage is regulated by modulating the PFET switch on-time to control the average current sent to the load.

The output voltage is equal to the average voltage at the LX pin.

While in operation, the output voltage is regulated by switching at a constant frequency and then modulating the energy per cycle to control the power to the load. Energy per cycle is set by modulating the PFET switch on-time pulse width to control the peak inductor current. This is done by comparing the signal from the current-sense amplifier with a slope compensated error signal from the voltage-feedback error amplifier. At the beginning of each cycle, the clock turns on the PFET switch, causing the inductor current to ramp up. When the current sense signal ramps past the error amplifier signal, the PWM comparator turns off the PFET switch and turns on the NFET synchronous rectifier, ending the first part of the cycle.

If an increase in load pulls the output down, the error amplifier output increases, which allows the inductor current to ramp higher before the comparator turns off the PFET. This increases the average current sent to the output and

adjusts for the increase in the load. Before appearing at the PWM comparator, a slope compensation ramp from the oscillator is subtracted from the error signal for stability of the current feedback loop.

#### **Internal Synchronous Rectifier**

To reduce the rectifier forward voltage drop and the associated power loss, the AS1339 uses an internal NFET as a synchronous rectifier. The big advantage of a synchronous rectification is the higher efficiency in a condition where the output voltage is low compared to the voltage drop across an ordinary rectifier diode. During the inductor current down slope in the second part of each cycle the synchronous rectifier is turned on. Before the next cycle the synchronous rectifier is turned off.

There is no need for an external diode because the NFET is conducting through its intrinsic body diode during the transient intervals before it turns on.

## **Bypass Mode**

This mode connects IN1A and IN1B directly to PAA and PAB with the internal  $110m\Omega$  (typ) bypass FET, while the step-down converter is forced into 100% duty-cycle operation during high-power transmission. Due to the low on-resistance in this mode, the result is low dropout, high efficiency and a high output current capability.

The AS1339 enters bypass mode automatically when  $VIN \le 2.69 \text{ x VREFIN}$  and thus prevents excessive output ripple as the step-down converter approaches dropout. Due to an internal limitation of VREFIN  $\le 1.5V$  the maximum output voltage is limited to  $2.78 \times 1.5V = 4.17V$  in Bypass Mode.

#### **Shutdown Mode**

To put the PA step-down converter in shutdown mode, connect PA\_EN to GND or disconnect PA\_EN (NC =>logic-low). During shutdown mode, the control circuitry, internal switching MOSFET, and synchronous rectifier are turned off and LX becomes high impedance. For normal operation, connect PA\_EN to IN1A/B or logic-high.

To place LDO1 or LDO2 in shutdown mode, connect EN1 or EN2 to GND or disconnect EN1 or EN2 (NC => logic-low). The outputs of the LDOs are pulled to ground through an internal  $100\Omega$  resistor during shutdown. When the PA stepdown and LDOs are all in shutdown, the AS1339 enters a very low power state, where the input current drops to  $0.8\mu$ A (typ).

**Note:** All enable Pins (PA EN, EN1 and EN2) have an internal  $110k\Omega$  pull-down resistance.

#### **Soft-Start**

The internal soft-start circuitry of the PA step-down converter limits inrush current at startup, reducing transients on the input source. Soft-start is favorable for supplies with high output impedance such as Li+ and alkaline cells. The DC-DC can start-up with full output load of  $7.5\Omega$ .

#### **Analog REFIN Control**

The PA step-down converter uses REFIN to set the output voltage, which enables the converter to operate in applications requiring dynamic voltage control. The output voltage is limited to an upper level of 3.85V, when operating in PWM mode. In Bypass mode the output voltage is limited to VIN.

#### Notes:

- 1.  $VOUT = 2.5 \times VREFIN$

- 2. If REFIN is left floating the output voltage of the step-down converter can assume any value between 0.6V and Vin.

#### Thermal Overload Protection

To prevent the AS1339 from short-term misuse and overload conditions the chip includes a thermal overload protection. To block the normal operation mode the device is turning off the PFET and the NFET in PWM and bypass mode as soon as the junction temperature exceeds 140°C. To resume the normal operation the temperature has to drop below 130°C.

Note: Continuing operation in thermal overload conditions may damage the device and is considered bad practice.

# 9 Application Information

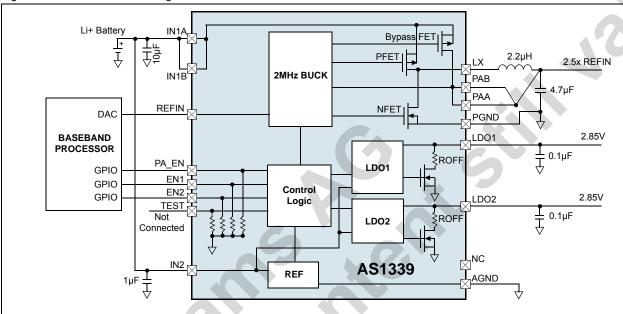

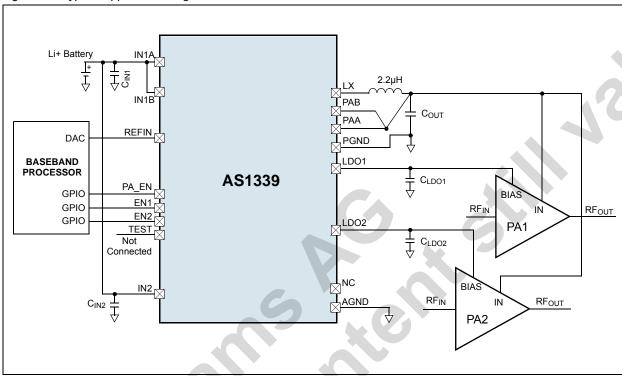

The AS1339 is designed to supply power amplifiers for RF applications. The output power of the PA can directly be controlled via the output voltage of the AS1339. Figure 50 shows a typical application.

Figure 50. Typical Application Diagram

## **Capacitor Selection for Step-Down Converter**

#### **Input Capacitor**

To reduce the current peaks drawn from the battery or power source and to reduce the switching noise in the device an input capacitor is highly recommended. At the switching frequency the impedance of the capacitor should be very low. It's recommended to use a X5R or X7R dielectric multilayer ceramic capacitor due to their small size, low ESR and small temperature coefficients. For most applications a  $4.7\mu F$  capacitor is sufficient. To decrease the interfering noise and to lower the input ripple the capacitor value can be set higher (e.g.  $10\mu F$ ).

#### **Output Capacitor**

To ensure a stable loop regulation and a small output voltage ripple a low impedance capacitor should be used. It's recommended to use a X5R or X7R dielectric multilayer ceramic capacitor due to their small size, low ESR and small temperature coefficients. For most applications a  $4.7\mu F$  capacitor is sufficient. To achieve a better load-transient performance and to decrease the output ripple the capacitor value can be set higher (e.g.  $10\mu F$ ).

Table 6. Recommended Capacitors for the Step-Down Converter

| Name       | Part Number        | С     | Voltage | Туре | Size | Manufacturer           |

|------------|--------------------|-------|---------|------|------|------------------------|

| CIN1. COUT | GRM21BR60J106KE01  | 10μF  | 6.3V    | X5R  | 0805 | Murata                 |

|            | GRM21BR61C475KA88  | 4.7µF | 16V     | X5R  | 0805 | www.murata.com         |

| J., 3001   | C0603C475K8PAC7867 | 4.7μF | 10V     | X5R  | 0603 | KEMET<br>www.kemet.com |

## Capacitor Selection for LDO's

#### **Input Capacitor**

The capacitor for the LDO Input should have at least a value of the sum of the output capacitors of LDO1 and LDO2. With a larger input capacitance and lower ESR a better noise rejection and line transient response can be achieved.

#### **Output Capacitor**

For the LDO outputs the capacitor value depends on the needed load current. For a stable operation with rated maximum load currents a minimum output capacitor of 1µF is recommended. At light loads of 10mA or less a 0.1µF capacitor is sufficient. With larger output capacitance a reduced output noise, improved load-transient response, better stability and power-supply rejection can be achieved.

Table 7. Recommended Capacitors for the LDO's

| Name         | Part Number       | С     | Voltage | Туре | Size | Manufacturer             |

|--------------|-------------------|-------|---------|------|------|--------------------------|

| CIN2, CLDO1, | C0402C104K4RAC    | 100nF | 16V     | X7R  | 0402 | KEMET<br>www.kemet.com   |

| CLDO2        | GRM155R61A105KE15 | 1µF   | 10V     | X5R  | 0402 | Murata<br>www.murata.com |

#### **Inductor Selection**

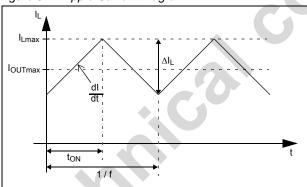

For most applications the value of the external inductor should be in the range of  $1.5\mu H$  to  $4.7\mu H$  as the inductor value has a direct effect on the ripple current. The selected inductor must be rated for its DC resistance and saturation current. The inductor ripple current ( $\Delta IL$ ) decreases with higher inductance and increases with higher VIN to VOUT.

In Equation (EQ 3) the maximum inductor current in PWM mode under static load conditions is calculated. The saturation current of the inductor should be rated higher than the maximum inductor current as calculated with Equation (EQ 4). This is recommended because the inductor current will rise above the calculated value during heavy load transients.

The inductor current ripple  $\Delta IL$  (see EQ 3) is defined by the slope of the current (dI / dt) (see EQ 1) multiplied by the PFET on-time ton (see EQ 2).

Figure 51. Ripple Current Diagram

$$\frac{dI}{dt} = \frac{V_{IN} - V_{OUT}}{L} \tag{EQ 1}$$

$$t_{ON} = DutyCycle \times \frac{1}{f}$$

$DutyCycle = \frac{V_{OUT}}{V_{IN}}$  (EQ 2)

$$\Delta I_L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f \times L}$$

(EQ 3)

$$I_{LMAX} = I_{OUTMAX} + \frac{\Delta I_L}{2}$$

(EQ 4)

f .... Switching Frequency (2.0MHz typical)

L .... Inductor Value

ILMAX .... Maximum Inductor current

$\Delta I_L$  .... Peak to Peak inductor ripple current

IOUTMAX .... Applied load current

Accepting larger values of ripple current allows the use of low inductance values, but results in higher output voltage ripple, greater core losses, and lower output current capability. The total losses of the coil have a strong impact on the efficiency of the dc/dc conversion and consist of both the losses in the dc resistance and the following frequency-dependent components:

- 1. The losses in the core material (magnetic hysteresis loss, especially at high switching frequencies)

- 2. Additional losses in the conductor from the skin effect (current displacement at high frequencies)

- 3. Magnetic field losses of the neighboring windings (proximity effect)

- 4. Radiation losses

Note: For highest efficiency, a low DC-resistance inductor is recommended.

Table 8. Recommended Inductors

| Part Number    | L     | DCR                    | <b>Current Rating</b> | Dimensions (L/W/T) | Manufacturer      |

|----------------|-------|------------------------|-----------------------|--------------------|-------------------|

| MLP2520S1R5S   | 1.5µH | $80 \text{m}\Omega$    | 1.5A                  | 2.5x2.0x1.2mm      | TDK               |

| MLP2520S2R2S   | 2.2µH | 110mΩ                  | 1.2A                  | 2.5x2.0x1.2mm      | www.tdk.com       |

| MLP2520S3R3S   | 3.3µH | 110mΩ                  | 1.0A                  | 2.5x2.0x1.2mm      |                   |

| EPL2014-222MLC | 2.2µH | 120mΩ                  | 0.98A                 | 2.2x2.0x1.4mm      | Coilcraft         |

| EPL2014-332MLC | 3.3µH | 152mΩ                  | 0.8A                  | 2.2x2.0x1.4mm      | www.coilcraft.com |

| EPL2014-472MLC | 4.7µH | 231mΩ                  | 0.65A                 | 2.2x2.0x1.4mm      |                   |

| XPL2010-222ML  | 2.2µH | 156m $\Omega$          | 1.2A                  | 2.0x1.9x1.0mm      |                   |

| XPL2010-332ML  | 3.3µH | $207 \mathrm{m}\Omega$ | 0.925A                | 2.0x1.9x1.0mm      |                   |

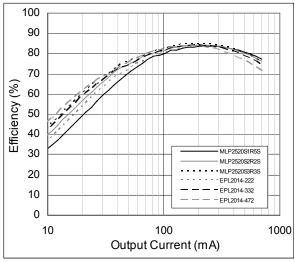

Figure 52. Efficiency Comparison of different Inductors; VIN = 3.9V, VOUT = 1.0V

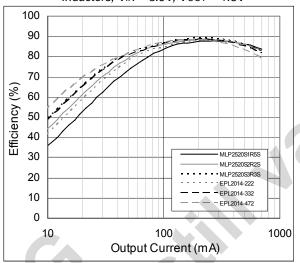

Figure 53. Efficiency Comparison of different Inductors; VIN = 3.9V, VOUT = 1.5V

## **Example**

The following system should be designed:

- A supply with a Lithium-Ion Battery = 4.5V

- Vout = 3.0V

- Iоитмах = 500mA

For the first step VREF is calculated as shown in Equation (EQ 5).

$$V_{REF} = \frac{V_{OUT}}{2.5} = 1,2V$$

(EQ 5)

$$V_{IN} \le 2,69 \times V_{REF} \tag{EQ 6}$$

Due to Equation (EQ 6): VIN = 3.23V

If Vin is falling below 3.23V the device is going into Bypass mode (see Bypass Mode on page 17).

Hence a 2.2μH coil is used, ΔIL can be calculated with Equation (EQ 3): ΔIL= 227mA

With this result IMAX can be calculated with Equation (EQ 4): IMAX = 614mA.

The saturation current of the coil should be chosen slightly higher than IMAX because heavy load transients could increase the peak current. For a short period of time (~50µs) the peak inductor current can rise up to a value of approximately 1.1A (p-channel MOSFET peak current limit). In this case a coil with a rated saturation current of ~800mA can be chosen.

## **Layout Considerations**

Please carefully observe that large peak currents of up to 1.1A and high switching frequencies will make the PCB layout a very important part of the system performance and compliance. A proper PCB design will minimize electro magnetic interference (EMI) as well as voltage gradients in the ground plane, which both can result in application instabilities. Please closely follow the guidelines as mentioned below.

- Keep the power traces as short and wide as possible (IN1A, IN1B, IN2, LX, PAA, PAB, PGND)

- Place all capacitors as close as possible to the pins of the device

- Avoid voltage gradients in the ground plane

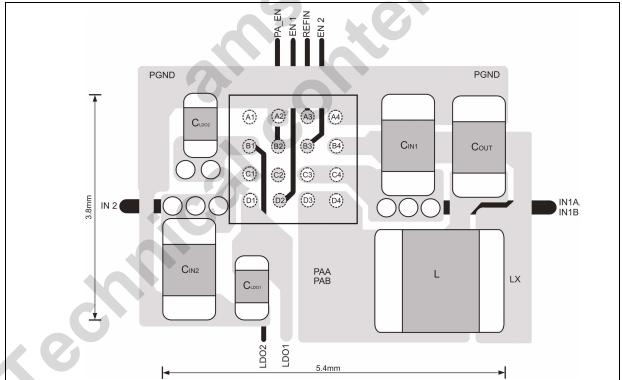

Please note the following PCB layout considerations shown in Figure 54:

- The negative terminals of COUT and CIN1/CIN2 are kept as close as possible to each other. It is recommended to connect these terminals directly to PGND at a star point.

- The current path between pins IN1A/IN1B (C3/C4) and pin PGND (A4) via CIN1 is routed very short

- The current path between pins PAB/PAA (D3/D4) and pin PGND (A4) via COUT is routed very short

- The connection between LX (B4) and pins PAB/PAA (D3/D4) via the coil (L) is routed very short

- To keep the cross-coupling between the LDOs and DC/DC minimized, in regard to supply ripple and noise induction, the IN1 and IN2 path are separated. Both power inputs should be connected at a star point directly at the main supply

- To prevent voltage gradients between AGND (A2) and PGND (A4), these pins are connected via a short, low ohmic. trace to each other.

Figure 54. Layout for Space Limited Applications

# 10 Package Drawings and Markings

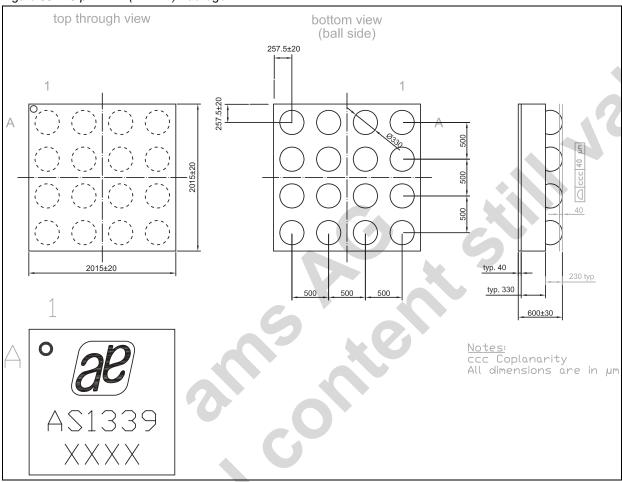

The devices are available in a 16-pin WLP (2x2mm) package.

Figure 55. 16-pin WLP (2x2mm) Package

# 11 Ordering Information

The devices are available as the standard products shown in Table 9.

Table 9. Ordering Information

| Ordering Code | Marking | Description                                    | Delivery Form | Package            |

|---------------|---------|------------------------------------------------|---------------|--------------------|

| AS1339-BWLT   | AS1339  | 650mA RF Step-Down DC-DC for PA, with two LDOs | Tape and Reel | 16-pin WLP (2x2mm) |

Note: All products are RoHS compliant and Pb-free.

Buy our products or get free samples online at ICdirect: http://www.austriamicrosystems.com/ICdirect

For further information and requests, please contact us mailto:sales@austriamicrosystems.com or find your local distributor at http://www.austriamicrosystems.com/distributor

## Copyrights

Copyright © 1997-2009, austriamicrosystems AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### **Disclaimer**

Devices sold by austriamicrosystems AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. austriamicrosystems AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. austriamicrosystems AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with austriamicrosystems AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by austriamicrosystems AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by austriamicrosystems AG is believed to be correct and accurate. However, austriamicrosystems AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of austriamicrosystems AG rendering of technical or other services.

#### **Contact Information**

Headquarters austriamicrosystems AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria

Tel: +43 (0) 3136 500 0 Fax: +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.austriamicrosystems.com/contact