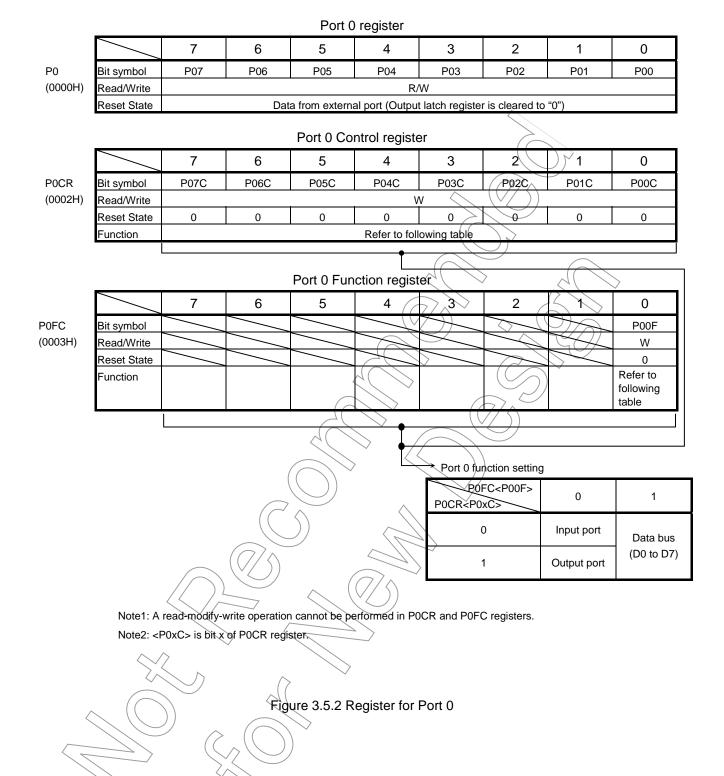

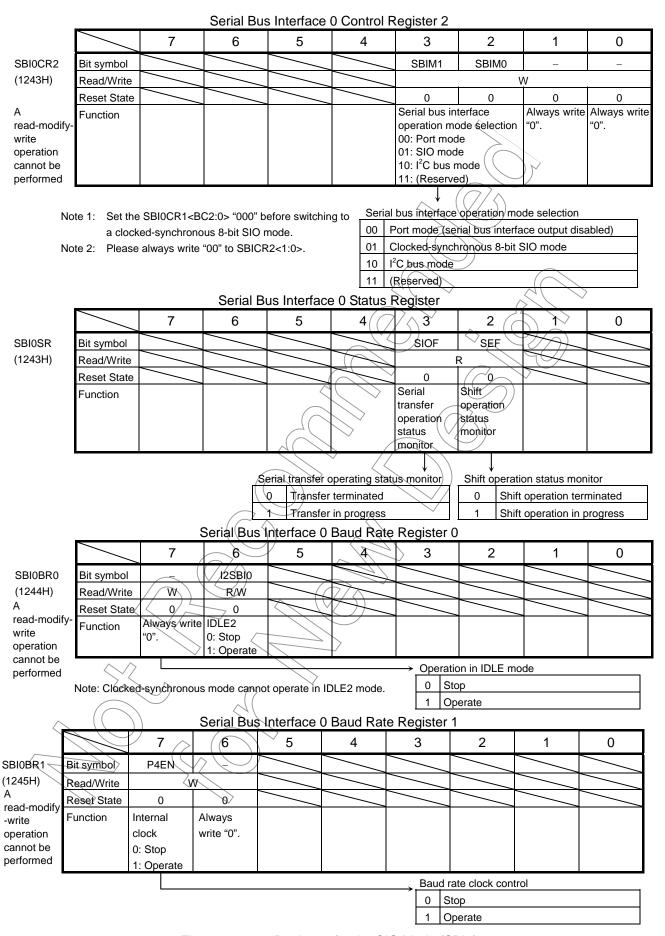

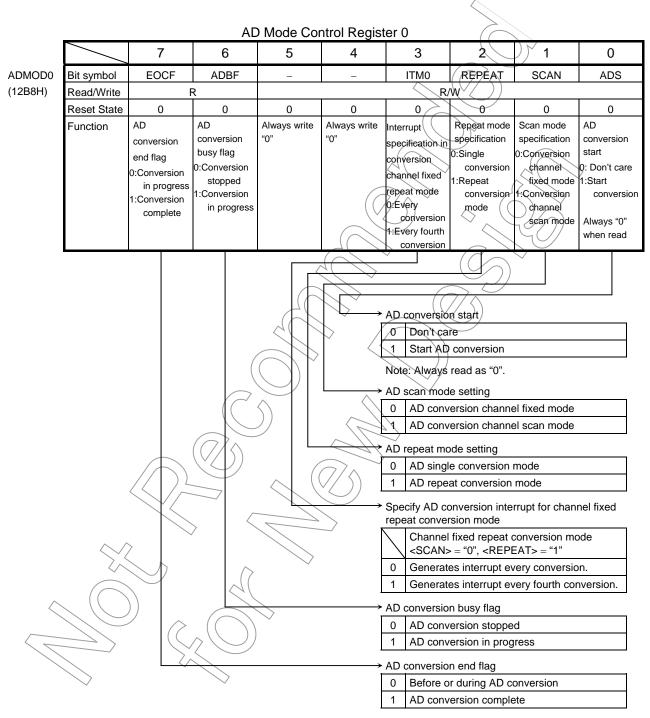

# **TOSHIBA**

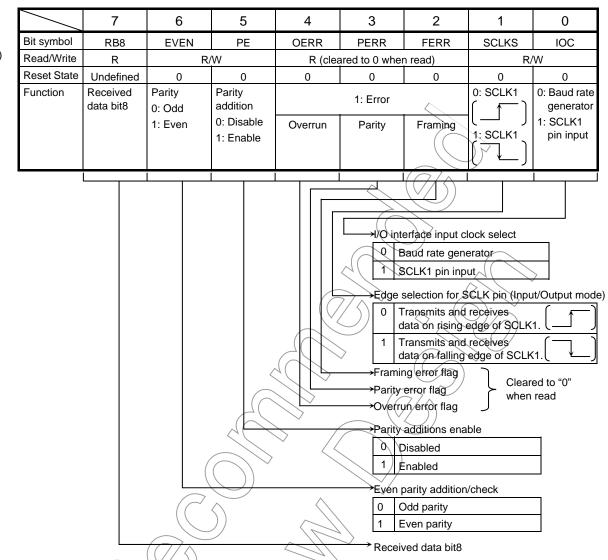

TOSHIBA Original CMOS 32-Bit Microcontroller

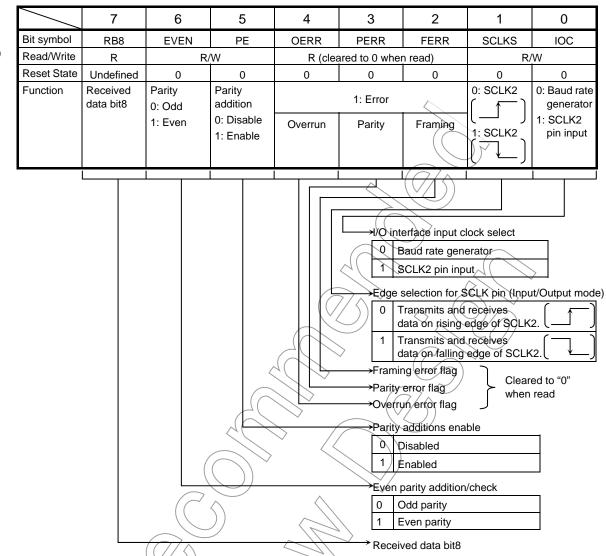

TLCS-900/H1 Series

TMP92CY23FG

TMP92CY23DFG

TMP92CD23AFG

TMP92CD23ADFG

### **TOSHIBA CORPORATION**

Semiconductor Company

# Preface

Thank you very much for making use of Toshiba microcomputer LSIs. Before use this LSI, refer the section, "Notes and Restrictions".

**TOSHIBA**

#### CMOS 32-Bit Microcontrollers

# TMP92CY23FG/TMP92CY23DFG/TMP92CD23AFG/TMP92CD23ADFG

#### Outline and Device Characteristics

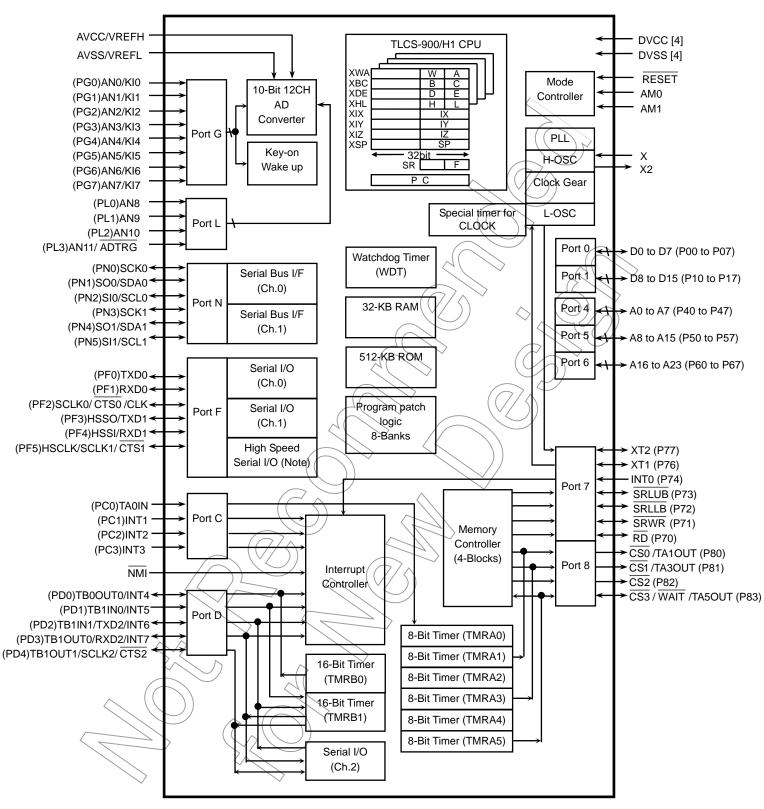

The TMP92CY23/CD23A are a high-speed advanced 32-bit Microcontroller developed for controlling equipment which processes mass data.

The TMP92CY23/CD23A has a high-performance CPU (900/H1 CPU) and various built-in I/Os. TMP92CY23FG, TMP92CY23FG, TMP92CD23AFG and TMP92CD23ADFG are housed in a 100-pin flat package.

| Product Name  | RAM      | ROM       | Package              |

|---------------|----------|-----------|----------------------|

| TMP92CY23FG   | 16K byte | 256K byte | LQFP100-P-1414-0.50F |

| TMP92CY23DFG  | ,        | ,         | QFP-P-1420-0.65A     |

| TMP92CD23AFG  | 20K byto | F10K byto | LQFP100-P-1414-0.50F |

| TMP92CD23ADFG | 32K byte | 512K byte | QFP-P-1420-Ø,65A     |

Device characteristics are as follows:

- (1) CPU: 32-bit CPU (900/H1 CPU)

- Compatible with 900/L1 instruction code

- 16 Mbytes of linear address space

- General-purpose register and register banks

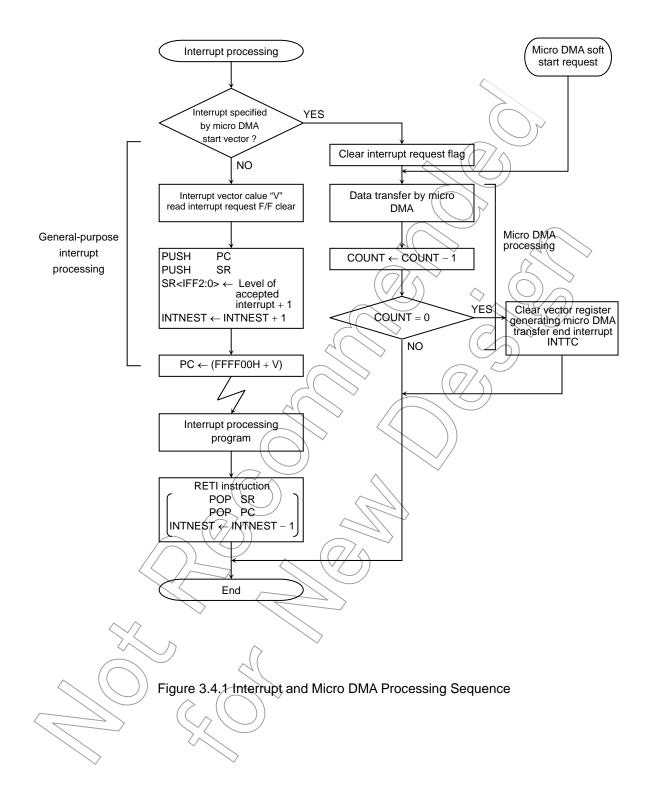

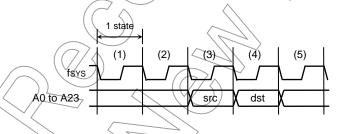

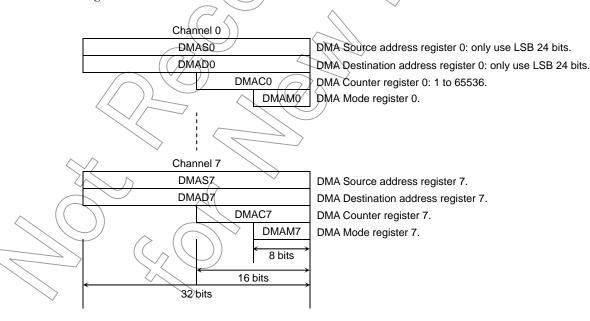

- Micro DMA: 8 channels (250 ns/4 bytes at fsys = 20 MHz, best case)

- (2) Minimum instruction execution time: 50 ns (at fsys = 20 MHz)

- (3) External memory expansion

- Expandable up to 16 Mbytes (Shared program/data area)

- Can simultaneously support 8- or 16-bit width external data bus ... Dynamic data bus sizing

- Separate bus system

- (4) Memory controller

- Chip select output: 4 channels

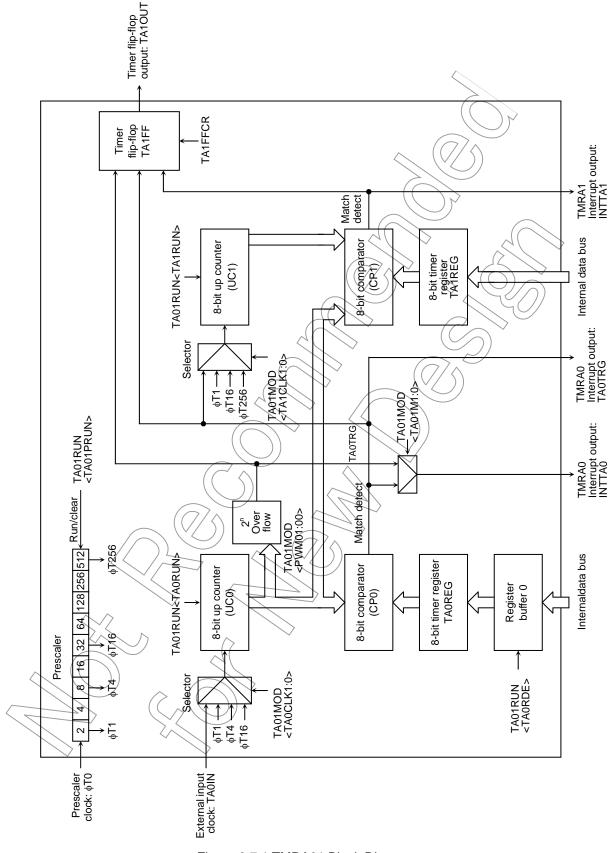

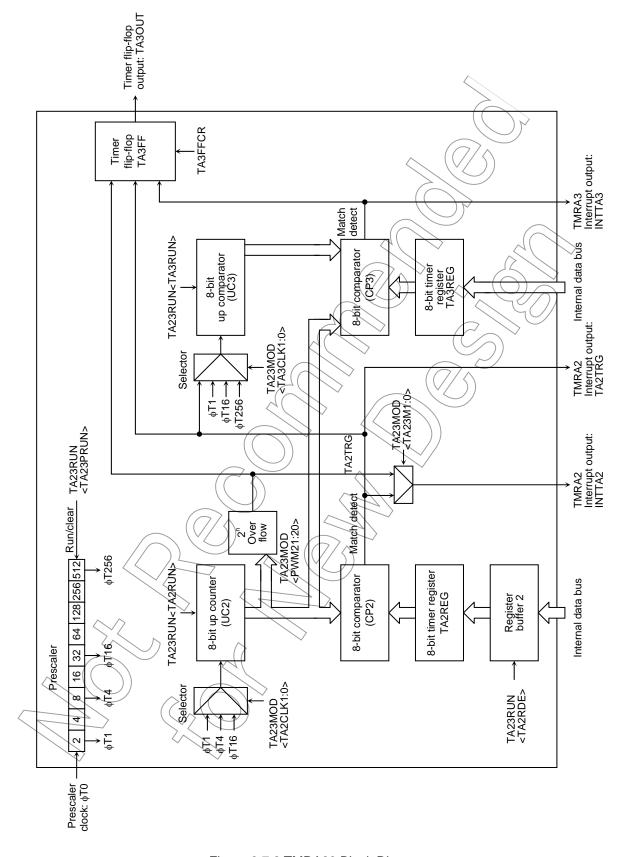

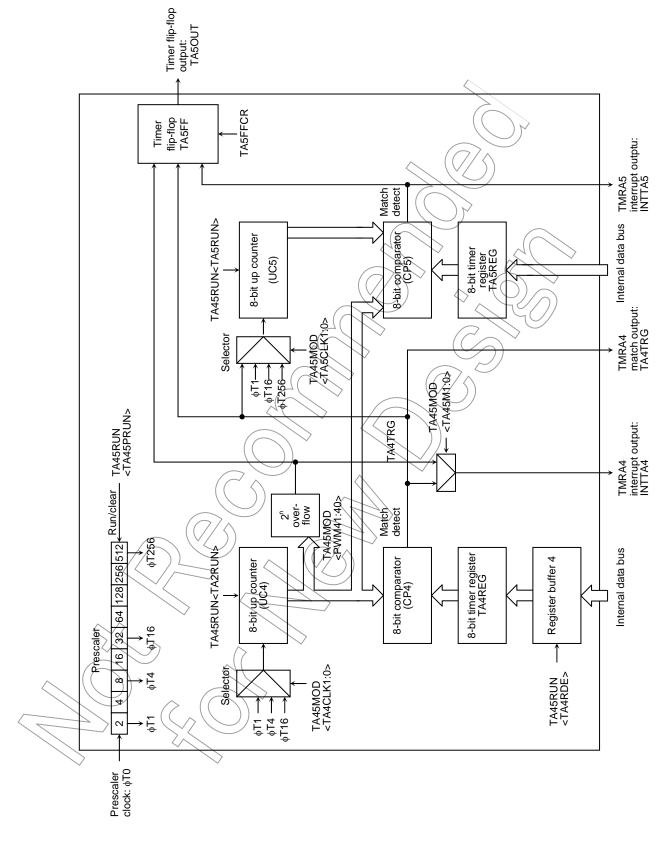

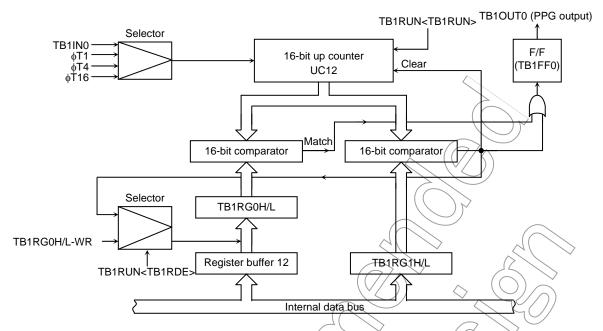

- (5) 8-bit timers: 6 channels

- (6) 16-bit timers: 2 channels

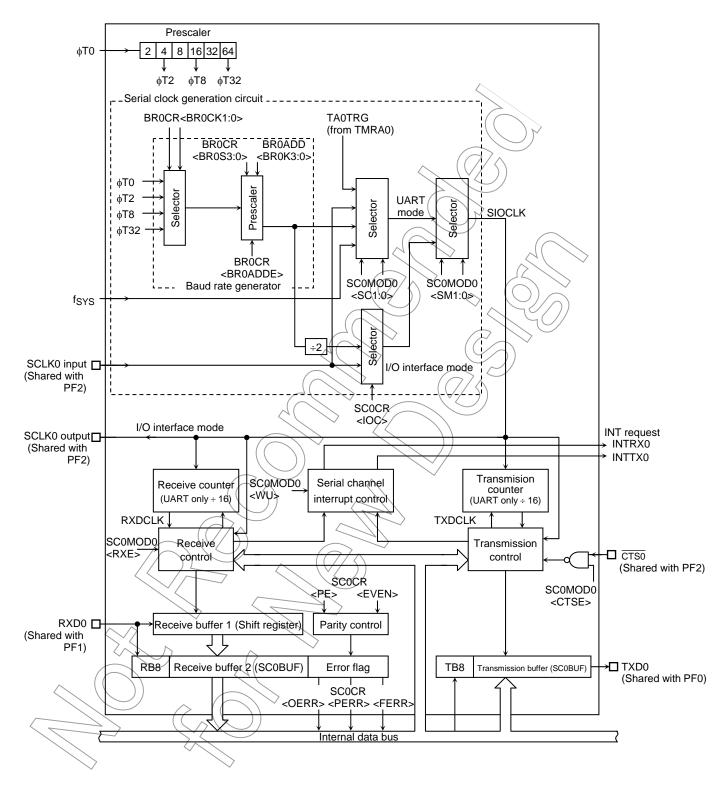

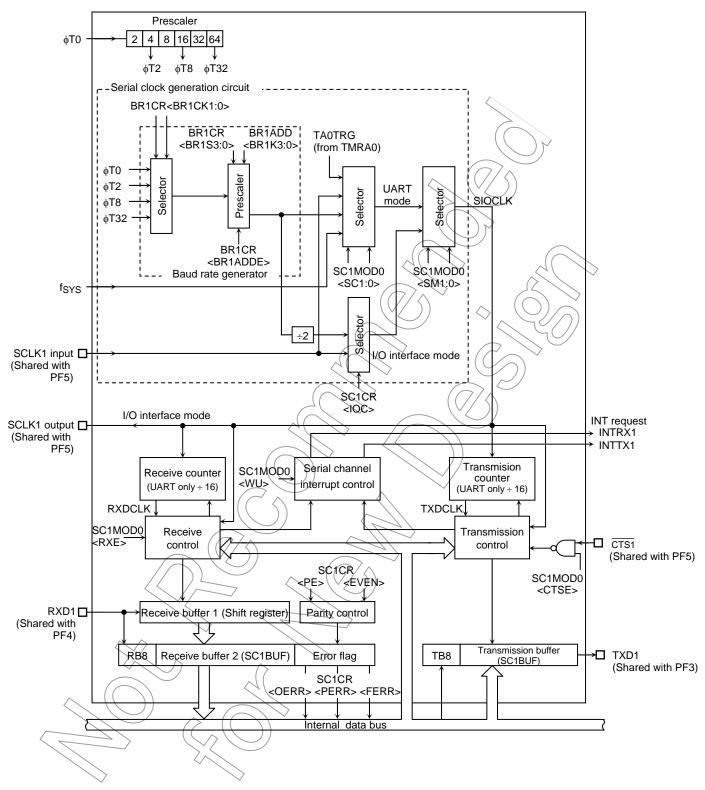

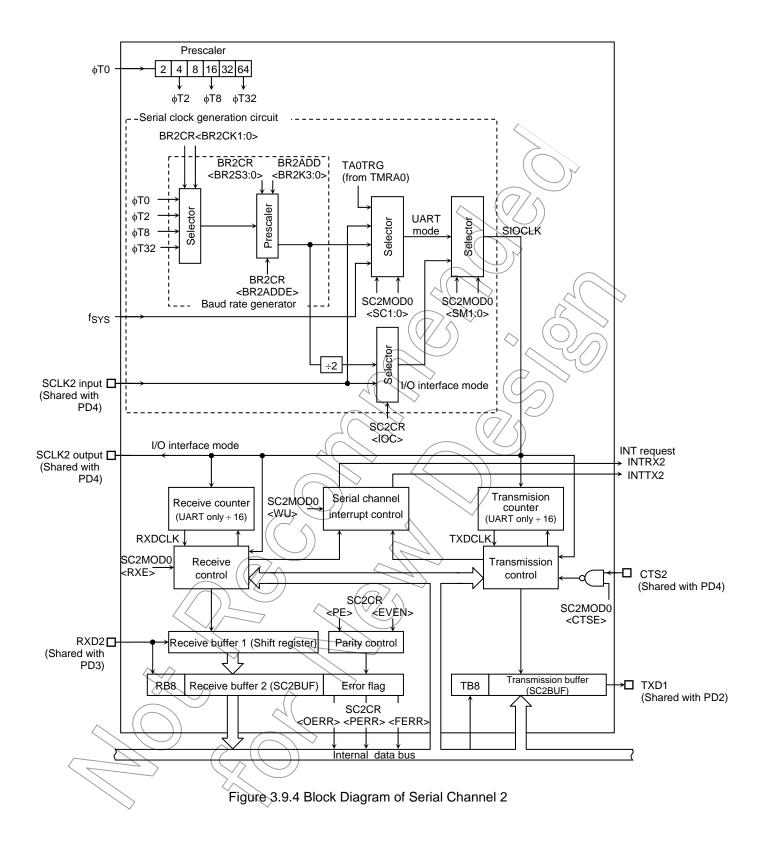

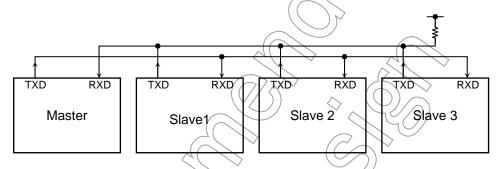

- (7) General-purpose serial interface: 3 channels

- (UART/synchronous mode: 3 channels (channel 0, 1 and 2)

- IrDA yer. 1.0 (115 kbps) mode selectable: 3 channels (channel 0, 1 and 2)

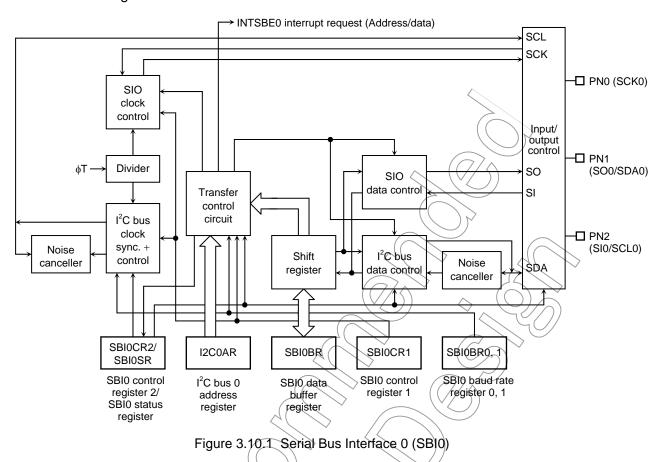

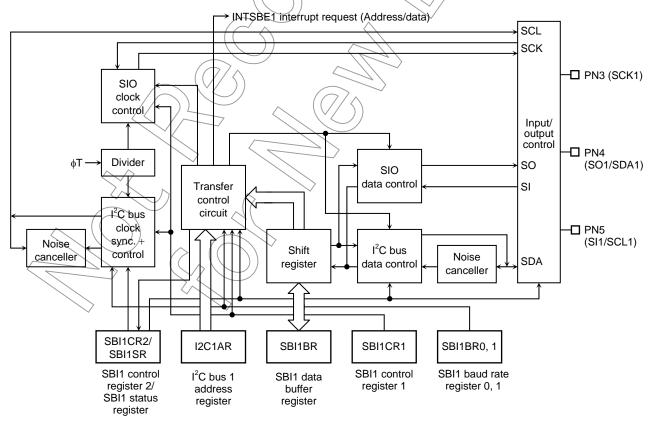

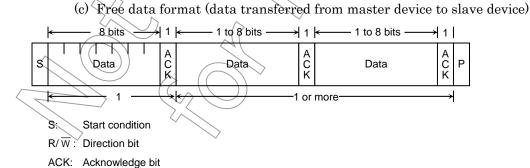

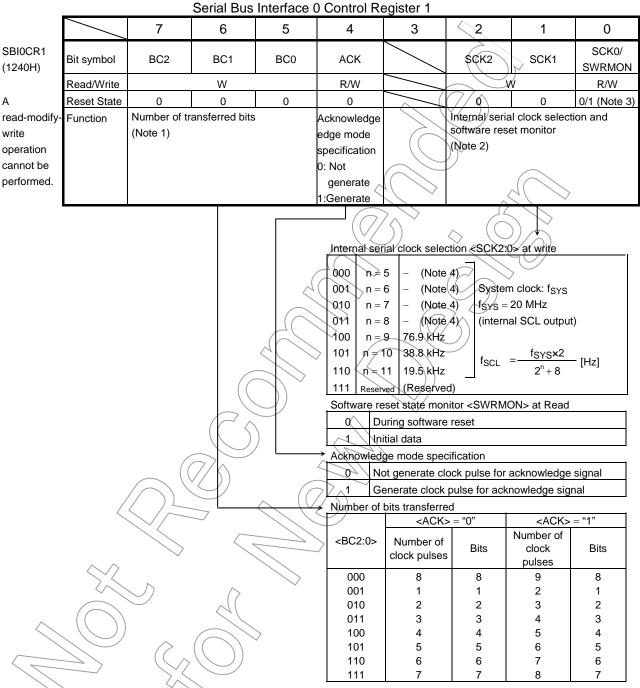

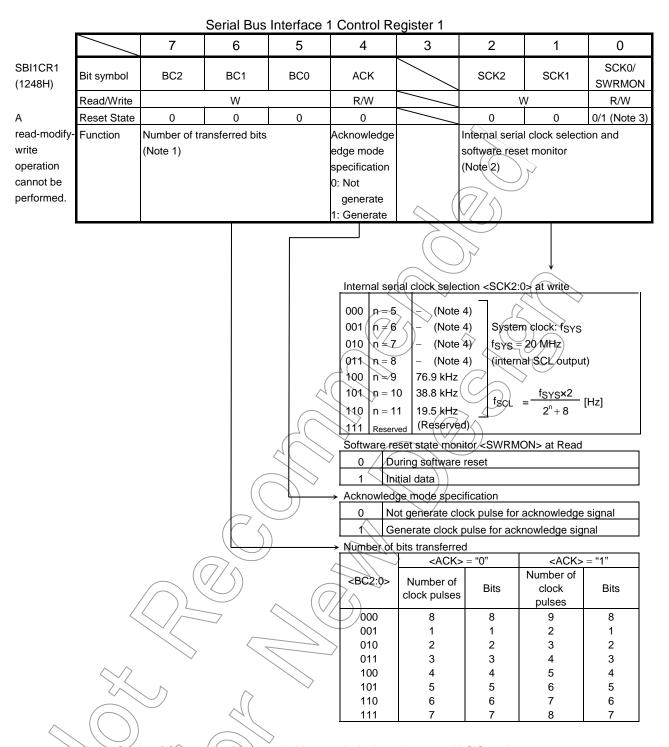

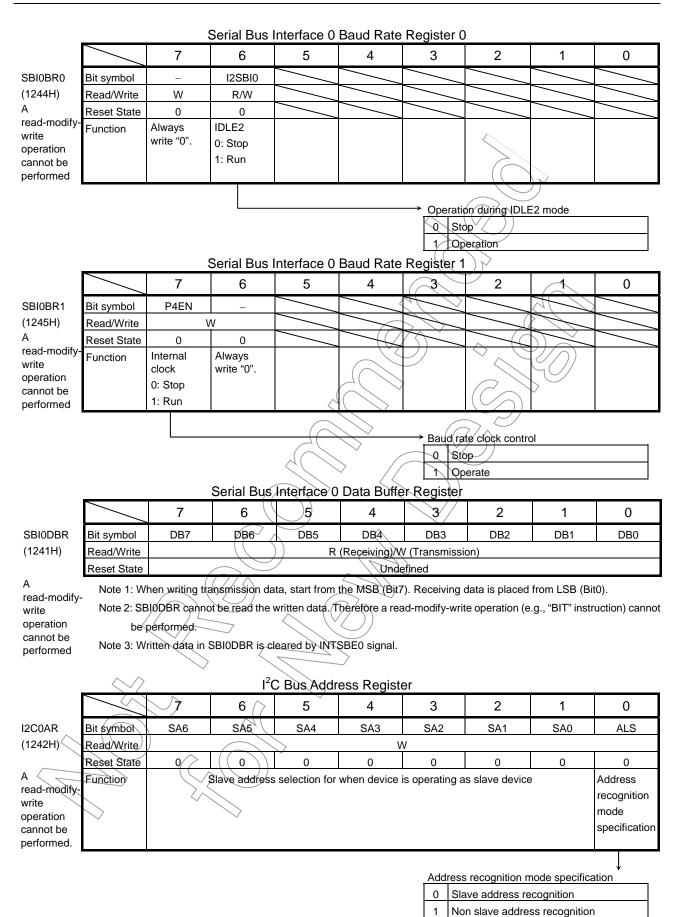

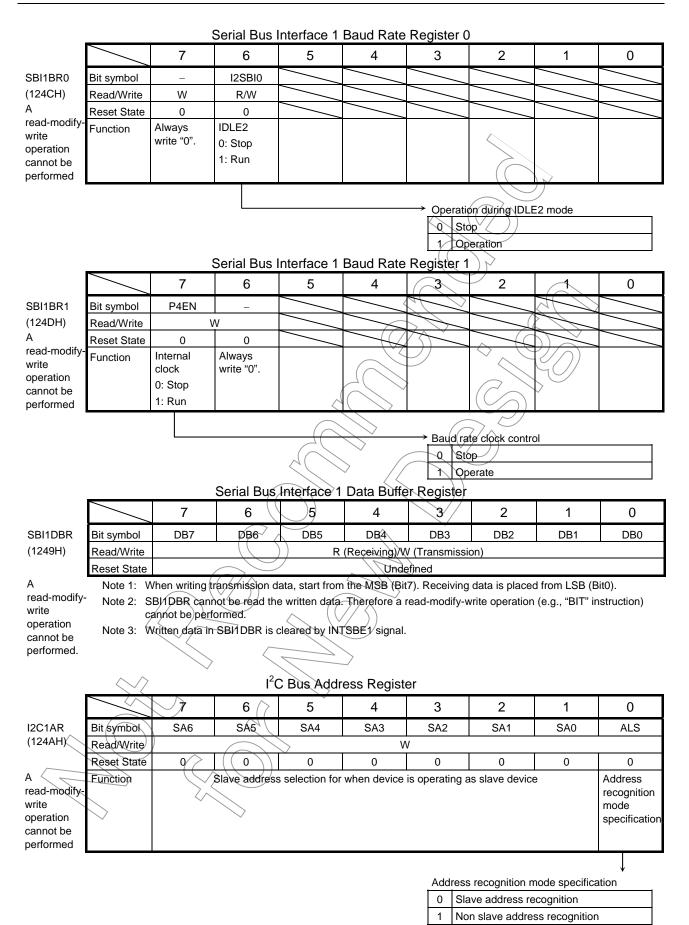

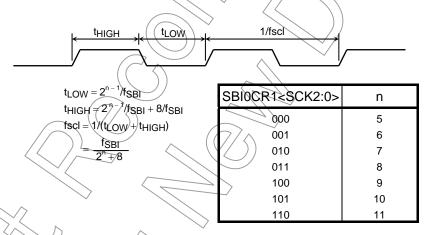

- (8) Serial bus interface 2 channels

- I<sup>2</sup>C bus modé/

- Clock synchronous mode

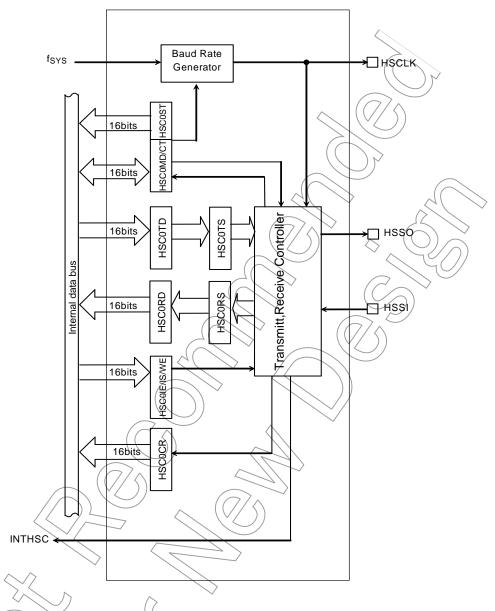

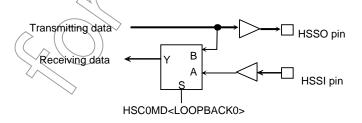

- (9) High Speed serial interface: 1 channels

Note: This circuit is not built into TMP92CY23.

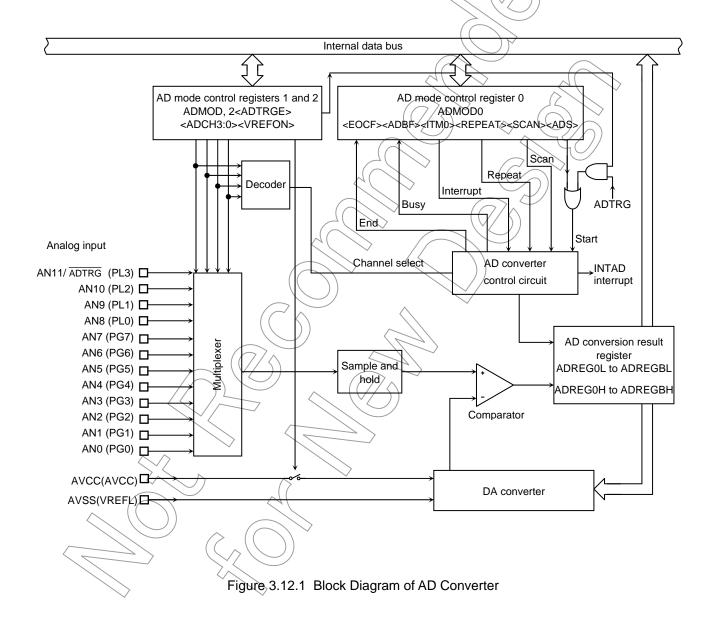

- (10) 10-bit AD converter: 12 channels

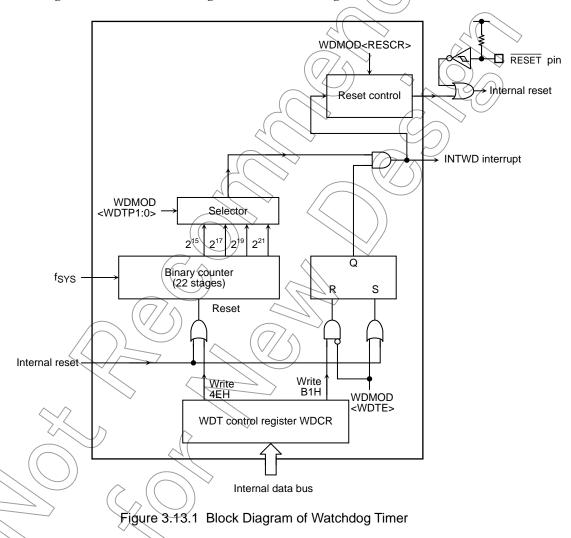

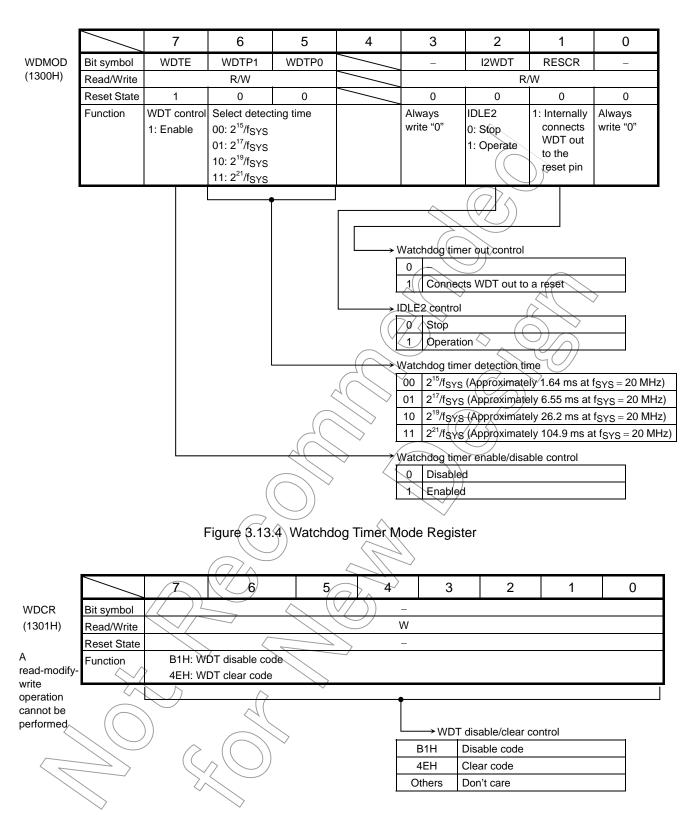

- (11) Watchdog timer

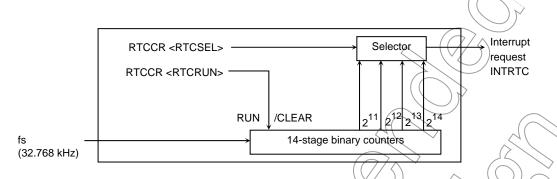

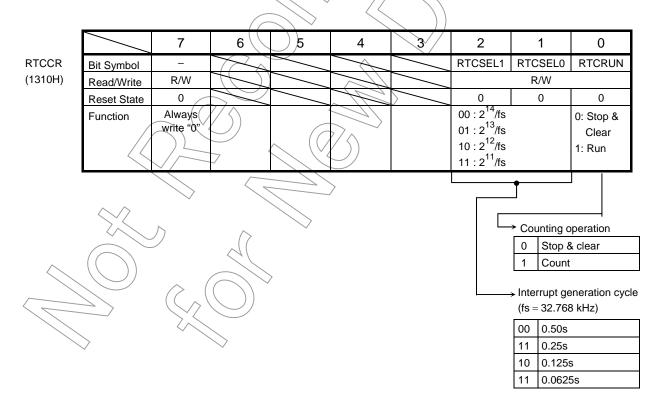

- (12) Special timer for CLOCK

92CY23-1 2009-08-28

- (13) Key-on wake up (only for HALT release):8 channels

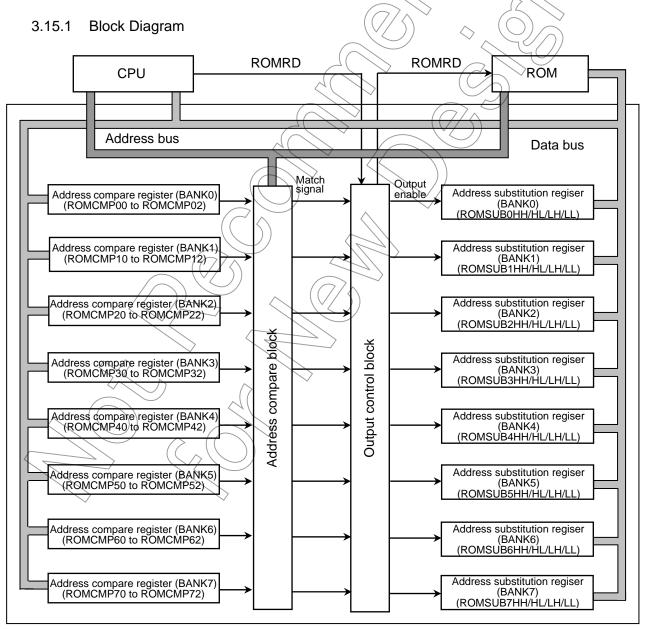

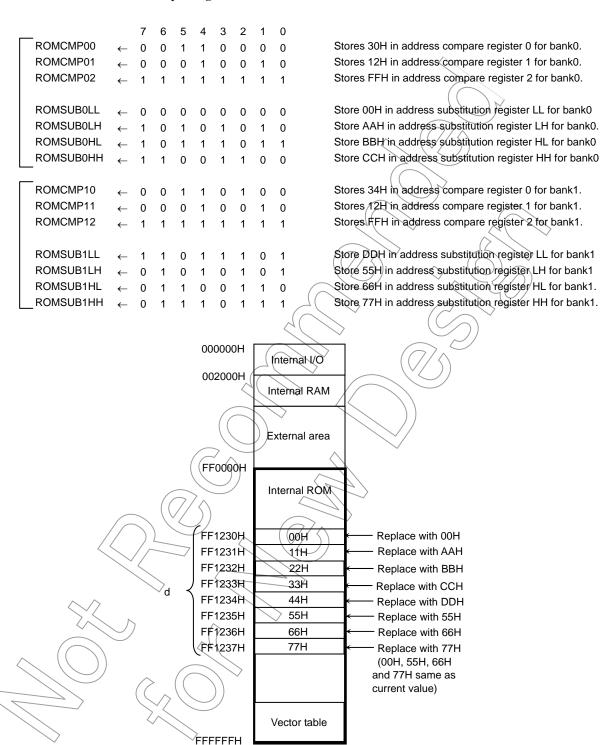

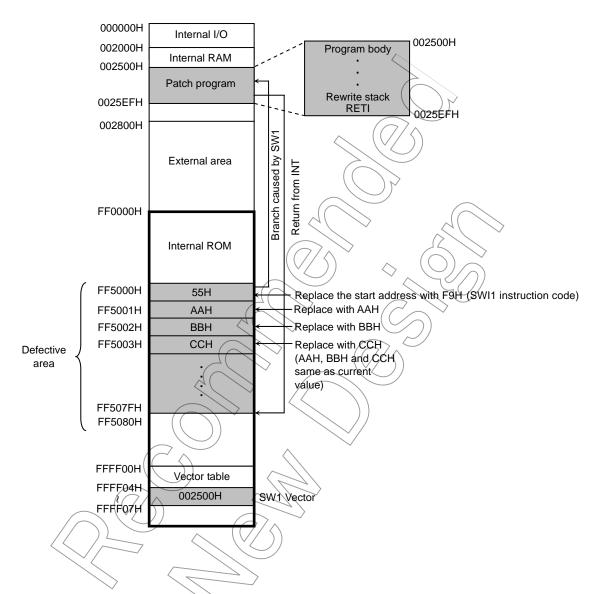

- (14) Program patch logic: 8 banks

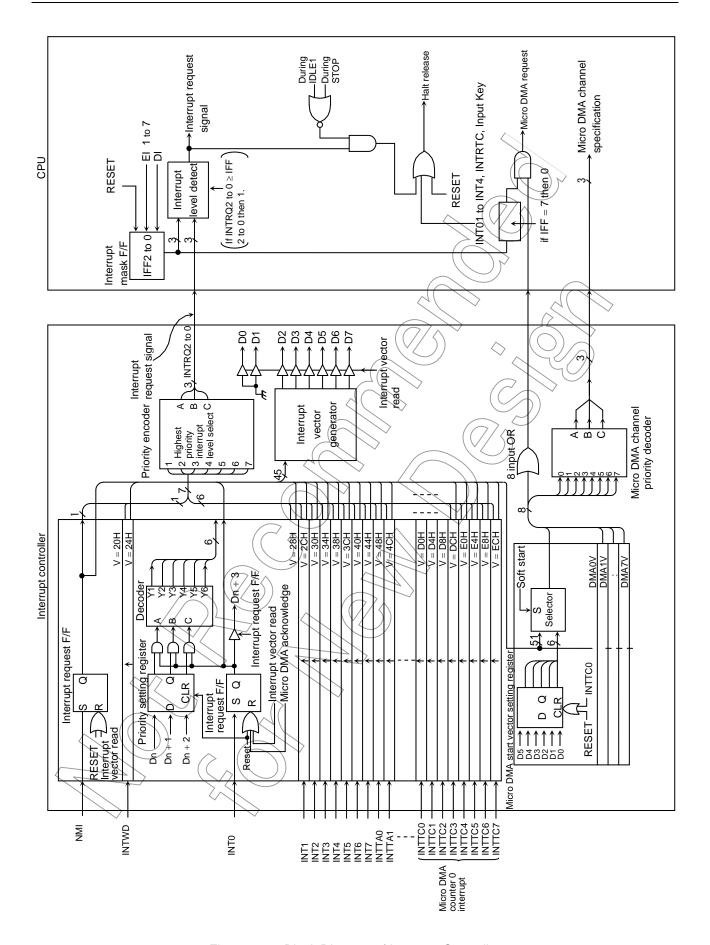

- (15) Interrupts: TMP92CY23: 50 interrupts, TMP92CD23A: 51 interrupts

- 9 CPU interrupts: Software interrupt instruction and illegal instruction

- 32 internal interrupts (TMP92CY23), 33 internal interrupts (TMP92CD23A)

: Seven selectable priority levels

• 9 external interrupts (INT0 to INT7 and NMI): Seven selectable priority levels (INT0 to INT7 selectable edge or level interrupt)

(16) Input/output ports: 84 pins

(17) Standby function

• Three HALT modes: IDLE2 (Programmable), IDLE1, STOP

(18) Clock controller

• Clock doubler (PLL)

• Clock gear function: Select high-frequency clock to fc/16

• Special timer for CLOCK (fs = 32.768 kHz)

(19) Operating voltage

•  $V_{CC} = 3.0 \text{ V}$  to 3.6 V (fc max = 40 MHz,  $f_{OSCH}$  max = 10 MHz (TMP92CD23A))

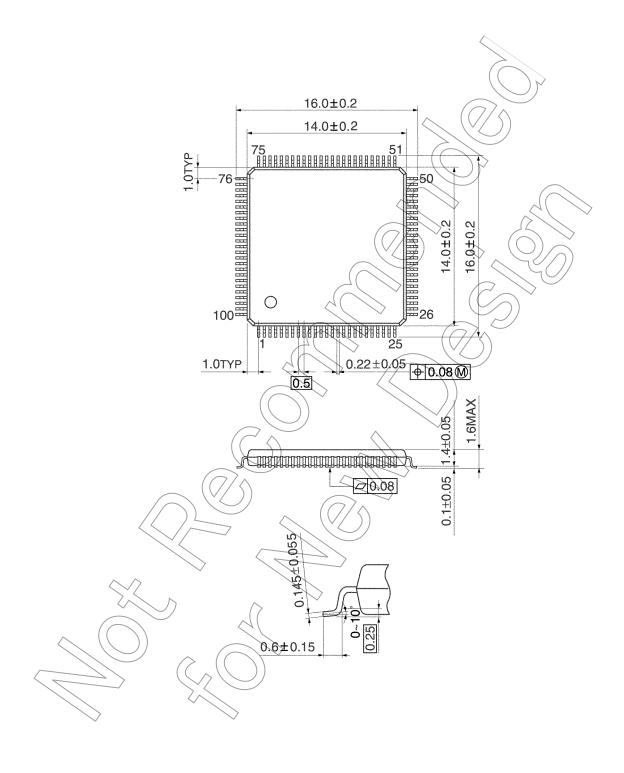

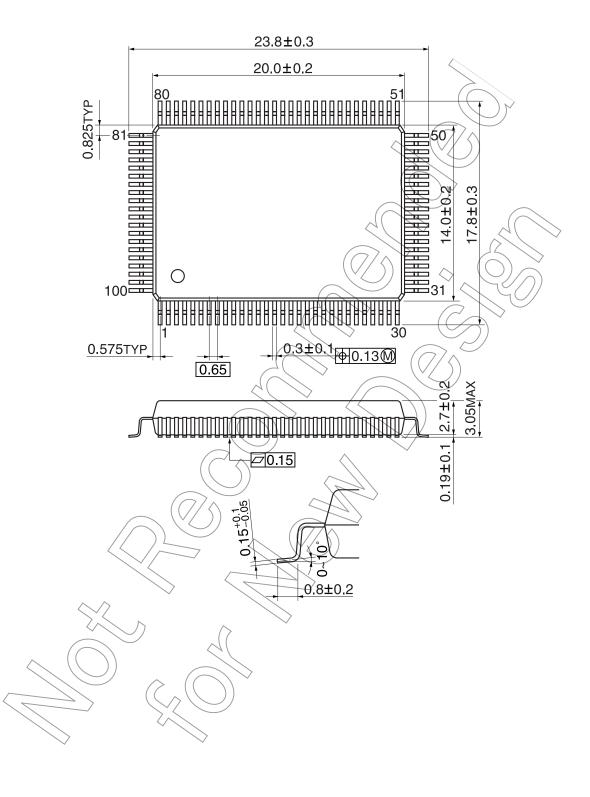

(20) Package

• 100-pin QFP: LQFP100-P-1414-0.50F (TMP92CY23FG/TMP92CD23AFG) QFP100-P-1420-0.65A (TMP92CY23DFG/TMP92CD23ADFG)

(): Initial function after reset

Note: This circuit is not built into TMP92CY23.

Figure 1.1 TMP92CY23/CD23A Block Diagram

# 2. Pin Assignment and Functions

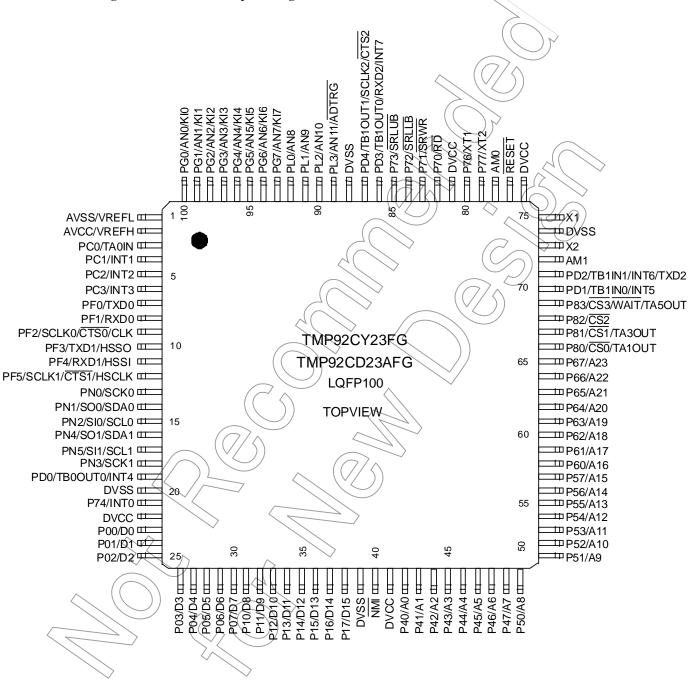

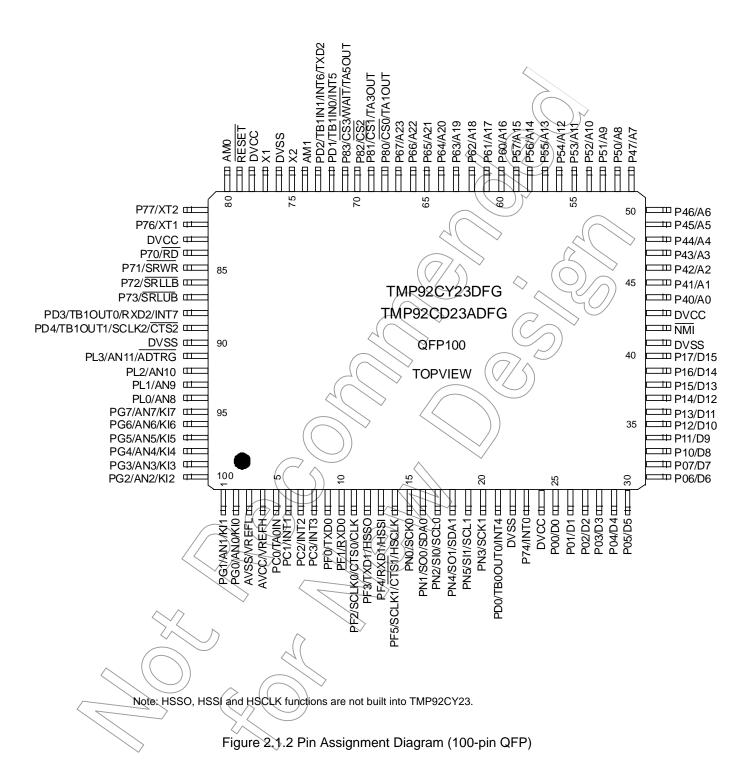

The assignment of input/output pins for the TMP92CY23/CD23A, their names and functions are as follows:

### 2.1 Pin Assignment Diagram

Figure 2.1.1 shows the pin assignment of the TMP92CY23FG/TMP92CD23AFG.

Note: HSSO, HSSI and HSCLK functions are not built into TMP92CY23.

Figure 2.1.1 Pin Assignment Diagram (100-pin LQFP)

TOSHIBA

Figure 2.1.2 shows the pin assignment of the TMP92CY23DFG/TMP92CD23ADFG.

92CY23-5 2009-08-28

# 2.2 Pin Names and Functions

The following table shows the names and functions of the input/output pins.

Table 2.2.1 Pin Names and Functions (1/3)

| Pin name   | Number of Pin | I/O     | Function                                                                                   |

|------------|---------------|---------|--------------------------------------------------------------------------------------------|

| P00 to P07 | 8             | I/O     | Port 0: I/O port Input or output specifiable in units of bits                              |

| D0 to D7   |               | I/O     | Data: Data bus 0 to 7                                                                      |

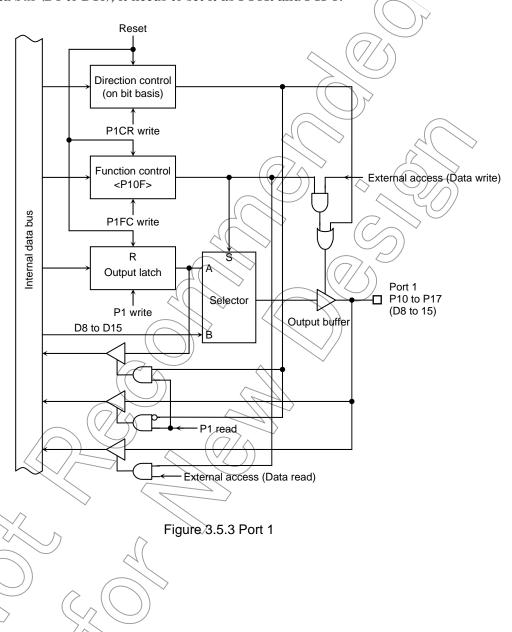

| P10 to P17 | 8             | I/O     | Port 1: I/O port Input or output specifiable in units of bits                              |

| D8 to D15  |               | I/O     | Data: Data bus 8 to 15                                                                     |

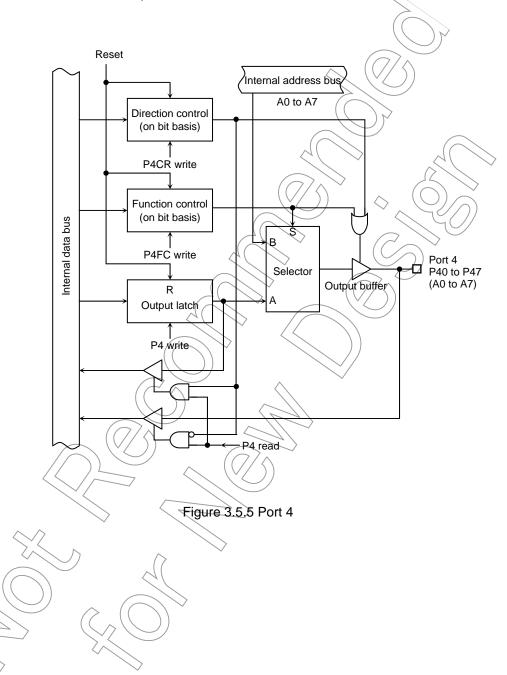

| P40 to P47 | 8             | I/O     | Port 4: I/O port Input or output specifiable in units of bits                              |

| A0 to A7   |               | Output  | Address: Address bus 0 to 7                                                                |

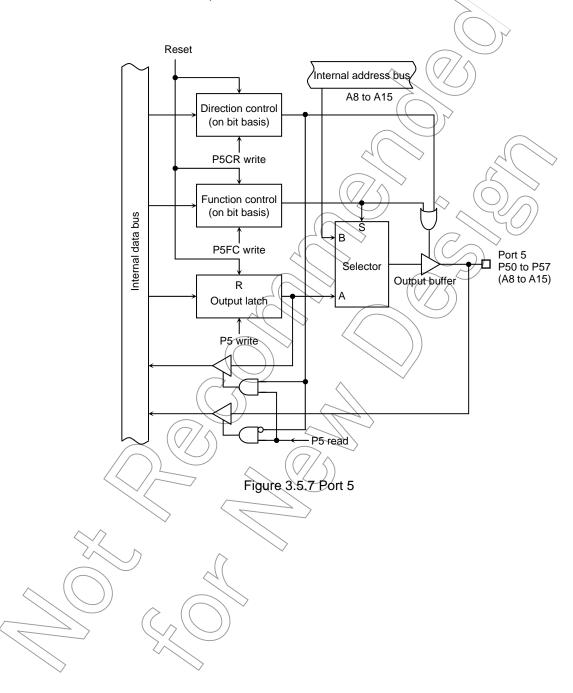

| P50 to P57 | 8             | I/O     | Port 5: I/O port Input or output specifiable in units of bits                              |

| A8 to A15  |               | Output  | Address: Address bus 8 to 15                                                               |

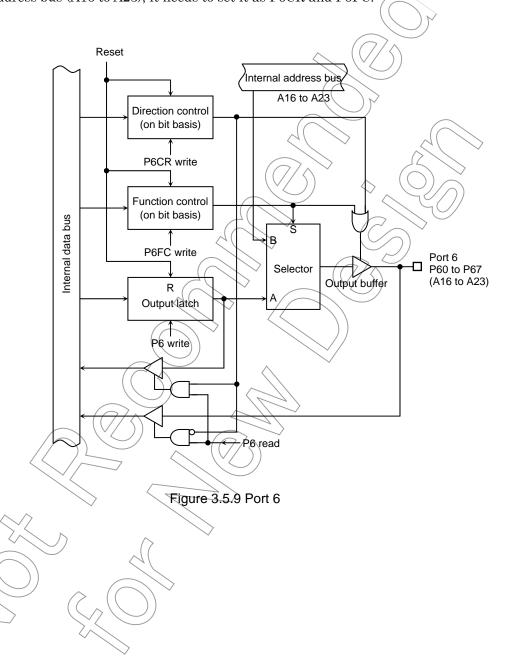

| P60 to P67 | 8             | I/O     | Port 6: I/O port Input or output specifiable in units of bits                              |

| A16 to A23 |               | Output  | Address: Address bus 16 to 23                                                              |

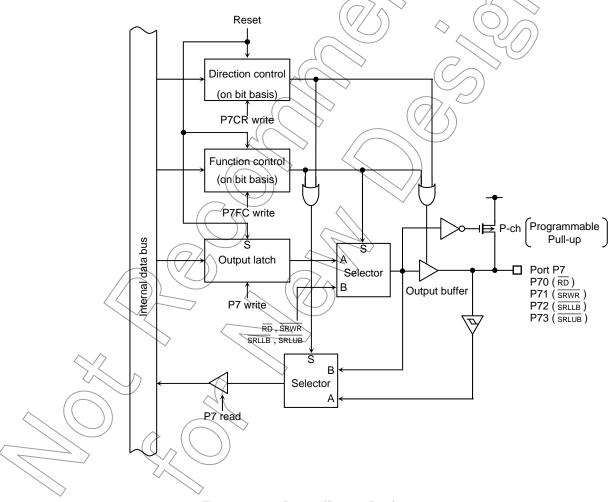

| P70        | 1             | I/O     | Port 70: I/O port (Schmitt input, with pull-up resistor)                                   |

| RD         |               | Output  | Read: Outputs strobe signal for read external memory.                                      |

| P71        | 1             | I/O     | Port 71: I/O port (Schmitt input, with pull-up resistor)                                   |

| SRWR       |               | Output  | Write enable for SRAM: Strobe signal for wiriting data.                                    |

| P72        | 1             | I/O     | Port 72: I/O port (Schmitt input, with pull-up resistor)                                   |

| SRLLB      |               | Output  | Data enable for SRAM on pins D0 to D7                                                      |

| P73        | 1             | I/O     | Port 73: I/O port (Schmitt input, with pull-up resistor)                                   |

| SRLUB      |               | Output  | Data enable for SRAM on pins D8 to D15                                                     |

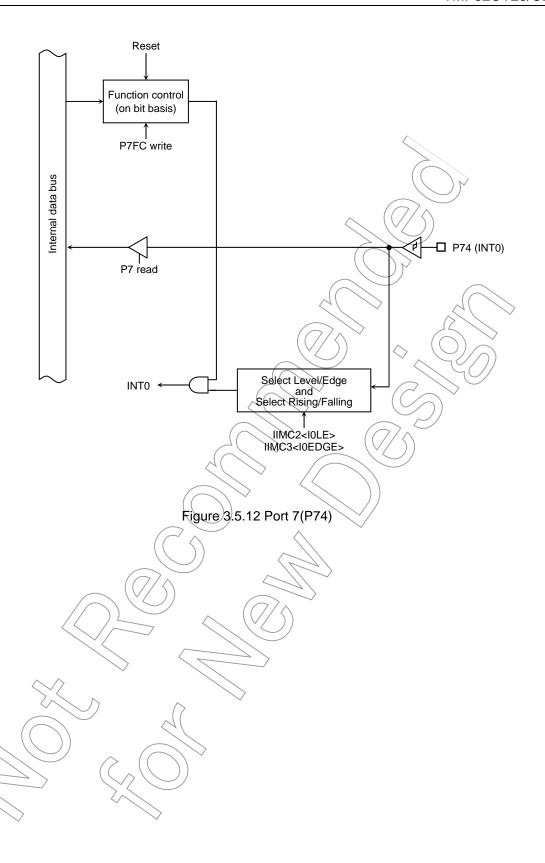

| P74        | 1             | Input   | Port 74: Input port (Schmitt input)                                                        |

| INT0       |               | Input   | Interrupt request pin 0: Interrupt request pin with programmable level/rising/falling edge |

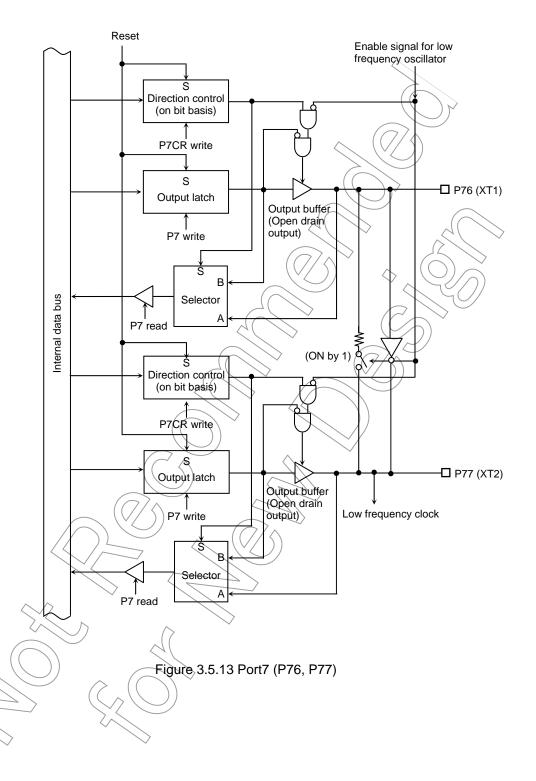

| P76        | 1             | I/O     | Port 76: I/O port (Open drain output)                                                      |

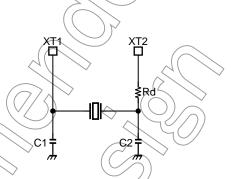

| XT1        |               | Input   | Low-frequency oscillator connection Input pins                                             |

| P77        | 1             | I/O     | Port 77:1/O port (Open drain output)                                                       |

| XT2        |               | Output  | Low-frequency oscillator connection Output pins                                            |

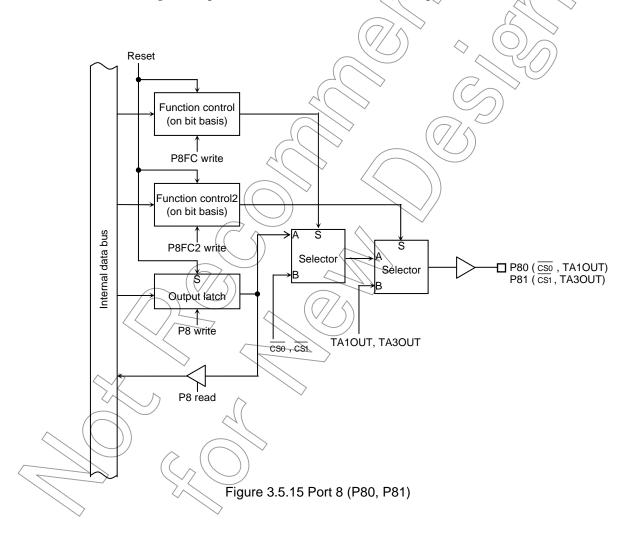

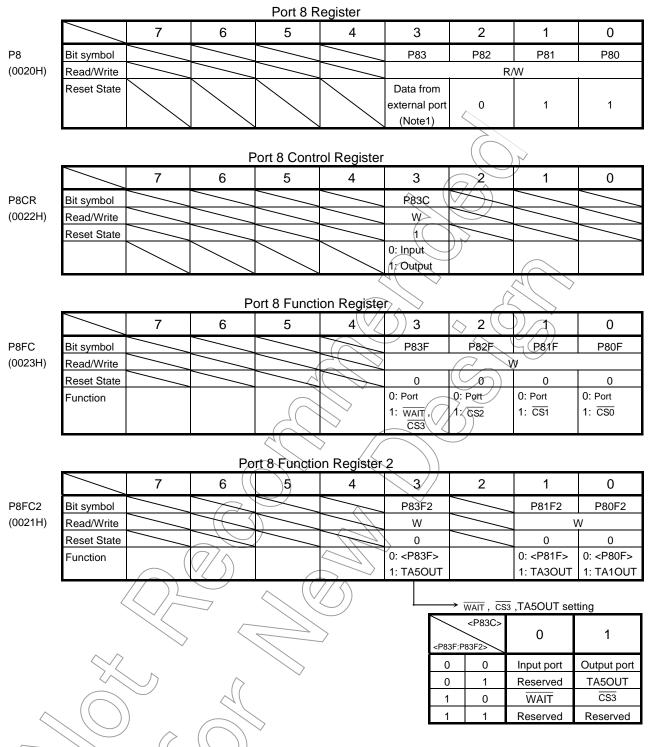

| P80        | 1             | Output  | (Port 80) Output port                                                                      |

| CS0        |               | Output  | Chip select 0: Outputs "Low" when address is within specified address area                 |

| TA1OUT     |               | Output  | 8-bit timer 1 Output: Output pin of 8-bit timer TMRA0 or TMRA1                             |

| P81        | 1 /           | Output  | Port 81: Output port                                                                       |

| CS1        |               | Output  | Chip select 1: Outputs "Low" when address is within specified address area                 |

| TA3OUT     |               | Oûtput  | 8-bit timer 3 Output: Output pin of 8-bit timer TMRA2 or TMRA3                             |

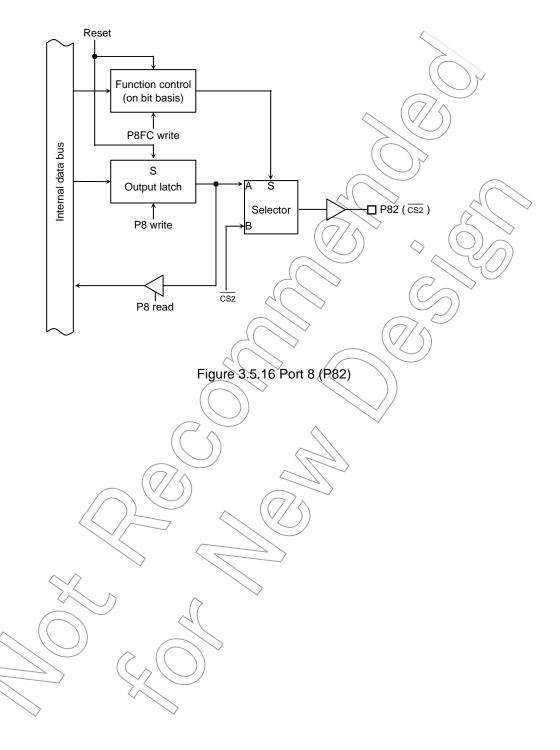

| P82        | 1             | Output  | Port 82: Output port                                                                       |

| CS2        |               | Output  | Chip select 2: Outputs "Low" when address is within specified address area                 |

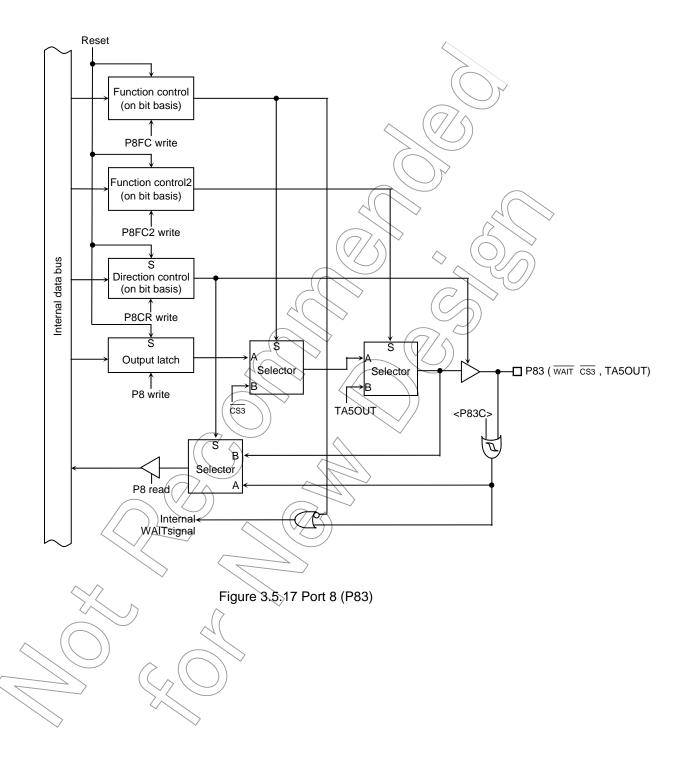

| P83        | $\searrow$    | I/O     | Port 83: I/O port (Schmitt input)                                                          |

| CS3        | 7/            | Output  | Chip select 3: Outputs "Low" when address is within specified address area                 |

| TA5OUT     |               | Output  | 8-bit/timer 5 Output: Output pin of 8-bit timer TMRA4 or TMRA5                             |

| WAIT       |               | Input   | Wait Signal used to request CPU bus wait                                                   |

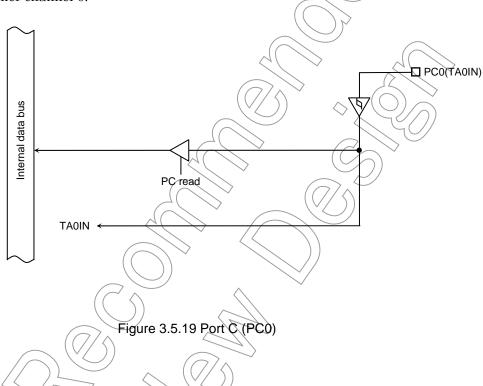

| PC0        | (1)           | Input   | Port C0: Input port (Schmitt input)                                                        |

| TAOIN      |               | Input ( | 8-bit timer 0 input: Input pin of 8-bit timer TMRA0                                        |

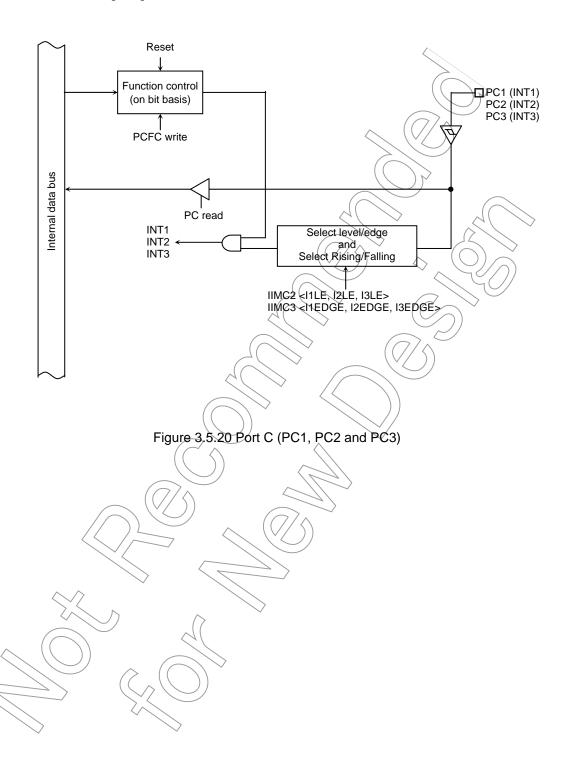

| PC1        | <u> </u>      | Input   | Port C1: Input port (Schmitt input)                                                        |

| INT1       |               | Input   | Interrupt request pin 1: Interrupt request pin with programmable level/rising/falling edge |

| PC2        | 1             | Input   | Port C2: Input port (Schmitt input)                                                        |

| INT2       |               | Input   | Interrupt request pin 2: Interrupt request pin with programmable level/rising/falling edge |

| PC3        | 1             | Input   | Port C3: Input port (Schmitt input)                                                        |

| INT3       |               | Input   | Interrupt request pin 3: Interrupt request pin with programmable level/rising/falling edge |

Table 2.2.2 Pin Names and Functions (2/3)

| Pin name    | Number of Pin | I/O             | Function                                                                                    |

|-------------|---------------|-----------------|---------------------------------------------------------------------------------------------|

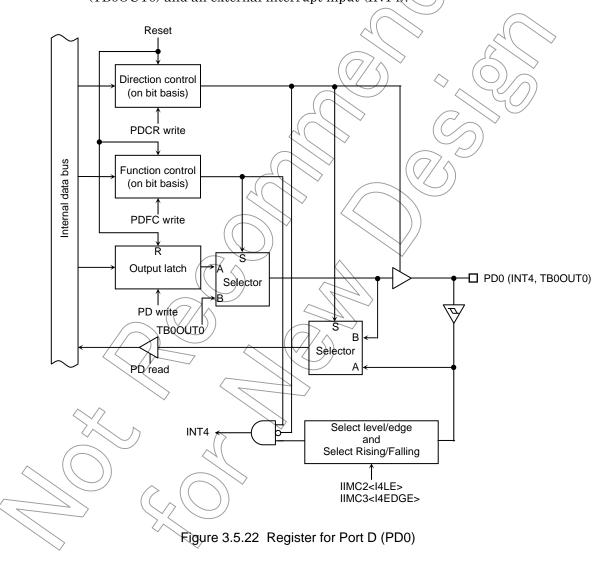

| PD0         | 1             | I/O             | Port D0: I/O port (Schmitt input)                                                           |

| TB0OUT0     |               | Output          | 16-bit timer 0 output 0: Output pin of 16-bit timer TMRB0                                   |

| INT4        |               | Input           | Interrupt request pin 4 : Interrupt request pin with programmable level/rising/falling edge |

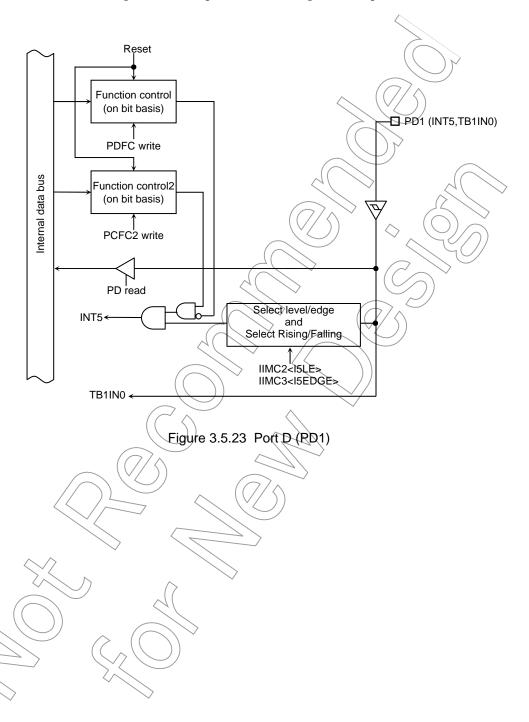

| PD1         | 1             | Input           | Port D1: Input port (Schmitt input)                                                         |

| TB1IN0      |               | Input           | 16-bit timer 1 input 0: Input of count/capture trigger in 16-bit timer TMRB1                |

| INT5        |               | Input           | Interrupt request pin 5: Interrupt request pin with programmable level/rising/falling edge  |

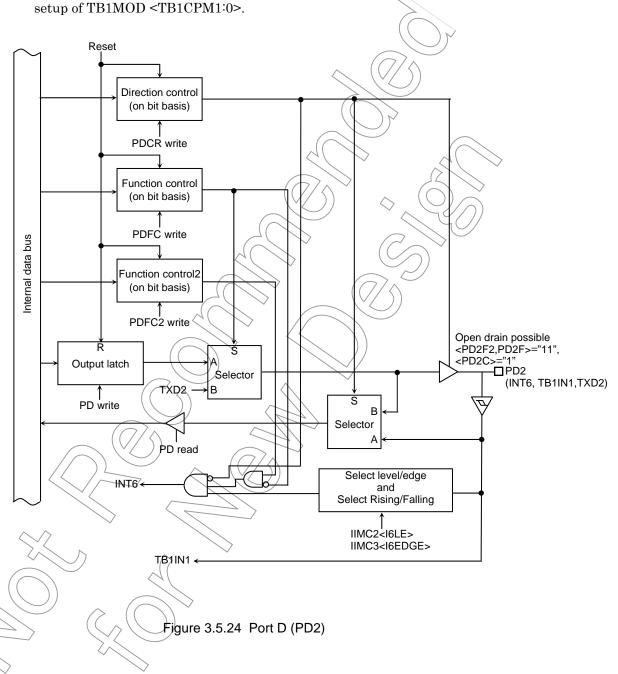

| PD2         | 1             | I/O             | Port D2: I/O port (Schmitt input)                                                           |

| TB1IN1      |               | Input           | 16-bit timer 1 input 1: Input of count/capture trigger in 16-bit timer TMRB1                |

| TXD2        |               | Output          | Serial 2 send data: Open drain output programmable                                          |

| INT6        |               | Input           | Interrupt request pin 6: Interrupt request pin with programmable level/rising/falling edge  |

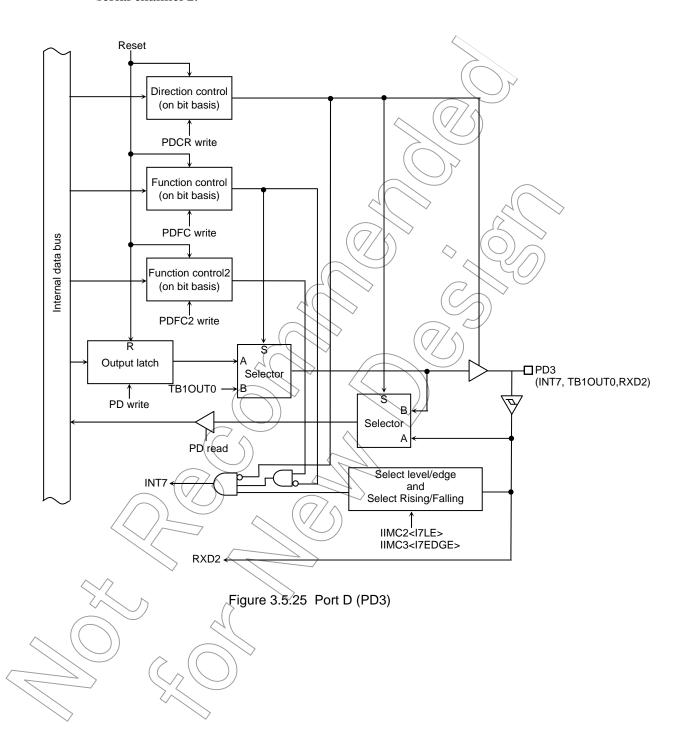

| PD3         | 1             | I/O             | Port D3: I/O port (Schmitt input)                                                           |

| TB1OUT0     |               | Output          | 16-bit timer 1 output 0: Output pin of 16-bit timer TMRB1                                   |

| RXD2        |               | Input           | Serial 2 receive data                                                                       |

| INT7        |               | Input           | Interrupt request pin 7: Interrupt request pin with programmable level/rising/falling edge  |

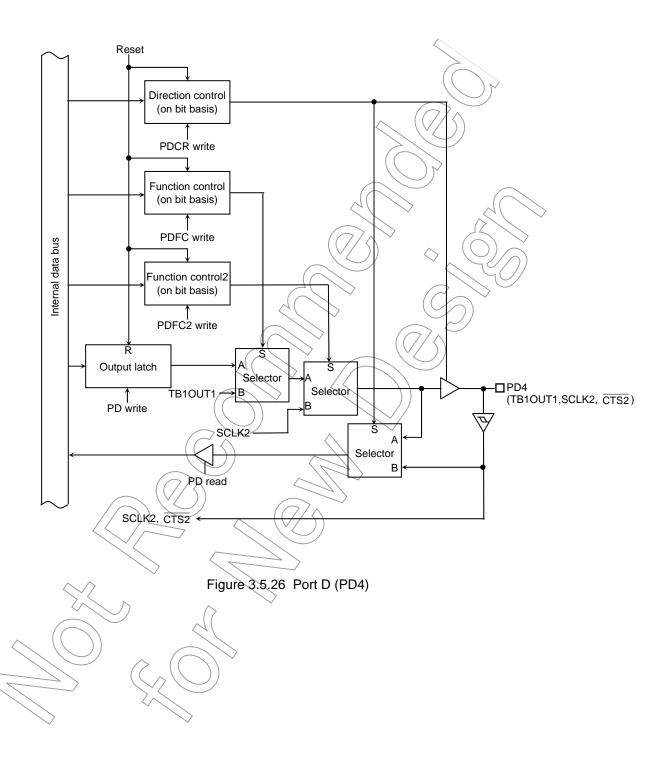

| PD4         | 1             | I/O             | Port D4: I/O port (Schmitt input)                                                           |

| TB1OUT1     |               | Output          | 16-bit timer 1 output 1: Output pin of 16-bit timer TMRB1                                   |

| SCLK2       |               | I/O             | Serial 2 clock I/O                                                                          |

| CTS2        |               | Input           | Serial 2 data send enable (Clear to send)                                                   |

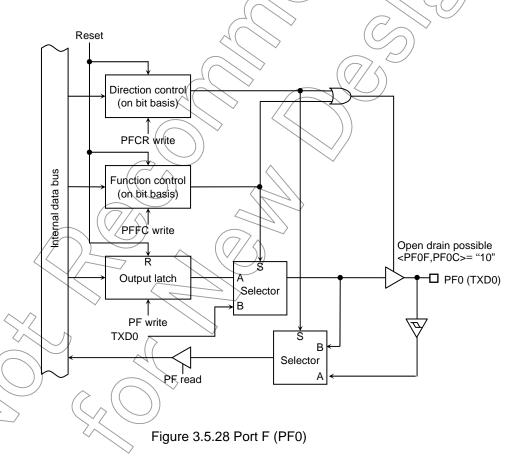

| PF0         | 1             | I/O             | Port F0: I/O port (Schmitt input)                                                           |

| TXD0        |               | Output          | Serial 0 send data: Open drain output programmable                                          |

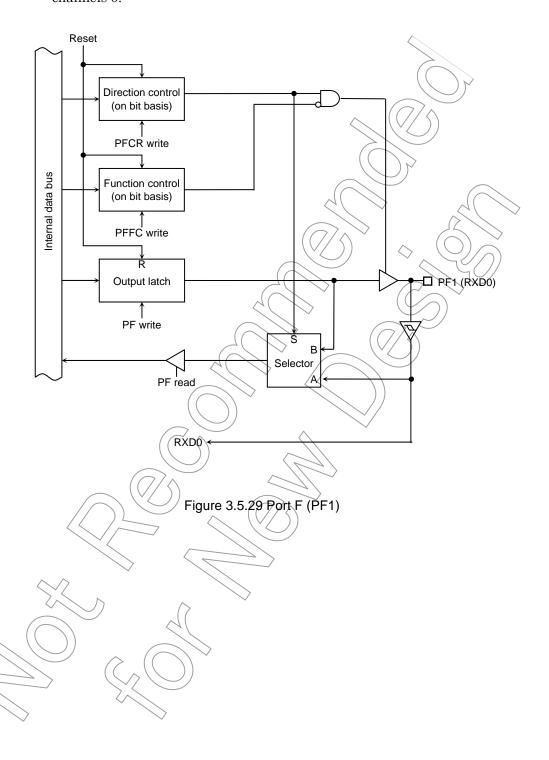

| PF1         | 1             | I/O             | Port F1: I/O port (Schmitt input)                                                           |

| RXD0        |               | Input           | Serial 0 receive data                                                                       |

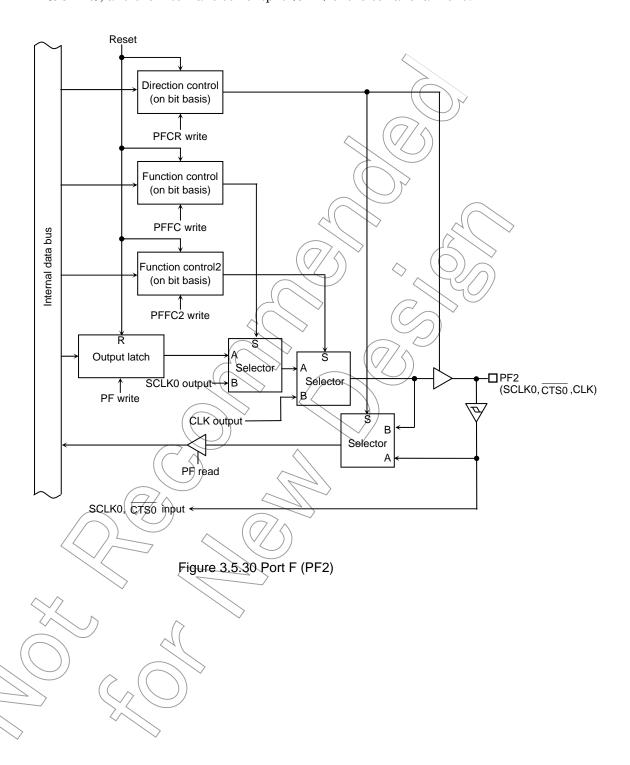

| PF2         | 1             | I/O             | Port F2: I/Q port (Schmitt input)                                                           |

| SCLK0       |               | I/O             | Serial 0 clock I/Q                                                                          |

| CTS0        |               | Input           | Serial 0 data send enable (Clear to send)                                                   |

| CLK         |               | Output          | Clock: System Clock output                                                                  |

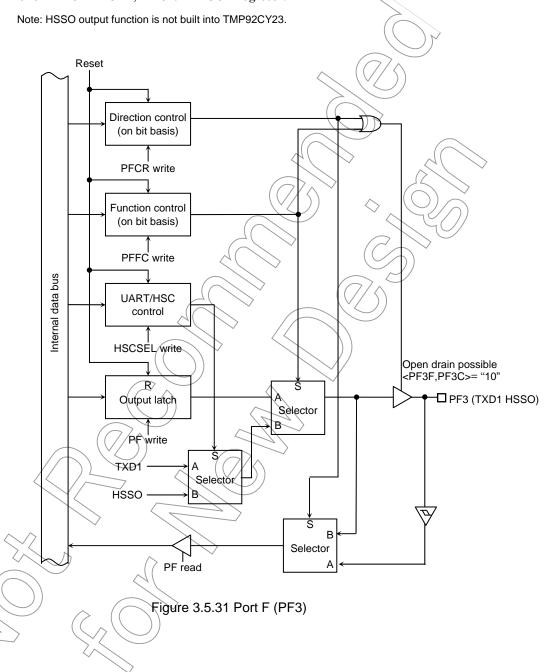

| PF3         | 1             | I/O             | Port F3: I/O port (Schmitt input)                                                           |

| TXD1        |               | Output          | Serial ( send data: Open drain output programmable                                          |

| HSSO        |               | Output          | High speed Serial send data (Note)                                                          |

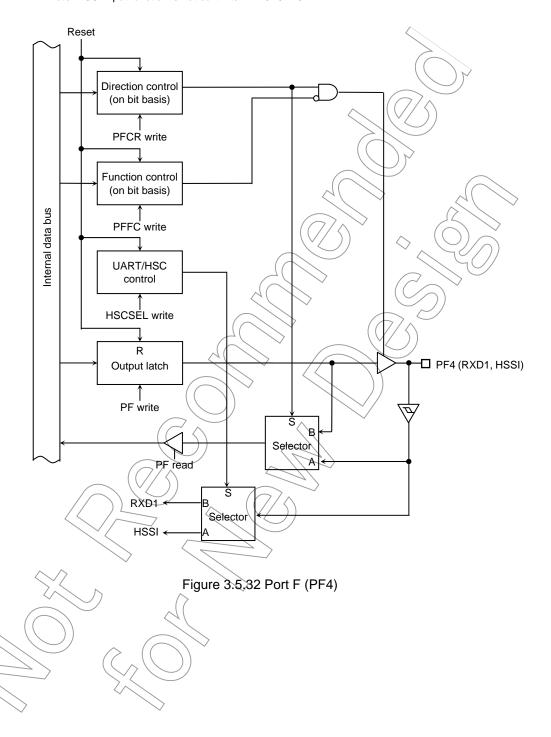

| PF4         | 1             | 1/0             | Port F4: I/O port (Schmitt input)                                                           |

| RXD1        |               | Input (//       | Serial 1 receive data                                                                       |

| HSSI        |               | Input           | High speed Serial receive data (Note)                                                       |

| PF5         | 1/ <          | 1/0             | Port F5: I/O port (Schmitt input)                                                           |

| SCLK1       |               | \/\I/O          | Serial 1 clock I/O                                                                          |

| CTS1        |               | Input           | Serial 1 data send enable (Clear to send)                                                   |

| HSCLK       |               | Output          | High speed Serial clock output (Note)                                                       |

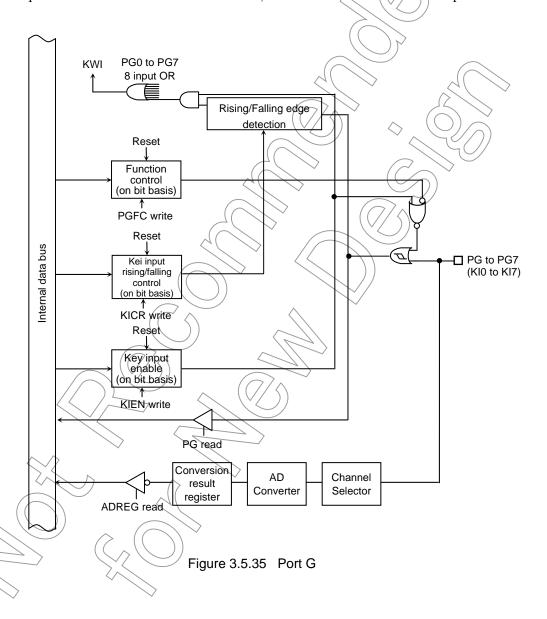

| PG0 to PG7  | (X)           | Input           | Port G: Input port (Schmitt input)                                                          |

| AN0 to AN7  |               | $\supset$       | Analog input 0 to 7: Pin used to input to AD conveter                                       |

| KI0 to KI7  |               | /               | Key input 0 to 7: Pin used for key-on wakeup 0 to 7                                         |

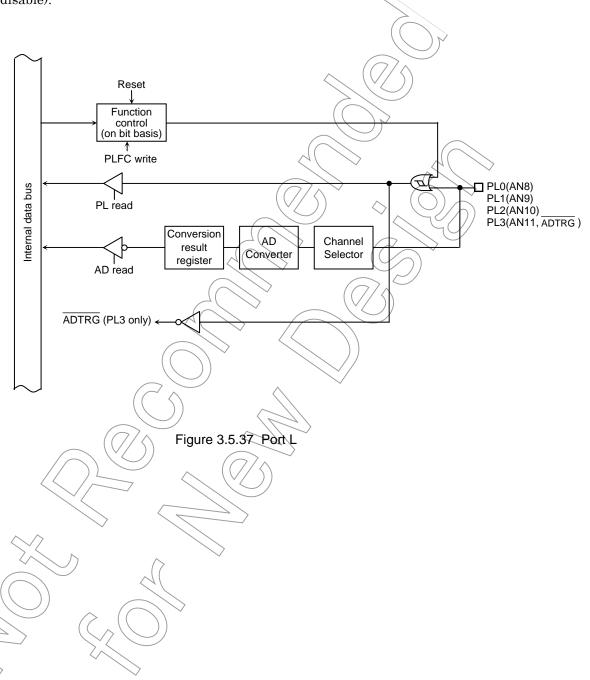

| PL0 to PL3  | 4)            | Input           | Port L: Input port (Schmitt input)                                                          |

| AN8 to AN11 |               | $\sim$ $\alpha$ | Analog input 8 to 11: Pin used for input to A/D conveter                                    |

| ADTRG       |               | (())            | A/D trigger: Signal used for request A/D start (Shared with PL3)                            |

Note: HSSO, HSSI and HSCLK functions are not built into TMP92CY23.

Table 2.2.3 Pin Names and Functions (3/3)

| Pin name     | Number of Pin | I/O    | Function                                                                                                                                             |

|--------------|---------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

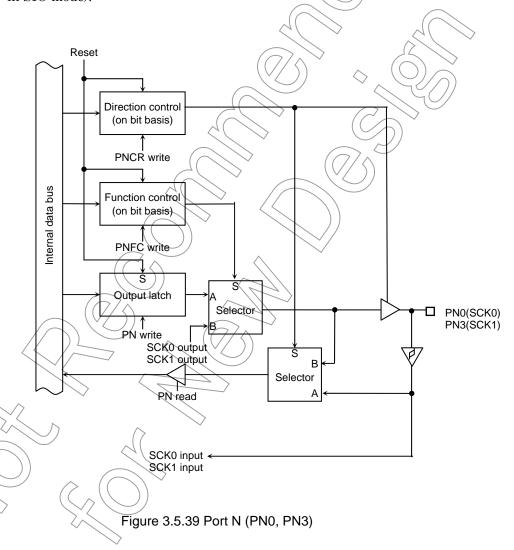

| PN0          | 1             | I/O    | Port N0: I/O port (Schmitt input)                                                                                                                    |

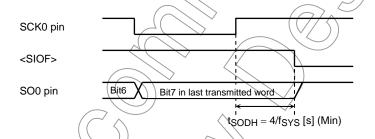

| SCK0         |               | I/O    | Serial bus interface 0 clock I/O data at SIO mode                                                                                                    |

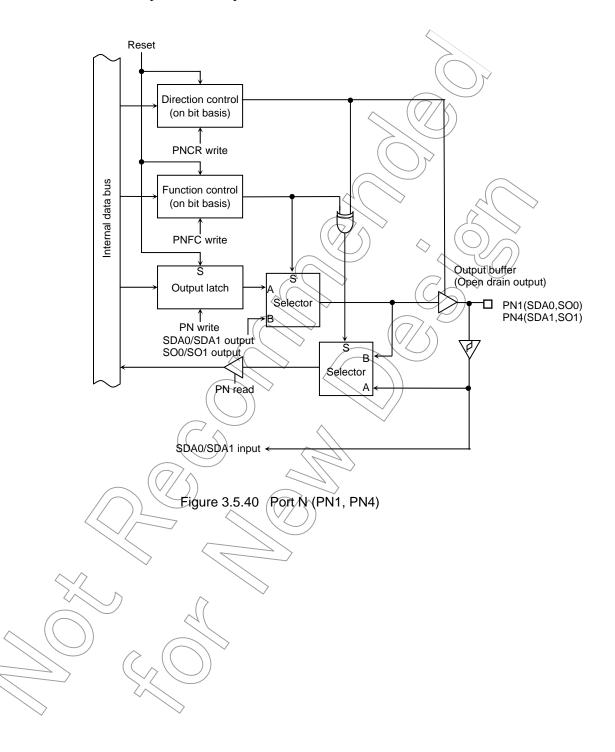

| PN1          | 1             | I/O    | Port N1: I/O port (Schmitt input, Open drain output)                                                                                                 |

| SO0          |               | Output | Serial bus interface 0 send data at SIO mode                                                                                                         |

| SDA0         |               | I/O    | Serial bus interface 0 send/receive data at I <sup>2</sup> C mode                                                                                    |

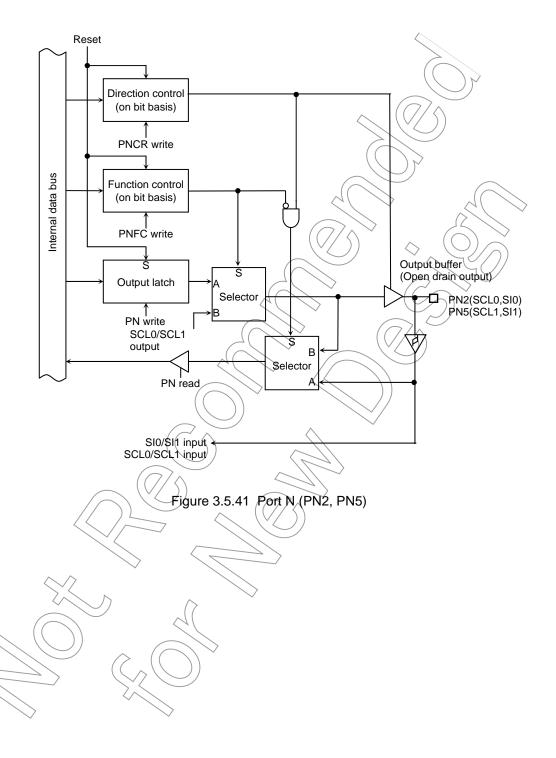

| PN2          | 1             | I/O    | Port N2: I/O port (Schmitt input, Open drain output)                                                                                                 |

| SI0          |               | Input  | Serial bus interface 0 receive data at SIO mode                                                                                                      |

| SCL0         |               | I/O    | Serial bus interface 0 clock I/O data at I <sup>2</sup> C mode                                                                                       |

| PN3          | 1             | I/O    | Port N3: I/O port (Schmitt input)                                                                                                                    |

| SCK1         |               | I/O    | Serial bus interface 1 clock I/O data at SIO mode                                                                                                    |

| PN4          | 1             | I/O    | Port N4: I/O port (Schmitt input, Open drain output)                                                                                                 |

| SO1          |               | Output | Serial bus interface 1 send data at SIO mode                                                                                                         |

| SDA1         |               | I/O    | Serial bus interface 1 send/receive data at I <sup>2</sup> C mode                                                                                    |

| PN5          | 1             | I/O    | Port N5: I/O port (Schmitt input, Open drain output)                                                                                                 |

| SI1          |               | Input  | Serial bus interface 1 receive data at SIQ mode                                                                                                      |

| SCL1         |               | I/O    | Serial bus interface 1 clock I/O data at 120 mode                                                                                                    |

| NMI          | 1             | Input  | Non-maskable interrupt request pin: Interrupt request pin with programmable falling edge level or with both edge levels programmable (Schmitt input) |

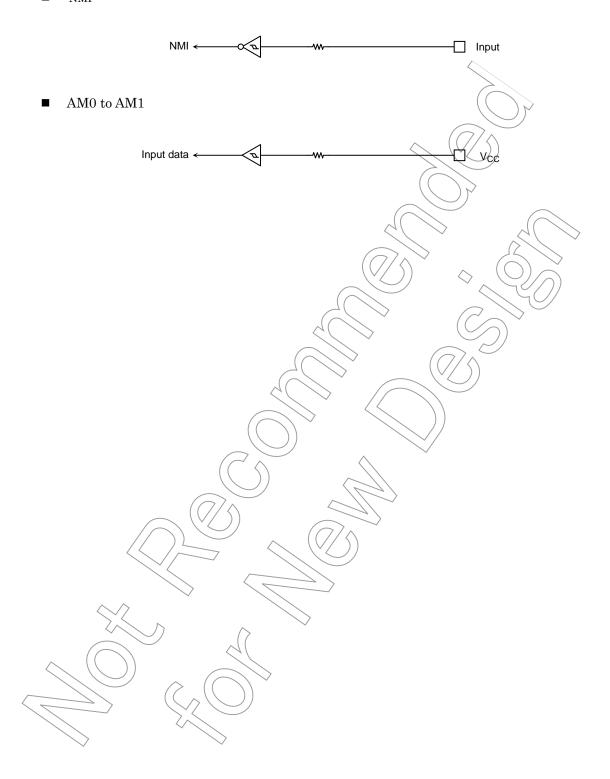

| AMO, AM1     | 2             | Input  | Operation mode: Fixed to AM1 = "1" and AM0 = "1"                                                                                                     |

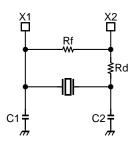

| X1 / X2      | 2             | I/O    | High-frequency oscillator connection I/O pins                                                                                                        |

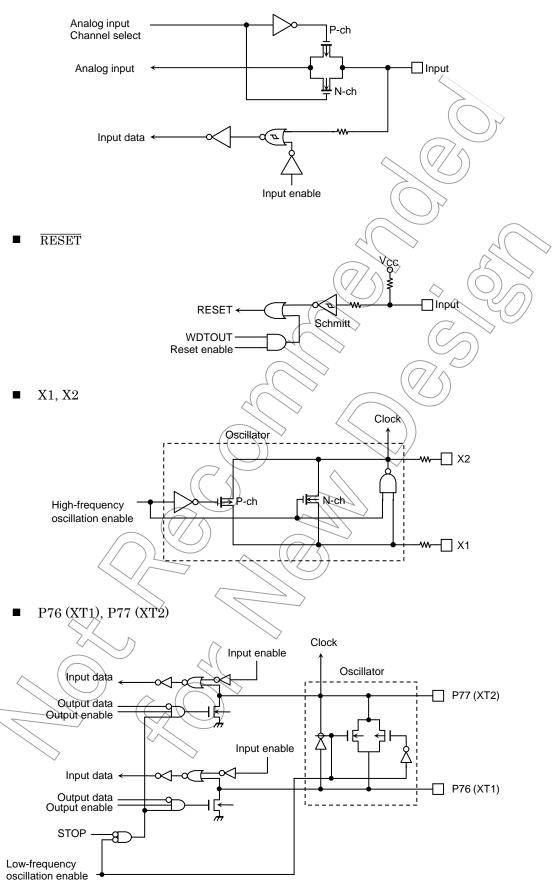

| RESET        | 1             | Input  | Reset: Intializes_TMP92CY23/CD23A (Schmitt input, with pull-up resistor)                                                                             |

| AVCC / VREFH | 1             | Input  | Pin used for both power supply pin for AD converter and standard power supply for AD converter (H)                                                   |

| AVSS / VREFL | 1             | Input  | Pin used for both GND pin for AD converter (0 V) and standard power supply pin for AD converter (L)                                                  |

| DVCC         | 4             |        | Power supply pins (All DVCC pins should be connected to the power supply pin)                                                                        |

| DVSS         | 4             | _      | GND pins (0 V) (All DVSS pins shold be connected to GND(0V))                                                                                         |

92CY23-8 2009-08-28

# 3. Operation

This section describes the basic components, functions and operation of the TMP92CY23/CD23A

### 3.1 CPU

The TMP92CY23/CD23A contains an advanced high-speed 32-bit CPU (TLCS-900/H1 CPU)

#### 3.1.1 CPU Outline

The TLCS-900/H1 CPU is a high-speed, high-performance CPU based on the TLCS-900/L1 CPU. The TLCS-900/H1 CPU has an expanded 32-bit internal data bus to process instructions more quickly.

The following is an outline of the CPU:

Table 3.1.1 TMP92CY23/CD23A Outline

| TMP92CY23/CD23A                                        |

|--------------------------------------------------------|

| 24 bits                                                |

| 32 bits 🔾                                              |

| Max 20 MHz                                             |

| 1-clock access (50 ns at fsys = 20MHz)                 |

| 32-bit 1-clock access                                  |

| 32-bit interleave 2-1-1-1-clock access                 |

| 8-bit 2-clock access                                   |

| 8- or 16-bit 2-clock access<br>(waits can be inserted) |

| 1-clock (50 ns at f <sub>SYS</sub> =20MHz)             |

| 2-clock (100 ns at f <sub>SYS</sub> =20MHz)            |

| 12 bytes                                               |

| Compatible with TLCS-900/L1                            |

| (LDX instruction is deleted)                           |

| Maximum mode only                                      |

| 8 channels                                             |

|                                                        |

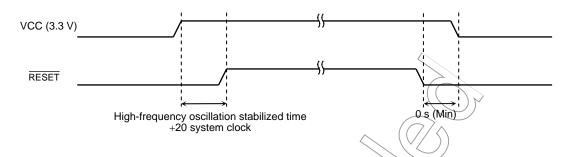

### 3.1.2 Reset Operation

When resetting the TMP92CY23/CD23A, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input low for at least 20 system clocks (64  $\mu$ s at fc = 10 MHz).

At reset, since the clock doubler (PLL) is bypassed and the clock-gear is set to 1/16, the system clock operates at 312.5 kHz (fc = 10 MHz).

When the reset has been accepted, the CPU performs the following:

• Sets the program counter (PC) as follows in accordance with the reset vector stored at address FFFF00H to FFFF02H:

PC<7:0> ← da

← data in location FFFF00H

PC<15:8>

← data in location FFFF01H

PC<23:16>

← data in location FFFF02H

- Sets the stack pointer (XSP) to 00000000H.

- Sets bits <IFF2:0> of the status register (\$R) to 111 (thereby setting the interrupt level mask register to level 7).

- Clears bits <RFP1:0> of the status register to 00 (there by selecting register bank 0).

When the reset is released, the CPU starts executing instructions according to the program counter settings. CPU internal registers not mentioned above do not change when the reset is released.

When the reset is accepted, the CPU sets internal I/O, ports and other pins as follows.

- Initializes the internal I/O registers.

- Sets the port pins, including the pins that also act as internal I/O, to general-purpose input or output port mode.

A RESET input terminal becomes "High", if reset release is carried out, a built-in FlashROM warm-up circuit (notes) will start operation, and internal reset will be canceled after the end of the circuit of operation.

Memory controller operation cannot be ensured until the power supply becomes stable after power on reset. External RAM data provided before turning on the TMP92CY23/CD23A may be corrupted because the control signals are unstable until the power supply becomes stable after power-on reset.

Note: Although this product is a MaskROM product, in order to consider as the same operation as a FlashROM product, built-in FlashROM warm-up time enters. The warm-up time of build-in FlashROM into becomes it as follows.

at  $f_{OSCH} = 10 \text{ MHz}$ 409.6µs (2<sup>12</sup>/  $f_{OSCH}$ )

92CY23-10

Figure 3.1.1 shows the example of operating the reset timing of TMP92CY23/CD23A.

Figure 3.1.1 Power on Reset Timing Example

# 3.1.3 Setting of AM0 and AM1

Set AM1 and AM0 pins as shown in Table 3.4.2 according to system usage.

Table 3.1.2 Operation Mode Setup Table

|                       | . / _ \ | V .    | /~-           |     |

|-----------------------|---------|--------|---------------|-----|

| Operation Mode        | 4(      | > Mode | e Setup Input | Pin |

| Operation Mode        | R       | ESET   | AM1,          | AM0 |

| Internal ROM starting | _       |        |               | 1   |

|                       |         |        |               |     |

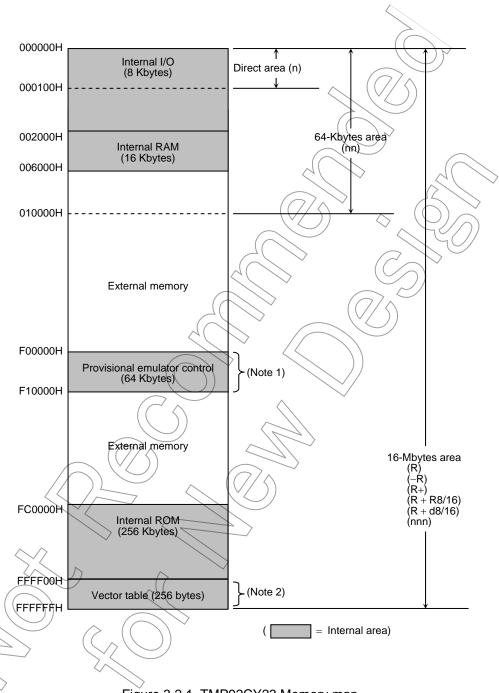

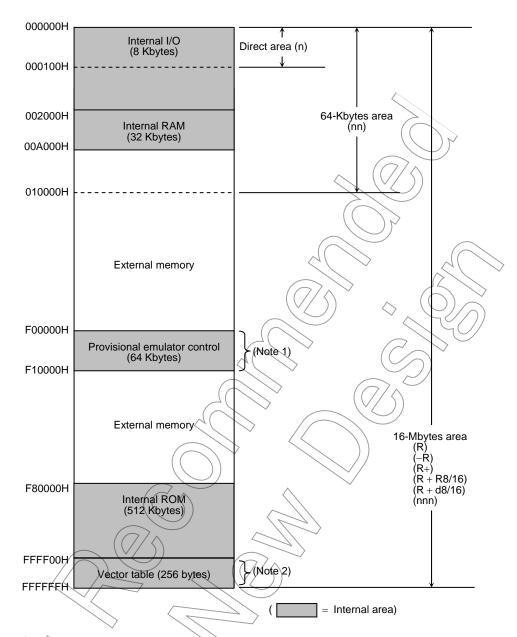

## 3.2 Memory Map

Figure 3.2.2 show the memory maps of the TMP92CY23, and Figure 3.2.2 show the memory maps of the TMP92CD23A respectively.

Figure 3.2.1 TMP92CY23 Memory map

Figure 3.2.2 TMP92CD23A Memory Map

Note 1: The Provisional emulator control area, mapped F00000H to F0FFFFH after reset, is for emulator use and so is not available.

When emulator SRWR signal and RD signal are asserted, this area is accessed. Ensure external memory is used.

Note 2: Do not use the last 16 byte area (FEFFF0H to FFFFFFH). This area is reserved for an emulator.

# 3.3 Clock Function and Stand-by Function

The TMP92CY23/CD23A contains (1) clock gear, (2) clock doubler (PLL), (3) stand-by controller and (4) noise reduction circuits. They are used for low power, low noise systems.

This chapter is organized as follows:

- 3.3.1 Block diagram of system clock

- 3.3.2 SFR

- 3.3.3 System clock controller

- 3.3.4 Clock doubler (PLL)

- 3.3.5 Noise reduction circuits

- 3.3.6 Stand-by controller

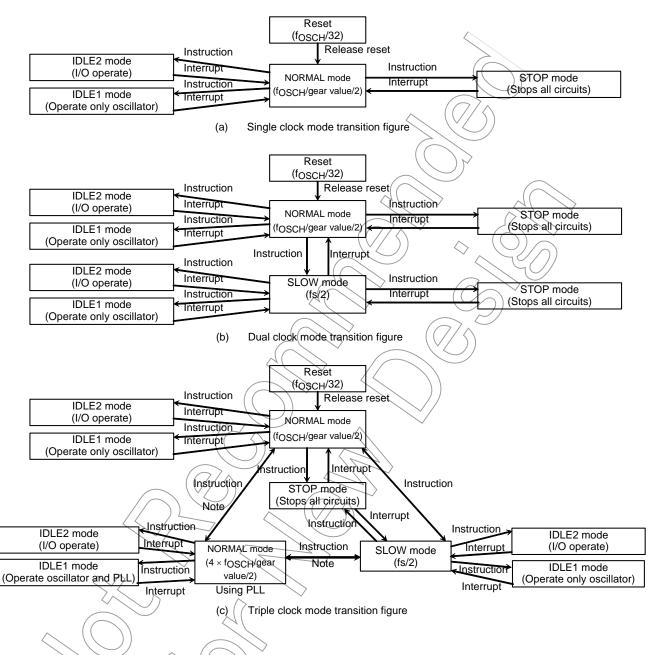

The clock operating modes are as follows: (a) single clock mode (X1, X2 pins only), (b) dual clock mode (X1, X2, XT1 and XT2 pins) and (c) triple clock mode (X1, X2, XT1 and XT2 pins and PLL).

Figure 3.3.1 shows a transition figure.

Note 1: It is not possible to control PLL in SLOW mode when shifting from SLOW mode to NORMAL mode with use of PLL. (PLL start up/stop/change write to PLLCR0<PLLON>, PLLCR1<FCSEL> register)

Note 2: When shifting from NORMAL mode with use of PLL to NORMAL mode, execute the following setting in the same order.

1) Change CPU clock (PLLCR0<FCSEL> ← "0")

2) Stop PLL circuit (PLLCR1<PLLON> ← "0")

Note 3: It is not possible to shift from NORMAL mode with use of PLL to STOP mode directly.

NORMAL mode should be set once before shifting to STOP mode. (Stop the high-frequency oscillator after stopping PLL.)

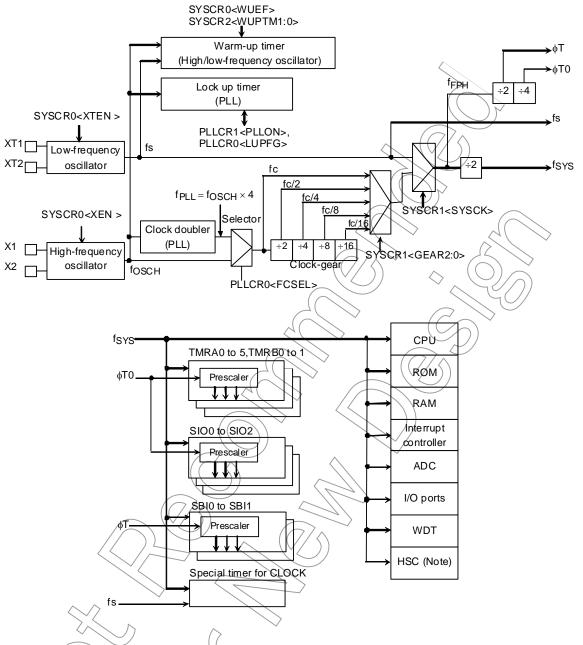

Figure 3.3.1 System Clock Block Diagram

The clock frequency input from the X1 and X2 pins is called  $f_{OSCH}$  and the clock frequency input from the XT1 and XT2 pins is called fs. The clock frequency selected by SYSCR1<SYSCK> is called the clock  $f_{FPH}$ . The system clock  $f_{SYS}$  is defined as the divided clock of  $f_{FPH}$ , and one cycle of  $f_{SYS}$  is defined as one state.

### 3.3.1 Block Diagram of System Clock

Note: This circuit is not built into TMP92CY23.

Figure 3.3 2 Block Diagram of System Clock

Frequency of external oscillator is 6 to 10MHz. Don't connect oscillator more than 10MHz. (TMP92CD23A only)

#### 3.3.2 SFR

| 3.3.    | .2 SFR      |                                                          |                                                                      |                                                                                         |                |                                                       |                                                                                                       |          |                                                   |

|---------|-------------|----------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------|

|         |             | 7                                                        | 6                                                                    | 5                                                                                       | 4              | 3                                                     | 2                                                                                                     | 1        | 0                                                 |

| SYSCR0  | Bit symbol  | XEN                                                      | XTEN                                                                 |                                                                                         |                |                                                       | WUEF                                                                                                  |          |                                                   |

| (10E0H) | Read/Write  | R/                                                       | W                                                                    |                                                                                         |                |                                                       | R/W                                                                                                   |          |                                                   |

|         | Reset State | 1                                                        | 0                                                                    |                                                                                         |                |                                                       | 0                                                                                                     |          |                                                   |

|         | Function    | High-frequency oscillator (fosch) 0: Stop 1: Oscillation | Low-<br>frequency<br>oscillator<br>(fs)<br>0: Stop<br>1: Oscillation |                                                                                         |                |                                                       | Warm-up timer 0: Write don't care 1: Write start timer 0: Read end warm-up 1: Read do not end warm-up |          |                                                   |

|         |             | 7                                                        | 6                                                                    | 5                                                                                       | 4 ((           | 7/3                                                   | 2 (                                                                                                   | 51>      | 0                                                 |

| SYSCR1  | Bit symbol  |                                                          |                                                                      |                                                                                         |                | SYSCK                                                 | GEAR2                                                                                                 | GEAR1    | GEAR0                                             |

| (10E1H) | Read/Write  |                                                          |                                                                      |                                                                                         |                |                                                       | R                                                                                                     | w        | I.                                                |

|         | Reset State |                                                          |                                                                      |                                                                                         |                |                                                       | (1 <sup>2</sup> )                                                                                     |          | 0                                                 |

|         | Function    |                                                          |                                                                      |                                                                                         |                | 1:-fs                                                 | 001: fc/2<br>010: fc/4<br>011: fc/8<br>100: fc/16<br>101: Reserve<br>110: Reserve                     | ed<br>ed |                                                   |

|         |             | 7                                                        | 6                                                                    | )) 5                                                                                    | 4              | 3                                                     | 2                                                                                                     | 1        | 0                                                 |

| SYSCR2  | Bit symbol  | -                                                        |                                                                      | WUPTM1                                                                                  | WALLWO         | HALTM1                                                | HALTM0                                                                                                |          | DRVE                                              |

| (10E2H) | Read/Write  | R/W                                                      | $\triangle$                                                          |                                                                                         |                | W                                                     |                                                                                                       |          | R/W                                               |

|         | Reset State | //0 ))                                                   |                                                                      | 1 (                                                                                     | (// Ø)         | 1                                                     | 1                                                                                                     |          | 0                                                 |

|         | Function    | Always<br>write "0"                                      | > <                                                                  | Warm-up tim<br>00: Reserve<br>01: 2 <sup>8</sup> /input f<br>10: 2 <sup>14</sup> /input | d<br>frequency | HALT mode<br>00: Reserve<br>01: STOP m<br>10: IDLE1 m | ode                                                                                                   |          | 1:<br>The inside of<br>STOP mode<br>also drives a |

Note 1: The unassigned registers SYSCR0<bit5:3>, SYSCR0<bit1:0>, SYSCR1<bit7:4>, and SYSCR2<bit7:6,1> are read as undefined value.

11: IDLE2 mode

Note 2: Low-frequency oscillator is enabled on reset.

Figure 3.3.3 SFR for System Clock

11: 2<sup>16</sup>/input frequency

pin

EMCCR0 (10E3H)

|             | 7            | 6 | 5 | 4 | 3 | 2           | 1            | 0              |

|-------------|--------------|---|---|---|---|-------------|--------------|----------------|

| Bit symbol  | PROTECT      |   |   |   |   | EXTIN(Note) | -            | DRVOSCL        |

| Read/Write  | R            |   |   |   |   |             | R/W          |                |

| Reset state | 0            |   |   |   |   | 0           | 1            | 1              |

| Function    | Protect flag |   |   |   |   | 1: External | Always write | fs oscillator  |

|             | 0: OFF       |   |   |   |   | clock       | "1"          | driver ability |

|             | 1: ON        |   |   |   |   |             |              | 1: Normal      |

|             |              |   |   |   |   |             |              | 0: Weak        |

Note: This register is a register for TMP92CY23. There is no <EXTIN> in TMP92CD23A. Please refer to the following for the register for TMP92CD23A.

EMCCR0 (10E3H)

|   |             | 7                      | 6 | 5 | 4 | 3 | 2                    | 1                   | 0                               |

|---|-------------|------------------------|---|---|---|---|----------------------|---------------------|---------------------------------|

| ) | Bit symbol  | PROTECT                |   |   |   |   | <u> </u>             | =                   | DRVOSCL                         |

|   | Read/Write  | R                      |   |   |   | 1 | )                    | RAW                 |                                 |

|   | Reset State | 0                      |   |   |   |   | 0                    | \(\lambda_1\)       | <u>)</u> 1                      |

|   | Function    | Protect flag<br>0: OFF |   |   |   |   | Always<br>write "0"  | Always<br>write "1" | fs oscillator<br>driver ability |

|   |             | 1: ON                  |   |   |   |   | $\Diamond$ $\langle$ | $2/\sqrt{n}$        | 1: Normal                       |

|   |             |                        |   |   |   | ) |                      | 5//                 | 0: Weak                         |

Note: This register is a register for TMP92CD23A.

Note1: When restarting the oscillator from the stop oscillation state (e.g. restarting the oscillator in STOP mode), set EMCCR0<DRVOSCL>= "1".

Note2: Do not write EMCCR0<EXTIN> = "1" when using external resonator.

2 7 4 3 1 6 5 0 EMCCR1 Bit symbol (10E4H) Read/Write Reset State Switch the protect ON/OFF by writing the following to 1st-KEY, 2nd-KEY Function st-KEY: write in sequence EMCCR1 = 5AH, EMCCR2 = A5H EMCCR2 Bit symbol 2nd-KEY: write in sequence EMCCR1 = A5H, EMCCR2 = 5AH (10E5H) Read/Write Reset State unction

Figure 3.3.4 SFR for System Clock

PLLCR0 (10E8H)

|             | 7 | 6                                         | 5                                           | 4 | 3 | 2 | 1              | 0 |

|-------------|---|-------------------------------------------|---------------------------------------------|---|---|---|----------------|---|

| Bit symbol  |   | FCSEL                                     | LUPFG                                       |   |   |   |                |   |

| Read/Write  |   | R/W                                       | R                                           |   |   |   |                |   |

| Reset State |   | 0                                         | 0                                           |   |   |   |                |   |

| Function    |   | Select fc<br>clock<br>0: fosch<br>1: fpLL | Lock up timer status flag 0: Not end 1: End |   |   |   | ) <del>r</del> |   |

Note: Ensure that the logic of PLLCR0<LUPFG> is different from 900/L1's DFM.

PLLCR1 (10E9H)

|             | 7                                    | 6 | 5 | 4 | 3             | 2                   | 1              | 0 |

|-------------|--------------------------------------|---|---|---|---------------|---------------------|----------------|---|

| Bit symbol  | PLLON                                |   |   |   | $\mathcal{A}$ | <del>}</del>        |                |   |

| Read/Write  | R/W                                  |   |   |   |               | $\int_{0}^{\infty}$ | $\int_{-}^{r}$ |   |

| Reset State | 0                                    |   |   |   |               |                     | 4              |   |

| Function    | Control<br>on/off<br>0: OFF<br>1: ON |   |   |   |               | \$\langle(()        |                |   |

Figure 3.3.5 SFR for PLL

### 3.3.3 System Clock Controller

The system clock controller generates the system clock signal (fsys) for the CPU core and internal I/O. It contains two oscillation circuits and a clock gear circuit for high-frequency (fc) operation. The register SYSCR1<SYSCK> changes the system clock to either fc or fs, SYSCR0<XEN> and SYSCR0<XTEN> control enabling and disabling of each oscillator, and SYSCR1<GEAR2:0> sets the high-frequency clock gear to either 1, 2, 4, 8 or 16 (fc, fc/2, fc/4, fc/8 or fc/16). These functions can reduce the power consumption of the equipment in which the device is installed.

The combination of settings  $\langle XEN \rangle = "1"$ ,  $\langle SYSCK \rangle = "0"$  and  $\langle GEAR2:0 \rangle = "100"$  will cause the system clock (fsys) to be set to fc/32 (fc/16  $\times$  1/2) after reset.

For example, fSYS is set to 0.3125 MHz when the 10 MHz oscillator is connected to the X1 and X2 pins.

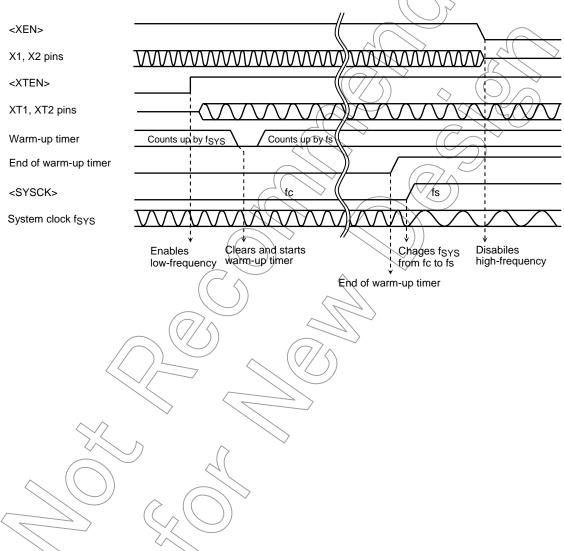

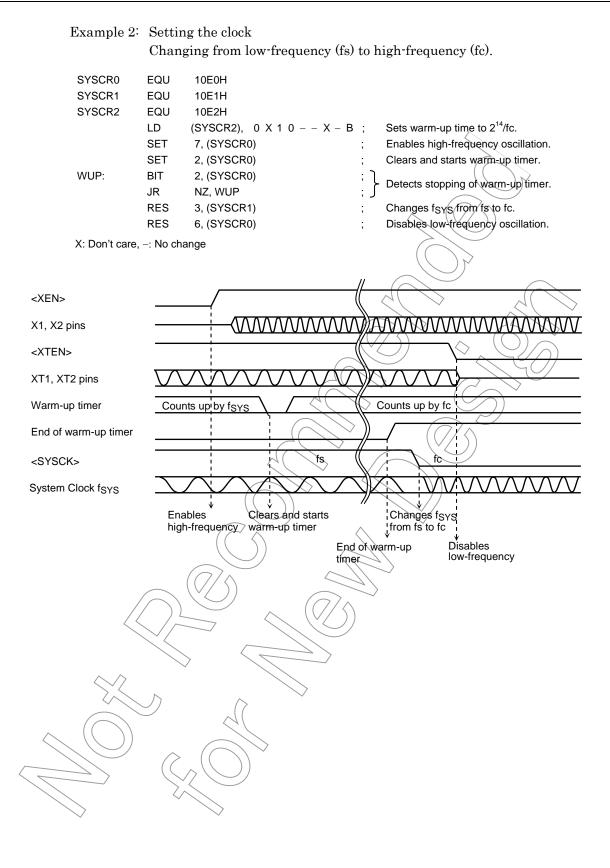

### (1) Switching from normal mode to slow mode

When the resonator is connected to the X1 and X2 pins, or to the X11 and XT2 pins, the warm-up timer can be used to change the operation frequency after stable oscillation has been attained.

The warm-up time can be selected using SYSCR2<WUPTM1:0>,

This warm-up timer can be programmed to start and stop as shown in the following examples 1 and 2.

Table 3.3.1 shows the warm-up time.

Note 1: When using an oscillator (other than a resonator) with stable oscillation, a warm-up timer is not needed.

Note 2: The warm-up timer is operated by an oscillation clock. Hence, there may be some variation in warm-up time.

Table 3.3.1 Warm-up Times

|                                                 | . (0/1                   | at f <sub>OSCH</sub> = 10 MHz, fs = 32.768 kHz |

|-------------------------------------------------|--------------------------|------------------------------------------------|

| Warm-up Time<br>SYSCR2<br><wuptm1:0></wuptm1:0> | Change to<br>Normal Mode | Change to<br>Slow Mode                         |

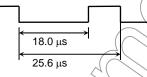

| 01 (28/frequency)                               | 25.6 (μs)                | 7.8 (ms)                                       |

| 10 (2 <sup>14</sup> /frequency)                 | 1.638 (ms)               | 500 (ms)                                       |

| 11 (2 <sup>16</sup> /frequency)                 | 6.554 (ms)               | 2000 (ms)                                      |

Example 1: Setting the clock

Changing from high-frequency (fc) to low-frequency (fs).

SYSCR0 EQU 10E0H SYSCR1 EQU 10E1H SYSCR2 EQU 10E2H LD (SYSCR2),  $0 \times 1 \cdot 1 - X - B$ ; Sets warm-up time to 2<sup>16</sup>/fs. Enables low-frequency oscillation. SET 6, (SYSCR0) Clears and starts warm-up timer. SET 2, (SYSCR0) WUP: BIT 2, (SYSCR0) Detects stopping of warm-up timer. NZ, WUP JR 3, (SYSCR1) Changes fsys from fc to fs. SET Disables high-frequency oscillation. RES 7, (SYSCR0)

X: Don't care, -: No change

92CY23-21 2009-08-28

92CY23-22 2009-08-28

#### (2) Clock gear controller

fFPH is set according to the contents of the clock gear select register SYSCR1<GEAR2:0> to either fc, fc/2, fc/4, fc/8 or fc/16. Using the clock gear to select a lower value of fFPH reduces power consumption.

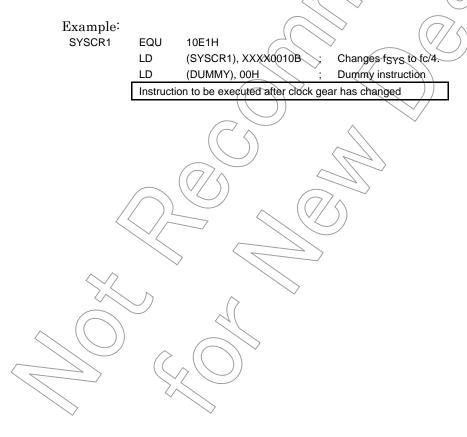

Example 3: Changing to a high-frequency gear

```

SYSCR1 EQU 10E1H

LD (SYSCR1), XXXX0001B ; Changes f<sub>SYS</sub> to fc/2.

X: Don't care

```

(High-speed clock gear changing)

To change the clock gear, write the register value to the SYSCR1<GEAR2:0> register. It is necessary for the warm-up time to elapse before the change occurs after writing the register value.

There is the possibility that the instruction following the clock gear changing instruction is executed by the clock gear before changing. To execute the instruction following the clock gear switching instruction by the clock gear after changing, input the dummy instruction as follows (instruction to execute the write cycle).

92CY23-23 2009-08-28

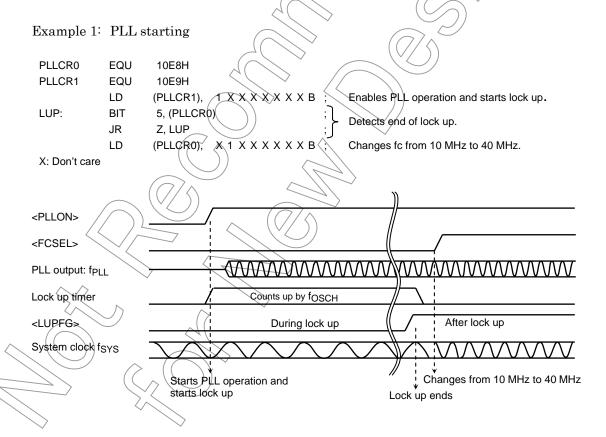

#### 3.3.4 Clock Doubler (PLL)

PLL outputs the fpLL clock signal, which is four times as fast as fosch. A low-speed-frequency oscillator can be used, even though the internal clock is high-frequency.

A reset initializes PLL to stop status, so setting to PLLCR0, PLLCR1 register is needed before use.

As with an oscillator, this circuit requires time to stabilize. This is called the lock up time and it is measured by a 16-stage binary counter. Lock up time is about 16 ms at fOSCH = 10 MHz

#### Note 1: Input frequency range for PLL

The input frequency range (High-frequency oscillation) for PLL is as follows:  $f_{OSCH} = 6$  to 10 MHz ( $V_{CC} = 3.0$  to 3.6 V)

#### Note 2: PLLCR0<LUPFG>

The logic of PLLCR0<LUPFG> is different from 900/L1's DFM. Exercise care in determining the end of lock up time.

The following is an example of settings for PLL starting and PLL stopping.

92CY23-24 2009-08-28

Example 2: PLL stopping

PLLCR0 EQU 10E8H PLLCR1 EQU 10E9H

LD (PLLCR0), X0XXXXXXB ; Changes fc from 40 MHz to10 MHz.

LD (PLLCR1), 0XXXXXXXB ; Stop PLL.

X: Don't care

<FCSEL>

<PLLON>

PLL output: fPLL

System clock f<sub>SYS</sub>

Changes from 40 MHz to 10 MHz Stops PLL operation

92CY23-25

2009-08-28

#### <u>Limitations on the use of PLL</u>

1. It is not possible to execute PLL enable/disable control in the SLOW mode (fs) (writing to PLLCR0 and PLLCR1).

PLL should be controlled in the NORMAL mode.

2. When stopping PLL operation during PLL use, execute the following settings in the same order.

```

LD (PLLCR0), 00H ; Change the clock f<sub>PLL</sub> to f<sub>OSCH</sub>

LD (PLLCR1), 00H ; PLL stop

```

3. When stopping the high-frequency oscillator during PLL use, stop PLL before stopping the high-frequency oscillator.

Examples of settings are shown below:

- (1) Start up/change control

- (OK) Low-frequency oscillator operation mode (fs) (high-frequency oscillator STOP)

→ High-frequency oscillator start up → High-frequency oscillator operation mode (fosch) → PLL start up → PLL use mode (fpld)

```

High-frequency oscillator start/warm-up start

LD

(SYSCR0),

₿;

WUP:

BIT

2, (SYSCR0)

Check for warm-up end flag

NZ. WUP

JR

B :

LD

(SYSCR1),

Change the system clock fs to fosch

В

PLL start-up/lock up start

ΙD

(PLLCR1),

LUP:

BIT

5, (PLLCR0)

Check for lock up end flag

JR

Z. LUP

LD

(PLLCR0),

Change the system clock fosch to fpll

```

(OK) Low-frequency oscillator operation mode (fs) (high-frequency oscillator Operate) High-frequency oscillator operation mode (fosch) → PLL start up → PLL use mode (fpLL)

```

LD

(SYSCR1),

В

Change the system clock fs to fosch

LD

(PLLCR1),

PLL start-up/lock up start

LUP:

BIT

5, (PLLCR0)

Check for lock up end flag

JR

Z, LUP

QJ

(PLLCR0),

Change the system clock fosch to fpll

```

(Error) Low-frequency oscillator operation mode (fs) (high-frequency oscillator STOP)  $\rightarrow$  High-frequency oscillator start up  $\rightarrow$  PLL start up  $\rightarrow$  PLL use mode (fpl.)

```

(SYSCRO),

LD

High-frequency oscillator start/warm-up start

WUP:

BIT

2, (SYSCR0)

Check for warm-up end flag

JR

NZ, WUP

LD

(PLLCR1),

PLL start-up/lock up start

LUP:

BIT

5, (PLLCR0)

Check for lock up end flag

JR

Z, LUP

LD

(PLLCR0),

Change the internal clock fosch to fpll

LD

(SYSCR1),

Change the system clock fs to fPLL

```

92CY23-26 2009-08-28

TOSHIBA

#### (2) Change/stop control

(OK) PLL use mode (f<sub>PLL</sub>)  $\rightarrow$  High-frequency oscillator operation mode (f<sub>OSCH</sub>)  $\rightarrow$  PLL Stop  $\rightarrow$  Low-frequency oscillator operation mode (fs)  $\rightarrow$  High-frequency oscillator stop

TMP92CY23/CD23A

```

LD

(PLLCR0),

- 0 - - - - - B;

Change the system clock fell to fosch

LD

(PLLCR1),

0 - - - - - B:

PLL stop

- 1 - - - B;

Change the system clock fosch to fs

LD

(SYSCR1),

---B:

LD

(SYSCR0),

High-frequency oscillator stop

```

(Error) PLL use mode (fpLL) → Low-frequency oscillator operation mode (fs) → PLL stop → High-frequency oscillator stop

```

LD (SYSCR1), ---- B; Change the system clock fpll to fs

LD (PLLCR0), -0---- B; Change the internal clock (fc) fpll to fosch

LD (PLLCR1), 0---- B; PLL stop

LD (SYSCR0), 0---- B; High-frequency oscillator stop

```

(OK) PLL use mode (fPLL) → Set the STOP mode → High frequency oscillator operation mode (fOSCH) → PLL stop → Halt (High frequency oscillator stop)

(Error) PLL use mode (fpll)  $\rightarrow$  Set the STOP mode  $\rightarrow$  Halt (High-frequency oscillator stop)

```

LD (SYSCR2), ---- 0 1 B: Set the STOP mode (This command can execute before use of PLL)

```

**TOSHIBA**

#### 3.3.5 Noise Reduction Circuits

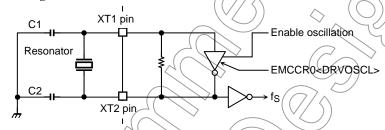

Noise reduction circuits are built-in, allowing implementation of the following features.

- (1) Reduced drivability for low-frequency oscillator

- (2) Reduced drivability for low-frequency oscillator (Note)

- (3) SFR protection of register contents

Note: This function can use only TMP92CY23.

These functions need a setup by EMCCR0, EMCCR1, and EMCCR2 register.

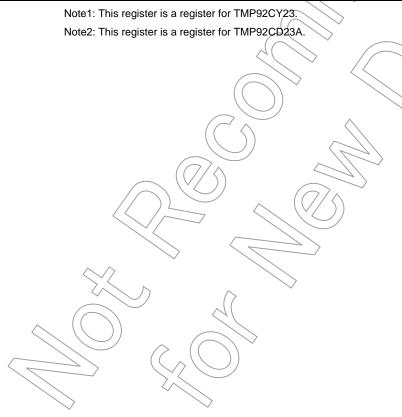

(1) Reduced drivability for low-frequency oscillator

(Purpose)

Reduces noise and power for oscillator when a resonator is used.

(Block diagram)

(Setting method)

The drive ability of the oscillator is reduced by writing "0" to the EMCCR0<DRVOSCL> register. At reset, <DRVOSCL> is initialized to "1" and the oscillator starts oscillation by normal drivability when the power-supply is on.

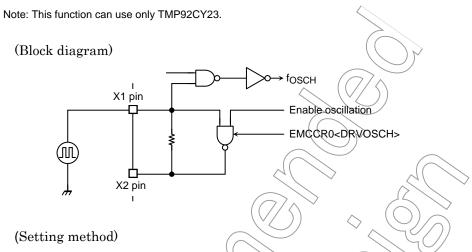

### (2) Single drive for high-frequency oscillator (Note)

#### (Purpose)

Remove the need for twin drives and prevent operational errors caused by noise input to X2 pin when an external oscillator is used.

The oscillator is disabled and starts operation as buffer by writing "1" to EMCCR0<EXTIN> register. X2 pin's output is always "1".)

At reset, <EXTIN> is imitialized to "0".

92CY23-29 2009-08-28

#### (2) Runaway prevention using SFR protection register

(Purpose)

Prevention of program runaway caused by introduction of noise.

Write operations to a specified SFR are prohibited so that the program is protected from runaway caused by stopping of the clock or by changes to the memory control register (memory controller) which prevent fetch operations.

Runaway error handling is also facilitated by INTPO interruption.

#### Specified SFR list

1. Memory controller

B0CSL/H, B1CSL/H, B2CSL/H, B3CSL/H, BEXCSL/H

MSAR0, MSAR1, MSAR2, MSAR3,

MAMR0, MAMR1, MAMR2, MAMR3, RMEMCR

- 2. Clock gear SYSCR0, SYSCR1, SYSCR2, EMCCR0

- 4. PLL PLLCR0, PLLCR1

#### (Operation explanation)

Execute and release of protection (write operation to specified SFR) becomes possible by setting up a double key to EMCCR1 and EMCCR2 registers.

#### (Double key)

1st KEY: writes in sequence, 5AH at EMCCR1 and A5H at EMCCR2 2nd KEY: writes in sequence, A5H at EMCCR1 and 5AH at EMCCR2

Protection state can be confirmed by reading EMCCRO<PROTECT>.

At reset, protection becomes OFF.

INTPO interruption also occurs when a write operation to the specified SFR is executed with protection in the ON state.

### 3.3.6 Stand-by Controller

(1) HALT modes and port drive register

When the HALT instruction is executed, the operating mode switches to IDLE2, IDLE1 or STOP mode, depending on the contents of the SYSCR2<HALTM1:0> register.

The subsequent actions performed in each mode are as follows:

1. IDLE2: only the CPU halts.

The internal I/O is available to select operation during IDLE2 mode by setting the following register.

Table 3.3.2 shows the register setting operation during IDLE2 mode.

Table 3.3.2 SFR Setting Operation during IDLE2 Mode

| Internal I/O | SFR                       |

|--------------|---------------------------|

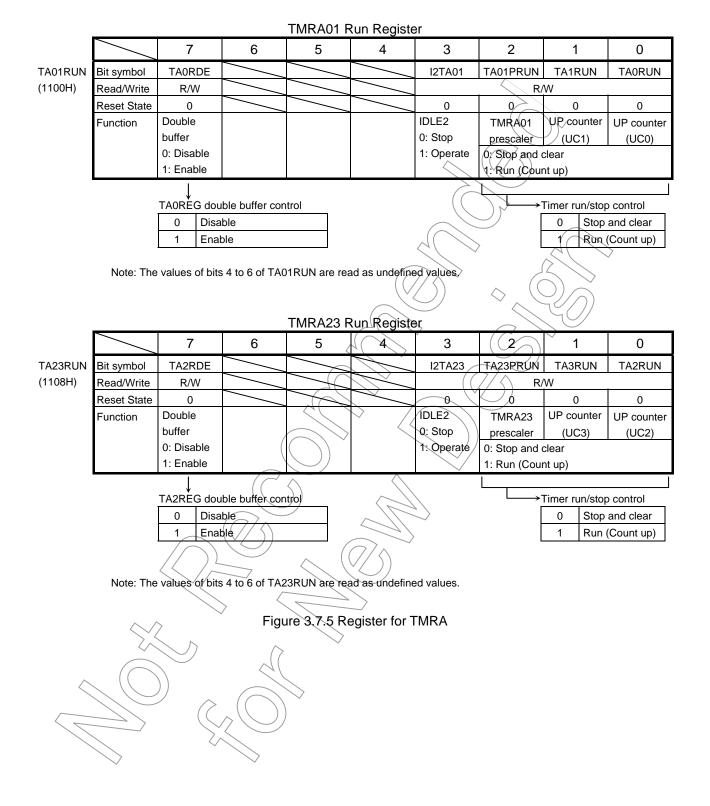

| TMRA01       | TA01RUN <i2ta01></i2ta01> |

| TMRA23       | TA23RUN<12TA23>           |

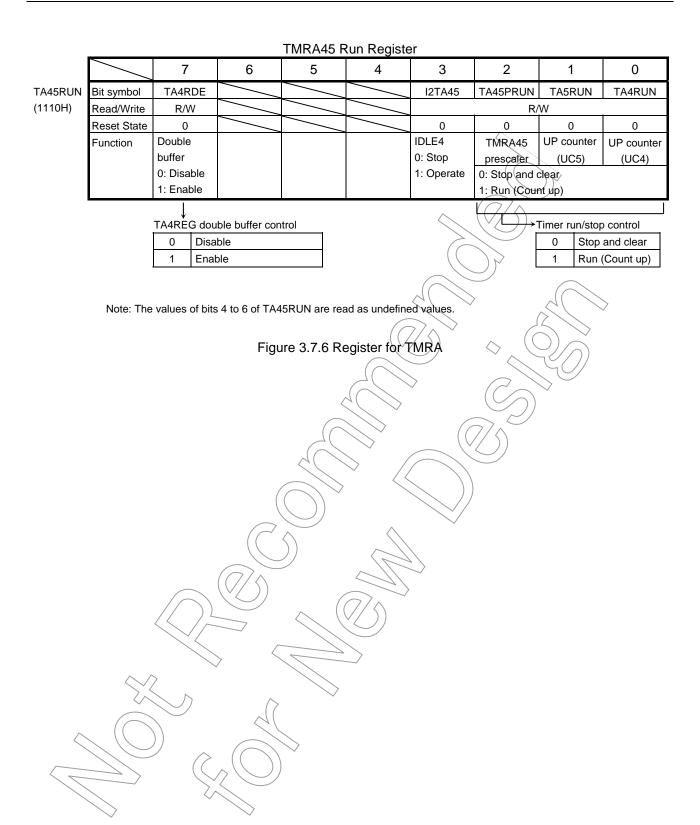

| TMRA45       | TA45RUN < 12TA45>         |

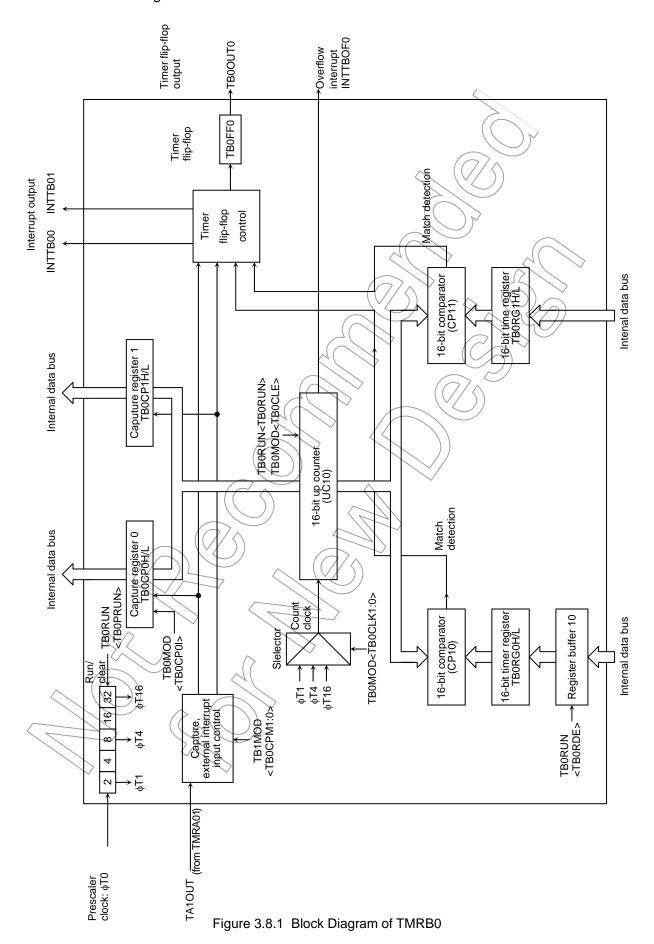

| TMRB0        | TBORUN<12TBO>             |

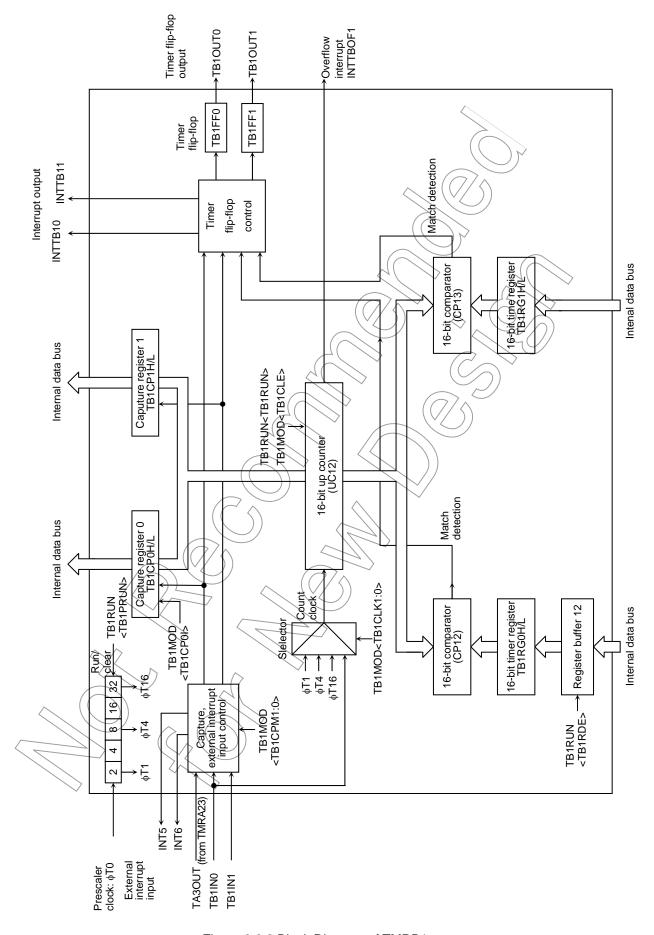

| TMRB1        | TB1RUN<12TB1>             |

| SIO0         | SC0MOD1 <i2s0></i2s0>     |

| SIO1         | SC1MOD1 <i2s1></i2s1>     |

| SIO2         | SC2MOD1 <i2s2></i2s2>     |

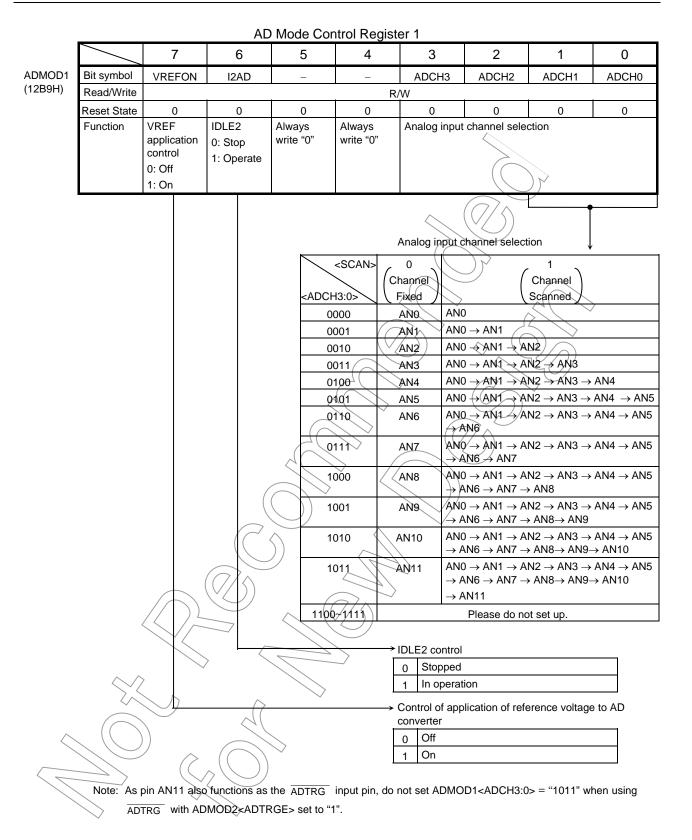

| AD converter | ADMOD1 <i2ad></i2ad>      |

| WDT (        | WDMOD<12WDT>              |

| SBI0         | SBI0BR0 <i2sbi0></i2sbi0> |

| SBI1         | SBI1BR0 <i2sbi1></i2sbi1> |

- 2. IDLE1: Only the oscillator and the Special timer for CLOCK continue to operate.

- 3. STOP: All internal circuits stop operating.

The operation of each of the different HALT modes is described in Table 3.3.3.

Table 3.3.3 I/O Operation during HALT Modes

|  |                              | \ )                              |                                                                                                       |         |      |  |

|--|------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------|---------|------|--|

|  | HALT Mode                    |                                  | IDLE2                                                                                                 | IDLE1   | STOP |  |

|  | SYSCR2 <haltm1:0></haltm1:0> |                                  | <u> </u>                                                                                              | 10      | 01   |  |

|  |                              | CPU                              | Stop                                                                                                  |         |      |  |

|  | Block                        | I/O ports                        | The state at the time of "HALT"  Table 3.3.7 and Table 3.3.8 reference instruction execution is held. |         |      |  |

|  |                              | TMRA, TMRB SIO, SBI AD converter | Available to select operation block                                                                   | Stop    |      |  |

|  |                              | WDT                              | > spanning                                                                                            |         |      |  |

|  |                              | Interrupt controller             |                                                                                                       |         |      |  |

|  |                              | HSC (Note)                       | Operate                                                                                               |         |      |  |

|  |                              | Special timer for<br>CLOCK       | o político.                                                                                           | Operate |      |  |

Note: This circuit is not built into TMP92CY23.

#### (2) How to release the HALT mode

These halt states can be released by resetting or requesting an interrupt. The halt release sources are determined by the combination of the states of the interrupt mask register <IFF2:0> and the HALT modes. The details for releasing the halt status are shown in Table 3.3.4.

#### Release by interrupt requesting

The HALT mode release method depends on the status of the enabled interrupt. When the interrupt request level set before executing the HALT instruction exceeds the value of the interrupt mask register, the interrupt is processed depending on its status after the HALT mode is released, and the CPU status executing the instruction that follows the HALT instruction. When the interrupt request level set before executing the HALT instruction is less than the value of the interrupt mask register, HALT mode release is not executed. (in non-maskable interrupts, interrupt processing is processed after releasing the HALT mode regardless of the value of the mask register.) However only for INTO to INT7, INTRTC interrupts, even if the interrupt request level set before executing the halt instruction is less than the value of the interrupt mask register, HALT mode release is executed. In this case, the interrupt is processed, and the CPU starts executing the instruction following the HALT instruction, but the interrupt request flag is held at "1".

#### Release by resetting

Release of all half statuses is executed by resetting.

When the STOP mode is released by RESET, it is necessary to allow enough resetting time (see Table 3.3.5) for operation of the oscillator to stabilize.

When releasing the HALT mode by resetting, the internal RAM data keeps the state before the HALT instruction is executed. However the other settings contents are initialized. (Releasing due to interrupts keeps the state before the HALT instruction is executed.)

| Status of Received Interrupt |          |                                                     | Interrupt Enabled                         |       | Interrupt Disabled                   |         |                                        |      |

|------------------------------|----------|-----------------------------------------------------|-------------------------------------------|-------|--------------------------------------|---------|----------------------------------------|------|

|                              |          |                                                     | (Interrupt level) $\geq$ (Interrupt mask) |       | (Interrupt level) < (Interrupt mask) |         |                                        |      |

| HALT Mode                    |          |                                                     | IDLE2                                     | IDLE1 | STOP                                 | IDLE2   | IDLE1                                  | STOP |

|                              |          | NMI                                                 | •                                         | •     | <b>♦</b> *1                          | -//     | _                                      | _    |

|                              |          | INTWDT                                              | •                                         | ×     | ×                                    | - (     | -                                      | _    |

|                              |          | INT0 to INT4, INT7 (Note 1)                         | •                                         | •     | <b>♦</b> *1                          | 0       | ) / 0                                  | 0*1  |

| ø                            |          | INT5,INT6 (PORT) (Note 1)                           | •                                         | •     | <b>♦</b> *1                          | 600     | 0                                      | 0*1  |

| lanc                         |          | INT5,INT6 (TMRB1)                                   | •                                         | ×     | × <                                  | ( ( /×/ | ×                                      | ×    |

| lea                          |          | INTTA0 to INTTA5                                    | •                                         | ×     | ×                                    | )<br>)  | ×                                      | ×    |

| Halt State Clearance         | nterrupt | INTB00, INTTB01, INTTB10, INTTB11, INTTB00, INTTB01 | •                                         | ×     | × ((                                 | *       | ×                                      | ×    |

| of Halt S                    | Int      | INTRX0 to INTRX2,<br>INTTX0 to INTTX2               | •                                         | ×     |                                      | )<br>>  | *                                      | ×    |

| 9                            |          | INTAD                                               | •                                         | ×     | ×                                    | ×       | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ | ×    |

| Source                       |          | KWI                                                 | •                                         | •     | <b>( /</b> */\                       | Δ       | $\Delta$                               | Δ    |

| S                            |          | INTRTC                                              | •                                         | •     | $( \times ( \times ) )$              | 0       |                                        | ×    |

|                              |          | INTSBE0 to INTSBE1                                  | •                                         | ×     | ×                                    | × <     | \(\x\)                                 | ×    |

|                              |          | INTHSC (Note4)                                      | •                                         | ×     | ×                                    | (%)     | $\searrow$                             | ×    |

|                              |          | RESET                                               | Initialize LSI                            |       |                                      |         |                                        |      |

Table 3.3.4 Source of Halt State Clearance and Halt Clearance Operation

- ♦: After clearing the HALT mode, CPU starts interrupt processing.

- o: After clearing the HALT mode, CPU resumes executing starting from the instruction following the HALT instruction.

- x: Cannot be used to release the HALT mode.

- -: The priority level (interrupt request level) of non-maskable interrupts is fixed to 7, the highest priority level. This combination is not available.

- Δ: Since KWI does not have a function as interruption, this combination does not exist.

- \*1: Release of the HALT mode is executed after warm up time has elapsed.

- Note 1: When the HALT mode is cleared by an INTO to 7 interrupt of the level mode in the interrupt enabled status, hold level "H" until starting interrupt processing. If level "L" is set before holding level "L", interrupt processing is correctly started.

- Note 2: Although a KWI can cancel all HALT mode states, the function as interruption does not have it.

- Note 3: Specify the HSCSEL register when selecting INTTX1 or INTHSC interrupt with the same interrupt factor.

- Note4: The INTHSC interrupt is not built into TMP92CY23.

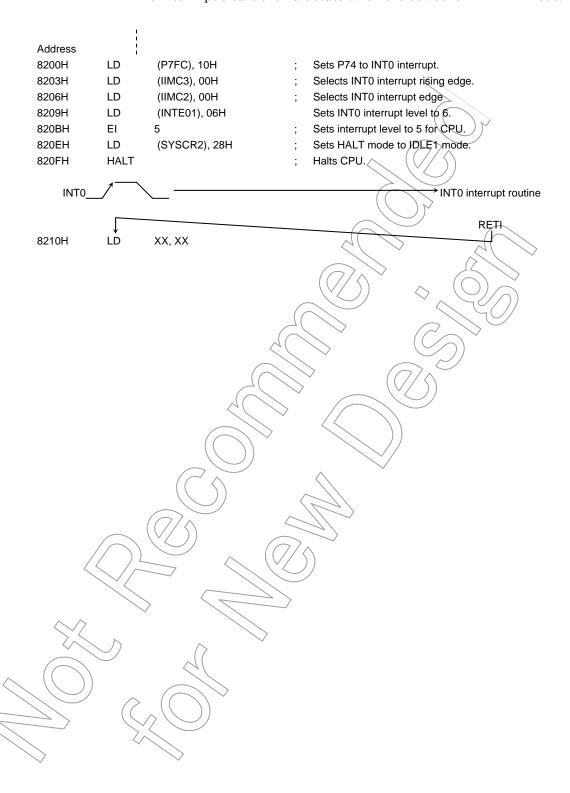

Example: Releasing IDLE1 mode

An INT0 interrupt clears the halt state when the device is in IDLE1 mode.

92CY23-34 2009-08-28

## (3) Operation

### 1. IDLE2 mode

In IDLE2 mode only specific internal I/O operations, as designated by the IDLE2 setting register, can take place. Instruction execution by the CPU stops.

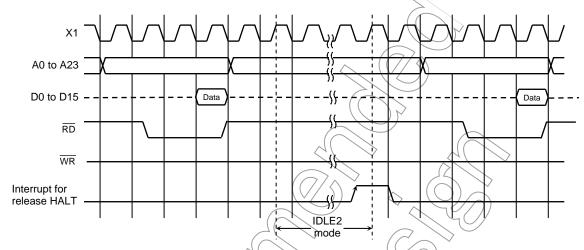

Figure 3.3.6 illustrates an example of the timing for clearance of the IDLE2 mode halt state by an interrupt.

Figure 3.3.6 Timing Chart for IDLE2 Mode Halt State Cleared by Interrupt

### 2. IDLE1 mode

In IDLE1 mode, only the internal oscillator and Special timer for Clock continue to operate. The system clock stops.

In the halt state, the interrupt request is sampled asynchronously with the system clock; however, clearance of the halt state (e.g., restart of operation) is synchronous with it.

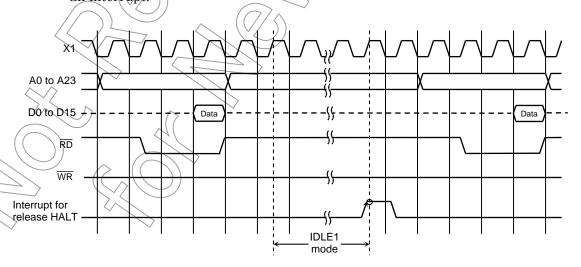

Figure 3.3.7 illustrates the timing for clearance of the IDLE1 mode halt state by an interrupt.

Figure 3.3.7 Timing Chart for IDLE1 Mode Halt State Cleared by Interrupt

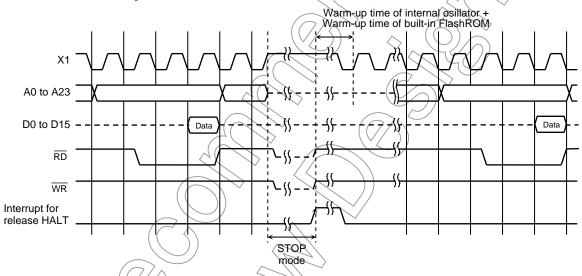

### STOP mode

When STOP mode is selected, all internal circuits stop, including the internal oscillator.

After STOP mode has been cleared system clock output starts when the warm-up time by the counter for a warm-up of internal oscillator and built-in FlashROM warm-up time.

The example of a setting of the Warm-up time at the time of STOP mode release is shown in Table 3.3.5. The warm-up time of built-in FlashROM is shown in Table 3.3.6.

Note: Although this product is a MaskROM product; in order to consider as the same operation as a FlashROM product, built-in FlashROM warm-up time enters.

Figure 3.3.8 illustrates the timing for clearance of the STOP mode halt state by an interrupt.

Figure 3.3.8 Timing Chart for STOP Mode Halt State Cleared by Interrupt

Table 3.3.5 Example of Warm-up Time after Releasing STOP Mode

at  $f_{OSCH} = 10 \text{ MHz}$ ,  $f_{SCH} = 32.768 \text{ kHz}$

| SY\$CR1         | SYSCR2 <wuptm1:0></wuptm1:0> |                       |                       |  |  |  |  |

|-----------------|------------------------------|-----------------------|-----------------------|--|--|--|--|

| <sysck></sysck> | 01 (28)                      | 10 (2 <sup>14</sup> ) | 11 (2 <sup>16</sup> ) |  |  |  |  |

| 0 (fc)          | 25.6 μs                      | 1.638 ms              | 6.554 ms              |  |  |  |  |

| (1 (fs) )       | 7.8 ms                       | 500 ms                | 2000 ms               |  |  |  |  |

Table 3.3.6 Example of Warm-up Time after Built-in FlashROM (at the time of STOP mode release)

at  $f_{OSCH} = 10$  MHz,  $f_{SCH} = 32.768$  kHz

2009-08-28

|        | 00011                                         |

|--------|-----------------------------------------------|

| 0 (fc) | 409.6 μs (2 <sup>12</sup> /f <sub>OSCH)</sub> |

| 1 (fs) | 125 ms (2 <sup>12</sup> /fs )                 |

Table 3.3.7 Input Buffer State Table

|           | Input Buffer State Input Buffer State |                 |                     |                      |              |                                                 |                                                                      |                             |                     |                      |  |  |

|-----------|---------------------------------------|-----------------|---------------------|----------------------|--------------|-------------------------------------------------|----------------------------------------------------------------------|-----------------------------|---------------------|----------------------|--|--|

|           |                                       |                 | 14/1                | - ODIII:-            | Inp          | out Buffer Sta                                  | ate                                                                  | I. IIAIT                    | (OTOD)              |                      |  |  |

|           | Input                                 |                 | When the oper       | e CPU is             | In HALT mod  | de (IDLE1/2)                                    | DD) "                                                                | <u>In HALT m</u><br>E = "1" | ode (STOP)          | "0"                  |  |  |

| Port      | Function                              | During          |                     |                      |              |                                                 |                                                                      |                             | DRVE                |                      |  |  |

| Name      | Name                                  | During<br>Reset | When                | When                 | When used as | When                                            | When used as                                                         | When                        | When                | When                 |  |  |

|           | Name                                  | Reset           | used as<br>Function | used as<br>Input pin | Function     | used as<br>Input pin                            | Function                                                             | used as<br>Input pin        | used as<br>Function | used as<br>Input pin |  |  |

|           |                                       |                 | pin                 | iliput pili          | pin          | input pin                                       | pin                                                                  | iliput pili                 | pin                 | iliput pili          |  |  |

| P00-P07   | D0-D7                                 |                 | ON upon             |                      | Piii         |                                                 | Piii                                                                 |                             | PIII                |                      |  |  |

|           |                                       |                 | external            |                      |              |                                                 |                                                                      |                             |                     |                      |  |  |

| P10-P17   | D8-D15                                |                 | read (*1)           |                      |              |                                                 |                                                                      | (( ))                       | >                   |                      |  |  |

| P40-P47   | _                                     | OFF             |                     |                      |              |                                                 |                                                                      |                             |                     |                      |  |  |

| P50-P57   | _                                     | 0.1             |                     |                      | OFF          |                                                 | OFF /                                                                | 7                           | OFF                 |                      |  |  |

| P60-P67   | _                                     |                 |                     | ON                   | 0            |                                                 |                                                                      | ( ))                        | 011                 |                      |  |  |

| P70(*2)   | _                                     |                 | OFF                 |                      |              |                                                 | ///                                                                  |                             |                     |                      |  |  |

| P71-P73   |                                       |                 |                     |                      |              |                                                 |                                                                      | >                           |                     |                      |  |  |

| (*2)      | _                                     | ON              |                     |                      |              |                                                 | $\backslash \backslash \backslash \backslash \backslash \backslash $ |                             |                     |                      |  |  |

| P74       | INT0                                  | OIV             |                     |                      |              |                                                 | ON                                                                   |                             | ON                  |                      |  |  |

| F74       | Oscillator                            |                 | ON                  | OFF                  | ON           | $\mathcal{A}($                                  | ON                                                                   | _                           |                     |                      |  |  |

| P76       | XT1                                   | OFF             | OFF                 | OFF                  | OFF          |                                                 | ŎFF                                                                  |                             | OFF                 |                      |  |  |

| D77       | Port                                  | OFF             |                     |                      |              |                                                 | $\rightarrow$                                                        | 14                          |                     |                      |  |  |

| P77       |                                       |                 | _                   |                      | -            | $( \langle //                                 $ | -                                                                    |                             | ×                   |                      |  |  |

| P83       | WAIT                                  |                 |                     |                      | OFF          |                                                 | OFF⇔                                                                 | 7                           | OFF                 |                      |  |  |

| PC0       | TA0IN                                 |                 |                     |                      |              |                                                 |                                                                      | ///                         | O/                  |                      |  |  |

| PC1       | INT1                                  |                 |                     |                      |              |                                                 |                                                                      |                             |                     |                      |  |  |

| PC2       | INT2                                  |                 |                     |                      | 4( /         |                                                 | ((                                                                   |                             |                     |                      |  |  |

| PC3       | INT3                                  |                 |                     |                      |              | ~                                               |                                                                      |                             | ON                  |                      |  |  |

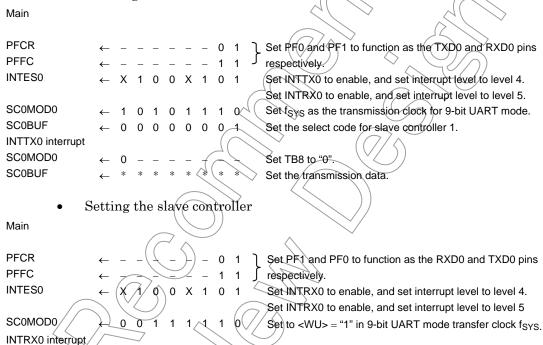

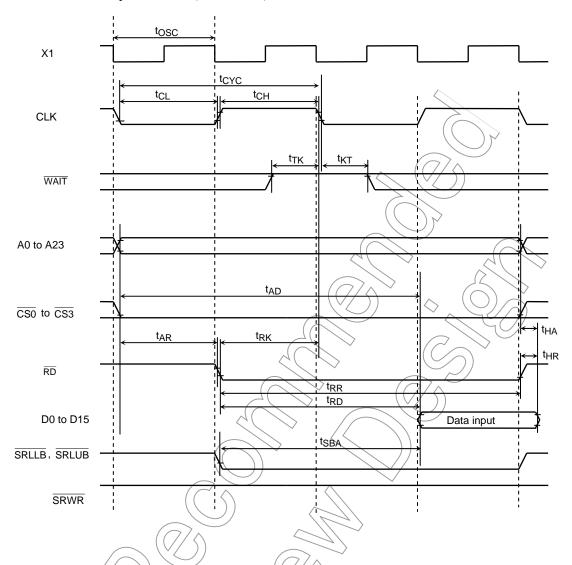

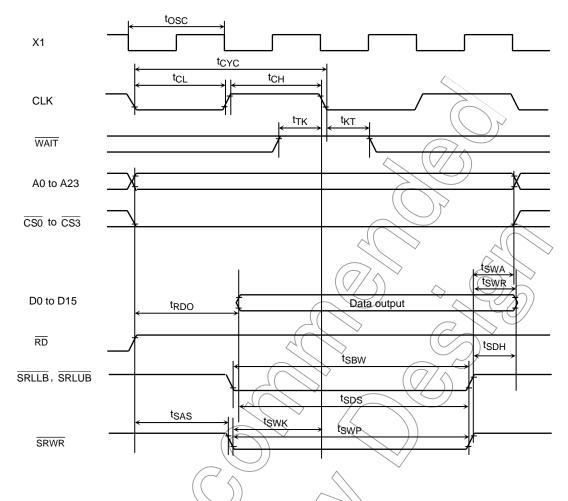

| PD0       | INT4                                  |                 |                     | (                    |              |                                                 | (O/4)                                                                | \                           |                     |                      |  |  |