# MN8355

# Display Processor Unit(DPU)

#### Outline

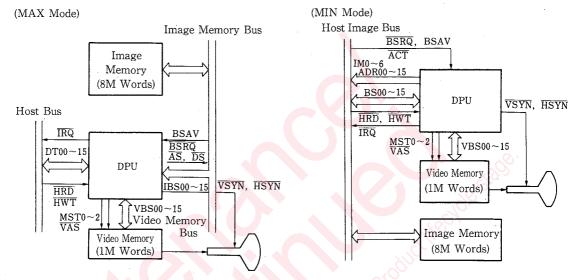

The DPU(Display Processor Unit)ME8355 is a basic LSI for a bit map multiwindow display unit which has realized flexible controls (non-interlace,interlace,interlace shrunk scan) for the CRT display unit, and high-speed data transfer control functions for the image memory, which stores original pictures, and the video memory, which stores CRT display data.

#### ■ Features

- High-speed data transfer function

High-speed transfer of rectangular area data in the video memory and image memory data enlargement/reduction

- 8 kinds of operations for transfer-to data

- CRT display control function 3 scan modes

- Cursor control function 255 x 255 optionally shaped cursor display enabled Background data mask function at cursor display time

- Two dimensional coordinates control function

Specification of the two dimensional coordinates of data transfer control parameters for the video memory and image memory

- Flexible system configuration2 pin functions of MAX and MIN modes

- Memory space:1M words for the video memory,8M words for the image memory

- No.of display pixels:Max.4,096 x 4,096 dots

- Transfer control speed:500 ns/word(max.clock at 16 MHz)

- Internal and external buses of 16 bits/word

- •84-pin flag package

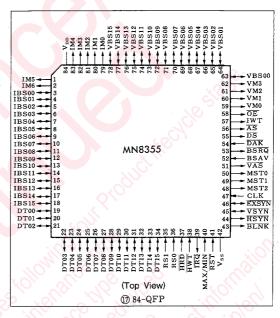

#### Pin Configuration

#### Applications

- Work stations

- Intelligent terminals

- Word processors

- Personal computers, etc

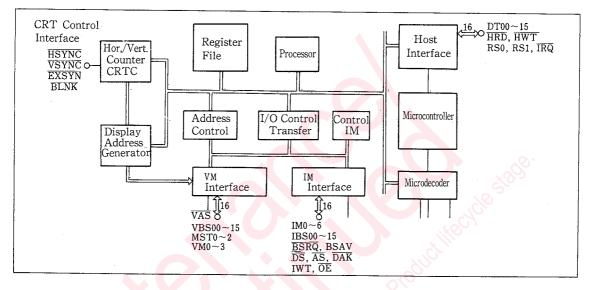

#### Block Diagram

### Absolute Maximum Ratings (T<sub>a</sub>=95°C, T<sub>j</sub>≤150°C)

| Item                          | Symbol          | Rating                   | Unit |

|-------------------------------|-----------------|--------------------------|------|

| Supply voltage                | $V_{DD}$        | -0.3~7                   | - V  |

| Pin voltage                   | V <sub>IN</sub> | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Power consumption             | P <sub>D</sub>  | 400                      | mW   |

| Operating ambient temperature | $T_{opr}$       | 0~+95                    | °C   |

| Storage temperature           | $T_{ m stg}$    | -55~+150                 | °C   |

## ■ Recommended Operating Conditions

$V_{DD} = 5V \pm 5\%$ ,  $V_{SS} = 0V$ ,  $T_{opr} = 0$  to 70°C

#### ■ Electrical Characteristics

## ●DC Characteristics (VDD=5V±5%, Vss=OV, Ta=O to 70°C)

|                | Item                      | Symbol           | Condition                       | min.                                             | typ. | max.            | Unit           |

|----------------|---------------------------|------------------|---------------------------------|--------------------------------------------------|------|-----------------|----------------|

| Supply cur     | rrent                     | $I_{DD}$         | المالي دور                      |                                                  |      | 80              | mA             |

| Power con      | sumption                  | $P_{D}$          | .x 12 M.                        | <del>                                     </del> | -    | 400             | mW             |

|                | Input pins other than CLK | V <sub>IH</sub>  | 2.4 to V <sub>DD</sub> for HWT  | 2.0                                              |      | V <sub>DD</sub> | V              |

| Input voltage  | _ // U                    | VIL              |                                 | 0                                                | _    | 0.8             | V              |

| mput voitage   | CLK input                 | V <sub>ICH</sub> | 25 412                          | 3.0                                              |      | V <sub>DD</sub> | V              |

|                | CLK Input                 | $V_{\text{ICL}}$ |                                 | 0                                                | **   | 0.8             | V              |

|                | Input pin                 | I <sub>IN1</sub> | $V_{IN} = 0.4 V \sim V_{DD}$    | -10                                              |      | 10              | μA             |

| Input current  | 3rd pin                   | $I_{1N2}$        | $V_{IN} = 0.4V = V_{DD}$        | -10                                              |      | 10              | μA             |

|                | Open drain                | $I_{IN3}$        |                                 | -150                                             |      | 10              | μΑ             |

|                | "H" output pin            | V <sub>OH</sub>  | $I_{\text{OH}} = -400 \mu A$    | 2.4                                              |      | V <sub>DD</sub> | V              |

| Output voltage | "L" 3rd pin               | Vol              | I <sub>OL</sub> =2mA            | 0                                                |      | 0.45            | V              |

|                | "L" open drain            | Volod            | $I_{OL}=2mA$                    | 0                                                |      | 0.45            | V              |

| Input capa     | citance                   | Ст               | f=1MHz, V <sub>offset</sub> =2V |                                                  | 5    |                 | <sub>P</sub> F |

| Output cap     | pacitance                 | Co               | f=1MHz, V <sub>offset</sub> =2V |                                                  | 10   |                 | ₽F             |

## ● AC Characteristics (V<sub>DD</sub>=5V±5%, V<sub>SS</sub>=0V, Ta=0 to 70°C)

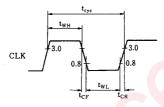

#### 1. Operating Conditions

| Input clock cycle  Clock "H" level pulse width  Clock "L" level pulse width  Clock fall time | t <sub>cyc</sub> twh twL tcF |                                          | 62.5<br>15 |           | 1000  | ns       |

|----------------------------------------------------------------------------------------------|------------------------------|------------------------------------------|------------|-----------|-------|----------|

| Clock "L" level pulse width                                                                  | twL                          |                                          | 15         |           |       |          |

|                                                                                              |                              |                                          |            |           |       | ns       |

| Clock fall time                                                                              | tcr                          |                                          | 15         |           |       | ns       |

| Clock fall time                                                                              |                              |                                          |            |           | 10    | ns       |

| Clock rise time                                                                              | tcr                          |                                          |            |           | 10    | ns       |

| DS \ DAK \                                                                                   | t <sub>A</sub>               |                                          | 0          |           |       | ns       |

| DAK fall time                                                                                | t₃                           |                                          |            |           | 30    | ns       |

| DS / ~ DAK /                                                                                 | tc                           |                                          | 0          |           | .0,.  | ns       |

| DAK \ rise time                                                                              | t₀                           |                                          |            | 40        | 30    | ns       |

| Data delay time from DAK                                                                     | t <sub>E</sub>               | At read cycle time                       |            | S)        | 50    | ns       |

| Data hold time to DAK                                                                        | t <sub>F</sub>               | At ready cycle time                      | 0          | 76        |       | ns       |

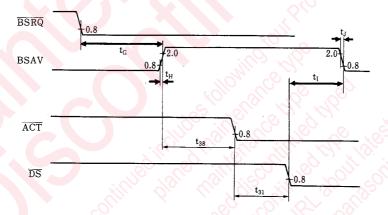

| BSRQ\~BSAV\                                                                                  | t <sub>G</sub>               |                                          | 0          |           |       | ns       |

| BSAV rise time                                                                               | t <sub>H</sub>               |                                          | 1:10       |           | 30    | ns       |

| DS ~~BSAV ~                                                                                  | tı                           |                                          | 0          |           |       | ns       |

| BSAV fall time                                                                               | t <sub>J</sub>               |                                          |            | 30        | ns    |          |

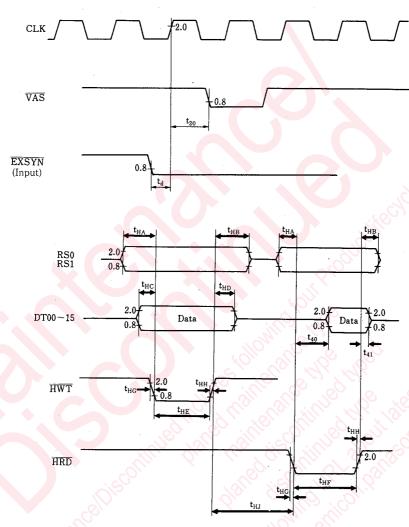

| Setup time to CLK                                                                            | ta                           |                                          | 40         |           |       | ns       |

| Hold time to CLK                                                                             | t <sub>b</sub>               |                                          | 3          |           |       | ns       |

| Setup time to CLK                                                                            | t <sub>c</sub>               | (0),                                     | 30         |           |       | ns       |

| Setup time to CLK                                                                            | t <sub>d</sub>               |                                          | 30         |           | ns    | <u> </u> |

| RS0, RS1, setup time to HWT, HRD                                                             | t <sub>HA</sub>              | illis Ab                                 | 20         |           | į,    | ns       |

| RS0, RS1 hold time to HWT, HRD                                                               | tнв                          | 107, 08                                  | 20         |           |       | ns       |

| Data setup time to HWT                                                                       | t <sub>HC</sub>              | 2 00, 115, 109                           | 20         |           |       | ns       |

| Data hold time to HWT                                                                        | t <sub>HD</sub>              | 10, 10, 10, 10, 10, 10, 10, 10, 10, 10,  | 20         | (1)       | 2     | ns       |

| HWT pulse width                                                                              | t <sub>HE</sub>              |                                          | 250        | <i>``</i> | 000   | ns       |

| HRD pulse width                                                                              | t <sub>HF</sub>              | 10 10 10 11 11 11 11 11 11 11 11 11 11 1 | 250        | 200       | 7:1/2 | ns       |

| HWT, HRD fall time                                                                           | t <sub>HG</sub>              | Y 11, 9, 18, -01, 4,5                    | 1/1/0      | 30        | ns    |          |

| HWT, HRD rise time                                                                           | t <sub>HH</sub>              | 182 316 3111 CO. 182                     | 99,        | 30        | ns    |          |

| Timer from HWT ✓ to HRD ✓                                                                    | t <sub>HJ</sub>              | 10 40 415 Hay                            | 200        | ۲         |       | ns       |

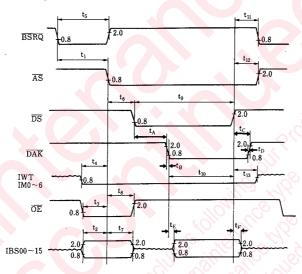

## 2. Operation Characteristics (tcyc=83.3ns (12MHz))

| Item                                             | Symbol          | Condition          | min. | typ. | max. | Unit |

|--------------------------------------------------|-----------------|--------------------|------|------|------|------|

| BSRQ \through AS                                 | t <sub>1</sub>  | BSAV fixed at "H"  | 130  |      | 190  | ns   |

| Address setup time to AS                         | t <sub>2</sub>  | , MO 60,           | 50   |      | 100  | ns   |

| $\overline{OE} \sim \overline{AS} \sim$          | t <sub>3</sub>  | 1 10 11 11         | 60   |      | 100  | ns   |

| IWT, IM0-6 preceding time to $\overline{\rm AS}$ | t <sub>4</sub>  | is with            | 60   |      | 100  | ns   |

| BSRQ pulse width                                 | t <sub>5</sub>  | BSAV fixed at "H"  | 130  |      | 190  | ns   |

| ĀS √~DS √                                        | t <sub>6</sub>  | 12 HIS.            | 70   |      | 100  | ns   |

| Address hold time to AS                          | t <sub>7</sub>  | 0/62               | 70   | L    | 120  | ns   |

| ĀS <u></u> ∼ŌE ✓                                 | t <sub>8</sub>  | At read cycle time | 70   |      | 100  | ns   |

| DS pulse width                                   | t <sub>9</sub>  | DAK fixed at "L"   | 270  |      | 400  | ns   |

| DAK\~DS \                                        | t10             |                    | 200  |      | 500  | ns   |

| DS / through next BSRQ \                         | t11             |                    | 70   |      |      | ns   |

| DS x~AS x                                        | t <sub>i2</sub> |                    | 70   |      | 100  | ns   |

## 2. Operation Characteristics (tcyc=83.3 ns (12MHz) (Continued) )

| Item                                        | Symbol          | Condition                             | min.  | typ. | max.  | Unit |

|---------------------------------------------|-----------------|---------------------------------------|-------|------|-------|------|

| IWT, IM0-6 hols time to $\overline{\rm DS}$ | t13             |                                       | 70    |      | 110   | ns   |

| DS /~ OE /                                  | t <sub>14</sub> | At write cycle time                   | 70    |      | 110   | ns   |

| Data hold time to DS                        | t <sub>15</sub> |                                       | 70    | 1    |       | ns   |

| AS > through data send                      | t <sub>16</sub> | At write cycle                        | - 80  |      | 130   | ns   |

| BSAV   through AS                           | t <sub>17</sub> |                                       | 130   |      | 400   | ns   |

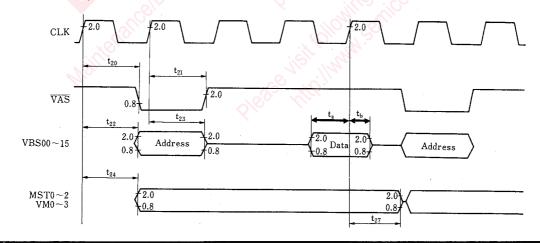

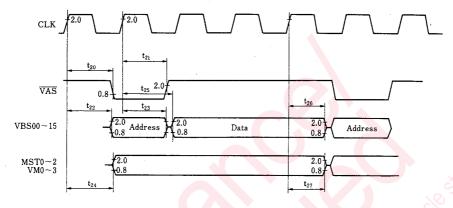

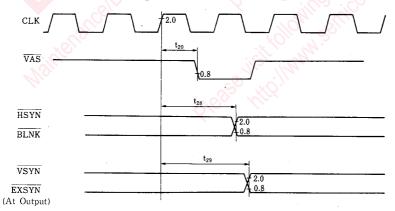

| CLK / throgh VAS                            | t <sub>20</sub> |                                       | 15    |      | - 50  | ns   |

| Next CLK / through VAS /                    | t <sub>21</sub> |                                       | 15    |      | 50    | ns   |

| CLK / throgh address output                 | t <sub>22</sub> |                                       | 20    |      | 70    | ns   |

| Next CLK through address output stop        | t <sub>23</sub> |                                       | 22    |      | 70    | ns   |

| CLK through MS0-2, VM0-3 send               | t <sub>24</sub> |                                       | 20    | 2    | 70    | ns   |

| Next CLK _ through data output              | t <sub>25</sub> |                                       | 22    | 10   | 70    | ns   |

| CLK _fthrough data stop                     | t <sub>26</sub> |                                       | 22    | 10,  | 70    | ns   |

| CLKthrough MST0-2, VM0-3 stop               | t <sub>27</sub> |                                       | 15    | 2,3  | 70    | ns   |

| CLK / through HSYN, BLNK output/stop        | t <sub>28</sub> |                                       | 7 /// |      | 100   | ns   |

| CLK through VSYN, EXSYN output/stop         | t <sub>29</sub> |                                       | 7     |      | 150ns |      |

| BSRQ\~ACT\                                  | t <sub>30</sub> | BSAV fixed at "H"                     | 70    |      | 110   | ns   |

| ACT ~ DS ~                                  | t <sub>31</sub> |                                       | 130   |      | 190   | ns   |

| Address setup time to DS                    | t <sub>32</sub> |                                       | 110   |      | 190   | ns   |

| IWT, IM0−6 setup time to DS                 | t <sub>33</sub> | 100                                   | 130   |      | 190   | ns   |

| Data setup time to DS                       | t <sub>34</sub> | At write cycle time                   | 110   |      | 190   | ns   |

| DS / through ACT /                          | t <sub>35</sub> |                                       | 70    |      | 100   | ns   |

| Address hold time to DS                     | t <sub>36</sub> | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 70    |      | 100   | ns   |

| Data hold time to DS                        | t <sub>37</sub> | 6, 40, 416 11                         | 70    | 3    | 100   | ns   |

| BSAV / through ACT                          | t <sub>38</sub> | - 762. 770. CO. Y.                    | 70    | 1111 | 300   | ns   |

| Read access time                            | t <sub>40</sub> | At read cycle time                    | S     | (0)  | 150   | ns   |

| Data hold time                              | t <sub>41</sub> | At read cycle time                    | 5     | 5.   | 3     | ns   |

## 3. Operation Characteristics (tcyc=62.5ns (16MHz))

| Item                                    | Symbol          | Condition          | min. | typ. | max. | Unit |

|-----------------------------------------|-----------------|--------------------|------|------|------|------|

| BSRQ \ through \ \AS \ \                | $t_1$           | BSAV fixed at "H"  | 100  |      | 150  | ns   |

| Address setup time to AS                | $t_2$           | 10, 91, -0         | 30   |      | 70   | ns   |

| OE <i>₹</i> ~AS <i>₹</i>                | t <sub>3</sub>  | k illis ilo        | 40   |      | 75   | ns   |

| IWT, IM0−6 preceding time to AS         | t <sub>4</sub>  | 1101 011           | 40   |      | 75   | ns   |

| BSRQ pulse width                        | t <sub>5</sub>  | BSAV fixed at "H"  | 100  |      | 150  | ns   |

| $\overline{AS} \sim \overline{DS} \sim$ | t <sub>6</sub>  | The Size           | 40   |      | 75   | ns   |

| Address hold time to $\overline{AS}$    | t <sub>7</sub>  | 1/2 //1/4          | 40   |      | 100  | ns   |

| AS ∼OE ✓                                | t <sub>8</sub>  | At read cycle time | 40   |      | 80   | ns   |

| DS pulse width                          | t <sub>9</sub>  | DAK fixed at "L"   | 200  |      | 300  | ns   |

| DAK ∼ DS ✓                              | t <sub>10</sub> | Q.                 | 150  |      | 400  | ns   |

| DS / through next BSRQ \                | t11             |                    | 40   |      |      | ns   |

**Panasonic**

### 3. Operation Characteristics (tcyc=62.5ns (16MHz) (Continued))

| Item .                                      | Symbol            | Condition           | min. | typ.   | max.  | Unit |

|---------------------------------------------|-------------------|---------------------|------|--------|-------|------|

| DS /~ AS /                                  | t <sub>12</sub> . |                     | 40   |        | 75    | ns   |

| IWT, IM0-6 hold time to $\overline{\rm DS}$ | t13               |                     | 40   |        | 80    | ns   |

| DS /~OE /                                   | t <sub>14</sub>   | At write cycle time | 40   |        | 80    | ns   |

| Data hold time to DS                        | t <sub>15</sub>   |                     | 40   |        |       | ns   |

| AS \ through data send                      | t <sub>16</sub>   | At write cycle time | 60   |        | 110   | ns   |

| BSAV / through AS \                         | t <sub>17</sub>   |                     | 100  |        | 300   | ns   |

| CLK / through VAS                           | t <sub>20</sub>   |                     | 15   |        | 50    | ns   |

| NextCLK / through VAS /                     | t <sub>21</sub>   |                     | 15   |        | 50    | ns   |

| CLK through address output                  | t <sub>22</sub>   |                     | 20   |        | 70    | ns   |

| Next CLK through address output time        | t <sub>23</sub>   |                     | 22   |        | 70    | ns   |

| CLK / through MST0-2, VM0-3 stop            | t <sub>24</sub>   |                     | 20   | S      | 70    | ns   |

| Next CLK / through data stop                | t <sub>25</sub>   |                     | 22   | 10     | 70    | ns   |

| CLK / through data stop                     | t <sub>26</sub>   |                     | 22   | 9      | 70    | ns   |

| CLK/MST0-2,VM0-3stop                        | t <sub>27</sub>   |                     | 15   | •      | 70    | ns   |

| CLK through HSYN, BLNK output/stop          | t <sub>28</sub>   |                     |      |        | 100   | ns   |

| CLK through VSYN, EXSYN output/stop         | t <sub>29</sub>   |                     | 7    |        | 150   | ns   |

| BSRQ \~ACT \                                | t <sub>30</sub>   | BSAV = fixed at "H" | 40   | -      | 75    | ns   |

| ACT ~DS ~                                   | t <sub>31</sub>   |                     | 100  |        | 150   | ns   |

| Address setup time to DS                    | t <sub>32</sub>   |                     | 90   |        | 150ns |      |

| IWT, IM0−6 setup time to DS                 | t <sub>33</sub>   |                     | 100  |        | 150   | ns   |

| Data setup time to DS                       | t <sub>34</sub>   | At write cycle time | 90   |        | 150   | ns   |

| DS / through ACT /                          | t <sub>35</sub>   | 10/11/68            | 40   |        | 75    | ns   |

| Addres hold time to DS                      | t <sub>36</sub>   |                     | 40   |        | 75    | ns   |

| Data hold time to DS                        | t <sub>37</sub>   | J 5 60 11 11        | 40   | 1      | 75    | ns   |

| BSAV / through ACT                          | t <sub>38</sub>   | 190 190 180 190     | 40   | J. III | 230   | ns   |

| Read access time                            | t <sub>40</sub>   | At read cycle time  | 50 X | 37° 0  | 150   | ns   |

| Data hold time                              | t <sub>41</sub>   | At read cycle time  | 5    |        | )     | ns   |

## • AC Characteristics Measuring Load

## ■ Pin Descriptions(MAX Mode)

| Pin No.         | Symbol                | I/O | Description                                                                                                                                                                                                                                                         |

|-----------------|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>79~83 | IM5<br>IM6<br>IM0~IM4 | 0   | Upper 7bits of the image memory address (lower 16bits are sent in a time sharing manner through IBS00-IBS15.                                                                                                                                                        |

| 3~18            | IBS00~IBS15           | I/O | Pins to serve as data transfer routes between the inside of the DPU and the image memory. Data infromation and address infromation is inputted/outputted synchronously with DS and AS, respectively. IBS00 is the MSB.                                              |

| 19~34           | DT00~DT15             | I/O | Pins to serve as communication routes for command parameters and read data between the DPU and host processor                                                                                                                                                       |

| 35<br>36        | RSI<br>RS0            | I   | Pins to select communication registers inside the DPU                                                                                                                                                                                                               |

| 37              | HRD                   | I   | Pin to specify a transfer direction at DT00-DT15.                                                                                                                                                                                                                   |

| 38              | HWT                   | I   | Pin to specify a transfer direction at DT00-DT15. Write data for DT00-DT15 is latched at a rear edge.                                                                                                                                                               |

| 39              | ĪRQ                   | 0   | Interrupt request signal due to a factor caused inside the DPU. It is outputted as far as there exists an interrupt factor.                                                                                                                                         |

| 40              | MAX/MIN               | I   | MAX/MIN mode switching input. MAX mode at "H" level input time, and MIN mode at "L" level input                                                                                                                                                                     |

| 41              | RST                   | I   | Reset input pin                                                                                                                                                                                                                                                     |

| 42              | V <sub>ss</sub>       | _   | GND                                                                                                                                                                                                                                                                 |

| 43              | BLNK                  | 0   | Blanking control signal output pin to the CRT unit                                                                                                                                                                                                                  |

| 44              | HSYN                  | 0   | Horizontal sync. signal output pin to the CRT unit                                                                                                                                                                                                                  |

| 45              | VSYN                  | I/O | Vertical sync. signal output pin to the CRT unit                                                                                                                                                                                                                    |

| 46              | EXSYN                 | I/O | Functions as an output pin when the DPU is placed in the master mode, and as an input pin when placed in the slave mode. In the master mode, it outputs the VSYNC signal at non-interlace time, and only the VYNC signal for an odd-number field at interlace time. |

| 47              | CLK                   | I   | Clock input pin to the DPU. Clock with one fourth cycle of a basic video memory cycle                                                                                                                                                                               |

| 48~50           | MST2~MST0             | 0   | Cycle status signal to the video memory. Outputted synchronously with VAS.                                                                                                                                                                                          |

| 51              | VAS                   | 0   | Sync. signal to access the video memory. always outputted at 4 clocks a cycle. Used to synchronize the peripheral circuit, which control the video memory, and a DPU operation timing.                                                                              |

| 52              | BSAV                  | I   | Response signal to the BSRQ signal. Data transfer starts when logic "1" of this signal is detected after sending the BSRQ signal.                                                                                                                                   |

| 53              | BSRQ                  | 0   | Bus use right request signal outputted prior to data transfer                                                                                                                                                                                                       |

| 54              | DAK                   | I   | Response signal to DA outputted from the DPU. Used as an image memory data latch check signal at data send time, and used to inform the DPU at data input time that data infromation to be inputted has been set on the bus.                                        |

## ■ Pin Descriptions(MAX Mode) (Continued)

| Pin No. | Symbol      | I/O | Description                                                                                                                                                                                                                                                       |

|---------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55      | DS          | O   | Data information I/O sync. signal. Logic "1" one clock after the AS signal is sent. At data send time, data is sent to BS00-BS14 simultaneously when this signal is set to logic "1", and after this signal is set to logic "0", data send stops one clock later. |

| 56      | ĀS          | 0   | Control signal to indicate a timing for the DPU to send the lower 16bits of the image memory address to BS00-BS15.                                                                                                                                                |

| 57      | TWI         | 0   | Control pin for the DPU to infrom the image memory of a transfer direction. When this signal is of logic "0", it indicates a transfer from the DPU to the image memory.                                                                                           |

| 58      | ŌĒ          | 0   | Data transfer control pin for IBS00-IBS15. Set to logic "1" at the timing from the DPU to send address information or write data information.                                                                                                                     |

| 59~62   | VM0~VM3     | O   | Upper 4-bit adress pins to access the video memory. Sent when the DPU accesses the video memory. VMO is the MSB.                                                                                                                                                  |

| 63~78   | VBS00~VBS15 | Ì/O | Pins to serve as data transfer routes between the inside of the DPU and image memory. Address information is outputted synchronously with the VAS signal. VBS00 is the MSB.                                                                                       |

| 84      | $V_{DD}$    | _   | +5V power connection pin                                                                                                                                                                                                                                          |

The image bus and host bus in the MAX mode are put in one channel as for a pin configuration in the MIN mode.

|                             | MAX Mode    | MIN Mode    | ilo,                     |

|-----------------------------|-------------|-------------|--------------------------|

| Image Bus ←                 | IBS00~IBS15 | ADR00~ADR15 | Image Memory Address Bus |

| (Address Data Time Sharing) | DT00~DT15   | BS00~BS15   | Host Image Bus           |

| Host Bus                    | ĀS          | So illo     | 2,, 11, 10,              |

| Address Sync. Signal        | ŌĒ          | ACT         | 10 40° 011               |

## ■ Pin Descriptions(MIN Mode)

| Pin No. | Symbol      | I/O | Description                                                                                                                                                     |

|---------|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 58      | ACT         | 0   | Control signal to indicate that the DPU occupies the image bus (host bus) and executes a bus transfer cycle.                                                    |

| 3~18    | ADR00~ADR15 | 0   | The lower 15bits of the image (or host) memory address are sent synchronously with the ACT signal.                                                              |

| 19~34   | BS00~BS15   | I/O | Bus to serve as a command/parameter communication route between the DPU and host processor, and an information transfer route between the image memory and DPU. |

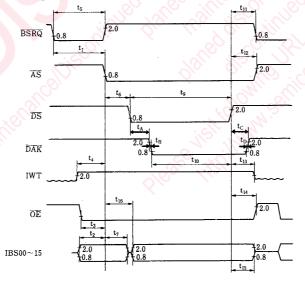

#### ■ Timing Diagrams

●External Clock Input Timing

● Image Memory Read Timing (MAX Mode)

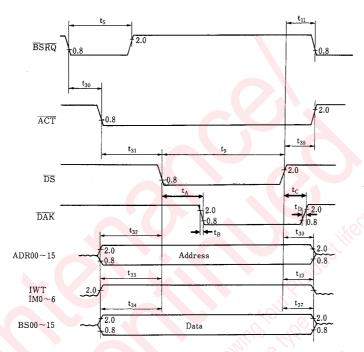

● Image Memory Write Timing (MAX Mode)

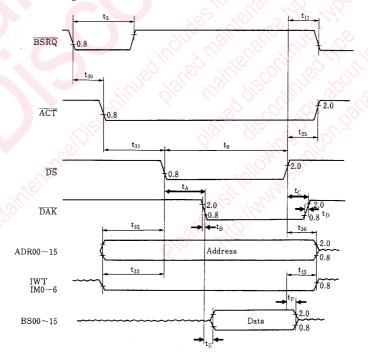

$\bullet \, \mathsf{Image} \,\, \mathsf{Memory} \,\, \mathsf{Write} \,\, \mathsf{Timing} \,\, (\mathsf{MIN} \,\, \mathsf{Mode})$

#### ● Image Memory Read Timing (MIN Mode)

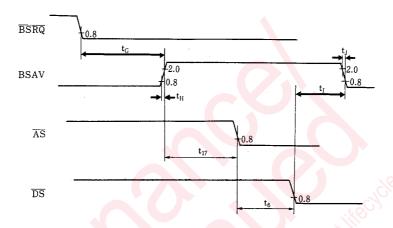

#### ●BSRQ, BSAV Timing

(MAX Mode)

(MIN Mode)

#### Video Memory Read Timing

#### ● Video Memory Write Timing

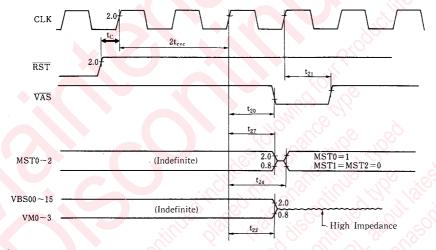

#### • RST Signal and VM Interface

Indefinite means the state where electrical high/low level or high impedance cannot be prescribed.

#### HSYN, BLNK, VSYN Signal Timing

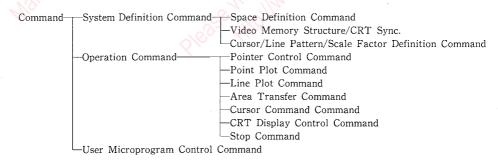

## **■ DPU Command System**

#### System Configuration

#### Specifications

| Item                  | Description                      |                                       |  |  |

|-----------------------|----------------------------------|---------------------------------------|--|--|

| Package               |                                  | 84-pin flat package                   |  |  |

| Process               |                                  | 2μm, CMOS                             |  |  |

| Integration           |                                  | Approx. 85,000 elements               |  |  |

| Max. clock            |                                  | 16MHz                                 |  |  |

| Moment anale          | Video memory                     | 250ns (max.)*3) (Sync. system)        |  |  |

| Memory cycle          | Image memory                     | 500ns (max.)*3) (async. system)       |  |  |

| Bus width             | 16bits                           | s/word for both internal and external |  |  |

| Momorus anaga         | Video memory                     | 1M words*1)                           |  |  |

| Memory space          | Image memory                     | 8M words                              |  |  |

| No. of display pixels | illi Q                           | Max. 4,096×4,096 dots                 |  |  |

|                       | Speed                            | 500ns/word*3)                         |  |  |

| Transfer control      | Scale factor                     | $1/n \sim n \ (n=1 \sim 16)$          |  |  |

| Transfer Control      | Min. unit                        | 1 dot                                 |  |  |

|                       | Raster operation                 | 8 kinds of operations                 |  |  |

| CRT control           | Scan mode                        | 3 kinds                               |  |  |

| CKI control           | External sync.                   | Enabled (VSYN signal)                 |  |  |

| Cursor control        | Optionally shaped (255×255 dots) |                                       |  |  |

| Cursor collitor       | cursor mask controllable         |                                       |  |  |

| Graphic               | Poi                              | int draw (direct/relative address)*2) |  |  |

| Graphic               | H                                | orizontal/vertical segment draw*2)    |  |  |

<sup>\*1)</sup> Cursor working area included

\*2) Line pattern register designation

\*3) At maximum clock (16MHz)

## ■ Commands List

| Group                     |                                         | Mnemonic |            |          |     |                     | In                                           | ıstr     | ucti       | on (      | ode a         | nd I            | ara | met      | er       |               |     |                | V 00 1 1 00 |  |  |  |  |

|---------------------------|-----------------------------------------|----------|------------|----------|-----|---------------------|----------------------------------------------|----------|------------|-----------|---------------|-----------------|-----|----------|----------|---------------|-----|----------------|-------------|--|--|--|--|

|                           | Space definition                        | DFSRCS   | 0          | 1        | 0   | 1                   |                                              |          | 0          | 0         | 0             | 0               | V   |          |          |               |     |                |             |  |  |  |  |

|                           | command                                 |          |            |          |     |                     | ,                                            |          |            |           | SWD           | Γ               | •   |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          |            |          |     |                     |                                              |          | `          | +         |               |                 |     |          | SC       | RGI           | I   |                |             |  |  |  |  |

|                           |                                         |          | SORGL      |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         | DFDSTS   | 0          | 1        | 0   | 1                   | 1                                            |          | 0          | 1         | 0 (           |                 | )   | 0        | 0        | 0             | 0   | 0              | V           |  |  |  |  |

|                           |                                         |          |            |          |     |                     |                                              | $\leq$   |            |           | DWD'          | Γ               |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          |            |          |     |                     |                                              |          | _          |           |               |                 |     |          | DC       | RGI           | I   |                |             |  |  |  |  |

|                           | 777.1                                   |          |            |          |     |                     |                                              |          |            |           | OORG          |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           | Video memory structure/CRT sync. timing | SYNC     |            | 0        | 1 1 |                     | )                                            | 0        | 0          | 0         | 0             | 0               | 0   | 0        | 0        | 0             | 2.0 | 1              | 0           |  |  |  |  |

|                           | definition command                      |          | <u></u>    | 7        |     |                     | _                                            |          |            |           | HFP           |                 |     |          |          | 20,           | _   |                |             |  |  |  |  |

|                           |                                         |          |            |          | HS  |                     |                                              |          |            |           |               |                 |     |          |          | <u> </u>      |     |                |             |  |  |  |  |

|                           |                                         |          |            |          |     |                     |                                              |          |            |           | HBP           |                 |     | _,       | <u>V</u> |               |     |                |             |  |  |  |  |

|                           |                                         |          |            |          |     |                     | _                                            |          |            |           | DPR2          |                 | 4.0 | (2)      |          |               |     |                |             |  |  |  |  |

| Command Definition System |                                         |          |            |          |     |                     | $\rightarrow$                                | -        |            | P         | DPR1          |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          | VS         |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          | VBP        |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          | LPF        |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               |     |                |             |  |  |  |  |

| nitic                     |                                         |          | VFP<br>ATR |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               |     |                |             |  |  |  |  |

| efir                      |                                         |          | NR         |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               |     |                |             |  |  |  |  |

| d D                       |                                         |          |            |          |     |                     |                                              | :(       | 9          |           | PCH           |                 |     |          |          |               |     | _              | <u> </u>    |  |  |  |  |

| nan                       |                                         |          |            |          |     |                     |                                              |          |            |           |               |                 |     |          |          |               | 1   |                |             |  |  |  |  |

| - u                       | Cursor defintion                        | DFCSS    | (          | _        |     | _                   | -                                            | 1        | 1          | 0         | 0             | 0.0             | 0   | 0        | 0        | 0             | -   |                |             |  |  |  |  |

| ပိ                        | command                                 |          |            |          |     | <del>, \</del>      |                                              | 7        | 0          |           | CWD7          | -               |     |          |          | <del>(Ö</del> |     | $\overline{a}$ |             |  |  |  |  |

|                           |                                         |          |            |          | 76  | <u> </u>            | ŽŽ,                                          | 9        | _          | حر        | 6             | <del></del>     |     |          |          | CORGH         |     |                |             |  |  |  |  |

|                           |                                         |          |            | -6       | D.  | ~()                 | _                                            | _0       | 10         | (         | CORG          | L,0             | 0   | 46       | 30       |               | 77. |                |             |  |  |  |  |

|                           |                                         | STCS     | 1          | 0        | ) 0 | 0                   | 0                                            | 1        | 0          | 0         | 0             | 0               | 0   | 0        | 0        | 0             | 0   | (              | )           |  |  |  |  |

|                           |                                         |          | 00         |          | 6   |                     | 0/2                                          |          | ?          |           | $\triangle X$ |                 | 1), |          | 0//      | ,             |     |                |             |  |  |  |  |

|                           |                                         |          |            | 70       |     | $\mathcal{C}_{(0)}$ |                                              | X/C      | 5          | 2/5       | $\triangle Y$ | <sup>9</sup> 0, | ,   | <u> </u> | )        |               |     |                |             |  |  |  |  |

|                           |                                         |          |            | <u> </u> |     |                     | 6                                            | <u> </u> | _          | $U_{P_i}$ | X             |                 | 2   | 0        |          |               |     |                |             |  |  |  |  |

|                           |                                         |          |            |          |     | 0                   | <u>()</u>                                    |          | <u>.C)</u> |           | Y             |                 | 20. |          |          |               |     |                |             |  |  |  |  |

|                           |                                         | STCSM    | 1          | . 0      | 0   | 00                  |                                              | 1        | 0          | 0         | 0             | 0               | 0   | 0        | 0        | 0             | 0   | -              | 1           |  |  |  |  |

|                           |                                         |          |            |          |     | <u> </u>            |                                              |          | -          | 11,       | $\triangle X$ |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          | <u> </u>   |          | ••• |                     |                                              | 7/       | <u>),</u>  | (         | $\triangle Y$ |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           | 10,0                                    |          | -          |          |     |                     | <u>,                                    </u> | 0,       |            | 113       | XM            |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          |            |          |     | 10                  |                                              | ١.,٧     | A P        |           | XY            |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           | Mo.                                     |          | -          |          | ()  | 7/                  |                                              | 117      | 10         |           | XC            |                 |     |          |          |               |     |                |             |  |  |  |  |

|                           |                                         |          |            |          | _6  | J                   | $O_{\mathcal{M}}$                            | )        |            |           | YC            |                 |     |          |          |               |     |                |             |  |  |  |  |

# ■ Commands List (Continued)

| Group                      | Command              | Mnemonic          | T                           |          |               |     | Ins                    | truc | tion        | Code | e and            | Par   | ame | ter       |    |                |          |          |  |  |

|----------------------------|----------------------|-------------------|-----------------------------|----------|---------------|-----|------------------------|------|-------------|------|------------------|-------|-----|-----------|----|----------------|----------|----------|--|--|

|                            | Scale factor         | STZM              | 0                           | 1        | 0             | 1   | 0                      | 0    | 1           | _1   | 0                | 0     | 0_  | 0         | 0  | 0              | 0        | 0        |  |  |

| System definition command. | definition command   |                   | MX                          |          |               |     |                        |      | ZX          |      | MY               |       |     |           |    |                | ZY       |          |  |  |

|                            | Line pattern defini- | STPTR             | 0                           | 1        | 0             | 1   | 0                      | 0    | 0           | 1    | 0                | 0     | 0   | 0         | 0  | 0              | 0        | 0        |  |  |

|                            | tion command         |                   |                             |          |               |     |                        |      |             | DA   | ТА               |       |     |           |    |                |          |          |  |  |

|                            | Pointer control      | STSRCP            | 0                           | 1        | 0             | 1   | 0                      | 1    | 1           | 0    | 0                | 0     | 0   | 0         | 0  | 0              | 0        | R        |  |  |

|                            | command              |                   |                             |          |               |     |                        |      |             |      | $\triangle X$    |       |     |           |    |                |          |          |  |  |

|                            |                      |                   |                             |          |               |     |                        |      |             | _Y/  | $\triangle Y$    |       |     |           |    |                |          |          |  |  |

|                            |                      | STDSTP            | 0                           | 1        | 0             | 1   | 0                      | 1    | 1           | 1    | 0                | 0     | 0_  | 0         | 0  | 0              | 0        | R        |  |  |

|                            |                      |                   |                             |          |               |     |                        |      |             |      | $\triangle X$    |       |     |           |    | <del>-</del> - |          |          |  |  |

|                            |                      |                   |                             |          |               |     |                        |      |             |      | ΔY               |       |     |           | 20 | _              |          |          |  |  |

|                            |                      | FXSRCP            | 0                           | 1        | 0             | 1_  | 0                      | 1    | 0           | 0    | 0                | 0     | 0   | 0         | 0  | 0              | 0        | 0        |  |  |

| 77                         |                      |                   |                             |          |               |     |                        |      |             |      |                  |       | P.  | PADRH     |    |                |          |          |  |  |

|                            |                      |                   |                             |          |               |     | _                      |      |             |      | DRL              |       | 1   | <u>J'</u> |    |                |          |          |  |  |

|                            |                      | FXDSTP            | 0                           | 1        | 0             | 11  | 0                      | 1    | 0           | 1    | 0                | 0     | 0   | 0         | 0  | 0              | 0        | 0        |  |  |

| ıanı                       |                      |                   | PADRI                       |          |               |     |                        |      |             |      |                  |       |     |           |    |                |          |          |  |  |

| mm                         |                      | PADRL             |                             |          |               |     |                        |      |             |      |                  |       |     |           |    | DOI            |          | D        |  |  |

| Operation Command          | Point plot           | RSET              | 0                           | 0        | 0             | 0   | 0_                     | 0    | PT          |      | 0                | 0     | 0   | 0         |    | ROI            | <u>.</u> | R        |  |  |

| lon                        | command              |                   | X/ $\triangle$ X            |          |               |     |                        |      |             |      |                  |       |     |           |    |                |          |          |  |  |

| rati                       |                      |                   |                             |          |               |     |                        | _    |             |      | ΔY               |       |     |           |    | DO1            |          | 0        |  |  |

| )pe                        |                      | PSETS             | 0                           | 0        |               |     | ID_                    | -0   | PT          | -    | 0                | 0     | 0   | 0         |    | ROI            |          | 0        |  |  |

| Ç                          | Line plot            | HLINE             | 0                           | 1        | 0             | 0_  | 0                      | 1    | 0           | D    | 0                | 0     | 0   | 0         |    | RO             |          |          |  |  |

|                            | command              |                   |                             |          |               | - 1 | $\partial_{J_{J_{s}}}$ |      | <u>_(V)</u> |      | \X_              | 0     |     |           |    | DO             |          | T 0      |  |  |

|                            |                      | VLINE             | 0                           | 1        | 0             | 0   | 0                      | 1    | 1           | D    | 0                | 0     | 0   | 0         | 3  | RO             |          | 10_      |  |  |

|                            |                      |                   |                             |          | \C:           |     | 1 6                    | Τ.   |             |      | 2 Y              | T - D | IR  | В         |    | RO             | <u> </u> | 0        |  |  |

|                            | Area transfer        | MV                | 1                           | 0        | 0             | 1.  | Z                      | 0    | <u>00</u>   | 0    | 0                | L     | IK  | D         |    | KO.            | F        | 10       |  |  |

|                            | command              |                   | $\triangle X$ $\triangle Y$ |          |               |     |                        |      |             |      |                  |       |     |           |    |                |          |          |  |  |

|                            |                      |                   |                             |          |               |     |                        | -    | 3.5         |      | 0                | 0     | 0   | 0         |    | RO             | D        | 0        |  |  |

|                            | Cursor control       | STRTCS            | 1                           | 1        | 0             | 10  | 0                      | 40   | M           | 7/6  | $\frac{1}{X}$    | U     | U   | 0-        | _  | KO.            | L        |          |  |  |

|                            | command              | Piji              | ×   - 6                     | 7.0.     | -4            | 00. | <del>- \</del>         | 12   | 11          |      | Y                |       | 75  |           |    |                |          |          |  |  |

|                            | ) · Y                |                   | -                           | <u> </u> |               |     | <u>_</u>               |      | 3.4         | . (2 | 1 0              | 0     | 0   | 0         | 1  | RO             | D        | R        |  |  |

|                            |                      | MVCS              | 1                           | 1        | 1             | 1   | 0                      | 6    | M           | 77   | 10               | 50    | U   | U         |    | KO             | т        | <u> </u> |  |  |

|                            |                      | X/\(\triangle X\) |                             |          | <del>-0</del> | O.  |                        | ),   | <u> </u>    | )    | <del>-0)</del> - |       |     |           | -  |                |          |          |  |  |

|                            |                      | Y/\Delta Y        |                             |          |               |     |                        |      |             |      | 0                | 0     | 0   | 0         | 0  |                | 0        | 0        |  |  |

|                            |                      | STPCS             | 1                           | 1        | 1             | 0   | 0                      | 0    | 0           | 0    | U                | U     | U   | U         | U  | U              | U        | U        |  |  |

#### ■ Commands List (Continued)

| Group                                | Command                   | Mnemonic | Instruction Code and Parameter |     |   |   |   |     |     |     |     |     |     |    |     |    |       |   |  |  |  |

|--------------------------------------|---------------------------|----------|--------------------------------|-----|---|---|---|-----|-----|-----|-----|-----|-----|----|-----|----|-------|---|--|--|--|

|                                      | CRT Display               | STDADR   | 0                              | 1   | 0 | 1 | 1 | 1   | 1   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

|                                      | Control Command           |          |                                |     |   |   |   |     |     |     |     |     |     |    |     |    | DADRH |   |  |  |  |

| þ                                    |                           |          |                                |     |   |   |   |     |     | DA  | DRL |     | •   |    |     |    |       |   |  |  |  |

| nan                                  |                           | DSTRT    | 0                              | 1   | 1 | 0 | 1 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 1 |  |  |  |

| Command                              |                           | DSTP     | 0                              | 1   | 1 | 0 | 1 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

| ರ                                    | Parameter Read<br>Command | RDSRCP   | 0                              | 1   | 1 | 1 | 0 | 0   | 1   | 0 - | 0   | 0   | 0   | 0  | 0   | 0  | 0     | С |  |  |  |

| ion                                  |                           | RDDSTP   | 0                              | 1   | 1 | 1 | 0 | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | C |  |  |  |

| Operation                            |                           | RDCSP    | 0                              | 1   | 1 | 1 | 0 | 1   | 1   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

|                                      |                           | RDSRCD   | 0                              | 1   | 1 | 1 | 1 | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0. | 0     | 0 |  |  |  |

|                                      |                           | RDDSTD   | 0                              | 1   | 1 | 1 | 1 | 1   | 1   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

|                                      |                           | RDMD     | 0                              | 1   | 1 | 1 | 1 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

|                                      | Stop Command              | HLT      | 0                              | 1   | 1 | 1 | 1 | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

| _                                    | User microprogram         | LDMP     | 1                              | . 0 | 1 | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

| ran<br>nd                            | control command           |          | IM                             |     |   |   |   |     |     |     |     | ADI | ORH |    |     |    |       |   |  |  |  |

| rog                                  |                           |          |                                |     |   |   |   |     |     | IMA | DRL |     |     |    |     |    |       |   |  |  |  |

| on                                   |                           | SVMP     | 1                              | 0   | 1 | 0 | 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 1 |  |  |  |

| User Microprogram<br>Control Command |                           |          |                                |     |   |   |   |     |     | 01  | 5   |     |     | IM | ADI | RH |       |   |  |  |  |

| Ser                                  |                           |          |                                |     |   |   |   |     |     | IMA | DRS |     |     |    |     |    |       |   |  |  |  |

| 20                                   |                           | EXMP     | 1                              | 0   | 1 | 1 |   | ENT | (0) | 0   | 0   | 0   | 0   | 0  | 0   | 0  | 0     | 0 |  |  |  |

Note) Unused bits in parameters shold be basically Ø.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805