#### 1. Features and Benefits

- CLIP / Caller-ID support

- Line status measuring facilities

- Line event registration

- Lightning safe

- Pre-programming of default settings

- Powered by PSTN line (less than 10 μA power consumption during offline)

- SW programmable for worldwide use

## 2. Applications

- Analog front-end PSTN interfaces

- DECT base stations

- Low / high speed modems

- Payphones

- PBX / Fax

- PC-Voice and mixed voice/data applications

- Remote configuration / E-pay / POS terminals

- Settop boxes

- Utility meter reading

- VOIP converters on POTS (terminal side)

### 3. Ordering information

| Number               | Package Description                                                                                      |

|----------------------|----------------------------------------------------------------------------------------------------------|

| MLX32001EE-SO16WREEL | Plastic small outline package; 16 leads; body width 300 mil Packed per 1500 pcs REEL                     |

| MLX32001EE-SO16WTUBE | Plastic small outline package; 16 leads; body width 300 mil Packed per 22 tubes of 46 pcs / tube = 1012. |

| MLX32001FA-SO16WREEL | Plastic small outline package; 16 leads; body width 300 mil<br>Packed per 1500 pcs REEL                  |

| MLX32001FA-SO16WTUBE | Plastic small outline package; 16 leads; body width 300 mil Packed per 22 tubes of 46 pcs / tube = 1012. |

## 4. Functional Block Diagram

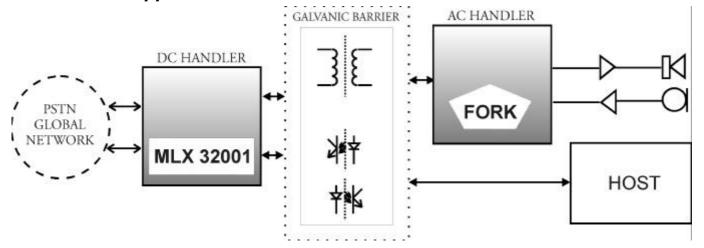

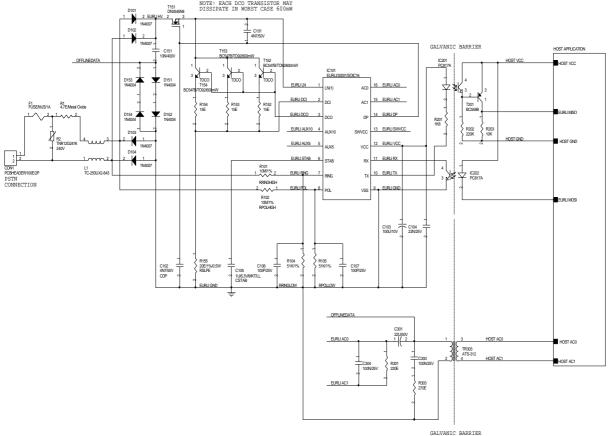

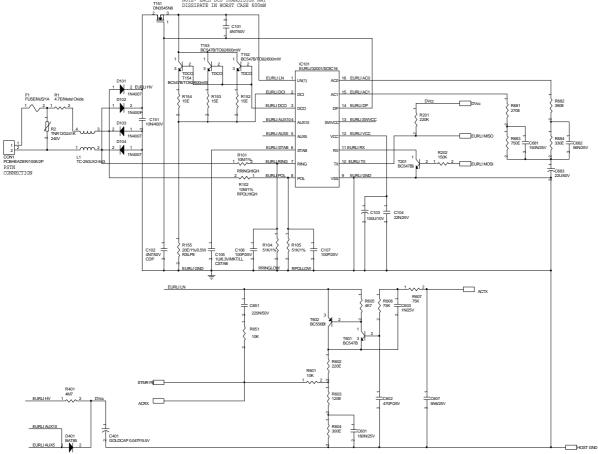

### 4.1 Modem application

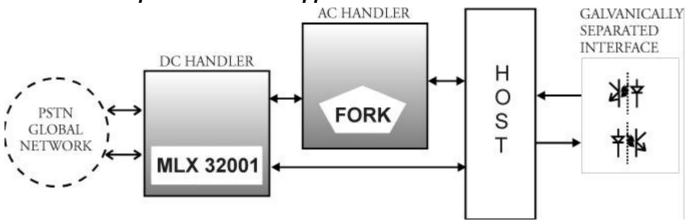

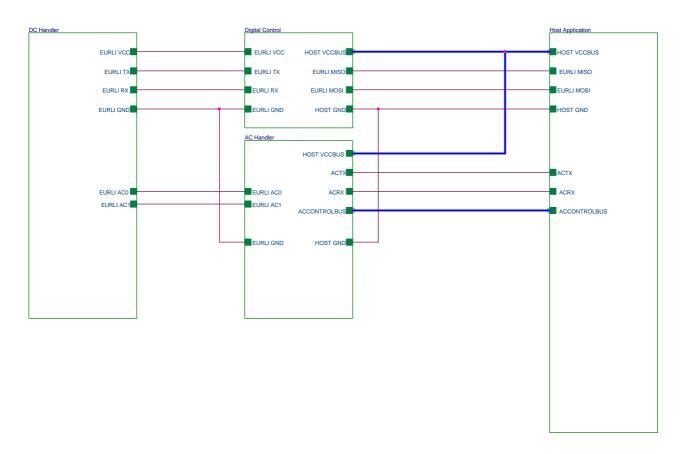

### 4.2 PC-Voice application

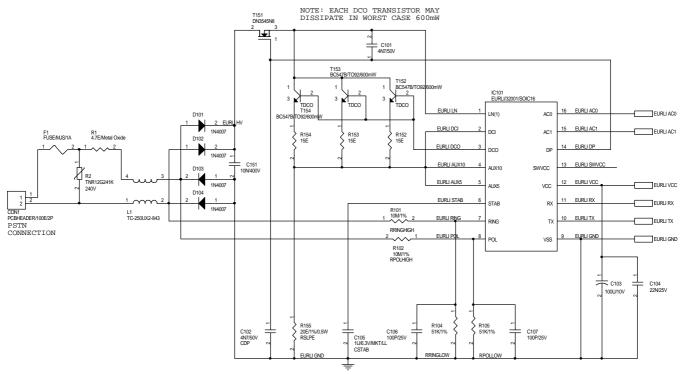

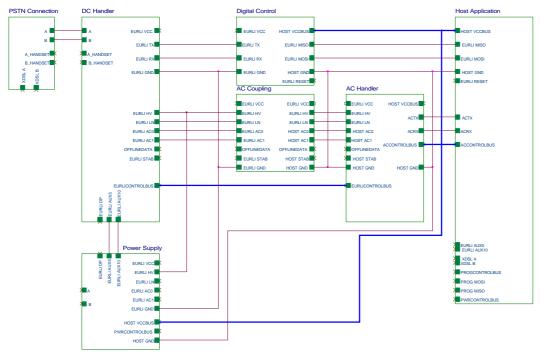

### 4.3 PSTN Line powered modem application

## 5. Description

MLX32001 implements the DC-handler of a universal PSTN Line Interface. It is fully telephone line powered and digital control is performed by a special UART*FLEX*. There is no crystal or resonator linked to MLX32001 and thus the core as well as the UART are capable to adapt themselves to the HOST UART's preferred communication speeds. The synchronisation time of the UART is 2400 bps +/- 25%.

To ensure that long term drift and temperature will not affect communication stability, the communication channel must be synchronised on a frequent basis. If the line conditions get low and MLX32001 has to switch down to 1 of its 4 low power modes, synchronisation locking expires to ensure that power supply dependent communication times will never unlock.

There are 64 bytes (512 bits) of user RAM accessible in MLX32001 to store country and network operator dependent settings. These settings are retrieved from a small parameter database that supports data originating from the following 3 sources:

- 1) <u>Type Approval Regulations</u> that more or less specify the network (e.g. what kind of AC termination is required; what levels of open line voltages, ring voltages and online currents can be expected; how are transient timings for online / offline / CLIP and polarity dependent phenomena specified, what common mode unbalance is required)

- 2) Design and market Experience: Known network errors and network non-compliance problems can be implemented in MLX32001 drivers and state machine to let the line interface properly handle interworking problems (e.g. how much spikes can be expected during polarity reversal; how much time does it take the power supply SLIC to switch between online detect and online supply mode; what total current interruptions can be expected; how much time can pass before an acceptable dialtone is detected)

- 3) <u>Local Line Adaptation</u>: Local line adaptation is defined as the ability to measure the telephone line conditions of the actual network termination point

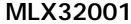

## MLX32001

#### Universal PSTN Line Interface

where MLX32001 is powered and accordingly adapt optimally to that telephone network. This means that MLX32001 is capable of measuring all relevant DC and transient phenomena on a telephone line that characterise this line. Consequently settings can be optimised for (extremely) long line operation, low current operation, parallel operation with 1 or more telephones in parallel, line monitoring (detect line transients, line parallel pickup and replace and total line disconnect).

In a PC controlled environment, parameters and drivers are residing in the PC's memory, while the front end (USB) controller such as the USB Cypress C7Y67001 is performing bitwise control and is handling the UART.

MLX32001 is not only a fully line powered device, it also generates power supply for local hosting microcontrollers. It has 2 different sources of power supply generation: AUX5, AUX10 delivering 5 and 10mA nominally if sufficient line current is available. The AUX5 supply can be programmed in steps of 20 $\mu A$ . This allows the designer to modify the HOST's supply current while exactly regulating the supply voltage with just an internal A/D convertor input on the HOST.

With those features it is possible to built standalone (modem) applications with hosting controllers like NEC UPD78F9177G, Texas Instruments MSP430-series and Hitachi H8-36XX series. These controllers are then fully line powered but still perform powerful functions like full V.22 modem implementation, S0 contact scanning for utility meters, E-data transfer interface for POS and E-cash modules

Any line interface requiring galvanic separation has a line powered PSTN-side and a HOST controller side where primary controlling power is available. With the MLX32001 there is a consistent and dominant separation between AC and DC handling:

- All non-AC handling is regarded as DC handling and is performed by MLX32001 at the PSTN-powered side, including (im)pulse dialing, overshoot control, polarity detection, hookswitch control, ring detection and line event monitoring. For universal line interface designs, the DC handling part is always identical

- All pure AC-handling is performed at the HOST side, as it differs from application to application and depends on AC line transformer choice, the number of reference termination sections and the number of SMTR feedback filter elements.

For worldwide coverage of Balanced Return Loss 2 impedances are needed. If the design specification is limited to 600E terminating countries only 1 is required. The excellent THD and Noise characteristics are the result of the fully line powered operation. Other DAA's transfer power

supply from the HOST to the PSTN side, giving possible problems for lightning safety, radio interference at higher frequencies and frame ground sensitive coupling problems.

The AC-handler part of the design has not been integrated into MLX32001 for 2 major reasons:

- In designs that include a galvanic separation, the DC-handler is on the line powered side, while the AC-handler resides on the HOST powered side. Since MLX32001 supports each possible line transformer, the DC-handler section is identical for all designs, while the AC-handler part depends very much on line transformer selection.

- 2) For galvanically coupled designs the STMR filters used require capacitor values up to 2.2μF. Integrating such high values into silicon will either be expensive or (with some impedance conversion tricks) will result in a Total Harmonic Distortion of the transmitting stage that is higher than the 72dB required by V.90 modems. To allow any design to work with MLX32001 it was decided to build up any appropriate AC-handler by conventional components, thus reaching the best possible THD levels as well as the most cost effective total design setup.

Interworking reliability is the most important aspect of any global line interface. MLX32001 design setup has been done together with a traditional AC-type line transformer for galvanic barrier implementation. This has the following advantages:

- The setup is totally safe for common mode lightning: there are <u>no</u> high voltage capacitors required between the PSTN powered side and the HOST powered side. Since the coupling is inductive, the higher the frequency, the higher the impedance and the lower the coupling currents.

- 2) Proven and reliable electromagnetic coupling technology

- 3) 4kV of separation can be reached supporting global access with 1 transformer

- 4) 2 standard PC-817 opto-couplers are sufficient to pass all MLX32001 digital control signals

Finally, MLX32001 supports full line event monitoring. This means that any line event occurring in online or offline mode will generate an event within MLX32001 where the host decides what to do with it. For modems, this means that other telephones picked up and replaced in parallel can be properly handled without closing down the connection or terminating the download procedures. Also MLX32001 can be linked 'virtually' online. In this mode, MLX32001 based designs never answer incoming calls and never originate calls during line busy states. Also the actual line use versus daytime period is 'monitored' and it is consequently decided what is the best period to make service calls or autodownload configuration data.

## 6. Pin description

| PSTN CONNECTED<br>PINS AT LEFT | HOST CONNECTED<br>PINS AT RIGHT |

|--------------------------------|---------------------------------|

| □ LN ●                         | AC0                             |

| DCI                            | AC1                             |

| DCO                            | DP                              |

| AUX10                          | swcc                            |

| AUX5                           | vcc                             |

| STAB                           | RX                              |

| RING                           | тх                              |

| POL                            | vss                             |

| L                              |                                 |

#### PIN-TYPE DESCRIPTION

| PIN | NAME  | PINTYPE               |

|-----|-------|-----------------------|

|     |       |                       |

| 1   | LN    | ANALOG SIGNAL HV      |

| 2   | DCI   | ANALOG COIL IN        |

| 3   | DCO   | ANALOG COIL OUT       |

| 4   | AUX10 | ANALOG HV             |

| 5   | AUX5  | ANALOG HV             |

| 6   | STAB  | ANALOG COIL REFERENCE |

| 7   | RING  | ANALOG INPUT          |

| 8   | POL   | ANALOG INPUT          |

| 9   | VSS   | GROUND                |

| 10  | TX    | DIG OUTPUT            |

| 11  | RX    | DIG INPUT             |

| 12  | VCC   | POSITIVE POWER SUPPLY |

| 13  | SWVCC | DIG OUTPUT            |

| 14  | DP    | OUTPUT HV             |

| 15  | AC1   | ANALOG SIGNAL HV      |

| 16  | AC0   | ANALOG SIGNAL HV      |

Note HV = high voltage pin

#### Remarks:

- Low voltage signals are on the bottom half. High voltage pins at the upper half.

- RING/POL are grouped together and should be routed together on the pcb.

- LN/DCI are grouped together. The highest possible DC current is flowing through these pins.

- Logic control signals are grouped together (RX, TX).

- AC0/AC1 switches AUX5, AUX10 and DP are as close as possible to LN.

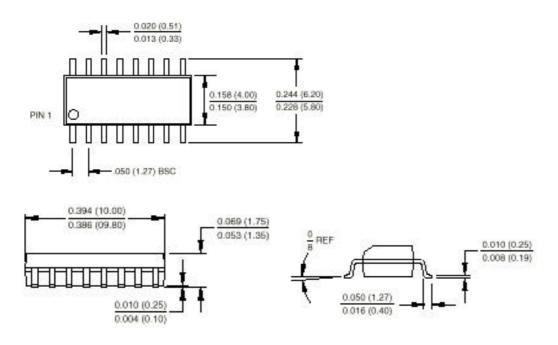

## 7. Package description, dimensions in inches and (millimeters)

## 8. Electrical specifications

Note: All parameters are specified at 20 degrees Celsius and Vcc = 3.3V unless stated otherwise

| VCC positive power supply                                                         | Reference                                           | Min  | Тур | Max                  | Unit |

|-----------------------------------------------------------------------------------|-----------------------------------------------------|------|-----|----------------------|------|

| Operating supply voltage                                                          | V <sub>CC</sub>                                     | 1.8  | 3.3 | 7.2                  | V    |

| Reduced operating area supply voltage (SOS)                                       | $\mathbf{v}_{\mathbf{cc}}$                          | 1.4  | 3.0 | 3.2                  | V    |

| Hysteresis Power-On-Reset circuitry                                               | V <sub>CCHYST</sub>                                 | 0.6  |     | 0.2                  | V    |

| Trysteresis 10 wer on reset enealtry                                              | V CCHYS1                                            | 0.0  |     |                      | •    |

| Operating supply currents into LN:                                                |                                                     |      |     |                      |      |

| OFFLINE standby                                                                   | $I_{LN}$                                            |      | 7   | 15                   | μΑ   |

| OFFLINE during activity detect                                                    | $I_{ m LN}$                                         |      | 70  | 100                  | μΑ   |

| OFFLINE during activity detect in SOS                                             | $I_{ m LN}$                                         |      | 140 | 200                  | μΑ   |

|                                                                                   |                                                     | 4.0  | 4.3 | 4.6                  | •    |

| ONLINE supply in zener area                                                       | I <sub>LN</sub>                                     |      |     |                      | mA   |

| ONLINE supply not in zener area                                                   | $I_{LN}$                                            | 3.1  | 3.3 | 3.5                  | mA   |

| 7371                                                                              |                                                     |      |     |                      |      |

| LN input                                                                          |                                                     |      |     | 10                   |      |

| Voltage range                                                                     | $ m V_{LN}$                                         | -0.6 | 2.2 | 42                   | V    |

| ONLINE current                                                                    | $\mathbf{I}_{	ext{ONL}}$                            | 0.2  | 3.3 | 22.1(*)              | mA   |

| (*) Aux10 and Aux5 active and fully on                                            | 77                                                  | 40   |     |                      |      |

| ONLINE impedance 300-3400Hz DCO off                                               | Z <sub>ONL</sub>                                    | 40   | 400 | 400                  | kΩ   |

| Resistor to C <sub>STAB</sub> for DCO control                                     | RLN <sub>STAB</sub>                                 | 320  | 400 | 480                  | kΩ   |

| Resistor to C <sub>STAB</sub> in DCO start mode                                   | RLN <sub>START</sub>                                | 15   | 21  | 27                   | kΩ   |

| Pin capacitance                                                                   | $C_{LN}$                                            |      | 100 |                      | pF   |

| AC signal distortion in 10010kHz band between either                              | THD                                                 |      |     | -80                  | dB   |

| AC0 and AC1 outputs:                                                              |                                                     |      |     |                      |      |

|                                                                                   |                                                     |      |     |                      |      |

| LN input (FA Version)                                                             |                                                     |      |     |                      |      |

| Noise generation in 3003400 Hz band @ BW = 31Hz                                   | $\mathbf{P}_{\mathbf{NOISE}}$                       |      |     | -87                  | dBm  |

| Relative to a 300E termination                                                    |                                                     |      |     |                      |      |

|                                                                                   |                                                     |      |     |                      |      |

| DCI input                                                                         |                                                     |      |     |                      |      |

| Voltage range                                                                     | $V_{DCI}$                                           | -0.6 |     | V <sub>CC</sub> +0.6 | V    |

| Mute current (V <sub>DCI</sub> =3V)                                               | $\mathbf{I}_{	ext{MUTE}}$                           |      | -50 |                      | mA   |

| Mute offset $(V_{LN} - V_{DCI})$ @ $I_{MUTE} = 50 \text{mA}$                      | $\mathbf{V}_{	ext{MUTE}}$                           |      | 1.0 | 1.5                  | V    |

| Mute offset ( $V_{LN}$ - $V_{DCI}$ ) @ $I_{MUTE} = 10$ mA                         | $\mathbf{V}_{	ext{MUTE}}$                           |      | 0.3 | 0.4                  | V    |

| Input impedance to Ground                                                         | $\mathbf{R}_{\mathbf{DCI}}$                         | 70   | 87  | 105                  | kΩ   |

| Pin capacitance                                                                   | C <sub>DCI</sub>                                    |      | 50  |                      | pF   |

|                                                                                   |                                                     |      |     |                      |      |

| DCO output                                                                        |                                                     |      |     |                      |      |

| Source current ( $\beta_{\text{FEDCO}} >= 50$ , $I_{\text{DC}} = 100 \text{mA}$ ) | $I_{OH}$                                            | 3.5  |     | 7.8                  | mA   |

| Sink current                                                                      | $I_{OL}$                                            |      | 3.0 |                      | mA   |

| Q <sub>DCO</sub> DC current gain                                                  | $\mathbf{Q}_{\mathrm{DCO}}\mathbf{H}_{\mathrm{FE}}$ | 50   |     |                      |      |

| Output impedance from DCO                                                         | $\mathbf{R}_{	ext{DCO}}$                            |      |     | 100                  | Ω    |

| Voltage range                                                                     |                                                     | -0.6 |     | 3.6                  | V    |

| Pin capacitance when DCO disabled                                                 | $C_{DCO}$                                           |      | 50  |                      | pF   |

| Output impedance                                                                  | $\mathbf{Z}_{	exttt{DCO}}$                          |      |     | 100                  | Ω    |

|                                                                                   |                                                     |      |     |                      |      |

| AUX10 output                                                                      |                                                     |      |     |                      |      |

| Auxiliary voltage range                                                           | $V_{AUX10}$                                         | -0.6 |     | 42                   | V    |

| DC Leakage current                                                                | I <sub>AUX10LEAK</sub>                              |      |     | 1                    | μA   |

| Supply current                                                                    | I <sub>AUX10</sub>                                  | 9.5  | 10  | 10.5                 | mA   |

| Input impedance to Ground when disabled                                           | R <sub>AUX10</sub>                                  | 10   |     | 1 7.2                | ΜΩ   |

| Input impedance to LN when enabled                                                | Z <sub>AUX10</sub>                                  | 1    |     | 1                    | ΜΩ   |

| Pin capacitance                                                                   |                                                     |      | 20  | +                    | pF   |

| 1 iii capacitance                                                                 | $C_{AUX10}$                                         |      | 40  |                      | hτ   |

|                                                                  |                              |         |                   | <u> </u>             |           |

|------------------------------------------------------------------|------------------------------|---------|-------------------|----------------------|-----------|

|                                                                  |                              |         |                   |                      |           |

| AUX5 output                                                      |                              |         |                   |                      |           |

| Auxiliary voltage range                                          | $V_{AUX5}$                   | -0.6    |                   | 42                   | V         |

| Battery backup current ( $V_{LN} >= 4V$ )                        | I <sub>AUX5BACKUP</sub>      | -4      |                   | -25                  | μA        |

| Supply current                                                   | $I_{AUX5}$                   | 4.5     | 5                 | 5.5                  | mA        |

| Input impedance to Ground when disabled                          | $\mathbf{R}_{\mathrm{AUX5}}$ |         | 8                 |                      | $M\Omega$ |

| Input impedance to LN when enabled                               | $\mathbf{Z}_{\mathrm{AUX5}}$ |         | 400               |                      | kΩ        |

| Pin capacitance                                                  | C <sub>AUX5</sub>            |         | 20                |                      | pF        |

| SPYMODE operation:                                               |                              |         |                   |                      |           |

| 1 LSB DC current step                                            | IAUX5 <sub>STEP</sub>        | 18      | 20                | 22                   | μA        |

| Spymode Full Range current                                       |                              |         | I <sub>AUX5</sub> |                      | mA        |

| 1,                                                               |                              |         | Hens              |                      |           |

| STAB input                                                       |                              |         |                   |                      |           |

| Voltage range                                                    | $ m V_{STAB}$                | -0.6    |                   | V <sub>CC</sub> +0.6 | V         |

| Discharge peak current                                           | I <sub>STABDIS</sub>         | 0.0     |                   | 5                    | mA        |

| DC Leakage @ 1 LSB V <sub>LN</sub> programming error             | I <sub>STABLEAK</sub>        |         |                   | 300                  | nA        |

| Pin capacitance                                                  | C <sub>STAB</sub>            |         | 3                 | 200                  | pF        |

| 1 in cupacitance                                                 | SIAB                         |         |                   | 1                    | Pr.       |

| RING input                                                       |                              |         |                   |                      |           |

| Voltage range                                                    | V <sub>RING</sub>            | -0.6    |                   | V <sub>CC</sub> +0.6 | V         |

| AC Input impedance relative to C <sub>STAB</sub>                 | ZIN <sub>RING</sub>          | 0.75    | 1                 | 1.25                 | MΩ        |

| DC Leakage current                                               |                              | 0.73    | 1                 | 100                  | nA        |

| Pin capacitance                                                  | I <sub>RINGLEAK</sub>        |         | 3                 | 100                  |           |

| riii capacitance                                                 | C <sub>RING</sub>            |         | 3                 | +                    | pF        |

| nor t                                                            |                              |         |                   |                      |           |

| POL input                                                        | <del>-</del> -7              | 0.6     |                   | T7 0 6               | *7        |

| Voltage range                                                    | V <sub>POL</sub>             | -0.6    | - 1               | V <sub>CC</sub> +0.6 | V         |

| AC Input impedance relative to C <sub>STAB</sub>                 | ZIN <sub>POL</sub>           | 0.75    | 1                 | 1.25                 | MΩ        |

| DC Leakage current                                               | I <sub>POLLEAK</sub>         |         |                   | 100                  | nA        |

| Pin capacitance                                                  | $C_{POL}$                    |         | 3                 |                      | pF        |

|                                                                  |                              |         |                   |                      |           |

| TX output                                                        |                              |         |                   |                      |           |

| Output voltage LOW (I <sub>OL</sub> =0.5mA)                      | $VOL_{TX}$                   |         |                   | 0.3                  | V         |

| DC Leakage current                                               | I <sub>TXLEAK</sub>          |         |                   | 100                  | nA        |

| Output sink current at Vcc > 2.1V                                | $I_{TXSINK}$                 | 1.7     |                   | 3.5                  | mA        |

| Max. data transfer cap. in OFFLINE (I <sub>TXSINK</sub> = 500uA) | N <sub>TXMAXBYTES</sub>      |         |                   | 30                   | Bytes/s   |

| Pin capacitance                                                  | $C_{TX}$                     |         | 3                 |                      | PF        |

|                                                                  |                              |         |                   |                      |           |

| RX input (FA) version                                            |                              |         |                   |                      |           |

| Quiescent current from RX ( $V_{RX} = 0V$ )                      | $RPU_{RX}$                   |         |                   | -5                   | μA        |

| Input voltage low                                                | VIL <sub>RX</sub>            | 0.1     |                   |                      | V         |

| Input voltage high                                               | $VIH_{RX}$                   |         |                   | 0.3                  | V         |

| Hysteresis <sup>1</sup>                                          | V <sub>RXHYST</sub>          |         | 0                 |                      | V         |

| Maximum data transfer capacity in OFFLINE                        | N <sub>RXMAXBYTES</sub>      |         |                   | 60                   | Bytes/s   |

| Pin capacitance                                                  | $C_{RX}$                     |         | 3                 |                      | PF        |

| UARTFLEX locking area for 0x55 SYNC_WDR                          | T <sub>LOCKSPAN</sub>        | 1800    | 2400              | 3000                 | Bits/s    |

|                                                                  |                              |         |                   |                      |           |

| RX input (EE) version                                            |                              |         |                   |                      |           |

| Pull-up resistor to V <sub>CC</sub>                              | $RPU_{RX}$                   |         | 66                |                      | kΩ        |

| Input voltage low                                                | VIL <sub>RX</sub>            |         |                   | 0.33Vcc              | V         |

| Input voltage high                                               | VIH <sub>RX</sub>            | 0.66Vcc |                   |                      | V         |

| Hysteresis                                                       | V <sub>RXHYST</sub>          |         | 0.6               |                      | V         |

<sup>&</sup>lt;sup>1</sup> The RX pin in FA version is a current sourced driving pin that eliminates the typical miller capacity problem of an optocoupler. There is no voltage change on the pin during transfer.

# MLX32001

## Universal PSTN Line Interface

| Maximum data transfer capacity in OFFLINE        | N <sub>RXMAXBYTES</sub> |       |      | 30                   | Bytes/s |

|--------------------------------------------------|-------------------------|-------|------|----------------------|---------|

| Pin capacitance                                  | $C_{RX}$                |       | 3    |                      | pF      |

| UARTFLEX locking area for 0x55 SYNC_WDR          | T <sub>LOCKSPAN</sub>   | 1800  | 2400 | 3000                 | Bits/s  |

|                                                  |                         |       |      |                      |         |

| SWVCC output                                     |                         |       |      |                      |         |

| SWVCC Voltage range                              | $ m V_{AUX5}$           | -0.6  |      | V <sub>CC</sub> +0.6 | V       |

| Leakage current (low level)                      | I <sub>SWVCCLEAK</sub>  |       |      | -1                   | μA      |

| Drive current (high level)                       | I <sub>SWVCC</sub>      | 0.25  | 0.5  | 1.0                  | mA      |

| Pin capacitance                                  | $C_{SWVCC}$             |       | 6    |                      | pF      |

|                                                  |                         |       |      |                      |         |

| DP output                                        |                         |       |      |                      |         |

| DP Voltage range                                 | $V_{DP}$                | -0.6  |      | 42                   | V       |

| DP Maximum current sink                          | $IOL_{DP}$              | 200   |      |                      | μA      |

| DP Leakage current                               | ILK <sub>DP</sub>       |       |      | 100                  | nA      |

| Capacitance to Ground                            | C <sub>DPMIN</sub>      | 3.3   |      |                      | nF      |

| Resistance to LN in ONLINE ( $V_{LN} >= 4V$ )    | $R_{\mathrm{DPLN}}$     |       | 10   |                      | kΩ      |

|                                                  |                         |       |      |                      |         |

| AC0 & AC1 output                                 |                         |       |      |                      |         |

| Voltage range                                    | V <sub>AC</sub>         | -0.6  |      | 42                   | V       |

| Resistance to LN (closed, $V_{LN} >= 4V$ )       | $RON_{AC}$              | 16    | 25   | 36                   | Ω       |

| Resistance to GND (1 opened, $V_{LN} >= 4V$ )    | $ROFF_{AC}$             | 600   |      |                      | kΩ      |

| Resistance to GND (both closed, $V_{LN} >= 4V$ ) | ROFF <sub>AC</sub>      | 350   |      |                      | kΩ      |

| Internal clock frequency low speed mode          | Fosclow                 | 196   | 200  | 204                  | kHz     |

| Internal clock frequency highspeed mode          | Foschigh                | 3.136 | 3.2  | 3.264                | MHz     |

| Operating temperature                            | T <sub>OPERNORM</sub>   | 0     | 20   | 70                   | °C      |

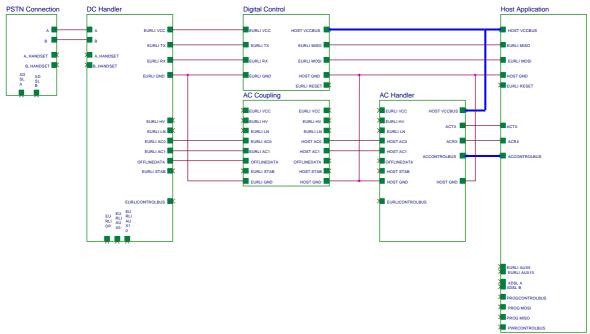

## 9. Typical application diagrams

## 9.1 V.90 modem

#### Block diagram

Line interface, DC-handler and line transformer

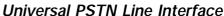

### 9.2 PC-Voice

#### PC-Voice block diagram

PC-Voice line interface and DC-handler

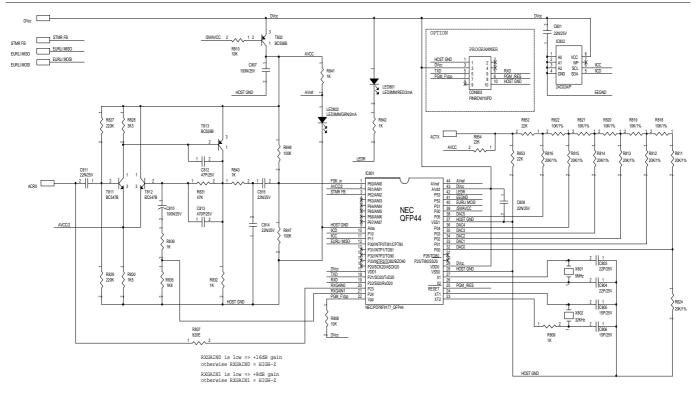

# 9.3 Line powered modem / meter reading / POS application

Block diagram

AC- and DC-handler

Host application and RX-amplifier

### 10. Information

For ordering please contact: Melexis Swiss Branch 38, Chemin de Buchaux CH-2022 Bevaix Switzerland Phone +41 (4132)8470660 Fax +41 (4132)8470699

E-mail: <u>iva@melexis.com</u>

Web: www.melexis.com

For design information please contact: Joritel International B.V. Mr Rien van der Linden Fregatstraat 99 3534 RC Utrecht Netherlands Phone: +31 (30)2421519

Fax: +31 (30)2442176 E-mail: rien@joritel.nl Web: www.joritel.nl