# MICROELECTRONICS 2A Single Cell Switchmode Li-Ion/Polymer Battery Charger with System Power-Path Selection and Automatic USB/Charger Detection

# DESCRIPTION

The EUP8218 is a highly integrated single cell Li-ion and Li-polymer battery charger. It integrates a constantfrequency PWM controller with high accuracy regulation of input current, charge current, and voltage. It also provides battery detection, pre-conditioning, charge termination, and charge status monitoring.

The EUP8218 provides power path selection function. When the qualified adapter is present, the system is powered by the adapter. Otherwise, the system is powered by the battery. It also integrates an USBconnection-monitoring device used to determine if a standard USB device or a battery-charging device is connected.

The EUP8218 charges the battery in three phases: pre-conditioning, fast-charge constant current and constant voltage. In all stages, an internal control loop monitors the IC junction temperature and reduce charge current if the internal temperature threshold (120°C) is exceeded. Additionally, a battery pack thermistor monitoring input (TS) is included that monitors battery temperature for safety charging.

Charge is terminated when the current reaches 10% of the fast charge rate. A programmable charge timer offers a safety back up. The EUP8218 automatically restarts the charge cycle if the battery voltage falls below an internal threshold, and enters a low-quiescent current sleep mode when the input voltage falls below the battery voltage.

The EUP8218 features Dynamic Power Management (DPM) to reduce the charge current when the input power limit is reached to avoid over-loading the adapter. A highly-accurate current-sense amplifier enables precise measurement of input current from adapter to monitor overall system power.

The EUP8218 is available in a 28-pin, 4mm×4mm TQFN package.

# FEATURES

- 4.5V-20V Input Operating Range

- High Integration

- Automatic Power Path Selector Between Adapter and Battery

- Automatic USB/Charger Detection

- Dynamic Power Management

- Integrated 20V High Side Switching MOSFET

- Safety

- Thermal Regulation Loop Throttles Back Current to Limit Tj=120°C

- Thermal Shutdown

- Battery Thermistor Sense Hot/Cold Charge Suspend & Battery Detect

- Input Over-Voltage Protection with Programmable Thereshold

- Accuracy

- ±1% Charge Voltage Regulation

- ±10% Charge Current Regulation

- ±10% Input Current Regulation

- Less than 25µA Battery Current with Adapter Removed

- Less than 5mA Input Current with Adapter Present and Charge Disabled

- 4mm×4mm TQFN-28 Package

- RoHS Compliant and 100% Lead (Pb)-Free Halogen-Free

#### APPLICATIONS

- Mobile and Smart Phones

- Tablet PC

- Handheld Devices

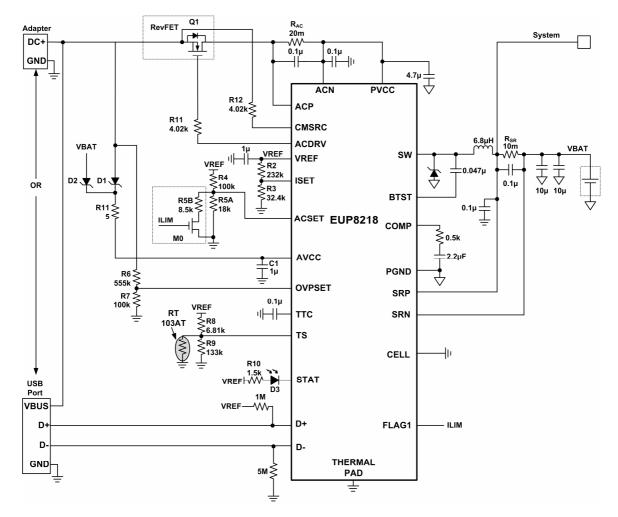

## **Typical Application Circuit**

Figure 1. 1-Cell Typical Application Schematic with Single Cell Battery (USB or adapter with input OVP 10.5V, 2A charge current, 0.2A pre-charge current, 2.5A adapter current or ILIM 0.9A limit current.R5B use 3.8k for 0.5A limit current.)

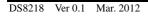

Figure 2.

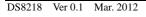

# **Pin Configurations**

| Package Type | Pin Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN-28      | (TOP VIEW) $(TOP VIEW)$ $(TO$ |

# **Pin Description**

| PIN   | TQFN-28 | I/O/P | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACN   | 1       | Ι     | Adapter current sense resistor negative input. A $0.1\mu$ F ceramic capacitor is placed from ACN to ACP to provide differential-mode filtering. An optional $0.1\mu$ F ceramic capacitor is placed from ACN pin to AGND for common-mode filtering.                                                                                                                                          |

| ACP   | 2       | P/I   | Adapter current sense resistor positive input. A $0.1\mu$ F ceramic capacitor is placed from ACN to ACP to provide differential-mode filtering. A $0.1\mu$ F ceramic capacitor is placed from ACP pin to AGND for common-mode filtering.                                                                                                                                                    |

| CMSRC | 3       | 0     | Connect to the source of N-channel RevFET. Place $4k\Omega$ resistor from CMSRC pin to the source of RevFET to control the turn-on speed.                                                                                                                                                                                                                                                   |

| ACDRV | 4       | 0     | AC adapter to PVCC switch driver output. Connect to $4k\Omega$ resistor then to the gate of the RevFET N-channel power MOSFET.                                                                                                                                                                                                                                                              |

| STAT  | 5       | 0     | Open-drain charge status pin with $1.5k\Omega$ pull up to power rail. The STAT pin can be used to drive LED or communicate with the host processor. It indicates various charger operations: LOW when charge in progress. HIGH when charge is complete or in SLEEP mode. Blinking at 0.5Hz when fault occurs, including charge suspend, input over-voltage, timer fault and battery absent. |

| TS    | 6       | Ι     | Temperature qualification voltage input. Connect a negative temperature coefficient thermistor. Program the hot and cold temperature window with a resistor divider from VREF to TS to AGND. The temperature qualification window can be set to 5-40°C or wider. The 103AT thermistor is recommended.                                                                                       |

| TTC   | 7       | 0     | Safety Timer and termination control. Connect a capacitor from this node to AGND to set the fast charge safety timer (5.6min/nF). Pre-charge timer is internally fixed to 30 minutes. Pull the TTC to LOW to disable the charge termination and safety timer. Pull the TTC to HIGH to disable the safety timer but allow the charge termination.                                            |

| VREF  | 8       | Р     | 3.3V reference voltage output. Place a $1\mu$ F ceramic capacitor from VREF to AGND pin close to the IC. This voltage could be used for programming ISET and ACSET and TS pins. It may also serve as the pull-up rail of STAT pin and CELL pin.                                                                                                                                             |

| D+    | 9       | Ι     | D+ and D- Connections for USB Input Adapter Detection-When a charge cycle is initiated by the USB input , and a short is detected between D+ and D- , the FLAG1 $\sim$                                                                                                                                                                                                                      |

| D-    | 10      | Ι     | is low and the input current limit set by ACSET shall not change. If a short is not detected, the FLAG1 is high and the input current limit is changed to the predetermined USB2 or USB3 current limit.                                                                                                                                                                                     |

| FLAG1 | 11      | 0     | Charger/standard USB device detect flag-When an USB charger is plugged in, the FLAG1 is low. While a standard USB device is plugged in, the FLAG is high.                                                                                                                                                                                                                                   |

| PIN            | TQFN-28 | I/O/P | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ISET           | 13      | Ι     | Fast charge current set point. Use a voltage divider from VREF to ISET to AGND to set the fast charge current:<br>$I_{CHG}=V_{ISET}/(20*R_{SR})$<br>The pre-charge and termination current is internally as one tenth of the charge current. The charger is disabled when ISET pin voltage is below 40mV and enabled when ISET pin voltage is above 120mV. |

| CELL           | 14      | Ι     | Cell selection pin. Set CELL pin LOW for 1-cell with a fixed 4.2V.                                                                                                                                                                                                                                                                                         |

| SRN            | 15      | Ι     | Battery Sense Input. A bypass capacitor of $20\mu$ F is required to minimize ripple voltage. When VBAT is within 90mV of AVCC, the EUP8218 is forced into sleep mode.                                                                                                                                                                                      |

| SRP            | 16      | I/P   | Current Amplifier Sense Input. A sense resistor, RSENSE, must be connected between the SRN and SRP pins.                                                                                                                                                                                                                                                   |

| ACSET          | 17      | Ι     | Input current set point. Use a voltage divider from VREF to ACSET to AGND to set this value:<br>$I_{DPM}=V_{ACSET}/(20*R_{AC})$                                                                                                                                                                                                                            |

| OVPSET         | 18      | Ι     | Valid input voltage set point. Use a voltage divider from input to OVPSET to AGND to set this voltage. The voltage above internal 1.6V reference indicates input over-voltage, and the voltage below internal 0.5V reference indicates input under-voltage. LED driven by STAT pin keeps blinking, reporting fault condition.                              |

| COMP           | 20      | 0     | Compensation, Soft-Start Pin. Charging begins when the COMP pin reaches 850mV. The recommended compensation components are a $2.2\mu$ F (or larger) capacitor and a 0.5k series resistor. A 100 $\mu$ A current into the compensation capacitor also sets the soft-start slew rate.                                                                        |

| BTST           | 21      | Р     | PWM high side driver positive supply.                                                                                                                                                                                                                                                                                                                      |

| AGND           | 22      | Р     | Analog Ground.                                                                                                                                                                                                                                                                                                                                             |

| PGND           | 23      | Р     | Power ground. Ground connection for high-current power converter node. On<br>PCB layout, connect directly to ground connection of input and output capacitors<br>of the charger. Only connect to AGND through the Thermal Pad underneath the<br>IC.                                                                                                        |

| SW             | 24,25   | Р     | Switching node, charge current output inductor connection. Connect the $0.047\mu$ F bootstrap capacitor from SW to BTST.                                                                                                                                                                                                                                   |

| PVCC           | 26, 27  | Р     | Charger input voltage. Connect at least 10µF ceramic capacitor from PVCC to PGND and place it as close as possible to IC.                                                                                                                                                                                                                                  |

| AVCC           | 28      | P/I   | IC power positive supply. Place a $1\mu$ F ceramic capacitor from AVCC to AGND<br>and place it as close as possible to IC. Place a $10\Omega$ resistor from input side to<br>AVCC pin to filter the noise. For 5V input, a $5\Omega$ resistor is recommended.                                                                                              |

| NC             | 12,19   |       | No connect                                                                                                                                                                                                                                                                                                                                                 |

| Thermal<br>Pad | AGND    | Р     | Exposed pad beneath the IC. Always solder Thermal Pad to the board, and have vias on the Thermal Pad plane star-connecting to AGND and ground plane for high-current power converter. It dissipates the heat from the IC.                                                                                                                                  |

# **Ordering Information**

| Order Number | Package Type | Marking        | <b>Operating Temperature Range</b> |

|--------------|--------------|----------------|------------------------------------|

| EUP8218JIR1  | TQFN-28      | xxxxx<br>P8218 | -40°C to +85°C                     |

| EUP8218 | Lead Free Code<br>1: Lead Free, Halogen Free<br>Packing<br>R: Tape & Reel |

|---------|---------------------------------------------------------------------------|

|         | Operating temperature range<br>I: Industry Standard                       |

|         | Package Type<br>J: TQFN                                                   |

### **Absolute Maximum Ratings (1)**

| ■ PVCC, AVCC, ACP, ACN, ACDRV, CMSRC, BTST, SRP, SRN          |

|---------------------------------------------------------------|

| SW2V to 20V                                                   |

| • OVPSET, TS,TTC, CELL, COMP, D+,D-,FLAG1                     |

| ■ VREF, ISET, ACSET, STAT                                     |

| ■ PGND, AGND0.3V to 0.3V                                      |

| ■ Maximum Difference Voltage, SRP-SRN, ACP-ACN                |

| ■ Package Thermal Resistance ,TQFN-28 ,θ <sub>JA</sub> 40°C/W |

| ■ Junction temperature range, T <sub>J</sub> 150°C            |

| ■ Storage temperature range, Tstg                             |

| ■ Lead temperature (soldering, 10s) 260°C                     |

|                                                               |

# **Recommended Operating Conditions (2)**

|                                            |                  | Min. | Max. | Unit |

|--------------------------------------------|------------------|------|------|------|

| Input voltage                              | V <sub>IN</sub>  | 4.5  | 20   | V    |

| Output voltage                             | V <sub>OUT</sub> |      | 4.5  | V    |

| Output current ( $R_{SR}$ 10m $\Omega$ )   | I <sub>OUT</sub> | 0.5  | 4    | А    |

| Maximum difference voltage                 | ACP-ACN          | -200 | 200  | mV   |

| Maximum difference voltage                 | SRP-SRN          | -200 | 200  | mV   |

| Ambient Temperature Range , T <sub>A</sub> |                  | -40  | 85   | °C   |

Note (1): Stress beyond those listed under "Absolute Maximum Ratings" may damage the device.

Note (2): The device is not guaranteed to function outside the recommended operating conditions.

### **Electrical Characteristics**

$4.5V \le V(PVCC, AVCC) \le 20V, -40^{\circ}C < T_J < + 125^{\circ}C$ , typical values are at  $T_A = 25^{\circ}C$ , with respect to AGND (unless otherwise noted).

| Symbol               | Parameter                                                                   | Conditions                                                                                                                                | EUP8218 |      |      | Unit |

|----------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|------|

| Symbol               |                                                                             |                                                                                                                                           | Min.    | Тур. | Max. | Umi  |

| OPERATING            | CONDITIONS                                                                  |                                                                                                                                           |         |      |      |      |

| V <sub>AVCC_OP</sub> | AVCC input voltage operating range during charging                          |                                                                                                                                           | 4.5     |      | 20   | V    |

| QUIESCENT            | CURRENTS                                                                    | -                                                                                                                                         |         |      | _    |      |

|                      |                                                                             | $\label{eq:Vavcc} \begin{split} V_{AVCC} > V_{UVLO},  V_{SRN} > V_{AVCC} \\ (SLEEP),  T_J = 0^\circ C \text{ to } 85^\circ C \end{split}$ |         |      | 25   |      |

| $I_{BAT}$            | Battery discharge current<br>(sum of currents into<br>AVCC, PVCC, ACP, ACN) | BTST, SW, SRP, SRN, $V_{AVCC} > V_{UVLO}$ , $V_{AVCC} > V_{SRN}$ , ISET < 40mV, $V_{BAT}$ =4.2V, Charge disabled                          |         |      | 25   | μΑ   |

|                      |                                                                             | BTST, SW, SRP, SRN, $V_{AVCC} > V_{UVLO}$ , $V_{AVCC} > V_{SRN}$ , ISET > 120mV, $V_{BAT}$ =4.2V, Charge done                             |         |      | 25   |      |

|                      |                                                                             | $V_{AVCC} > V_{UVLO}, V_{AVCC} > V_{SRN},$<br>ISET < 40mV, $V_{BAT}$ =4.2V, Charge disabled                                               |         | 2.5  | 5    |      |

| I <sub>AC</sub>      | Adapter supply current<br>(sum of current into<br>AVCC,ACP, ACN)            | $V_{AVCC} > V_{UVLO}, V_{AVCC} > V_{SRN},$<br>ISET > 120mV, Charge enabled,<br>no switching                                               |         | 2.5  | 5    | m A  |

|                      |                                                                             | $\label{eq:VAVCC} \begin{split} V_{AVCC} &> V_{UVLO},  V_{AVCC} > V_{SRN}, \\ ISET &> 120mV,  Charge \ enabled, \\ switching \end{split}$ |         | 15   |      |      |

$4.5V \le V(PVCC, AVCC) \le 20V, -40^{\circ}C < T_J < + 125^{\circ}C$ , typical values are at  $T_A = 25^{\circ}C$ , with respect to AGND (unless otherwise noted).

| Symbol                      | Parameter                                                                     | Conditions                                          | E    | UP821 | .8   | Unit |

|-----------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------|------|-------|------|------|

| Symbol                      | rarameter                                                                     | Conultions                                          | Min. | Тур.  | Max. | Unit |

|                             | OLTAGE REGULATION                                                             |                                                     | 1    | 6     | T    |      |

| V <sub>BAT_REG</sub>        | SRN regulation voltage                                                        | CELL to AGND, measured on SRN                       |      | 4.2   |      | V    |

|                             | Charge voltage regulation accuracy                                            | $T_J = 0^{\circ}C$ to $85^{\circ}C$                 | -1%  |       | 1%   |      |

| CURRENT R                   | REGULATION — FAST CHAR                                                        | GE                                                  | 1    |       | •    |      |

| V <sub>ISET</sub>           | ISET Voltage Range                                                            | $RSENSE = 10m\Omega$                                | 0.12 |       | 0.8  | V    |

| K <sub>ISET</sub>           | Charge Current Set Factor<br>(Amps of Charge Current per<br>Volt on ISET pin) | RSENSE = $10m\Omega$                                |      | 5     |      | A/V  |

|                             | ChargeCurrent Regulation<br>Accuracy (with Schottky<br>diode on SW)           | $V_{SRP-SRN} = 20 \text{ mV}$                       | -10% |       | 10%  |      |

| $V_{ISET\_CD}$              | Charge Disable Threshold                                                      | ISET falling                                        | 40   | 50    |      | mV   |

| V <sub>ISET_CE</sub>        | Charge Enable Threshold                                                       | ISET rising                                         |      | 100   | 120  | mV   |

| I <sub>ISET</sub>           | Leakage Current into ISET                                                     | VISET = 2V                                          |      |       | 100  | nA   |

|                             | RENT REGULATION                                                               |                                                     | 1    |       |      |      |

| K <sub>DPM</sub>            | Input DPM Current Set<br>Factor (Amps of Input Current<br>per Volt on ACSET)  | RSENSE = $10m\Omega$                                |      | 5     |      | A/V  |

|                             | Input DPM Current Regulation<br>Accuracy (with Schottky diode<br>on SW)       |                                                     | -10% |       | 10%  |      |

| I <sub>ACSET</sub>          | Leakage Current into ACSET pin                                                | VACSET = 2V                                         |      |       | 100  | nA   |

| CURRENT R                   | <b>REGULATION – PRE-CHARG</b>                                                 | E                                                   |      |       |      |      |

| <b>K</b> <sub>IPRECHG</sub> | Precharge current set factor                                                  | Percentage of fast charge current                   |      | 10%   |      |      |

| CHARGE TH                   | ERMINATION                                                                    |                                                     |      |       |      |      |

| <b>K</b> <sub>TERM</sub>    | Termination current set factor                                                | Percentage of fast charge current                   |      | 10%   |      |      |

| t <sub>TERM_DEG</sub>       | Deglitch time for termination (both edges)                                    |                                                     |      | 100   |      | ms   |

| t <sub>QUAL</sub>           | Termination qualification time                                                | $V_{SRN} > V_{RECH}$ and $I_{CHG} \! < \! I_{TERM}$ |      | 250   |      | ms   |

| I <sub>QUAL</sub>           | Termination qualification current                                             | Discharge current once termination is detected      |      | 2     |      | mA   |

| INPUT UND                   | ER-VOLTAGE LOCK-OUT CO                                                        | OMPARATOR (UVLO)                                    |      |       |      |      |

| V <sub>UVLO</sub>           | AC under-voltage rising threshold                                             | Measure on AVCC                                     | 3.4  | 3.6   | 3.9  | V    |

| $V_{\rm UVLO\_HYS}$         | AC under-voltage hysteresis, falling                                          | Measure on AVCC                                     |      | 300   |      | mV   |

| SLEEP COM                   | <b>IPARATOR (REVERSE DISCH</b>                                                | LARGING PROTECTION)                                 |      |       |      |      |

| V <sub>SLEEP</sub>          | SLEEP mode threshold                                                          | $V_{AVCC} - V_{SRN}$ falling                        | 30   | 90    | 150  | mV   |

| $V_{SLEEP\_HYS}$            | SLEEP mode hysteresis                                                         | $V_{AVCC} - V_{SRN}$ rising                         |      | 200   |      | mV   |

| t <sub>sleep_fall_cd</sub>  | SLEEP deglitch to disable charge                                              | V <sub>AVCC</sub> – V <sub>SRN</sub> falling        |      | 1     |      | ms   |

$4.5V \le V(PVCC, AVCC) \le 20V, -40^{\circ}C < T_J < + 125^{\circ}C$ , typical values are at  $T_A = 25^{\circ}C$ , with respect to AGND (unless otherwise noted).

| Symbol                             | Donomator                                                                     | Conditions                                   | F    | EUP821 | 8    | TInit |

|------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------|------|--------|------|-------|

| Symbol                             | Parameter                                                                     | Conditions                                   | Min. | Typ.   | Max. | Unit  |

| SLEEP COMP                         | ARATOR (REVERSE DISCI                                                         | HARGING PROTECTION)                          |      |        | •    |       |

| t <sub>sleep_fall</sub><br>_fetoff | SLEEP deglitch to turn off input FETs                                         | $V_{AVCC} - V_{SRN}$ falling                 |      | 5      |      | ms    |

| t <sub>sleep_fall</sub>            | Deglitch to enter SLEEP<br>mode, disable VREF and<br>enter low quiescent mode | V <sub>AVCC</sub> – V <sub>SRN</sub> falling |      | 100    |      | ms    |

| t <sub>sleep_pwrup</sub>           | Deglitch to exit SLEEP<br>mode, and enable VREF                               | V <sub>AVCC</sub> – V <sub>SRN</sub> rising  |      | 30     |      | ms    |

| BAT LOWV C                         | OMPARATOR                                                                     |                                              |      |        |      |       |

| $V_{\text{LOWV}}$                  | Precharge to fast charge transition                                           | CELL to AGND, measure on SRN                 | 2.85 | 2.9    | 2.95 | v     |

| $V_{\text{LOWV}_{\text{HYS}}}$     | Fast charge to precharge hysteresis                                           | CELL to AGND, measure on SRN                 |      | 200    |      | mV    |

| t <sub>pre_to_fas</sub>            | VLOWV rising deglitch                                                         | Delay to start fast charge current           |      | 25     |      | ms    |

| $t_{fast\_to\_pre}$                | VLOWV falling deglitch                                                        | Delay to start precharge current             |      | 25     |      | ms    |

| RECHARGE (                         | COMPARATOR                                                                    |                                              |      |        |      |       |

| V <sub>RECHG</sub>                 | Recharge Threshold, below<br>regulation voltage limit,<br>VBAT_REG-VSRN       | CELL to AGND, measure on SRN                 | 70   | 100    | 130  | mV    |

| t <sub>RECH_RISE_DEG</sub>         | VRECHG rising deglitch                                                        | V <sub>SRN</sub> decreasing below VRECHG     |      | 10     |      | ms    |

| t <sub>RECH_FALL_DEG</sub>         | VRECHG falling deglitch                                                       | V <sub>SRN</sub> increasing above VRECHG     |      | 10     |      | ms    |

| BAT OVER-V                         | OLTAGE COMPARATOR                                                             |                                              |      |        |      |       |

| $V_{OV\_RISE}$                     | Over-voltage rising<br>threshold                                              | As percentage of $V_{BAT_{REG}}$             |      | 104%   |      |       |

| V <sub>OV_FALL</sub>               | Over-voltage falling<br>threshold                                             | As percentage of V <sub>SRN</sub>            |      | 102%   |      |       |

| INPUT OVER-                        | VOLTAGE COMPARATOR                                                            | (ACOV)                                       | •    | •      | •    |       |

| V <sub>ACOV</sub>                  | AC Over-Voltage Rising<br>Threshold to turn off<br>RevFET                     | OVPSET rising                                | 1.55 | 1.6    | 1.65 | v     |

| $V_{ACOV\_HYS}$                    | AC over-voltage falling hysteresis                                            | OVPSET falling                               |      | 50     |      | mV    |

| t <sub>ACOV_RISE_DEG</sub>         | AC Over-Voltage Rising<br>Deglitch to turn off RevFET<br>and Disable Charge   | OVPSET rising                                |      | 1      |      | μs    |

| t <sub>ACOV_FALL_DEG</sub>         | AC Over-Voltage Falling<br>Deglitch to Turn on RevFET                         | OVPSET falling                               |      | 30     |      | ms    |

| INPUT UNDE                         | R-VOLTAGE COMPARATO                                                           | R (ACUV)                                     |      | •      | •    |       |

| V <sub>ACUV</sub>                  | AC Under-Voltage Falling<br>Threshold to turn off<br>RevFET                   | OVPSET falling                               | 0.45 | 0.5    | 0.55 | v     |

| $V_{ACUV\_HYS}$                    | AC Under-Voltage Rising<br>Hysteresis                                         | OVPSET rising                                |      | 100    |      | mV    |

$4.5V \le V(PVCC, AVCC) \le 20V, -40^{\circ}C < T_J < + 125^{\circ}C$ , typical values are at  $T_A = 25^{\circ}C$ , with respect to AGND (unless otherwise noted).

| Sumbol                      | Devemator                                                                     | Conditions                                                                         | E        | CUP821 | 8     | Unit |

|-----------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------|--------|-------|------|

| Symbol                      | Parameter                                                                     | Conditions                                                                         | Min.     | Typ.   | Max.  | Unit |

| INPUT UNDE                  | R-VOLTAGE COMPARATO                                                           | R (ACUV)                                                                           |          |        |       |      |

| t <sub>ACOV_FALL_DEG</sub>  | AC Under-Voltage Falling<br>Deglitch to turn off RevFET<br>and Disable Charge | OVPSET falling                                                                     |          | 1      |       | μs   |

| $t_{ACOV\_RISE\_DEG}$       | AC Under-Voltage Rising<br>Deglitch to turn on RevFET                         | OVPSET rising                                                                      |          | 30     |       | ms   |

| THERMAL RI                  | EGULATION                                                                     |                                                                                    |          |        |       |      |

| $T_{J\_REG}$                | Junction Temperature<br>Regulation Accuracy                                   | ISET > 120mV, Charging                                                             |          | 120    |       | °C   |

| T <sub>SHUT</sub>           | Thermal shutdown rising temperature                                           | Temperature rising                                                                 |          | 150    |       | °C   |

| THERMAL SH                  | HUTDOWN COMPARATOR                                                            |                                                                                    |          |        |       |      |

| t <sub>SHUT_RISE_DEG</sub>  | Thermal shutdown rising deglitch                                              | Temperature rising                                                                 |          | 100    |       | μs   |

| t <sub>SHUT_FALL_DEG</sub>  | Thermal shutdown falling deglitch                                             | Temperature falling                                                                |          | 10     |       | ms   |

| THERMISTO                   | R COMPARATOR                                                                  |                                                                                    |          | 1      |       |      |

| $V_{\text{LTF}}$            | Cold Temperature Threshold,<br>TS pin Voltage Rising<br>Threshold             | Charger suspends charge. As percentage to $V_{VREF}$                               | 71.5%    | 73.5%  | 75.5% |      |

| $V_{\text{LTF}_\text{HYS}}$ | Cold Temperature Hysteresis,<br>TS pin Voltage Falling                        | As percentage to $V_{\text{VREF}}$                                                 |          | 0.4%   |       |      |

| $\mathbf{V}_{\mathrm{HTF}}$ | Hot Temperature TS pin voltage rising Threshold                               | As percentage to $V_{\text{VREF}}$                                                 | 45.6%    | 47.2%  | 49.8% |      |

| V <sub>TCO</sub>            | Cut-off Temperature TS<br>pin voltage falling Threshold                       | As percentage to $V_{\text{VREF}}$                                                 | 43.2%    | 44.7%  | 46.2% |      |

| t <sub>TS_CHG_SUS</sub>     | Deglitch time for<br>Temperature Out of Range<br>Detection                    | $V_{TS} > V_{LTF}$ , or $V_{TS} < _{VTCO}$ , or $V_{TS} < _{VHTF}$                 |          | 20     |       | ms   |

| t <sub>ts_chg_resume</sub>  | Deglitch time for<br>Temperature in Valid<br>Range Detection                  | $V_{TS} < V_{LTF} - V_{LTF_HYS}$ or $V_{TS} > V_{TCO}$ ,<br>or $V_{TS} => V_{HTF}$ |          | 400    |       | ms   |

| CHARGE OVI                  | ER-CURRENT COMPARAT                                                           | OR (CYCLE-BY-CYCLE)                                                                |          |        |       |      |

| V <sub>OCP_CHRG</sub>       | Charge Over-Current<br>Rising Threshold,<br>VSRP>2.2V                         | Current as percentage of fast charge current                                       |          | 160%   |       |      |

| BAT SHORT (                 | COMPARATOR                                                                    |                                                                                    |          |        |       |      |

| $V_{\text{BATSHT}}$         | Battery short falling threshold                                               | Measure on SRN                                                                     |          | 2      |       | V    |

| $V_{BATSHT\_HYS}$           | Battery short rising hysteresis                                               | Measure on SRN                                                                     |          | 200    |       | mV   |

| t <sub>BATSHT_DEG</sub>     | Deglitch on both edges                                                        |                                                                                    | <u> </u> | 1      |       | μs   |

| V <sub>BATSHT</sub>         | Charge Current during<br>BATSHORT                                             | Percentage of fast charge current                                                  |          | 10%    |       |      |

| VREF REGUL                  | ATOR                                                                          |                                                                                    |          |        |       |      |

| $V_{VREF\_REG}$             | VREF regulator voltage                                                        | $V_{AVCC} > V_{UVLO}$ , No load                                                    | 3.267    | 3.3    | 3.333 | V    |

| I <sub>VREF_LIM</sub>       | VREF current limit                                                            | $V_{VREF} = 0 V, V_{AVCC} > V_{UVLO}$                                              | 35       |        | 90    | mA   |

$4.5V \le V(PVCC, AVCC) \le 20V, -40^{\circ}C < T_J < + 125^{\circ}C$ , typical values are at  $T_A = 25^{\circ}C$ , with respect to AGND (unless otherwise noted).

| Symak al                | Parameter                                                                      | C 1141                                               | E    | Unit |      |                                              |

|-------------------------|--------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|----------------------------------------------|

| Symbol                  |                                                                                | Conditions                                           | Min. | Тур. | Max. | Unit                                         |

| TTC INPUT               |                                                                                | · · · · · · · · · · · · · · · · · · ·                |      |      |      |                                              |

| t <sub>prechrg</sub>    | Precharge Safety Timer                                                         | Precharge time before fault occurs                   | 1620 | 1800 | 1980 | Sec                                          |

| t <sub>fastchrg</sub>   | Fast Charge Timer Range                                                        | Tchg=C <sub>TTC</sub> *K <sub>TTC</sub>              | 1    |      | 10   | hr                                           |

|                         | Fast Charge Timer<br>Accuracy                                                  |                                                      | -10% |      | 10%  |                                              |

| K <sub>TTC</sub>        | Timer Multiplier                                                               |                                                      |      | 5.6  |      | min<br>/nF                                   |

| $V_{TTC\_LOW}$          | TTC Low Threshold                                                              | TTC falling                                          |      |      | 0.4  | V                                            |

| I <sub>TTC</sub>        | TTC Source/Sink Current                                                        |                                                      | 45   | 50   | 55   | μA                                           |

| V <sub>TTC_OSC_HI</sub> | TTC oscillator high<br>threshold                                               |                                                      |      | 1.5  |      | V                                            |

| V <sub>TTC_OSC_LO</sub> | TTC oscillator low<br>threshold                                                |                                                      |      | 1    |      | V                                            |

| AC SWITCH               | (RevFET) DRIVER                                                                | •                                                    | •    |      | •    |                                              |

| $V_{ACDRV\_REG}$        | Gate Drive Voltage on<br>RevFET                                                | $V_{ACDRV}$ - $V_{CMSRC}$ when $V_{AVCC} > V_{UVLO}$ |      | 4    |      | V                                            |

| BATTERY DI              | ETECTION                                                                       |                                                      |      |      |      |                                              |

| t <sub>WAKE</sub>       | Wake timer                                                                     | Max time charge is enabled                           |      | 500  |      | ms                                           |

| I <sub>WAKE</sub>       | Wake current                                                                   | RSENSE = $10 \text{ m}\Omega$                        | 50   | 125  | 200  | m A                                          |

| t <sub>DISCHARGE</sub>  | Discharge timer                                                                | Max time discharge current is applied                |      | 1    |      | sec                                          |

| I <sub>DISCHARGE</sub>  | Discharge current                                                              |                                                      |      | 8    |      | m A                                          |

| I <sub>FAULT</sub>      | Fault current after a timeout fault                                            |                                                      |      | 2    |      | m A                                          |

| V <sub>WAKE</sub>       | Wake threshold with respect<br>to VREG To detect battery<br>absent during WAKE | Measure on SRN                                       |      | 100  |      | mV/c<br>ell                                  |

| V <sub>DISCH</sub>      | Discharge Threshold to<br>detect battery absent during<br>discharge            | Measure on SRN                                       |      | 2.9  |      | V/cel                                        |

| INTERNAL P              |                                                                                |                                                      |      |      |      | <u>.                                    </u> |

| fsw                     | PWM Switching Frequency                                                        |                                                      | 450  | 500  | 550  | kHz                                          |

| CHARGER SI              | ECTION POWER-UP SEQUE                                                          | ENCING                                               |      | •    |      |                                              |

| t <sub>CE_DELAY</sub>   | Delay from ISET above<br>120mV to start charging<br>battery                    |                                                      |      | 1.5  |      | s                                            |

| LOGIC IO PI             | N CHARACTERISTICS                                                              |                                                      |      | •    |      |                                              |

| V <sub>OUT_LO</sub>     | STAT Output Low<br>Saturation Voltage                                          | Sink Current = 5mA                                   |      |      | 0.5  | V                                            |

| LOGIC IO PI             | N CHARACTERISTICS                                                              | ·                                                    | ·    |      | ·    | <u> </u>                                     |

| V <sub>CELL_LO</sub>    | CELL pin input low<br>threshold, 1 cell                                        | CELL pin voltage falling edge                        |      |      | 0.5  | v                                            |

| INPUT CHAR              | ACTERISTICS                                                                    | ·                                                    | ·    | ·    | ·    | <u> </u>                                     |

| $I_{\rm off}D+$         | Off Leakage Current                                                            | D+=5V                                                |      |      | 1    | μA                                           |

| I <sub>off</sub> D-     | Off Leakage Current                                                            | D-=5V                                                |      |      | 1    | μA                                           |

| OUTPUT CHA              | ARACTERISTICS                                                                  | ·                                                    | ·    | ·    | ·    | <u> </u>                                     |

| V <sub>OL</sub> FLAG1   | Maximum LOW Output<br>Voltage                                                  | V <sub>AVCC</sub> =5V, I <sub>OL</sub> =20µA         |      |      | 0.3  | v                                            |

$4.5V \le V(PVCC, AVCC) \le 20V, -40^{\circ}C < T_J < + 125^{\circ}C$ , typical values are at  $T_A = 25^{\circ}C$ , with respect to AGND (unless otherwise noted).

| Symbol           | Parameter              | Conditions | EUP8218 |        |       | Unit |  |

|------------------|------------------------|------------|---------|--------|-------|------|--|

| Symbol           | rarameter              | Conditions | Min.    | Typ. M | Max.  | Umt  |  |

| OUTPUT CHA       | OUTPUT CHARACTERISTICS |            |         |        |       |      |  |

| D+/D-            |                        |            | 1.025   | 1.300  | 1.400 | V    |  |

| Threshold        |                        |            | 1.025   | 1.500  | 1.400 | v    |  |

| t <sub>off</sub> | Flag1 HIGH to LOW      | 100pF Load |         | 10     |       | ns   |  |

| t <sub>on</sub>  | Flag1 LOW to HIGH      | 100pF Load |         | 50     |       | ns   |  |

#### **Truth Table**

| <b>Connection State</b> | V <sub>AVCC</sub> | D-          | D+             | FLAG1 |

|-------------------------|-------------------|-------------|----------------|-------|

| STD USB Device          | 5V                | R to Gnd    | R to $V_{REF}$ | HIGH  |

| USB Charger             | 5V                | Short to D+ | Short to D-    | LOW   |

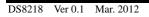

### **Operational Flow Chart**

Figure 3.

EUP8218

#### **FUNCTIONAL DESCRIPTION**

#### **Battery Current Regulation**

The ISET input sets the maximum charging current. Battery current is sensed by current sensing resistor RSR connected between SRP and SRN. The full-scale differential voltage between SRP and SRN is 40mV max. The equation for charge current is:

$$I_{CHARGE} = \frac{V_{ISET}}{20 \times R_{SR}}$$

(1)

The valid input voltage range of ISET is up to 0.8V. With  $10m\Omega$  sense resistor, the maximum output current is 4A. With  $20m\Omega$  sense resistor, the maximum output current is 2A.

The charger is disabled when ISET pin voltage is below 40mV and is enabled when ISET pin voltage is above 120mV. For  $10m\Omega$  current sensing resistor, the minimum fast charge current must be higher than 600mA.

Under high ambient temperature, the charge current will fold back to keep IC temperature not exceeding 120°C.

#### **Battery Precharge Current Regulation**

On Power-up, if the battery voltage is below the VLOWV threshold, the EUP8218 applies the pre-charge current to the battery. This pre-charge feature is intended to revive deeply discharged cells. If the VLOWV threshold is not reached within 30 minutes of initiating pre-charge, the charger turns off and a FAULT is indicated on the status pins.

For EUP8218, the pre-charge current is set as 10% of the fast charge rate set by ISET voltage.

$$I_{\text{PRECHARGE}} = \frac{V_{\text{ISET}}}{200 \times R_{\text{SR}}}$$

(2)

#### **Input Current Regulation**

The total input current from an AC adapter or other DC sources is a function of the system supply current and the battery charging current. System current normally fluctuated as portions of the systems are powered up or down. Without Dynamic Power Management (DPM), the source must be able to supply the maximum system current and the maximum available charger input current simultaneously. By using DPM, the input current regulator reduces the charging current when the summation of system power and charge power exceeds the maximum input power. Therefore, the current capability of the AC adapter can be lowered, reducing system cost.

Input current is set by the voltage on ACSET pin using the following equation:

$$I_{\rm DPM} = \frac{V_{\rm ACSET}}{20 \times R_{\rm AC}} \tag{3}$$

The ACP and ACN pins are used to sense across RAC with default value of  $20m\Omega$ . However, resistors of other values can also be used. A larger sense resistor will give a larger sense voltage and higher regulation accuracy, at the expense of higher conduction loss.

#### Charge Termination, Recharge, and Safety Timers

The charger monitors the charging current during the voltage regulation phase. Termination is detected when the SRN voltage is higher than recharge threshold and the charge current is less than the termination current threshold, as calculated below:

$$I_{\text{TERM}} = \frac{V_{\text{ISET}}}{200 \times R_{\text{SR}}} \tag{4}$$

where  $V_{ISET}$  is the voltage on the ISET pin and RSR is the sense resistor. There is a 25ms deglitch time during transition between fast-charge and pre-charge.

As a safety backup, the charger also provides an internal fixed 30 minutes pre-charge safety timer and a programmable fast charge timer. The fast charge time is programmed by the capacitor connected between the TTC pin and AGND, and is given by the formula:

$$t_{\rm TTC} = C_{\rm TTC} \times K_{\rm TTC} \tag{5}$$

Where  $C_{TTC}$  is the capacitor connected to TTC and  $K_{TTC}$  is the constant multiplier.

A new charge cycle is initiated when one of the following conditions occurs:

- The battery voltage falls below the recharge threshold

- A power-on-reset (POR) event occurs

- ISET pin toggled below 40mV (disable charge) and above 120mV (enable charge)

Pull TTC pin to AGND to disable both termination and fast charge safety timer (reset timer). Pull TTC pin to VREF to disable the safety timer, but allow charge termination.

#### Power Up

The charge uses a SLEEP comparator to determine the source of power on the AVCC pin, since AVCC can be supplied either from the battery or the adapter. With the adapter source present, if the AVCC voltage is greater than the SRN voltage, the charger exits SLEEP mode. If all conditions are met for charging, the charger then starts charge the battery (see *the Enabling and Disabling Charging* section). If SRN voltage is greater than AVCC, the charger enters low quiescent current SLEEP mode to minimize current drain from the battery. During SLEEP mode, the VREF output turns off and the STAT pin goes to high impedance.

If AVCC is below the UVLO threshold, the device is disabled.

#### Input Under-Voltage Lock-Out (UVLO)

The system must have a minimum AVCC voltage to allow proper operation. This AVCC voltage could come from either input adapter or battery, since a conduction path exists from the battery to AVCC through D2. When AVCC is below the UVLO threshold, all circuits on the IC are disabled.

#### Input Over-Voltage/Under-Voltage Protection

ACOV provides protection to prevent system damage due to high input voltage. In EUP8218, once the voltage on OVPSET is above the 1.6V ACOV threshold or below the 0.5V ACUV threshold, charge is disabled and input MOSFETs turn off. The EUP8218 provides flexibility to set the input qualification threshold.

#### **Enable and Disable Charging**

The following conditions have to be valid before charging is enabled:

- ISET pin above 120mV

- •Device is not in Under-Voltage-Lock-Out (UVLO) mode (i.e.  $V_{AVCC} > V_{UVLO}$ )

- Device is not in SLEEP mode (i.e.  $V_{AVCC} > V_{SRN}$ )

- OVPSET voltage is between 0.5V and 1.6V to qualify the adapter

- 1.5s delay is complete after initial power-up

- VREF LDO voltages are at correct levels

- Thermal Shut down (TSHUT) is not valid

- TS fault is not detected

- RevFET turns on (See *System Power Selector* for details)

One of the following conditions stops on-going charging:

- ISET pin voltage is below 40mV

- Device is in UVLO mode

- Adapter is removed, causing the device to enter SLEEP mode

- OVPSET voltage indicates the adapter is not valid

- VREF LDO voltage is overloaded

- TSHUT temperature threshold is reached

- TS voltage goes out of range indicating the battery temperature is too hot or too cold

- RevFET turns off

- TTC timer expires or pre-charge timer expires

#### System Power Selector

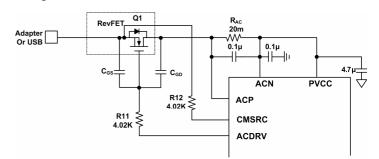

The IC automatically switches adapter or battery power to the system load. The battery is connected to the system by default during power up or during SLEEP mode. When the adapter plugs in and the voltage is above the battery voltage, the IC exits SLEEP mode, the adapter supply the system and battery. When the adapter is absent, the battery supply the system.

The ACDRV is used to drive a n-channel power MOSFETs between adapter and ACP. The n-channel FET with the drain connected to the ACP (Q1) provides reverse battery discharge protection, and minimizes system power dissipation with its low-RDS<sub>ON</sub>.

#### **Converter Operation**

The EUP8218 employs a 500KHz constant-frequency step-down switching regulator. The fixed frequency oscillator keeps tight control of the switching frequency under all conditions of input voltage, battery voltage, charge current, and temperature, simplifying output filter design and keeping it out of the audible noise region.

Both the current loop and the voltage loop share a common, high impedance, compensation node (COMP pin). A series capacitor and resistor on this pin compensates both loops. The resistor is included to provide a zero in the loop response and boost the phase margin. The compensation capacitor also provides a soft-start function for the charger. Upon start-up, then ramp at a rate set by the internal 100 $\mu$ A pullup current source and the external capacitor. Battery charge current starts ramping up when the COMP pin voltage reaches 0.85V. With a 2.2 $\mu$ F capacitor, time to start charge is about 18ms. Capacitance can be increased if a longer start-up time is needed.

#### **Charge Over-Current Protection**

The charger monitors top side MOSFET current by high side sense FET. When peak current exceeds MOSFET limit, it will turn off the top side MOSFET and keep it off until the next cycle. The charger has a secondary cycle-to-cycle over-current protection. It monitors the charge current, and prevents the current from exceeding 160% of the programmed charge current. The high-side gate drive turns off when either over-current condition is detected, and automatically resumes when the current falls below the over-current threshold.

#### **Charge Under-Current Protection**

After the recharge, if the SRP-SRN voltage decreases below 5mV, the low side FET will be turned off for the rest of the switching cycle. During discontinuous conduction mode (DCM), the low side FET will only turn on for a short period of time when high side FET turn on every four times to provide refresh charge for the capacitor. This is important to prevent negative inductor current from causing any boost effect in which the input voltage increases as power is transferred from the battery to the input capacitors. This can lead to an over-voltage on the AVCC node and potentially cause damage to the system.

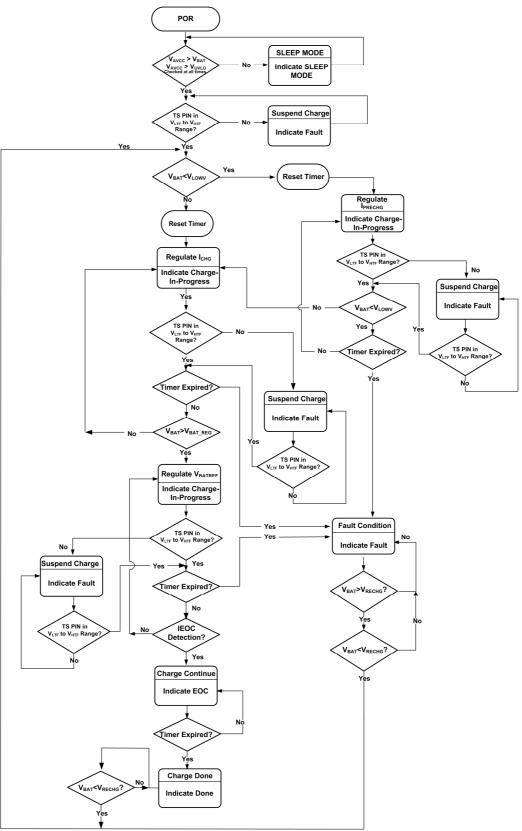

#### **Battery Detection**

For applications with removable battery packs, IC provides a battery absent detection scheme to reliably detect insertion or removal of battery packs. The battery detection routine runs on power up, or if battery voltage falls below recharge threshold voltage due to removing a battery or discharging a battery.

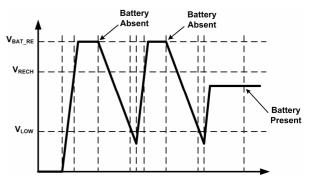

#### Figure 4.

Once the device has powered up, a 8-mA discharge current is applied to the SRN terminal. If the battery voltage falls below the LOWV threshold within 1 second, the discharge source is turned off, and the charger is turned on at low charge current (125mA). If the battery voltage gets up above the recharge threshold within 500ms, there is no battery present and the cycle restarts. If either the 500ms or 1 second timer time out before the respective thresholds are hit, a battery is detected and a charge cycle is initiated.

**Figure 5. Battery Detect Timing Diagram**

Care must be taken that the total output capacitance at the battery node is not so large that the discharge current source cannot pull the voltage below the LOWV threshold during the 1 second discharge time. The maximum output capacitances can be calculated according to the following equations:

$$C_{MAX} = \frac{I_{DISCH} \times t_{DISCH}}{4.1V - 2.9V}$$

(6)

Where  $C_{MAX}$  is the maximum output capacitance, IDISCH is the discharge current,  $t_{DISCH}$  is the discharge time.

#### **Battery Short Protection**

When SRN pin voltage is lower than 2V it is considered as battery short condition during charging period. The charger will shut down immediately for 1ms, then soft start back to the charging current the same as precharge current. This prevents high current may build in output inductor and cause inductor saturation when battery terminal is shorted during charging. The converter works in non-synchronous mode during battery short.

#### **Battery Over-Voltage Protection**

The converter will not allow the high-side FET to turn-on until the battery voltage goes below 102% of the regulation voltage. This allows one-cycle response to an over-voltage condition – such as occurs when the load is removed or the battery is disconnected. A total 6mA current sink from SRP/SRN to AGND allows discharging the stored output inductor energy that is transferred to the output capacitors. If battery over-voltage condition lasts for more than 30ms, charge is disabled.

#### **Temperature Qualification**

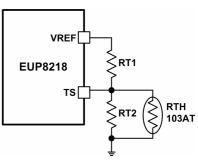

The controller continuously monitors battery temperature by measuring the voltage between the TS pin and AGND. A negative temperature coefficient thermistor (NTC) and an external voltage divider typically develop this voltage. The controller compares this voltage against its internal thresholds to determine if charging is allowed.

To initiate a charge cycle, the battery temperature must be within the  $V_{LTF}$  to  $V_{HTF}$  thresholds. If battery temperature is outside of this range, the controller

suspends charge and waits until the battery temperature is within the  $V_{LTF}$  to  $V_{HTF}$  range. During the charge cycle the battery temperature must be within the  $V_{LTF}$  to  $V_{TCO}$  thresholds. If battery temperature is outside of this range, the controller suspends charge and waits until the battery temperature is within the  $V_{LTF}$  to  $V_{HTF}$  range. The controller suspends charge by turning off the PWM charge MOSFETss. Figure 6 summarizes the operation.

| VREF             | TEMPERATURE RANGE<br>TO INITIATE CHARGE | TEMPERATURE RANGE<br>DURING A CHARGE CYCLE | EE        |  |  |  |

|------------------|-----------------------------------------|--------------------------------------------|-----------|--|--|--|

| , TAL            | CHARGE SUSPENDED                        | CHARGE SUSPENDED                           |           |  |  |  |

|                  |                                         | <br> V <sub>LT</sub><br>                   | 'F<br>IFH |  |  |  |

|                  | CHARGE at full C                        | <br> <br>  CHARGE at full C<br> <br>       |           |  |  |  |

| V <sub>HTF</sub> | CHARGE SUSPENDED                        | ן<br>ר                                     | TF        |  |  |  |

| AGND             |                                         | CHARGE SUSPENDED<br> <br>  AG              | GND       |  |  |  |

|                  | Figure 6.                               |                                            |           |  |  |  |

Assuming a 103AT NTC thermistor on the battery pack as shown in Figure 7, the values of RT1 and RT2 can be determined by using Equation 7 and Equation 8:

$$RT2 = \frac{V_{VREF} \times RTH_{COLD} \times RTH_{HOT} \times \left(\frac{1}{V_{LTF}} - \frac{1}{V_{TCO}}\right)}{RTH_{HOT} \times \left(\frac{V_{VREF}}{V_{TCO}} - 1\right) - RTH_{COLD} \times \left(\frac{V_{VREF}}{V_{LTF}} - 1\right)}$$

(7)

$$RT1 = \frac{\frac{V_{VREF}}{V_{LTF}} - 1}{\frac{1}{RT2} + \frac{1}{RTH_{COLD}}}$$

(8)

Select 0°C to 45°C range for Li-ion or Li-polymer battery,

$RTH_{COLD} = 27.28 \text{ k}\Omega$  $RTH_{HOT} = 4.911 \text{ k}\Omega$  $RT1 = 5.23 \text{ k}\Omega$  $RT2 = 30.1 \text{ k}\Omega$

After select closest standard resistor value, by calculating the thermistor resistance at temperature threshold, the final temperature range can be gotten from thermistor datasheet temperature-resistance table.

**Figure 7. TS Resistor Network**

# MOSFET Short Circuit and Inductor Short Circuit Protection

The IC has a short circuit protection feature. Its cycle-by-cycle current monitoring feature is achieved through monitoring the voltage drop across Rdson of the MOSFETs. The charger will be latched off, but the RevFET keep on to power the system. The only way to reset the charger from latch-off status is remove adapter then plug adapter in again. Meanwhile, STAT is blinking to report the fault condition.

#### **Thermal Regulation and Shutdown Protection**

The TQFN package has low thermal impedance, which provides good thermal conduction from the silicon to the ambient, to keep junctions temperatures low. The internal thermal regulation loop will fold back the charge current to keep the junction temperature from exceeding 120°C. As added level of protection, the charger converter turns off and self-protects whenever the junction temperature exceeds the TSHUT threshold of 150°C.

The charger stays off until the junction temperature falls below  $130^{\circ}$ C.

#### **Timer Fault Recovery**

The IC provides a recovery method to deal with timer fault conditions. The following summarizes this method:

Condition 1: The battery voltage is above the recharge threshold and a timeout fault occurs.

Recovery Method: The timer fault will clear when the battery voltage falls below the recharge threshold, and battery detection will begin. A POR or taking ISET below 40mV will also clear the fault.

Condition 2: The battery voltage is below the recharge threshold and a timeout fault occurs.

Recovery Method: Under this scenario, the IC applies the fault current to the battery. This small current is used to detect a battery removal condition and remains on as long as the battery voltage stays below the recharge threshold. If the battery voltage goes above the recharge threshold, the IC disabled the fault current and executes the recovery method described in Condition 1. A POR or taking ISET below 40mV will also clear the fault.

#### **Charge Status Outputs**

The open-drain STAT outputs indicate various charger operations as listed in Table 1. These status pins can be used to drive LEDs or communicate with the host processor. Note that OFF indicates that the open-drain transistor is turned off.

| Charge State                                                                                                            | STAT  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|

| Charge in progress (including recharging)                                                                               | ON    |  |  |  |

| Charge complete, Sleep mode, Charge disabled                                                                            | OFF   |  |  |  |

| Charge suspend, Input over-voltage, Battery<br>over-voltage, timer fault, , battery absent,<br>OTP, TS-FAULT, OCP_HSFET | BLINK |  |  |  |

#### Table 1. STAT Pin Definition

#### **USB/Charger Detection**

EUP8218 sets the FLAG1 pin to high or low to indicate whether a standard USB device or a charger is connected to the USB port. The D- line connects a 5M pull-down resistor to ground and D+ line connects a 1M push-up resistor to VREF.

When a condition exists where a charger is plugged into the USB port (D+/D- short), the voltage divider of 1M and 5M comes out a voltage of 2.75V on the D+/Dinputs. This makes FLAG1 low, indicating a charger is connected to USB port. In this condition, M0 (as shown in Figure1 at page2) is not turn on, and the input current limit set by ACSET shall not change.

In a condition where a standard USB device is plugged into the USB port, the D+ input is pull up to VREF and D- input is pull low, which makes FLAG1 high. In this condition, M0 is turn on, the voltage of ACSET changes accordingly. The input limit current is changed to a predetermined USB2 or USB3 limit current which can be set by Resistor R5B (as shown in Figure1 at Page 2).

# Inductor, Capacitor, and Sense Resistor Selection Guidelines

Table 2 provides a summary of typical LC components for various charge currents.

Table 2. Typical Values as a Function of Charge Current

| Charge Current     | 1A    | 2A    | 3A    | 4A    |

|--------------------|-------|-------|-------|-------|

| Output inductor L  | 6.8µH | 6.8µH | 3.3µH | 2.2µH |

| Output capacitor C | 10µF  | 20µF  | 20µF  | 30µF  |

#### **APPLICATION INFORMATION**

#### **Inductor Selection**

The EUP8218 has a 500-kHz switching frequency to allow the use of small inductor and capacitor values. Inductor saturation current should be higher than the charging current ( $I_{CHG}$ ) plus half the ripple current ( $I_{RIPPLE}$ ):

$$I_{SAT} \ge I_{CHG} + (1/2)I_{RIPPLE}$$

(9)

Inductor ripple current depends on input voltage ( $V_{IN}$ ), duty cycle (D =  $V_{OUT}/V_{IN}$ ), switching frequency (fs), and inductance (L):

$$I_{RIPPLE} = \frac{V_{IN} \times D \times (1 - D)}{f_S \times L}$$

(10)

The maximum inductor ripple current happens with D = 0.5 or close to 0.5. Usually inductor ripple is designed in the range of 20% to 40% of the maximum charging current as a trade-off between inductor size and efficiency for a practical design.

#### **Inductor Capacitor**

The input capacitor should have enough ripple current rating to absorb input switching ripple current. The worst case RMS ripple current is half of the charging current when duty cycle is 0.5. If the converter does not operate at 50% duty cycle, then the worst case capacitor RMS current ICIN occurs where the duty cycle is closest to 50% and can be estimated by the following equation:

$$I_{\text{CIN}} = I_{\text{CHG}} \times \sqrt{D \times (1 - D)}$$

(11)

A low ESR ceramic capacitor such as X7R or X5R is preferred for the input decoupling capacitor and should be placed as close as possible to the drain of the high-side MOSFET and source of the low-side MOSFET. The voltage rating of the capacitor must be higher than the normal input voltage level. A 25V rating or higher capacitor is preferred for a 15V input voltage. A  $20\mu$ F capacitance is suggested for a typical 3A to 4A charging current.

#### **Output Capacitor**

The output capacitor also should have enough ripple current rating to absorb output switching ripple current. The output capacitor RMS current ICOUT is given as:

$$I_{\text{COUT}} = \frac{I_{\text{RIPPLE}}}{2 \times \sqrt{3}} \approx 0.29 \times I_{\text{RIPPLE}} \quad (12)$$

The output capacitor voltage ripple can be calculated as follows:

$$\Delta V_{\rm O} = \frac{V_{\rm OUT}}{8 {\rm LCfs}^2} \left( 1 - \frac{V_{\rm OUT}}{V_{\rm IN}} \right)$$

(13)

At certain input/output voltages and switching frequencies, the voltage ripple can be reduced by increasing the output filter LC.

The EUP8218 has an internal loop compensator. To achieve good loop stability, the resonant frequency of the output inductor and output capacitor should be designed between 15 kHz and 25 kHz. The preferred ceramic capacitor has a 25V or higher rating, X7R or X5R.

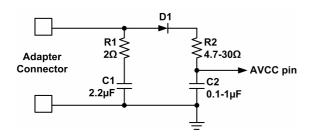

#### **Input Filter Design**

During adapter hot plug-in, the parasitic inductance and the input capacitor from the adapter cable form a second order system. The voltage spike at the AVCC pin may be beyond the IC maximum voltage rating and damage the IC. The input filter must be carefully designed and tested to prevent an over-voltage event on the AVCC pin.

There are several methods to damping or limiting the over-voltage spike during adapter hot plug-in. An electrolytic capacitor with high ESR as an input capacitor can damp the over-voltage spike well below the IC maximum pin voltage rating. A high current capability TVS Zener diode can also limit the over-voltage level to an IC safe level. However, these two solutions may not be lowest cost or smallest size.

A cost effective and small size solution is shown in Figure 8. R1 and C1 are composed of a damping RC network to damp the hot plug-in oscillation. As a result, the over-voltage spike is limited to a safe level. D1 is used for reverse voltage protection for the AVCC pin. C2 is the AVCC pin decoupling capacitor and it should be placed as close as possible to the AVCC pin. R2 and C2 form a damping RC network to further protect the IC from high dv/dt and high voltage spike. The C2 value should be less than the C1 value so R1 can dominant the equivalent ESR value to get enough damping effect for hot plug-in. R1 and R2 must be sized enough to handle in-rush current power loss according to the resistor manufacturer's datasheet. The filter component values always need to be verified with a real application and minor adjustments may be needed to fit in the real application circuit.

**Figure 8. Input Filter**

#### Input RevFET

N-type MOSFETs are used as input RevFET(Q1) for better cost effective and small size solution, as shown in Figure 9. There is a surge current during Q1 turn-on period when a valid adapter is inserted. Decreasing the turn-on speed of Q1 can limit this surge current in desirable range by selecting a MOSFET with relative bigger C<sub>GD</sub> and/or C<sub>GS</sub>. At the case Q1 turn on too fast, we need add external C<sub>GD</sub> and/or C<sub>GS</sub>. For example, 4.7nF C<sub>GD</sub> and 47nF C<sub>GS</sub> are adopted on EVM while using NexFET CSD17313 as Q1.

**Figure 9. Input RevFET**

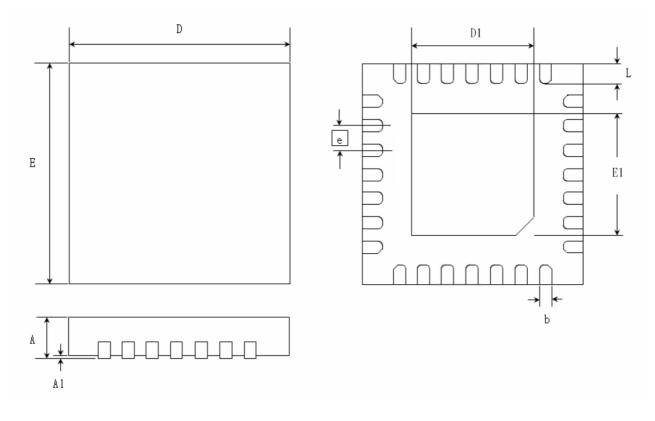

# **Preliminary**

# **Packaging Information**

| SYMBOLS | MILLIMETERS |      | INCHES    |       |  |

|---------|-------------|------|-----------|-------|--|

|         | MIN.        | MAX. | MIN.      | MAX.  |  |

| А       | 0.70        | 0.80 | 0.028     | 0.031 |  |

| A1      | 0.00        | 0.05 | 0.000     | 0.002 |  |