# **Primary Side Regulation**

# Off-Line PWM Controllers with Integrated Power MOSFET

# STR5A100D Series

# **General Descriptions**

The STR5A100D series is power IC with primary side regulation for switching power supplies, incorporating a sense MOSFET and a current mode PWM controller IC.

Employing the Primary Side Regulation, the product achieves power supply systems with few external components. Including a startup circuit and a standby function in the controller, the product achieves the low standby power by the automatic switching between the PWM operation in normal operation and the burst-oscillation under light load conditions. The rich set of protection features helps to realize low component counts, and high performance-to-cost power supply.

#### **Features**

- Primary Side Regulation

- Constant Voltage (CV), Constant Current (CC) Control

- Auto Standby Function

No Load Power Consumption < 30mW</li>

- Operation Mode

- Normal Operation ------PWM Mode

- · Light Load Operation ------Green-Mode

- · Standby------ Burst Oscillation Mode

- Build-in Startup Circuit (reducing power consumption at standby operation, shortening the startup time)

- Current Mode Type PWM Control

- Random Switching Function

- Leading Edge Blanking Function

- Soft Start Function (reducing the stress of power MOSFET and secondary side rectifier diode at startup)

- Protections

Overcurrent Protection (OCP)------------Pulse-by-Pulse Overvoltage Protection (OVP) ------ Auto-Restart Thermal Shutdown Protection (TSD) ----- Auto-Restart

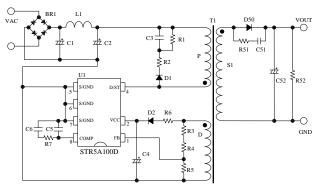

# **Typical Application Circuit**

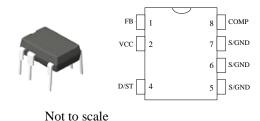

## Package DIP8

## Lineup

• Electrical Characteristics  $V_{D/ST}(max.) = 730 \text{ V}$

$f_{OSC(AVG)}(typ.) = 65 \text{ kHz}$

| Products  | R <sub>DS(ON)</sub> (max.) | $I_{\mathrm{DLIM(H)}}$ |

|-----------|----------------------------|------------------------|

| STR5A162D | 24.6 Ω                     | 0.285 A                |

| STR5A164D | 13 Ω                       | 0.41 A                 |

Output Power, P<sub>OUT</sub>\*

| <b>D</b>  | Ada    | pter          | Open frame |               |  |

|-----------|--------|---------------|------------|---------------|--|

| Products  | AC230V | AC85<br>~265V | AC230V     | AC85<br>~265V |  |

| STR5A162D | 4 W    | 3.5 W         | 5 W        | 4.5 W         |  |

| STR5A164D | 6.0 W  | 5.5 W         | 8.5 W      | 7 W           |  |

<sup>\*</sup> The EI-16 core of transformer is assumed. The output power is based on the thermal ratings, and the peak output power can be 120 to 140 % of the value stated here. At low output voltage, small core and short ON Duty, the output power may be less than the value stated here.

# **Applications**

- · White Goods

- Other SMPS

# **CONTENTS**

| Ger  |                                                                                                          | escriptions                               |                                                 |  |  |  |  |  |  |

|------|----------------------------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------|--|--|--|--|--|--|

| 1.   | Absolute Maximum Ratings 3                                                                               |                                           |                                                 |  |  |  |  |  |  |

| 2.   | Recommended Operating Conditions 3                                                                       |                                           |                                                 |  |  |  |  |  |  |

| 3.   | Electri                                                                                                  | cal Characteristics                       | 3                                               |  |  |  |  |  |  |

| 4.   | Perfor                                                                                                   | mance Curves                              | 5                                               |  |  |  |  |  |  |

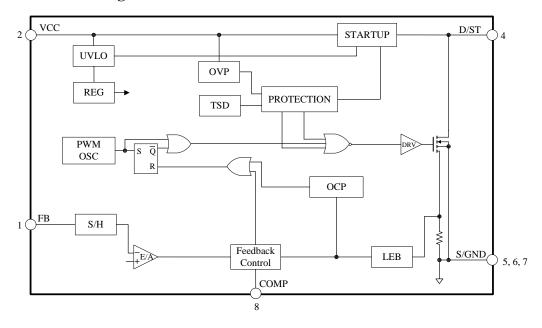

| 5.   | Functi                                                                                                   | onal Block Diagram                        | 6                                               |  |  |  |  |  |  |

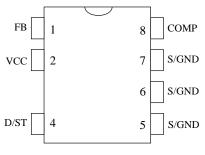

| 6.   | Pin Co                                                                                                   | onfiguration Definitions                  | 6                                               |  |  |  |  |  |  |

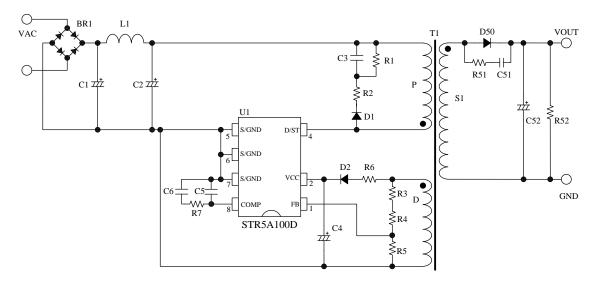

| 7.   | Typica                                                                                                   | ll Application Circuit                    | 6                                               |  |  |  |  |  |  |

| 8.   | Packag                                                                                                   | ge Outline                                | 7                                               |  |  |  |  |  |  |

| 9.   | Marki                                                                                                    | ng Diagram                                | 7                                               |  |  |  |  |  |  |

|      | 10.1<br>10.2<br>10.3<br>10.4<br>10.5<br>10.6<br>10.7<br>10.8<br>10.9<br>10.10<br>10.11<br>10.12<br>10.13 | Startup Operation                         | 8<br>8<br>9<br>10<br>11<br>11<br>11<br>12<br>12 |  |  |  |  |  |  |

| 11.  | Design<br>11.1                                                                                           | Notes1<br>External Components1            |                                                 |  |  |  |  |  |  |

|      |                                                                                                          | PCB Trace Layout and Component Placement1 |                                                 |  |  |  |  |  |  |

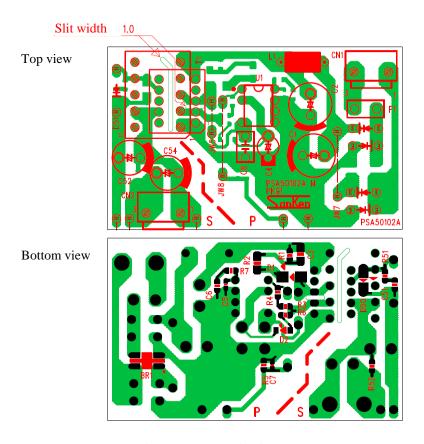

| 12.  | Patteri                                                                                                  | n Layout Example1                         | <b>7</b>                                        |  |  |  |  |  |  |

| 13.  | 3. Reference Design of Power Supply18                                                                    |                                           |                                                 |  |  |  |  |  |  |

| OP   | OPERATING PRECAUTIONS20                                                                                  |                                           |                                                 |  |  |  |  |  |  |

| TN/I | рорти                                                                                                    | ANT NOTES                                 | 1                                               |  |  |  |  |  |  |

# 1. Absolute Maximum Ratings

• The polarity value for current specifies a sink as "+," and a source as "-," referencing the IC.

• Unless otherwise specified,  $T_A$  is 25 °C, 5 pin = 6 pin = 7 pin

| Parameter                        | Symbol              | Test Conditions                                | Pins  | Rating        | Units | Notes  |

|----------------------------------|---------------------|------------------------------------------------|-------|---------------|-------|--------|

| FB Pin Voltage                   | $V_{FB}$            |                                                | 1 – 5 | 7.0           | V     |        |

| FB Pin Source Current            | ${ m I}_{ m FB}$    | Single pulse                                   | 1 – 5 | - 10          | mA    |        |

| VCC Pin Voltage                  | $V_{CC}$            |                                                | 2-5   | -0.3 to 32    | V     |        |

| D/ST Pin Voltage                 | $V_{\mathrm{D/ST}}$ |                                                | 4 – 5 | - 0.3 to 730  | V     |        |

| Drain Peak Current               | Ţ                   | Positive: Single pulse<br>Negative: Within 2µs | 4-5   | - 0.2 to 0.69 | A     | 5A162D |

| Diam Feak Current                | $I_{DP}$            | of pulse width                                 |       | - 0.2 to 0.97 | A     | 5A164D |

| COMP Pin Voltage                 | $V_{COMP}$          |                                                | 8 - 5 | - 0.3 to 7.0  | V     |        |

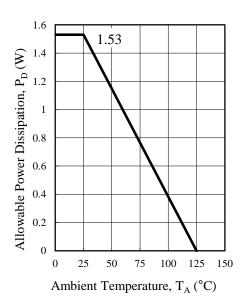

| Power Dissipation <sup>(1)</sup> | $P_D$               | (2)                                            | _     | 1.53          | W     |        |

| Operating Ambient Temperature    | $T_{OP}$            |                                                | _     | - 40 to 125   | °C    |        |

| Storage Temperature              | $T_{stg}$           |                                                | _     | - 40 to 125   | °C    |        |

| Junction Temperature             | $T_{j}$             |                                                | _     | 150           | °C    |        |

<sup>(1)</sup> Refer to MOSFET Temperature versus Power Dissipation Curve

# 2. Recommended Operating Conditions

Recommended operating conditions means the operation conditions maintained normal function shown in electrical characteristics.

| Parameter                     | Symbol                | Min.  | Max. | Units | Notes |

|-------------------------------|-----------------------|-------|------|-------|-------|

| D/ST Pin Voltage in Operation | $V_{\text{D/ST(OP)}}$ | - 0.3 | 584  | V     |       |

| VCC Pin Voltage in Operation  | $V_{CC(OP)}$          | 11    | 27   | V     |       |

# 3. Electrical Characteristics

• The polarity value for current specifies a sink as "+," and a source as "-," referencing the IC.

• Unless otherwise specified,  $T_A$  is 25 °C,  $V_{D/ST} = 10 \text{ V}$ , pin = 6 pin = 7 pin

| Parameter                            | Symbol               | Test<br>Conditions                                        | Pins  | Min.  | Тур.  | Max.  | Units | Notes |  |

|--------------------------------------|----------------------|-----------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| Power Supply Startup Operation       |                      |                                                           |       |       |       |       |       |       |  |

| Operation Start Voltage              | V <sub>CC(ON)</sub>  |                                                           | 2 - 5 | 13.6  | 15.0  | 16.6  | V     |       |  |

| Operation Stop Voltage               | V <sub>CC(OFF)</sub> |                                                           | 2-5   | 7.3   | 8.1   | 8.9   | V     |       |  |

| Circuit Current in Operation         | I <sub>CC(ON)</sub>  | $V_{CC} = 12 \text{ V}$                                   | 2-5   | _     | _     | 2.5   | mA    |       |  |

| Startup Circuit Operation<br>Voltage | V <sub>STARTUP</sub> | $V_{CC} = 13.5 \text{ V}$                                 | 4 – 5 | 19    | 29    | 39    | V     |       |  |

| Startup Current                      | I <sub>STARTUP</sub> | $V_{CC} = 13.5 \text{ V} $<br>$V_{D/ST} = 100 \text{ V} $ | 2-5   | - 3.7 | - 2.1 | - 0.9 | mA    |       |  |

| PWM Operation                        |                      |                                                           |       |       |       |       |       |       |  |

| Average Switching Frequency          | $f_{OSC(AVG)} \\$    | $V_{COMP} = 5.5 \text{ V}$                                | 4 – 5 | 57    | 65    | 73    | kHz   |       |  |

| Frequency Modulation Deviation       | Δf                   |                                                           | 4 – 5 | _     | 2.8   | _     | kHz   |       |  |

<sup>(2)</sup> When embedding this hybrid IC onto the printed circuit board (cupper area in a 15mm×15mm)

# STR5A100D Series

| Parameter                                                  | Symbol                | Test<br>Conditions                                                | Pins  | Min.  | Тур.  | Max.  | Units | Notes  |

|------------------------------------------------------------|-----------------------|-------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|

| Feedback Reference Voltage                                 | V <sub>FB(REF)</sub>  |                                                                   | 1 – 5 | 2.45  | 2.50  | 2.55  | V     |        |

| Feedback Current                                           | $V_{FB(OP)}$          | $V_{FB} = 2.4 \text{ V}$                                          | 1 – 5 | - 2.4 | - 0.8 | -     | μΑ    |        |

| Minimum Sampling Time                                      | $t_{\mathrm{FBMS}}$   |                                                                   | 1 – 5 | _     | _     | 2.2   | μs    |        |

| Standby Operation Threshold                                | N/                    |                                                                   | 0. 5  | 1.7   | 2.3   | 3.1   | V     | 5A162D |

| Voltage                                                    | $V_{STBOP}$           |                                                                   | 8 – 5 | 1.3   | 2.0   | 2.7   | V     | 5A164D |

| Standby Operation Cycle                                    | $T_{STBOP}$           |                                                                   | 4 – 5 | _     | 1.3   | _     | ms    |        |

| Maximum ON Duty                                            | $D_{MAX}$             |                                                                   | 4 – 5 | 50    | 57    | 64    | %     |        |

| COMP Pin Sink Current                                      | I <sub>COMP(SI)</sub> | $V_{COMP} = 5.5 \text{ V}$                                        | 8-5   | _     | 4.5   | _     | μΑ    |        |

| COMP Pin Source Current                                    | I <sub>COMP(SO)</sub> | $V_{COMP} = 2.5 \text{ V}$                                        | 8-5   | _     | - 4.5 | _     | μΑ    |        |

| Error Amplifier Conductance                                | gm                    | $V_{FB} = 2.4V$<br>to 2.6V                                        | _     | _     | 16    | _     | μS    |        |

| <b>Protection Function</b>                                 |                       |                                                                   |       |       |       |       |       |        |

| Leading Edge Blanking Time                                 | $t_{ m BW}$           |                                                                   | _     | _     | 250   | _     | ns    |        |

| Drain Current Limit<br>Compensation ON Duty <sup>(1)</sup> | $D_{DPC}$             |                                                                   | _     | _     | 27    | _     | %     |        |

| Drain Current Limit                                        | Ţ                     |                                                                   | 4 5   | 0.250 | 0.285 | 0.320 | A     | 5A162D |

| (ON Duty $\geq 27 \%$ )                                    | $I_{DLIM(H)}$         |                                                                   | 4 – 5 | 0.36  | 0.41  | 0.46  | A     | 5A164D |

| Drain Current Limit                                        | 7                     |                                                                   | 4 5   | 0.210 | 0.242 | 0.280 | A     | 5A162D |

| (ON Duty = 0 %)                                            | $I_{DLIM(L)}$         |                                                                   | 4 – 5 | 0.29  | 0.34  | 0.39  | A     | 5A164D |

| OVP Threshold Voltage                                      | V <sub>CC(OVP)</sub>  |                                                                   | 2-5   | 27.5  | 29.3  | 31.3  | V     |        |

| Constant Current Control Delay<br>Time                     | t <sub>CCD</sub>      |                                                                   | 4 – 5 | _     | 90    | _     | ms    |        |

| Thermal Shutdown Operating<br>Temperature <sup>(1)</sup>   | $T_{j(TSD)}$          |                                                                   | _     | 135   | _     | _     | °C    |        |

| Thermal Shutdown Hysteresis <sup>(1)</sup>                 | $T_{j(TSDHYS)}$       |                                                                   | _     | _     | 70    | -     | °C    |        |

| Power MOSFET                                               |                       |                                                                   |       |       |       |       |       |        |

| Drain Leakage Current                                      | $I_{DSS}$             | $T_{\rm j} = 125~{\rm ^{\circ}C}$<br>$V_{\rm D/ST} = 584~{\rm V}$ | 4 – 5 | _     | _     | 50    | μA    |        |

| On Resistance                                              | D                     | $I_D = 28.5 \text{ mA}$                                           | 4 - 5 | _     | 21.0  | 24.6  | Ω     | 5A162D |

| On Resistance                                              | $R_{DS(ON)}$          | $I_D = 41 \text{ mA}$                                             | 4 – 5 | _     | 11    | 13    | Ω     | 5A164D |

| Switching Time                                             | $t_{\mathrm{f}}$      |                                                                   | 4 – 5 | _     | _     | 250   | ns    |        |

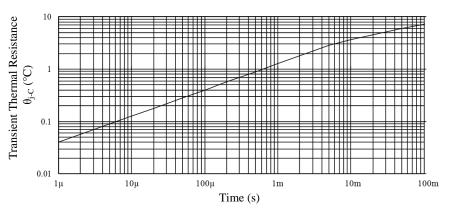

| Thermal Characteristics                                    |                       |                                                                   |       |       |       |       |       |        |

| Thermal Resistance Junction to Frame (1)(2)                | $\theta_{\text{j-F}}$ |                                                                   | _     | _     | _     | 20    | °C/W  |        |

| Thermal Resistance Junction to Case <sup>(1)(3)</sup>      | $\theta_{\text{j-C}}$ |                                                                   | -     | _     | _     | 24    | °C/W  |        |

<sup>(1)</sup> Design assurance

(2) Frame temperature (T<sub>F</sub>) measured at the root of the 6 pin (S/GND)

(3) Case temperature (T<sub>C</sub>) measured at the center of the case top surface

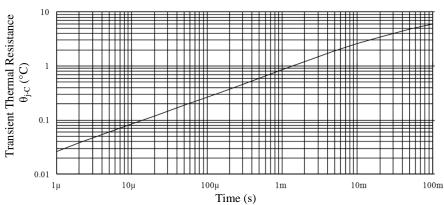

# 4. Performance Curves

Figure 4-3 Ambient Temperature versus Power Dissipation Curve

Figure 4-2 STR5A162D Transient Thermal Resistance Curve

Figure 4-2 STR5A164D Transient Thermal Resistance Curve

# 5. Functional Block Diagram

# 6. Pin Configuration Definitions

| Pin | Name  | Descriptions                                                                                 |

|-----|-------|----------------------------------------------------------------------------------------------|

| 1   | FB    | Input of constant voltage control signal                                                     |

| 2   | VCC   | Power supply voltage input for Control Part and input of Overvoltage Protection (OVP) signal |

| 3   | -     | (Pin removed)                                                                                |

| 4   | D/ST  | MOSFET Drain and input of startup current                                                    |

| 5   |       |                                                                                              |

| 6   | S/GND | MOSFET Source and ground                                                                     |

| 7   |       |                                                                                              |

| 8   | COMP  | Input of phase compensation                                                                  |

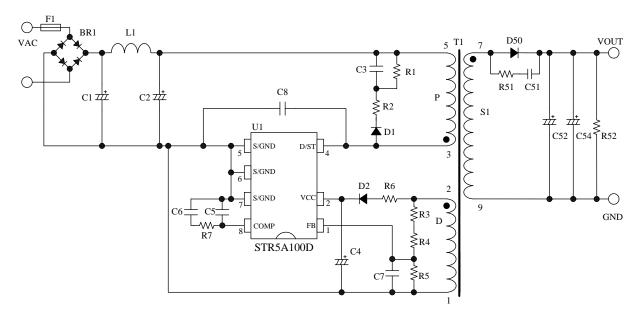

# 7. Typical Application Circuit

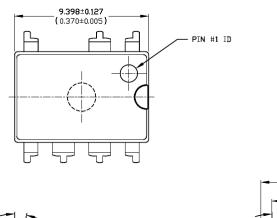

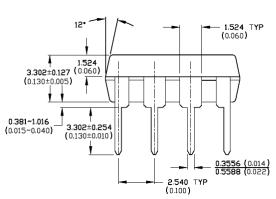

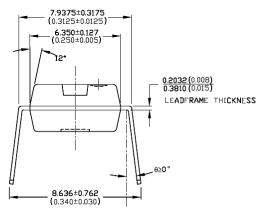

# 8. Package Outline

DIP8

# **NOTES:**

- 1) Unit: mm (inch)

- 2) Controlling dimensions are in inches; millimeter dimensions are for reference only

- 3) Pb-free. Device composition compliant with the RoHS directive

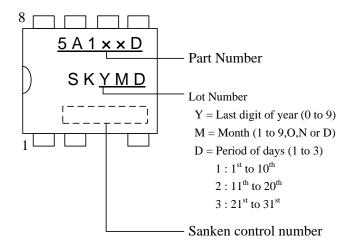

# 9. Marking Diagram

# 10.Operational Description

- All of the parameter values used in these descriptions are typical values, unless they are specified as minimum or maximum.

- With regard to current direction, "+" indicates sink current (toward the IC) and "-" indicates source current (from the IC).

## 10.1 **Startup Operation**

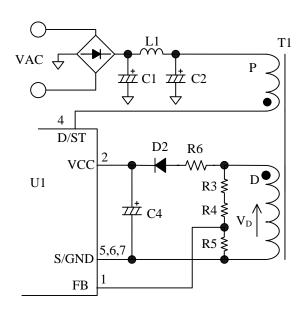

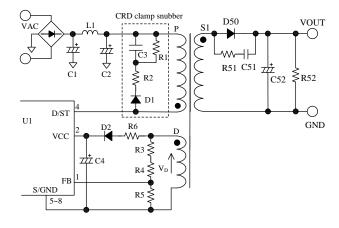

Figure 10-1 shows the VCC pin peripheral circuit.

The IC incorporates the startup circuit. The circuit is connected to D/ST pin. When D/ST pin voltage reaches to Startup Circuit Operation Voltage  $V_{STARTUP} = 29 \text{ V}$ , the startup circuit starts operation.

During the startup process, the constant current,  $I_{STARTUP} = -2.1$  mA, charges C4 at VCC pin. When VCC pin voltage increases to  $V_{CC(ON)} = 15.0$  V, the control circuit starts switching operation. After switching operation begins, the startup circuit turns off automatically so that its current consumption becomes zero.

The approximate startup time of IC,  $t_{START,}$  is calculated as follows:

$$t_{START} = C4 \times \frac{V_{CC(ON)} - V_{CC(INT)}}{|I_{STARTUP}|}$$

(1)

where,

$t_{START}$ : Startup time of IC in second  $V_{CC(INT)}$ : Initial voltage on VCC pin in V

Figure 10-1 VCC pin peripheral circuit

# 10.2 Undervoltage Lockout (UVLO)

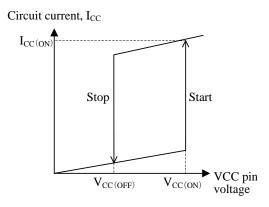

Figure 10-2 shows the relationship of VCC pin voltage and circuit current  $I_{CC}.$  When VCC pin voltage increases to  $V_{CC(ON)}=15.0$  V, the control circuit starts switching operation and the circuit current  $I_{CC}$  increases. When VCC pin voltage decreases to  $V_{CC(OFF)}=8.1$  V, the control circuit stops operation by UVLO (Undervoltage Lockout) circuit, and reverts to the state before startup.

Figure 10-2 Relationship between VCC pin voltage and  $I_{CC}$

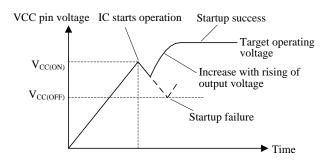

# 10.3 **Auxiliary Winding**

Figure 10-3 shows VCC voltage behavior during the startup period. When VCC pin voltage increases to  $V_{CC(ON)} = 15.0 \text{ V}$  at startup, the IC starts the operation. Then circuit current increases and VCC pin voltage decreases. Since the Operation Stop  $V_{CC(OFF)} = 8.1 \text{ V}$  is low, the auxiliary winding voltage reaches to setting value before VCC pin voltage decreases to V<sub>CC(OFF)</sub>. Thus control circuit continues the operation. The voltage from the auxiliary winding D in Figure 10-1 becomes a power source to the control circuit in operation. The approximate value of auxiliary winding voltage is about 12 V to 16 V, taking account of the winding turns of D winding so that VCC pin voltage satisfies Equation (2) within the specification of input and output voltage variation of power supply.

Figure 10-3 VCC pin voltage during startup period

$$V_{CC(OFF)}(max.) < V_{CC} < V_{CC(OVP)}(min.)$$

$$\Rightarrow$$

8.9 (V) < V<sub>CC</sub> < 27.5 (V) (2)

In addition, the auxiliary winding voltage  $V_{\text{D}}$  is determined as follows:

$$V_{D} = \frac{N_{D}}{N_{S}} \times (V_{OUT} + V_{F})$$

(3)

where,

$N_D$ : Turns of auxiliary winding of transformer

N<sub>S</sub>: Turns of secondary side winding of transformer

V<sub>OUT</sub>: Output voltage

$V_{\text{F}}$ : Forward drop voltage of secondary side rectifier diode D50

When VCC pin voltage reaches to  $V_{\text{CC(OFF)}}$  and a startup failure occurs as shown in Figure 10-3, increase the C4 value. Since the larger capacitance causes the longer startup time of IC, it is necessary to check and adjust the startup process based on actual operation in the application.

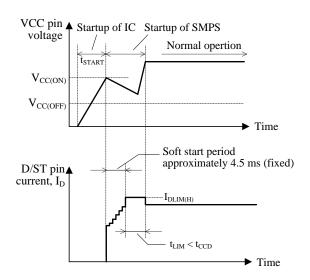

#### 10.4 **Soft Start Function**

Figure 10-4 shows the behavior of VCC pin voltage and drain current during the startup period.

The IC activates the soft start circuitry during the startup period. Soft start time is fixed to around 4.5 ms. During the soft start period, over current threshold is increased step-wisely (7 steps). This function reduces the voltage and the current stress of MOSFET and secondary side rectifier diode.

Figure 10-4 V<sub>CC</sub> and I<sub>D</sub> behavior during startup

Since the Leading Edge Blanking Function (refer to Section 10.8) is deactivated during the soft start period, there is the case that ON time is less than the leading edge blanking time,  $t_{\rm BW} = 250~{\rm ns}$ .

After the soft start period, D/ST pin current,  $I_D$ , is limited by the Drain Current Limit,  $I_{DLIM(H)}$ , until the output voltage increases to the target operating voltage. This period is given as  $t_{LJM}$ .

In case  $t_{LIM}$  is longer than the CC Operation Delay Time,  $t_{CCD}$ , the output power is limited by the CC mode.

Thus, it is necessary to adjust the value of output capacitor and the turn ratio of auxiliary winding D so that the  $t_{LIM}$  is less than  $t_{CCD} = 90$  ms.

# 10.5 Primary Side Regulation (PSR)

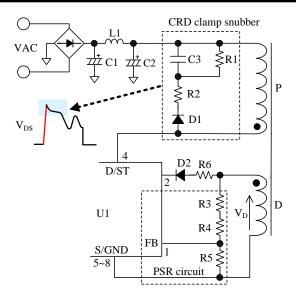

The IC is for Primary Side Regulation (PSR). In PSR, the auxiliary winding voltage is divided by resistors (R3, R4 and R5) and is induced into FB pin as shown in Figure 10-5. The constant voltage output control is achieved by using FB pin voltage.

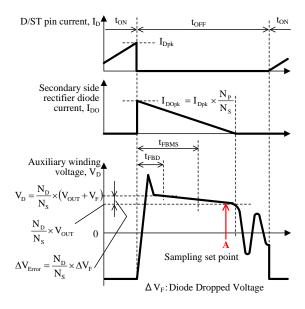

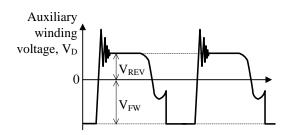

Figure 10-6 shows the detection timing of auxiliary winding voltage  $V_D$ . When the power MOSFET turns off, the energy stored in transformer is provided to secondary side of the circuit. Then the current  $I_{DO}$  flows through the secondary side rectifier diode. After the transfer of energy, power MOSFET continues off state and the free oscillation of  $V_D$  starts. During the free oscillation period,  $I_{DO}$  becomes zero.

The feedback signal is generated by sampling the shoulder of  $V_D$  waveform (point A in Figure 10-6). Thus the effect of  $V_F$  is minimized.

The Minimum Sampling Time,  $t_{FBMS}$ , is 2.2  $\mu$ s (max.). Since the sampling time becomes the shortest in burst oscillation mode (refer to Section 10.10), the sampling time should be more than  $t_{FBMS}$  (shown in Figure 10-6).

The ideal waveform of auxiliary winding voltage  $V_D$  is shown in Figure 10-6. The  $V_D$  waveform depends on the waveform of the primary winding P voltage. In order to reduce the transient surge of  $V_D$  waveform, a clamp snubber circuit of a capacitor-resistor-diode (CRD) combination should be added on the primary winding P as shown in Figure 10-5.

In order to improve the accuracy of  $V_D$  waveform sampling, the IC has sampling delay time,  $t_{FBD}$ , so that the surge component of the waveform at the turning off of power MOSFET is not sampled.

In case that the width of the surge component is longer than  $t_{FBD}=0.9~\mu s$ , the width should be adjusted to be under  $t_{FBD}$ . It is achieved by adjusting the value of R1 and C3 and by reducing the peak and width of the surge component.

In addition, in order to realize the ideal  $V_D$  waveform shown in Figure 10-6, add the resistor R2 in series with the diode of CRD circuit to suppress the ringing of the waveform.

Figure 10-5 FB pin peripheral circuit

Figure 10-6 Detection timing of auxiliary winding voltage

#### 10.6 Constant Voltage (CV) Control

The IC achieves the constant voltage (CV) control of the power supply output by using the peak-current-mode control method, which enhances the response speed and provides the stable operation.

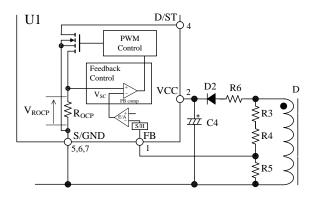

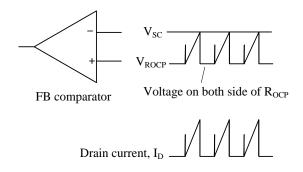

The IC controls the peak value of the voltage of build-in sense resistor ( $V_{ROCP}$ ) to be close to target voltage ( $V_{SC}$ ), comparing  $V_{ROCP}$  with  $V_{SC}$  by internal FB comparator. Feedback Control circuit receives the sampling voltage which is the reversed auxiliary winding voltage by using error amplifier (refer to Figure 10-7 and Figure 10-8)

• Light Load Conditions

The FB pin voltage increases with the increase of the

output voltage when the output load becomes light. Accordingly, the output voltage of internal error amplifier (target voltage  $V_{SC}$ ) decreases. As a result, the peak value of  $V_{ROCP}$  is controlled to be lower so that the peak of the drain current decreases. This control prevents the output voltage from increasing.

#### · Heavy Load Conditions

The control circuit performs reverse operations to the former. The target voltage  $V_{SC}$  of internal comparator becomes higher and the peak drain current increases. This control prevents the output voltage from decreasing.

Figure 10-7 FB pin peripheral circuit

Figure 10-8 Drain current I<sub>D</sub> and FB comparator in steady operation

#### 10.7 Constant Current (CC) Control

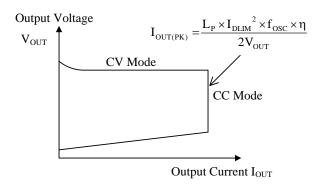

The IC operates in Constant Current (CC) Control when output current reaches to constant load and the state continues for more than the Constant Current Control Delay Time,  $t_{\rm CCD} = 90$  ms. In case the IC is in discontinuous operation, the CV/CC characteristic is as shown in Figure 10-9.

When output current reaches to constant load, MOSFET drain current is limited to the Drain Current Limit  $I_{DLIM(H)}$ . When the output voltage becomes low, the CC Control is maintained by lowering the oscillation frequency  $f_{OSC}$ . When the output voltage becomes low, the FB pin voltage becomes low. When FB pin voltage

decreases to about 1.6 V or less, the IC is stops oscillation and restarts. The IC repeats the intermittent oscillation operation until the FB pin voltage keeps about 1.6 V or more after the output voltage increases.

Figure 10-9 CV/CC characteristics

# 10.8 Leading Edge Blanking Function

The IC uses the peak-current-mode control method for the constant voltage control of output.

In peak-current-mode control method, there is a case that the power MOSFET turns off due to unexpected response of FB comparator or overcurrent protection circuit (OCP) to the steep surge current in turning on a power MOSFET.

In order to prevent this operation, Leading Edge Blanking Time,  $t_{\rm BW} = 250$  ns is built-in.

In the period of  $t_{BW}$ , the IC does not respond to the surge voltage in turning on the power MOSFET.

## 10.9 **Random Switching Function**

The IC modulates its switching frequency randomly by superposing the modulating frequency on  $f_{OSC(AVG)}$  in normal operation. This function reduces the conduction noise compared to others without this function, and simplifies noise filtering of the input lines of power supply.

# 10.10 Auto Standby Function

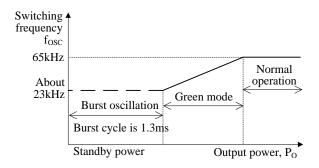

Auto Standby Function automatically changes the oscillation mode to green mode or burst oscillation mode, when the output load becomes lower, the drain current  $I_D$  decreases and the oscillation frequency becomes lower gradually (Green Mode) as shown in Figure 10-10.

In order to reduce the switching loss, the number of switching is reduced in green mode and the switching operation is stopped during a constant period in burst oscillation mode.

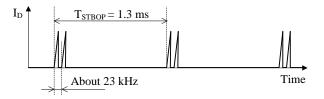

The burst oscillation mode operates by the Standby Operation Cycle,  $T_{STBOP} = 1.3$  ms and the switching

frequency about 23 kHz. In light load, the number of minimum switching times is two times in  $T_{STBOP}$  (refer to Figure 10-11)

Since the oscillator of burst oscillation cycle setting and the oscillator of switching oscillation frequency setting are not synchronized each other, the switching frequency may be high at near the Standby Operation Threshold Voltage,  $V_{\text{STBOP}}$ .

Figure 10-10 Relationship between  $P_{\text{O}}$  and  $f_{\text{OSC}}$

Figure 10-11 Switching waveform at burst oscillation

#### 10.11 Overcurrent Protection Function (OCP)

Overcurrent Protection Function (OCP) detects each drain peak current level of a power MOSFET on pulse-by-pulse basis, and limits the output power when the current level reaches to Drain Current Limit.

When this OCP operation continues for more than the Constant Current Control Delay Time,  $t_{CCD} = 90$  ms, Constant Current (CC) control is activated (refer to 10.7 Constant Current (CC) Control).

#### **Input Compensation Function**

ICs with PWM control usually have some propagation delay time. The steeper the slope of the actual drain current at a high AC input voltage is, the larger the actual drain peak current is, compared to the Drain Current Limit. Thus, the peak current has some variation depending on the AC input voltage in the drain current limitation state.

In order to reduce the variation of peak current in the drain current limitation state, the IC incorporates a built-in Input Compensation function.

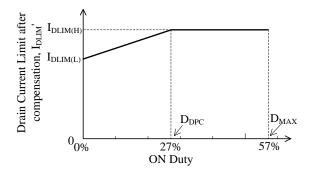

The Input Compensation function superposes a signal with a constant slope (Figure 10-12) into the internal current detection signal and varies the internal threshold voltage.

When AC input voltage is low (ON Duty is broad), the Drain Current Limit after compensation increases. The difference of peak drain current become small compared with the case where the AC input voltage is high (ON Duty is narrow).

The compensation signal depends on ON Duty. The relation between the ON Duty and the drain current limit after compensation  $I_{DLIM}$  is expressed as Equation (4). When ON Duty is broader than 27 %, the drain current limit becomes a constant value  $I_{DLIM(H)}$ .

$$I_{DLIM}' = \frac{I_{DLIM(H)} - I_{DLIM(L)}}{27(\%)} \times Duty + I_{DLIM(L)}$$

(4)

where.

Duty: MOSFET ON Duty (%)

STR5A164D

$I_{DLIM(H)}$ : Drain current limit (ON Duty  $\geq 27 \%$ )  $I_{DLIM(L)}$ : Drain current limit (ON Duty = 0 %)

|           | $I_{\text{DLIM(H)}}$ | $I_{DLIM(L)}$ |

|-----------|----------------------|---------------|

| STR5A162D | 0.285 A              | 0.242 A       |

0.41 A

0.34 A

Figure 10-12 Relationship between ON Duty and Drain Current Limit after compensation

# 10.12 Overvoltage Protection (OVP)

When a voltage between VCC pin and S/GND terminal increases to  $V_{\text{CC(OVP)}} = 29.3 \text{ V}$  or more, OVP Function is activated and stops switching operation.

When OVP Function is activated, VCC pin voltage decreases to Operation Stop Voltage  $V_{\text{CC(OFF)}} = 8.1 \text{ V}$ . After that, the IC reverts to the initial state by UVLO (Undervoltage Lockout) circuit, and the IC starts operation when VCC pin voltage increases to  $V_{\text{CC(ON)}} = 15.0 \text{ V}$  by Startup Current. Thus the intermittent operation by UVLO is repeated in OVP condition.

This intermittent operation reduces the stress of parts such as power MOSFET and secondary side rectifier diode. In addition, this operation reduces power consumption because the switching period in this intermittent operation is short compared with oscillation stop period. When the abnormal condition is removed,

the IC returns to normal operation automatically.

In case the VCC pin voltage is provided by using auxiliary winding of transformer, the overvoltage conditions such as FB pin open can be detected because the VCC pin voltage is proportional to FB pin voltage. The approximate value of output voltage  $V_{\rm OUT(OVP)}$  in OVP condition is calculated by using Equation (5).

$$V_{OUT(OVP)} = \frac{V_{OUT(NORMAL)}}{V_{CC(NORMAL)}} \times 29.3$$

(5)

where.

$V_{OUT(NORMAL)}$ : Output voltage in normal operation  $V_{CC(NORMAL)}$ : VCC pin voltage in normal operation

## 10.13 Thermal Shutdown Protection (TSD)

When the temperature of control circuit increases to Thermal Shutdown Operating Temperature  $T_{j(TSD)} = 135$  °C (min.) or more, Thermal Shutdown Protection function is activated and stops switching operation.

In TSD condition, the intermittent operation by UVLO is repeated by same mechanism as described in "10.12 Overvoltage protection (OVP)".

The TSD function of the IC incorporates the hysteresis. When the temperature of the IC decreases to  $T_{\rm j(TSD)}\text{--}T_{\rm j(TSDHYS)}$ , the IC releases the TSD operation and restarts.

## 11.Design Notes

#### 11.1 External Components

Take care to use properly rated, including derating as necessary and proper type of components.

Figure 11-1 Peripheral circuit of FB pin and VCC pin

#### • Output Electrolytic Capacitor

Apply proper derating to ripple current, voltage, and temperature rise. Use of high ripple current and low impedance types, designed for switch mode power supplies, is recommended.

#### • FB Pin Peripheral Circuit and CRD Clamp Snubber

Figure 11-1 shows the FB pin peripheral circuit. The auxiliary winding voltage,  $V_D$  is divided by resistors (R3, R4 and R5) and induced into FB pin. The FB pin voltage is controlled to be Feedback Reference Voltage,  $V_{FB(REF)} = 2.50 \text{ V}$ .

The value of R5 is about 3.3 k $\Omega$  to 10 k $\Omega$ .

The value of R3 and R4 are calculated as follows:

$$R3 + R4 = \frac{\frac{N_{D}}{N_{S}} \times (V_{OUT} + V_{F}) - V_{FB(REF)}}{\frac{V_{FB(REF)}}{R5} - I_{FB(OP)}}$$

(6)

where.

N<sub>D</sub>: Turns of auxiliary winding of transformer

N<sub>S</sub>: Turns of secondary side winding of transformer

V<sub>OUT</sub>: Output voltage

$V_{\mathrm{F}}$ : Forward drop voltage of secondary side rectifier diode D50

$V_{FB(REF)}$ : Feedback Reference Voltage, 2.50 V

$I_{FB(OP)}$ : Feedback Current,  $-0.8 \mu A$

In addition, the negative voltage is input to FB pin. As shown in Figure 11-2, the negative voltage,  $V_{\text{FW}}$ , of  $V_{\text{D}}$  is calculated as follows:

$$V_{\text{FW}} = \frac{N_{\text{D}}}{N_{\text{P}}} \times V_{\text{IN(AC)}} \times \sqrt{2}$$

(7)

where,

$$\begin{split} &V_{IN(AC)}: Input\ voltage \\ &N_D: Turns\ of\ D\ winding \\ &N_P: Turns\ of\ P\ winding \end{split}$$

Figure 11-2 The auxiliary winding voltage waveform

The absolute maximum rating of FB Pin Source Current,  $I_{FB}$  is -10 mA. The value of R3 and R4 are chosen so that the FB pin source current,  $I_{FB(FW)}$ ,

satisfies Equation (8) considered about surge.

$$\begin{split} I_{\text{FB(FW)}} &= \frac{V_{\text{FW}}}{R3 + R4} \\ &= \frac{N_{\text{D}}}{N_{\text{p}}} \times \frac{V_{\text{IN(AC)}}}{R3 + R4} \times \sqrt{2} \le -5 \text{mA} \end{split} \tag{8}$$

There, the maximum input voltage substitutes in  $V_{\text{IN(AC)}}$ .

R3, R4 and R5 should be adjusted in actual operation condition.

The IC generates the feedback signal by sampled  $V_D$  waveform that is FB pin input signal. In order to improve the accuracy of  $V_D$  waveform sampling, it is necessary to realize the ideal  $V_D$  waveform for reducing the peak and width of the surge component and suppressing the ringing. Because the  $V_D$  waveform depends on the waveform of the primary winding P voltage, a clamp snubber circuit should be added on the primary winding P. The method of setting the value of the clamp snubber circuit is shown in 10.5 Primary Side Regulation (PSR).

In order to maintain the sampling accuracy during light load operation, an auxiliary switch diode SARS05 should be used as D1 where the approximate value of R2 is 220  $\Omega$  to 470  $\Omega.$  R2 should be adjusted to obtain proper  $V_D$  waveform in actual operation condition.

#### • VCC Pin Peripheral Circuit

The reference value of C4 (see Figure 11-1) is generally from 4.7  $\mu F$  to 2.2  $\mu F$ . The startup time is determined by the value of C4 (refer to Section 10.1 Startup Operation).

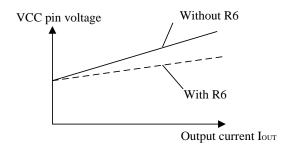

In actual power supply circuits, there are cases in which the VCC pin voltage fluctuates in proportion to the output current,  $I_{OUT}$  (see Figure 11-3), and the Overvoltage Protection function (OVP) on the VCC pin may be activated. This happens because C4 is charged to a peak voltage on the auxiliary winding D, which is caused by the transient surge voltage coupled from the primary winding when the power MOSFET turns off.

Figure 11-3 Variation of VCC pin voltage and power supply output current with / without R6 resistor

For alleviating C4 peak charging, it is effective to add some value R6, of several tenths of ohms to several ohms, in series with D2 (see Figure 11-1). The optimal value of R6 should be determined using a transformer matching what will be used in the actual application, because the variation of the auxiliary winding voltage is affected by the transformer structural design.

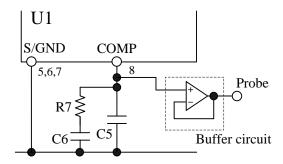

#### • COMP Pin Peripheral Circuit

Figure 11-4shows the COMP pin peripheral circuit. The capacitor C5 between COMP pin and S/GND pin performs for high frequency noise reduction and phase compensation.

C5 should be connected to both COMP pin and S/GND pin as short as possible. The recommended value of C5 is 100 pF to 680 pF. The approximate value of both C6 and R7 are 680 pF to 2200 pF and 680 k $\Omega$ , respectively. These should be adjusted on actual operation.

Because the internal impedance of COMP pin is high, the measurement of COMP pin waveform by using the oscilloscope needs a caution.

Especially in light load condition, the probe of the oscilloscope may affect the control of IC. Thus the voltage-follower (buffer) circuit with high impedance Op Amp should be used for the measurement of COMP pin.

Figure 11-4 COMP pin peripheral circuit

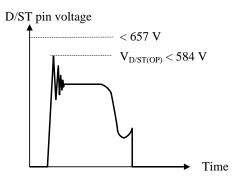

# • D/ST Pin

The internal power MOSFET connected to D/ST pin (see Figure 11-1) is permanently damaged when the D/ST pin voltage and the current exceed the Absolute Maximum Ratings. Therefore, as shown in Figure 11-5, The D/ST pin voltage is tuned to be less than about 90 % of the Absolute Maximum Ratings (657 V) in all condition of actual operation, and the value of transformer and components should be selected based on actual operation in the application.

And the D/ST pin voltage in normal operation is tuned to be the Recommended Operating Conditions,  $V_{\text{D/ST(OP)}} < 584 \text{ V}$ .

The fast recovery diodes are recommended for using as D2 and D51. The way of setting the value

of the clamp snubber circuit is shown in section 10.5 Primary Side Regulation.

Figure 11-5 D/ST pin voltage waveform

#### • Bleeder Resistance

Since the IC employs the primary side regulation, the IC continues burst oscillation operation at light load in order to detect the state of secondary side.

In case the power supply is used under light load condition (input power is 25 mW or less at maximum input voltage) or no load condition, in order to prevent the increase of output voltage, the bleeder resistance, R52, is connected to both ends of the output capacitor, C52, as shown in Figure 11-1.

The value of R52 should be selected based on actual operation in the application after the R52 which loss of R52 becomes about 10 mW is connected.

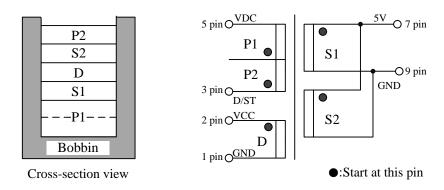

#### • Transformer

Apply proper design margin to core temperature rise by core loss and copper loss.

Because the switching currents contain high frequency currents, the skin effect may become a consideration.

Choose a suitable wire gauge in consideration of the RMS current and a current density of about 3 to  $4A/mm^2$ .

If measures to further reduce temperature are still necessary, the following should be considered to increase the total surface area of the wiring:

- Increase the number of wires in parallel.

- Use litz wires.

- Thicken the wire gauge.

When the leakage inductance between primary winding and secondary winding increases, the turn-on surge of MOSFET becomes large. And in case the leakage inductance between secondary winding and auxiliary winding increases, the accuracy of feedback detection may become low.

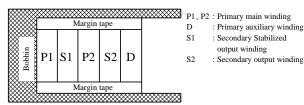

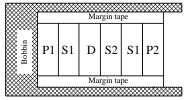

Thus Figure 11-6 shows the winding structural examples to decrease the leakage inductance of transformer.

Figure 11-6 shows the winding structural examples of

two outputs circuit. P1 and P2 are windings divided the primary winding into two. S1 is a stabilized output winding of secondary-side windings, controlled to constant voltage.

- Winding structural example (a): Separating the auxiliary winding D from the primary windings P1 and P2.

- Winding structural example (b): Placing the auxiliary winding D within the secondary-side stabilized output winding, S1, in order to improve the coupling of those windings.

Winding structural example (a)

Winding structural example (b)

Figure 11-6 Winding structural examples

# 11.2 PCB Trace Layout and Component Placement

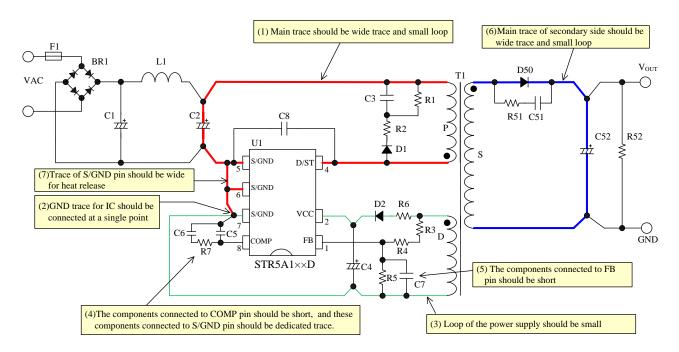

Since the PCB circuit trace design and the component layout significantly affects operation, EMI noise, and power dissipation, the high frequency PCB trace should be low impedance with small loop and wide trace.

In addition, the ground traces affect radiated EMI noise, and wide, short traces should be taken into account.

Figure 11-7 shows the circuit design example.

(1) Main Circuit Trace Layout: S/GND pin to C2 to T1 (winding P) to D/ST pin

This is the main trace containing switching currents, and thus it should be as wide trace and small loop as possible.

If C2 and the IC are distant from each other, placing a capacitor such as film capacitor (about 0.1  $\mu F$  and with proper voltage rating) close to the transformer or the IC is recommended to reduce impedance of the high frequency current loop.

#### (2) Control Ground Trace Layout

Since the operation of IC may be affected from the large current of the main trace that flows in control ground trace, the control ground trace should be connected at a single point grounding of point A as close to the S/GND pin as possible.

(3) VCC Trace Layout: S/GND pin to C4 (negative) to T1 (winding D) to R6 to D2 to C4 (positive) to VCC pin

This is the trace for supplying power to the IC, and thus it should be as small loop as possible. If C4 and the IC are distant from each other, placing a capacitor such as film capacitor  $C_f$  (about 0.1  $\mu F$  to 1.0  $\mu F$ ) close to the VCC pin and the S/GND pin is recommended.

## (4) COMP Trace Layout

C5, C6 and R7 are connected to COMP pin for phase compensation. These capacitors and resistor should be placed to shorten the trace between COMP pin and S/GND pin. In order to stabilize the operation of IC, a dedicated trace to S/GND pin is recommended.

#### (5) FB Trace Layout

The auxiliary winding voltage is divided by resistors and is induced to FB pin. In order to achieve the accurate primary side regulation, the trace between the resistors and FB pin should be as short as possible.

(6) Secondary Rectifier Smoothing Circuit Trace Layout: T1 (winding S) to D50 to C52

This is the trace of the rectifier smoothing loop, carrying the switching current, and thus it should be as wide trace and small loop as possible. If this trace is thin and long, inductance resulting from the loop may increase surge voltage at turning off the power MOSFET. Proper rectifier smoothing trace layout helps to increase margin against the power MOSFET breakdown voltage, and reduces stress on the clamp snubber circuit and losses in it.

## (7) Thermal Considerations

Because the power MOSFET has a positive thermal coefficient of  $R_{DS(ON)}$ , consider it in thermal design. Since the copper area under the IC and the S/GND trace act as a heatsink, its traces should be as wide as possible.

Figure 11-7 Example of peripheral circuit around the IC

# 12.Pattern Layout Example

The following show the PCB pattern layout example and the circuit schematic with STR5A100D series.

Figure 12-1 PCB circuit trace layout example

Figure 12-2 Circuit schematic for PCB circuit trace layout

The above circuit symbols correspond to these of Figure 12-1.

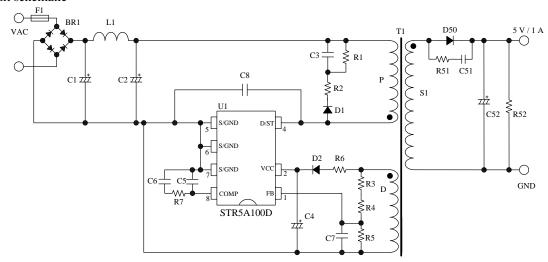

# 13. Reference Design of Power Supply

As an example, the following show the power supply specification, the circuit schematic, the bill of materials, and the transformer specification.

Power supply specification

| IC                   | STR5A164D           |

|----------------------|---------------------|

| Input voltage        | AC 85 V to AC 265 V |

| Maximum output power | 5 W (max.)          |

| Output voltage       | 5 V                 |

| Output current       | 1 A (max.)          |

#### • Circuit schematic

#### • Bill of materials

| Symbol  | Part type         | Ratings <sup>(1)</sup> | Recommended<br>Sanken Parts | Symbol   | Part type           | Ratings <sup>(1)</sup> | Recommended<br>Sanken Parts |

|---------|-------------------|------------------------|-----------------------------|----------|---------------------|------------------------|-----------------------------|

| BR1     | General           | 600 V, 1 A             |                             | R4 (2)   | Chip                | 15 kΩ                  |                             |

| F1      | Fuse              | AC 250 V, 1 A          |                             | R5 (2)   | Chip                | 4.7 kΩ                 |                             |

| L1* (2) | CM inductor       | 330 μΗ                 |                             | R6 (2)   | Chip                | 0 Ω                    |                             |

| C1      | Electrolytic      | 400 V, 4.7 μF          |                             | R7 (2)   | Chip                | 680 kΩ                 |                             |

| C2      | Electrolytic      | 400 V, 4.7 μF          |                             | D1       | General             | 800 V, 1 A             | SARS05                      |

| C3      | Ceramic, chip     | 630 V, 1000 pF         |                             | D2       | Fast recovery, chip | FRD 200 V, 1 A         |                             |

| C4      | Electrolytic      | 50 V, 10 μF            |                             | U1       | IC                  | STR5A164D              |                             |

| C5 (2)  | Ceramic, chip     | 330 pF                 |                             | T1       | Transformer         | See the specification  |                             |

| C6 (2)  | Ceramic, chip     | 1000 pF                |                             | D50      | Schottky            | 60 V, 3 A              | SJPB-L6                     |

| C7 (2)  | Ceramic, chip     | Open                   |                             | C51      | Ceramic, chip       | 50 V, 2200 pF          |                             |

| C8 (2)  | Ceramic, chip     | Open                   |                             | C52 (2)  | Electrolytic        | 10V, 470μF             |                             |

| R1 (3)  | Metal oxide, chip | 470 kΩ                 |                             | R51      | Chip                | 22 Ω                   |                             |

| R2      | Chip              | 270 Ω                  |                             | R52* (2) | Chip                | 2.7 kΩ                 |                             |

| R3 (2)  | Chip              | 3.9 kΩ                 |                             |          |                     |                        |                             |

<sup>(1)</sup> Unless otherwise specified, the voltage rating of capacitor is 50 V or less and the power rating of resistor is 1/8 W or less.

$<sup>^{\</sup>left(2\right)}$  It is necessary to be adjusted based on actual operation in the application.

<sup>(3)</sup> Resistors applied high DC voltage and of high resistance are recommended to select resistors designed against electromigration or use combinations of resistors in series for that to reduce each applied voltage, according to the requirement of the application.

• Transformer specification

□ Primary inductance, L<sub>P</sub>: 1.7 mH

□ Core size : EI-16

<sup>a</sup> AL-value: 118 nH/N<sup>2</sup> (Center gap of about 0.3 mm)

Winding specification

| Winding           | Symbol | Number of turns (T) | Wire diameter (mm)   | Construction | Wire                  |

|-------------------|--------|---------------------|----------------------|--------------|-----------------------|

| Primary winding 1 | P1     | 80                  | φ 0.16               | Two layers   | Enameled Copper Wire  |

| Primary winding 2 | P2     | 40                  | φ 0.16               | Single-layer | Enameled Copper Wire  |

| Auxiliary winding | D      | 18                  | $\phi 0.16 \times 2$ | Single-layer | Enameled Copper Wire  |

| Output winding 1  | S1     | 8                   | $\phi 0.3 \times 2$  | Single-layer | Triple insulated wire |

| Output winding 2  | S2     | 8                   | φ 0.3 × 2            | Single-layer | Triple insulated wire |

Figure 13-1 Example of transformer structure

#### Notes:

- 1) Coupling between D winding and S1 winding should be adjusted and be improved by applying the solid winding construction in D winding, for example.

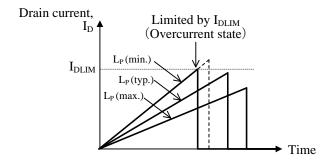

- 2) The peak value of drain current  $I_D$  in normal operation is determined by  $L_P$  value. Since the slope of  $I_D$  is expressed as  $V_{DS}/L_P$ , the smaller the  $L_P$  value, the steeper the slope of  $I_D$  becomes. Thus the peak value of drain current becomes high as shown in Figure 13-2. The IC limits the peak current by drain current limit  $I_{DLIM}$  (Overcurrent state). If  $L_P$  value becomes small by variation, there is the case that the system is in overcurrent state. Then the designed output power cannot be achieved. Thus the  $L_P$  value should be determined after the confirmation in actual operation using minimum  $L_P$  value within the variation, where the peak current value should be less than  $I_{DLIM}(MIN)$  in minimum input voltage of power supply.

Figure 13-2 Relation between L<sub>P</sub> and drain current I<sub>D</sub>

#### **OPERATING PRECAUTIONS**

In the case that you use Sanken products or design your products by using Sanken products, the reliability largely depends on the degree of derating to be made to the rated values. Derating may be interpreted as a case that an operation range is set by derating the load from each rated value or surge voltage or noise is considered for derating in order to assure or improve the reliability. In general, derating factors include electric stresses such as electric voltage, electric current, electric power etc., environmental stresses such as ambient temperature, humidity etc. and thermal stress caused due to self-heating of semiconductor products. For these stresses, instantaneous values, maximum values and minimum values must be taken into consideration. In addition, it should be noted that since power devices or IC's including power devices have large self-heating value, the degree of derating of junction temperature affects the reliability significantly.

Because reliability can be affected adversely by improper storage environments and handling methods, please observe the following cautions.

## **Cautions for Storage**

- Ensure that storage conditions comply with the standard temperature (5 to 35°C) and the standard relative humidity (around 40 to 75%); avoid storage locations that experience extreme changes in temperature or humidity.

- Avoid locations where dust or harmful gases are present and avoid direct sunlight.

- Reinspect for rust on leads and solderability of the products that have been stored for a long time.

#### **Cautions for Testing and Handling**

When tests are carried out during inspection testing and other standard test periods, protect the products from power surges from the testing device, shorts between the product pins, and wrong connections. Ensure all test parameters are within the ratings specified by Sanken for the products.

#### Remarks About Using Silicone Grease with a Heatsink

- When silicone grease is used in mounting the products on a heatsink, it shall be applied evenly and thinly. If more silicone grease than required is applied, it may produce excess stress.

- Volatile-type silicone greases may crack after long periods of time, resulting in reduced heat radiation effect.

Silicone greases with low consistency (hard grease) may cause cracks in the mold resin when screwing the products to a heatsink.

Our recommended silicone greases for heat radiation purposes, which will not cause any adverse effect on the product life, are indicated below:

| Type   | Suppliers                            |

|--------|--------------------------------------|

| G746   | Shin-Etsu Chemical Co., Ltd.         |

| YG6260 | Momentive Performance Materials Inc. |

| SC102  | Dow Corning Toray Co., Ltd.          |

#### Soldering

- When soldering the products, please be sure to minimize the working time, within the following limits:

- $260 \pm 5$  °C  $10 \pm 1$  s (Flow, 2 times)

- $380 \pm 10$  °C  $3.5 \pm 0.5$  s (Soldering iron, 1 time)

- Soldering should be at a distance of at least 1.5 mm from the body of the products.

## **Electrostatic Discharge**

- When handling the products, the operator must be grounded. Grounded wrist straps worn should have at least  $1M\Omega$  of resistance from the operator to ground to prevent shock hazard, and it should be placed near the operator.

- Workbenches where the products are handled should be grounded and be provided with conductive table and floor mats

- When using measuring equipment such as a curve tracer, the equipment should be grounded.

- When soldering the products, the head of soldering irons or the solder bath must be grounded in order to prevent leak voltages generated by them from being applied to the products.

- The products should always be stored and transported in Sanken shipping containers or conductive containers, or be wrapped in aluminum foil.

#### **IMPORTANT NOTES**

- The contents in this document are subject to changes, for improvement and other purposes, without notice. Make sure that this is the latest revision of the document before use.

- Application and operation examples described in this document are quoted for the sole purpose of reference for the use of the products herein and Sanken can assume no responsibility for any infringement of industrial property rights, intellectual property rights or any other rights of Sanken or any third party which may result from its use. Unless otherwise agreed in writing by Sanken, Sanken makes no warranties of any kind, whether express or implied, as to the products, including product merchantability, and fitness for a particular purpose and special environment, and the information, including its accuracy, usefulness, and reliability, included in this document.

- Although Sanken undertakes to enhance the quality and reliability of its products, the occurrence of failure and defect of semiconductor products at a certain rate is inevitable. Users of Sanken products are requested to take, at their own risk, preventative measures including safety design of the equipment or systems against any possible injury, death, fires or damages to the society due to device failure or malfunction.

- Sanken products listed in this document are designed and intended for the use as components in general purpose electronic equipment or apparatus (home appliances, office equipment, telecommunication equipment, measuring equipment, etc.).

- When considering the use of Sanken products in the applications where higher reliability is required (transportation equipment and its control systems, traffic signal control systems or equipment, fire/crime alarm systems, various safety devices, etc.), and whenever long life expectancy is required even in general purpose electronic equipment or apparatus, please contact your nearest Sanken sales representative to discuss, prior to the use of the products herein.

- The use of Sanken products without the written consent of Sanken in the applications where extremely high reliability is required (aerospace equipment, nuclear power control systems, life support systems, etc.) is strictly prohibited.

- When using the products specified herein by either (i) combining other products or materials therewith or

(ii) physically, chemically or otherwise processing or treating the products, please duly consider all

possible risks that may result from all such uses in advance and proceed therewith at your own

responsibility.

- Anti radioactive ray design is not considered for the products listed herein.

- Sanken assumes no responsibility for any troubles, such as dropping products caused during transportation out of Sanken's distribution network.

- The contents in this document must not be transcribed or copied without Sanken's written consent.