**Engineering Specification**

## Type 14.1 XGA Color TFT/LCD Module Model Name:IAXG15S

## Document Control Number : OEM I-915S-01

Note:Specification is subject to change without notice. Consequently it is better to contact to International Display Technology before proceeding with the design of your product incorporating this module.

> Sales Support International Display Technology

- i Contents

- i Contents

- ii Record of Revision

- 1.0 Handling Precautions

- 2.0 General Description

- 2.1 Characteristics

- 2.2 Functional Block Diagram

- 3.0 Absolute Maximum Ratings

- 4.0 Optical Characteristics

- 5.0 Signal Interface

- 5.1 Connectors

- 5.2 Interface Signal Connector

- 5.3 Interface Signal Description

- 5.4 Interface Signal Electrical Characteristics

- 5.4.1 Signal Electrical Characteristics for LVDS Receiver

- 5.4.2 LVDS Receiver Internal Circuit

- 5.4.3 Recommended Guidelines for Motherboard PCB Design and Cable Selection

- 5.5 Signal for Lamp connector

- 6.0 Pixel format image

- 7.0 Parameter guide line for CFL Inverter

- 8.0 Interface Timings

- 8.1 Timing Characteristics

- 8.2 Timing Definition

- 9.0 Power Consumption

- 10.0 Power ON/OFF Sequence

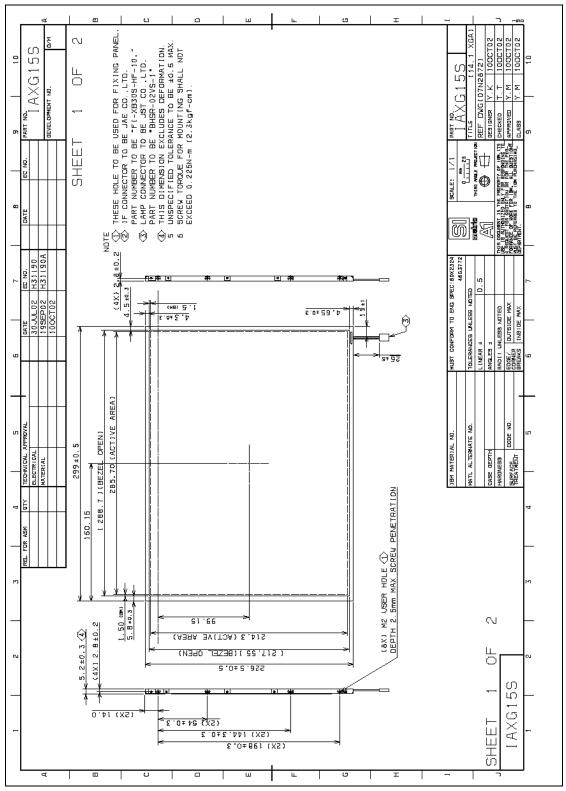

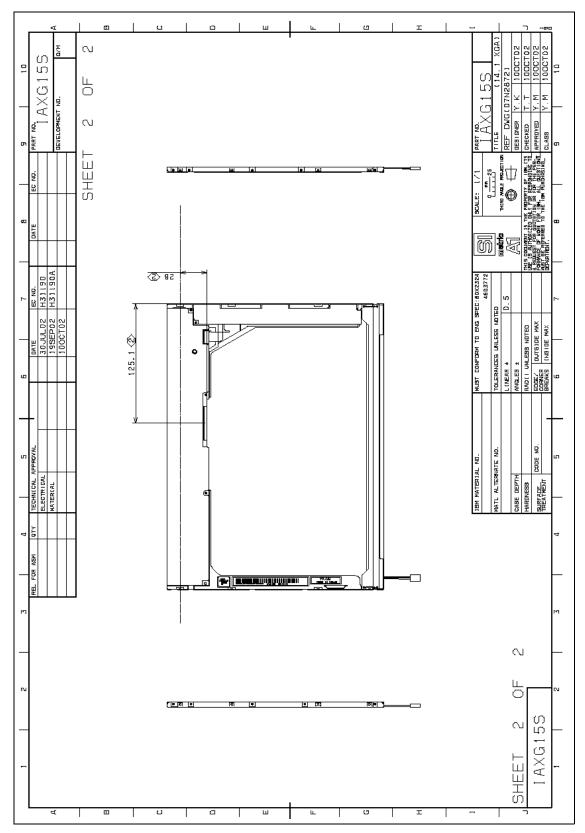

- **11.0 Mechanical Characteristics**

- 12.0 National Test Lab Requirement

# ii Record of Revision

| Date            | Document<br>Revision | Page | Summary                                                                                              |

|-----------------|----------------------|------|------------------------------------------------------------------------------------------------------|

| November 5,2002 | OEM I-915S-01        | All  | First Edition for customer.<br>Based on Internal Spec. as of August 7,2002.<br>(Cable length : 25mm) |

# **1.0 Handling Precautions**

- If any signals or power lines deviate from the power on/off sequence, it may cause shorten the life of the LCD module.

- The LCD panel and the CFL are made of glass and may break or crack if dropped on a hard surface, so please handle them with care.

- CMOS ICs are included in the LCD panel. They should be handled with care, to prevent electrostatic discharge.

- Do not press the reflector sheet at the LCD module to any directions.

- Do not stick the adhesive tape on the reflector sheet at the back of the LCD module.

- Please handle with care when mount in the system cover. Mechanical damage for lamp cable/lamp connector may cause safety problems.

- Small amount of materials having no flammability grade is used in the LCD module. The LCD module should be supplied by power complied with requirements of Limited Power Source (2.5, IEC60950 or UL60950), or be applied exemption conditions of flammability requirements (4.7.3.4, IEC60950 or UL60950) in an end product.

- The LCD module is designed so that the CFL in it is supplied by Limited Current Circuit (2.4, IEC60950 or UL60950).

- The fluorescent lamp in the liquid crystal display(LCD) contains mercury. Do not put it in trash that is disposed of in landfills. Dispose of it as required by local ordinances or regulations.

- Never apply detergent or other liquid directly to the screen.

- Wipe off water drop immediately. Long contact with water may cause discoloration or spots.

- When the panel surface is soiled, wipe it with absorbent cotton or other soft cloth; do not use solvents or abrasives.

- Do not touch the front screen surface in your system, even bezel.

- Gently wipe the covers and the screen with a soft cloth.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by International Display Technology for any infringements of patents or other right of the third partied which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of International Display Technology or others.

- The information contained herein may be changed without prior notice. It is therefore

advisable to contact International Display Technology before proceeding with the design of

equipment incorporating this product.

## 2.0 General Description

This specification applies to the Type 14.1 Color TFT/LCD Module 'IAXG15S'.

This module is designed for a display unit of a notebook style personal computer.

The screen format and electrical interface are intended to support the XGA (1024(H) x 768(V)) screen. Support color is native 262k colors ( RGB 6-bit data driver ).

All input signals are LVDS(Low Voltage Differential Signaling) interface compatible.

This module does not contain an inverter card for backlight.

### 2.1 Characteristics

The following items are characteristics summary on the table under 25 degree C condition:

| CHARACTERISTICS ITEMS                | SPECIFICATIONS                                             |

|--------------------------------------|------------------------------------------------------------|

| Screen Diagonal [cm]                 | 35.7                                                       |

| Active Area [mm]                     | 285.7(H) x 214.3(V)                                        |

| Pixels H x V [pixels]                | 1024(x3) x 768                                             |

| Pixel Pitch [mm]                     | 0.279(per one triad) x 0.279                               |

| Pixel Arrangement                    | R.G.B. Vertical Stripe                                     |

| Display Mode                         | Normally White                                             |

| White Luminance [cd/m <sup>2</sup> ] | 150 Typ. (center) @ CFL current =6.0mA                     |

| Contrast Ratio                       | 200 : 1 Тур.                                               |

| Optical Rise Time+Fall Time [msec]   | 45 Тур. , 50 Мах.                                          |

| Nominal Input Voltage [Volt]         | +3.3 Typ. (+3.0 to +3.6:VDD)                               |

| Logic Power Consumption [watt]       | 1.2 Typ. (VDD)(All Black Pattern)                          |

| Backlight Power Consumption [watt]   | 3.8 Typ.(@CFL current 6.0mA without Inverter loss)         |

| Weight [grams]                       | 380 Min., 400 Typ.,420 Max.                                |

| Physical Size [mm]                   | 299.0(W) x 226.5(H) x 5.2(D) Typ.                          |

| CCFL Cable Length [mm]               | 25mm                                                       |

| Electrical Interface                 | 4 pairs LVDS(R/G/B Data (6-bit),<br>3 sync signals, Clock) |

| Support Color                        | Native 262K colors ( RGB 6-bit data driver )               |

| Temperature Range [deg. C]           | 0 to +50 (Operating)<br>-20 to +60 (Storage, Shipping)     |

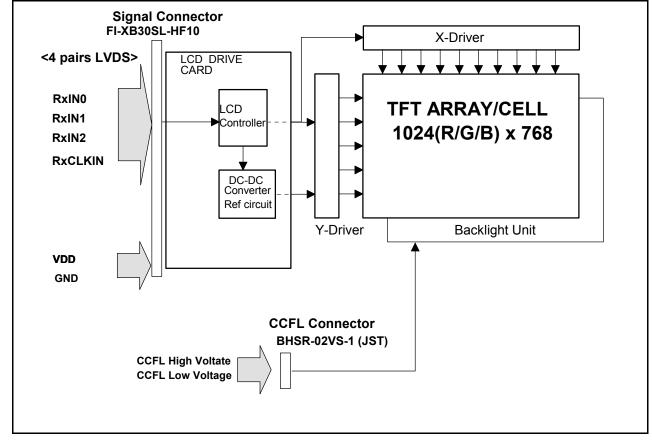

### 2.2 Functional Block Diagram

The following diagram shows the functional block of the Type 14.1 Color TFT/LCD Module.

# 3.0 Absolute Maximum Ratings

Absolute maximum ratings of the module is as follows :

| Item                        | Symbol       | Min  | Max        | Unit  | Conditions                  |

|-----------------------------|--------------|------|------------|-------|-----------------------------|

| Supply Voltage              | VDD -0.3     |      | +4.0       | V     |                             |

| Input Voltage of Signal     | Other Inputs | -0.3 | VDD+0.3    | V     |                             |

| Lamp Ignition Voltage       | VCFL         | -    | +1,650     | Vrms  | Ta = 0 [deg.C]              |

| CFL Current                 | ICFL         | -    | 7          | mArms |                             |

| CFL Peak Inrush Current     | ICFLP        | -    | 20         | mArms | Ta = 25 [deg.C]<br>(Note 1) |

| Operating Temperature       | TOP          | 0    | +50        | deg.C | (Note 2)                    |

| Operating Relative Humidity | HOP          | 8    | 95         | %RH   | (Note 2)                    |

| Storage Temperature         | TST          | -20  | +60        | deg.C | (Note 2)                    |

| Storage Relative Humidity   | HST          | 5    | 95         | %RH   | (Note 2)                    |

| Vibration                   |              |      | 1.5 10-200 | G Hz  |                             |

| Shock                       |              |      | 50 18      | G ms  | Rectangle wave              |

Note :

1. Duration : 50 [msec] Max.

2. Maximum Wet-Bulb should be 39 degree C and No condensation.

# 4.0 Optical Characteristics

The optical characteristics are measured under stable conditions as follows under 25 degree C condition:

| Item                                                | Conditions                        | Specification                  |         |

|-----------------------------------------------------|-----------------------------------|--------------------------------|---------|

|                                                     |                                   | Тур.                           | Note    |

| Viewing Angle<br>(Degrees)                          | Horizontal (Right)<br>K≥10 (Left) | 40<br>40                       | -       |

| K:Contrast Ratio                                    | Vertical (Upper)<br>K≥10 (Lower)  | 15<br>30                       | -<br>-  |

| Contrast ratio                                      |                                   | 200                            | -       |

| Response Time                                       | Dising L Colling                  | 45                             | 50 Max. |

| (ms)                                                | Rising + Falling                  | 40                             | SO Max. |

| Color                                               | Red x                             | 0.577                          | -       |

| Chromaticity                                        | Red y                             | 0.338                          | -       |

| (CIE)                                               | Green x                           | 0.310                          | -       |

|                                                     | Green y                           | 0.544                          | -       |

|                                                     | Blue x                            | 0.158                          | -       |

|                                                     | Blue y                            | 0.124                          | -       |

|                                                     | White x                           | 0.313                          | -       |

|                                                     | White y                           | 0.329                          | -       |

| White Luminance (cd/m <sup>2</sup> )<br>ICFL 6.0 mA |                                   | 150Typ.<br>Center              | -       |

|                                                     |                                   | 140Typ.<br>5 points<br>average |         |

Anti Glare Treatment : Display surface treatment of this LCD module is Nitto Denko ARC150T.

# 5.0 Signal Interface

### 5.1 Connectors

Physical interface is described as for the connector on module.

These connectors are capable of accommodating the following signals and will be following components.

| Connector Name / Designation | For Signal Connector |

|------------------------------|----------------------|

| Manufacturer                 | JAE                  |

| Type / Part Number           | FI-XB30SL-HF10       |

| Mating Type / Part Number    | FI-X30M, FI-X30C2L   |

| Connector Name / Designation | For Lamp Connector |

|------------------------------|--------------------|

| Manufacturer                 | JST                |

| Type / Part Number           | BHSR-02VS-1        |

| Mating Type / Part Number    | SM02B-BHSS-1       |

### 5.2 Interface Signal Connector

| Pin # | Signal Name       | Pin # | Signal Name       |

|-------|-------------------|-------|-------------------|

| 1     | FG (GND)          | 17    | GND               |

| 2     | GND               | 18    | RxCLKIN- (Note 2) |

| 3     | VDD               | 19    | RxCLKIN+ (Note 2) |

| 4     | VDD               | 20    | GND               |

| 5     | Reserved (Note 1) | 21    | Reserved (Note 1) |

| 6     | Reserved (Note 1) | 22    | Reserved (Note 1) |

| 7     | Reserved (Note 1) | 23    | GND               |

| 8     | Reserved (Note 1) | 24    | Reserved (Note 1) |

| 9     | RxIN0- (Note 2)   | 25    | Reserved (Note 1) |

| 10    | RxIN0+ (Note 2)   | 26    | GND               |

| 11    | GND               | 27    | Reserved (Note 1) |

| 12    | RxIN1- (Note 2)   | 28    | Reserved (Note 1) |

| 13    | RxIN1+ (Note 2)   | 29    | GND               |

| 14    | GND               | 30    | Reserved (Note 1) |

| 15    | RxIN2- (Note 2)   | 31    | Reserved (Note 1) |

| 16    | RxIN2+ (Note 2)   | 32    | FG (GND)          |

Note :

1. 'Reserved' pins are not allowed to connect any other line.

2. Voltage levels of all input signals are LVDS compatible. Refer to "Signal Electrical Characteristics for LVDS", for voltage levels of all input signals.

### 5.3 Interface Signal Description

Signal Description

| Signal Name        | Description                                                      |

|--------------------|------------------------------------------------------------------|

| RxIN0+, RxIN0-     | LVDS differential data input (Red0-Red5, Green0)                 |

| RxIN1+, RxIN1-     | LVDS differential data input (Green1-Green5,Blue0-Blue1)         |

| RxIN2+, RxIN2-     | LVDS differential data input (Blue2-Blue5, HSync, VSync, DSPTMG) |

| RxCLKIN+, RxCLKIN- | LVDS differential clock input                                    |

| VDD                | +3.3V Power Supply                                               |

| GND                | Ground                                                           |

Note :

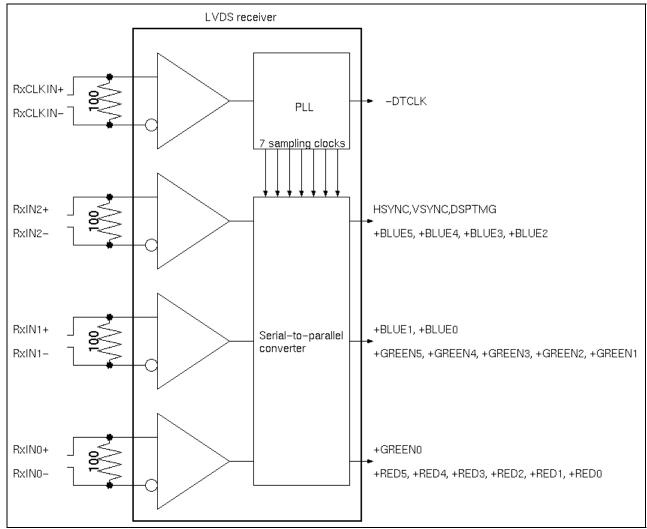

- The module uses a 100ohm resistor between positive and negative data lines of each receiver input.

- Input signals shall be low or Hi-Z state when VDD is off.

| SIGNAL NAME                                                          | Description                                                                                              |                                                                                                                                                                                      |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +RED5<br>+RED4<br>+RED3<br>+RED2<br>+RED1<br>+RED0                   | Red Data 5 (MSB)<br>Red Data 4<br>Red Data 3<br>Red Data 2<br>Red Data 1<br>Red Data 0 (LSB)             | Red-pixel Data<br>Each red pixel's brightness data consists of these 6 bits<br>pixel data.                                                                                           |

| +GREEN 5<br>+GREEN 4<br>+GREEN 3<br>+GREEN 2<br>+GREEN 1<br>+GREEN 0 | Green Data 5 (MSB)<br>Green Data 4<br>Green Data 3<br>Green Data 2<br>Green Data 1<br>Green Data 0 (LSB) | Green-pixel Data<br>Each green pixel's brightness data consists of these 6 bits<br>pixel data.                                                                                       |

| +BLUE 5<br>+BLUE 4<br>+BLUE 3<br>+BLUE 2<br>+BLUE 1<br>+BLUE 0       | Blue Data 5 (MSB)<br>Blue Data 4<br>Blue Data 3<br>Blue Data 2<br>Blue Data 1<br>Blue Data 0 (LSB)       | Blue-pixel Data<br>Each blue pixel's brightness data consists of these 6 bits<br>pixel data.                                                                                         |

| -DTCLK                                                               | Data Clock                                                                                               | The typical frequency is 65.0 MHz. The signal is used to strobe the pixel data and DSPTMG signals. All pixel data shall be valid at the falling edge when the DSPTMG signal is high. |

| DSPTMG                                                               | Display Timing                                                                                           | This signal is strobed at te falling edge of -DTCLK. When the signal is high, the pixel data shall be valid to be displayed.                                                         |

| VSYNC                                                                | Vertical Sync                                                                                            | The signal is synchronized to -DTCLK .                                                                                                                                               |

| HSYNC                                                                | Horizontal Sync                                                                                          | The signal is synchronized to -DTCLK .                                                                                                                                               |

**Note :** Output signals from any system shall be low or Hi-Z state when VDD is off.

### 5.4 Interface Signal Electrical Characteristics

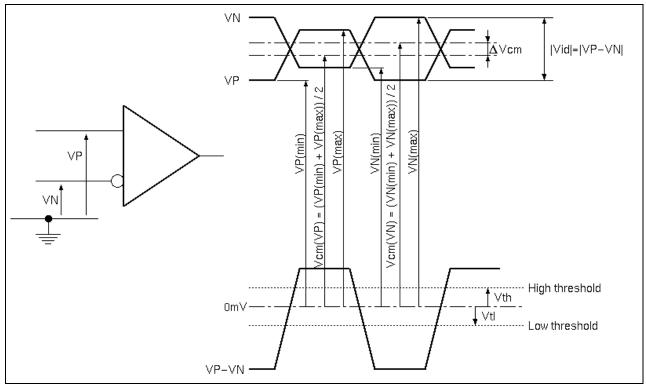

#### 5.4.1 Signal Electrical Characteristics for LVDS Receiver

The LVDS receiver equipped in this LCD module is compatible with ANSI/TIA/TIA-644 standard.

#### **Electrical Characteristics**

| Parameter                            | Symbol | Min  | Тур | Max  | Unit | Conditions        |

|--------------------------------------|--------|------|-----|------|------|-------------------|

| Differential Input High Threshold    | Vth    |      |     | +100 | mV   | Vcm=+1.2V         |

| Differential Input Low Threshold     | Vtl    | -100 |     |      | mV   | Vcm=+1.2V         |

| Magnitude Differential Input Voltage | Vid    | 100  |     | 600  | mV   |                   |

| Common Mode Voltage                  | Vcm    | 1.0  | 1.2 | 1.4  | V    | Vth - Vtl = 200mV |

| Common Mode Voltage Offset           | ∆Vcm   | -50  |     | +50  | mV   | Vth - Vtl = 200mV |

Note :

- Input signals shall be low or Hi-Z state when VDD is off.

- All electrical characteristics for LVDS signal are defined and shall be measured at the interface connector of LCD.

Voltage Definitions

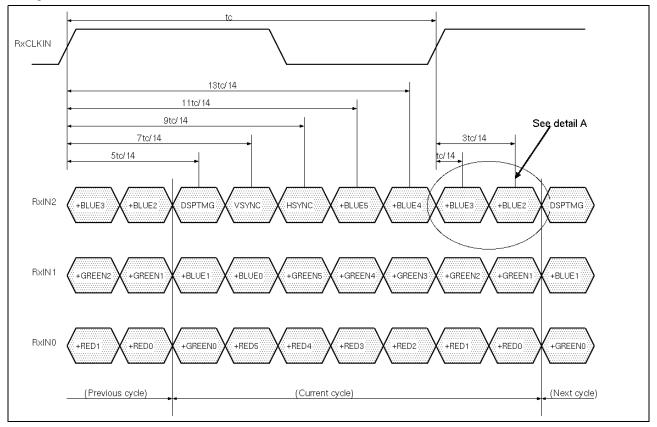

#### Timming Requirements

| Parameter                      | Symbol | Min   | Тур   | Max   | Unit   | Conditions                               |  |

|--------------------------------|--------|-------|-------|-------|--------|------------------------------------------|--|

| Clock Frequency                | fc     | 50    | 65    | 67    | MHz    |                                          |  |

| Cycle Time                     | tc     | 14.93 | 15.38 | 20.00 | ns     |                                          |  |

| Data Setup Time (Note 1)       | Tsu    | 600   |       |       | ps     | fc = 65MHz, $tCCJ < 50ps$ ,              |  |

| Data Hold Time (Note 2)        | Thd    | 600   |       |       | ps     | Vth-Vtl = 400mV,<br>Vcm = 1.2V, ∆Vcm = 0 |  |

| Cycle-to-cycle jitter (Note 3) | tCCJ   | -150  |       | +150  | ps     | fc = 65MHz, Tsu=Thd=900ps                |  |

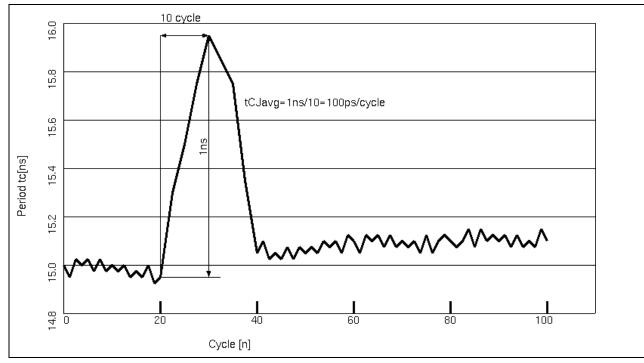

| Cycle Modulation Rate (Note 4) | tCJavg |       |       | 20    | ps/clk | fc = 65MHz, Tsu=Thd=900ps                |  |

Note :

1. All values are at VDD=3.3V, Ta=25 degree C.

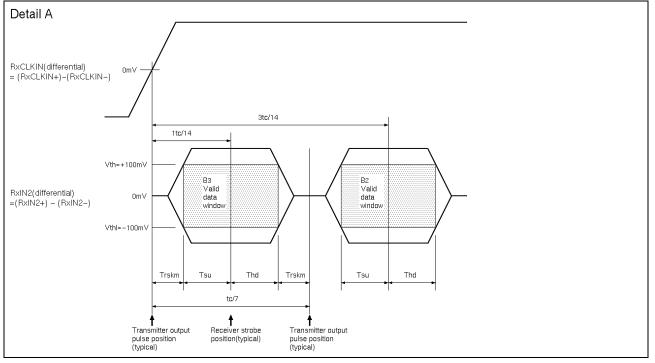

2. See figure "Timing Definition" and "Timing Definition(detail A)" for definition.

- 3. Jitter is the magnitude of the change in input clock period.

- 4. This specification defines maximum average cycle modulation rate in peak-to-peak transition within any 100 clock cycles. Figure "Cycle Modulation Rate" illustrates a case against this requirement. This specification is applied only if input clock peak jitter within any 100 clock cycles is greater than 300ps.

**Timing Definition**

#### Timing Definition(detail A)

**Note:** Tsu and Thd are internal data sampling window of receiver. Trskm is the system skew margin; i.e., the sum of cable skew, source clock jitter, and other inter-symbol interference, shall be less than Trskm.

#### Cycle Modulation Rate

### 5.4.2 LVDS Receiver Internal Circuit

The following figure shows the internal block diagram of the LVDS receiver. This LCD module equips termination resistors for LVDS link.

#### 5.4.3 Recommended Guidelines for Motherboard PCB Design and Cable Selection

Following the suggestions below will help to achieve optimal results.

- Use controlled impedance media for LVDS signals. They should have a matched differential impedance of 100ohm.

- Match electrical lengths between traces to minimize signal skew.

- Isolate TTL signals from LVDS signals.

- For cables, twisted pair, twinax, or flex circuit with close coupled differential traces are recommended.

### 5.5 Signal for Lamp Connector

| Pin # | Signal Name       |

|-------|-------------------|

| 1     | Lamp High Voltage |

| 2     | Lamp Low Voltage  |

# 6.0 Pixel format image

Following figure shows the relationship of the input signals and LCD pixel format image. Even and odd pair of RGB data are sampled at a time.

|            | 0      | 1  | 102 | 2 1023   |

|------------|--------|----|-----|----------|

| 1st Line   | RGB RG | ЭВ | RG  | BRGB     |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    |     |          |

|            |        |    | 1   |          |

| 768th Line | RGBRO  | ЗВ | RG  | в RGB    |

|            |        |    |     | <u> </u> |

|            |        |    |     |          |

# 7.0 Parameter guide line for CFL Inverter

| SYMBOL | PARAMETER                                         | MIN   | D.P-1<br>Note1 | MAX | UNITS              | CONDITION                         |

|--------|---------------------------------------------------|-------|----------------|-----|--------------------|-----------------------------------|

| (L63)  | White Luminance<br>(Center)<br>(5 points average) | -     | 150<br>140     | -   | [cd/m²]<br>[cd/m²] | Ta=25[deg. C]                     |

| ICFL   | CFL current                                       | 4.0   | 6.0            | 7.0 | [mArms]            | Ta=25[deg. C]<br><b>(Note2,5)</b> |

| ICFLP  | CFL Peak Inrush Current                           |       |                | 20  | [mA]               | Ta=25[deg. C]<br><b>(Note2,6)</b> |

| FCFL   | CFL Frequency                                     | 40    |                | 70  | [kHz]              | Ta=25[deg. C]<br><b>(Note 3)</b>  |

| VCFLi  | Inverter Ignition Voltage                         | 1,600 |                |     | [Vrms]             | Ta=0[deg. C]                      |

| VCFL   | CFL Voltage (Reference)                           |       | 640            |     | [Vrms]             | Ta=25[deg. C]                     |

| PCFL   | CFL Power consumption                             |       | 3.8            | 4.2 | [W]                | Ta=25[deg. C]<br>(Note 4)         |

Note :

1. Design Point-1

2. If it exceeds MIN/MAX values, then "CFL Life", "ON/OFF Cycle", and "SAFETY" will not be guaranteed.

3. CFL Frequency should be carefully determined to avoid interference between inverter and TFT LCD.

4. Calculated value for reference (ICFL x VCFL = PCFL).

5. It should be employed the inverter which has `Duty Dimming`, if ICFL is less than 4[mA].

6. Duration: 50msec MAX

The following chart is Luminance versus Lamp Current for your reference.

TBD

## 8.0 Interface Timings

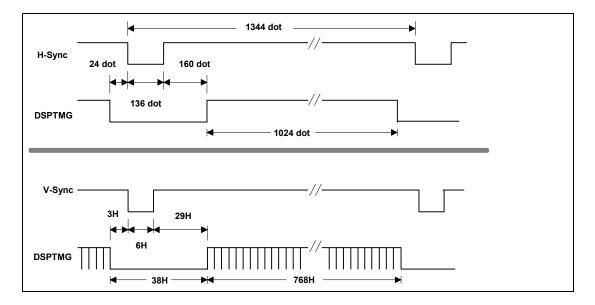

Basically, interface timings should match the VESA 1024x768 / 60 Hz (VG901101) manufacturing guide line timing. These timings described here are not actual input timings of LCD module but output timings of SN75LVDS86DGG(Texas Instruments) or equivalent.

### 8.1 Timing Characteristics

Timing Characteristics (based on VESA 1024 x 768 / 60Hz)

| Symbol |                    | MIN   | TYP    | MAX   | Unit   | Note |

|--------|--------------------|-------|--------|-------|--------|------|

| fdck   | DTCLK Frequency    | 50.00 | 65.00  | 67.00 | [MHz]  |      |

| tck    | DTCLK cycle time   | 14.93 | 15.38  | 20.00 | [nsec] |      |

| tx     | X total time       | 1206  | 1344   | 2047  | [tck]  |      |

| tacx   | X active time      | 1024  | 1024   | 1024  | [tck]  |      |

| Hsync  | H frequency        |       | 48.363 |       | [KHz]  |      |

| Hsw    | H-Sync width       | 8     | 136    |       | [tck]  | 2    |

| Hbp    | H back porch       | 8     | 160    |       | [tck]  | 2    |

| Hfp    | H front porch      | 0     | 24     |       | [tck]  |      |

| ty     | Y total time       | 777   | 806    | 1023  | [tx]   |      |

| tacy   | Y active time      | 768   | 768    | 768   | [tx]   |      |

| Vsync  | Frame rate         | 50    | 60     | 61    | [Hz]   |      |

| Vw     | V-sync Width       | 1     | 6      |       | [tx]   |      |

| Vfp    | V-sync front porch | 1     | 3      |       | [tx]   |      |

| Vbp    | V-sync back porch  | 7     | 29     | 63    | [tx]   | 1    |

Note :

1. Vbp should be static

2. Hsw + Hbp >= 32 [tck]

3. When there are invalid timing, Display appears black pattern. Synchronous Signal Defects and enter Auto Refresh for LCD Module Protection Mode.

### 8.2 Timing Definition

# 9.0 Power Consumption

Input power specifications are as follows;

| SYMBOL | PARAMETER                                   | Min | Тур | Max  | UNITS   | CONDITION                        |

|--------|---------------------------------------------|-----|-----|------|---------|----------------------------------|

| VDD    | Logic/LCD Drive<br>Voltage                  | 3.0 | 3.3 | 3.6  | [V]     | Load Capacitance 20[uF]          |

| PDD    | VDD Power                                   |     |     | 1.91 | [W]     | Max. Pattern,<br>VDD=3.6[V]      |

| PDD    | VDD Power                                   |     | 1.2 |      | [W]     | All Black Pattern,<br>VDD=3.3[V] |

| IDD    | VDD Current                                 |     |     | 530  | [mA]    | Max Pattern,<br>VDD=3.6[V]       |

| IDD    | VDD Current                                 |     | 360 |      | [mA]    | All Black Pattern,<br>VDD=3.3[V] |

| VDDrp  | Allowable Logic/LCD<br>Drive Ripple Voltage |     |     | 100  | [mVp-p] |                                  |

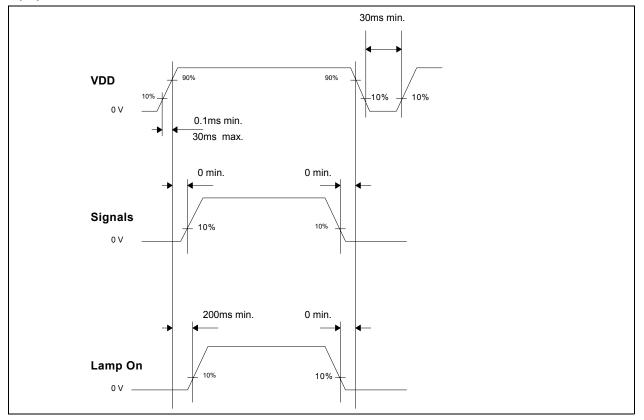

## 10.0 Power ON/OFF Sequence

VDD power and lamp on/off sequence is as follows. Interface signals are also shown in the chart. Signals from any system shall be Hi-Z state or low level when VDD is off.

### **11.0 Mechanical Characteristics**

# 12.0 National Test Lab Requirement

The display module is authorized to Apply the UL Recognized Mark.

#### **Conditions of Acceptability**

Conditions of Acceptability - When installed on the end-product, consideration shall be given to the following;

- 1. This component has been judged on the basis of the required spacings in the Standard for Safety of Information Technology Equipment, CSA/ UL60950, Third Edition, dated December 1,2000, Sub-clause 2.10, which would cover the component itself if submitted for Listing.

- 2. The unit is intended to be supplied by SELV and Limited Power Source. Also separated from electrical parts, which may produce high temperature that could cause ignition by as least 13mm of air or by a solid barrier of material of V-1 minimum.

- 3. The terminals and connectors are suitable for factory wiring only.

- 4. A suitable electrical enclosure shall be provided.

\*\*\*\*\*\* End Of Page \*\*\*\*\*\*