# **Bt218**

### 20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

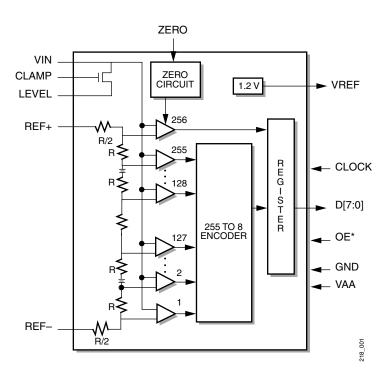

The Bt218 is an 8-bit flash A/D converter designed specifically for video digitizing applications. A flash converter topology is used with 256 high-speed comparators in parallel to digitize the analog input signal.

Flexible input ranges enable NTSC and CCIR video signals to be digitized without requiring a video amplifier.

The TTL-compatible output data and OVERFLOW are registered synchronously with the clock signal. The OE\* three-states the D[7:0] outputs asynchronously to CLOCK.

The ZERO input is used to zero the comparators, while CLAMP allows DC restoration of an AC-coupled video signal (by forcing the VIN input to the voltage on the LEVEL pin). •

The Bt218 contains 256 high-speed comparators, a 255-to-8 encoder, an output register, and a resistor divider network. Of the 256 comparators, 255 are used to digitize the analog signal; the additional comparator is used to generate the OVERFLOW bit.

#### **Functional Block Diagram**

#### **Distinguishing Features**

- 20 MSPS operation

- Bt208 pin compatibility

- · No video amplifier requirement

- ±1/4 LSB typical DL error

- ±1/2 LSB typical IL error

- External zero and clamp control

- Overflow output

- On-chip reference

- Output enable control

- · TTL compatibility

- +5 V CMOS monolithic

- construction

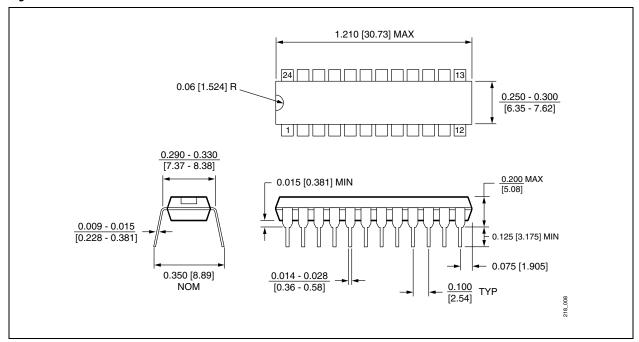

- 24-pin 0.3" DIP or 28-pin PLCC

- packages

- · Typical power dissipation: 500 mW

#### **Applications**

- Image processing

- · Image capture

- · Desktop publishing

- · Graphic art systems

#### **Related Products**

- Bt252

- Bt254

- Bt261

### **Ordering Information**

| Model Number | Package                 | Speed  | Ambient Temperature Range |

|--------------|-------------------------|--------|---------------------------|

| Bt218KP20    | 24-Pin 0.3" Plastic DIP | 20 MHz | 0 °C to 70 °C             |

| Bt218KPJ20   | 28-Pin Plastic J-Lead   | 20 MHz | 0 °C to 70 °C             |

Information provided by Conexant Systems, Inc. (Conexant) is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The trademarks "Conexant" and the Conexant symbol are trademarks of Conexant Systems, Inc.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of their respective companies. All other marks mentioned herein are the property of their respective holders.

© 1999 Conexant Systems, Inc. Printed in U.S.A. All Rights Reserved

**Reader Response:** Conexant strives to produce quality documentation, and welcomes your feedback. Please send comments and suggestions to conexant.tech.pubs@conexant.com. For technical questions, contact your local Conexant sales office or field applications engineer.

L218\_D Conexant

# **Table of Contents**

| List o | f Figu | res v                        |

|--------|--------|------------------------------|

| List o | f Tabl | <b>es</b> vii                |

| 1.0    | Circ   | uit Description1-1           |

|        | 1.1    | Pin Descriptions             |

|        | 1.2    | General Operation. 1-4       |

| 2.0    | PC I   | Board Layout Considerations  |

|        | 2.1    | PC Board Considerations      |

|        | 2.2    | <b>Ground Planes</b>         |

|        | 2.3    | <b>Power Planes</b>          |

|        | 2.4    | Application Information. 2-4 |

| 3.0    | Para   | ametric Information          |

|        | 3.1    | DC Electrical Parameters 3-1 |

|        | 3.2    | AC Electrical Parameters     |

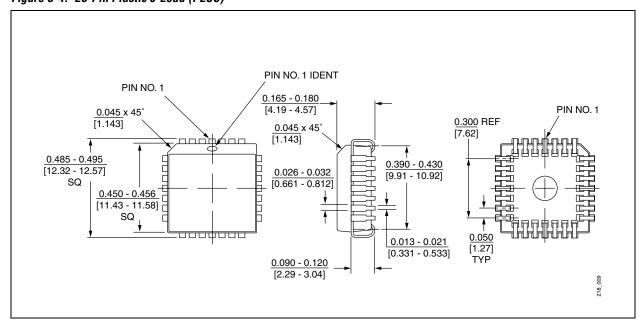

|        | 3.3    | Package Drawings 3-9         |

|        | 3.4    | Revision History             |

Table of Contents Bt218

Bt218 List of Figures

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

# **List of Figures**

| Figure 1-1. | Pinout Diagrams                                 | 1-8 |

|-------------|-------------------------------------------------|-----|

| Figure 1-2. | General Operation                               | 1-8 |

| Figure 2-1. | Typical Connection Diagram (Internal Reference) | 2-2 |

| Figure 2-2. | Using an External Reference                     | 2-4 |

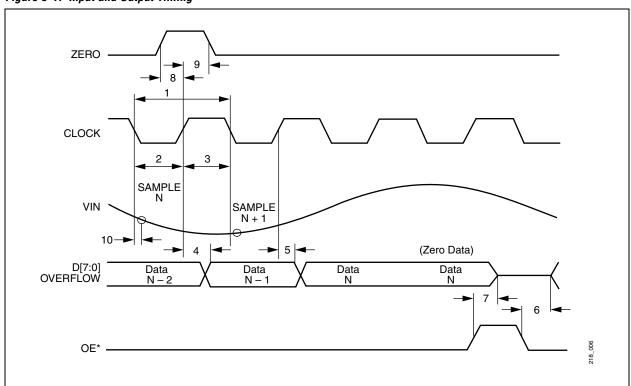

| Figure 3-1. | Input and Output Timing                         | 3-7 |

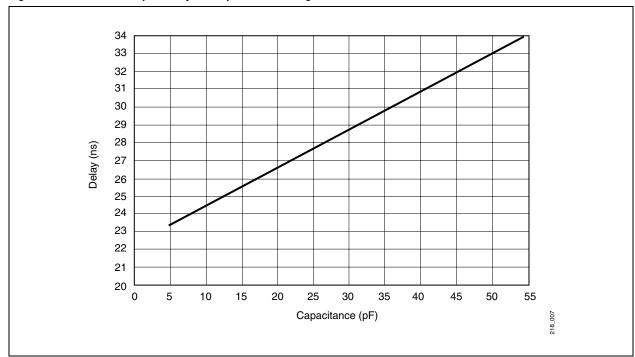

| Figure 3-2. | Bt218KPJ Output Delay vs. Capacitive Loading    | 3-8 |

| Figure 3-3. | 24-Pin 0.300" Plastic DIP                       | 3-9 |

| Figure 3-4. | 28-Pin Plastic J-Lead (PLCC)                    | 3-9 |

List of Figures Bt218

Bt218 List of Tables

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

## **List of Tables**

| lable 1-1. | Pin Descriptions                   | . 1-1 |

|------------|------------------------------------|-------|

| Table 1-2. | Output Coding Example              | . 1-4 |

| Table 2-1. | Typical Parts (Internal Reference) | 2-3   |

| Table 2-2. | Video Signal Tolerances            | . 2-  |

| Table 3-1. | Recommended Operating Conditions   | . 3-1 |

| Table 3-2. | Absolute Maximum Ratings           | . 3-2 |

| Table 3-3. | DC Characteristics                 | . 3-3 |

| Table 3-4. | AC Characteristics                 | . 3-  |

| Table 3-5. | Revision History                   | 3-10  |

List of Tables Bt218

# **1.0 Circuit Description**

## 1.1 Pin Descriptions

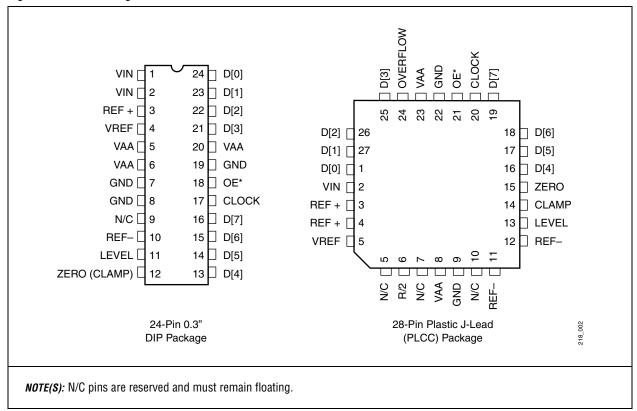

The Bt218 is available as a 24-pin DIP and as a 28-pin Plastic Leaded Chip Carrier (PLCC). Pin descriptions are listed in Table 1-1. Both packages are illustrated in Figure 1-1.

Table 1-1. Pin Descriptions (1 of 2)

| Pin Name | Description                                                                                                                                                                                                                                                                                                          |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[7:0]   | Data outputs (TTL compatible). D[0] is the least significant data bit. These outputs are latched and output following the second rising edge of CLOCK. Coding is binary. For optimum performance, D[7:0] should have minimal loading. If a large capacitive load is being driven, an external buffer is recommended. |

| OE*      | Output enable control input (TTL compatible). Negating OE* three-states D[7:0] asynchronously. The OVERFLOW output is not affected by the state of OE*.                                                                                                                                                              |

| OVERFLOW | Overflow output (TTL compatible). OVERFLOW is latched and output following the second rising edge of CLOCK. OE* does not affect the OVERFLOW output signal. OVERFLOW is not available on the DIP package.                                                                                                            |

| CLOCK    | Clock input (TTL compatible). It is recommended that this pin be driven by a dedicated TTL buffer to minimize sampling jitter.                                                                                                                                                                                       |

| REF+     | Top of ladder voltage reference (voltage input). REF+ sets the VIN voltage level that corresponds to \$FF on the D[7:0] outputs. All REF+ pins must be connected together as close to the device as possible. For noise immunity reasons, a decoupling capacitor is not recommended on REF+.                         |

| REF-     | Bottom of ladder voltage reference (voltage input). Typically, this input is connected to GND. REF— sets the VIN voltage level that corresponds to \$00 on the D[7:0] outputs. All REF— pins must be connected together as close to the device as possible.                                                          |

1.0 Circuit Description Bt218

### 1.1 Pin Descriptions

Table 1-1. Pin Descriptions (2 of 2)

| Pin Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/2        | Midtap of reference ladder (voltage output). R/2 is not available on the DIP package. If not used, this pin should remain floating. If used, it should be buffered by a voltage follower. For noise immunity reasons, a decoupling capacitor is not recommended on R/2.                                                                                                                                                                                                                                                                                                                                                                                          |

| VIN        | Analog signal inputs (voltage input). All VIN pins must be connected together as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ZERO/CLAMP | Zeroing control input (TTL compatible). While ZERO is a logical one, the comparators are zeroed and D[7:0] output data is held to the current state. ZERO is latched on the rising edge of CLOCK. On the 24-pin DIP package, ZERO and CLAMP share the same pin; hence, zeroing and clamping occur simultaneously.  Clamp control input (TTL compatible). While CLAMP is a logical one, the VIN inputs are forced to the voltage level on the LEVEL pin to perform DC restoration of an AC-coupled video signal. CLAMP is asynchronous to clock. On the 24-pin DIP package, ZERO and CLAMP share the same pin; hence, ZERO and CLAMP are asserted simultaneously. |

| LEVEL      | Level control input (voltage input). This input is used to specify what voltage level to use for clamping while CLAMP is a logical one. LEVEL is used only to DC restore AC-coupled video signals. In applications where the video signal is DC-coupled to VIN, the LEVEL pin should float or be connected to VIN.                                                                                                                                                                                                                                                                                                                                               |

| VREF       | Voltage reference output pin. This pin provides a 1.2 V (typical) output. A decoupling capacitor is not recommended on VREF.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VAA        | Analog power. All VAA pins must be connected together on the same PCB plane and as close to the device as possible to prevent latchup. A 0.1 $\mu\text{F}$ ceramic capacitor should be connected between each group of VAA pins and GND, as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                     |

| GND        | Ground. All GND pins must be connected together on the same PCB plane and as close to the device as possible to prevent latchup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

Bt218 1.0 Circuit Description

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

1.1 Pin Descriptions

Figure 1-1. Pinout Diagrams

### 1.2 General Operation

The Bt218 converts an analog signal in the range of REF- ≤Vin ≤REF+, generating a binary number from \$00 to \$FF, and an OVERFLOW output (see Table 1-2). The values of REF+ and REF- are flexible to enable various video signals to be digitized without requiring a video amplifier. Refer to the Parametric Information and Application Information sections for suggested configurations.

Table 1-2. Output Coding Example

| Vin (V) <sup>(1)</sup> | Overflow | D[7:0]  | OE* |

|------------------------|----------|---------|-----|

| >0.998                 | 1        | \$FF    | 0   |

| 0.996                  | 0        | \$FF    | 0   |

| 0.992                  | 0        | \$FE    | 0   |

| :                      | :        | :       | :   |

| 0.500                  | 0        | \$81    | 0   |

| 0.496                  | 0        | \$80    | 0   |

| 0.492                  | 0        | \$7F    | 0   |

| :                      | :        | :       | :   |

| 0.004                  | 0        | \$01    | 0   |

| <0.002                 | 0        | \$00    | 0   |

|                        |          | 3–State | 1   |

|                        | •        | •       |     |

#### NOTE(S):

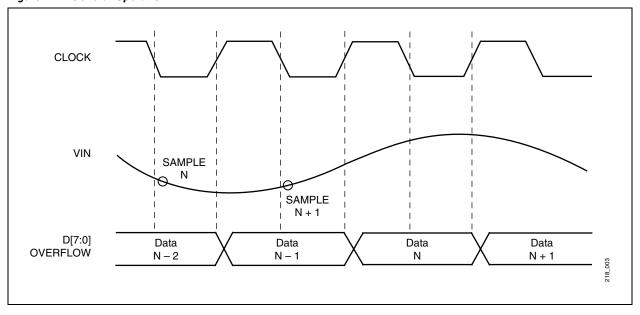

Figure 1-2 illustrates the input and output timing of the Bt218. The sample is taken following the falling edge of CLOCK. The binary data and OVERFLOW are registered and output onto the D[7:0] and OVERFLOW pins on the second rising edge of CLOCK.

With REF+ = 1.000 V and REF- = 0.000 V. Ideal Center Values. 1 LSB = 3.9063 mV.

Bt218 1.0 Circuit Description

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

1.2 General Operation

Figure 1-2. General Operation

### **Comparator Zeroing**

The ZERO input is used to periodically zero the comparators. The comparators have an initial threshold mismatch caused by manufacturing tolerances. Zeroing charges capacitors in the comparators that offset this threshold mismatch. But because capacitors discharge, the comparators must be periodically zeroed. While ZERO is a logical one, the comparators are zeroed. During ZERO cycles, D[7:0] and OVERFLOW are not updated. They retain the data loaded before the ZERO cycle.

#### **Input Signal Clamping**

CLAMP and LEVEL are used only in applications where the video signal is AC coupled to VIN. While CLAMP is a logical one, the VIN input is forced to the voltage level of the LEVEL pin to DC restore the video signal. In applications where the video signal is DC coupled to VIN, the LEVEL pin should float or be connected to VIN, or CLAMP should always be a logical zero (on the 28-pin PLCC package only).

1.0 Circuit Description Bt218

1.2 General Operation

## 2.0 PC Board Layout Considerations

### 2.1 PC Board Considerations

For optimum performance, before PCB layout is begun, study the CMOS digitizer layout examples in the Bt208, Bt251, or Bt253 Evaluation Module Operation and Measurements, Application Notes AN-13, 14, and 15, respectively. These application notes can be found in the Conexant Applications Handbook. The layout should be optimized for lowest noise on the Bt218 power and ground lines by shielding the digital inputs and providing good decoupling. The lead length between groups of VAA and GND pins should be as short as possible to minimize inductive ringing.

### 2.2 Ground Planes

Use a single ground plane covering both digital and analog logic.

#### 2.3 Power Planes

### 2.3 Power Planes

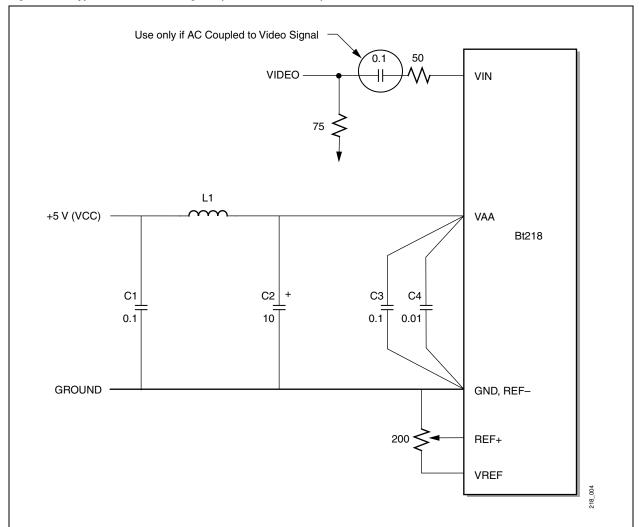

The Bt218 and any associated analog circuitry should have their own power plane, referred to as the analog power plane. This power plane should be connected to the regular PCB power plane (VCC) at a single point through a ferrite bead, as illustrated in Figure 2-1. Table 2-1 lists the parts. This bead should be located within 3 inches of the Bt218.

The regular PCB power plane should provide power to all digital logic on the PC board, and the analog power plane should provide power to all Bt218 power pins, any voltage reference circuitry, and any input amplifiers. It is important that the regular PCB power plane does not overlay the analog power plane.

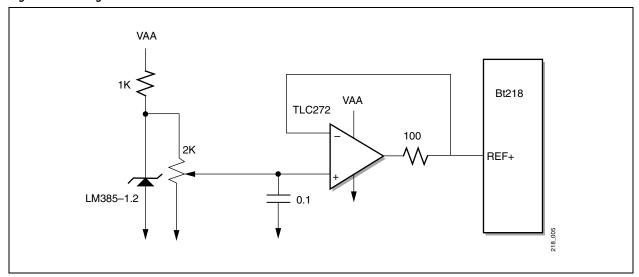

Figure 2-1. Typical Connection Diagram (Internal Reference)

2.3 Power Planes

Table 2-1. Typical Parts (Internal Reference)

| Location | Description                    | Vendor Part Number    |

|----------|--------------------------------|-----------------------|

| C1, C3   | 0.1 μF ceramic capacitor       | Erie RPE112Z5U104M50V |

| C2       | 10 μF capacitor                | Mallory CSR13G106KM   |

| C4       | 0.01 μF ceramic chip capacitor | AVX 12102T103QA1018   |

| L1       | Ferrite bead                   | Fair-Rite 2743001111  |

**NOTE(S):** The vendor numbers above are listed only as a guide. Substitution of devices with similar characteristics will not affect the performance of the Bt218.

#### **Supply Decoupling**

The bypass capacitors should be installed with the shortest leads possible, consistent with reliable operation, to reduce the lead inductance.

Each group of VAA and GND pins should have a 0.1 mF ceramic chip capacitor located as close as possible to the device pins. The capacitors should be connected directly to the VAA and GND pins with short, wide traces.

#### **Signal Interconnect**

The digital signals of the Bt218 must be isolated as much as possible from the analog inputs and other analog circuitry to prevent crosstalk. Also, these digital signals should not overlay the analog power plane.

Termination resistors for the digital signals should be connected to the digital PCB power and ground planes.

### 2.4 Application Information

# Using the Internal Reference

The Bt218 has a 1.2 V on-chip reference available (VREF). VREF may be divided down and used to drive the REF+ input, as illustrated in Figure 2-1. The 200 W potentiometer serves three purposes:

- 1. To allow adjustment for different video signal levels,

- 2. To allow for video level tolerances, and

- 3. To adjust for tolerance of the internal reference.

VREF should supply at least 6 mA of current to maintain voltage stability over temperature. Thus, VREF should drive a resistive load between 90 and 240 W.

## Using An External Reference

Figure 2-2 illustrates the use of a 1.2 V LM385 and a TLC272 to generate a 0–1.2 V reference for applications that require a better reference tempco than the internal reference can supply. Supply decoupling of the op-amp is not shown. Any standard op-amp may be used that can operate from a single +5 V supply.

To prevent ringing in the TLC272 from clock kickback, a 100 W resistor is recommended, as illustrated in Figure 2-2. If an op-amp is chosen that has a better transient response than the TLC272, the resistor may not be needed. This circuit may also be used to drive the Ref– if a value other than ground is desired. Because single-supply op-amps are limited, Ref– may not be set below ~300 mV. To drive Ref– to true 0 V in the op-amp configuration, a dual supply must be used. Extreme care must be used in power sequencing to ensure all positive supplies (op-amp and A/D) power on before the negative supply. This will prevent latchup of the A/D.

Figure 2-2. Using an External Reference

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

2.4 Application Information

# AC-Coupled vs. DC-Coupled Input

The Bt218 may be either AC or DC coupled to the video signal, as illustrated in Figure 2-1. The 75  $\Omega$  resistor to ground provides the typical 75  $\Omega$  termination required by video signals. The 50  $\Omega$  resistor provides isolation from any clock kick-back noise on VIN and prevents it from being coupled onto the video signal. If the Bt218 is DC-coupled to the video signal, the 0.1 mF capacitor is not used and CLAMP should be grounded.

#### Zeroing

Unlike many CMOS A/D converters requiring the comparators to be zeroed every clock cycle, the comparators in the Bt218 are designed to be only periodically zeroed. It is convenient to assert ZERO during each horizontal blanking interval.

Before the Bt218 is used after a power-up condition, ZERO must be a logical one for at least 1000 clock cycles (cumulative) to initialize the comparators to the rated linearity. In normal video applications this will be transparent because of the number of horizontal scan lines that will have occurred before the Bt218 was used.

While the recommended zeroing interval is maintained, the Bt218 will meet linearity specifications. The longer the time between zeroing intervals, the more the linearity error increases.

#### **Input Ranges**

Table 2-2 lists some common video signal amplitudes. If a signal may possibly exceed 1.2 V, it should be attenuated (with a resistor divider network) so as not to exceed the 1.2 V input range.

Table 2-2. Video Signal Tolerances

| Video Standard  | Nominal Amplitude Worst Case Amplitudes |            |

|-----------------|-----------------------------------------|------------|

| RS-170 w/o sync | 1.0 V BLACK-WHITE                       | 0.9–1.1 V  |

| RS-170 w/o sync | 1.4 V SYNC-WHITE                        | 1.2–1.6 V  |

| RS-170 w/sync   | 1.2 V SYNC-WHITE                        | 1.0–1.4 V  |

| RS-170 w/sync   | 0.7 V BLACK-WHITE                       | 0.6-0.85 V |

When a full-scale range less than 0.7 V is used to digitize, the Bt218's integral linearity errors are constant in terms of voltage, regardless of the value of the reference voltage. Lower reference voltages will, therefore, produce larger integral linearity errors in terms of LSBs.

For example, with a reference difference of 0.6 V, 0.6 V video signals may be digitized. However, the Integral Linearity (IL) error will increase to about  $\pm 1.8$  LSB, and the SNR will be about 40 db. With a reference difference of 0.5 V, 0.5 V video signals may be digitized with an IL error of about  $\pm 2$  LSB, and the SNR will be approximately 39 db.

#### **Output Noise**

Although the Bt218 does exhibit some output noise for a DC input, the output noise remains relatively constant for any input bandwidth (see the AC Characteristics section). Competitive A/D converters have no noise for a DC input; however, the output noise increases greatly as the input bandwidth and clock rate increase.

#### **PC Board Sockets**

If a socket is required, a low-profile socket is recommended, such as AMP part number 641746–2 for the PLCC package.

2.4 Application Information

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

#### ESD and Latchup Considerations

Correct ESD-sensitive handling procedures are required to prevent device damage, which can produce symptoms of catastrophic failure or erratic device behavior with somewhat leaky inputs.

All logic inputs should be held low until power to the device has settled to the specified tolerance. Power decoupling networks with large time constants should be avoided. They could delay VAA power to the device. Ferrite beads must be used only for analog power VAA decoupling. Inductors can cause a power supply time constant delay that induces latchup.

Latchup can be prevented by ensuring that all VAA pins are at the same potential and that the VAA supply voltage is applied before the signal pin voltages. The correct power-up sequence ensures that any signal pin voltage will never exceed the power supply voltage by more than +0.5 V.

# 3.0 Parametric Information

## 3.1 DC Electrical Parameters

Table 3-1. Recommended Operating Conditions

| Parameters                     | Symbol | Min       | Тур          | Max  | Units |

|--------------------------------|--------|-----------|--------------|------|-------|

| Power Supply                   | VAA    | 4.5       | 5.00         | 5.5  | V     |

| Voltage References             |        |           |              |      |       |

| Тор                            | REF+   | 0.7       | 1            | 2.0  | V     |

| Bottom                         | REF-   | 0         | 0            | 1.3  | V     |

| Difference (Top-Bottom)        | _      | 0.7       | 1            | 1.2  | V     |

| Input Amplitude Range          | _      | 0.7       | 1            | 1.2  | V     |

| Analog Input Range             | _      | _         | REF- to REF+ | _    | V     |

| LEVEL Input Voltage            | _      | GND - 0.5 | REF-         | REF+ | V     |

| Time between Zeroing Intervals | _      | _         | 60           | 150  | μs    |

| Ambient Operating Temperature  | TA     | 0         | _            | +70  | °C    |

Table 3-2. Absolute Maximum Ratings

| Parameters                                        | Symbol | Min       | Тур | Max       | Units |

|---------------------------------------------------|--------|-----------|-----|-----------|-------|

| VAA (Measured to GND)                             | _      | _         | _   | 7.0       | V     |

| Voltage on any Signal Pin <sup>(1)</sup>          | _      | GND - 0.5 | _   | VAA + 0.5 | V     |

| Analog Input Voltage                              | _      | GND - 0.5 | _   | VAA + 0.5 | V     |

| R/2 Output Current                                | _      | _         | _   | 25        | μА    |

| Ambient Operating Temperature                     | TA     | -55       | _   | +125      | °C    |

| Storage Temperature                               | TS     | -65       | _   | +150      | °C    |

| Junction Temperature                              | TJ     | _         | _   | +150      | °C    |

| Soldering Temperature<br>(5 Seconds, ¼" from Pin) | TSOL   | _         | _   | 260       | °C    |

| Vapor Phase Soldering<br>(1 Minute)               | TVSOL  | _         | _   | 220       | °C    |

#### NOTE(S).

<sup>(1)</sup> This device employs high-impedance CMOS devices on all signal pins. It should be handled as an ESD-sensitive device. Voltage on any signal pin that exceeds the power supply voltage by more than +0.5 V can induce destructive latchup.

<sup>2.</sup> Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

3.1 DC Electrical Parameters

Table 3-3. DC Characteristics (1 of 2)

| Parameters                              | Symbol | Min | Тур        | Max | Units  |

|-----------------------------------------|--------|-----|------------|-----|--------|

| Resolution                              | _      | 8   | 8          | 8   | Bits   |

| Accuracy                                |        |     |            |     |        |

| Integral Linearity Error <sup>(1)</sup> | IL     | _   | ±0.5       | ±1  | LSB    |

| Differential Linearity Error            | DL     | _   | ±0.25      | ±1  | LSB    |

| Output Noise <sup>(2)</sup>             | _      | _   | ±1         | _   | LSB    |

| Coding                                  | I      | l   | I          |     | l      |

| No Missing Codes                        | _      | _   | Guaranteed | _   | Binary |

| VIN Analog Inputs <sup>(3)</sup>        |        |     |            |     |        |

| CLAMP = 0                               |        |     |            |     |        |

| Input Current (Leakage)                 | IB     | _   | _          | 1   | μА     |

| Input Capacitance                       | CAIN   | _   | 35         | _   | pF     |

| CLAMP = 1                               |        | •   |            | 1   | 1      |

| Input Impedance                         | RIN    | _   | 50         | _   | Ω      |

| REF+ Reference Input                    |        |     |            |     |        |

| Input Impedance                         | RREF+  | _   | 500        | _   | Ω      |

| Digital Inputs                          |        |     |            |     |        |

| Input High Voltage                      | VIH    | 2.0 | _          | _   | V      |

| Input Low Voltage                       | VIL    | _   | _          | 0.8 | V      |

| Input High Current (Vin = 2.4 V)        | IIH    | _   | _          | 1   | μА     |

| Input Low Current (Vin = 0.4 V)         | IIL    | _   | _          | -1  | μА     |

| Input Capacitance                       | CIN    | _   | 10         | _   | pF     |

| Digital Outputs                         |        |     |            |     |        |

| Output High Voltage (IOH = -50 μA)      | VOH    | 2.4 | _          | _   | V      |

| Output Low Voltage (IOL = 1.6 mA)       | VOL    | _   | _          | 0.4 | V      |

| Three-State Current                     | IOZ    | _   | _          | 10  | μА     |

| Output Capacitance                      | COUT   | _   | _          | 10  | pF     |

3.0 Parametric Information Bt218

#### 3.1 DC Electrical Parameters

20 MSPS Monolithic CMOS 8-Bit Flash Video A/D Converter

Table 3-3. DC Characteristics (2 of 2)

| Parameters                 | Symbol | Min | Тур | Max | Units |

|----------------------------|--------|-----|-----|-----|-------|

| Internal Voltage Reference | VREF   | _   | 1.2 | _   | V     |

| Regulation (at 6 mA)       |        | _   | 5   | _   | mV    |

| Output Current             | IREF   | _   | _   | 15  | mA    |

#### NOTE(S):

- (1) Using best-fit linearity (offset independent).

- (2) Clock duty cycle adjusted for minimum output noise for a DC input. For a DC input, output noise may increase if clock duty cycle is not adjusted.

- (3) LEVEL = GND.

- 4. Test conditions (unless otherwise specified): "Recommended Operating Conditions" with REF+ = 1 V and REF− = GND. REF− ≤Vin ≤REF+, and LEVEL = float. Typical values are based on nominal temperature, i.e. room temperature, and nominal voltage, i.e. 5 V.

3.2 AC Electrical Parameters

### 3.2 AC Electrical Parameters

Table 3-4. AC Characteristics (1 of 3)

| Parameters                           | Symbol | Min | Тур | Max  | Units |

|--------------------------------------|--------|-----|-----|------|-------|

| Conversion Rate                      | Fs     | _   | _   | 20   | MHz   |

| Clock Cycle Time (Figure 3-1)        | 1      | 50  | _   | _    | ns    |

| Clock Low Time                       | 2      | 20  | _   | _    | ns    |

| Clock High Time                      | 3      | 20  | _   | _    | ns    |

| Data Output Delay Time (Figure 3-2)  | 4      | _   | _   | 40   | ns    |

| Data Output Hold Time                | 5      | 9   | _   | _    | ns    |

| OE* Asserted to D[7:0] Valid         | 6      | _   | _   | 25   | ns    |

| OE* Negated to D[7:0] 3-Stated       | 7      | _   | _   | 25   | ns    |

| ZERO Setup Time                      | 8      | 0   | _   | _    | ns    |

| ZERO Hold Time                       | 9      | 20  | _   | _    | ns    |

| ZERO, CLAMP High Time <sup>(1)</sup> | _      | 1   | _   | _    | Clock |

| Aperture Delay                       | 10     | _   | 10  | _    | ns    |

| Aperture Jitter                      | _      | _   | 50  | _    | ps    |

| Full Power Input Bandwidth           | BW     | _   | _   | Fs/2 | MHz   |

| Transient Response <sup>(2)</sup>    | _      | _   | 1   | _    | Clock |

| Overload Recovery <sup>(3)</sup>     | _      | _   | 1   | _    | Clock |

| Zero Recovery Time <sup>(4)</sup>    | _      | _   | 1   | _    | Clock |

| RMS Signal-to-Noise Ratio            | SNR    |     |     |      |       |

| Fin = 4.20 MHz, Fs = 12.27 MHz       | _      | _   | 44  | _    | dB    |

| Fin = 4.20 MHz, Fs = 13.50 MHz       | _      | _   | 44  | _    | dB    |

| Fin = 4.20 MHz, Fs = 14.32 MHz       | _      | _   | 44  | _    | dB    |

| Fin = 5.75 MHz, Fs = 13.50 MHz       | _      | _   | 43  | _    | dB    |

| Fin = 5.75 MHz, Fs = 14.75 MHz       | _      | _   | 43  | _    | dB    |

| Fin = 5.75 MHz, Fs = 17.72 MHz       | _      | _   | 43  | _    | dB    |

| Fin = 10.0 MHz, Fs = 20.00 MHz       |        | _   | 39  | _    | dB    |

#### 3.2 AC Electrical Parameters

Table 3-4. AC Characteristics (2 of 3)

| Parameters                               | Symbol | Min | Тур | Max | Units |

|------------------------------------------|--------|-----|-----|-----|-------|

| RMS Signal and Distortion-to-Noise Ratio | SINAD  |     |     |     |       |

| Fin = 4.20 MHz, Fs = 12.27 MHz           | _      | _   | 42  | _   | dB    |

| Fin = 4.20 MHz, Fs = 13.50 MHz           | _      | _   | 42  | _   | dB    |

| Fin = 4.20 MHz, Fs = 14.32 MHz           | _      | _   | 42  | _   | dB    |

| Fin = 5.75 MHz, Fs = 13.50 MHz           | _      | _   | 41  | _   | dB    |

| Fin = 5.75 MHz, Fs = 14.75 MHz           | _      | _   | 41  | _   | dB    |

| Fin = 5.75 MHz, Fs = 17.72 MHz           | _      | _   | 41  | _   | dB    |

| Fin = 10.0 MHz, Fs = 20.00 MHz           | _      | _   | 37  | _   | dB    |

| Total Harmonic Distortion                | THD    | •   | •   |     |       |

| Fin = 4.20 MHz, Fs = 12.27 MHz           | _      | _   | 47  | _   | dB    |

| Fin = 4.20 MHz, Fs = 13.50 MHz           | _      | _   | 47  | _   | dB    |

| Fin = 4.20 MHz, Fs = 14.32 MHz           | _      | _   | 47  | _   | dB    |

| Fin = 5.75 MHz, Fs = 13.50 MHz           | _      | _   | 47  | _   | dB    |

| Fin = 5.75 MHz, Fs = 14.75 MHz           | _      | _   | 47  | _   | dB    |

| Fin = 5.75 MHz, Fs = 17.72 MHz           | _      | _   | 47  | _   | dB    |

| Fin = 10.0 MHz, Fs = 20.00 MHz           | _      | _   | 44  | _   | dB    |

| Spurious Free Dynamic Range              | SFDR   | •   | •   |     |       |

| Fin = 4.20 MHz, Fs = 12.27 MHz           | _      | _   | 50  | _   | dB    |

| Fin = 4.20 MHz, Fs = 13.50 MHz           | _      | _   | 50  | _   | dB    |

| Fin = 4.20 MHz, Fs = 14.32 MHz           | _      | _   | 50  | _   | dB    |

| Fin = 5.75 MHz, Fs = 13.50 MHz           | _      | _   | 50  | _   | dB    |

| Fin = 5.75 MHz, Fs = 14.75 MHz           | _      | _   | 50  | _   | dB    |

| Fin = 5.75 MHz, Fs = 17.72 MHz           | _      | _   | 50  | _   | dB    |

| Fin = 10.0 MHz, Fs = 20.00 MHz           | _      | _   | 47  | _   | dB    |

3.2 AC Electrical Parameters

**Table 3-4. AC Characteristics** (3 of 3)

| Parameters                                     | Symbol | Min | Тур | Max | Units  |

|------------------------------------------------|--------|-----|-----|-----|--------|

| Differential Gain Error <sup>(5)</sup>         | DG     | _   | 2   | _   | %      |

| Differential Phase Error <sup>(5)</sup>        | DP     | _   | 1   | _   | Degree |

| Supply Current (Excluding REF+) <sup>(6)</sup> | IAA    | _   | 100 | 160 | mA     |

| Pipeline Delay <sup>(7)</sup>                  | _      | 2   | 2   | 2   | Clocks |

Test conditions (unless otherwise specified): "Recommended Operating Conditions" with REF+ = 1 V and REF-  $\leq$  QND. REF-  $\leq$ Vin  $\leq$  REF+ and , LEVEL = float. TTL input values are 0–3 V with input rise and fall times  $\leq$ 4 ns, measured between the 10 percent and 90 percent points. Timing reference points at 1.5 V for digital inputs and outputs. D0–D7 and OVERFLOW output load  $\leq$ 40 pF. Typical values are based on nomimal temperature, i.e. room temperature, and nominal voltage, i.e., 5 V.

#### NOTE(S):

- (1) Number of clock cycles ZERO is a logical one does not affect linearity. For best performance, ZERO should be a logical one for an odd number of clock cycles.

- (2) For full-scale step, input, full accuracy attained in specified time.

- (3) Time to recover to full accuracy after a >1.2 V input signal.

- (4) Time to recover to full accuracy following a zero cycle.

- (5) 4x NTSC subcarrier, unlocked.

- (6) IAA (typ) at VAA = 5.0 V, Fin = 4.2 MHz, and Fs = 14.32 MHz,  $T_{CASE}$  = Ambient. IAA (max) at VAA = 5.5 V, Fin = 10 MHz, and Fs = 20 MHz,  $T_{CASE}$  = 0 °C.

- (7) Pipeline delay is defined as discrete clock period in addition to the half-cycle analog sampling delay.

Figure 3-1. Input and Output Timing

Figure 3-2. Bt218KPJ Output Delay vs. Capacitive Loading

3.3 Package Drawings

## 3.3 Package Drawings

Figure 3-3. 24-Pin 0.300" Plastic DIP

Figure 3-4. 28-Pin Plastic J-Lead (PLCC)

## 3.4 Revision History

Table 3-5. Revision History

| Revision | Change from Previous Revision                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| В        | Changes to Figure 2-2. New configuration for the external reference voltage.                                                                                                   |

| С        | Deleted 30 MHz device information. Revised PC Board Layout Considerations. Revised and expanded DC Characteristics. Added Figure 3-2. Datasheet status changed to Preliminary. |

| D        | Obsolete EVM module.                                                                                                                                                           |

#### **Further Information**

literature@conexant.com 1-800-854-8099 (North America) 33-14-906-3980 (International)

#### Web Site

www.conexant.com

#### World Headquarters

Conexant Systems, Inc. 4311 Jamboree Road P. O. Box C Newport Beach, CA 92658-8902 Phone: (949) 483-4600

Phone: (949) 483-4600 Fax: (949) 483-6375

#### U.S. Florida/South America

Phone: (727) 799-8406 Fax: (727) 799-8306

**U.S. Los Angeles** Phone: (805) 376-0559

Fax: (805) 376-8180

## **U.S. Mid-Atlantic** Phone: (215) 244-6784

Fax: (215) 244-9292

#### U.S. North Central

Phone: (630) 773-3454 Fax: (630) 773-3907

#### U.S. Northeast

Phone: (978) 692-7660 Fax: (978) 692-8185

#### U.S. Northwest/Pacific West

Phone: (408) 249-9696 Fax: (408) 249-7113

#### U.S. South Central

Phone: (972) 733-0723 Fax: (972) 407-0639

#### U.S. Southeast

Phone: (919) 858-9110 Fax: (919) 858-8669

#### U.S. Southwest

Phone: (949) 483-9119 Fax: (949) 483-9090

#### **APAC Headquarters**

Conexant Systems Singapore, Pte.

1 Kim Seng Promenade Great World City #09-01 East Tower SINGAPORE 237994 Phone: (65) 737 7355 Fax: (65) 737 9077

#### Australia

Phone: (61 2) 9869 4088 Fax: (61 2) 9869 4077

#### China

Phone: (86 2) 6361 2515 Fax: (86 2) 6361 2516

#### Hong Kong

Phone: (852) 2827 0181 Fax: (852) 2827 6488

#### India

Phone: (91 11) 692 4780 Fax: (91 11) 692 4712

#### Korea

Phone: (82 2) 565 2880 Fax: (82 2) 565 1440

Phone: (82 53) 745 2880 Fax: (82 53) 745 1440

#### **Europe Headquarters**

Conexant Systems France Les Taissounieres B1 1681 Route des Dolines BP 283 06905 Sophia Antipolis Cedex

FRANCE Phone: (33 1) 41 44 36 50

Phone: (33 1) 41 44 36 50 Fax: (33 4) 93 00 33 03

#### **Europe Central**

Phone: (49 89) 829 1320 Fax: (49 89) 834 2734

#### **Europe Mediterranean**

Phone: (39 02) 9317 9911 Fax: (39 02) 9317 9913

#### **Europe North**

Phone: (44 1344) 486 444 Fax: (44 1344) 486 555

#### **Europe South**

Phone: (33 1) 41 44 36 50 Fax: (33 1) 41 44 36 90

#### Middle East Headquarters

Conexant Systems Commercial (Israel) Ltd. P. O. Box 12660 Herzlia 46733, ISRAEL Phone: (972 9) 952 4064 Fax: (972 9) 951 3924

#### Japan Headquarters

Conexant Systems Japan Co., Ltd. Shimomoto Building 1-46-3 Hatsudai, Shibuya-ku, Tokyo 151-0061 JAPAN Phone: (81 3) 5371-1567 Fax: (81 3) 5371-1501

#### Taiwan Headquarters

Conexant Systems, Taiwan Co., Ltd. Room 2808 International Trade Building 333 Keelung Road, Section 1 Taipei 110, TAIWAN, ROC Phone: (886 2) 2720 0282 Fax: (886 2) 2757 6760