MC68HC11ED0

Technical Summary

HCMOS

Microcontroller Unit

# **MC68HC11ED0**

## **Technical Summary — MC68HC11ED0**

## **List of Sections**

| Section 1. General Description15                   |

|----------------------------------------------------|

| Section 2. Pin Assignments19                       |

| Section 3. Central Processor Unit (CPU)23          |

| Section 4. Operating Modes and On-Chip Memory 43   |

| Section 5. Resets and Interrupts                   |

| Section 6. Parallel Input/Output (I/O) Ports65     |

| Section 7. Serial Communications Interface (SCI)71 |

| Section 8. Serial Peripheral Interface (SPI)81     |

| Section 9. Timing System87                         |

MC68HC11ED0 — Rev. 1.0

**List of Sections**

## **Technical Summary — MC68HC11ED0**

## **Table of Contents**

## **Section 1. General Description**

| 1.1                                              | Contents                                                                                                                                                                                                                 |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2                                              | Introduction                                                                                                                                                                                                             |

| 1.3                                              | Features                                                                                                                                                                                                                 |

| 1.4                                              | Structure17                                                                                                                                                                                                              |

| 1.5                                              | Ordering Information18                                                                                                                                                                                                   |

|                                                  | Section 2. Pin Assignments                                                                                                                                                                                               |

| 2.1                                              | Contents                                                                                                                                                                                                                 |

| 2.2                                              | Introduction19                                                                                                                                                                                                           |

| 2.3                                              | 44-Pin Plastic-Leaded Chip Carrier (PLCC)                                                                                                                                                                                |

| 2.4                                              | 44-Pin Quad Flat Pack (QFP)21                                                                                                                                                                                            |

| 2.5                                              | 40-Pin Plastic Dual In-Line Package (DIP)22                                                                                                                                                                              |

|                                                  | Section 3. Central Processor Unit (CPU)                                                                                                                                                                                  |

| 3.1                                              | Contents                                                                                                                                                                                                                 |

| 3.2                                              | Introduction                                                                                                                                                                                                             |

| 3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.4<br>3.3.5 | CPU Registers       24         Accumulators A, B, and D       25         Index Register X (IX)       26         Index Register Y (IY)       26         Stack Pointer (SP)       26         Program Counter (PC)       28 |

| 0.0.0                                            |                                                                                                                                                                                                                          |

MC68HC11ED0 — Rev. 1.0

# **Table of Contents**

| 3.3.6  | Condition Code Register (CCR)                 | .29  |

|--------|-----------------------------------------------|------|

| 3.3.6. | 1 Carry/Borrow (C)                            | .29  |

| 3.3.6. | 2 Overflow (V)                                | .29  |

| 3.3.6. | 3 Zero (Z)                                    | .29  |

| 3.3.6. | 4 Negative (N)                                | .30  |

| 3.3.6. | 5 I-Interrupt Mask (I)                        | .30  |

| 3.3.6. |                                               |      |

| 3.3.6. | 7 X-Interrupt Mask (X)                        | .30  |

| 3.3.6. | 8 STOP Disable (S)                            | .31  |

| 3.4    | Data Types                                    | .31  |

| 3.5    | Opcodes and Operands                          | .31  |

| 3.6    | Addressing Modes                              |      |

| 3.6.1  | Immediate                                     |      |

| 3.6.2  | Direct                                        |      |

| 3.6.3  | Extended                                      |      |

| 3.6.4  | Indexed                                       |      |

| 3.6.5  | Inherent                                      |      |

| 3.6.6  | Relative                                      | .34  |

| 3.7    | Instruction Set                               | .34  |

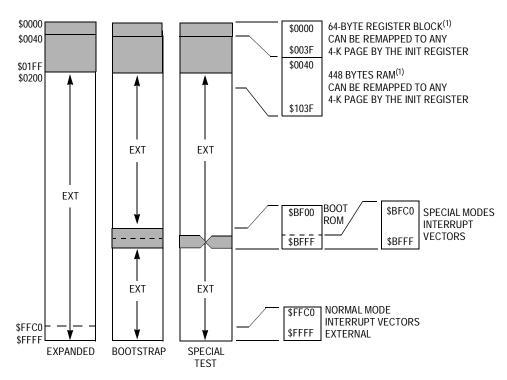

| S      | Section 4. Operating Modes and On-Chip Memory |      |

| 4.1    | Contents                                      | .43  |

| 4.2    | Introduction                                  | .43  |

| 4.3    | Operating Modes                               | .44  |

| 4.3.1  | Bootstrap Mode                                | .44  |

| 4.3.2  | Special Test Mode                             | .44  |

| 4.3.3  | Expanded Operating Mode                       | .45  |

| 4.4    | Mode Selection                                | . 46 |

| 4.5    | On-Chip Memory                                | .48  |

| 4.5.1  | Memory Map and Register Block                 | .49  |

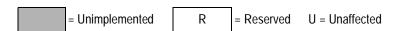

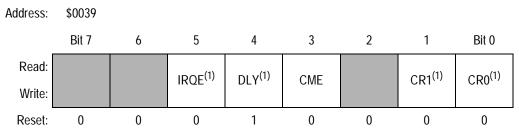

| 4.5.2  | RAM                                           | .56  |

## **Section 5. Resets and Interrupts**

| 5.1   | Contents                                                    | .57 |

|-------|-------------------------------------------------------------|-----|

| 5.2   | Introduction                                                | .57 |

| 5.3   | Resets                                                      | .57 |

| 5.4   | System Configuration Options Register                       | .60 |

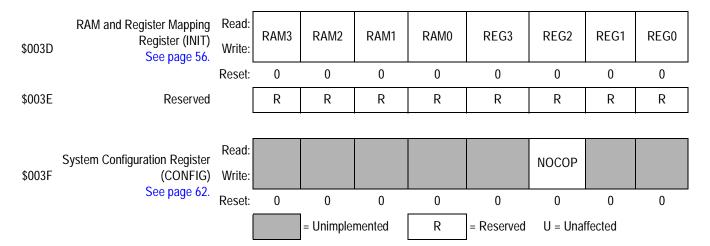

| 5.5   | Arm/Reset COP Timer Circuitry Register                      | .61 |

| 5.6   | Configuration Control Register                              | .62 |

| 5.7   | Highest Priority I-Bit Interrupt and Miscellaneous Register | .63 |

|       | Section 6. Parallel Input/Output (I/O) Ports                |     |

| 6.1   | Contents                                                    | .65 |

| 6.2   | Introduction                                                | .65 |

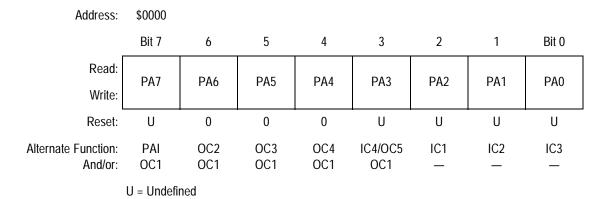

| 6.3   | Port A Data Register                                        | .66 |

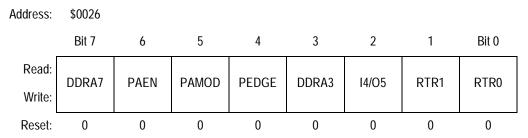

| 6.4   | Pulse Accumulator Control Register                          | .67 |

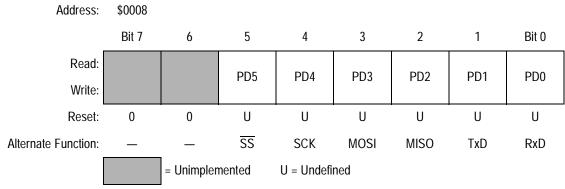

| 6.5   | Port D Data Register                                        | .68 |

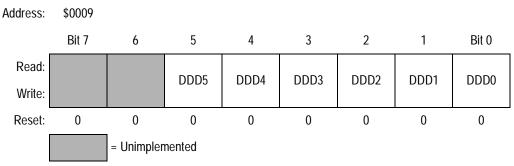

| 6.6   | Port D Data Direction Register                              | .69 |

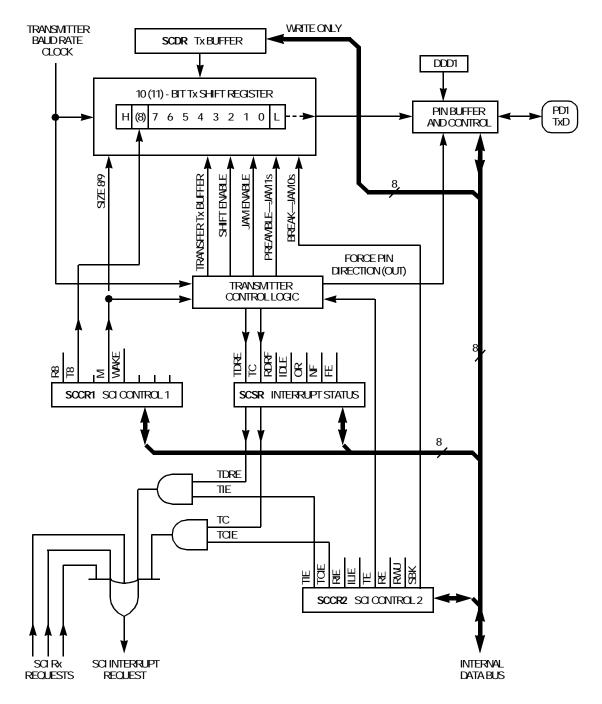

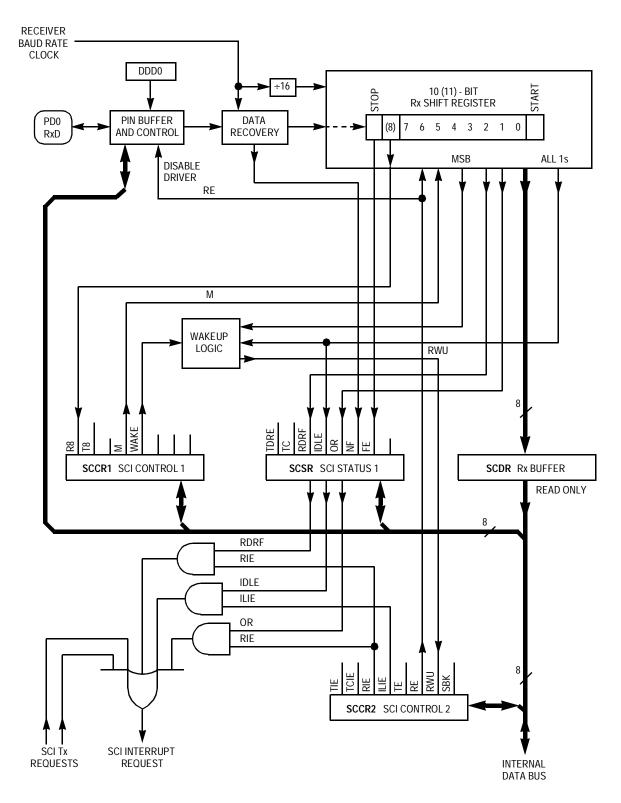

| 9     | Section 7. Serial Communications Interface (SCI)            |     |

| 7.1   | Contents                                                    | .71 |

| 7.2   | Introduction                                                | .71 |

| 7.3   | SCI Registers                                               | .74 |

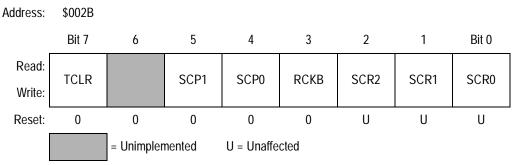

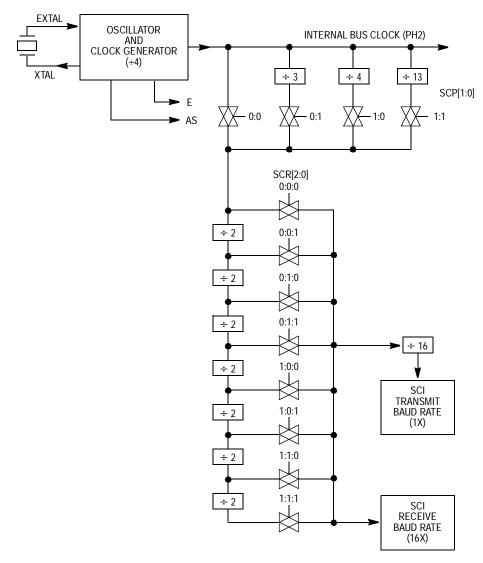

| 7.3.1 | Baud Rate Register                                          | .74 |

| 7.3.2 | Serial Communications Control Register 1                    | .77 |

| 7.3.3 | Serial Communications Control Register 2                    | .78 |

| 7.3.4 | Serial Communication Status Register                        | .79 |

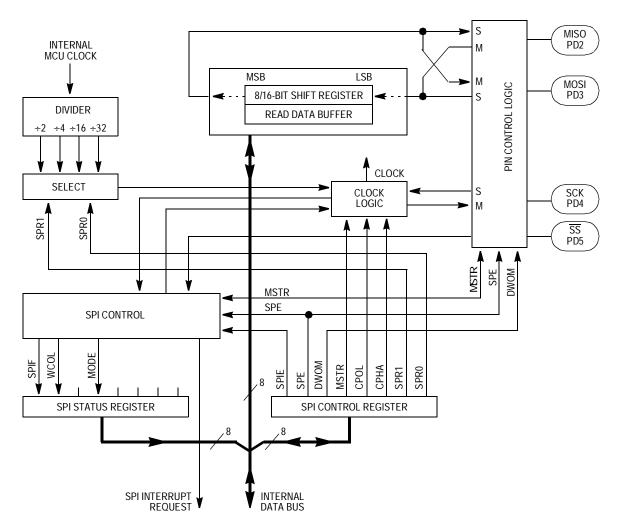

| 7.3.5 | Serial Communications Data Register                         | .80 |

MC68HC11ED0 — Rev. 1.0

## **Table of Contents**

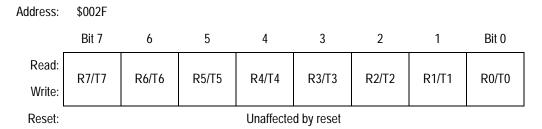

| 8.1                                                                                            | Contents                        |

|------------------------------------------------------------------------------------------------|---------------------------------|

| 8.2                                                                                            | Introduction                    |

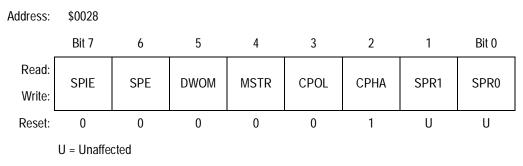

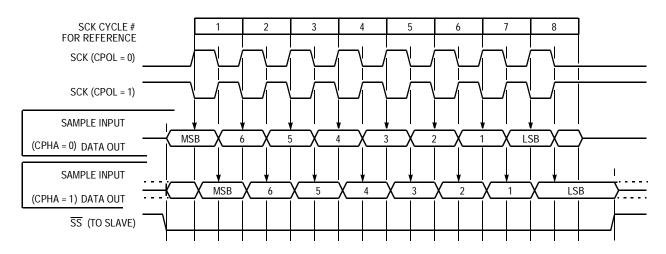

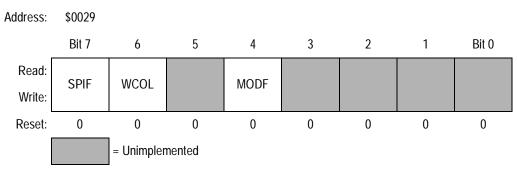

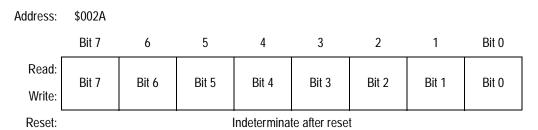

| 8.3<br>8.3.1<br>8.3.2<br>8.3.3                                                                 | SPI Registers                   |

|                                                                                                | Section 9. Timing System        |

| 9.1                                                                                            | Contents                        |

| 9.2                                                                                            | Introduction88                  |

| 9.3<br>9.3.1<br>9.3.2<br>9.3.3<br>9.3.4<br>9.3.5<br>9.3.6<br>9.3.7<br>9.3.8<br>9.3.9<br>9.3.10 | Timer Registers                 |

| 9.3.11                                                                                         | Timer Interrupt Flag 1 Register |

| 9.3.12<br>9.3.13                                                                               | 3                               |

| 9.4<br>9.4.1<br>9.4.2                                                                          | Pulse Accumulator               |

## **Technical Summary — MC68HC11ED0**

# **List of Figures**

| Figu                   | ıre                      | Title                    | Page              |

|------------------------|--------------------------|--------------------------|-------------------|

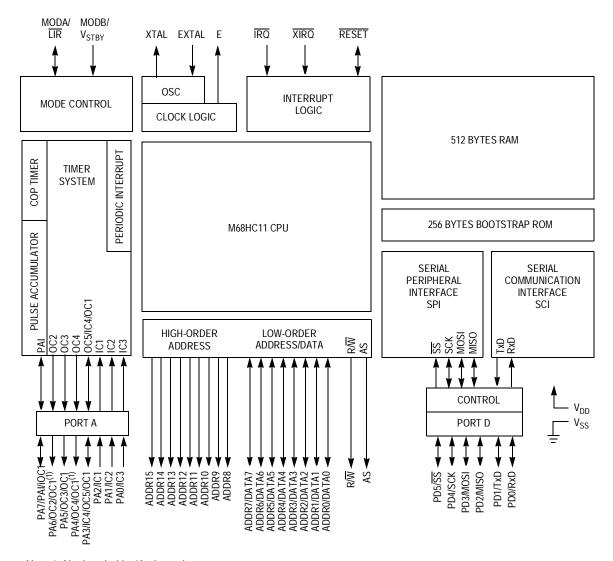

| 1-1                    | MC68HC11ED0 Bloc         | k Diagram                | 17                |

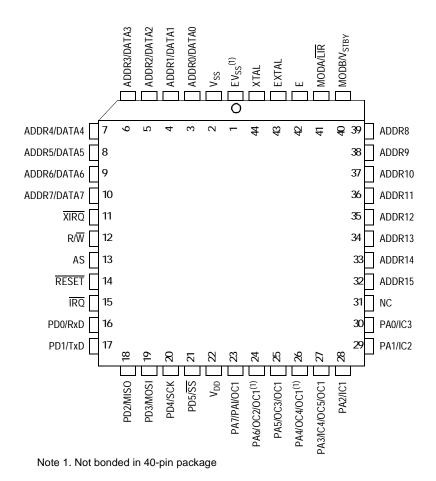

| 2-1                    | Pin Assignments for      | 44-Pin PLCC              | 20                |

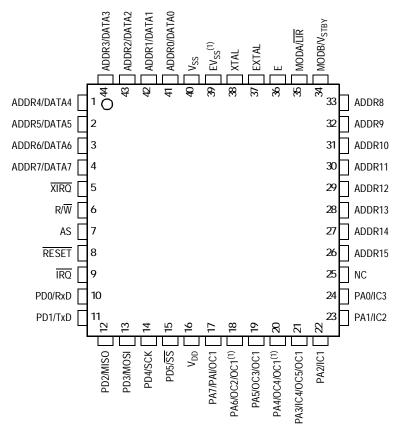

| 2-2                    | Pin Assignments for      | 44-Pin QFP               |                   |

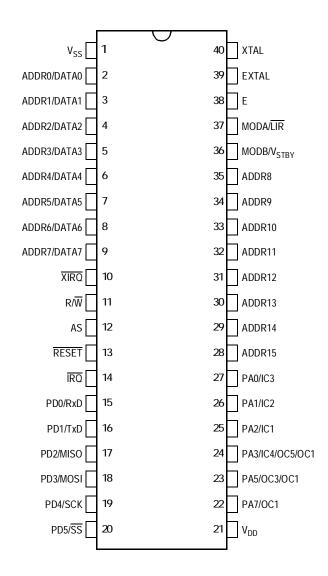

| 2-3                    | Pin Assignments for      | 40-Pin DIP               | 22                |

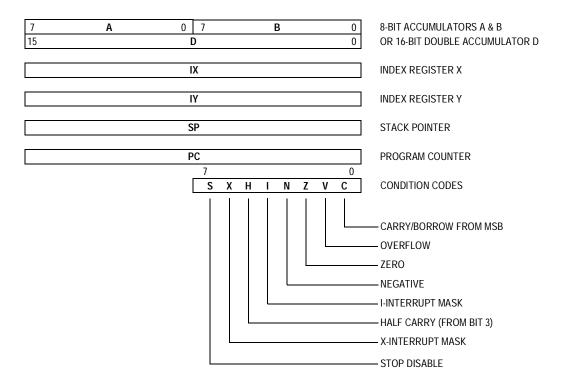

| 3-1                    | Programming Model        |                          | 25                |

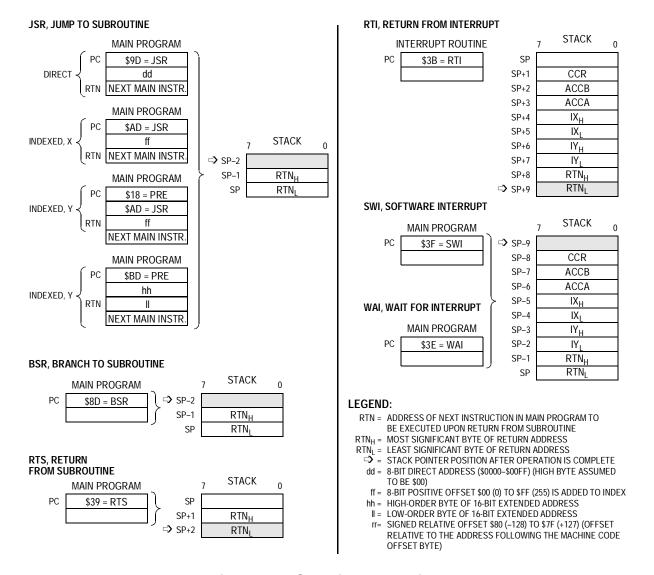

| 3-2                    | Stacking Operations      |                          |                   |

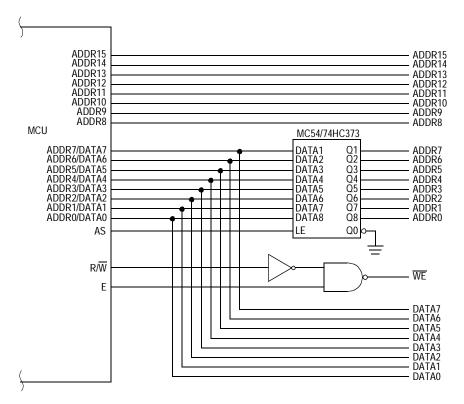

| 4-1                    | Address and Data De      | emultiplexing            | 46                |

| 4-2                    | Highest Priority I-Bit I | nterrupt                 |                   |

|                        |                          | s Register (HPRIO)       |                   |

| 4-3                    |                          | nory Map                 |                   |

| 4-4                    |                          | Bit Assignments          |                   |

| 4-5                    | RAM and Register M       | apping Register (INIT)   |                   |

| 5-1                    | System Configuration     | Options Register (OP     | TION)60           |

| 5-2                    | Arm/Reset COP Time       | er Circuitry Register (C | OPRST)61          |

| 5-3                    | System Configuration     | Register (CONFIG).       | 62                |

| 5-4                    | Highest Priority I-Bit I |                          |                   |

|                        | and Miscellaneous        | s Register (HPRIO)       |                   |

| 6-1                    | Port A Data Register     | (PORTA)                  | 66                |

| 6-2                    | Pulse Accumulator C      | ontrol Register (PACTI   | _) 67             |

| 6-3                    | Port D Data Register     | (PORTD)                  | 68                |

| 6-4                    | Port D Data Direction    | Register (DDRD)          | 69                |

| 7-1                    | SCI Transmitter Block    | k Diagram                | 72                |

| 7-2                    | SCI Receiver Block D     | Diagram                  | 73                |

| MC68HC11ED0 — Rev. 1.0 |                          |                          | Technical Summary |

|                        |                          |                          |                   |

## List of Figures

| Figur      | re Title                                                | Page  |

|------------|---------------------------------------------------------|-------|

| 7-3        | Baud Rate Register (BAUD)                               | 74    |

| 7-4        | SCI Baud Rate Generator Clock Diagram                   | 76    |

| 7-5        | Serial Communications Control Register 1 (SCCR1)        | 77    |

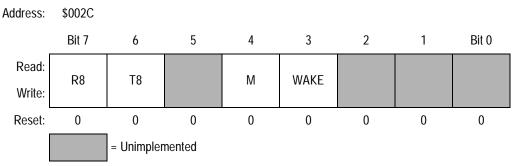

| <b>7-6</b> | Serial Communications Control Register 2 (SCCR2)        | 78    |

| 7-7        | Serial Communications Status Register (SCSR)            |       |

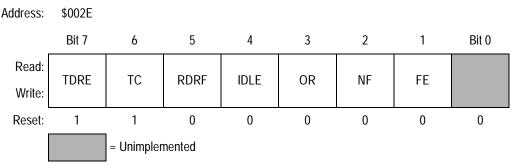

| 7-8        | Serial Communications Data Register (SCDR)              | 80    |

| 0.4        | CDI Digale Digarana                                     | 00    |

| 8-1        | SPI Block Diagram                                       |       |

| 8-2        | Serial Peripheral Control Register (SPCR)               |       |

| 8-3        | SPI Transfer Format                                     |       |

| 8-4<br>8-5 | Serial Peripheral Status Register (SPSR)                |       |

| 0-0        | Serial Periprieral Data I/O Register (SPDR)             | 00    |

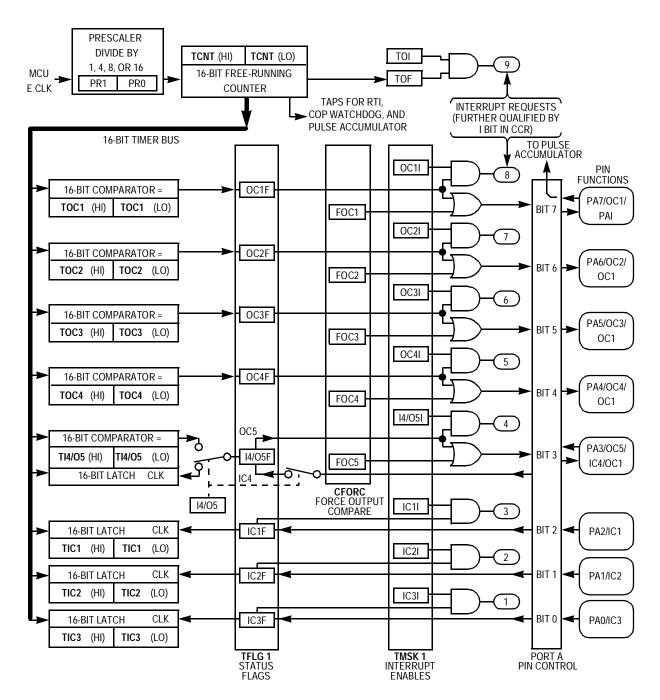

| 9-1        | Timer Block Diagram                                     | 90    |

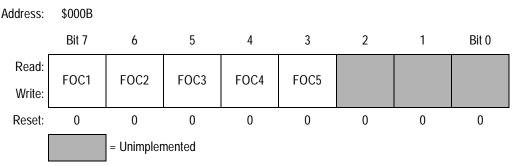

| 9-2        | Timer Compare Force Register (CFORC)                    |       |

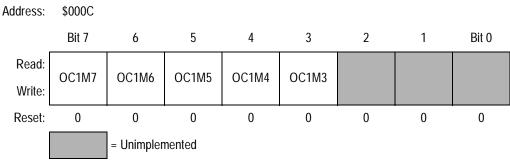

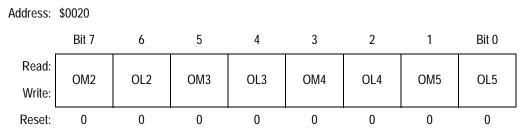

| 9-3        | Output Compare 1 Mask Register (OC1M)                   | 92    |

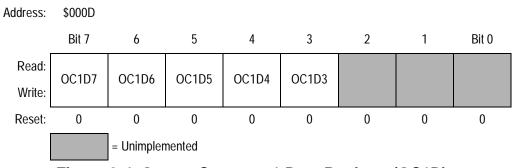

| 9-4        | Output Compare 1 Data Register (OC1D)                   |       |

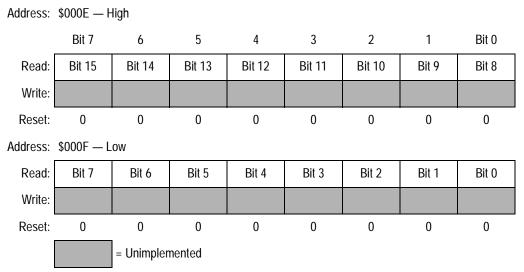

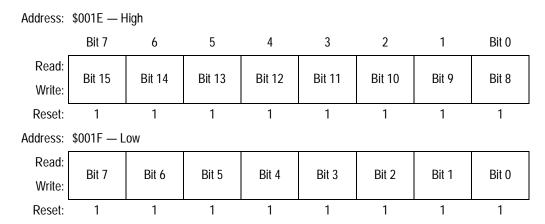

| 9-5        | Timer Count Register (TCNT)                             | 93    |

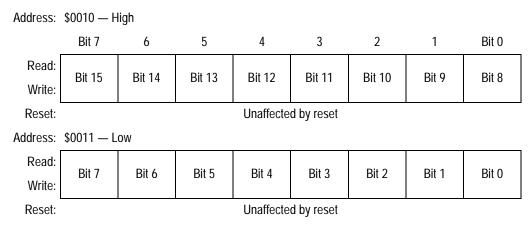

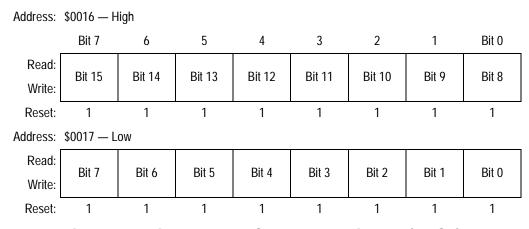

| 9-6        | Timer Input Capture Register 1 (TIC1)                   | 94    |

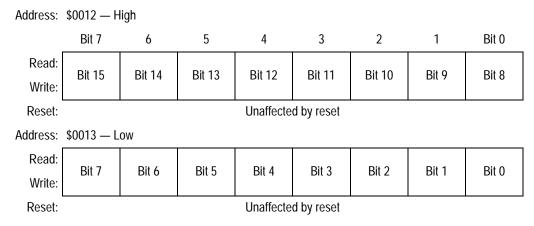

| 9-7        | Timer Input Capture Register 2 (TIC2)                   | 94    |

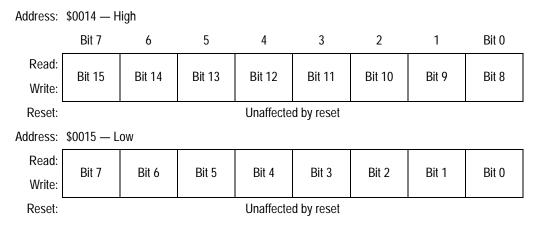

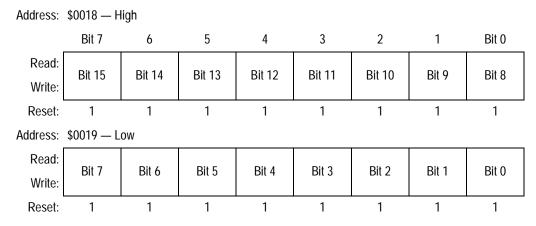

| 9-8        | Timer Input Capture Register 3 (TIC3)                   | 94    |

| 9-9        | Timer Output Compare Register 1 (TOC1)                  | 95    |

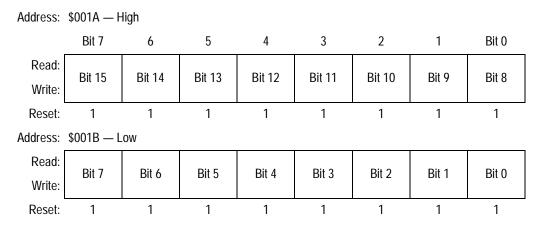

| 9-10       | Timer Output Compare Register 2 (TOC2)                  | 95    |

| 9-11       | Timer Output Compare Register 3 (TOC3)                  |       |

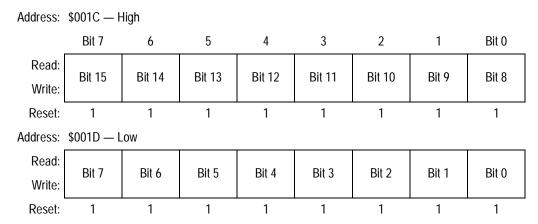

| 9-12       | Timer Output Compare Register 4 (TOC4)                  |       |

| 9-13       | Timer Input Capture4/Output Compare 5 Register (TI4/O5) |       |

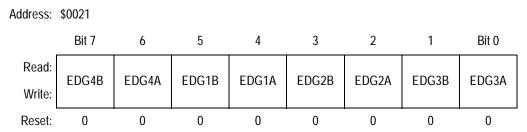

| 9-14       | Timer Control Register 1 (TCTL1)                        |       |

| 9-15       | Timer Control Register 2 (TCTL2)                        |       |

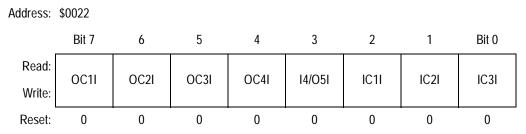

| 9-16       | Timer Interrupt Mask 1 Register (TMSK1)                 |       |

| 9-17       | Timer Interrupt Flag 1 Register (TFLG1)                 |       |

| 9-18       | Timer Interrupt Mask 2 Register (TMSK2)                 |       |

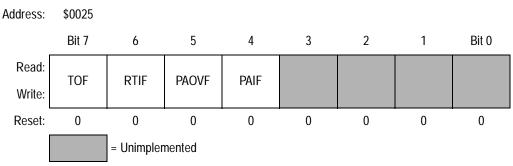

| 9-19       | Timer Interrupt Flag 2 Register (TFLG2)                 |       |

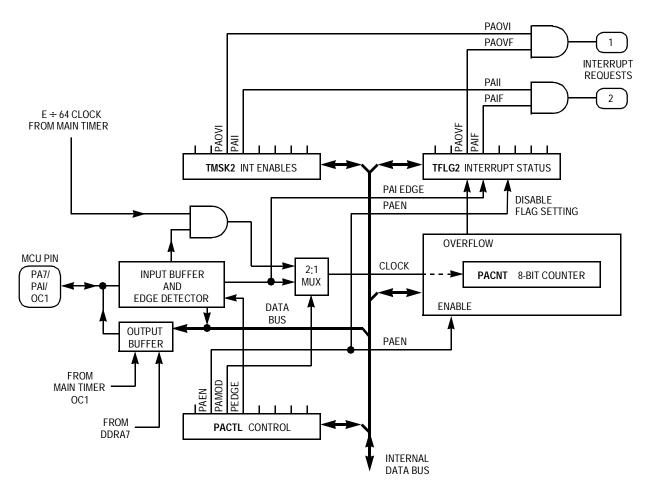

| 9-20       | Pulse Accumulator System Block Diagram                  |       |

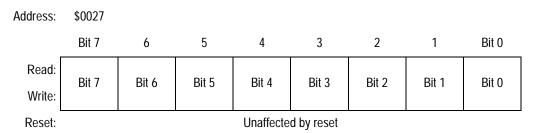

| 9-21       | Pulse Accumulator Country Register (PACNT)              |       |

| 9-22       | Pulse Accumulator Counter Register (PACNT)              | . 106 |

## **Technical Summary — MC68HC11ED0**

## **List of Tables**

| Title                                  | Page                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Ordering Information            | 18                                                                                                                                                                                                                                                                                                                                                                                               |

| Reset Vector Comparison                | 28                                                                                                                                                                                                                                                                                                                                                                                               |

| Instruction Set                        | 35                                                                                                                                                                                                                                                                                                                                                                                               |

| Interrupt and Reset Vector Assignments |                                                                                                                                                                                                                                                                                                                                                                                                  |

| COP Timer Rate Select                  | 61                                                                                                                                                                                                                                                                                                                                                                                               |

| Highest Priority Interrupt Selection   | 64                                                                                                                                                                                                                                                                                                                                                                                               |

| Input/Output Ports                     | 65                                                                                                                                                                                                                                                                                                                                                                                               |

| Prescaler Rates                        | 74                                                                                                                                                                                                                                                                                                                                                                                               |

| Baud Rates                             | 75                                                                                                                                                                                                                                                                                                                                                                                               |

| SPI Clock Rate Selects                 | 84                                                                                                                                                                                                                                                                                                                                                                                               |

| Timer Summary                          | 89                                                                                                                                                                                                                                                                                                                                                                                               |

| Timer Output Compare Actions           | 97                                                                                                                                                                                                                                                                                                                                                                                               |

| Timer Control Configuration            | 98                                                                                                                                                                                                                                                                                                                                                                                               |

| Timer Prescale                         | 101                                                                                                                                                                                                                                                                                                                                                                                              |

| Pulse Accumulator Timing               | 104                                                                                                                                                                                                                                                                                                                                                                                              |

| RTI Rates (Period Length)              | 105                                                                                                                                                                                                                                                                                                                                                                                              |

| RTI Rates (Frequency)                  | 105                                                                                                                                                                                                                                                                                                                                                                                              |

|                                        | Device Ordering Information.  Reset Vector Comparison. Instruction Set.  Interrupt and Reset Vector Assignments COP Timer Rate Select Highest Priority Interrupt Selection.  Input/Output Ports.  Prescaler Rates Baud Rates.  SPI Clock Rate Selects.  Timer Summary Timer Output Compare Actions Timer Control Configuration Timer Prescale Pulse Accumulator Timing RTI Rates (Period Length) |

MC68HC11ED0 — Rev. 1.0

List of Tables

## Technical Summary — MC68HC11ED0

## **Section 1. General Description**

#### 1.1 Contents

| 1.2 | Introduction         | 15 |

|-----|----------------------|----|

| 1.3 | Features             | 16 |

| 1.4 | Structure            | 17 |

| 1.5 | Ordering Information | 18 |

#### 1.2 Introduction

The MC68HC11ED0 is a low-cost member of the M68HC11 Family of microcontrollers (MCU). This MCU has a multiplexed address/data bus and is characterized by high speed and low-power consumption. The fully static design allows operation at frequencies from 3 MHz to dc.

Pin count is minimized for cost-sensitive applications. Because there is no on-chip read-only memory (ROM), this device is optimized for expanded-bus systems. On-chip serial peripheral interface (SPI) and serial communications interface (SCI) provide a convenient means or transferring data to and from internal random-access memory (RAM). Refer to Figure 1-1.

## **General Description**

#### 1.3 Features

#### Features include:

- M68HC11 CPU

- Power-saving stop and wait modes

- 512 bytes of RAM

- Multiplexed address and data buses

- Enhanced 16-bit timer with 4-stage programmable prescaler

- Three input capture (IC) channels

- Four output compare (OC) channels

- One additional channel, selectable as fourth IC or fifth OC

- 8-bit pulse accumulator

- Real-time interrupt circuit

- Computer operating properly (COP) watchdog

- Clock monitor

- Enhanced asynchronous non-return-to-zero (NRZ) SCI

- Enhanced SPI

- Eight bidirectional input/output (I/O) lines

- Three input-only lines

- Three output-only lines (one output-only line in 40-pin package)

- Packaging options:

- 44-pin plastic-leaded chip carrier (PLCC)

- 44-pin quad flat pack (QFP)

- 40-pin plastic dual in-line package (DIP)

General Description Structure

#### 1.4 Structure

See Figure 1-1 for a block diagram of the MC68HC11ED0 MCU.

Note 1. Not bonded in 40-pin package

Figure 1-1. MC68HC11ED0 Block Diagram

MC68HC11ED0 — Rev. 1.0

## **General Description**

## 1.5 Ordering Information

**Table 1-1** provides ordering information for the MC68HC11ED0. Refer to **Section 2. Pin Assignments**.

**Table 1-1. Device Ordering Information**

| Package      | Temperature                        | Description                                | Frequency                  | MC Order Number |                |

|--------------|------------------------------------|--------------------------------------------|----------------------------|-----------------|----------------|

|              | -40°C to +85°C                     | No ROM/EPROM<br>No EEPROM<br>512 bytes RAM | 2 MHz                      | MC68HC11ED0CFN2 |                |

|              | -40°C to +65°C                     |                                            | 3 MHz                      | MC68HC11ED0CFN3 |                |

| 44 nin DI CC | -40°C to +105°C                    |                                            | 2 MHz                      | MC68HC11ED0VFN2 |                |

| 44-pin PLCC  |                                    |                                            | 3 MHz                      | MC68HC11ED0VFN3 |                |

|              | 4000 1 40500                       |                                            | 2 MHz                      | MC68HC11ED0MFN2 |                |

|              | -40°C to +125°C                    |                                            | 3 MHz                      | MC68HC11ED0MFN3 |                |

|              | –40°C to +85°C                     | No ROM/EPROM<br>No EEPROM<br>512 bytes RAM | 2 MHz                      | MC68HC11ED0CFU2 |                |

|              |                                    |                                            | 3 MHz                      | MC68HC11ED0CFU3 |                |

| 44 nin OED   | -40°C to +105°C                    |                                            | 2 MHz                      | MC68HC11ED0VFU2 |                |

| 44-pin QFP   |                                    |                                            | 3 MHz                      | MC68HC11ED0VFU3 |                |

|              | -40°C to +125°C                    |                                            | 2 MHz                      | MC68HC11ED0MFU2 |                |

|              |                                    |                                            | 3 MHz                      | MC68HC11ED0MFU3 |                |

|              | 40°C to 195°C                      |                                            | 2 MHz                      | MC68HC11ED0CP2  |                |

|              | −40°C to +85°C                     | No ROM/EPROM                               | 3 MHz                      | MC68HC11ED0CP3  |                |

| 44 nin DID   | -40°C to +105°C<br>-40°C to +125°C |                                            | 2 MHz                      | MC68HC11ED0VP2  |                |

| 44-pin DIP   |                                    | -40 C to +105 C                            | No EEPROM<br>512 bytes RAM | 3 MHz           | MC68HC11ED0VP3 |

|              |                                    |                                            | 2 MHz                      | MC68HC11ED0MP2  |                |

|              |                                    |                                            | 3 MHz                      | MC68HC11ED0MP3  |                |

### Technical Data — MC68HC11ED0

## **Section 2. Pin Assignments**

#### 2.1 Contents

| 2.2 | Introduction19                              |

|-----|---------------------------------------------|

| 2.3 | 44-Pin Plastic-Leaded Chip Carrier (PLCC)   |

| 2.4 | 44-Pin Quad Flat Pack (QFP)21               |

| 2.5 | 40-Pin Plastic Dual In-Line Package (DIP)22 |

#### 2.2 Introduction

The MC68HC11ED0 pin assignments are shown here for these packages:

- 44-pin plastic-leaded chip carrier (PLCC)

- 44-pin quad flat pack (QFP)

- 40-pin plastic dual in-line package (DIP)

## **Pin Assignments**

### 2.3 44-Pin Plastic-Leaded Chip Carrier (PLCC)

Refer to Figure 2-1 for the 44-pin PLCC pin assignments.

Figure 2-1. Pin Assignments for 44-Pin PLCC

Pin Assignments 44-Pin Quad Flat Pack (QFP)

### 2.4 44-Pin Quad Flat Pack (QFP)

Refer to Figure 2-2 for the 44-pin QFP pin assignments.

Note 1. Not bonded in 40-pin package

Figure 2-2. Pin Assignments for 44-Pin QFP

MC68HC11ED0 — Rev. 1.0

## **Pin Assignments**

### 2.5 40-Pin Plastic Dual In-Line Package (DIP)

Refer to Figure 2-3 for the 40-pin DIP pin assignments.

Figure 2-3. Pin Assignments for 40-Pin DIP

## Technical Data — MC68HC11ED0

# **Section 3. Central Processor Unit (CPU)**

#### 3.1 Contents

| 3.2 Introduction                    | 24      |

|-------------------------------------|---------|

| 3.3 CPU Registers                   | 24      |

| 3.3.1 Accumulators A, B, and D      |         |

| 3.3.2 Index Register X (IX)         |         |

| 3.3.3 Index Register Y (IY)         |         |

| 3.3.4 Stack Pointer (SP)            |         |

| 3.3.5 Program Counter (PC)          |         |

| 3.3.6 Condition Code Register (CCR) |         |

| 3.3.6.1 Carry/Borrow (C)            |         |

| 3.3.6.2 Overflow (V)                |         |

| 3.3.6.3 Zero (Z)                    | 29      |

| 3.3.6.4 Negative (N)                |         |

| 3.3.6.5 I-Interrupt Mask (I)        |         |

| 3.3.6.6 Half Carry (H)              |         |

| 3.3.6.7 X-Interrupt Mask (X)        |         |

|                                     |         |

| 3.4 Data Types                      | 31      |

| 3.5 Opcodes and Operands            | 31      |

| 3.6 Addressing Modes                | 32      |

| 3.6.1 Immediate                     |         |

| 3.6.2 Direct                        | 33      |

| 3.6.3 Extended                      |         |

| 3.6.4 Indexed                       |         |

| 3.6.5 Inherent                      |         |

| 3.6.6 Relative                      |         |

| 3.7 Instruction Set                 | 34      |

| . J. ( )   HISHUGHOH OF             | . , , 2 |

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

#### 3.2 Introduction

This section presents information on M68HC11:

- Central processor unit (CPU) architecture

- Data types

- Addressing modes

- Instruction set

- Special operations such as subroutine calls and interrupts

The CPU is designed to treat all peripheral, input/output (I/O), and memory locations identically as addresses in the 64-Kbyte memory map. This is referred to as memory-mapped I/O. I/O has no instructions separate from those used by memory. This architecture also allows accessing an operand from an external memory location with no execution time penalty.

## 3.3 CPU Registers

M68HC11 CPU registers are an integral part of the CPU and are not addressed as if they were memory locations. The seven registers, discussed in the following paragraphs, are shown in **Figure 3-1**.

Central Processor Unit (CPU)

CPU Registers

Figure 3-1. Programming Model

#### 3.3.1 Accumulators A, B, and D

Accumulators A and B are general-purpose 8-bit registers that hold operands and results of arithmetic calculations or data manipulations. For some instructions, these two accumulators are treated as a single double-byte (16-bit) accumulator called accumulator D. Although most instructions can use accumulators A or B interchangeably, these exceptions apply:

- The ABX and ABY instructions add the contents of 8-bit accumulator B to the contents of 16-bit register X or Y, but there are no equivalent instructions that use A instead of B.

- The TAP and TPA instructions transfer data from accumulator A

to the condition code register or from the condition code register

to accumulator A. However, there are no equivalent instructions

that use B rather than A.

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

- The decimal adjust accumulator A (DAA) instruction is used after binary-coded decimal (BCD) arithmetic operations, but there is no equivalent BCD instruction to adjust accumulator B.

- The add, subtract, and compare instructions associated with both A and B (ABA, SBA, and CBA) only operate in one direction, making it important to plan ahead to ensure that the correct operand is in the correct accumulator.

#### 3.3.2 Index Register X (IX)

The IX register provides a 16-bit indexing value that can be added to the 8-bit offset provided in an instruction to create an effective address. The IX register can also be used as a counter or as a temporary storage register.

#### 3.3.3 Index Register Y (IY)

The 16-bit IY register performs an indexed mode function similar to that of the IX register. However, most instructions using the IY register require an extra byte of machine code and an extra cycle of execution time because of the way the opcode map is implemented. Refer to **3.5 Opcodes and Operands** for further information.

#### 3.3.4 Stack Pointer (SP)

The M68HC11 CPU has an automatic program stack. This stack can be located anywhere in the address space and can be any size up to the amount of memory available in the system. Normally, the SP is initialized by one of the first instructions in an application program. The stack is configured as a data structure that grows downward from high memory to low memory. Each time a new byte is pushed onto the stack, the SP is decremented. Each time a byte is pulled from the stack, the SP is incremented. At any given time, the SP holds the 16-bit address of the next free location in the stack. Figure 3-2 is a summary of SP operations.

Central Processor Unit (CPU)

CPU Registers

Figure 3-2. Stacking Operations

When a subroutine is called by a jump-to-subroutine (JSR) or branch-to-subroutine (BSR) instruction, the address of the instruction after the JSR or BSR is automatically pushed onto the stack, least significant byte first. When the subroutine is finished, a return-from-subroutine (RTS) instruction is executed. The RTS pulls the previously stacked return address from the stack and loads it into the program counter. Execution then continues at this recovered return address.

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

When an interrupt is recognized, the current instruction finishes normally, the return address (the current value in the program counter) is pushed onto the stack, all of the CPU registers are pushed onto the stack, and execution continues at the address specified by the vector for the interrupt.

At the end of the interrupt service routine, a return-from interrupt (RTI) instruction is executed. The RTI instruction causes the saved registers to be pulled off the stack in reverse order. Program execution resumes at the return address.

Certain instructions push and pull the A and B accumulators and the X and Y index registers and are often used to preserve program context. For example, pushing accumulator A onto the stack when entering a subroutine that uses accumulator A and then pulling accumulator A off the stack just before leaving the subroutine ensures that the contents of a register will be the same after returning from the subroutine as it was before starting the subroutine.

### 3.3.5 Program Counter (PC)

The program counter, a 16-bit register, contains the address of the next instruction to be executed. After reset, the program counter is initialized from one of six possible vectors, depending on operating mode and the cause of reset. See **Table 3-1**.

**Table 3-1. Reset Vector Comparison**

| Mode         | POR or RESET Pin | Clock Monitor | COP Watchdog |

|--------------|------------------|---------------|--------------|

| Normal       | \$FFFE, \$FFFF   | \$FFFC, D     | \$FFFA, B    |

| Test or boot | \$BFFE, \$BFFF   | \$BFFC, D     | \$BFFA, B    |

Central Processor Unit (CPU)

CPU Registers

#### 3.3.6 Condition Code Register (CCR)

This 8-bit register contains:

- Five condition code indicators (C, V, Z, N, and H),

- Two interrupt masking bits (IRQ and XIRQ)

- A stop disable bit (S)

In the M68HC11 CPU, condition codes are updated automatically by most instructions. For example, load accumulator A (LDAA) and store accumulator A (STAA) instructions automatically set or clear the N, Z, and V condition code flags. Pushes, pulls, add B to X (ABX), add B to Y (ABY), and transfer/exchange instructions do not affect the condition codes. Refer to **Table 3-2**, which shows what condition codes are affected by a particular instruction.

#### 3.3.6.1 Carry/Borrow (C)

The C bit is set if the arithmetic logic unit (ALU) performs a carry or borrow during an arithmetic operation. The C bit also acts as an error flag for multiply and divide operations. Shift and rotate instructions operate with and through the carry bit to facilitate multiple-word shift operations.

#### 3.3.6.2 Overflow (V)

The overflow bit is set if an operation causes an arithmetic overflow. Otherwise, the V bit is cleared.

#### 3.3.6.3 Zero (Z)

The Z bit is set if the result of an arithmetic, logic, or data manipulation operation is 0. Otherwise, the Z bit is cleared. Compare instructions do an internal implied subtraction and the condition codes, including Z, reflect the results of that subtraction. A few operations (INX, DEX, INY, and DEY) affect the Z bit and no other condition flags. For these operations, only = and  $\neq$  conditions can be determined.

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

#### 3.3.6.4 Negative (N)

The N bit is set if the result of an arithmetic, logic, or data manipulation operation is negative (MSB = 1). Otherwise, the N bit is cleared. A result is said to be negative if its most significant bit (MSB) is a 1. A quick way to test whether the contents of a memory location has the MSB set is to load it into an accumulator and then check the status of the N bit.

#### 3.3.6.5 I-Interrupt Mask (I)

The interrupt request (IRQ) mask (I bit) is a global mask that disables all maskable interrupt sources. While the I bit is set, interrupts can become pending, but the operation of the CPU continues uninterrupted until the I bit is cleared. After any reset, the I bit is set by default and can be cleared only by a software instruction. When an interrupt is recognized, the I bit is set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, a return-from-interrupt instruction is normally executed, restoring the registers to the values that were present before the interrupt occurred. Normally, the I bit is 0 after a return from interrupt is executed. Although the I bit can be cleared within an interrupt service routine, "nesting" interrupts in this way should be done only when there is a clear understanding of latency and of the arbitration mechanism. Refer to Section 5. Resets and Interrupts.

#### 3.3.6.6 Half Carry (H)

The H bit is set when a carry occurs between bits 3 and 4 of the arithmetic logic unit during an ADD, ABA, or ADC instruction. Otherwise, the H bit is cleared. Half carry is used during BCD operations.

#### 3.3.6.7 X-Interrupt Mask (X)

The XIRQ mask (X) bit disables interrupts from the  $\overline{\text{XIRQ}}$  pin. After any reset, X is set by default and must be cleared by a software instruction. When an  $\overline{\text{XIRQ}}$  interrupt is recognized, the X and I bits are set after the registers are stacked, but before the interrupt vector is fetched. After the interrupt has been serviced, an RTI instruction is normally executed, causing the registers to be restored to the values that were present

Central Processor Unit (CPU)

Data Types

before the interrupt occurred. The X interrupt mask bit is set only by hardware (RESET or XIRQ acknowledge). X is cleared only by program instruction (TAP, where the associated bit of A is 0; or RTI, where bit 6 of the value loaded into the CCR from the stack has been cleared). There is no hardware action for clearing X.

#### 3.3.6.8 STOP Disable (S)

Setting the STOP disable (S) bit prevents the STOP instruction from putting the M68HC11 into a low-power stop condition. If the STOP instruction is encountered by the CPU while the S bit is set, it is treated as a no-operation (NOP) instruction, and processing continues to the next instruction. S is set by reset; STOP is disabled by default.

## 3.4 Data Types

The M68HC11 CPU supports four data types:

- 1. Bit data

- 2. 8-bit and 16-bit signed and unsigned integers

- 3. 16-bit unsigned fractions

- 4. 16-bit addresses

A byte is eight bits wide and can be accessed at any byte location. A word is composed of two consecutive bytes with the most significant byte at the lower value address. Because the M68HC11 is an 8-bit CPU, there are no special requirements for alignment of instructions or operands.

## 3.5 Opcodes and Operands

The M68HC11 Family of microcontrollers uses 8-bit opcodes. Each opcode identifies a particular instruction and associated addressing mode to the CPU. Several opcodes are required to provide each instruction with a range of addressing capabilities. Only 256 opcodes

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

would be available if the range of values were restricted to the number able to be expressed in 8-bit binary numbers.

A 4-page opcode map has been implemented to expand the number of instructions. An additional byte, called a prebyte, directs the processor from page 0 of the opcode map to one of the other three pages. As its name implies, the additional byte precedes the opcode.

A complete instruction consists of a prebyte, if any, an opcode, and zero, one, two, or three operands. The operands contain information the CPU needs for executing the instruction. Complete instructions can be from one to five bytes long.

## 3.6 Addressing Modes

Six addressing modes can be used to access memory:

- Immediate

- Direct

- Extended

- Indexed

- Inherent

- Relative

These modes are detailed in the following paragraphs. All modes except inherent mode use an effective address. The effective address is the memory address from which the argument is fetched or stored or the address from which execution is to proceed. The effective address can be specified within an instruction, or it can be calculated.

#### 3.6.1 Immediate

In the immediate addressing mode, an argument is contained in the byte(s) immediately following the opcode. The number of bytes following the opcode matches the size of the register or memory location being operated on. There are 2-, 3-, and 4- (if prebyte is required) byte

Central Processor Unit (CPU)

Addressing Modes

immediate instructions. The effective address is the address of the byte following the instruction.

#### 3.6.2 **Direct**

In the direct addressing mode, the low-order byte of the operand address is contained in a single byte following the opcode, and the high-order byte of the address is assumed to be \$00. Addresses \$00–\$FF are thus accessed directly, using 2-byte instructions. Execution time is reduced by eliminating the additional memory access required for the high-order address byte. In most applications, this 256-byte area is reserved for frequently referenced data. In M68HC11 MCUs, the memory map can be configured for combinations of internal registers, RAM, or external memory to occupy these addresses.

#### 3.6.3 Extended

In the extended addressing mode, the effective address of the argument is contained in two bytes following the opcode byte. These are 3-byte instructions (or 4-byte instructions if a prebyte is required). One or two bytes are needed for the opcode and two for the effective address.

#### 3.6.4 Indexed

In the indexed addressing mode, an 8-bit unsigned offset contained in the instruction is added to the value contained in an index register (IX or IY). The sum is the effective address. This addressing mode allows referencing any memory location in the 64-Kbyte address space. These are 2- to 5-byte instructions, depending on whether a prebyte is required.

#### 3.6.5 Inherent

In the inherent addressing mode, all the information necessary to execute the instruction is contained in the opcode. Operations that use only the index registers or accumulators, as well as control instructions with no arguments, are included in this addressing mode. These are 1- or 2-byte instructions.

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

#### 3.6.6 Relative

The relative addressing mode is used only for branch instructions. If the branch condition is true, an 8-bit signed offset included in the instruction is added to the contents of the program counter to form the effective branch address. Otherwise, control proceeds to the next instruction. These are usually 2-byte instructions.

#### 3.7 Instruction Set

Refer to **Table 3-2**, which shows all the M68HC11 instructions in all possible addressing modes. For each instruction, the table shows the operand construction, the number of machine code bytes, and execution time in CPU E-clock cycles.

Central Processor Unit (CPU) Instruction Set

Table 3-2. Instruction Set (Sheet 1 of 7)

| Mnemonic           | Operation                   | Description                           | Addressing       |                                     | Instruction    |                            |                                  |                       |   |   |   |   |   |   |   |   |  |

|--------------------|-----------------------------|---------------------------------------|------------------|-------------------------------------|----------------|----------------------------|----------------------------------|-----------------------|---|---|---|---|---|---|---|---|--|

|                    | ·                           | -                                     | Mode             |                                     | Opcode Operand |                            | Cycles                           | S X H I N Z \         |   |   |   |   |   |   |   |   |  |

| ABA                | Add<br>Accumulators         | $A + B \Rightarrow A$                 |                  | INH                                 |                | 1B                         | _                                | 2                     | _ | _ | Δ |   | Δ | Δ | Δ |   |  |

| ABX                | Add B to X                  | IX + (00 : B) ⇒ IX                    |                  | INH                                 |                | 3A                         | _                                | 3                     | _ | _ | _ | _ | _ | _ | _ | - |  |

| ABY                | Add B to Y                  | IY + (00 : B) ⇒ IY                    |                  | INH                                 | 18             | 3A                         | _                                | 4                     | _ | _ | _ | _ | _ | _ | _ | - |  |

| ADCA (opr)         | Add with Carry<br>to A      | $A + M + C \Rightarrow A$             | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | 89<br>99<br>B9<br>A9<br>A9 | ii<br>dd<br>hh II<br>ff<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | Δ | _ | Δ | Δ | Δ | 2 |  |

| ADCB (opr)         | Add with Carry<br>to B      | $B + M + C \Rightarrow B$             | B<br>B<br>B<br>B | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | C9<br>D9<br>F9<br>E9       | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | Δ | _ | Δ | Δ | Δ |   |  |

| ADDA (opr)         | Add Memory to<br>A          | A + M ⇒ A                             | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | 8B<br>9B<br>BB<br>AB<br>AB | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | Δ | _ | Δ | Δ | Δ | ž |  |

| ADDB (opr)         | Add Memory to<br>B          | B + M ⇒ B                             | B<br>B<br>B<br>B | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | CB<br>DB<br>FB<br>EB<br>EB | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | Δ | _ | Δ | Δ | Δ | 4 |  |

| ADDD (opr)         | Add 16-Bit to D             | $D + (M : M + 1) \Rightarrow D$       |                  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | C3<br>D3<br>F3<br>E3       | jj kk<br>dd<br>hh II<br>ff<br>ff | 4<br>5<br>6<br>6<br>7 | _ | _ | _ | _ | Δ | Δ | Δ | , |  |

| ANDA (opr)         | AND A with<br>Memory        | $A \bullet M \Rightarrow A$           | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | 84<br>94<br>B4<br>A4<br>A4 | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | 0 | - |  |

| ANDB (opr)         | AND B with<br>Memory        | $B \bullet M \Rightarrow B$           | B<br>B<br>B<br>B | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18             | C4<br>D4<br>F4<br>E4       | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _ | Δ | Δ | 0 | - |  |

| ASL (opr)          | Arithmetic Shift<br>Left    | ————————————————————————————————————— |                  | EXT<br>IND,X<br>IND,Y               | 18             | 78<br>68<br>68             | hh II<br>ff<br>ff                | 6<br>6<br>7           | _ | _ | _ | _ | Δ | Δ | Δ |   |  |

| ASLA               | Arithmetic Shift<br>Left A  | ————————————————————————————————————— | A                | INH                                 |                | 48                         | _                                | 2                     | _ | _ | _ | _ | Δ | Δ | Δ |   |  |

| ASLB               | Arithmetic Shift<br>Left B  | C b7 b0                               | В                | INH                                 |                | 58                         | _                                | 2                     | _ | _ | _ | _ | Δ | Δ | Δ |   |  |

| ASLD               | Arithmetic Shift<br>Left D  |                                       |                  | INH                                 |                | 05                         | _                                | 3                     | - | _ | _ | _ | Δ | Δ | Δ |   |  |

| ASR                | Arithmetic Shift<br>Right   | b7 b0 C                               |                  | EXT<br>IND,X<br>IND,Y               | 18             | 77<br>67<br>67             | hh II<br>ff<br>ff                | 6<br>6<br>7           | - | _ | _ | _ | Δ | Δ | Δ |   |  |

| ASRA               | Arithmetic Shift<br>Right A | b7 b0 C                               | A                | INH                                 |                | 47                         | _                                | 2                     | _ | _ | _ | _ | Δ | Δ | Δ |   |  |

| ASRB               | Arithmetic Shift<br>Right B | b7 b0 C                               | В                | INH                                 |                | 57                         | _                                | 2                     | - | _ | _ | _ | Δ | Δ | Δ |   |  |

| BCC (rel)          | Branch if Carry<br>Clear    | ? C = 0                               |                  | REL                                 |                | 24                         | rr                               | 3                     | _ | _ | _ | _ | _ | _ | _ | - |  |

| CLR (opr)<br>(msk) | Clear Bit(s)                | $M \cdot (mm) \Rightarrow M$          |                  | DIR<br>IND,X<br>IND,Y               | 18             | 15<br>1D<br>1D             | dd mm<br>ff mm<br>ff mm          | 6<br>7<br>8           | _ | _ | _ | _ | Δ | Δ | 0 | - |  |

MC68HC11ED0 — Rev. 1.0

## **Central Processor Unit (CPU)**

Table 3-2. Instruction Set (Sheet 2 of 7)

| Mnomenia                     | Operation                    | Dogorintian            | Addressing                                    | Instruction                   |                                  |                       |   | Condition Codes |   |   |   |   |   |   |  |  |

|------------------------------|------------------------------|------------------------|-----------------------------------------------|-------------------------------|----------------------------------|-----------------------|---|-----------------|---|---|---|---|---|---|--|--|

| Mnemonic                     | Operation                    | Description            | Mode                                          | Opcode                        | Operand                          | Cycles                | S | Х               | Н | ı | N | Z | ٧ | С |  |  |

| BCS (rel)                    | Branch if Carry<br>Set       | ? C = 1                | REL                                           | 25                            | rr                               | 3                     | _ | _               |   |   | _ | _ | _ |   |  |  |

| BEQ (rel)                    | Branch if = Zero             | ? Z = 1                | REL                                           | 27                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BGE (rel)                    | Branch if ∆ Zero             | ? N ⊕ V = 0            | REL                                           | 2C                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BGT (rel)                    | Branch if > Zero             | ? Z + (N ⊕ V) = 0      | REL                                           | 2E                            | rr                               | 3                     | _ |                 |   |   | _ |   |   |   |  |  |

| BHI (rel)                    | Branch if<br>Higher          | ? C + Z = 0            | REL                                           | 22                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BHS (rel)                    | Branch if<br>Higher or Same  | ? C = 0                | REL                                           | 24                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BITA (opr)                   | Bit(s) Test A<br>with Memory | A • M                  | A IMM<br>A DIR<br>A EXT<br>A IND,X<br>A IND,Y | 85<br>95<br>B5<br>A5<br>18 A5 | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _               | _ | _ | Δ | Δ | 0 | _ |  |  |

| BITB (opr)                   | Bit(s) Test B<br>with Memory | B∙M                    | B IMM<br>B DIR<br>B EXT<br>B IND,X<br>B IND,Y | C5<br>D5<br>F5<br>E5          | ii<br>dd<br>hh II<br>ff<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _               | _ | _ | Δ | Δ | 0 | _ |  |  |

| BLE (rel)                    | Branch if ∆ Zero             | ? Z + (N ⊕ V) = 1      | REL                                           | 2F                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BLO (rel)                    | Branch if Lower              | ? C = 1                | REL                                           | 25                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BLS (rel)                    | Branch if Lower or Same      | ? C + Z = 1            | REL                                           | 23                            | rr                               | 3                     | _ | _               | _ | _ | - | _ | _ | _ |  |  |

| BLT (rel)                    | Branch if < Zero             | ? N ⊕ V = 1            | REL                                           | 2D                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BMI (rel)                    | Branch if Minus              | ? N = 1                | REL                                           | 2B                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BNE (rel)                    | Branch if not = Zero         | ? Z = 0                | REL                                           | 26                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BPL (rel)                    | Branch if Plus               | ? N = 0                | REL                                           | 2A                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BRA (rel)                    | Branch Always                | ? 1 = 1                | REL                                           | 20                            | rr                               | 3                     | _ |                 |   |   |   |   |   |   |  |  |

| BRCLR(opr)<br>(msk)<br>(rel) | Branch if<br>Bit(s) Clear    | ? M • mm = 0           | DIR<br>IND,X<br>IND,Y                         | 13<br>1F<br>18 1F             | dd mm rr<br>ff mm rr<br>ff mm rr | 6<br>7<br>8           | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BRN (rel)                    | Branch Never                 | ? 1 = 0                | REL                                           | 21                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BRSET(opr)<br>(msk)<br>(rel) | Branch if Bit(s)<br>Set      | ? (M) • mm = 0         | DIR<br>IND,X<br>IND,Y                         | 12<br>1E<br>18 1E             | dd mm rr<br>ff mm rr<br>ff mm rr | 6<br>7<br>8           | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BSET (opr)<br>(msk)          | Set Bit(s)                   | $M + mm \Rightarrow M$ | DIR<br>IND,X<br>IND,Y                         | 14<br>1C<br>18 1C             | dd mm<br>ff mm<br>ff mm          | 6<br>7<br>8           | _ | _               | _ | _ | Δ | Δ | 0 | _ |  |  |

| BSR (rel)                    | Branch to<br>Subroutine      | See Figure 3-2         | REL                                           | 8D                            | rr                               | 6                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BVC (rel)                    | Branch if<br>Overflow Clear  | ? V = 0                | REL                                           | 28                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| BVS (rel)                    | Branch if<br>Overflow Set    | ? V = 1                | REL                                           | 29                            | rr                               | 3                     | _ | _               | _ | _ | _ | _ | _ | _ |  |  |

| CBA                          | Compare A to B               | A – B                  | INH                                           | 11                            | _                                | 2                     | _ | _               | _ | _ | Δ | Δ | Δ | Δ |  |  |

| CLC                          | Clear Carry Bit              | 0 ⇒ C                  | INH                                           | 0C                            | _                                | 2                     | _ | _               |   |   | _ |   | _ | 0 |  |  |

| CLI                          | Clear Interrupt<br>Mask      | 0 ⇒ I                  | INH                                           | 0E                            | _                                | 2                     | _ | _               | _ | 0 | _ | _ | _ | _ |  |  |

| CLR (opr)                    | Clear Memory<br>Byte         | $0 \Rightarrow M$      | EXT<br>IND,X<br>IND,Y                         | 7F<br>6F<br>18 6F             | hh II<br>ff<br>ff                | 6<br>6<br>7           | _ | _               | _ | _ | 0 | 1 | 0 | 0 |  |  |

| CLRA                         | Clear<br>Accumulator A       | 0 ⇒ A                  | A INH                                         | 4F                            | _                                | 2                     | _ | _               | _ | _ | 0 | 1 | 0 | 0 |  |  |

| CLRB                         | Clear<br>Accumulator B       | $0 \Rightarrow B$      | B INH                                         | 5F                            | _                                | 2                     | _ | _               | _ | _ | 0 | 1 | 0 | 0 |  |  |

| CLV                          | Clear Overflow<br>Flag       | $0 \Rightarrow V$      | INH                                           | 0A                            | _                                | 2                     | _ | _               | _ | _ | _ | _ | 0 | _ |  |  |

| CMPA (opr)                   | Compare A to<br>Memory       | A – M                  | A IMM A DIR A EXT A IND,X A IND,Y             | 81<br>91<br>B1<br>A1<br>18 A1 | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4<br>5 | _ | _               | _ | _ | Δ | Δ | Δ | Δ |  |  |

Central Processor Unit (CPU) Instruction Set

Table 3-2. Instruction Set (Sheet 3 of 7)

| Mnemonic   | Operation                         | Description                            | Ad               | dressing                            |                            | Ir                         | struction                        |                       |         |   | Co | nditio | n Coo | les |   |   |

|------------|-----------------------------------|----------------------------------------|------------------|-------------------------------------|----------------------------|----------------------------|----------------------------------|-----------------------|---------|---|----|--------|-------|-----|---|---|

| winemonic  | Operation                         | Description                            |                  | Mode                                | Op                         | code                       | Operan                           | d Cycles              | S       | Х | Н  | ı      | N     | Z   | ٧ | С |

| CMPB (opr) | Compare B to<br>Memory            | B – M                                  | B<br>B<br>B      | IMM<br>DIR<br>EXT<br>IND,X          |                            | C1<br>D1<br>F1<br>E1       | ii<br>dd<br>hh II<br>ff          | 2<br>3<br>4<br>4      | -       | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| COM (opr)  | Ones                              | \$FF – M ⇒ M                           | В                | IND,Y<br>EXT                        | 18                         | E1 73                      | ff<br>hh II                      | 5<br>6                | _       | _ | _  |        | Δ     | Δ   | 0 | 1 |

| COMA       | Complement<br>Memory Byte<br>Ones | \$FF – A ⇒ A                           | A                | IND,X<br>IND,Y<br>INH               | 18                         | 63<br>63<br>43             | ff<br>ff                         | 6 7 2                 | <u></u> |   |    |        | Δ     | Δ   | 0 | 1 |

|            | Complement<br>A                   | ·                                      |                  |                                     |                            |                            |                                  |                       |         |   |    |        |       |     |   |   |

| COMB       | Ones<br>Complement<br>B           | \$FF – B ⇒ B                           | В                | INH                                 |                            | 53                         | _                                | 2                     |         | _ | _  | _      | Δ     | Δ   | 0 | 1 |

| CPD (opr)  | Compare D to<br>Memory 16-Bit     | D – M : M + 1                          |                  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 1A<br>1A<br>1A<br>1A<br>CD | 83<br>93<br>B3<br>A3<br>A3 | jj kk<br>dd<br>hh II<br>ff<br>ff | 5<br>6<br>7<br>7<br>7 |         | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| CPX (opr)  | Compare X to<br>Memory 16-Bit     | IX – M : M + 1                         |                  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | CD                         | 8C<br>9C<br>BC<br>AC<br>AC | jj kk<br>dd<br>hh II<br>ff<br>ff | 4<br>5<br>6<br>6<br>7 | _       | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| CPY (opr)  | Compare Y to<br>Memory 16-Bit     | IY – M : M + 1                         |                  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18<br>18<br>18<br>1A<br>18 | 8C<br>9C<br>BC<br>AC<br>AC | jj kk<br>dd<br>hh II<br>ff<br>ff | 5<br>6<br>7<br>7<br>7 | _       | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| DAA        | Decimal Adjust<br>A               | Adjust Sum to BCD                      |                  | INH                                 |                            | 19                         | _                                | 2                     | _       | _ | _  | _      | Δ     | Δ   | Δ | Δ |

| DEC (opr)  | Decrement<br>Memory Byte          | M − 1 ⇒ M                              |                  | EXT<br>IND,X<br>IND,Y               | 18                         | 7A<br>6A<br>6A             | hh II<br>ff<br>ff                | 6<br>6<br>7           | _       | _ | _  | _      | Δ     | Δ   | Δ | _ |

| DECA       | Decrement<br>Accumulator<br>A     | A − 1 ⇒ A                              | A                | INH                                 |                            | 4A                         | _                                | 2                     | _       | _ | _  | _      | Δ     | Δ   | Δ | _ |

| DECB       | Decrement<br>Accumulator<br>B     | B – 1 ⇒ B                              | В                | INH                                 |                            | 5A                         | _                                | 2                     | -       | _ | _  | _      | Δ     | Δ   | Δ | _ |

| DES        | Decrement<br>Stack Pointer        | SP – 1 ⇒ SP                            |                  | INH                                 |                            | 34                         | _                                | 3                     | _       | _ | _  | _      | _     | _   | _ | _ |

| DEX        | Decrement<br>Index Register<br>X  | IX − 1 ⇒ IX                            |                  | INH                                 |                            | 09                         | _                                | 3                     | _       | _ | _  | _      | _     | Δ   | _ | _ |

| DEY        | Decrement<br>Index Register<br>Y  | IY − 1 ⇒ IY                            |                  | INH                                 | 18                         | 09                         | _                                | 4                     | _       | _ | _  | _      | _     | Δ   | _ | _ |

| EORA (opr) | Exclusive OR A with Memory        | $A \oplus M \Rightarrow A$             | A<br>A<br>A<br>A | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                         | 88<br>98<br>B8<br>A8<br>A8 | ii<br>dd<br>hh II<br>ff<br>ff    | 2<br>3<br>4<br>4<br>5 | _       | _ | _  | _      | Δ     | Δ   | 0 | _ |

| EORB (opr) | Exclusive OR B with Memory        | $B \oplus M \Rightarrow B$             | B<br>B<br>B<br>B | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18                         | C8<br>D8<br>F8<br>E8       | ii<br>dd<br>hh II<br>ff<br>ff    | 2<br>3<br>4<br>4<br>5 | _       | _ | _  | _      | Δ     | Δ   | 0 | _ |

| FDIV       | Fractional<br>Divide 16 by 16     | $D/IX \Rightarrow IX; r \Rightarrow D$ |                  | INH                                 |                            | 03                         | _                                | 41                    | -       | _ | _  | _      | _     | Δ   | Δ | Δ |

| IDIV       | Integer Divide<br>16 by 16        | $D/IX \Rightarrow IX; r \Rightarrow D$ |                  | INH                                 |                            | 02                         | _                                | 41                    |         | _ | _  | _      | _     | Δ   | 0 | Δ |

| INC (opr)  | Increment<br>Memory Byte          | M + 1 ⇒ M                              |                  | EXT<br>IND,X<br>IND,Y               | 18                         | 7C<br>6C<br>6C             | hh II<br>ff<br>ff                | 6<br>6<br>7           | _       | _ | _  |        | Δ     | Δ   | Δ | = |

| INCA       | Increment<br>Accumulator<br>A     | A + 1 ⇒ A                              | A                | INH                                 |                            | 4C                         | _                                | 2                     | _       | _ | _  | _      | Δ     | Δ   | Δ | _ |

MC68HC11ED0 — Rev. 1.0

# **Central Processor Unit (CPU)**

Table 3-2. Instruction Set (Sheet 4 of 7)

| Mnemonic   | Operation                        | Description                           | Addressing                          |                                           | nstruction                 |                       |   |   |   | nditio | n Co |   |   |   |

|------------|----------------------------------|---------------------------------------|-------------------------------------|-------------------------------------------|----------------------------|-----------------------|---|---|---|--------|------|---|---|---|

| winemonic  | Operation                        | Description                           | Mode                                | Opcode                                    | Operand                    | Cycles                | S | Х | Н | ı      | N    | Z | ٧ | С |

| INCB       | Increment<br>Accumulator<br>B    | B + 1 ⇒ B                             | B INH                               | 5C                                        | _                          | 2                     | _ | _ | _ | _      | Δ    | Δ | Δ | _ |

| INS        | Increment<br>Stack Pointer       | SP + 1 ⇒ SP                           | INH                                 | 31                                        | _                          | 3                     | _ | _ | _ | _      | -    | _ | _ | _ |

| INX        | Increment<br>Index Register<br>X | $IX + 1 \Rightarrow IX$               | INH                                 | 08                                        | _                          | 3                     | _ | _ | _ | _      | _    | Δ | _ | _ |

| INY        | Increment<br>Index Register<br>Y | IY + 1 ⇒ IY                           | INH                                 | 18 08                                     | _                          | 4                     | _ | _ | _ | _      | _    | Δ | _ | _ |

| JMP (opr)  | Jump                             | See Figure 3–2                        | EXT<br>IND,X<br>IND,Y               | 7E<br>6E<br>18 6E                         | hh II<br>ff<br>ff          | 3<br>3<br>4           | _ | _ | _ | _      | _    | _ | _ | _ |

| JSR (opr)  | Jump to<br>Subroutine            | See Figure 3–2                        | DIR<br>EXT<br>IND,X<br>IND,Y        | 9D<br>BD<br>AD<br>18 AD                   | dd<br>hh II<br>ff          | 5<br>6<br>6<br>7      | _ | _ | _ | _      | _    | _ | _ | _ |

| LDAA (opr) | Load<br>Accumulator<br>A         | $M \Rightarrow A$                     | A IMM A DIR A EXT A IND,X A IND,Y   | 86<br>96<br>B6<br>A6<br>18 A6             | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _      | Δ    | Δ | 0 | _ |

| LDAB (opr) | Load<br>Accumulator<br>B         | $M \Rightarrow B$                     | B IMM B DIR B EXT B IND,X B IND,Y   | C6<br>D6<br>F6<br>E6                      | ii<br>dd<br>hh II<br>ff    | 2<br>3<br>4<br>4<br>5 | _ | _ | _ | _      | Δ    | Δ | 0 | _ |

| LDD (opr)  | Load Double<br>Accumulator<br>D  | $M \Rightarrow A, M+1 \Rightarrow B$  | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | CC<br>DC<br>FC<br>EC<br>18 EC             | jj kk<br>dd<br>hh II<br>ff | 3<br>4<br>5<br>5<br>6 | _ | _ | _ | _      | Δ    | Δ | 0 | _ |

| LDS (opr)  | Load Stack<br>Pointer            | M : M + 1 ⇒ SP                        | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 8E<br>9E<br>BE<br>AE<br>18 AE             | jj kk<br>dd<br>hh II<br>ff | 3<br>4<br>5<br>5      | _ | _ | _ | _      | Δ    | Δ | 0 | _ |

| LDX (opr)  | Load Index<br>Register<br>X      | M : M + 1 ⇒ IX                        | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | CE<br>DE<br>FE<br>EE<br>CD EE             | jj kk<br>dd<br>hh II<br>ff | 3<br>4<br>5<br>5      | _ | _ | _ | _      | Δ    | Δ | 0 | _ |

| LDY (opr)  | Load Index<br>Register<br>Y      | M : M + 1 ⇒ IY                        | IMM<br>DIR<br>EXT<br>IND,X<br>IND,Y | 18 CE<br>18 DE<br>18 FE<br>1A EE<br>18 EE | jj kk<br>dd<br>hh II<br>ff | 4<br>5<br>6<br>6<br>6 | _ | _ | _ |        | Δ    | Δ | 0 | _ |

| LSL (opr)  | Logical Shift<br>Left            | ————————————————————————————————————— | EXT<br>IND,X<br>IND,Y               | 78<br>68<br>18 68                         | hh II<br>ff<br>ff          | 6<br>6<br>7           | _ | _ | _ | _      | Δ    | Δ | Δ | Δ |

| LSLA       | Logical Shift<br>Left A          | C b7 b0 C b7 b0                       | A INH                               | 48                                        | _                          | 2                     | _ | _ | _ | _      | Δ    | Δ | Δ | Δ |