# 4510 Group

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

#### DESCRIPTION

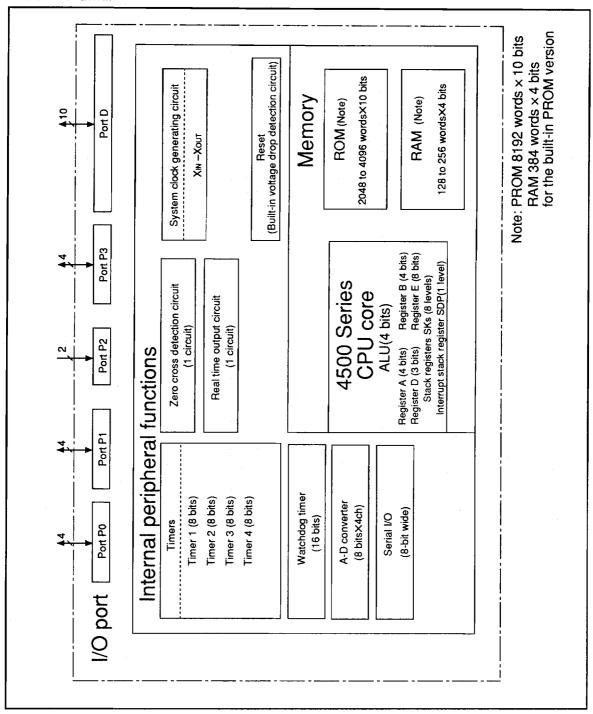

The 4510 Group is a 4-bit single-chip microcomputer designed with CMOS technology. Its CPU is that of the 4500 series using a simple, high-speed instruction set. The computer is equipped with serial I/O, four 8-bit timers (each timer has a reload register), A-D converter, and zero cross detection circuit.

The various microcomputers in the 4510 Group include variations of the built-in memory type and package as shown in the table below.

#### **FEATURES**

- Minimum instruction execution time............. 0.5 μs (at 6.0 MHz system clock frequency)

- Supply voltage

4.5 V to 5.5 V (at 6.0 MHz system clock frequency)

4.0 V to 5.5 V (at 4.0 MHz system clock frequency)

2.5 V to 5.5 V (at 2.0 MHz system clock frequency)

2.0 V to 5.5 V (at 1.5 MHz system clock frequency: only for Mask ROM versions)

| _ |                                            |

|---|--------------------------------------------|

|   | Timer 1 8-bit timer with a reload register |

|   | Timer 28-bit timer with a reload register  |

|   | Timer 38-bit timer with a reload register  |

|   | Timer 48-bit timer with a reload register  |

| • | Interrupt 8 sources                        |

| • | Serial I/O 8 bit-wide                      |

| • | A-D converter                              |

|   | 8-bit successive comparison method X 4ch   |

| • | Zero cross detection circuit1              |

| • | Real time output circuit1                  |

|   | Watchdog timer                             |

| • | Voltage drop detection circuit 1           |

| • | Clock generating circuit                   |

| • | LED drive directly enabled (port D)        |

#### **APPLICATION**

Timers

VCR, microwave oven, rice cooker, audio, telephone, office equipment

| Product             | ROM (PROM) size<br>(X 10 bits) | RAM size<br>(X 4 bits) | Package               | ROM type      |

|---------------------|--------------------------------|------------------------|-----------------------|---------------|

| M34510M2A-XXXSP/FP  | 2048 words                     | 128 words              |                       |               |

| M34510M4A-XXXSP/FP  | 4096 words                     | 256 words              | SP: 32P4B FP: 36P2R-A | Mask ROM      |

| M34510E8-XXXSP/FP * | 2100                           | 204                    |                       | One Time PROM |

| M34510E8SS **       | 8192 Words                     | 8192 words   384 words | 32S1B                 | EPROM         |

<sup>\*:</sup> Shipped after writing (shipped in blank: M34510E8SP/FP)

<sup>\*\*:</sup> For program development

# **4510 Group**

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

# **BLOCK DIAGRAM**

# PERFORMANCE OVERVIEW

| Pa                               | arameter        |                    | Function                                                                                    |  |  |

|----------------------------------|-----------------|--------------------|---------------------------------------------------------------------------------------------|--|--|

| Number of bas                    | sic instruc     | tions              | 122                                                                                         |  |  |

| Minimum instru                   | uction exe      | cution time        | 0.5 µs (at 6.0 MHz system clock frequency) (Refer to the electrical characteristics because |  |  |

|                                  |                 |                    | the minimum instruction execution time depends on the supply voltage.)                      |  |  |

| Memory sizes                     | ROM             | M34510M2A          | 2048 words × 10 bits                                                                        |  |  |

|                                  |                 | M34510M4A          | 4096 words X 10 bits                                                                        |  |  |

|                                  |                 | M34510E8           | 8192 words × 10 bits                                                                        |  |  |

| RAM M34510M2A 128 words X 4 bits |                 | 128 words × 4 bits |                                                                                             |  |  |

|                                  |                 | M34510M4A          | 256 words × 4 bits                                                                          |  |  |

|                                  |                 | M34510E8           | 384 words × 4 bits                                                                          |  |  |

| Input/Output                     | Do-De           | 1/0                | Ten independent I/O ports; ports D4 and D5 are also used as RTP. Ports D6-D9 are also       |  |  |

| ports                            | !               |                    | used as INTO, CNTR, Sck, and Sout, respectively.                                            |  |  |

|                                  | P00-P03         | 1/0                | 4-bit I/O port; each pin is equipped with a pull-up function and a key-on wakeup function.  |  |  |

|                                  |                 |                    | Both functions can be switched by software.                                                 |  |  |

|                                  | P10-P13         | 1/0                | 4-bit I/O port; each pin is equipped with a pull-up function and a key-on wakeup function.  |  |  |

|                                  | 1               | ,                  | Both functions can be switched by software.                                                 |  |  |

|                                  | P20-P21         | Input              | 2-bit input port; ports P20 and P21 are also used as Sin and INT1, respectively.            |  |  |

|                                  | P30-P33         | 1/0                | 4-bit I/O port; these pins are also used as four analog input pins.                         |  |  |

|                                  | CNTR            | 1/0                | Timer I/O; CNTR pin is also used as port D7.                                                |  |  |

|                                  | INTO            | Input              | Interrupt input; INTO pin is also used as port De and zero cross input pin. INTO pin is     |  |  |

|                                  |                 |                    | equipped with a key-on wakeup function.                                                     |  |  |

|                                  | INT1            | Input              | Interrupt input; INT1 pin is also used as port P21.                                         |  |  |

|                                  | RTP             | Output             | Real time output; RTP pins are also used as ports D4 and D5.                                |  |  |

|                                  | ZEROX           | Input              | Zero cross input; ZEROX pin is also used as port De.                                        |  |  |

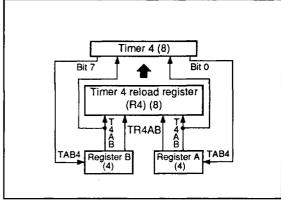

| Timers                           | Timer 1         |                    | 8-bit programmable timer with a reload register                                             |  |  |

|                                  | Timer 2         |                    | 8-bit programmable timer with a reload register is also used as an event counter.           |  |  |

|                                  | Timer 3         |                    | 8-bit programmable timer with a reload register                                             |  |  |

|                                  | Timer 4         |                    | 8-bit programmable timer with a reload register is also used as an event counter.           |  |  |

| A-D converter                    |                 |                    | 8 bits X 1; comparator can be used by software.                                             |  |  |

| Serial I/O                       |                 |                    | 8-bit wide                                                                                  |  |  |

| Interrupt                        | Sources         |                    | 8 (two for external, four for timer, one for A-D, and one for serial I/O)                   |  |  |

|                                  | Nesting         |                    | 1 level                                                                                     |  |  |

| Subroutine nes                   | sting           |                    | 8 levels                                                                                    |  |  |

| Device structu                   | re              |                    | CMOS silicon gate                                                                           |  |  |

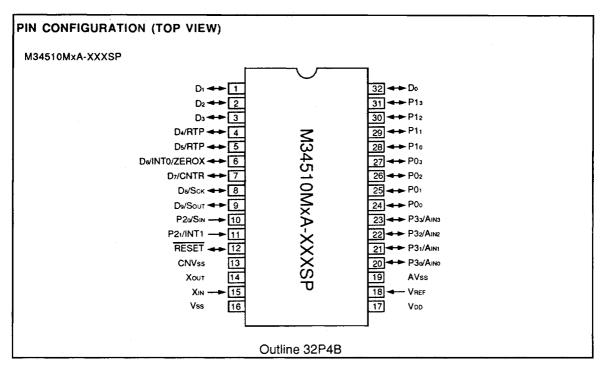

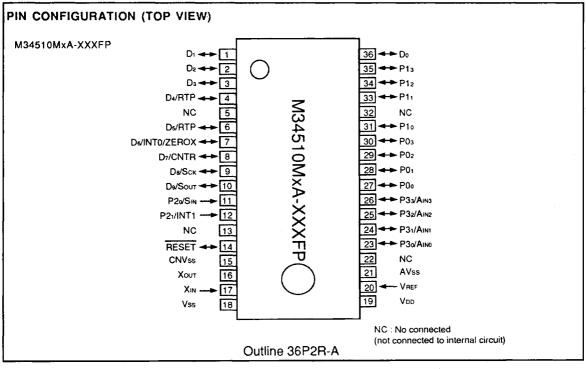

| Package                          | M34510N         | 1xA-XXXSP          | 32-pin plastic molded SDIP (32P4B)                                                          |  |  |

|                                  | M34510N         | 1xA-XXXFP          |                                                                                             |  |  |

| Operating temperature range      |                 | ange               | -20 °C to 85 °C (-20 °C to 70 °C for the built-in EPROM version, M34510E8SS)                |  |  |

| Supply voltage                   |                 |                    | 2.0 V to 5.5 V (Refer to the electrical characteristics because the supply voltage depends  |  |  |

|                                  |                 |                    | on the system clock frequency.)                                                             |  |  |

| Power                            | wer Active mode |                    | 4 mA                                                                                        |  |  |

| dissipation                      |                 |                    | (at 6.0 MHz system clock frequency, VDD = 5 V, output transistors in the cut-off state)     |  |  |

| (typical value)                  |                 |                    | 2 mA                                                                                        |  |  |

|                                  |                 |                    | (at 1.5 MHz system clock frequency, VDD = 5 V, output transistors in the cut-off state)     |  |  |

|                                  | RAM back        | (-up mode          | 0.1 μA (at room temperature, VDD = 5 V, output transistors in the cut-off state)            |  |  |

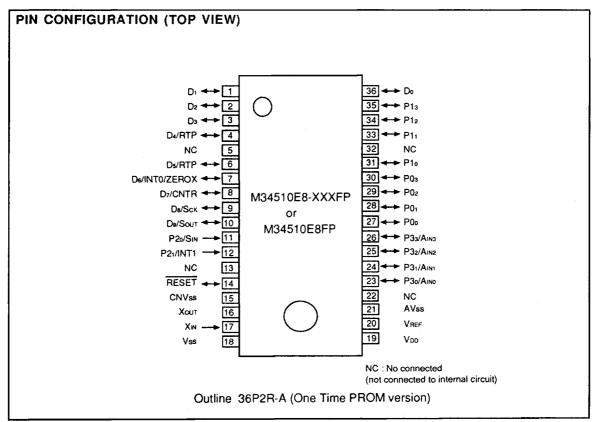

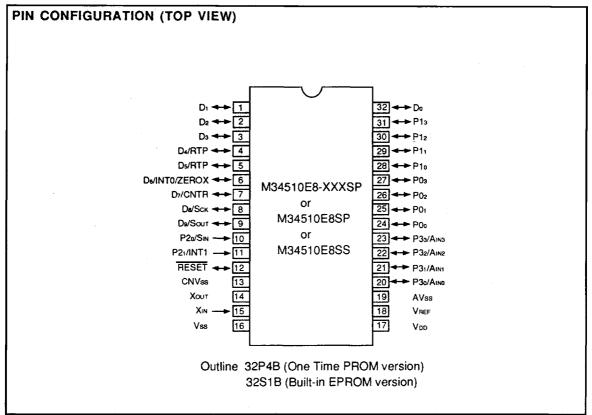

# мітѕивізні міспосомрителя 4510 Group

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

# PIN DESCRIPTION

| Pin       | Name                    | Input/Output | Function                                                                           |  |

|-----------|-------------------------|--------------|------------------------------------------------------------------------------------|--|

| VσD       | Power supply            | -            | Connected to a plus power supply.                                                  |  |

| Vss       | Ground                  |              | Connected to a 0 V power supply.                                                   |  |

| CNVss     | CNVss                   | _            | Connect CNVss to Vss and apply "L" (OV) to CNVss certainly.                        |  |

| AVss      | Ground for analog       |              | Connected to a 0 V power supply for A-D converter.                                 |  |

|           | power supply            |              | Connect AVss to Vss.                                                               |  |

| VREF      | Reference voltage input | -            | Reference voltage input pin for the A-D converter.                                 |  |

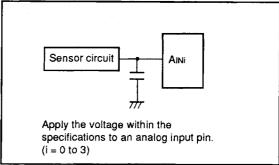

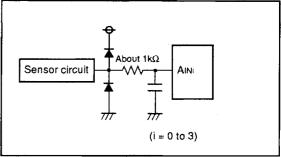

| AINO-AIN3 | Analog input            | Input        | Analog input pins for A-D converter. Alno-Alno are also used as ports P3o-P3o.     |  |

| RESET     | Reset I/O               | 1/0          | An N-channel open-drain I/O pin for a system reset. When the watchdog timer        |  |

|           |                         |              | causes the system to be reset, the RESET pin outputs "L" level.                    |  |

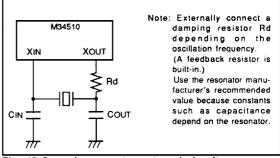

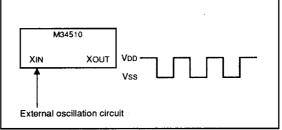

| XIN       | System clock input      | Input        | I/O pins of the system clock generating circuit. XIN and XOUT can be connected     |  |

| Xout      | System clock output     | Output       | to a ceramic resonator. A feedback resistor is built-in between them.              |  |

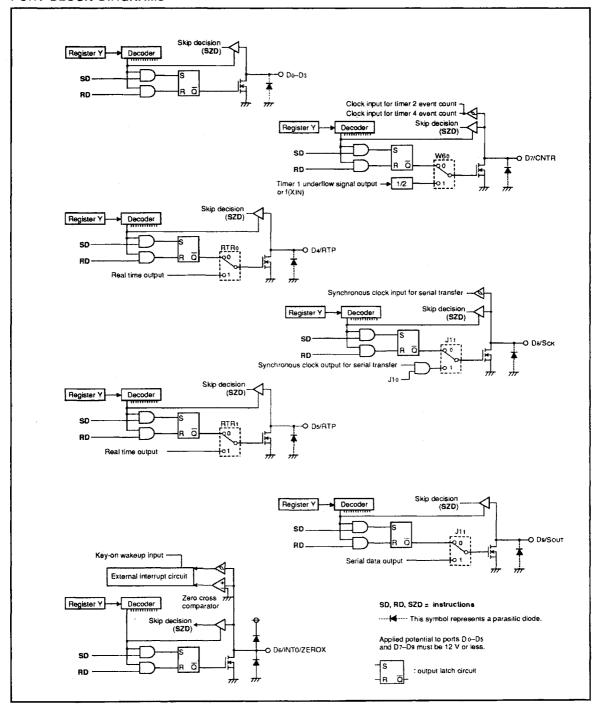

| Do-D9     | I/O port D              | 1/0          | Each pin of port D has an independent 1-bit wide I/O function. Each pin has        |  |

|           |                         |              | an output latch. For input use, set the latch of the specified bit to "1." The     |  |

|           |                         |              | output structure is N-channel open-drain.                                          |  |

|           |                         |              | Ports D4 and D5 are also used as RTP. Ports D6-D9 are also used as INTO/           |  |

|           |                         |              | ZEROX, CNTR, Sck, and Sout, respectively.                                          |  |

| P00-P03   | I/O port P0             | 1/0          | Each of ports P0 and P1 serves as a 4-bit I/O port, and it can be used as          |  |

|           |                         | ·            | inputs when the output latch is set to "1." The output structure is N-channel      |  |

| P10-P13   | VO 01                   |              | open-drain.                                                                        |  |

| P10-P13   | I/O port P1             |              | Every pin of the ports has a key-on wakeup function and a pull-up function.        |  |

|           |                         |              | Both functions can be switched by software.                                        |  |

| P20P21    | Input port P2           | Input        | 2-bit input port. Ports P2o and P21 are also used as SIN and INT1, respectively.   |  |

| P30-P33   | I/O port P3             | 1/0          | 4-bit I/O port. The output structure is N-channel open-drain. Port P3 is also      |  |

|           |                         |              | used as analog input pins.                                                         |  |

| CNTR      | Timer input/output      | 1/0          | CNTR pin has the function to input the clock for the timer 2 and timer 4 event     |  |

|           |                         |              | counters, and to output the timer 1 underflow signal divided by 2 or the signal    |  |

|           |                         |              | of XIN divided by 2.                                                               |  |

|           |                         |              | CNTR pin is also used as port D7.                                                  |  |

| INTO      | Interrupt input         | Input        | INTO pin accepts an external interrupt. It also accepts the input signal to return |  |

|           |                         |              | the system from the RAM back-up state.                                             |  |

|           |                         |              | INTO pin is also used as port De.                                                  |  |

| INT1      | Interrupt input         | Input        | INT1 pin accepts an external interrupt.                                            |  |

|           |                         |              | INT1 pin is also used as port P21.                                                 |  |

| ZEROX     | Zero cross input        | Input        | ZEROX pin is also used as the zero cross input pin by software.                    |  |

|           |                         |              | ZEROX pin is also used as De/INTO pin.                                             |  |

| Sin       | Serial data input       | Input        | SIN pin is used to input serial data signals by software.                          |  |

|           |                         |              | SIN pin is also used as port P2o.                                                  |  |

| Sout      | Serial data output      | Output       | Sour pin is used to output serial data signals by software.                        |  |

|           |                         |              | Sout pin is also used as port Da.                                                  |  |

| Sck       | Serial I/O clock        | 1/0          | Sck pin is used to input and output synchronous clock signals for serial data      |  |

|           | input/output            |              | transfer by software.                                                              |  |

|           | 1                       |              | Scк pin is also used as port Dв.                                                   |  |

| RTP       | Real time output        | Output       | RTP pins are also used as real time output pins by software.                       |  |

|           | 1                       |              | RTP pins are also used as ports D4 and D5, respectively.                           |  |

#### MULTIFUNCTION

| Pin            | Multifunction | Pin            | Multifunction   |

|----------------|---------------|----------------|-----------------|

| D <sub>4</sub> | RTP           | RTP (Note 2)   | D4              |

| D <sub>5</sub> | RTP           | RTP            | D5              |

| De             | INT0/ZEROX    | INTO (Note 2)  | De/ZEROX        |

| D7             | CNTR          | INTI           | P21             |

| Dв             | Sck           | Sck (Note 2)   | Ds              |

| D <sub>9</sub> | Sout          | SOUT           | De              |

| P20            | Sin           | SIN            | P20             |

| P21            | INT1          | CNTR (Note 2)  | D7              |

| P30            | Aino          | Aino (Note 2)  | P30             |

| P31            | Ain1          | AIN1           | P31             |

| P32            | AIN2          | Ain2           | P32             |

| P33            | Ains          | Ains           | P3 <sub>3</sub> |

|                |               | ZEROX (Note 2) | D6/INTO         |

Notes 1: Pins except above have just single function.

#### CONNECTIONS OF UNUSED PINS

| Pin                 | Connection                              | Pin               | Connection                              |

|---------------------|-----------------------------------------|-------------------|-----------------------------------------|

| Хоит                | Open (when using an external clock)     | P2o/SiN           | Connect to Vss                          |

| AVss/VREF           | Connect to Vss                          | P21/INT1          | 7                                       |

| Do-D3               | Connect to Vss, or set the output latch | P30/AIN0-P33/AIN3 | Connect to Vss, or set the output latch |

| D <sub>4</sub> /RTP | to "0" and open.                        | [[                | to "0" and open,                        |

| Ds/RTP              |                                         | P00-P03           | Open or connect to Vss (Note)           |

| De/INTO/ZEROX       | 7                                       | P10-P13           | Open or connect to Vss (Note)           |

| D7/CNTR             |                                         |                   |                                         |

| Ds/Sck              | 1                                       |                   |                                         |

| Ds/Sout             | 7                                       | ]]                |                                         |

Note: When the P00-P03 and P10-P13 are connected to Vss, turn off their pull-up transistors (register PU0i="0") and also invalidate the key-on wakeup functions (register K0i="0") by software. When these pins are connected to Vss while the key-on wakeup functions are left valid, the system fails to return from RAM back-up state. When these pins are open, turn on their pull-up transistors (register PU0i="1") by software, or set the output latch to "0."

Be sure to select the key-on wakeup functions and the pull-up functions with every two pins. If only one of the two pins for the key-on wakeup function is used, turn on their pull-up transistors by software and also disconnect the other pin. (i = 0, 1, 2, or 3.)

(Note when the output latch is set to "0" and pins are open)

- •After system is released from reset, port is in a high-impedance state until it is set the output latch to "0" by software. Accordingly, the voltage level of pins is undefined and the excess of the supply current may occur while the port is in a high-impedance state.

- •To set the output latch periodically by software is recommended because value of output latch may change by noise or a program run away (caused by noise).

(Note when connecting to Vss and VDD)

•Connect the unused pins to Vss or Vpp using the thickest wire at the shortest distance against noise.

<sup>2:</sup> The I/O of D6, the input of D4, D5, D7-D9, P20 and P21, and the output of P30-P33 can be used even when INTO/ZEROX, RTP, CNTR, Sck, Sout, Sin, INT1 and Aino-Ain3 are selected.

# **PORT FUNCTION**

| Port    | Pin           | Input/<br>Output | Output structure     | Control<br>bits | Control  | Control registers | Remark                                 |

|---------|---------------|------------------|----------------------|-----------------|----------|-------------------|----------------------------------------|

| Port D  | Do-D3         | 1/0              | N-channel open-drain | 1               | SD       |                   |                                        |

| 1       | D4/RTP        | (10)             | ,                    |                 | RD       | RTR               | <b>]</b> .                             |

| 1       | Ds/RTP        |                  |                      |                 | SZD      | RTR               | 1                                      |

|         | De/INTO/ZEROX | 1                |                      |                 | CLD      | 11                | Key-on wakeup function                 |

|         | D7/CNTR       | }                |                      |                 | SNZI0    | W6                |                                        |

|         | Ds/Sck        |                  |                      |                 | (Note 1) | J1                |                                        |

|         | De/Sout       |                  |                      |                 |          | J1                |                                        |

| Port P0 | P00-P03       | 1/0              | N-channel open-drain | 4               | OP0A     | PU0               | Built-in programmable pull-up          |

|         |               | (4)              |                      |                 | IAP0     | K0 .              | functions                              |

|         |               |                  | ·                    |                 |          |                   | Key-on wakeup functions                |

|         |               |                  |                      |                 |          |                   | (programmable)                         |

| Port P1 | P10-P13       | 170              | N-channel open-drain | 4               | OP1A     | PU0               | Built-in programmable pull-up          |

| i       |               | (4)              |                      |                 | IAP1     | K0                | functions                              |

|         |               |                  |                      |                 |          |                   | Key-on wakeup functions (programmable) |

| Port P2 | P2o/Sin       | Input            |                      | 2               | IAP2     |                   |                                        |

| 1       | P21/INT1      | (2)              |                      |                 | SNZI1    |                   |                                        |

|         |               |                  | ,                    |                 | (Note 2) |                   |                                        |

| Port P3 | P3o/Aino      | 1/0              | N-channel open-drain | 4               | IAP3     | Q2                |                                        |

|         | P31/Ain1      | (4)              |                      |                 | OP3A     |                   |                                        |

|         | P32/Ain2      |                  |                      |                 |          |                   |                                        |

|         | P33/Ains      |                  |                      |                 |          |                   |                                        |

Notes 1: Level of the Ds/INTO pin can be examined with the SNZIO instruction.

2: Level of the P21/INT1 pin can be examined with the SNZI1 instruction.

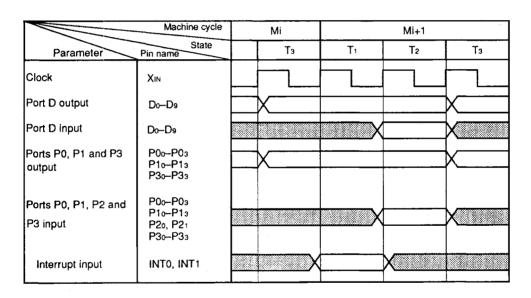

# **DEFINITION OF CLOCK AND CYCLE**

#### System clock

This is the source clock input to the XIN pin. Either the clock obtained by connecting an oscillator between the XIN and XOUT pins, or the external clock supplied through the XIN pin can be specified.

#### ●Instruction clock

The instruction clock is a signal derived by dividing the system clock by 3, and is the basic clock for controlling this product.

# ●Machine cycle

One machine cycle is the time required to execute the minimum instruction (one-cycle instruction). The machine cycle is equivalent to the instruction clock cycle.

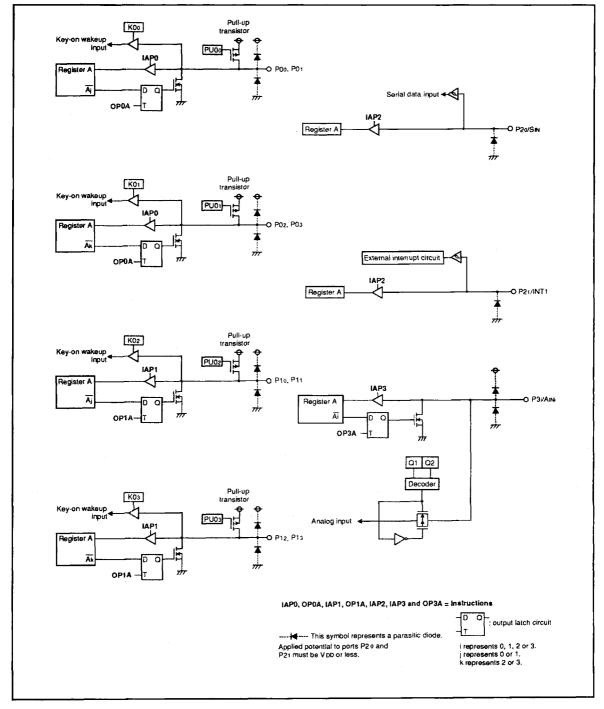

# PORT BLOCK DIAGRAMS

# PORT BLOCK DIAGRAMS (continued)

# FUNCTION BLOCK OPERATIONS CPU

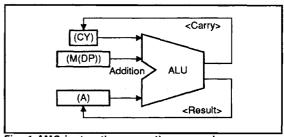

#### (1) Arithmetic logic unit (ALU)

The arithmetic logic unit ALU performs 4-bit arithmetic such as 4-bit data addition, comparison, AND operation, OR operation, and bit manipulation.

#### (2) Register A and carry flag

Register A is a 4-bit register used for arithmetic, transfer, exchange, and I/O operation.

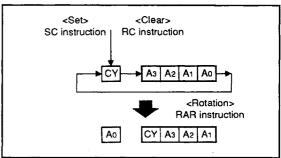

Carry flag CY is a 1-bit flag that is set to "1" when there is a carry with the AMC instruction (Figure 1).

It is unchanged with both A n instruction and AM instruction. The value of Ao is stored in carry flag CY with the RAR instruction (Figure 2).

Carry flag CY can be set to "1" with the SC instruction and cleared to "0" with the RC instruction.

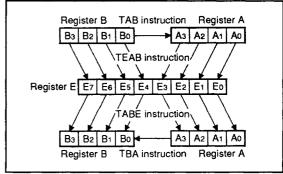

#### (3) Registers B and E

Register B is a 4-bit register used for temporary storage of 4-bit data, and for 8-bit data transfer together with register A.

Register E is an 8-bit register. It can be used for 8-bit data transfer with register B used as the high-order 4 bits and register A as the low-order 4 bits (Figure 3).

#### (4) Register D

Register D is a 3-bit register.

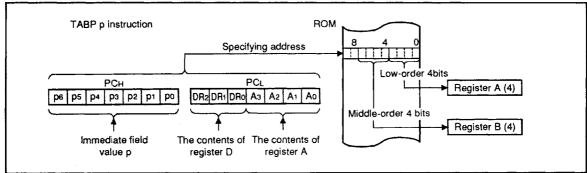

It is used to store a 7-bit ROM address together with register A and is used as a pointer within the specified page when the TABP p, BLA p, or BMLA p instruction is executed (Figure 4).

Fig. 1 AMC instruction execution example

Fig. 2 RAR instruction execution example

Fig. 3 Registers A, B and register E

Fig. 4 TABP p instruction execution example

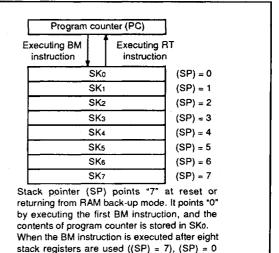

#### (5) Stack registers (SKs) and stack pointer (SP)

Stack registers (SKs) are used to temporarily store the contents of program counter (PC) just before branching until returning to the original routine when;

- branching to an interrupt service routine (referred to as an interrupt service routine),

- · performing a subroutine call, or

- executing the table reference instruction (TABP p). Stack registers (SKs) are eight identical registers, so that subroutines can be nested up to 8 levels. However, one of stack registers is used respectively when using an interrupt service routine and when executing a table reference instruction. Accordingly, be careful not to over the stack when performing these operations together. The contents of registers SKs are destroyed when 8 levels are exceeded.

The register SK nesting level is pointed automatically by 3-bit stack pointer (SP). The contents of the stack pointer (SP) can be transferred to register A with the TASP instruction.

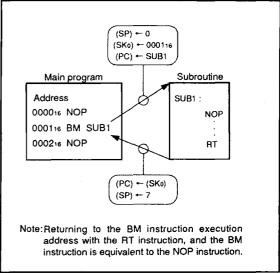

Figure 5 shows the stack registers (SKs) structure. Figure 6 shows the example of operation at subroutine call.

#### (6) Interrupt stack register (SDP)

Interrupt stack register (SDP) is a 1-stage register. When an interrupt occurs, this register (SDP) is used to temporarily store the contents of data pointer, carry flag, skip flag, register A, and register B just before an interrupt until returning to the original routine.

Unlike the stack registers (SKs), this register (SDP) is not used when executing the subroutine call instruction and the table reference instruction.

#### (7) Skip flag

Skip flag controls skip decision for the conditional skip instructions and continuous described skip instructions. When an interrupt occurs, the contents of skip flag is stored automatically in the interrupt stack register (SDP) and the skip condition is retained.

Fig. 5 Stack registers (SKs) structure

and the contents of SKo is destroyed.

Fig. 6 Example of operation at subroutine call

#### (8) Program counter (PC)

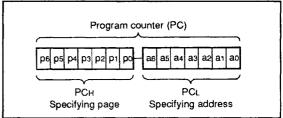

Program counter (PC) is used to specify a ROM address (page and address). It determines a sequence in which instructions stored in ROM are read. It is a binary counter that increments the number of instruction bytes each time an instruction is executed. However, the value changes to a specified address when branch instructions, subroutine call instructions, return instructions, or the table reference instruction (TABP p) is executed. Program counter consists of PCH (most significant bit to bit 7) which specifies to a ROM page and PCL (bits 6 to 0) which specifies an address within a page. After it reaches the last address (address 127) of a page, it specifies address 0 of the next page (Figure 7). Make sure that the PCH does not specify after the last page of the built-in ROM.

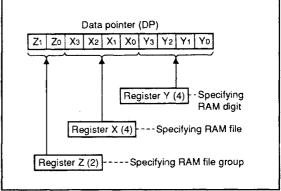

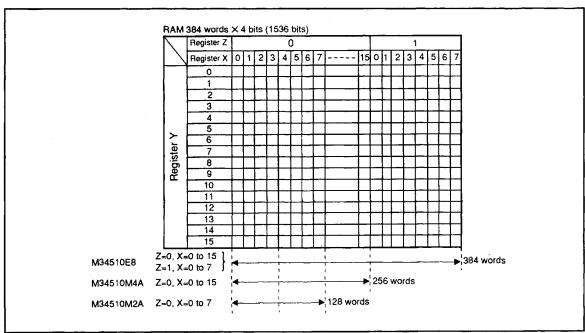

#### (9) Data pointer (DP)

Data pointer (DP) is used to specify a RAM address and consists of registers Z, X, and Y. Register Z specifies a RAM file group, register X specifies a file, and register Y specifies a RAM digit (Figure 8).

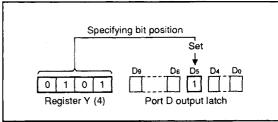

Register Y is also used to specify the port D bit position.

When using port D, set the port D bit position to register Y certainly and execute the SD, RD, or SZD instruction (Figure 9).

Fig. 7 Program counter (PC) structure

Fig. 8 Data pointer (DP) structure

Fig. 9 SD instruction execution example

# **PROGRAM MEMORY (ROM)**

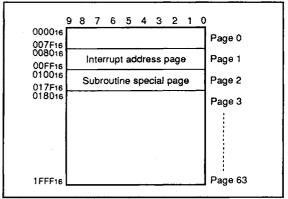

The program memory is a mask ROM. 1 word of ROM is composed of 10 bits. ROM is separated every 128 words by the unit of page (addresses 0 to 127). Table 1 shows the ROM size and pages. Figure 10 shows the ROM map of M34510E8.

Table 1 ROM size and pages

| Product   | ROM size<br>(X 10 bits) | Pages        |

|-----------|-------------------------|--------------|

| M34510M2A | 2048 words              | 16 (0 to 15) |

| M34510M4A | 4096 words              | 32 (0 to 31) |

| M34510E8  | 8192 words              | 64 (0 to 63) |

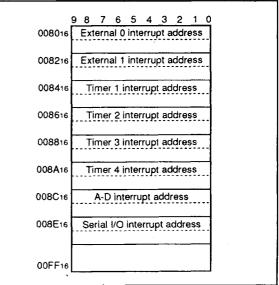

A part of page 1 (addresses 008016 to 00FF16) is reserved for interrupt addresses (Figure 11). When an interrupt occurs, the address (interrupt address) corresponding to each interrupt is set in the program counter, and the instruction at the interrupt address is executed. When using an interrupt service routine, write the instruction generating the branch to that routine at an interrupt address.

Page 2 (addresses 010016 to 017F16) is the special page for subroutine calls. Subroutines written in this page can be called from any page with the 1-word instruction (BM). Subroutines extending from page 2 to another page can also be called with the BM instruction when it starts on page 2. ROM pattern (bits 7 to 0) of all addresses can be used as data areas with the TABP p instruction.

Fig. 10 ROM map of M34510E8

Fig. 11 Page 1 (addresses 008016 to 00FF16) structure

# **DATA MEMORY (RAM)**

1 word of RAM is composed of 4 bits, but 1-bit manipulation (with the SB j, RB j, and SZB j instructions) is enabled for the entire memory area. A RAM address is specified by a data pointer. The data pointer consists of registers Z, X, and Y. Set a value to the data pointer certainly when executing an Instruction to access RAM.

Table 2 shows the RAM size. Figure 12 shows the RAM map

Table 2 RAM size

| Product   | RAM size                       |

|-----------|--------------------------------|

| M34510M2A | 128 words X 4 bits (512 bits)  |

| M34510M4A | 256 words X 4 bits (1024 bits) |

| M34510E8  | 384 words X 4 bits (1536 bits) |

Fig. 12 RAM map

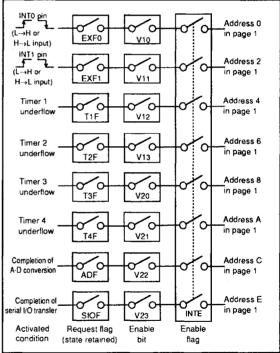

#### INTERRUPT FUNCTION

The interrupt type is a vectored interrupt branching to an individual address (interrupt address) according to each interrupt source. An interrupt occurs when the following 3 conditions are satisfied.

- An interrupt activated condition is satisfied (request flag = "1")

- · interrupt enable bit is enabled ("1")

- · Interrupt enable flag is enabled (INTE = "1")

Table 3 shows interrupt sources. (Refer to each interrupt request flag for details of activated conditions.)

#### (1) Interrupt enable flag (INTE)

The interrupt enable flag (INTE) controls whether the every interrupt enable/disable. Interrupts are enabled when INTE flag is set to "1" with the EI instruction and disabled when INTE flag is cleared to "0" with the DI instruction. When any interrupt occurs, the INTE flag is automatically cleared to "0," so that other interrupts are disabled until the EI instruction is executed.

#### (2) Interrupt enable bit

Use an interrupt enable bit of interrupt control registers V1 and V2 to select the corresponding interrupt or skip instruction.

Table 4 shows the interrupt request flag, interrupt enable bit and skip instruction.

Table 5 shows the interrupt enable bit function.

# (3) Interrupt request flag

When the activated condition for each interrupt is satisfied, the corresponding interrupt request flag is set to "1." Each interrupt request flag is cleared to "0" when either;

- · an interrupt occurs, or

- the next instruction is skipped with a skip instruction.

Each interrupt request flag is set when the activated condition is satisfied even if the interrupt is disabled by the INTE flag or its interrupt enable bit. Once set, the interrupt request flag retains set until a clear condition is satisfied.

Accordingly, an interrupt occurs when the interrupt disable state is released while the interrupt request flag is set

If more than one interrupt request flag is set when the interrupt disable state is released, the interrupt priority level is as follows shown in Table 3.

Table 3 Interrupt sources

| Table 3           | able 5 interrupt sources |                     |                      |  |  |

|-------------------|--------------------------|---------------------|----------------------|--|--|

| Priority<br>level | Interrupt name           | Activated condition | Interrupt<br>address |  |  |

| 1                 | External 0 interrupt     | Level change of     | Address 0            |  |  |

|                   |                          | INTO pin            | in page 1            |  |  |

| 2                 | External 1 interrupt     | Level change of     | Address 2            |  |  |

|                   |                          | INT1 pin            | in page 1            |  |  |

| 3                 | Timer 1 interrupt        | Timer 1 underflow   | Address 4            |  |  |

|                   |                          |                     | in page 1            |  |  |

| 4                 | Timer 2 interrupt        | Timer 2 underflow   | Address 6            |  |  |

|                   |                          |                     | in page 1            |  |  |

| 5                 | Timer 3 interrupt        | Timer 3 underflow   | Address 8            |  |  |

|                   |                          |                     | in page 1            |  |  |

| 6                 | Timer 4 interrupt        | Timer 4 underflow   | Address A            |  |  |

|                   |                          |                     | in page 1            |  |  |

| 7                 | A-D interrupt            | Completion of       | Address C            |  |  |

| l                 |                          | A-D conversion      | in page 1            |  |  |

| 8                 | Serial I/O interrupt     | Completion of       | Address E            |  |  |

|                   |                          | serial I/O transfer | in page 1            |  |  |

Table 4 Interrupt request flag, interrupt enable bit and skip instruction

| Interrupt name       | Request flag | Skip instruction | Enable bit |

|----------------------|--------------|------------------|------------|

| External 0 interrupt | EXFO         | SNZ0             | V10        |

| External 1 interrupt | EXF1         | SNZ1             | V11        |

| Timer 1 interrupt    | T1F          | SNZT1            | V12        |

| Timer 2 interrupt    | T2F          | SNZT2            | V13        |

| Timer 3 interrupt    | T3F          | SNZT3            | V20        |

| Timer 4 interrupt    | T4F          | SNZT4            | V21        |

| A-D interrupt        | ADF          | SNZAD            | V22        |

| Serial I/O interrupt | SIOF         | SNZSI            | V23        |

Table 5 Interrupt enable bit function

| Interrupt enable bit | Occurrence of interrupt | Skip instruction |

|----------------------|-------------------------|------------------|

| 1                    | Enabled                 | Invalid          |

| 0                    | Disabled                | Valid            |

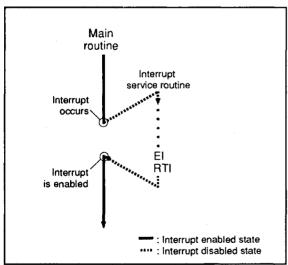

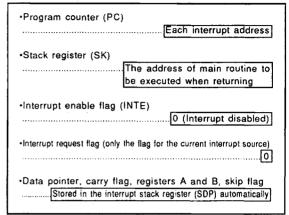

#### (4) Internal state during an interrupt

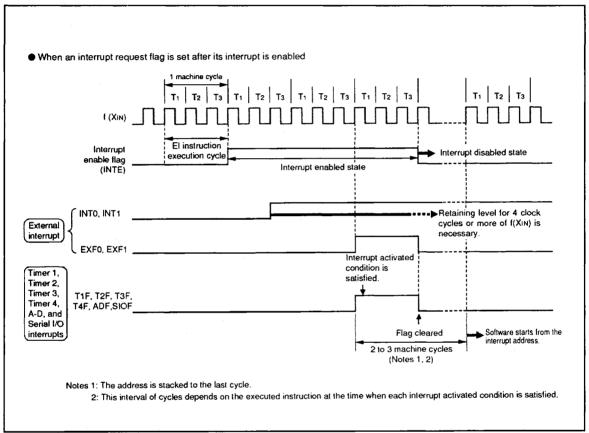

The internal state of the microcomputer during an interrupt is as follows (Figure 14).

- · Program counter (PC)

- An interrupt address is set in program counter. The address to be executed when returning to the main routine is automatically stored in the stack register (SK).

- Interrupt enable flag (INTE)

INTE flag is cleared to "0" so that interrupts are disabled.

- Interrupt request flag

Only the request flag for the current interrupt source is cleared to "0."

- Data pointer, carry flag, skip flag, registers A and B

The contents of these registers and flags are stored automatically in the interrupt stack register (SDP).

# (5) Interrupt processing

When an interrupt occurs, a program at an interrupt address is executed after branching a data store sequence to stack register. Write the branch instruction to an interrupt service routine at an interrupt address. Use the RTI instruction to return from an interrupt service routine.

Interrupt enabled by executing the El instruction is performed after executing 1 instruction (just after the next instruction is executed). Accordingly, when the El instruction is executed just before the RTI instruction, interrupts are enabled after returning the main routine. (Refer to Figure 13)

Fig. 13 Program example of interrupt processing

Fig. 14 Internal state when interrupt occurs

Fig. 15 Interrupt system diagram

# (6) Interrupt control registers

- Interrupt control register V1

Interrupt enable bits of external 0, external 1, timer

1 and timer 2 are assigned to register V1. Set the contents of this register through register A with the TV1A instruction. The TAV1 instruction can be used to transfer the contents of register V1 to register A.

- Interrupt control register V2

Interrupt enable bits of timer 3, timer 4, A-D and serial I/O are assigned to register V2. Set the contents of this register through register A with the TV2A instruction. The TAV2 instruction can be used to transfer the contents of register V2 to register A.

Table 6 Interrupt control registers

|       | Interrupt control register V1         | at | reset: 00002       | at RAM back-up : 00002         | R/W |

|-------|---------------------------------------|----|--------------------|--------------------------------|-----|

| V13   | Timer 2 interrupt enable bit          | 0  | Interrupt disabled | (SNZT2 instruction is valid)   |     |

| V 13  |                                       | 1  | Interrupt enabled  | (SNZT2 instruction is invalid) | _   |

| V12   | Timer 1 interrupt enable bit          | 0  | Interrupt disabled | (SNZT1 instruction is valid)   |     |

|       |                                       | 1  | Interrupt enabled  | (SNZT1 instruction is invalid) |     |

| V11   | Everyon distance and be big           | 0  | Interrupt disabled | (SNZ1 instruction is valid)    |     |

| V 17  | External 1 interrupt enable bit       | 1  | Interrupt enabled  | (SNZ1 instruction is invalid)  |     |

| V10   | External 0 interrupt enable bit       | 0  | Interrupt disabled | (SNZ0 instruction is valid)    |     |

|       |                                       | 1  | Interrupt enabled  | (SNZ0 instruction is invalid)  |     |

|       | Interrupt control register V2         | at | reset: 00002       | at RAM back-up : 00002         | R/W |

| Va    |                                       | 0  | Interrupt disabled | (SNZSI instruction is valid)   |     |

| V 23  | V23   Serial I/O interrupt enable bit |    | Interrupt enabled  | (SNZSI instruction is invalid) |     |

| V22   | A D interviet mobile hit              | 0  | Interrupt disabled | (SNZAD instruction is valid)   |     |

| V Z2  | A-D interrupt enable bit              | 1  | Interrupt enabled  | (SNZAD instruction is invalid) |     |

| V21   | Timer 4 interrupt enable bit          | 0  | Interrupt disabled | (SNZT4 instruction is valid)   |     |

| ¥ Z 1 |                                       | 1  | Interrupt enabled  | (SNZT4 instruction is invalid) |     |

| ١/٥٠  | Timer 3 interrupt enable bit          | 0  | Interrupt disabled | (SNZT3 instruction is valid)   |     |

| V20   |                                       | 1  | Interrupt enabled  | (SNZT3 instruction is invalid) |     |

Note: "R" represents read enabled, and "W" represents write enabled.

#### (7) Interrupt sequence

Interrupts only occur when the respective INTE flag, interrupt enable bits (V10-V13 and V20-V23), and interrupt request flag are "1." The interrupt actually occurs 2 to 3 machine cycles after the cycle in which all three

conditions are satisfied. The interrupt occurs after 3 machine cycles only when the three interrupt conditions are satisfied on execution of other than one-cycle instructions (Refer to Figure 16).

Fig. 16 Interrupt sequence

# **EXTERNAL INTERRUPTS**

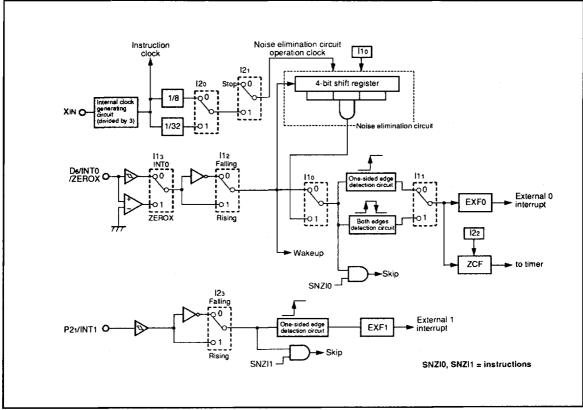

The 4510 Group has two external interrupts (external 0 and external 1). An external interrupt request occurs when a valid waveform is input to an interrupt input pin (edge detection).

External 0 interrupt is equipped with a noise elimination circuit and a zero cross detection circuit. The zero cross detection circuit detects the point when the voltage level of an alternating waveform passes 0 V. The external interrupts can be controlled with the interrupt control registers I1 and I2.

Table 7 External interrupt activated conditions

| Name                 | Input pin     | Activated condition                                                                                                                               | Valid waveform selection bit |

|----------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| External 0 interrupt | De/INT0/ZEROX | When the next waveform is input to De/INT0/ZEROX pin • Falling waveform (*H"→*L") • Rising waveform (*L"→*H") • Both rising and falling waveforms | 111<br> 112                  |

| External 1 interrupt | P21/INT1      | When the next waveform is input to P2₁/INT1 pin •Falling waveform ("H"→"L") •Rising waveform ("L"→"H")                                            | 123                          |

Fig. 17 External interrupt circuit structure

#### (1) External 0 interrupt request flag (EXF0)

External 0 interrupt request flag (EXF0) is set to "1" when a valid waveform is input to D6/INT0/ZEROX pin. External 0 interrupt is equipped with a noise elimination circuit and a zero cross detection circuit. The valid waveforms causing the interrupt must be retained at their level for 4 clock cycles or more of the system clock (Refer to Figure 16).

The state of EXF0 flag can be examined with the skip instruction (SNZ0). Use the interrupt control register V1 to select the interrupt or the skip instruction. The EXF0 flag is cleared to "0" when an interrupt occurs or when the next instruction is skipped with the skip instruction.

The De/INTO/ZEROX pin need not be selected the external interrupt input INTO function or the normal I/O port De function. However, the EXFO flag is set to "1" when a valid waveform is input even if it is used as an I/O port De.

#### External 0 interrupt activated condition

External 0 interrupt activated condition is satisfied when a valid waveform is input to De/INT0/ZEROX pin.

The valid waveform can be selected from rising waveform, falling waveform or both rising and falling waveforms. An example of how to use the external 0 interrupt is as follows.

- ① Clear the bits 0 and 3 of register I1 to "0," and select the valid waveform with the bits 1 and 2 of register I1.

- 2 Clear the EXF0 flag to "0" with the SNZ0 instruction.

- Set the NOP instruction for the case when a skip is performed with the SNZ0 instruction.

- Set both the external 0 interrupt enable bit (V1o) and the INTE flag to \*1."

The external 0 interrupt is now enabled. Now when a valid waveform is input to the Ds/INT0/ZEROX pin, the EXF0 flag is set to "1" and the external 0 interrupt occurs.

#### (2) External 1 interrupt request flag (EXF1)

External 1 interrupt request flag (EXF1) is set to "1" when a valid waveform is input to P2<sub>1</sub>/INT1 pin.

The valid waveforms causing the interrupt must be retained at their level for 4 clock cycles or more of the system clock (Refer to Figure 16).

The state of EXF1 flag can be examined with the skip instruction (SNZ1). Use the interrupt control register V1 to select the interrupt or the skip instruction. The EXF1 flag is cleared to "0" when an interrupt occurs or when the next instruction is skipped with the skip instruction.

The P21/INT1 pin need not be selected the external interrupt input INT1 function or the normal input port P21 function. However, the EXF1 flag is set to "1" when a valid waveform is input even if it is used as an input port P21.

#### External 1 interrupt activated condition

External 1 interrupt activated condition is satisfied when a valid waveform is input to P21/INT1 pin.

The valid waveform can be selected from rising waveform or falling waveform. An example of how to use the external 1 interrupt is as follows.

- Select the valid waveform with the bit 3 of register

12

- ② Clear the EXF1 flag to "0" with the SNZ1 instruction.

- ③ Set the NOP instruction for the case when a skip is performed with the SNZ1 instruction.

- Set both the external 1 interrupt enable bit (V11)

and the INTE flag to "1."

The external 1 interrupt is now enabled. Now when a valid waveform is input to the P21/INT1 pin, the EXF1 flag is set to "1" and the external 1 interrupt occurs.

# **4510 Group**

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

# (3) External interrupt control registers

• Interrupt control register I1 Register I1 controls the noise elimination circuit, valid waveform for the external 0 interrupt, return level (valid level of wakeup signal) from the RAM back-up mode, and De/INTO/ZEROX pin function. Set the contents of this register through register A with the TI1A instruction. The TAI1 instruction can be used to transfer the contents of register I1 to register A. • Interrupt control register 12

Register I2 controls the sampling clock of noise elimination circuit, valid waveform for the external 1 interrupt, set/clear of zero cross input flag. Set the contents of this register through register A with the TI2A instruction. The TAI2 instruction can be used to transfer the contents of register I2 to register A.

Table 8 External interrupt control registers

|              | Interrupt control register I1                                | at                    | reset : 00002                                                                              | at RAM back-up : state retained        | R/W      |  |  |  |

|--------------|--------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------|----------------------------------------|----------|--|--|--|

| 110          | I13 De/INT0/ZEROX pin function selection bit-                |                       | 0 INTO/De (input/output)                                                                   |                                        |          |  |  |  |

| 113          |                                                              |                       | ZEROX/D6 (input/output)                                                                    |                                        |          |  |  |  |

| 12           | Interrupt valid waveform for INTO pin/                       | 0                     | 0 Falling waveform ("L" level of INTO pin is recogniz<br>SNZIO instruction)/"L" level      |                                        |          |  |  |  |

| 112          | return level selection bit (Note 2)                          |                       | Rising waveform ("H" level of INTO pin is recognized with the SNZIO instruction)/"H" level |                                        |          |  |  |  |

| <b>i</b> 111 | ra . Publication of the control by                           |                       | One-sided edge detected                                                                    |                                        |          |  |  |  |

| 111          | Edge detection circuit control bit                           | 1 Both edges detected |                                                                                            |                                        |          |  |  |  |

| l1o          | Noise elimination circuit control bit                        | 0                     | Disabled                                                                                   |                                        |          |  |  |  |

| 110          | Noise elimination circuit control bit                        | 1                     | Enabled                                                                                    |                                        |          |  |  |  |

|              | Interrupt control register 12                                | at                    | reset : 00002                                                                              | at RAM back-up : state retained        | R/W      |  |  |  |

| 10-          | Interrupt valid waveform for INT1 pin selection bit (Note 2) |                       | Falling waveform SNZI1 instruction                                                         | ("L" level of INT1 pin is recognized.) | with the |  |  |  |

| 123          |                                                              |                       | Rising waveform ("H" level of INT1 pin is recognized with the SNZI1 instruction.)          |                                        |          |  |  |  |

| 10-          | 7                                                            | 0                     | Zero cross input flag cleared (set impossible)                                             |                                        |          |  |  |  |

| 122          | Zero cross input flag control bit                            | 1                     | Zero cross input flag set possible                                                         |                                        |          |  |  |  |

| 121          | Noise elimination circuit sampling clock                     | 0                     | Stop                                                                                       |                                        |          |  |  |  |

| 121          | control bit                                                  | 1                     | Operating                                                                                  |                                        |          |  |  |  |

| 120          | Noise elimination circuit sampling clock                     | 0                     | Instruction clock                                                                          |                                        |          |  |  |  |

| 120          | selection bit                                                | 1                     | Instruction clock                                                                          | divided by 32                          |          |  |  |  |

Notes 1: "R" represents read enabled, and "W" represents write enabled.

<sup>2:</sup> When the contents of I12 and I23 are changed, the external interrupt request flags EXF0 and EXF1 may be set, respectively. Accordingly, clear the EXF0 and EXF1 flags to "0" with the SNZ0 and SNZ1 instructions, respectively.

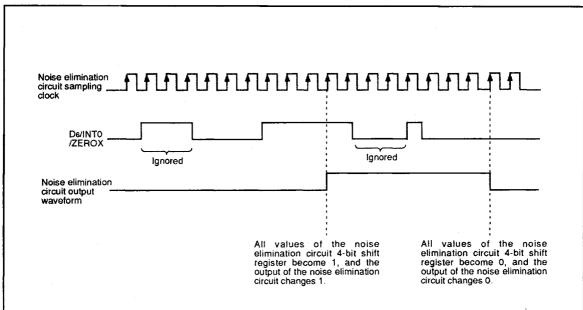

#### (4) Noise elimination circuit

External 0 interrupt is equipped with a noise elimination circuit. This noise elimination circuit takes sampling four times with the noise elimination circuit sampling clock which is the instruction clock divided by 8 or 32 when the level of external 0 interrupt input is changed. As a result, if values of the noise elimination circuit 4-bit shift register become "1111" or "0000," the output of the noise elimination circuit changes "1" or "0," respectively. An example of how to use the noise elimination circuit is as follows.

① Set the bit 0 of register I1 to "1," select the valid waveform (= valid edge) with the bits 1 and 2 of register I1, and select the pin function with the bit 3 of register I1.

- ② Clear the EXF0 flag to "0" with the SNZ0 instruction

- ③ Set the NOP instruction for the case when a skip is performed with the SNZ0 instruction.

- Set both the external 0 interrupt enable bit (V1o)

and the INTE flag to "1."

- Select the sampling clock of the noise elimination circuit with the bit 0 of register I2, and set the bit 1 of register I2 to \*1."

The external 0 interrupt is now enabled. Now when a valid waveform is input to the De/INTO/ZEROX pin, the EXF0 flag is set to "1" and the external 0 interrupt occurs.

Fig. 18 Noise elimination circuit operation

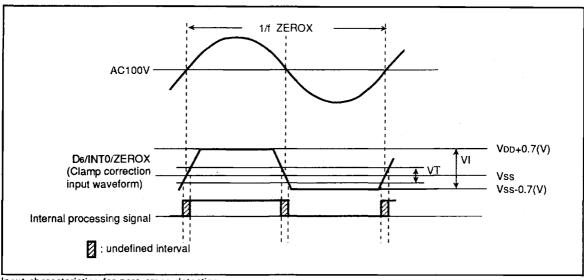

# **ZERO CROSS DETECTION CIRCUIT**

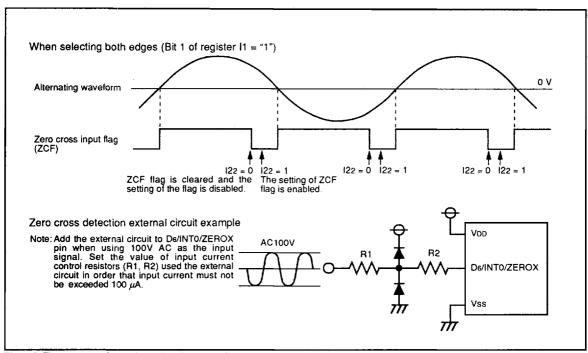

External 0 interrupt is equipped with a zero cross detection circuit which is used to detect the point when the voltage level of an alternating waveform passes 0 V (zero cross). Zero cross point to be detected can be selected when changing from minus to plus, plus to minus, or both.

The zero cross detection circuit can be used together with the noise elimination circuit.

In addition, the zero cross point which is detected by the zero cross detection circuit can be used as the start trigger for the timer 3 count operation (Refer to the zero cross input flag).

An example of how to use the zero cross detection circuit is as follows.

- ① Set the bit 3 of register I1 to "1" and select the valid waveform (= zero cross point to be detected) with bits 1 and 2.

- @ Clear the EXF0 flag to "0" with the SNZ0 instruction.

- Set the NOP instruction for the case when a skip is performed with the SNZ0 instruction.

- Set both the external 0 interrupt enable bit (V1c) and the INTE flag to "1."

The external 0 interrupt is now enabled. Now when an alternating waveform is input to the D6/INTO/ZEROX pin, zero cross point is detected, the EXF0 flag is set to "1," and the

external 0 interrupt occurs.

The interval from zero cross is detected until program at the interrupt address is executed is 4 to 5 machine cycles (the delay time is added when using the noise elimination circuit).

#### (1) Zero cross input flag (ZCF)

The zero cross input flag (ZCF) is used to start timer 3 count operation by the zero cross point which is detected with the zero cross detection circuit.

The ZCF flag is set to "1" when the voltage level of an alternating waveform input to the De/INTO/ZEROX pin passes 0 V. When the bit 2 of timer control register W3 is set to "1," timer 3 starts counting when the ZCF flag is set to "1" and stops counting when it is cleared to "0."

The ZCF flag can be controlled by the bit 2 (122) of register I2. It can be set (operation state) when I22 is set to "1." It cannot be set (stop state) when I22 is cleared to "0" because it is fixed to "0." Clear I22 to "0" to clear the ZCF flag. However, when it is to be used after clear, set I22 to "1" and return it to the operation state.

Fig. 19 Zero cross detection circuit operation

# **TIMERS**

The 4510 Group has the programmable timers.

· Programmable timer

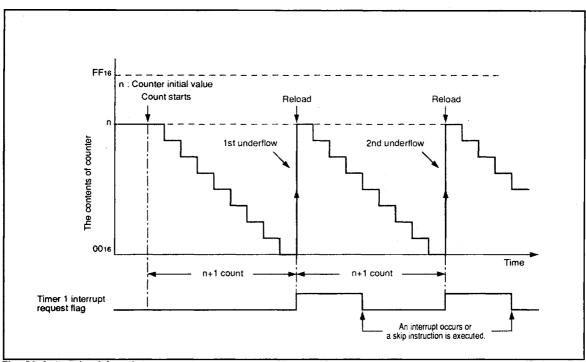

The programmable timer has a reload register and enables the frequency dividing ratio to be set. It is decremented from a setting value n. When it underflows (count to n + 1), a timer interrupt request flag is set to "1," new data is loaded from the reload register, and count continues (autoreload function).

Fixed dividing frequency timer

The fixed dividing frequency timer has the fixed frequency dividing ratio (n). An interrupt request flag is set to "1" after every n count of a count pulse.

Fig. 20 Auto-reload function

# MITSUBISHI MICROCOMPUTERS 4510 Group

# SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

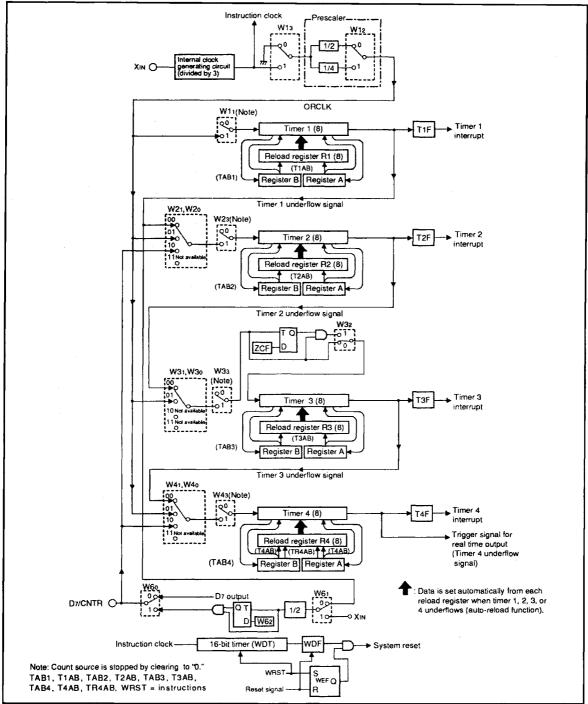

The 4510 Group timer consists of the following circuits.

· Prescaler : frequency divider

• Timer 1: 8-bit programmable timer

• Timer 2 : 8-bit programmable timer

• Timer 3: 8-bit programmable timer • Timer 4: 8-bit programmable timer

(Timers 1 to 4 have the interrupt function, respectively)

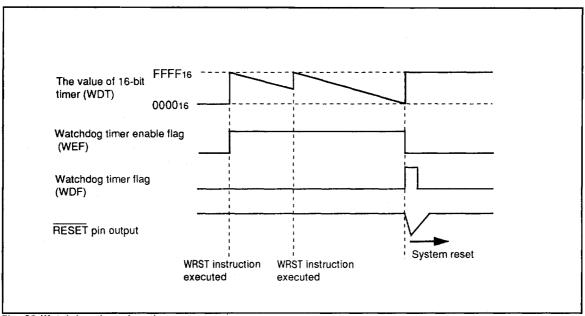

· Watchdog timer

These timers can be controlled with the timer control registers W1 to W6. Each function is described below.

Table 9 Function related timers

| Circuit        | Structure                                 | Count source                                          | Frequency<br>dividing ratio | Use of output signal                                 | Control register |

|----------------|-------------------------------------------|-------------------------------------------------------|-----------------------------|------------------------------------------------------|------------------|

| Prescaler      | Frequency divider                         | Instruction clock                                     | 2, 4                        | • Timer 1, 2, 3 and 4 count sources                  | W1               |

| Timer 1        | 8-bit programmable<br>binary down counter | Prescaler output (ORCLK)                              | 1 to 256                    | Timer 2 count source  CNTR output  Timer 1 interrupt | W1<br>W6         |

| Timer 2        | 8-bit programmable binary down counter    | Timer 1 underflow Prescaler output (ORCLK) CNTR input | 1 to 256                    | • Timer 3 count source<br>• Timer 2 interrupt        | W2               |

| Timer 3        | , ,                                       | Timer 2 underflow Prescaler output (ORCLK)            | 1 to 256                    | Timer 4 count source Timer 3 interrupt               | W3               |

| Timer 4        | ,                                         | Prescaler output (ORCLK)     CNTR input               | 1 to 256                    | Real time output     Timer 4 interrupt               | W4               |

| Watchdog timer | 16-bit fixed dividing<br>frequency        | • Instruction clock                                   | 65536                       | System reset                                         |                  |

# **4510 Group**

#### SINGLE-CHIP 4-BIT CMOS MICROCOMPUTER

Fig. 21 Timers structure

Table 10 Timer control registers

|                                 | Timer control register W1                                                                                                        | ;                                                                           | at reset : 00002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                         | R/W |  |  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|

| W13                             | Prescaler control bit                                                                                                            | 0                                                                           | Stop (state initiali                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | zed)                                                                                                                                                    |     |  |  |

| ** 13                           | Trescarci control bit                                                                                                            | 1                                                                           | 1 Operating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                         |     |  |  |

| W12                             | Prescaler dividing ratio selection bit                                                                                           | 0                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                         |     |  |  |

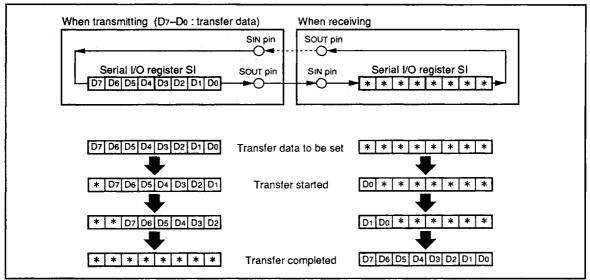

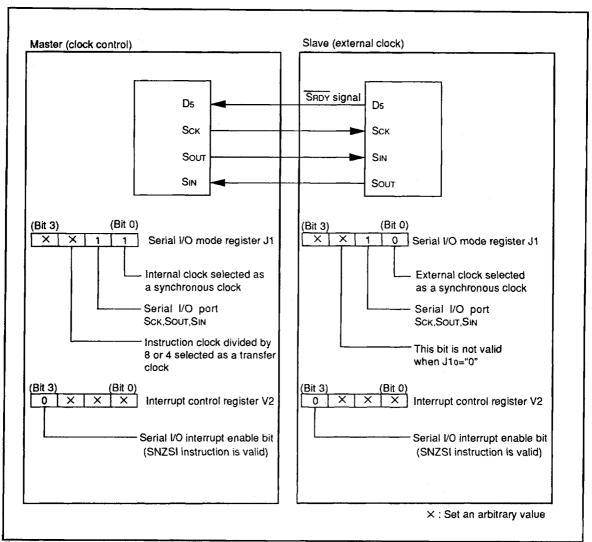

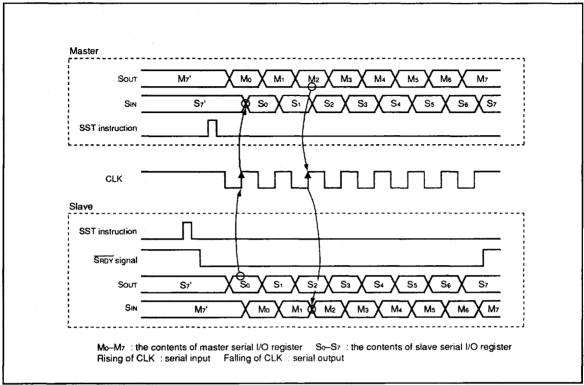

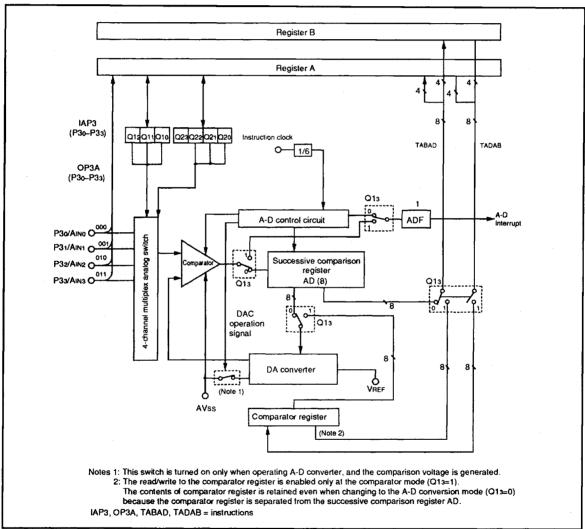

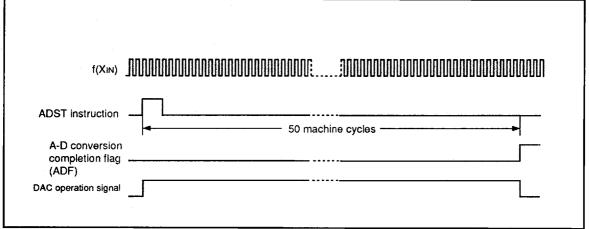

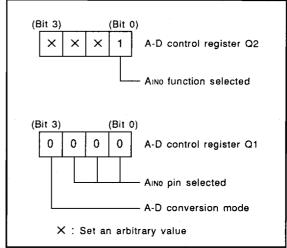

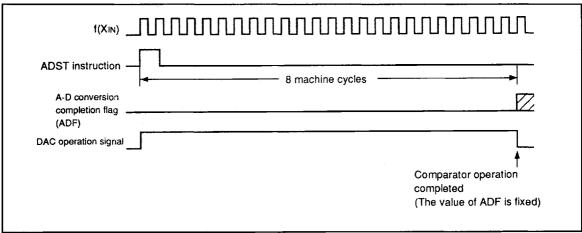

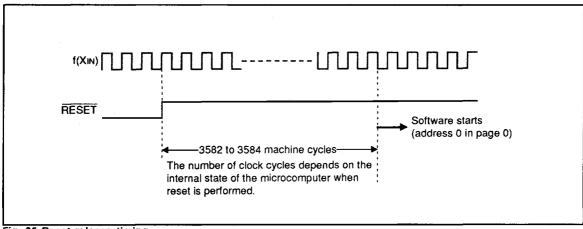

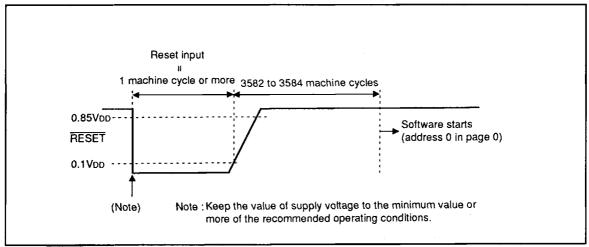

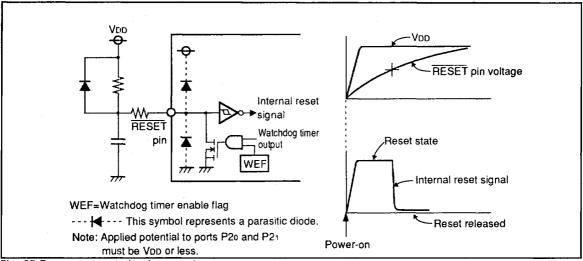

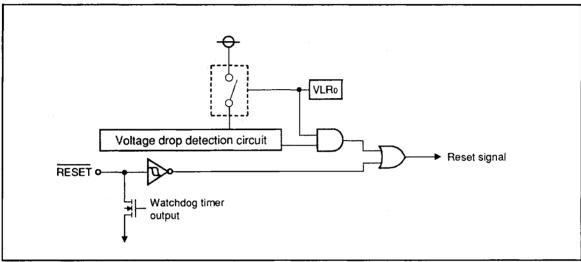

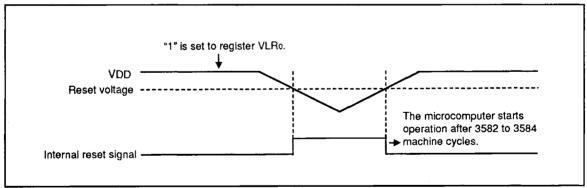

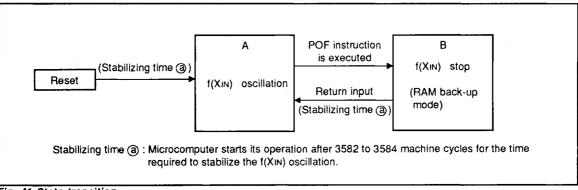

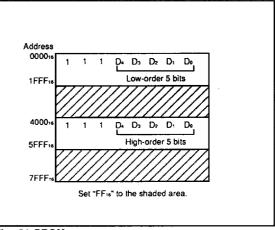

| 1712                            | Trescarer dividing ratio selection bit                                                                                           | 1 Instruction clock divided by 4                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                         |     |  |  |