# **Electrical Specifications**

DSP56002 (5.0 Volt Operation)

**DSP56L002** (3.3 Volt Operation – Lower Power Consumption)

The DSP56002 is fabricated in high density CMOS with TTL compatible inputs and outputs.

**Table 5** Absolute Maximum Ratings (GND = 0 Vdc)

| D. Alian                                                | 0                | Value                                 |                                       |      |

|---------------------------------------------------------|------------------|---------------------------------------|---------------------------------------|------|

| Rating                                                  | Symbol           | DSP56002                              | DSP56L002                             | Unit |

| Supply Voltage                                          | V <sub>CC</sub>  | -0.3 to +7.0                          | -0.3 to +4.0                          | V    |

| All Input Voltages                                      | V <sub>IN</sub>  | GND - 0.5 to<br>V <sub>CC</sub> + 0.5 | GND - 0.5 to<br>V <sub>CC</sub> + 0.5 | V    |

| Current Drain per Pin Excluding V <sub>CC</sub> and GND | ı                | 10                                    | 10                                    | mA   |

| Operating Temperature Range                             | TJ               | -40 to +105                           | 0 to +80                              | °C   |

| Storage Temperature                                     | T <sub>stg</sub> | -55 to +150                           | -55 to +150                           | °C   |

Table 6 Thermal Characteristics of Packages

| Thermal<br>Resistance              |                 | PQFP  |       |               | PGA   |       |               | TQFP  |       |

|------------------------------------|-----------------|-------|-------|---------------|-------|-------|---------------|-------|-------|

|                                    | Symbol          | Value | Units | Symbol        | Value | Units | Symbol        | Value | Units |

| Junction<br>to<br>Ambient          | Θ <sub>JA</sub> | 38    | °C/W  | $\Theta_{JA}$ | 22    | °C/W  | $\Theta_{JA}$ | 49    | °C/W  |

| Junction<br>to Case<br>(estimated) | Θ <sub>JC</sub> | 13    | °C/W  | ΘJC           | 6.5   | °C/W  | ΘJC           | 12    | °C/W  |

Note: See discussion under "Design Considerations, Heat Dissipation," page 86.

DSP56002

## DSP56002 DC Electrical Characteristics

$(V_{CC} = 5.0 \text{ Vdc} \pm 10\%; T_J = -40^{\circ} \text{ to} +105^{\circ} \text{ C})$

Table 7 DC Electrical Characteristics for the DSP56002

| Oh avas As vis Ais a                                                                                                                   | Cumbal                                                                      |                          | DSP56002      |                                                       |                |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------|---------------|-------------------------------------------------------|----------------|

| Characteristics                                                                                                                        | Symbol                                                                      | Min                      | Тур           | Max                                                   | Units          |

| Supply Voltage                                                                                                                         | V <sub>cc</sub>                                                             | 4.5                      | 5.0           | 5.5                                                   | V              |

| Input High Voltage  • Except EXTAL, RESET, MODA, MODB, MODC  • EXTAL  • RESET  • MODA, MODB, MODC                                      | V <sub>IH</sub><br>V <sub>IHC</sub><br>V <sub>IHR</sub><br>V <sub>IHM</sub> | 2.0<br>4.0<br>2.5<br>3.5 | 1111          | V <sub>CC</sub><br>V <sub>CC</sub><br>V <sub>CC</sub> | V<br>V<br>V    |

| Input Low Voltage                                                                                                                      | V <sub>IL</sub><br>V <sub>ILC</sub><br>V <sub>ILM</sub>                     | -0.5<br>-0.5<br>-0.5     | -<br>-<br>-   | 0.8<br>0.6<br>2.0                                     | V<br>V<br>V    |

| EXTAL, RESET, MODA/IRQA, MODB/IRQB, MODC/NMI, BR, WT                                                                                   | TIN                                                                         | ·<br>                    |               |                                                       |                |

| Three-State (Off-State) Input Current (@ 2.4 V / 0.4 V)                                                                                | I <sub>TSI</sub>                                                            | -10                      | _             | 10                                                    | μΑ             |

| Output High Voltage (I <sub>OH</sub> = -0.4 mA)                                                                                        | V <sub>OH</sub>                                                             | 2.4                      | _             | _                                                     | V              |

| Output Low Voltage ( $I_{OL} = 3.0 \text{ mA}$ ;<br>$\overline{\text{HREQ}} I_{OL} = 6.7 \text{ mA}$ , TXD $I_{OL} = 6.7 \text{ mA}$ ) | V <sub>OL</sub>                                                             |                          | <b>–</b>      | 0.4                                                   | ٧              |

| Internal Supply Current at 40 MHz (See Note 3) • in Wait Mode (See Note 1) • in Stop Mode (See Note 1)                                 | l <sub>ccw</sub><br>lccs                                                    | _                        | 90<br>12<br>2 | 105<br>20<br>95                                       | mA<br>mA<br>μA |

| Internal Supply Current at 66 MHz (See Note 3) • in Wait Mode (See Note 1) • in Stop Mode (See Note 1)                                 | l <sub>cci</sub><br>l <sub>ccw</sub><br>l <sub>ccs</sub>                    |                          | 95<br>15<br>2 | 130<br>25<br>95                                       | mA<br>mA<br>μA |

| PLL Supply Current (See Note 4) at 40 MHz at 66 MHz                                                                                    |                                                                             |                          | 1<br>1.1      | 1.5<br>1.5                                            | mA<br>mA       |

| CKOUT Supply Current (See Note 5)at 40 MHz<br>at 66 MHz                                                                                |                                                                             |                          | 14<br>28      | 20<br>35                                              | mA<br>mA       |

| Input Capacitance (See Note 2)                                                                                                         | C <sub>IN</sub>                                                             | _                        | 10            | _                                                     | pF             |

- 1. In order to obtain these results all inputs must be terminated (i.e., not allowed to float) using CMOS levels.

- 2. Periodically sampled and not 100% tested.

- 3. **Power Consumption** in the **Design Considerations** section describes how to calculate the external supply current.

- 4. Values given are for PLL enabled.

- 5. Values given are for CKOUT enabled.

# DSP56L002 DC Electrical Characteristics

$(V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}; T_J = 0^{\circ} \text{ to } +80^{\circ} \text{ C})$

Table 8 DC Electrical Characteristics for the DSP56L002

| Characteristics                                                                                                       | Comple at                                                |              | DSP56L00                                                              | )2             | 11-11-         |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------|-----------------------------------------------------------------------|----------------|----------------|

| Characteristics                                                                                                       | Symbol                                                   | Min          | Typ Max  3.3 3.6  - V <sub>CC</sub> - V <sub>CC</sub> - 0.8 - 0.4 - 1 | Units          |                |

| Supply Voltage                                                                                                        | V <sub>CC</sub>                                          | 3.0          | 3.3                                                                   | 3.6            | V              |

| Input High Voltage • Except EXTAL • EXTAL                                                                             | V <sub>IH</sub><br>V <sub>IHC</sub>                      | 2.0<br>2.7   | <u>-</u>                                                              |                | V              |

| Input Low Voltage • Except EXTAL • EXTAL                                                                              | V <sub>IL</sub>                                          | -0.5<br>-0.5 |                                                                       |                | V              |

| Input Leakage Current EXTAL, RESET, MODA/IRQA, MODB/IRQB, MODC/NMI, BR, WT                                            | I <sub>IN</sub>                                          | -1           | _                                                                     | 1              | μА             |

| Three-State (Off-State) Input Current (@ 2.4 V / 0.4 V)                                                               | I <sub>TSI</sub>                                         | -10          |                                                                       | 10             | μА             |

| Output High Voltage (I <sub>OH</sub> = -0.4 mA)                                                                       | V <sub>OH</sub>                                          | 2.4          |                                                                       |                | ٧              |

| Output Low Voltage ( $I_{OL}$ = 3.0 mA;<br>HREQ $I_{OL}$ = 6.7 mA, TXD $I_{OL}$ = 6.7 mA,<br>WR, RD $I_{OL}$ =2.0 mA) | V <sub>OL</sub>                                          |              | _                                                                     | 0.4            | V              |

| Internal Supply Current at 40 MHz (See Note 3) • in Wait Mode (See Note 1) • in Stop Mode (See Note 1)                | I <sub>CCI</sub><br>I <sub>CCW</sub><br>I <sub>CCS</sub> |              | 50<br>10<br>1                                                         | 65<br>14<br>50 | mA<br>mA<br>μA |

| PLL Supply Current (See Note 4)                                                                                       |                                                          | _            | 0.7                                                                   | 1.1            | mA             |

| CKOUT Supply Current (See Note 5)                                                                                     |                                                          | _            | 10                                                                    | 14             | mA             |

| Input Capacitance (See Note 2)                                                                                        | C <sub>IN</sub>                                          | _            | 10                                                                    | _              | pF             |

- 1. In order to obtain these results all inputs must be terminated (i.e., not allowed to float) using CMOS levels.

- 2. Periodically sampled and not 100% tested.

- 3. **Power Consumption** in the **Design Considerations** section describes how to calculate the external supply current.

- 4. Values given are for PLL enabled.

- 5. Values given are for CKOUT enabled.

## **AC Electrical Characteristics**

The timing waveforms in the AC Electrical Characteristics are tested with a  $V_{IL}$  maximum of 0.5 V and a  $V_{IH}$  minimum of 2.4 V for all pins, except EXTAL, RESET, MODA, MODB, and MODC. These four pins are tested using the input levels set forth in the DC Electrical Characteristics section. AC timing specifications which are referenced to a device input signal are measured in production with respect to the 50% point of the respective input signal's transition. DSP56002/L002 output levels are measured with the production test machine  $V_{OL}$  and  $V_{OH}$  reference levels set at 0.8 V and 2.0 V respectively.

#### **Internal Clocks**

For each occurrence of  $T_H$ ,  $T_L$ ,  $T_C$  or  $I_{CYC}$  substitute with the expressions given in Table 9.  $ET_H$ ,  $ET_L$ , and  $ET_C$  are further defined in Table 10. DF and MF are PLL division and multiplication factors set in registers.

Table 9 Internal Clocks

| Characteristics                                | Symbol         | Expression                                                                     |

|------------------------------------------------|----------------|--------------------------------------------------------------------------------|

| Internal Operation Frequency                   | f              |                                                                                |

| Internal Clock High Period - with PLL disabled | T <sub>H</sub> | ETH                                                                            |

| - with PLL enabled and MF $\leq$ 4             |                | (Min) 0.48 x ET <sub>C</sub> x DF/MF<br>(Max) 0.52 x ET <sub>C</sub> x DF/MF   |

| - with PLL enabled and MF > 4                  |                | (Min) 0.467 x ET <sub>C</sub> x DF/MF<br>(Max) 0.533 x ET <sub>C</sub> x DF/MF |

| Internal Clock Low Period                      | TL             |                                                                                |

| - with PLL disabled                            | _              | ETL                                                                            |

| - with PLL enabled and MF $\leq$ 4             |                | (Min) 0.48 x ET <sub>C</sub> x DF/MF<br>(Max) 0.52 x ET <sub>C</sub> x DF/MF   |

| - with PLL enabled and MF > 4                  |                | (Min) 0.467 x ET <sub>C</sub> x DF/MF<br>(Max) 0.533 x ET <sub>C</sub> x DF/MF |

| Internal Clock Cycle Time                      | T <sub>C</sub> | ET <sub>C</sub> x DF/MF                                                        |

| Instruction Cycle Time                         | lcyc           | 2 x T <sub>C</sub>                                                             |

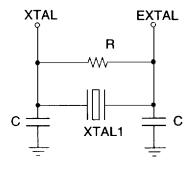

### Clock

The DSP56002/L002 system clock may be derived from the on-chip crystal oscillator as shown in Figure 3, or it may be externally supplied. An externally supplied square wave voltage source should be connected to EXTAL, leaving XTAL physically unconnected (see Figure 4) to the board or socket. The rise and fall time of this external clock should be 4 ns maximum.

#### Fundamental Frequency Crystal Oscillator

Suggested Component Values

R =  $680 \text{ K}\Omega \pm 10\%$ C =  $20 \text{ pf} \pm 20\%$

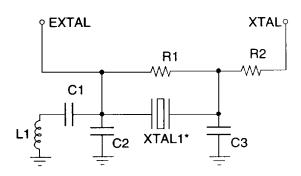

#### 3<sup>rd</sup> Overtone Crystal Oscillator

Suggested Component Values

$R1 = 470 \text{ K}\Omega \pm 10\%$   $R2 = 330 \Omega \pm 10\%$   $C1 = 0.1 \mu\text{f} \pm 20\%$   $C2 = 26 \text{ pf} \pm 20\%$   $C3 = 20 \text{ pf} \pm 10\%$   $L1 = 2.37 \mu\text{H} \pm 10\%$

XTAL = 40 MHz, AT cut, 20 pf load,  $50 \Omega$  max series resistance

#### **NOTES:**

- The suggested crystal source is ICM, # 433163 - 4.00 (4 MHz fundamental, 20 pf load) or # 436163 - 30.00 (30 MHz fundamental, 20 pf load).

- To reduce system cost, a ceramic resonator may be used instead of the crystal. Suggested source: Murata-Erie #CST4.00MGW040

- 1. \*3<sup>rd</sup> overtone crystal.

- The suggested crystal source is ICM, # 471163 - 40.00 (40 MHz 3<sup>rd</sup> overtone, 20 pf load).

- 3. R2 limits crystal current.

- Reference Benjamin Parzen, <u>The Design of Crystal and Other Harmonic Oscillators</u>, John Wiley & Sons, 1983.

Figure 3 Crystal Oscillator Circuits

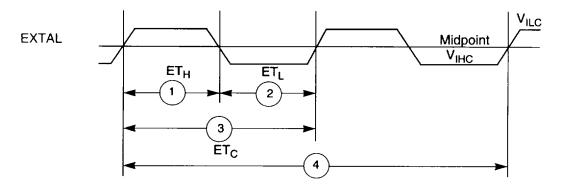

Clock

NOTE: The midpoint is  $V_{ILC}$  + 0.5 ( $V_{IHC}$  -  $V_{ILC}$ ).

Figure 4 External Clock Timing

Table 10 Clock Operation

| Num | Characteristics                                                                                                           | Symbol          | 40           | MHz           | 66             | MHz           | Unit  |

|-----|---------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|---------------|----------------|---------------|-------|

|     | Characteristics                                                                                                           | - Cymbol        | Min          | Max           | Min            | Max           | Oiiit |

|     | Frequency of Operation (EXTAL Pin)                                                                                        | E <sub>f</sub>  | 0            | 40            | 0              | 66            | MHz   |

| 1   | Clock Input High (See Note) • with PLL disabled (46.7% - 53.3% duty cycle) • with PLL enabled (42.5% - 57.5% duty cycle)  | ET <sub>H</sub> | 11.7<br>10.5 | ∞<br>235.5 μs | 7.09<br>6.36   | ∞<br>235.5 μs | ns    |

| 2   | Clock Input Low (See Note)  • with PLL disabled (46.7% - 53.3% duty cycle)  • with PLL enabled (42.5% - 57.5% duty cycle) | ETL             | 11.7<br>10.5 | ∞<br>235.5 µs | 7.09<br>6.36   | ∞<br>235.5 μs | ns    |

| 3   | Clock Cycle Time • with PLL disabled • with PLL enabled                                                                   | ET <sub>C</sub> | 25<br>25     | ∞<br>409.6 μs | 15.15<br>15.15 | ∞<br>409.6 μs | ns    |

| 4   | Instruction Cycle Time = I <sub>CYC</sub> = 2 × T <sub>C</sub> (See Note) • with PLL disabled • with PLL enabled          | Ісус            | 50<br>50     | ∞<br>819.2 μs | 30.3<br>30.3   | ∞<br>819.2 μs | ns    |

NOTE: External Clock Input High and External Clock Input Low are measured at 50% of the input transition.

## Phase-Locked Loop (PLL)

Table 11 Phase-Locked Loop Characteristics

| Characteristics                                        | Expression                                      | Min                  | Max                  | Unit |

|--------------------------------------------------------|-------------------------------------------------|----------------------|----------------------|------|

| VCO frequency when PLL enabled                         | MF x E <sub>f</sub><br>(See Notes 1,2)          | 10                   | f<br>(See Note 3)    | MHz  |

| PLL external capacitor (PCAP pin to V <sub>CCP</sub> ) | MF × Cpcap (See Note 4)<br>@ MF ≤ 4<br>@ MF > 4 | MF × 340<br>MF × 380 | MF × 480<br>MF × 970 | pF   |

#### NOTES:

- 1. The "E" in ETH, ETL, and ETC means external.

- 2. MF is the PCTL Multiplication Factor bits (MF0 MF11). DF is the PCTL Division Factor bits (DF0 DF3).

- 3. The maximum VCO frequency is limited to the internal operation frequency.

- 4. Cpcap is the value of the PLL capacitor (connected between PCAP pin and V<sub>CCP</sub>) for MF=1. The recommended value for Cpcap is 400 pF for MF ≤ 4 and 540 pF for MF > 4.

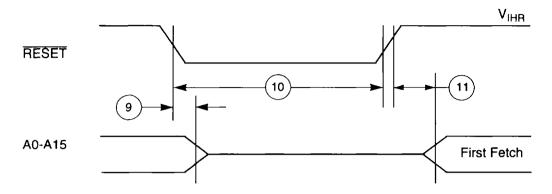

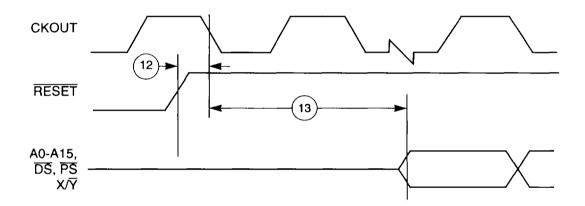

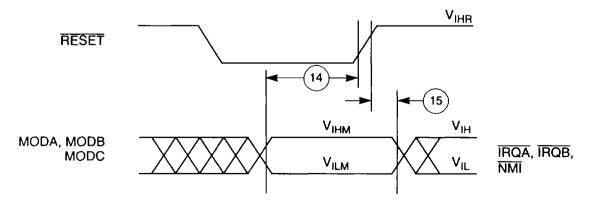

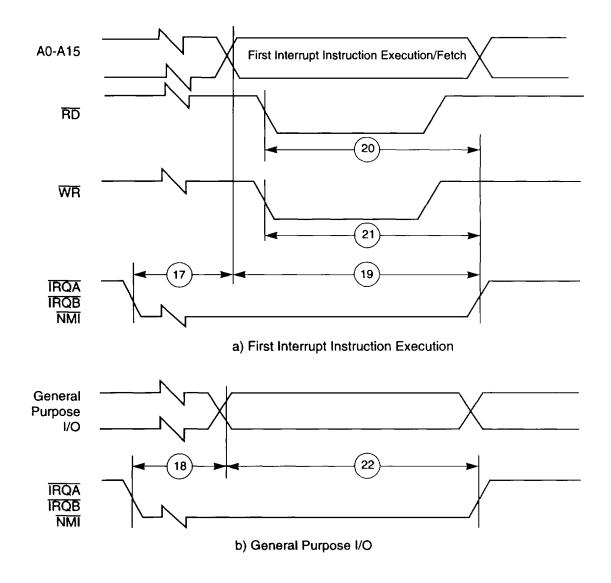

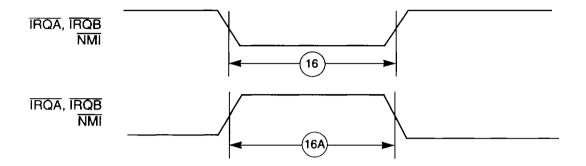

## Reset, Stop, Mode Select, and Interrupt Timing

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_{J} = -40^{\circ} \text{ to} + 105^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_J = 0^{\circ}$  to +80° C,  $C_L = 50 \text{ pF} + 2 \text{ TTL Loads}$

WS = Number of wait states (1 WS =  $T_C$ ) programmed into external bus access using BCR (WS = 0 - 15)

Table 12 Reset, Stop, Mode Select, and Interrupt Timing

| Num |                                                                                                                                                               | 40/6                                                                   |                      |                |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------|----------------|

|     | Characteristics -                                                                                                                                             | Min                                                                    | Max                  | Unit           |

| 9   | Delay from RESET Assertion to Address High Impedance (periodically sampled and not 100% tested).                                                              | _                                                                      | 26                   | ns             |

| 10  | Minimum Stabilization Duration Internal Oscillator PLL Disabled (See Note 1) External clock PLL Disabled (See Note 2) External clock PLL Enabled (See Note 2) | 75000 × T <sub>C</sub><br>25 × T <sub>C</sub><br>2500 × T <sub>C</sub> | <u>-</u>             | ns<br>ns<br>ns |

| 11  | Delay from Asynchronous RESET Deassertion to First External Address Output (Internal Reset Deassertion)                                                       | 8×T <sub>C</sub>                                                       | 9×T <sub>C</sub> +20 | ns             |

Table continued on next page

Table 12 Reset, Stop, Mode Select, and Interrupt Timing (continued)

|     | Characteristics                                                                                                                                                                         | 40/66                                                                | Unit                                                                                 |          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------|

| Num | Characteristics                                                                                                                                                                         | Min                                                                  | Max                                                                                  | Unit     |

| 12  | Synchronous Reset Setup Time from RESET Deassertion to CKOUT transition #1                                                                                                              | 8.5                                                                  | T <sub>C</sub>                                                                       | ns       |

| 13  | Synchronous Reset Delay Time from the CKOUT transition #1 to the First External Address Output                                                                                          | 8×T <sub>C</sub>                                                     | 8×T <sub>C</sub> +6                                                                  | ns       |

| 14  | Mode Select Setup Time                                                                                                                                                                  | 21                                                                   | _                                                                                    | ns       |

| 15  | Mode Select Hold Time                                                                                                                                                                   | 0                                                                    |                                                                                      | ns       |

| 16  | Minimum Edge-Triggered Interrupt Request Assertion Width                                                                                                                                | 13                                                                   | _                                                                                    | ns       |

| 16a | Minimum Edge-Triggered Interrupt Request Deassertion Width                                                                                                                              | 13                                                                   | _                                                                                    | ns       |

| 17  | Delay from IRQA, IRQB, NMI Assertion to External Memory Access Address Out Valid  Caused by First Interrupt Instruction Fetch Caused by First Interrupt Instruction Execution           | 5×T <sub>C</sub> +T <sub>H</sub><br>9×T <sub>C</sub> +T <sub>H</sub> |                                                                                      | ns<br>ns |

| 18  | Delay from IRQA, IRQB, NMI Assertion to General Purpose Transfer Output Valid caused by First Interrupt Instruction Execution                                                           | 11 × T <sub>C</sub> + T <sub>H</sub>                                 | _                                                                                    | ns       |

| 19  | Delay from Address Output Valid caused by First Interrupt Instruction Execute to Interrupt Request Deassertion for Level Sensitive Fast Interrupts (See Note 3)                         |                                                                      | 2 T <sub>C</sub> + T <sub>L</sub> +<br>(T <sub>C</sub> × WS) - 23                    | ns       |

| 20  | Delay from RD Assertion to Interrupt Request Deassertion for Level Sensitive Fast Interrupts (See Note 3)                                                                               | <del>_</del>                                                         | 2T <sub>C</sub> + (T <sub>C</sub> × WS) - 21                                         | ns       |

| 21  | Delay from WR Assertion to Interrupt Request Deassertion for Level Sensitive Fast Interrupts  • WS = 0  • WS > 0  (See Note 3)                                                          | <u>-</u>                                                             | 2×T <sub>C</sub> -21<br>T <sub>C</sub> +T <sub>L</sub> +<br>(T <sub>C</sub> ×WS) -21 | ns<br>ns |

| 22  | Delay from General-Purpose Output Valid to Interrupt Request Deassertion for Level Sensitive Fast Interrupts - If Second Interrupt Instruction is: Single Cycle Two Cycles (See Note 3) |                                                                      | T <sub>L</sub> - 31<br>(2 × T <sub>C</sub> ) + T <sub>L</sub> - 31                   | ns<br>ns |

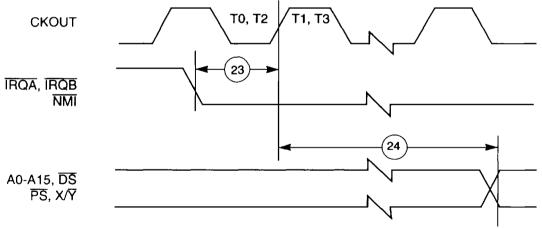

| 23  | Synchronous Interrupt Setup Time from IRQA, IRQB, NMI<br>Assertion to the CKOUT transition #2                                                                                           | 10                                                                   | T <sub>C</sub>                                                                       | ns       |

| 24  | Synchronous Interrupt Delay Time from the CKOUT transition #2 to the First External Address Output Valid caused by the First Instruction Fetch after coming out of Wait State           | 13 × T <sub>C</sub> + T <sub>H</sub>                                 | 13 × T <sub>C</sub> + T <sub>H</sub> + 6                                             | ns       |

Table 12 Reset, Stop, Mode Select, and Interrupt Timing (continued)

| Num | Characteristics                                                                                                                                                                                                                                            | 40/66                                                                                | l l m i d   |                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------|----------------|

|     | Characteristics                                                                                                                                                                                                                                            | Min                                                                                  | Max         | Unit           |

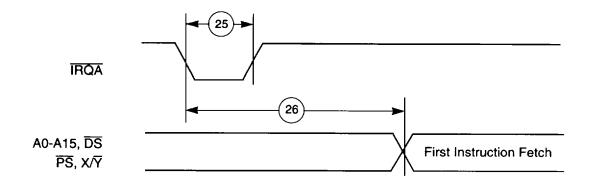

| 25  | Duration for IRQA Assertion to Recover from Stop State                                                                                                                                                                                                     | 12                                                                                   | _           | ns             |

| 26  | Delay from IRQA Assertion to Fetch of First Interrupt Instruction (when exiting 'Stop')  • Internal Crystal Oscillator Clock, OMR bit 6 = 0  • Stable External Clock, OMR bit 6 = 1  • Stable External Clock, PCTL bit 17 = 1  (See Note 1)                | 65548 × T <sub>C</sub><br>20 × T <sub>C</sub><br>13 × T <sub>C</sub>                 |             | ns<br>ns<br>ns |

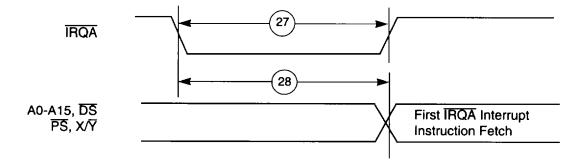

| 27  | Duration of Level Sensitive IRQA Assertion to ensure interrupt service (when exiting 'Stop')  • Internal Crystal Oscillator Clock, OMR bit 6 = 0  • Stable External Clock, OMR bit 6 = 1  • Stable External Clock, PCTL bit 17 = 1  (See Note 1)           | 65534 × T <sub>C</sub> + T <sub>L</sub><br>6 × T <sub>C</sub> + T <sub>L</sub><br>12 | <del></del> | ns<br>ns<br>ns |

| 28  | Delay from Level Sensitive IRQA Assertion to Fetch of First Interrupt Instruction (when exiting 'Stop')  • Internal Crystal Oscillator Clock, OMR bit 6 = 0  • Stable External Clock, OMR bit 6 = 1  • Stable External Clock, PCTL bit 17= 1  (See Note 1) | 65548 × T <sub>C</sub><br>20 × T <sub>C</sub><br>13 × T <sub>C</sub>                 | <u>-</u>    | ns<br>ns<br>ns |

#### NOTES:

- 1. A clock stabilization delay is required when using the on-chip crystal oscillator in two cases:

- · after power-on reset, and

- · when recovering from Stop mode.

During this stabilization period,  $T_C$ ,  $T_H$ , and  $T_L$  will not be constant. Since this stabilization period varies, a delay of 75,000  $\times$   $T_C$  is typically allowed to assure that the oscillator is stable before executing programs.

- 2. Circuit stabilization delay is required during reset when using an external clock in two cases:

- after power-on reset, and

- when recovering from Stop mode.

- 3. When using fast interrupts and IRQA and IRQB are defined as level-sensitive, then timings 19 through 22 apply to prevent multiple interrupt service. To avoid these timing restrictions, the deassertive edge-triggered mode is recommended when using fast interrupt. Long interrupts are recommended when using level-sensitive mode.

Figure 5 Reset Timing

Figure 6 Synchronous Reset Timing

Figure 7 Operating Mode Select Timing

Figure 8 External Level-Sensitive Fast Interrupt Timing

Figure 9 External Interrupt Timing (Negative Edge-Triggered)

Figure 10 Synchronous Interrupt from Wait State Timing

Figure 11 Recovery from Stop State Using IRQA

Figure 12 Recovery from Stop State Using IRQA Interrupt Service

Host I/O

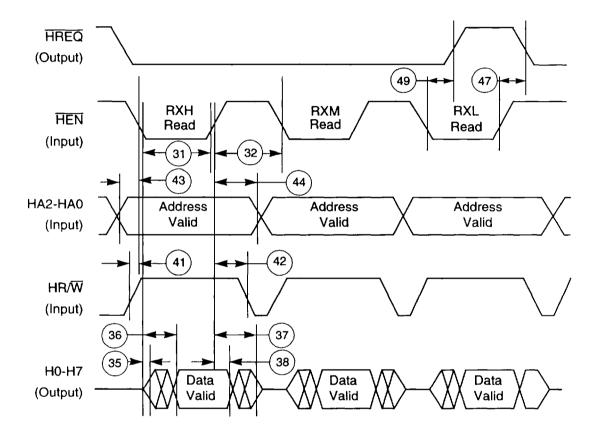

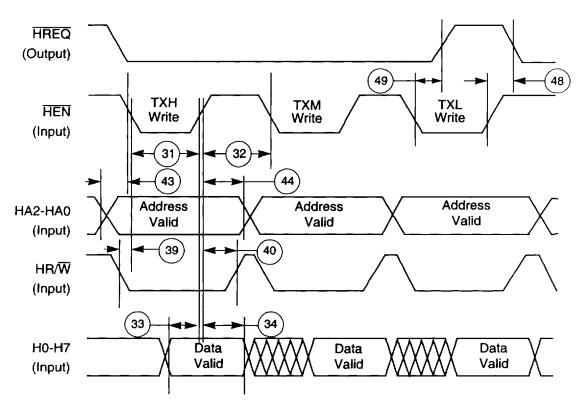

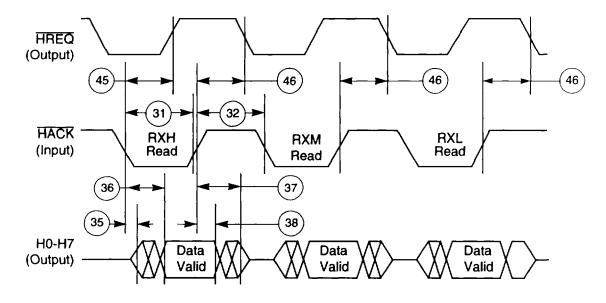

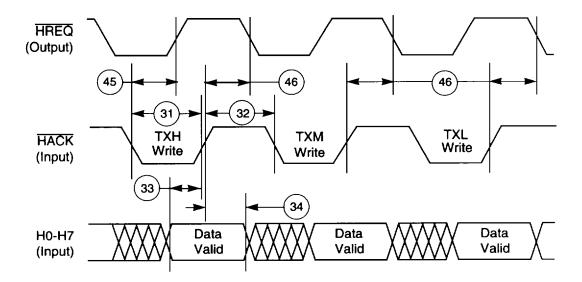

## **Host I/O Timing**

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_{J} = -40^{\circ} \text{ to } +105^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_J = 0^{\circ}$  to +80° C,  $C_L = 50 \text{ pF} + 2 \text{ TTL Loads}$

Active low lines should be "pulled up" in a manner consistent with the AC and DC specifications.

Table 13 Host I/O Timing

| N1  | Charactariation                                                                                                                     | 40/66 I                                            | 11          |                |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------|----------------|

| Num | Characteristics                                                                                                                     | Min                                                | Max         | <b>⊣</b> Unit  |

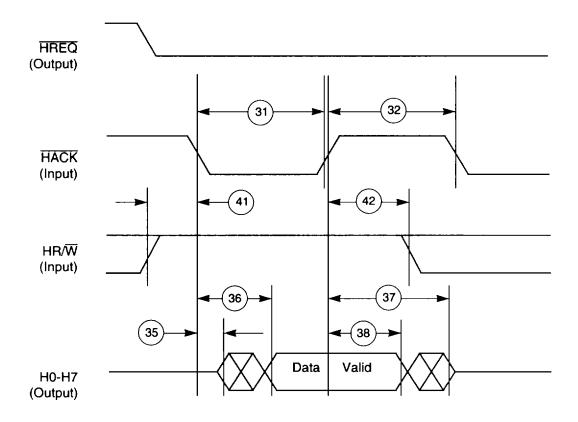

| 31  | HEN/HACK Assertion Width (See Note 1)  CVR, ICR, ISR, RXL Read  IVR, RXH/M Read  Write                                              | T <sub>C</sub> + 31<br>26<br>13                    | _<br>_<br>_ | ns             |

| 32  | HEN/HACK Deassertion Width (See Note 1)  • Between Two TXL Writes (See Note 2)  • Between Two CVR, ICR, ISR, RXL Reads (See Note 3) | 13<br>2×T <sub>C</sub> +31<br>2×T <sub>C</sub> +31 | <br><br>    | ns<br>ns<br>ns |

| 33  | Host Data Input Setup Time Before HEN/HACK Deassertion                                                                              | 4                                                  |             | ns             |

| 34  | Host Data Input Hold Time After HEN/HACK Deassertion                                                                                | 3                                                  | _           | ns             |

| 35  | HEN/HACK Assertion to Output Data Active from High Impedance                                                                        | 0                                                  |             | ns             |

| 36  | HEN/HACK Assertion to Output Data Valid                                                                                             |                                                    | 26          | ns             |

| 37  | HEN/HACK Deassertion to Output Data High Impedance (See Note 5)                                                                     | _                                                  | 18          | ns             |

| 38  | Output Data Hold Time After HEN/HACK Deassertion (See Note 6)                                                                       | 2.5                                                |             | ns             |

| 39  | HR/W Low Setup Time Before HEN Assertion                                                                                            | 0                                                  |             | ns             |

| 40  | HR/W Low Hold Time After HEN Deassertion                                                                                            | 3                                                  | -           | ns             |

| 41  | HR/W High Setup Time to HEN Assertion                                                                                               | 0                                                  |             | ns             |

| 42  | HR/W High Hold Time After HEN/HACK Deassertion                                                                                      | 3                                                  |             | ns             |

| 43  | HA0-HA2 Setup Time Before HEN Assertion                                                                                             | 0                                                  |             | ns             |

| 44  | HA0-HA2 Hold Time After HEN Deassertion                                                                                             | 3                                                  | <del></del> | ns             |

| 45  | DMA HACK Assertion to HREQ Deassertion (See Note 4)                                                                                 | 3                                                  | 45          | ns             |

Table 13 Host I/O Timing (continued)

| Mirana | Obawastawistia                                                                        | 40/66                                          |     |      |

|--------|---------------------------------------------------------------------------------------|------------------------------------------------|-----|------|

| Num    | Characteristics                                                                       | Min                                            | Max | Unit |

| 46     | DMA HACK Deassertion to HREQ Assertion (See Notes 4, 5)                               |                                                |     |      |

|        | for DMA RXL Read                                                                      | $T_L + T_C + T_H$ $T_L + T_C$                  | _   | ns   |

|        | for DMA TXL Write                                                                     | T <sub>L</sub> +T <sub>C</sub>                 |     | ns   |

|        | all other cases                                                                       | 0                                              | _   | ns   |

| 47     | Delay from HEN Deassertion to HREQ<br>Assertion for RXL Read (See Notes 4, 5)         | T <sub>L</sub> +T <sub>C</sub> +T <sub>H</sub> | _   | ns   |

| 48     | Delay from HEN Deassertion to HREQ Assertion for TXL Write (See Notes 4, 5)           | T <sub>L</sub> + T <sub>C</sub>                | _   | ns   |

| 49     | Delay from HEN Assertion to HREQ Deassertion for RXL Read, TXL Write (See Notes 4, 5) | 3                                              | 58  | ns   |

- 1. See Host Port Considerations in the section on Design Considerations.

- 2. This timing must be adhered to only if two consecutive writes to the TXL are executed without polling TXDE or HREQ.

- 3. This timing must be adhered to only if two consecutive reads from one of these registers are executed without polling the corresponding status bits or HREQ

- 4. HREQ is pulled up by a 1 k $\Omega$  resistor.

- 5. Specifications are periodically sampled and not 100% tested.

- 6. May decrease to 0 ns for future versions.

Figure 13 Host Interrupt Vector Register (IVR) Read

Figure 14 Host Read Cycle (Non-DMA Mode)

Host I/O

Figure 15 Host Write Cycle (Non-DMA Mode)

Figure 16 Host DMA Read Cycle

Figure 17 Host DMA Write Cycle

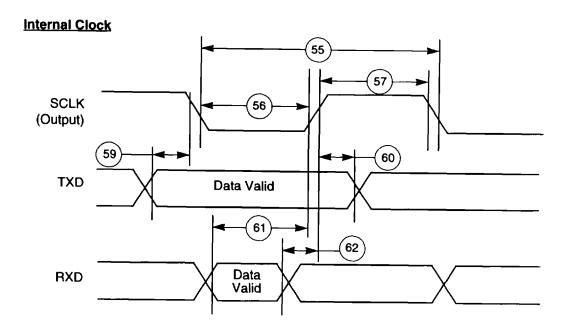

## Serial Communication Interface (SCI) Timing

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_{J} = -40^{\circ} \text{ to} + 105^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_{J} = 0^{\circ} \text{ to } +80^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

tSCC = Synchronous Clock Cycle Time (for internal clock, tSCC is determined by the SCI clock control register and  $T_C$ ). The minimum tSCC value is  $8 \times T_C$ .

Table 14 SCI Synchronous Mode Timing

| Marina | Characteristics                                                    | 40/66                        | 6 MHz                         | 11-16 |

|--------|--------------------------------------------------------------------|------------------------------|-------------------------------|-------|

| Num    | Characteristics                                                    | Min                          | Max                           | Unit  |

| 55     | Synchronous Clock Cycle — tSCC                                     | 8×T <sub>C</sub>             |                               | ns    |

| 56     | Clock Low Period                                                   | tSCC/2 - 10.5                | _                             | ns    |

| 57     | Clock High Period                                                  | tSCC/2 - 10.5                | -                             | ns    |

| 58     | < intentionally blank >                                            | _                            | _                             |       |

| 59     | Output Data Setup to Clock Falling<br>Edge (Internal Clock)        | tSCC/4 + T <sub>L</sub> - 26 | _                             | ns    |

| 60     | Output Data Hold After Clock Rising Edge (Internal Clock)          | tSCC/4 -T <sub>L</sub> - 8   | _                             | ns    |

| 61     | Input Data Setup Time Before Clock<br>Rising Edge (Internal Clock) | tSCC/4 + T <sub>L</sub> + 23 | _                             | ns    |

| 62     | Input Data Not Valid Before Clock<br>Rising Edge (Internal Clock)  | _                            | tSCC/4 + T <sub>L</sub> - 5.5 | ns    |

| 63     | Clock Falling Edge to Output Data<br>Valid (External Clock)        | <del>-</del>                 | 32.5                          | ns    |

| 64     | Output Data Hold After Clock Rising Edge (External Clock)          | T <sub>C</sub> + 3           | _                             | ns    |

| 65     | Input Data Setup Time Before Clock<br>Rising Edge (External Clock) | 16                           | <del>-</del>                  | ns    |

| 66     | Input Data Hold Time After Clock<br>Rising Edge (External Clock)   | 21                           | _                             | ns    |

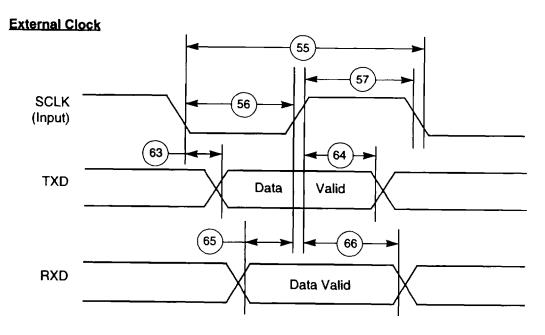

Table 15 SCI Asynchronous Mode Timing — 1X Clock

|     | Oh a sa sharla Na                                         | 40/66               |          |      |

|-----|-----------------------------------------------------------|---------------------|----------|------|

| Num | Characteristics                                           | Min                 | Max      | Unit |

| 67  | Asynchronous Clock Cycle - tACC                           | 64 × T <sub>C</sub> |          | ns   |

| 68  | Clock Low Period                                          | tACC/2 -11          | _        | ns   |

| 69  | Clock High Period                                         | tACC/2 -11          |          | ns   |

| 70  | < intentionally blank >                                   | _                   |          | _    |

| 71  | Output Data Setup to Clock Rising Edge (Internal Clock)   | tACC/2 -51          | _        | ns   |

| 72  | Output Data Hold After Clock Rising Edge (Internal Clock) | tACC/2 -51          | <u>-</u> | ns   |

Figure 18 SCI Synchronous Mode Timing

$\mbox{NOTE}\colon$  In the wire-OR mode, TXD can be pulled up by 1  $\mbox{K}\Omega$

Figure 19 SCI Asynchronous Mode Timing

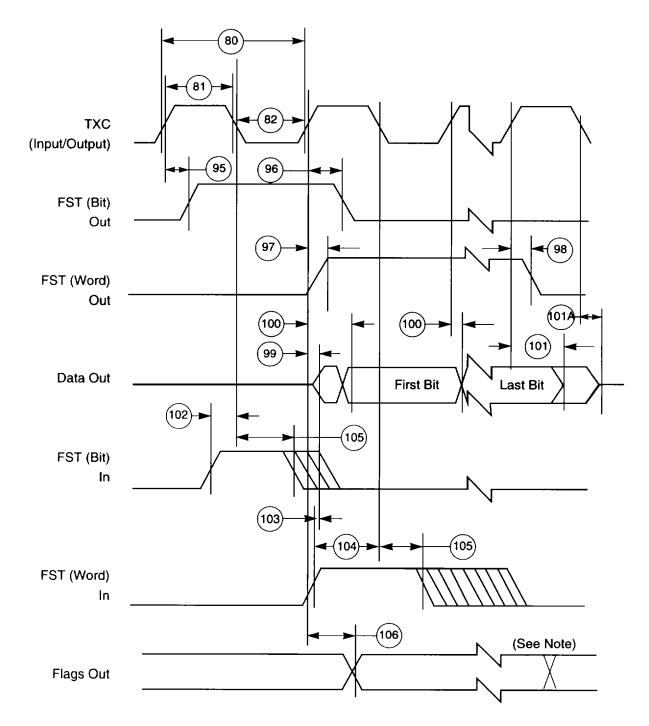

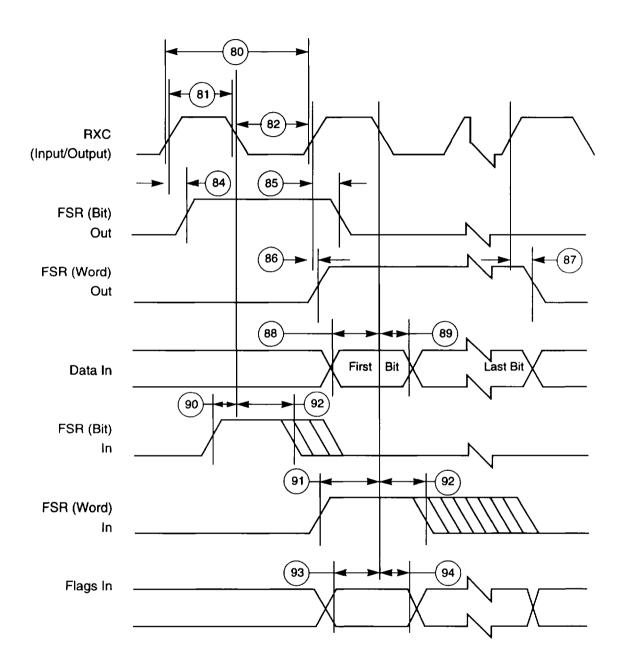

## Synchronous Serial Interface (SSI) Timing

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_{I} = -40^{\circ} \text{ to} + 105^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_{J} = 0^{\circ} \text{ to } +80^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

tSSICC = SSI clock cycle time

TXC (SCK Pin) = Transmit Clock

RXC (SC0 or SCK Pin) = Receive Clock

FST (SC2 Pin) = Transmit Frame Sync

FSR (SC1 or SC2 Pin) = Receive Frame Sync

i ck = Internal Clock

x ck = External Clock

g ck = Gated Clock

i ck a = Internal Clock, Asynchronous Mode (Asynchronous implies that

STD and SRD are two different clocks)

i ck s = Internal Clock, Synchronous Mode (Synchronous implies that

STD and SRD are the same clock)

bl = bit length

wl = word length

Table 16 SSI Timing

| Num | Characteristics                      | 40/66 M                                            |              |                |      |

|-----|--------------------------------------|----------------------------------------------------|--------------|----------------|------|

| Num | Characteristics                      | Min                                                | Max          | Case           | Unit |

| 80  | Clock Cycle-tSSICC (See Note 1)      | 4×T <sub>C</sub><br>3×T <sub>C</sub>               | <del></del>  | i ck<br>x ck   | ns   |

| 81  | Clock High Period                    | tSSICC/2 - 10.8<br>T <sub>C</sub> + T <sub>L</sub> | _            | i ck<br>x ck   | ns   |

| 82  | Clock Low Period                     | tSSICC/2 - 10.8<br>T <sub>C</sub> + T <sub>L</sub> | _            | i ck<br>x ck   | ns   |

| 83  | < intentionally blank >              |                                                    | _            | _              | _    |

| 84  | RXC Rising Edge to FSR Out (bl) High |                                                    | 40.8<br>25.8 | x ck<br>i ck a | ns   |

| 85  | RXC Rising Edge to FSR Out (bl) Low  |                                                    | 35.8<br>25.8 | x ck<br>i ck a | ns   |

| 86  | RXC Rising Edge to FSR Out (wl) High |                                                    | 35.8<br>20.8 | x ck<br>i ck a | ns   |

Table 16 SSI Timing (continued)

|     |                                                                         | 40/6              | 6 MHz                         | 0                        | 1 Imia |

|-----|-------------------------------------------------------------------------|-------------------|-------------------------------|--------------------------|--------|

| Num | Characteristics                                                         | Min               | Max                           | Case                     | Unit   |

| 87  | RXC Rising Edge to FSR Out (wl) Low                                     |                   | 35.8<br>20.8                  | x ck<br>i ck a           | ns     |

| 88  | Data In Setup Time Before RXC<br>(SCK in Synchronous Mode) Falling Edge | 3.3<br>15.8<br>13 | _<br>_<br>_                   | x ck<br>i ck a<br>i ck s | ns     |

| 89  | Data In Hold Time After RXC<br>Falling Edge                             | 18<br>3.3         | _                             | x ck<br>i ck             | ns     |

| 90  | FSR Input (bl) High Before RXC<br>Falling Edge                          | 0.8<br>17.4       | _                             | x ck<br>i ck a           | ns     |

| 91  | FSR Input (wl) High Before RXC<br>Falling Edge                          | 3.3<br>18.3       | _<br>_                        | x ck<br>i ck a           | ns     |

| 92  | FSR Input Hold Time After RXC<br>Falling Edge                           | 18.3<br>3.3       | _<br>_                        | x ck<br>i ck             | ns     |

| 93  | Flags Input Setup Before RXC<br>Falling Edge                            | 0.8<br>16.7       | _                             | x ck<br>i ck s           | ns     |

| 94  | Flags Input Hold Time After RXC<br>Falling Edge                         | 18.3<br>3.3       | _                             | x ck<br>i ck s           | ns     |

| 95  | TXC Rising Edge to FST Out (bl) High                                    | _                 | 31.6<br>15.8                  | x ck<br>i ck             | ns     |

| 96  | TXC Rising Edge to FST Out (bl) Low                                     |                   | 33.3<br>18.3                  | x ck<br>i ck             | ns     |

| 97  | TXC Rising Edge to FST Out (wl) High                                    |                   | 30.8<br>18.3                  | x ck<br>i ck             | ns     |

| 98  | TXC Rising Edge to FST Out (wl) Low                                     |                   | 33.3<br>18.3                  | x ck<br>i ck             | ns     |

| 99  | TXC Rising Edge to Data Out Enable from High Impedance                  | _                 | 33.3 + T <sub>H</sub><br>20.8 | x ck<br>i ck             | ns     |

| 100 | TXC Rising Edge to Data Out Valid                                       | _                 | 33.3 + T <sub>H</sub><br>22.4 | x ck<br>i ck             | ns     |

Table 16 SSI Timing (continued)

| Maria | Oh a saada al-Al                                            | 40/6        |                                |              |      |

|-------|-------------------------------------------------------------|-------------|--------------------------------|--------------|------|

| Num   | Characteristics                                             | Min         | Max                            | - Case       | Unit |

| 101   | TXC Rising Edge to Data Out High Impedance (See Note 2)     |             | 35.8<br>20.8                   | x ck<br>i ck | ns   |

| 101A  | TXC Falling Edge to Data Out High<br>Impedance (See Note 2) | _           | T <sub>C</sub> +T <sub>H</sub> | g ck         | ns   |

| 102   | FST Input (bl) Setup Time Before TXC<br>Falling Edge        | 0.8<br>18.3 | _                              | x ck<br>i ck | ns   |

| 103   | FST Input (wl) to Data Out Enable from High Impedance       |             | 30.8                           |              | ns   |

| 104   | FST Input (wl) Setup Time Before TXC Falling Edge           | 0.8<br>20.0 |                                | x ck<br>i ck | ns   |

| 105   | FST Input Hold Time After TXC<br>Falling Edge               | 18.3<br>3.3 | _                              | x ck<br>i ck | ns   |

| 106   | Flag Output Valid After TXC Rising Edge                     | _           | 32.5<br>20.8                   | x ck<br>i ck | ns   |

- 1. For internal clock, External Clock Cycle is defined by  $I_{\rm cyc}$  and SSI control register. 2. Periodically sampled, and not 100% tested

NOTE: In the Network mode, output flag transitions can occur at the start of each time slot within the frame. In the Normal mode, the output flag state is asserted for the entire frame period.

Figure 20 SSI Transmitter Timing

Figure 21 SSI Receiver Timing

External Bus Asynchronous

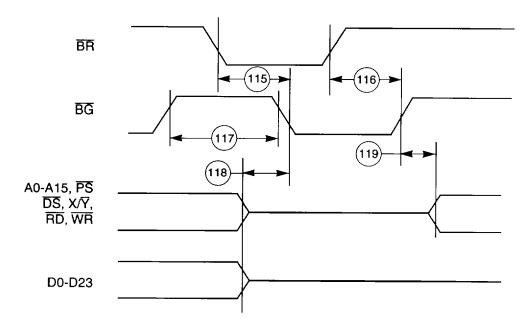

## **External Bus Asynchronous Timing**

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_J = -40^\circ \text{ to} + 105^\circ \text{ C}$ ,  $C_L = 50 \text{ pF} + 2 \text{ TTL Loads}$ DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_J = 0^\circ \text{ to} + 80^\circ \text{ C}$ ,  $C_L = 50 \text{ pF} + 2 \text{ TTL Loads}$

WS = Number of Wait States, as determined by BCR register (WS = 0 to 15)

#### **Capacitance Derating**

The DSP56002/L002 External Bus Timing Specifications are designed and tested at the maximum capacitive load of 50 pF, including stray capacitance. Typically, the drive capability of the External Bus pins (A0-A15, D0-D23,  $\overline{PS}$ ,  $\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ,  $X/\overline{Y}$ ,  $\overline{EXTP}$ ) derates linearly at 1 ns per 12 pF of additional capacitance from 50 pF to 250 pF of loading. Port B and C pins (HI, SCI, SSI, and Timer) derate linearly at 1 ns per 5 pF of additional capacitance from 50 pF to 250 pF of loading. Active low lines should be "pulled up" in a manner consistent with the AC and DC specifications.

Table 17 External Bus Asynchronous Timing

| N1  | Obarratariation                                                                | 40 MHz 66 MHz                                                     |                                                                     | 66 MHz                                                               | 11                                                                  |          |

|-----|--------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------|----------|

| Num | Characteristics                                                                | Min                                                               | Max                                                                 | Min                                                                  | Max                                                                 | Unit     |

| 115 | Delay from BR Assertion to BG Assertion                                        |                                                                   |                                                                     |                                                                      |                                                                     |          |

|     | With no external access from the DSP                                           | 2T <sub>C</sub> + T <sub>H</sub>                                  | 4T <sub>C</sub> + T <sub>H</sub> + 14                               | 2T <sub>C</sub> + T <sub>H</sub>                                     | 4T <sub>C</sub> + T <sub>H</sub> + 14                               | ns       |

|     | During external read or write access                                           | T <sub>C</sub> + T <sub>H</sub>                                   | 4T <sub>C</sub> + T <sub>H</sub> + (T <sub>C</sub> × WS) + 14       | T <sub>C</sub> + T <sub>H</sub>                                      | 4T <sub>C</sub> + T <sub>H</sub> + (T <sub>C</sub> × )<br>WS) + 14  | ns       |

|     | During external read-<br>modify-write access     During Stop mode -            | T <sub>C</sub> + T <sub>H</sub>                                   | 6T <sub>C</sub> + T <sub>H</sub> + (2 × T <sub>C</sub><br>× WS) +14 | T <sub>C</sub> + T <sub>H</sub>                                      | 6T <sub>C</sub> + T <sub>H</sub> + (2 × T <sub>C</sub><br>× WS) +14 | ns       |

|     | external bus will not be released and BG will not go low                       | 00                                                                | 14                                                                  | 00                                                                   | 14                                                                  | ns       |

|     | During Wait mode                                                               | T <sub>H</sub>                                                    | T <sub>C</sub> + T <sub>H</sub> + 15                                | T <sub>H</sub>                                                       | T <sub>C</sub> + T <sub>H</sub> + 15                                | ns       |

| 116 | Delay from BR Deasser-<br>tion to BG Deassertion                               | 2×T <sub>C</sub>                                                  | 4×T <sub>C</sub> + 12.5                                             | 2×T <sub>C</sub>                                                     | 4 × T <sub>C</sub> + 12.5                                           | ns       |

| 117 | BG Deassertion Duration  • During Wait mode  • All other cases                 | T <sub>C</sub> - 5.5<br>2 × T <sub>C</sub> + T <sub>H</sub> - 5.5 | _<br>_                                                              | T <sub>C</sub> - 5.5<br>2 × T <sub>C</sub> + T <sub>H</sub> -<br>5.5 |                                                                     | ns<br>ns |

| 118 | Delay from Address, Data,<br>and Control Bus High<br>Impedance to BG Assertion | 0                                                                 | _                                                                   | 0                                                                    |                                                                     | ns       |

| 119 | Delay from BG Deassertion to Address and Control Bus Enabled                   | 0                                                                 | T <sub>H</sub>                                                      | 0                                                                    | Тн                                                                  | ns       |

46

External Bus Asynchronous

Table 17 External Bus Asynchronous Timing (continued)

|     | Oh ava shartatta                                                                                                | 40 MH                                                                                       |                                                         | 6                                                                                           | 66 MHz                                                                                    |          |

|-----|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------|

| Num | Characteristics                                                                                                 | Min                                                                                         | Max                                                     | Min                                                                                         | Max                                                                                       | Unit     |

| 120 | Address Valid to WR Assertion  • WS = 0  • WS > 0                                                               | T <sub>L</sub> - 6<br>T <sub>C</sub> - 6                                                    |                                                         | T <sub>L</sub> - 4.5<br>T <sub>C</sub> - 4.5                                                |                                                                                           | ns<br>ns |

| 121 | WR Assertion Width  • WS = 0  • WS > 0                                                                          | T <sub>C</sub> - 4<br>WS × T <sub>C</sub> + T <sub>L</sub>                                  | -                                                       | T <sub>C</sub> - 4<br>WS × T <sub>C</sub> + T <sub>L</sub>                                  |                                                                                           | ns<br>ns |

| 122 | WR Deassertion to<br>Address Not Valid                                                                          | T <sub>H</sub> - 6                                                                          | -                                                       | T <sub>H</sub> - 4                                                                          | _                                                                                         | ns       |

| 123 | WR Assertion to Data Out Active From High Impedance • WS = 0 • WS > 0                                           | T <sub>H</sub> - 4<br>0                                                                     |                                                         | T <sub>H</sub> - 4<br>0                                                                     |                                                                                           | ns<br>ns |

| 124 | Data Out Hold Time from WR Deassertion (the maximum specification is periodically sampled, and not 100% tested) | T <sub>H</sub> - 7                                                                          | T <sub>H</sub> - 2.5                                    | T <sub>H</sub> - 5                                                                          | T <sub>H</sub> - 1.5                                                                      | ns       |

| 125 | Data Out Setup Time to  WR Deassertion  • WS = 0  • WS > 0                                                      | T <sub>L</sub> - 0.8<br>WS × T <sub>C</sub> + T <sub>L</sub> - 0.8                          | <del>-</del>                                            | T <sub>L</sub> - 0.4<br>WS×T <sub>C</sub> +<br>T <sub>L</sub> - 0.4                         | <u> </u>                                                                                  | ns       |

| 126 | RD Deassertion to<br>Address Not Valid                                                                          | T <sub>H</sub>                                                                              | _                                                       | T <sub>H</sub> - 1                                                                          | _                                                                                         | ns       |

| 127 | Address Valid to RD Deassertion • WS = 0 • WS > 0                                                               | T <sub>C</sub> + T <sub>L</sub> - 6<br>((WS + 1) × T <sub>C</sub> ) +<br>T <sub>L</sub> - 6 | <del>-</del>                                            | T <sub>C</sub> + T <sub>L</sub> - 6<br>((WS + 1) ×<br>T <sub>C</sub> ) + T <sub>L</sub> - 6 |                                                                                           | ns<br>ns |

| 128 | Input Data Hold Time to RD Deassertion                                                                          | 0                                                                                           |                                                         | 0                                                                                           |                                                                                           | ns       |

| 129 | RD Assertion Width  • WS = 0  • WS > 0                                                                          | T <sub>C</sub> - 4<br>((WS + 1) × T <sub>C</sub> ) - 4                                      | =                                                       | T <sub>C</sub> - 4<br>((WS + 1) ×<br>T <sub>C</sub> ) - 4                                   |                                                                                           | ns<br>ns |

| 130 | Address Valid to Input Data Valid  • WS = 0  • WS > 0                                                           | _<br>_                                                                                      | $T_C + T_L - 9.5$<br>((WS+1) × $T_C$ ) +<br>$T_L - 9.5$ | _<br>_                                                                                      | T <sub>C</sub> + T <sub>L</sub> - 7<br>((WS+1) × T <sub>C</sub> ) +<br>T <sub>L</sub> - 7 | ns<br>ns |

External Bus Asynchronous

Table 17 External Bus Asynchronous Timing (continued)

| <b>N</b> 1 | Ohavastavlatias                                      | 40                                                        | MHz                                                      | 66 MHz                                                        |                                                          | 11       |

|------------|------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|----------|

| Num        | Characteristics                                      | Min                                                       | Max                                                      | Min                                                           | Max                                                      | Unit     |

| 131        | Address Valid to<br>RD Assertion                     | T <sub>L</sub> - 6                                        |                                                          | T <sub>L</sub> - 4.5                                          | _                                                        | ns       |

| 132        | RD Assertion to Input Data Valid  • WS = 0  • WS > 0 | <del>-</del>                                              | T <sub>C</sub> - 7.5<br>((WS+1) × T <sub>C</sub> ) - 7.5 |                                                               | T <sub>C</sub> - 5.5<br>((WS+1) × T <sub>C</sub> ) - 5.5 | ns<br>ns |

| 133        | WR Deassertion to RD Assertion                       | T <sub>C</sub> - 7                                        | _                                                        | T <sub>C</sub> - 5                                            | _                                                        | ns       |

| 134        | RD Deassertion to RD Assertion                       | T <sub>C</sub> - 4                                        | _                                                        | T <sub>C</sub> - 2.5                                          | _                                                        | ns       |

| 135        | WR Deassertion to WR Assertion  • WS = 0  • WS > 0   | T <sub>C</sub> - 4<br>T <sub>C</sub> + T <sub>H</sub> - 4 | _                                                        | T <sub>C</sub> -3<br>T <sub>C</sub> +T <sub>H</sub> -3        |                                                          | ns<br>ns |

| 136        | RD Deassertion to WR Assertion • WS = 0 • WS > 0     | T <sub>C</sub> - 4<br>T <sub>C</sub> + T <sub>H</sub> - 4 |                                                          | T <sub>C</sub> - 2.5<br>T <sub>C</sub> + T <sub>H</sub> - 2.5 |                                                          | ns<br>ns |

Figure 22 Bus Request / Bus Grant Timing

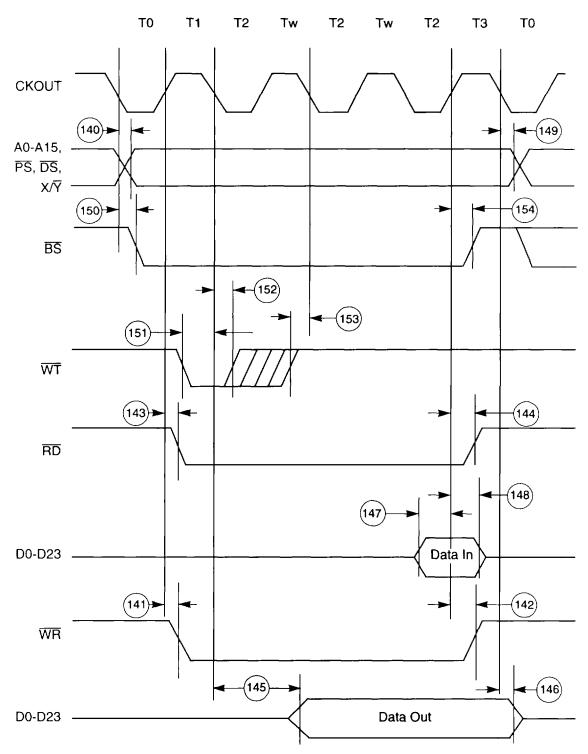

Figure 23 External Bus Asynchronous Timing

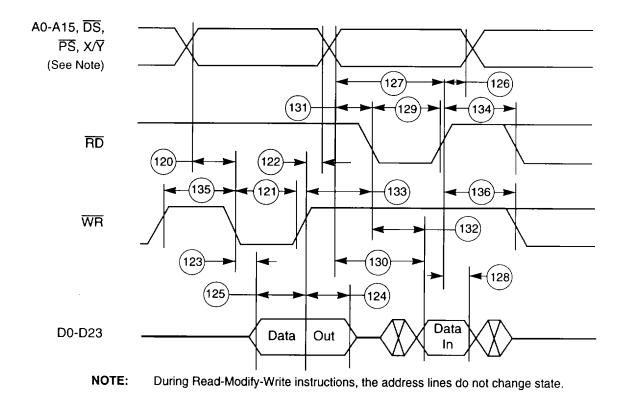

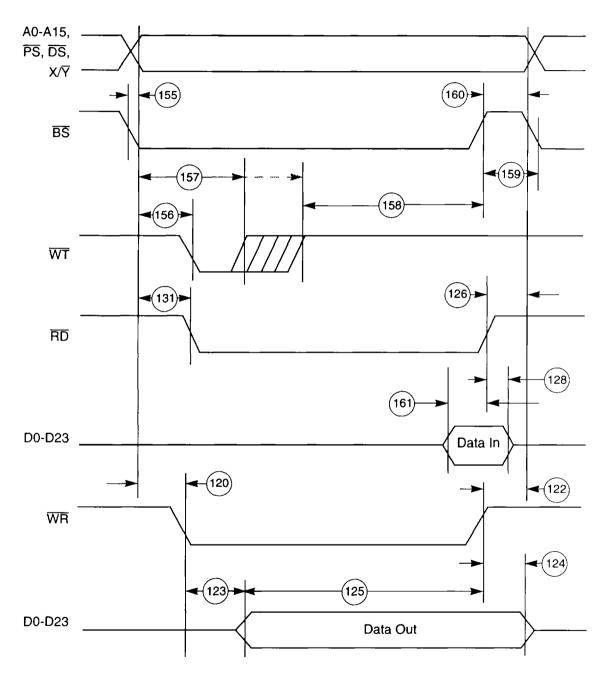

## **External Bus Synchronous Timing**

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_{J} = -40^{\circ} \text{ to } +105^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_{J} = 0^{\circ} \text{ to } +80^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

#### **Capacitance Derating**

The DSP56002/L002 external bus timing specifications are designed and tested at the maximum capacitive load of 50 pF, including stray capacitance. Typically, the drive capability of the external bus pins (A0-A15, D0-D23,  $\overline{PS}$ ,  $\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ,  $X/\overline{Y}$ ,  $\overline{EXTP}$ ) derates linearly at 1 ns per 12 pF of additional capacitance from 50 pF to 250 pF of loading. Port B and C pins (HI, SCI, SSI, and Timer) derate linearly at 1 ns per 5 pF of additional capacitance from 50 pF to 250 pF of loading. Active-low lines should be "pulled up" in a manner consistent with the AC and DC specifications.

40 MHz 66 MHz Unit Num Characteristics Min Max Min Max ns CKOUT transition #1 to Address Valid 6.2 140 CKOUT transition #2 to WR Assertion 141 WS=0 4.4 กร • WS>0  $T_{H} + 4.4$  $T_H + 4$ ns (See Note 1) CKOUT transition #2 to WR Deassertion 9.1 1 5 ns 142 1.3 CKOUT transition #2 to RD Assertion 3.9 3.9 143 ns CKOUT transition #2 to RD Deassertion 3.4 -3 3 144 0 ns 4.5 CKOUT transition #1 to Data-Out Valid 145 5.4 ns CKOUT transition #1 to Data-Out Invalid 0 0 ns 146 (See Note 3) Data-In Valid to CKOUT transition #2 3.4 3.4 147 (Setup) CKOUT transition #2 to Data-In Invalid 0 0 ns 148 0 0 149 CKOUT transition #1 to Address Invalid ns (See Note 3)

Table 18 External Bus Synchronous Timing

- 1. AC timing specifications which are referenced to a device input signal are measured in production with respect to the 50% point of the respective input signal's transition.

- 2. WS are wait state values specified in the BCR.

- 3. CKOUT transition #1 to data-out invalid (specification # T146) and CKOUT transition #1 to address invalid (specification # T149) indicate the time after which data/address are no longer guaranteed to be valid.

- 4. Timings are given from CKOUT midpoint to V<sub>OL</sub> or V<sub>OH</sub> of the corresponding pin(s).

- 5. CKOUT transition #1 is a falling edge of CKOUT for CKP=0.

NOTE: During Read-Modify-Write Instructions, the address lines do not change states.

Figure 24 Synchronous Bus Timing

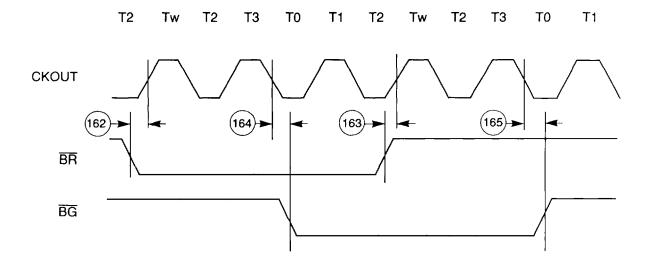

Bus Strobe / Wait

## **Bus Strobe / Wait Timing**

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_J = -40^{\circ} \text{ to} + 105^{\circ} \text{ C}$ ,  $C_L = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}$ ,  $T_{J} = 0^{\circ} \text{ to } +80^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

Table 19 Bus Strobe / Wait Timing

| N1  | Characteristics                                                                   | 40/6                    |                            |          |

|-----|-----------------------------------------------------------------------------------|-------------------------|----------------------------|----------|

| Num |                                                                                   | Min                     | Max                        | Unit     |

| 150 | CKOUT transition #1 to BS Assertion                                               | _                       | 5.6                        | ns       |

| 151 | WT Assertion to CKOUT transition #1(setup time)                                   | 5.3                     | _                          | ns       |

| 152 | CKOUT transition #1 to WT Deassertion for Minimum Timing                          | 0                       | T <sub>C</sub> - 7.9       | ns       |

| 153 | WT Deassertion to CKOUT transition #1 for Maximum Timing (2 wait states)          | 7.9                     | _                          | ns       |

| 154 | CKOUT transition #2 to BS Deassertion                                             | _                       | 5.2                        | ns       |

| 155 | BS Assertion to Address Valid                                                     | 0                       | 2.4                        | ns       |

| 156 | BS Assertion to WT Assertion (See Note 1)                                         | 0                       | T <sub>C</sub> - 10.9      | ns       |

| 157 | BS Assertion to WT Deassertion (See Note 1 and Note 3)                            | (WS-1) × T <sub>C</sub> | WS × T <sub>C</sub> - 13.5 | ns       |

| 158 | WT Deassertion to BS Deassertion                                                  | $T_{C} + T_{L} + 3.3$   | $2 \times T_C + T_L + 7.8$ | ns       |

| 159 | Minimum BS Deassertion Width for Consecutive External Accesses                    | T <sub>H</sub> - 1      |                            | ns       |

| 160 | BS Deassertion to Address Invalid (See Note 2)                                    | T <sub>H</sub> - 4.6    |                            | ns       |

| 161 | Data-In Valid to RD Deassertion (Set Up)                                          | 3.4                     |                            | ns       |

| 162 | BR Assertion to CKOUT transition #2 for Minimum Timing                            | 9.5                     | T <sub>C</sub>             | ns       |

| 163 | BR Deassertion to CKOUT transition #2 for Minimum Timing                          | 8                       | T <sub>C</sub>             | ns       |

| 164 | CKOUT transition #1 to BG Assertion                                               | _                       | 8.8                        | ns       |

| 165 | CKOUT transition #1 to BG Deassertion                                             | _                       | 5.3                        | ns       |

| 170 | EXTAL to CKOUT- PLL Disabled EXTAL to CKOUT - PLL Enabled and MF < 5 (See Note 5) | 3<br>0.3                | 9.7<br>3.7                 | ns<br>ns |

| 171 | CKOUT transition #2 to BN Assertion                                               | _                       | 5.7                        | ns       |

| 172 | CKOUT transition #2 to BN Deassertion                                             |                         | 5                          | ns       |

<sup>1.</sup> If wait states are also inserted using the BCR and if the number of wait states is greater than 2, then specification numbers 156 and 157 can be increased accordingly. (Notes continued on next page)

- 2. BS deassertion to address invalid indicates the time after which the address are no longer guaranteed to be valid.

- 3. The minimum number of wait states when using BS/WT is two (2).

- 4. For read-modify-write instructions, the address lines will not change states between the read and the write cycle. However, BS will deassert before asserting again for the write cycle. If wait states are desired for each of the read and write cycle, the WT pin must be asserted once for each cycle.

- 5. When EXTAL frequency is less than 33 MHz, then timing 170 is not guaranteed for a period of  $1000 \times T_C$  after PLOCK assertion following the events below:

- when enabling the PLL operation by software.

- when changing the multiplication factor.

- when recovering from the stop state if the PLL was turned off and it is supposed to turn on when exiting the stop state.

Figure 25 Synchronous Bus Request / Bus Grant Timing

Bus Strobe / Wait

NOTE: During Read-Modify-Write Instructions, the address lines do not change state. However, BS will deassert before asserting again for the write cycle.

Figure 26 Synchronous BS / WT Timings

NOTE: During Read-Modify-Write instructions, the address lines do not change state. However, BS will deassert before asserting again for the write cycle.

Figure 27 Asynchronous BS / WT Timings

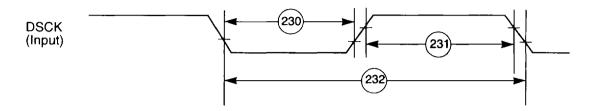

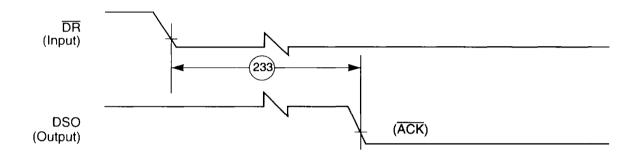

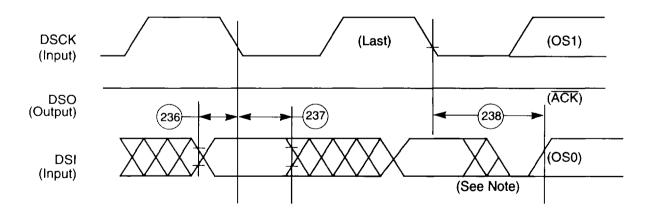

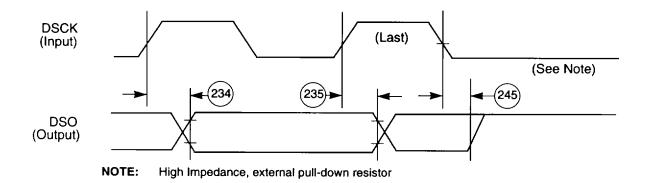

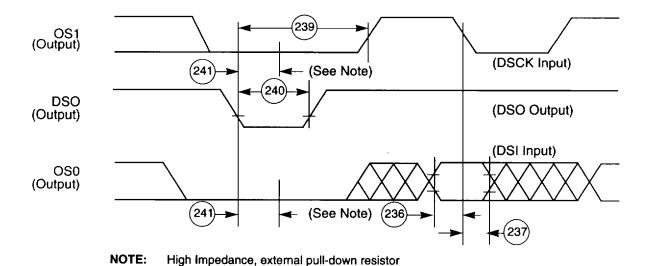

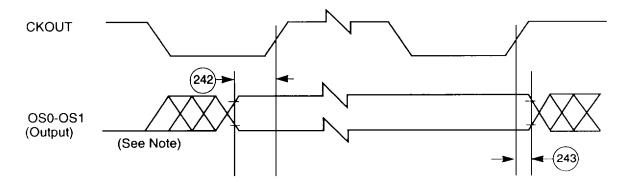

## OnCE™ Port Timing

DSP56002:  $V_{CC} = 5.0 \text{ Vdc} \pm 10\%$ ,  $T_{J} = -40^{\circ} \text{ to } +105^{\circ} \text{ C}$ ,  $C_{L} = 50 \text{ pF} + 2 \text{ TTL Loads}$

DSP56L002:  $V_{CC} = 3.3 \text{ Vdc} \pm 0.3 \text{ V}, T_J = 0^{\circ} \text{ to } +80^{\circ} \text{ C}, C_L = 50 \text{ pF} + 2 \text{ TTL Loads}$

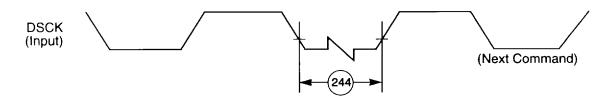

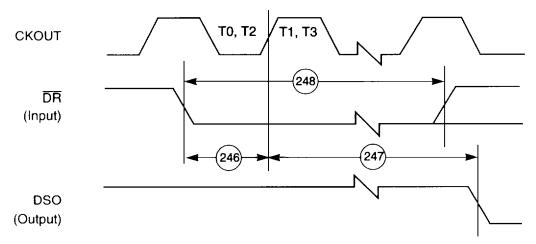

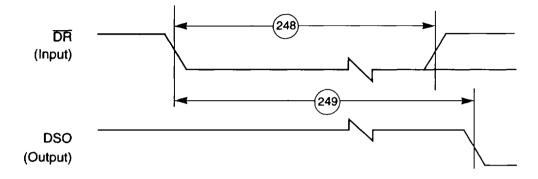

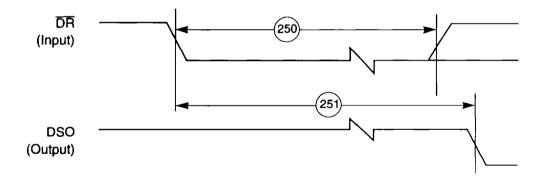

Table 20 OnCE<sup>TM</sup> Port Timing

|     | Ohausat-ulati                                                                                  | 40/66                                | 41-24                 |      |

|-----|------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|------|

| Num | Characteristics                                                                                | Min                                  | Max                   | Unit |

| 230 | DSCK Low                                                                                       | 40                                   |                       | ns   |

| 231 | DSCK High                                                                                      | 40                                   |                       | ns   |

| 232 | DSCK Cycle Time                                                                                | 200                                  | _                     | ns   |

| 233 | DR Asserted to DSO (ACK) Asserted                                                              | 5T <sub>C</sub>                      | _                     | ns   |

| 234 | DSCK High to DSO Valid                                                                         |                                      | 42                    | ns   |

| 235 | DSCK High to DSO Invalid                                                                       | 3                                    | -                     | ns   |

| 236 | DSI Valid to DSCK Low (Setup)                                                                  | 15                                   | <del></del>           | ns   |

| 237 | DSCK Low to DSI Invalid (Hold)                                                                 | 3                                    | _                     | ns   |

| 238 | Last DSCK Low to OS0-OS1, ACK Active                                                           | 3T <sub>C</sub> + T <sub>L</sub>     | _                     | ns   |

| 239 | DSO (ACK) Asserted to First DSCK High                                                          | 2T <sub>C</sub>                      | _                     | ns   |

| 240 | DSO (ACK) Assertion Width                                                                      | 4T <sub>C</sub> + T <sub>H</sub> - 3 | 5T <sub>C</sub> + 7   | ns   |

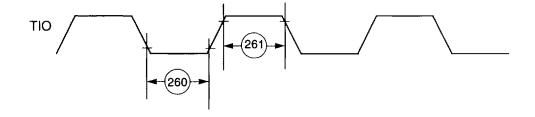

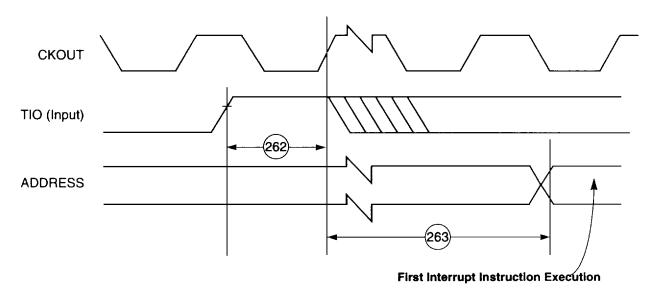

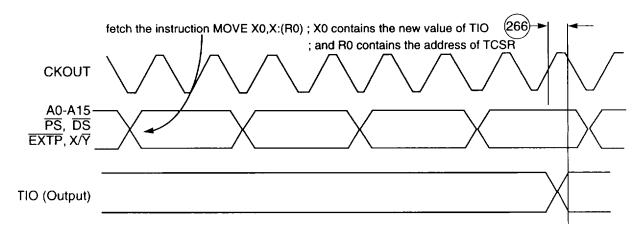

| 241 | DSO (ACK) Asserted to OS0-OS1 High Impedance (See Note 2)                                      | ~                                    | 0                     | ns   |