**FEATURES**

### SC11019/SC11020/SC11021/SC11022/SC11023/SC11074/SC11075 SIERRA SEMICONDUCTOR

2400 BPS Modem Advanced Controller (MAC)

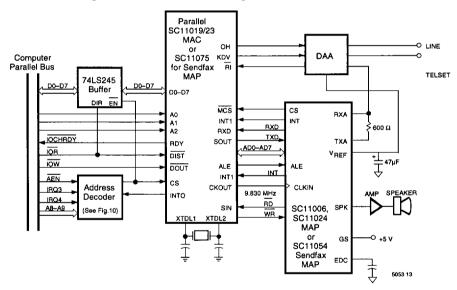

#### ☐ Direct interface to SC11024 or SC11006 single chip modem

- ☐ Complete "AT" command set in internal firmware

- ☐ Built-in UART

- ☐ Direct IBM PC bus interface

- ☐ CMOS technology

- ☐ G3 Fax added with SC11074,75

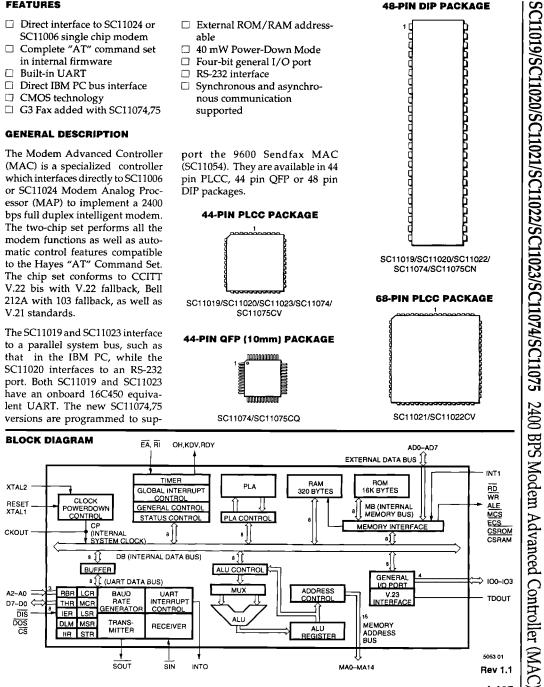

#### **GENERAL DESCRIPTION**

The Modem Advanced Controller (MAC) is a specialized controller which interfaces directly to SC11006 or SC11024 Modem Analog Processor (MAP) to implement a 2400 bps full duplex intelligent modem. The two-chip set performs all the modem functions as well as automatic control features compatible to the Hayes "AT" Command Set. The chip set conforms to CCITT V.22 bis with V.22 fallback, Bell 212A with 103 fallback, as well as V.21 standards.

The SC11019 and SC11023 interface to a parallel system bus, such as that in the IBM PC, while the SC11020 interfaces to an RS-232 port. Both SC11019 and SC11023 have an onboard 16C450 equivalent UART. The new SC11074,75 versions are programmed to sup☐ External ROM/RAM addressable

- 40 mW Power-Down Mode

- ☐ Four-bit general I/O port RS-232 interface

- ☐ Synchronous and asynchronous communication supported

port the 9600 Sendfax MAC (SC11054). They are available in 44 pin PLCC, 44 pin QFP or 48 pin DIP packages.

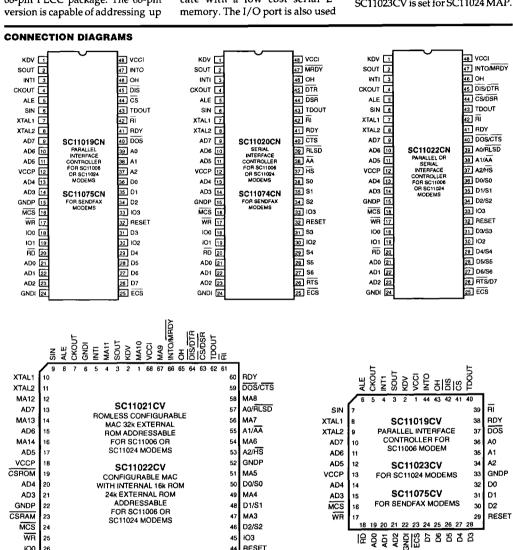

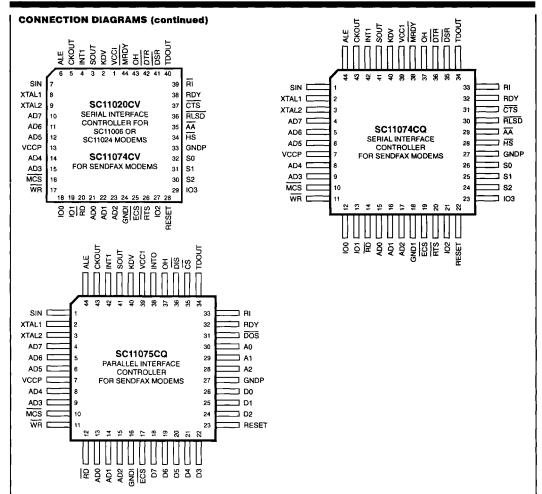

#### 44-PIN PLCC PACKAGE

SC11019/SC11020/SC11023/SC11074/ SC11075CV

#### 44-PIN QFP (10mm) PACKAGE

SC11074/SC11075CQ

48-PIN DIP PACKAGE

#### 68-PIN PLCC PACKAGE

SC11021/SC11022CV

1-167

Ю

1-168

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41

#### **GENERAL DESCRIPTION (continued)**

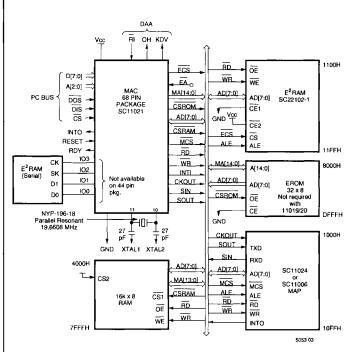

The SC11021 is the ROMless version capable of addressing 32k bytes of external memory and is available in a 68-pin PLCC package.

The SC11022 is the fully configurable version of both controllers and is available in 48-pin DIP and 68-pin PLCC package. The 68-pin to 24k bytes of external memory.

This MAC is similar to, and pin compatible with, the SC11011. The major differences are the addition of a 16k internal ROM containing all the DSP and Hayes compatible commands, plus a four bit I/O port which may be used to communicate with a low cost serial E2 to select the modem configuration-RS-232 or parallel interface, internal or external hybrid, SC11006 or SC11024 MAP. This port is not available in the 44-pin PLCC for parallel applications so these versions are factory programmed for internal hybrid. The SC11019CV is set for use with SC11006 MAP while SC11023CV is set for SC11024 MAP.

RESET

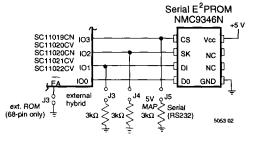

#### CONFIGURATIONS FOR SC11019CN, 20CN, 20CV, 22CV BIG MACS

All models listed above can operate with either serial or multiplexed E<sup>2</sup>PROMs for configuration and number storage. The internal ROM program automatically determines

which kind of E<sup>2</sup>PROM is connected and adapts accordingly.

Note that the SC11022 pin configuration matches that of the SC11011 controller except five new pins are

used that were formerly not connected. Four of these are the I/O pins described above. One is the TDOUT pin which will be used with SC11026 for V.23 signalling.

When substituting SC11022 for SC11011 it is only necessary to open the EA pin and remove the external EPROM. Connect the jumpers as shown if required to operate with SC11024 MAP, external hybrid or in serial mode.

Three of the four I/O pins on the specified models of the internal ROMed MAC are programmed to set the configuration at power-up or reset. Internal weak pull-up re-

#### CONFIGURATIONS FOR SC11019CN, 20CN, 20CV, 22CV BIG MACS (continued)

sistors will set the default configuration to internal hybrid, ±5 V SC11006 MAP interface and Parallel mode if there is no external pull-down.

External pull-down resistors must be added to select other options as indicated in the table. The I/O drivers will overcome these pull-up or pull-down resistors in normal operation to operate the serial  $E^2PROM$ . The I/O pins may be directly grounded if the serial  $E^2PROM$  is not used. The SC11074 and SC11075 do not support  $E^2PROM$ .

In the 44-pin version of SC11019, the I/O pins are not externally available. The SC11023 is internally bonded to select the 5 V only MAP (SC11024) configuration.

| MAC<br>PART NO. | PACKAGE | INT.<br>ROM | EXT.<br>ROM | UART<br>MODE | МАР        |

|-----------------|---------|-------------|-------------|--------------|------------|

| SC11019CV       | 44-PLCC | 16 k        | -           | Parallel     | SC11006    |

| SC11019CN       | 48-DIP  | 16 k        | -           | Parallel     | SC11006    |

| SC11020CV       | 44-PLCC | 16 k        | -           | Serial       | SC11006/24 |

| SC11020CN       | 48-DIP  | 16 k        | -           | Serial       | SC11006/24 |

| SC11021CV       | 68-PLCC | 0           | 32 k*       | Serial/Par.  | SC11006/24 |

| SC11022CV       | 68-PLCC | 16 k        | 24 k        | Serial/Par.  | SC11006/24 |

| SC11022CN       | 48-DIP  | 16 k        | -           | Serial/Par.  | SC11006/24 |

| SC11023CV       | 44-PLCC | 16 k        | -           | Parallel     | SC11024    |

| SC11074CN       | 44-PLCC | 16 k        | -           | Serial       | SC11044/54 |

| SC11074CN       | 48-DIP  | 16 k        | -           | Serial       | SC11044/54 |

| SC11074CQ       | 44-QFP  | 16 k        | -           | Serial       | SC11044/54 |

| SC11075CV       | 44-PLCC | 16 k        | -           | Parallel     | SC11044/54 |

| SC11075CN       | 48-DIP  | 16 k        | _           | Parallel     | SC11044/54 |

| SC11075CQ       | 44-QFP  | 16 k        |             | Parallel     | SC11044/54 |

#### INTERFACE BLOCK DIAGRAMS

Figure 2. MAC 68 Pin Package Interfaces to E<sup>2</sup>PROM, ROM Map

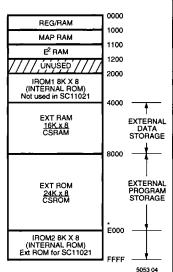

Figure 3. MAC Address Map

# SC11019/SC11020/SC11021/SC11022/SC11023/SC11074/SC11075

| Chip select, active low, input, TTL.  Address lines for UART register select, input, TTL.  Interrupt, output, CMOS/TTL, three-state. Pin is high impedance after reset.  B-bit data port, input-output, TTL, three-state.  Data out strobe (PC writes into UART regis- | RESET     | Master reset Schmitt input, TTL, active high. When RESET is high, MAC program counter resets to location 2000H. It resumes counting   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| Pin is high impedance after reset.  7–D0 8-bit data port, input-output, TTL, three-state.                                                                                                                                                                              | XTAL1     | after RESET goes low.                                                                                                                 |

| ==                                                                                                                                                                                                                                                                     |           | Together with XTAL2 for crystal input (19.660 MHz).                                                                                   |

| <del></del>                                                                                                                                                                                                                                                            | XTAL2     | Crystal output pin (19.6608 MHz).                                                                                                     |

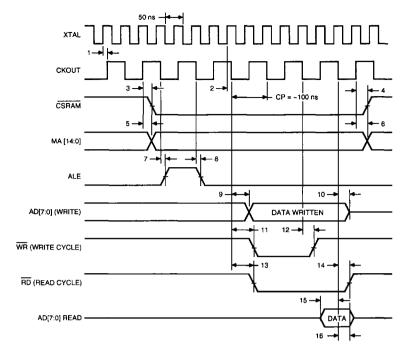

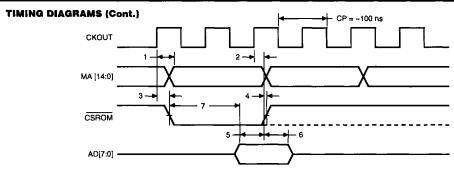

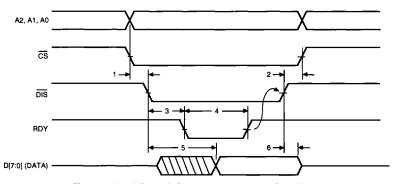

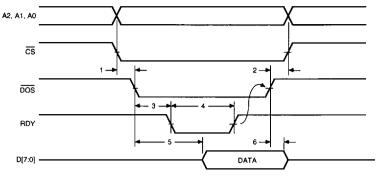

| ters), active low, input, TTL.                                                                                                                                                                                                                                         | CKOUT     | Clock output pin, TTL/CMOS, from MAC (9.8304 MHz, ~100 ns. cycle time).                                                               |

| DIS Data in strobe (PC reads from UART registers),                                                                                                                                                                                                                     | VCCI      | +5 V                                                                                                                                  |

| active low, input, TTL.                                                                                                                                                                                                                                                | GNDI      | Ground                                                                                                                                |

| II MAP Interface                                                                                                                                                                                                                                                       | VCCP      | Second Vcc pin                                                                                                                        |

| .D7-AD0 8-bit bidirectional multiplexed address/data                                                                                                                                                                                                                   | GNDP      | Second Gnd pin                                                                                                                        |

| bus, CMOS.  RAM read, output, CMOS/TTL, normally high, data on AD7-AD0 must be valid at the rising edge of this pulse.                                                                                                                                                 | TDOUT     | Output, TTL/CMOS, CCITT V.23 Transmit<br>Data Output (General I/O Port), three-state.<br>Controlled by General I/O Port.              |

| VR RAM write, output, CMOS/TTL, normally high, data on AD7-AD0 is valid at the rising edge of this pulse.                                                                                                                                                              | PD<br>RDY | Power Down Output, TTI/CMOS, Low indicates power down mode. SC11074, 75 only.  Ouput, ready signal for high speed PC-AT               |

| LE Address Latch Enable, output, CMOS/TTL, the address on ECS, MCS, AD7-AD0 are valid at the falling edge of this normally low pulse.                                                                                                                                  | V Ext     | interface.<br>tra Pins For 48 Pin Package (SC11019/21/22)                                                                             |

| OUT Transmit data, output, CMO5/TTL. Serial data to be transmitted by the modem.                                                                                                                                                                                       |           | General I/O Port, TTL/CMOS, three-state All these pins have weak internal 30 k $\Omega$ pull-ups to Vcc.                              |

| IN Received data, input; TTL. Serial data received from the MAP.                                                                                                                                                                                                       | IO0       | Serial E <sup>2</sup> PROM data out                                                                                                   |

| NTI Interrupt input, TTL; interrupt received from the MAP at 600 Hz. Interrupt is detected when this pin has a low to high transition. The line has to stay high for at least 200 ns.                                                                                  |           | Each I/O pin can be configured as either input or output under control of GIO (page 16). The internal ROM uses these pins as follows: |

| Map chip select for MAP interface, output, TTL/CMOS, addressing space is from 1000H to                                                                                                                                                                                 |           | Serial E <sup>2</sup> PROM D1/External 3 $k\Omega$ pull-down selects external hybrid configuration.                                   |

| 10FFH.                                                                                                                                                                                                                                                                 | 102       | Serial E <sup>2</sup> PROM clock/External 3 k $\Omega$ pull-down selects 5 V MAP (SC11024).                                           |

| CS External EERAM chip select or for second MAP chip select, output, TTL/CMOS, addressing space is fom 1100H to 11FFH.                                                                                                                                                 | 103       | Serial $E^2$ PROM $\overline{CS}$ /External 3 k $\Omega$ pull-down selects serial mode.                                               |

| III DAA Interface                                                                                                                                                                                                                                                      | VI Extr   | a Pins For 68 Pin Package Only (SC11021/22)                                                                                           |

| Ring indicator, input, Schmitt, when low, indicates the modem is receiving a ringing                                                                                                                                                                                   | MA0-MA    | Output, TTL/CMOS, 15 bit address bus for external program/data access.                                                                |

| signal.                                                                                                                                                                                                                                                                | CSROM     | Output, TTL/CMOS, chip select for external ROM, address from 8000H to DFFFH.                                                          |

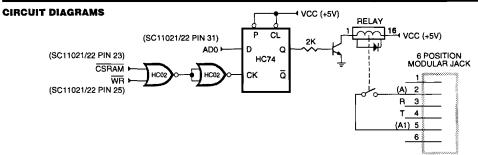

| Off-hook, output, TTL/CMOS, when high, indicates the DAA should go off-hook.                                                                                                                                                                                           | CSRAM     | Output, TTL/CMO5, chip select for external RAM, address from 4000H to 7FFFH.                                                          |

RTS CTS

#### PIN DESCRIPTION (Cont.)

#### VI Extra Pins For 68 Pin Package Only (SC11021/22)

| EA   | Input, External access enable. Low will cause the chip to jump to external vector 8000H after a 2000H reset. Also when this pin is low, the chip will use external interrupt vector. These functions are controlled by |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GNDI | internal ROM code. $\overline{EA}$ pin has a weak internal 30 k $\Omega$ pull-up to Vcc. Third Gnd pin for 68 pin package.                                                                                             |

| GNDI | internal 30 kΩ pull-up to Vcc.                                                                                                                                                                                         |

#### SC11020/21/22/74 Pin Description

(Interfaces to RS-232 port)

#### I MAP Interface

16 pins identical to SC11019 including: AD7–AD0, RD, WR, ALE, SOUT, SIN, INTI, MCS, ECS.

#### II RS-232 (Data Set Mode) and Display Interface

| DTR  | Data terminal ready, input, TTL.            |

|------|---------------------------------------------|

| ĀĀ   | Automatic answer enable (low), output, TTL/ |

|      | CMOS.                                       |

| HS   | High speed indicator, output, TTL/CMOS.     |

|      | Low when operating at 2400 bps rate. High   |

|      | otherwise.                                  |

| MRDY | Modem ready.                                |

| RLSD | Carrier detect, output, TTL/CMOS.           |

| DSR  | Data set ready, output, TTL/CMOS.           |

## Request to send, input, TTL. Clear to send, output, TTL/CMOS. **III DAA Interface**

3 pins the same as SC11019 namely: OH, RI, KDV.

#### **IV Switch Port Pins**

| S0-S4 | 5-bit input port for sensing switch setting inputs. External pull-up resistors (10 k $\Omega$ ) |

|-------|-------------------------------------------------------------------------------------------------|

|       | must be used on these inputs or they may be                                                     |

|       | hard wired to +5 V if not used.                                                                 |

|       | See Firmware release notes for functions supported.                                             |

| S0    | When low, selects dumb mode. Modem will not accept commands.                                    |

#### V Switch Port Pins for SC11074

| S0  | Dumb Mode (if pulled down)                            |

|-----|-------------------------------------------------------|

| S1  | Auto Answer (if pulled down)                          |

| S2  | &C0 if pulled high (&C1 if pulled down)               |

| 101 | INT/EXT Hybrid (external hybrid if pulled down)       |

| IO2 | &D2 if pulled down (&D0 if pulled high)               |

| 103 | T.I.E.S./Hayes Escape Sequence (Hayes if pulled down) |

#### VI Other Pins

10 pins, the same as SC11019 namely: RESET, XTAL1, XTAL2, CKOUT, VCC, GND1, VCCP, GND0, TDOUT, RDY, IO3-0.

#### VII Extra Pins For 48 Pin Package

| \$6 <b>-</b> \$8 | 3-bit input port for sensing switch setting inputs. External pull-up resistors (10 k $\Omega$ ) must be used on these inputs or they may be |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

|                  | hard wired to +5 V if not used.                                                                                                             |

|                  | See Firmware release notes for functions                                                                                                    |

| VIII E   | Extra Pins For 68 Pin Package Only                                                                                                                                                                                                                                                                               |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MA0-MA14 | Output, TTL/CMOS, 15 bit address bus for external program/data access.                                                                                                                                                                                                                                           |

| CŚROM    | Output, TTL/CMOS, chip select for external ROM, address from 8000H to DFFFH.                                                                                                                                                                                                                                     |

| CSRAM    | Output, TTL/CMOS, chip select for external RAM, address from 4000H to 7FFFH.                                                                                                                                                                                                                                     |

| EA       | Input, External access enable . Low will cause the chip to jump to external vector 8000H after a 2000H reset. Also when this pin is low, the chip will use external interrupt vector. These functions are controlled by internal ROM code. $\overline{EA}$ pin has a weak internal 30 k $\Omega$ pull-up to Vcc. |

| GNDI     | Third gnd pin for 68 pin package.                                                                                                                                                                                                                                                                                |

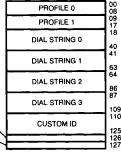

CHECK SUM CONFIGURATION OPTION

#### **MAC Operation**

The MAC is interrupted once every 1.667 ms (600 Hz). It reads two l channel samples and two Q channel samples (T/2 sampling) within 100 µs of receiving the interrupt.

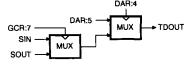

After the samples are processed a quadbit (4 bits) descrambled of data is written back to the MAP. The MAP will perform the synch to asynch conversion function, if operating in asynchronous mode, and outputs received data on SIN pin.

#### **Manufacturer Identification**

The optional external E<sup>2</sup>PROM may be used to store your manufacturer's ID in bytes 6EH thru 7DH (16 characters). This ID will be returned on command ATI3. The manufacturer's ID must be pre-written to the E2PROM. Only the phone numbers and settings are user programmable.

Dial strings are packed 5 bits per character.

Checksum is monitored at power up reset. If it does not match internal ROM, the E2RAM is assumed to be new. This causes the program to write the factory default values into the E2ROM. If the checksum matches the internal number, the configuration profile is read from the E2PROM into the modem registers before going to the command

E2 RAM ALLOCATION 127 x 16

# SOFTWARE ARCHITECTURE Operand Types

- 1. Short Integers: Short integers are 8-bit signed 2's complement variables. Arithmetic operations which generate results outside the range -128 and +127 will set the overflow bit in the Program Status Byte (PSB). There are no alignment restrictions on short integers.

- 2. Integers: Integers are 16-bit signed 2's complement variables. Arithmetic operations which generate results outside the range -32768 and +32767 will set the overflow bit in the PSB. The least significant byte of the integers is in the even byte address and the next most significant byte is in the next higher (odd) address. Therefore, the integers must be aligned at even byte boundaries in the address space. The address of a word is the address of its least significant byte (always an even address).

- 3. Bits: The bits within the bytes of the register file are numbered from 0 to 7 with 0 referring to the LSB. The only instructions that use bit addressing are JBC and JBS.

4. Long Integers: Long integers are 32-bit signed 2's complement variables. The result of a 16 x 16-bit multiply will be stored in a long integer. Only SHRL and SHLL manipulate this data type. Long integers are addressed by the address of their least significant byte in the register file. They should be aligned such that their address is evenly divisible by 4. The most significant byte of a long integer resides on "address" +3, where "address" is the long integer's address.

#### **Operand Addressing**

Three types of addressing are allowed:

- 1. Immediate Addressing: This is a direct field within the instruction. For short integers, this is an 8-bit field, whereas, for the integers this is a 16-bit field. Only one operand within an instruction can be immediate reference type. This operand must always be the last (right most) operand within an instruction.

- e.g. ADD AX, #340H is allowed ADD AX, #340H, BX is NOT allowed

- Register Direct Addressing: In this mode an 8-bit field is used to access a register from the 320 byte register file. The regiter address must conform to the alignment rules.

- e.g. ADD AX, BX :AX, BX must be "even" numbers

- ADDB AX, BX :AX, BX can be "odd" or "even"

- Indirect Addressing: A memory location can be addressed indirectly by placing its 16-bit address in the register file. Only one operand (the right most operand) within an instruction can be indirect.

- e.g. ADDB AL, BL, [CX] is allowed ADDB AL, [CX], BL is NOT allowed

# Program Status Byte (PSB), location 0192H

This is an 8-bit register storing the condition flags of arithmetic, shift, and compare instructions (see the following table). The programmer can access these bits by using address 0192H.

#### Firmware Revisions:

Firmware may be upgraded from time to time to add features and improve performance. Please call Sierra sales office for the current firmware documentation.

#### Program Status Byte (PSB) Location 0192H

| віт | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                      |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | PD     | Power-Down enable bit. Set HIGH to power-down. Set LOW to power-up. CKOUT slows down 32 times during power-down. Hardware reset on RI, DTR off ton in serial mode or RI, DIS, CS off to in parallel mode.                                                                                                     |

| 6   | Unused | N/A                                                                                                                                                                                                                                                                                                           |

| 5   | IP     | Global interrupt pending bit. Set upon receipt of interrupt. Cleared when interrupt service begins.                                                                                                                                                                                                           |

| 4   | IE     | Global interrupt enable bit; when zero, all interrupts are disabled.                                                                                                                                                                                                                                          |

| 3   | Z      | Zero bit; indicates the last arithmetic or compare instruction produced a zero result.                                                                                                                                                                                                                        |

| 2   | N      | Negative bit; indicates the last arithmetic or compare instruction produced a negative result.                                                                                                                                                                                                                |

| 1   | С      | Carry bit; indicates the state of the arithmetic carry from the most significant bit of the ALU for an arithmetic operation or the state of the last bit shifted out of the operand for a shift. Arithmetic "Borrow" after a subtract is the complement of the C flag (i.e. if borrow generated then $C=0$ ). |

| 0   | V      | Overflow bit; indicates the last arithmetic operation produced an overflow.                                                                                                                                                                                                                                   |

#### SOFTWARE ARCHITECTURE (Cont.)

#### **Power-Down Feature**

This MAC has the ability to operate in a standby or power-down mode in which the internal bus clock is divided by 32. This allows the CPU to continue to operate and monitor certain lines in readiness to resume normal operation. The process is fully automatic and transparent to the user.

When the SC11024 MAP is used with this MAC, it too is placed in the power-down mode. Together, the two chips consume typically 8.5 mA in this mode.

The MAC enters the power-down mode when the modem is off line and the DTE interface is inactive. Power-down is disabled in the test modes.

Normal operation resumes upon one or more of the following: DTR goes high (serial mode), RI goes

true, SIN goes low (serial mode) or  $\overline{\text{CS}}$  goes true (parallel mode). These inputs are hardwired to the power down register—bit 7 of program status byte.

(Note: Check with sales office listed for ROM code revision which supports power-down.)

#### **Interrupt Structure**

Four interrupt sources exist in the MAC, namely the external interrupt, timer interrupt, ring leading edge interrupt, and UART interrupt. The interrupt service routine address is 2004H.

- External interrupt: A low to high transition on the INTI pin initiates this interrupt.

- 2) Timer interrupt: Timer overflow interrupt—4.8 kHz frequency.

- Ring leading edge: Interrupt generated by leading edge of ring input.

- 4) UART interrupt: Interrupt from UART.

- a) Parallel version: From UMR register. Any one of the following can generate this interrupt.

RBR was read by external processor

Data was transferred from THR to TSR

LCR was changed

MCR was changed

DLL or DLM was changed

b) Serial version: In this configuration the interrupt signal from 16C450 compatible UART is brought in as an interrupt source to the internal CPU.

#### INTERRUPT CONTROL REGISTER (ICR), location 0193H

This is an 8 bit register to enable or disable each of the four interrupt sources and to record the interrupt sources. The upper four bits are read/write registers while the lower four bits are read only registers. A read operation to the register will automatically clear the lower four bits.

BIT0: "1" indicates UART requested an interrupt.

BIT1: "1" indicates RING leading edge requested an interrupt.

BIT2: "1" indicates TIMER overflow requested an interrupt.

BIT3: "1" indicates EXTERNAL source requested an interrupt.

BIT4: "1" to enable UART interrupt.

BIT5: "1" to enable RING leading edge interrupt.

BIT6: "1" to enable TIMER overflow interrupt.

BIT7: "1" to enable EXTERNAL interrupt.

Any one of these four interrupts will drive the processor to address 2004H. From there the software can check interrupt sources and do priority control to branch to different service routines.

#### INSTRUCTION SET

The MAC instruction set is a subset of Intel 8096 instruction set. The object codes, formats and the flags they effect are identical to those of 8096. The differences are:

- No VT or ST flags exist in the MAC.

- Register locations in the UART section can only be accessed by using indirect addressing.

1-174

- The operands refer to one or more bytes of the register file. ROM locations can only be addressed using indirect addressing.

- If a memory location is addressed between 1000H and 11FFH, an external six clock multiplexed bus operation is initiated. The multiplexed address/ data will use AD7-AD0 bus.

data tutil uca ALI/ ALKI mie

- When using ST or STB operations, the destinations are always considered to be indirect addresses.

- e.g. ST, AX, [BX] is allowed ST, AX, BX is NOT allowed

#### INSTRUCTION SET (Cont.)

#### Instruction Set Table

| MNEMONIC | NO. OF OPERANDS | OPERATION                       | BYTES <sup>1</sup> | TIME <sup>2</sup> |  |

|----------|-----------------|---------------------------------|--------------------|-------------------|--|

| ADD/ADDB | 2               | B ← A + B                       | 3                  | 10                |  |

| ADD/ADDB | 3               | $D \leftarrow A + B$            | 4                  | 10                |  |

| AND/ANDB | 2               | $B \leftarrow A \text{ AND } B$ | 3                  | 10                |  |

| AND/ANDB | 3               | $D \leftarrow A \text{ AND B}$  | 4                  | 10                |  |

| CMP/CMPB | 2               | D – A                           | 3                  | 10                |  |

| OJNZ     | 1               | Decrement & JNZ                 | 3                  | 9/12              |  |

| EXTB     | 1               | Sign Extend Byte                | 2                  | 7                 |  |

| BC       | 0               | Jump if bit clear               | 3                  | 10/13             |  |

| BS       | 0               | Jump if bit set                 | 3                  | 10/13             |  |

| C        | 0               | Jump if Carry Set               | 2                  | 5/8               |  |

| NC       | 0               | Jump if no carry                | 2                  | 5/8               |  |

| E        | 0               | Jump if =                       | 2                  | 5/8               |  |

| NE       | 0               | Jump if not =                   | 2                  | 5/8               |  |

| GT       | 0               | Jump if >                       | 2                  | 5/8               |  |

| GE       | 0               | Jump if >=                      | 2                  | 5/8               |  |

| LE       | 0               | Jump if < or =                  | 2                  | 5/8               |  |

| LT       | 0               | Jump if <                       | 2                  | 5/8               |  |

| V        | 0               | Jump if Overflow                | 2                  | 5/8               |  |

| NV       | 0               | Jump if no overflow             | 2                  | 5/8               |  |

| H        | 0               | Jump if higher                  | 2                  | 5/8               |  |

| NH       | 0               | Jump if not higher              | 2                  | 5/8               |  |

| LCALL    | 0               | Long Call                       | 3                  | 11                |  |

| LD/LDB   | 2               | Load                            | 3                  | 10                |  |

| MUL      | 3               | $D \leftarrow A * B$            | 5                  | 33                |  |

| NOP      | 0               | NO Operation                    | 1                  | 2                 |  |

| OR/ORB   | 2               | $D \leftarrow D OR A$           | 3                  | 10                |  |

| KOR/XORB | 2               | $D \leftarrow D XOR A$          | 3                  | 10                |  |

| PUSHF    | 0               | Push PSB                        | 1                  | 5                 |  |

| POPF     | 0               | Pop PSB                         | 1                  | 5                 |  |

| RET      | 0               | Return                          | 1                  | 10                |  |

| SHL/SHLB | 1               | Shift Left                      | 3                  | $11 + N^3$        |  |

| SHLL     | 1               | Shift Left Long                 | 3                  | $15 + N^3$        |  |

| SHR/SHRB | 1               | Shift Right                     | 3                  | $11 + N^3$        |  |

| SHRL     | 1               | Shift Right Long                | 3                  | $15 + N^3$        |  |

| SHRA     | 1               | Arith. Right Shift              | 3                  | $10 + N^3$        |  |

| HRAL     | 1               | Arith. Right Long               | 3                  | $15 + N^3$        |  |

| SJMP     | 0               | Short Jump                      | 2                  | 7                 |  |

| JMP      | 0               | Long Jump                       | 3                  | 9                 |  |

| ST/STB   | 2               | Store to Memory                 | 3                  | 13 <sup>4</sup>   |  |

| SUB/SUBB | 2               | $B \leftarrow B - A$            | 3                  | 10                |  |

| SUB/SUBB | 3               | $D \leftarrow B - A$            | 4                  | 10                |  |

<sup>&</sup>lt;sup>1</sup>Add one for immediate words.

<sup>&</sup>lt;sup>2</sup>Add 9 for indirect mode and 2 or 0 for immediate mode—see table. (Cycle times @ 100 ns)

<sup>&</sup>lt;sup>3</sup>N is number of bit shifts.

<sup>&</sup>lt;sup>4</sup>Indirect Mode.

#### HARDWARE ARCHITECTURE

The MAC device is organized with two buses that interconnect four main logic sections. The two buses are the internal data bus (DB) and address bus (Y). The four sections of the device are the internal processor, registers, memory, and dual port UART.

The two bus architecture was chosen to allow the MAC to execute the 8096 instruction set as fast or faster than the 8096 itself. The device is intended to run at 9.8304 MHz. A typical three operand instruction effectively executes in 10 clock cycles. The signed 16 x 16 multiply operation requires 34 clock cycles.

The internal data bus (DB) is the main bus of the device. It is an 8-bit bus that interconnects all four sections of the device. All intenal data travels on DB. The Y bus is a 16-bit output only bus from the internal processor that provides addresses to the memory and register sections of the device. This bus

allows memory control to be resident inside the internal processor without degrading performance.

The internal processor controls MAC operations and performs all of the required computation functions. The internal processor consists of a micro-control PLA and a 16-bit registered arithmetic/logic unit (RALU). The microcontrol PLA accepts as input 8096 instruction opcodes and generates the control sequences necessary to implement the instructions. The RALU performs instruction execution, operand address calculation, jump address calculation, program sequencing, and stack control. The program counter (PC) and stack pointer (SP) are contained within the RALU. The RALU is implemented with the 2901 silicon compiler.

The register section of the MAC includes RAM and the ports of the device. These locations are all treated as regis-

ters and may be accessed in register direct mode. Code can't be executed from registers. The UART registers are functionally, but not physically, part of the register section. The UART registers are accessed via indirect addressing mode only. There are 320 bytes of RAM to support DSP functions and the Hayes Smartmodem command set. The memory section of the MAC includes the program ROM and the external memory interface. The device contains 16K bytes of program ROM. The external memory interface allows the MAC to access program storage or data storage from external memory.

The UART section of the device implements the industry standard 16C450 UART. In its parallel version the MAC appears as a 16C450 to the user. The UART contains dual-port capability to allow the user and the internal processor access to its internal registers.

#### MEMORY DESCRIPTION

#### Internal ROM:

The 16K bytes of internal ROM is organized into 2 separate blocks of 8K bytes each: IROM1 and IROM2.

The SC11019/20/21/22/23 controllers are built with the same architecture as the SC11011 so that firmware will be upward compatible.

#### **External Read/Write:**

Three different types of external memory operations are defined.

A) For address from 1000H to 11FFH:

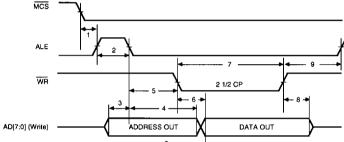

These external operations occur through the AD bus. These operations take six clock cycles, four more than internal operations. These are mainly for MAP & EEROM interfaces, however, instructions and data can also be fetched from these memory spaces.

B) For address from 4000H to 7FFFH: 68 pin only.

These memory spaces are reserved for external DATA storage. The MAC can

access external RAM through MA address bus and AD data bus. There are six clock memory cycles for each access.

C) For address from 8000H to FFFFH: 68 pin only.

For 68 pin package the chip fetches instructions from external program storage by MA0-MA14 and AD0-AD7. These operations are exactly the same as internal ROM fetch and they take 2 clock cycles. For the SC11021 ROMless version, the 8k bytes from E000H to FFFFH are also mapped for external access.

#### Memory Address MAP

| NAME               | ABV   | ADDRESS     | R/W | SIZE (bytes) |

|--------------------|-------|-------------|-----|--------------|

| INTERNAL RAM/REG   | RAM*  | 0000H-013FH | R/W | 320          |

|                    | REG*  | 0180H-0193H | R/W | 19 registers |

| EXTERNAL MAP/EERAM | MAP   | 1000H-10FFH | R/W | 256          |

|                    | EERAM | 1100H-11FFH | R/W | 256          |

| INTERNAL ROM***    | IROM1 | 2000-3FFFH  | RO  | 8K           |

|                    | IROM2 | E000H-FFFFH | RO  | 8K           |

| EXTERNAL RAM**     | RAM   | 4000H-7FFFH | R/W | 16K          |

| EXTERNAL ROM**     | ROM   | 8000H-DFFFH | RO  | 24K          |

These may only be accessed as memory locations (16-bit address) in an indirect mode. For direct addressing

a 9th bit (GCR [1], called Page Bit) must be set to switch from the first 256 bytes to the rest of the RAM.

\*\* For 68 pin package only. Memory address has 15 bits (MA14–MA0); 16th bit is accessed through CSROM and CSRAM.

\*\*\* The ROMless SC11021 uses external ROM E000H-DFFFH for a total 32 kbytes. Also, the SC11022CV when used with external ROM disables the upper 8k internal ROM and addresses 32k external (Eng. version uses only 24k).

#### REGISTER DESCRIPTION

This section contains a description of each of the registers in the MAC device. All of the registers of the device are 8-bits with 16-bit addresses. The registers are made up of bits that are either inputs or outputs. Input bits are read-only (RO). Output bits are read/write (R/W). The state of an output may be read back by the processor.

#### Test Mode:

RAM locations 00H and 100H are reserved for test mode. User access is prohibited.

#### Serial Mode:

In parallel mode (CONF = 0) the functions of the UART registers

are exactly the same as those in  $16C450\,UART$ . However in serial mode, (CONF = 1), the UART is turned around and controlled by the internal processor and it becomes a data set UART. The DTR, RTS, and OUT1 in MCR register becomes DSR, CTS, and RLSD outputs. The CTS, DSR in MSR register become RTS, DTR input status from RTS,  $\overline{DTR}$  pins.

#### Note:

In serial version to echo SIN to SOUT after RESET and then go back to normal operation.

- 1) Set "SB" in LCR to "1".

- 2) Sample RDI in UART monitor register.

- 3) Set  $CM = \overline{RDI}$  in the same register.

- 4) SOUT will be the same state as  $\overline{\text{CM}}$ .

- 5) Receiver is functioning, ignoring it.

- 6) After finishing all echoing, reset "SB" in LCR.

- 7) Update DLL, DLM, and set CM = 1 for normal operation.

- 8) Do a SET then RESET to RTRST bit to RESET RCV and TMR. Do a READ to LSR to clear LSR.

- 9) The UART is ready for normal operaton.

#### Register Address MAP

|                                |     | INTERNAL <sup>3</sup>            |                                |     | EXTERNAL <sup>6</sup> |     |

|--------------------------------|-----|----------------------------------|--------------------------------|-----|-----------------------|-----|

| NAME                           | ABV | INDIRECT<br>ADDRESS <sup>4</sup> | DIRECT<br>ADDRESS <sup>5</sup> | R/W | ADDRESS<br>A [2:0]    | R/W |

| UART Registers:                |     |                                  |                                |     |                       | -   |

| Receive Buffer <sup>1</sup>    | RBR | 80H                              | 180H                           | R/W | 00H                   | RO  |

| Transmit Holding <sup>1</sup>  | THR | 8AH                              | 18AH                           | R/W | 00H                   | WO  |

| Interrupt Enable <sup>1</sup>  | IER | 81H                              | 181H                           | R/W | 01H                   | R/W |

| Interrupt ID                   | IIR | 82H                              | 182H                           | RO  | 02H                   | RO  |

| Line Control                   | LCR | 83H                              | 183H                           | R/W | 03H                   | R/W |

| Modem Control                  | MCR | 84H                              | 184H                           | R/W | 04H                   | R/W |

| Line Status                    | LSR | 85H                              | 185H                           | R/W | 05H                   | R/W |

| Modem Status                   | MSR | 86H                              | 186H                           | R/W | 06H                   | R/W |

| Scratch Pad (8 bit)            | STR | 87H                              | 187H                           | R/W | 07H                   | R/W |

| Divisor Latch LSB <sup>2</sup> | DLL | 88H                              | 188H                           | R/W | 00H                   | R/W |

| Divisor Latch MSB <sup>2</sup> | DLM | 89H                              | 189H                           | R/W | 01H                   | R/W |

| UART Monitor                   | UMR | 8BH                              | 18BH                           | R/W |                       |     |

| Internal Registers:            |     |                                  |                                |     |                       |     |

| Switch Port                    | SWP | 8DH                              | 18DH                           | RO  |                       |     |

| General I/O Port               |     |                                  |                                |     |                       |     |

| Direction Register             | DIR | 8EH                              | 18EH                           | WO  | 1                     |     |

| Data Register                  | DAR | 8FH                              | 18FH                           | R/W |                       |     |

| General Control                | GCR | 90H                              | 190H                           | R/W |                       |     |

| TIMER                          | TIM | 91H                              | 191H                           | R/W |                       |     |

| Processor Status Byte          | PSB | 92H                              | 192H                           | R/W |                       |     |

| Interrupt Control              | ICR | 93H                              | 193H                           | R/W |                       |     |

- DLAB bit (LCR [7]) must be zero for external access.

- <sup>2</sup> DLAB bit (LCR [7]) must be one for external access.

<sup>&</sup>lt;sup>3</sup>Register access through MA bus.

<sup>48-</sup>bit addresses for indirect addressing only, with Page bit (GCR [1]) used.

<sup>&</sup>lt;sup>5</sup>16-bit addresses for direct addressing only.

<sup>&</sup>lt;sup>6</sup>UART register access through PC parallel system bus.

#### **ACCESSIBLE REGISTERS**

The system programmer may access or control any of the UART registers summarized in Table 1 via the CPU. These registers are used to control UART operations and to transmit and receive data. Their reset functions are summarized in Table 2.

# Line Control Register (LCR, location 183H)

The system programmer specifies the format of the asynchronous data communications exchange via the Line Control Register. In addition to controlling the format, the programmer may retrieve the contents of the Line Control Register for inspection. This feature simplifies system programming and eliminates the need for separate storage in system memory of the line characteristics. The contents of the Line Control Register are indicated in Table I and are described in the following.

Table 1: Summary of Accessible Registers

|           | Register Address                              |                                                    |                                                                 |                                               |                                             |                                              |                                              |                                              |                     |                          |               |

|-----------|-----------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------|---------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------|--------------------------|---------------|

|           | 0(DLAB=0)                                     | 0(DLAB=0)                                          | (DLAB=0)                                                        | 2                                             | 3                                           | 4                                            | 5                                            | 6                                            | 7                   | (DLAB=1)                 | (DLAB=1)      |

| Bit<br>No | Receiver<br>Buffer<br>Register<br>(Read Only) | Transmitter<br>Holding<br>Register<br>(Write Only) | Interrupt<br>Enable<br>Register                                 | Interrupt<br>Iden.<br>Register<br>(Read Only) | Line<br>Control<br>Register                 | MODEM<br>Control<br>Register                 | Line<br>Status<br>Register                   | MODEM<br>Status<br>Register                  | Scratch<br>Register | Divisor<br>Latch<br>(LS) | Latch<br>(MS) |

|           | RBR                                           | THR                                                | IER                                                             | IIR                                           | LCR                                         | MCR                                          | LSR                                          | MSR                                          | STR                 | DLL                      | DLM           |

| 0         | Data Bit 0*                                   | Data Bit 0                                         | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBFI) | "0" if<br>Interrupt<br>Pending                | Word<br>Length<br>Select<br>Bit 0<br>(WLS0) | Data<br>Terminal<br>Ready<br>(DTR)           | Data<br>Ready<br>(DR)                        | Delta<br>Clear<br>to Send<br>(DCTS)          | Bit 0               | Bit 0                    | Bit 8         |

| 1         | Data Bit 1                                    | Data Bit 1                                         | Enable Transmitter Holding Register Empty Interrupt (ETBEI)     | Interrupt<br>ID<br>Bit (0)                    | Word<br>Length<br>Select<br>Bit 1<br>(WLS1) | Request<br>to Send<br>(RTS)                  | Overrun<br>Error<br>(OE)                     | Delta<br>Data<br>Set<br>Ready<br>(DDSR)      | Bit 1               | Bit 1                    | Bit 9         |

| 2         | Data Bit 2                                    | Data Bit 2                                         | Enable<br>Receiver<br>Line Status<br>Interrupt<br>(ELSI)        | Interrupt<br>ID<br>Bit (1)                    | Number<br>of Stop<br>Bits (STB)             | Out 1                                        | Parity<br>Error<br>(PE)                      | Trailing<br>Edge Ring<br>Indicator<br>(TERI) | Bit 2               | Bit 2                    | Bit 10        |

| 3         | Data Bit 3                                    | Data Bit 3                                         | Enable<br>MODEM<br>Status<br>Interrupt<br>(EDSSI)               | 0                                             | Parity<br>Enable<br>(PEN)                   | Out 2<br>INT0 is<br>High-Z<br>when<br>out2=0 | Framing<br>Error<br>(FE)                     | Delta<br>Data<br>Carrier<br>Detect<br>(DDCD) | Bit 3               | Bit 3                    | Bit 11        |

| 4         | Data Bit 4                                    | Data Bit 4                                         | 0                                                               | 0                                             | Even<br>Parity<br>Select<br>(EPS)           | Loop                                         | Break<br>Interrupt<br>(BI)                   | Clear to<br>Send<br>(CTS)                    | Bit 4               | Bit 4                    | Bit 12        |

| 5         | Data Bit 5                                    | Data Bit 5                                         | 0                                                               | 0                                             | Stick<br>Parity                             | 0                                            | Transmitter<br>Holding<br>Register<br>(THRE) | Data<br>Set<br>Ready<br>(DSR)                | Bit 5               | Bit 5                    | Bit 13        |

| 6         | Data Bit 6                                    | Data Bit 6                                         | 0                                                               | 0                                             | Set<br>Break                                | 0                                            | Transmitter<br>Empty<br>(TEMT)               | Ring<br>Indicator<br>(RI)                    | Bit 6               | Bit 6                    | Bit 14        |

| 7         | Data Bit 7                                    | Data Bit 7                                         | 0                                                               | 0                                             | Divisor<br>Latch<br>Access<br>Bit<br>(DLAB) | 0                                            | 0                                            | Data<br>Carrier<br>Detect<br>(DCD)           | Bit 7               | Bit 7                    | Bit 15        |

\*Bit 0 is the least significant bit. It is the first bit senally transmitted or received.

**Bits 0 and 1:** These two bits specify the number of bits in each transmitted or received serial character. The encoding of bits 0 and 1 is as follows:

|   | Bit 1 | Bit 0 | Word<br>Length |

|---|-------|-------|----------------|

| Ī | 0     | 0     | 5 Bits         |

| l | 0     | 1     | 6 Bits         |

| l | 1     | 0     | 7 Bits         |

|   | 1     | 1     | 8 Bits         |

Bit 2: This bit specifies the number of Stop bits in each transmitted character. If bit 2 is a logic 0, one Stop bit is generated in the transmitted data. If bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one and a half Stop bits are generated. If bit 2 is a logic 1 when either a 6-, 7-, or 8-bit word length is selected, two Stop bits are generated. The Receiver checks the first Stop-bit only, regardless of the number of Stop bits selected.

Bit 3: This bit is the Parity Enable bit. When bit 3 is a logic 1, a Parity bit is generated (transmit data) or checked (receive data) between the last data word bit and Stop bit of the serial data. (The Parity bit is used to produce an even or odd number of 1s when the data word bits and the Parity bit are summed.)

Bit 4: This bit is the Even Parity Select bit. When bit 3 is a logic 1 and bit 4 is a logic 0, an odd number of logic 1s is transmitted or checked in the data word bits and Parity bit. When bit 3 is a logic 1 and bit 4 is a logic 1, an even number of logic 1s is transmitted or checked.

Bit 5: This bit is the Stick Parity bit. When bits 3, 4 and 5 are logic 1 the Parity bit is transmitted and checked by the receiver as a logic 0. If bits 3 and 5 are 1 and bit 4 is a logic 0, then the Parity bit is transmitted as a 1.

Table 2. Summary of Accessible Registers

| Register/Signal                      | Reset Control            | Reset State                                                     |

|--------------------------------------|--------------------------|-----------------------------------------------------------------|

| Interrupt Enable Register            | Master Reset             | All Bits Low (0–3) forced<br>and 4–7 permanent)                 |

| Interrupt Identification<br>Register | Master Reset             | Bit 0 is High, Bits 1 and 2 Low,<br>Bit 3–7 are permanently Low |

| Line Control Register                | Master Reset             | All Bits Low                                                    |

| Modem Control Register               | Master Reset             | All Bits Low                                                    |

| Line Status Register                 | Master Reset             | "All Bits Low, Except Bits 5<br>and 6 are High"                 |

| MODEM Status Register                | Master Reset             | "Bits 0–3 Low, Bits 4–7—<br>Input Signal"                       |

| SOUT                                 | Master Reset             | High                                                            |

| INTRPT (RCVR Errs)                   | Read LSR/MR              | Low                                                             |

| INTRPT<br>(RCVR Data Ready)          | Read BRR/MR              | Low                                                             |

| INTRPT (THRE)                        | Read IIR/Write<br>THR/MR | Low                                                             |

| INTRPT (Modem<br>Status Changes)     | Read RBR/MR              | Low                                                             |

Bit 6: This bit is the Break Control bit. When it is set to a logic 1, the serial output (SOUT) is forced to the Spacing (logic 0) state. The break is disabled by setting bit 6 to a logic 0. The Break Control bit acts only on SOUT and has not effect on the transmitter logic.

Note: This feature enables the CPU to alert a terminal in a computer communications system. If the following sequence is followed, no erroneous or extraneous characters will be transmitted because of the break.

- Load an all 0s, pad character, in response to THRE.

- 2. Set break after the next THRE.

- Wait for the transmitter to be idle, (TEMT=1), and clear break when normal transmission has to be restored

During the break, the Transmitter can be used as a character timer to accurately establish the break duration.

Bit 7: This bit is the Divisor Latch Access Bit (DLAB). It must be set high (logic 1) to access the Divisor Latches of the Baud Generator during a Read or Write operation. It must be set low (logic 0) to access the Receiver Buffer, the Transmitter Holding Register, or the Interrupt Enable Register.

#### **Programmable Baud Generator**

The UART contains a programmable Baud Generator that takes an internal clock of (3/32)(XTAL1) = 1.8432 MHz and divides it by any divisor from 1 to (216-1). The output frequency of the Baud Generator is  $16 \times \text{the Baud [(divisor # = (fre-}$ quency input)  $\div$  (baud rate x 16)]. Two 8-bit latches store the divisor in a 16-bit binary format. These Divisor Latches must be loaded during initialization in order to ensure desired operation of the Baud Generator. Upon loading either of the Divisor Latches, a 16-bit Baud counter is immediately loaded. This prevents long counts on the initial load.

Table 3 illustrates the used of the

Baud Generator with a crystal frequency of 19.6608 MHz. The accuracy of the desired baud rate is dependent on the crystal accuracy. Communication software writing values to the divisor latches typically expects the input to the UART to be 1.8432 MHz. They will work correctly only if the MAC input clock is maintained at 19.6608 MHz.

#### Line Status Register (LSR, location 185H)

| Desired<br>Baud<br>Rate | Divisor<br>Used to<br>Generate<br>16 x Clock | Error<br>Between<br>Desired<br>and Actual |

|-------------------------|----------------------------------------------|-------------------------------------------|

| 50                      | 2304                                         |                                           |

| 75                      | 1536                                         | -                                         |

| 110                     | 1047                                         | 0.026                                     |

| 134.4                   | 857                                          | 0.058                                     |

| 150                     | 768                                          | -                                         |

| 300                     | 384                                          |                                           |

| 600                     | 192                                          |                                           |

| 1200                    | 96                                           |                                           |

| 1800                    | 64                                           | _                                         |

| 2000                    | 58                                           | 0.69                                      |

| 2400                    | 48                                           | _                                         |

| 3600                    | 32                                           |                                           |

| 4800                    | 24                                           | _                                         |

| 7200                    | 16                                           | _                                         |

| 9600                    | 12                                           | _                                         |

| 19200                   | 6                                            | _                                         |

| 38400                   | 3                                            | _                                         |

| 57600                   | 2                                            | _                                         |

This 8-bit register provides status information to the CPU concerning the data transfer. The contents of the Line Status Register are indicated in Table 1 and are described below.

Bit 0: This bit is the receiver Data Ready (DR) indicator. Bit 0 is set to a logic 1 whenever a complete incoming character has been received and transferred into the Receiver Buffer Register. Bit 0 is reset to a logic 0 by reading the data in the Receiver Buffer Register. Bit 1: This bit is the Overrun Error (OE) indicator. Bit 1 indicates that data in the Receiver Buffer Register was not read by the CPU before the next character was transferred into the Receiver Buffer Register, thereby destroying the previous character. The OE indicator is reset whenever the CPU reads the contents of the Line Status Register.

Bit 2: This bit is the Parity Error (PE) indicator. Bit 2 indicates that the received data character does not have the correct even or odd parity, as selected by the even-parity-select bit. The PE bit is set to a logic 1 upon detection of a parity error and is reset to a logic 0 whenever the CPU reads the contents of the Line Status Register.

Bit 3: This bit is the Framing Error (FE) indicator. Bit 3 indicates that the received character did not have a valid Stop bit. Bit 3 is set to a logic 1 whenever the Stop bit following the last data bit or parity bit is detected as a zero bit (Spacing level). The FE indicator is reset whenever the CPU reads the contents of the Line Status indicator.

Bit 4: This bit is the Break Interrupt (BI) indicator. Bit 4 is set to a logic 1 whenever the received data input is held in the Spacing (logic 0) state for longer than a full word transmission time (that is, the total time of Start bit + data bits + Parity + Stop bits). The BI indicator is reset whenever the CPU reads the contents of the Line Status indicator.

Note: Bits 1 through 4 are the error conditions that produce a Receiver Line Status interrupt whenever any of the corresponding conditions are detected.

Bit 5: The bit is the Transmitter Holding Register Empty (THRE) indicator. Bit 5 indicates that the ACE is ready to accept a new character for transmission. In addition,

this bit causes the UART to issue an interrupt to the CPU when the Transmit Holding Register Empty Interrupt enable is set high. The THRE bit is set to a logic 1 when a character is transferred from the Transmitter Holding Register into the Transmitter Shift Register. The bit is reset to logic 0 concurrently with the loading of the Transmitter Holding Register by the CPU.

Bit 6: This bit is the Transmitter Empty (TEMT) indicator. Bit 6 is set to a logic 1 whenever the Transmitter Holding Register (THR) and the Transmitter Shift Register (TSR) are both empty. It is reset to a logic 0 whenever either the THR or TSR contains a data character.

Bit 7: This bit is permanently set to logic 0.

Note: The Line Status Register is intended for read operations only. Writing to this register is not recommended as this operation is used for factory testing.

#### Interrupt Identification Register (IIR, location 182H)

The UART has on-chip interrupt capability that allows for flexibility in interfacing popular microprocessors presently available. In order to provide minimum software overhead during data character transfers, the UART prioritizes interrupts into four levels. The four levels of interrupt conditions are as follows: Receiver Line Status (priority 1); Received Data Ready (priority 2); Transmitter Holding Register Empty (priority 3); and MODEM status (priority 4).

Information indicating that a prioritized interrupt is pending and the type of that interrupt are stored in the Interrupt Identification Register (IIR). When addressed during chip-select time, the IIR freezes the highest priority interrupt pending and no other interrupts change the IIR, even though they are recorded, until the particular interrupt is serviced by the CPU. The contents of the IIR are indicated in Table 1 and are described below.

Bit 0: This bit can be used in either a hardwired prioritized or polled environment to indicate whether an interrupt is pending. When bit 0 is a logic 0, an interrupt is pending and the IIR contents may be used as a pointer to the appropriate interrupt service routine. When bit 0 is a logic 1, no interrupt is pending and polling (if used) continues.

Bits 1 and 2: These two bits of the IIR are used to identify the highest priority interrupt pending as indicated in Table 4.

**Bits 3 through 7:** These five bits of the IIR are always logic 0.

# Interrupt Enable Register (IER, location 181H)

The 8-bit register enables the four types of interrupts of the UART to

separately activate the chip interrupt (INTRPT) output signal. It is possible to totally disable the interrupt system by resetting bits 0 through 3 of the Interrupt Enable Register. Similarly, by setting the appropriate bits of this register to a logic 1, selected interrupts can be enabled. Disabling the interrupt system inhibits the Interrupt Identification Register and the active (high) INTRPT output from the chip. All other system functions operate in their normal manner, including the setting of the Line Status and MODEM Status Registers. The contents of the Interrupt Enable Register are indicated in Table 1 and are described below.

**Bit 0:** This bit enables the Received Data Available Interrupt when set to logic 1.

**Bit 1:** This bit enables the Transmitter Holding Register Empty Interrupt when set to logic 1.

Bit 2: This bit enables the Receiver

Line Status Interrupt when set to logic 1.

Bit 3: This bit enables the MODEM Status Interrupt when set to logic 1.

Bits 4 through 7: These four bits are always logic 0.

#### **Modem Control Register**

This 8-bit register controls the interface with the MODEM or data set (or a peripheral device emulating a MODEM). The contents of the MODEM Control Register are indicated in Table 1 and are described below.

Bit 0: This bit controls the Data Terminal Ready (DTR) output. When bit 0 is set to a logic 1, the DTR output is forced to a logic 0. When bit 0 is reset to a logic 0, the DTR output is forced to a logic 1.

Bit 1: This bit controls the Request to Send ( $\overline{RTS}$ ) output. Bit 1 affects the  $\overline{RTS}$  output in a manner identical to that described above for bit 0.

| Interr | rupt Idei<br>Registe |       | on                | Interrupt Set and Reset Functions     |                                                                                |                                                                                                             |

|--------|----------------------|-------|-------------------|---------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Bit 2  | Bit 1                | Bit 0 | Priority<br>Level | Interrupt Type                        | Interrupt Source                                                               | Interrupt Reset Control                                                                                     |

| 0      | 0                    | 1     | -                 | None                                  | None                                                                           | _                                                                                                           |

| 1      | 1                    | 0     | Highest           | Receiver Line Status                  | Overrun Error or Parity<br>Error or Framing Error<br>or Break Interrupt        | Reading the Line Status<br>Register                                                                         |

| 1      | 0                    | 0     | Second            | Receiver Data Available               | Receiver Data Available                                                        | Reading the Receiver<br>Buffer Register                                                                     |

| 0      | 1                    | 0     | Third             | Transmitter Holding<br>Register Empty | Transmitter Holding<br>Register Empty                                          | Reading the IIR Register<br>(If source of interrupt) or<br>Writing into the Transmitter<br>Holding Register |

| 0      | 0                    | 0     | Fourth            | MODEM Status                          | Clear to Send or Data Set<br>Ready or Ring Indicator<br>or Data Carrier Detect | Reading the MODEM<br>Status Register                                                                        |

**Bit 2:** Out1. Auxiliary user-designated bit. It is connected to MSR[6] (RI) during local loopback.

**Bit 3:** Out 2. Auxiliary user-designated bit. It is connect to MSR[7] (DCD) during local loopback. When Out2 = 0, INTO pin is Hi-Z.

Bit 4: This bit provides a local loopback feature for diagnostic testing of the UART. When bit 4 is set to logic 1, the following occur: the transmitter Serial Output (SOUT) is set to the Marking (logic 1) state; the receiver Serial Input (SIN) is disconnected; the output of the Transmitter Shift Register is "looped back" into the Receiver Shift Register input: the four MO-DEM. Status Register bits CTS. DSR, DCD and RI are disconnected internally; and the four MODEM Control Register bits DTR, RTS, OUT1 and OUT2 are internally connected to the four MODEM Status Register inputs, and the MODEM Control output pins RLSD, CTS, DSR are forced to their inactive state (high). In the diagnostic mode, data that is transmitted is immediately received. This feature allows the processor to verify the transmit and received-data paths of the UART.

In the diagnostic mode, the receiver and transmitter interrupts are fully operational. The MODEM Control Interrupts are also operational, but the interrupts' sources are now the lower four bits of the MODEM Control Register instead of the four

MODEM Control inputs. The interrupts are still controlled by the Interrupt Enable Register.

Bits 5–7: These bits are permanently set to logic 0.

# Modem Status Register (MSR, location 186H)

This 8-bit register provides the current state of the control lines from the MODEM (or peripheral device) to the CPU in addition to this current-state information, four bits of the MODEM Status Register provide change information. These bits are set to a logic 1 whenever a control input from the MODEM changes state. They are reset to logic 0 whenever the CPU reads the MODEM Status Register.

The contents of the MODEM Status Register are indicated in Table 1 and are described below.

Bit 0: This bit is the Delta Clear to Send (DCTS) indicator. Bit 0 indicates that the CTS input to the chip has changed state since the last time it was read by the CPU.

Bit 1: This bit is the Delta Data Set Read (DDSR) indicator. Bit 1 indicates that the DSR input to the chip has changed state since the last time it was read by the CPU.

Bit 2: This bit is the Trailing Edge of Ring Indicator (TERI) detector. Bit 2 indicates that the RI input to the chip has changed from a low to a high state.

Bit 3: This is the Delta Data Carrier Detect (DDCD) indicator. Bit 3 indicates that the DCD input to the chip has changed state.

Note: Whenever bit 0, 1, 2, or 3 is set to logic 1, a MODEM Status Interrupt is generated.

Bit 4: This bit is the complement of the Clear to Send (CTS) input. If bit 4 (loop) of the MCR is set to a 1, this bit is equivalent to RTS in the MCR.

Bit 5: This bit is the complement of the Data Set Ready (DSR) input. If bit 4 of the MCR is set to a 1, this bit is equivalent of DTR in the MCR.

Bit 6: This bit is the complement of the Ring Indicator  $(\overline{RI})$  input. If bit 4 of the MCR is set to a 1, this bit is equivalent to OUT 1 in the MCR.

Bit 7: this bit is the complement of the Data Carrier Detect (DCD) input. If bit 4 of the MCR is set to a 1, this bit is equivalent to OUT 2 of the MCR.

# Scratchpad Register (STR, location 187H)

This 8-bit Read/Write Register does not control the ACE in any way. It is intended as a scratchpad register to be used by the programmer to hold data temporarily.

#### REGISTER DESCRIPTION (Cont.)

#### **UART Monitor (UMR, location 18BH):**

The UART Monitor register allows the processor to monitor UART operations. A read operation to the UART Monitor register will clear Bit 0 to Bit 4.

| BIT | NAME  | DESCRIPTION                                                                                                                                                                                                                                                                                            |

|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | RTRST | Reset receiver and transmitter. When set high both receiver and transmitter will be put into reset state.                                                                                                                                                                                              |

| 6   | СМ    | UART Command/Modem Output. When set HIGH the UART is placed in modem mode. At reset it is low, in command mode. This bit together with SB in LCR are used for bit by bit echoing. In serial version the user can set SB = 1 and CM = RDI to echo a bit. When CONF = 1 for normal operation set CM = 1. |