## LSU405 N-CHANNEL JFET

## Linear Systems replaces discontinued Siliconix U405

The LSU405 is a Low Noise, Low Drift, Monolithic Dual N-Channel JFET

The LSU405 is a high-performance monolithic dual JFET featuring extremely low noise, tight offset voltage and low drift over temperature specifications, and is targeted for use in a wide range of precision instrumentation applications. The LSU405 features a 5mV offset and 10-μV/°C drift. The LSU405 is a direct replacement for discontinued Siliconix LSU405.

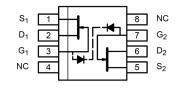

The 8 Pin P-DIP and 8 Pin SOIC provide ease of manufacturing, and the symmetrical pinout prevents improper orientation.

(See Packaging Information).

## LSU405 Applications:

- Wideband Differential Amps

- High-Speed, Temp-Compensated Single-Ended Input Amps

- **High-Speed Comparators**

- Impedance Converters and vibrations detectors.

| FEATURES                                                 |                                 |                                          |                 |  |  |  |  |

|----------------------------------------------------------|---------------------------------|------------------------------------------|-----------------|--|--|--|--|

| LOW DRIFT                                                |                                 | $ V_{GS1-2}/T  = 10\mu V/^{\circ}C$ TYP. |                 |  |  |  |  |

| LOW NOISE                                                |                                 | $e_n = 6nV/Hz @ 10Hz TYP.$               |                 |  |  |  |  |

| LOW PINCHOFF                                             |                                 | $V_p = 2.5V TYP.$                        |                 |  |  |  |  |

| ABSOLUTE MAXIMUM RATINGS                                 |                                 |                                          |                 |  |  |  |  |

| @ 25°C (unless otherwise noted)                          |                                 |                                          |                 |  |  |  |  |

| Maximum Temperatures                                     |                                 |                                          |                 |  |  |  |  |

| Storage Tem                                              | perature                        |                                          | -65°C to +150°C |  |  |  |  |

| Operating Ju                                             | nction Temperature              |                                          | +150°C          |  |  |  |  |

| Maximum Voltage and Current for Each Transistor – Note 1 |                                 |                                          |                 |  |  |  |  |

| -V <sub>GSS</sub>                                        | Gate Voltage to Drain or Source |                                          | 50V             |  |  |  |  |

| -V <sub>DSO</sub>                                        | Drain to Source Voltage         |                                          | 50V             |  |  |  |  |

| -I <sub>G(f)</sub>                                       | Gate Forward Current            |                                          | 10mA            |  |  |  |  |

| Maximum Power Dissipation                                |                                 |                                          |                 |  |  |  |  |

| Device Dissipation @ Free Air – Total 300mW              |                                 |                                          |                 |  |  |  |  |

| MATCHING CHARACTERISTICS @ 25°C UNLESS OTHERWISE NOTED |                 |       |       |                                     |  |  |

|--------------------------------------------------------|-----------------|-------|-------|-------------------------------------|--|--|

| SYMBOL                                                 | CHARACTERISTICS | VALUE | UNITS | CONDITIONS                          |  |  |

| V <sub>GS1-2</sub> / T  max.                           | DRIFT VS.       | 40    | μV/°C | $V_{DG}$ =10V, $I_{D}$ =200 $\mu$ A |  |  |

|                                                        | TEMPERATURE     |       |       | T <sub>A</sub> =-55°C to +125°C     |  |  |

| V <sub>GS1-2</sub>   max.                              | OFFSET VOLTAGE  | 20    | mV    | $V_{DG}$ =10V, $I_{D}$ =200 $\mu$ A |  |  |

ELECTRICAL CHARACTERISTICS @ 25°C (unless otherwise noted) CONDITIONS SYMBOL CHARACTERISTICS MIN TYP. MAX. UNITS BV<sub>GSS</sub> Breakdown Voltage 50 60  $V_{DS} = 0$  $I_D=1nA$ Gate-To-Gate Breakdown ±50 \_\_ ٧  $BV_{GGO}$  $I_D = 0$  $I_s = 0$  $I_G = 1nA$ TRANSCONDUCTANCE 2000 Full Conduction 7000 f = 1kHz 10\/ umho  $I_D = 200 \mu A$  f = 1kHzTypica<mark>l O</mark>per<mark>at</mark>ion 1000 2000 μmho 15V Mismatch 0.6 3 %  $|Y_{FS1-2}/Y_{FS}|$ **DRAIN CURRENT**  $V_{DG}$ = 10V10 V<sub>GS</sub>= 0V **Full Conduction** 0.5 mA Mismatch at Full Conduction  $|I_{DSS1-2}/I_{DSS}|$ 1 5 % **GATE VOLTAGE** Pinchoff voltage  $V_{GS}(off)$  or  $V_{r}$ -0.5 -2.5  $V_{DS} = 15V$  $I_D = 1nA$  $V_{GS}(on)$ **Operating Range** -2.3 ٧  $V_{DS}=15V$  $I_D = 200 \mu A$ **GATE CURRENT**  $V_{DG} = 15V I_D = 200 \mu A$ -I<sub>G</sub>max. Operating -4 -15 pΑ  $T_A = +125$ °C -I<sub>G</sub>max. High Temperature -10 nΑ -l<sub>GSS</sub>max. At Full Conduction 100 рΑ  $V_{DS} = 0$ -I<sub>GSS</sub>max. High Temperature 5  $V_{DG} = 15V$ T<sub>A</sub>= +125°C 5 5 рΑ **OUTPUT CONDUCTANCE Full Conduction** V<sub>DG</sub>= 10V 20 μmho  $V_{GS} = 0V$ Yoss  $V_{DG} = 15V$  $Y_{\underline{OS}}$ Operating 0.2 2 umho  $I_{D} = 500 \mu A$ **COMMON MODE REJECTION**  $V_{DS} = 10 \text{ to } 20V$ **CMR** -20 log | V <sub>GS1-2</sub>/ V <sub>DS</sub>| 95 dB  $I_D = 30 \mu A$ **NOISE**  $V_{DS} = 15V$  $V_{GS} = 0V$  $R_G = 10M$ NF **Figure** 0.5 dB f= 100Hz NBW= 6Hz  $V_{DS}$ =15V  $I_D$ =200 $\mu$ A f=10Hz NBW=1Hz e<sub>n</sub> Voltage 20 nV/√Hz **CAPACITANCE**  $\mathbf{C}_{\underline{\text{ISS}}}$ Input 8 рF  $V_{DS} = 15V$   $I_{D} = 200 \mu A$ f= 1MHz 1.5 рF  $C_{RSS}$ Reverse Transfer

Note 1 - These ratings are limiting values above which the serviceability of any semiconductor may be impaired

Available Packages:

LSU405 in PDIP / SOIC LSU405 available as bare die

Please contact Micross for full package and die dimensions

PDIP / SOIC (Top View)

Micross Components Europe

Tel: +44 1603 788967

Email: chipcomponents@micross.com Web: http://www.micross.com/distribution