## XGA DISPLAY CONTROLLER

#### PRELIMINARY INFORMATION

#### **FEATURES**

Supports both AT Bus and Micro Channel interfaces

Allows 2-chip AT Bus or Micro Channel bus XGA solution (IMS G201 + IMS G191)

Bus mastership on AT Bus and Micro Channel VGA and XGA standard registers

Programmable CRT controller supports many display modes including:

1280×1024 with 16/256 colors (interlaced) 1024×768 with 256 colors (non-interlaced) 800×600 with 65.536 colors (non-interlaced)

132 column text mode (1056×480 resolution) 16 bit true color support (5 Red. 6 Green, 5 Blue) Video RAM interface for high performance ISO-compliant screen refresh rates

Fully backwards compatible with IMS G200 XGA

display controller

208 pin PQFP package

IMS G201 coprocessor supports:

1. 2. 4. 8 and 16 bit Pixel and bit block transfers

Line drawing

Area filling

Logical and arithmetic pixel mixing

Pixel map masking

Scissoring

X, Y axis addressing

### **TABLE OF CONTENTS**

| 22.1  | IMS G201 description                              | 473 |

|-------|---------------------------------------------------|-----|

| 22.2  | Pin function reference guide                      | 476 |

| 22.3  | Coprocessor                                       | 484 |

| 22.4  | System bus interface                              | 487 |

| 22.5  | CRT and VRAM controller                           | 487 |

| 22.6  | XGA I/O-mapped and memory-mapped registers        | 489 |

| 22.7  | IMS G201 register reference guide                 | 493 |

| 22.8  | IMS G201 / IMS G191 communication                 | 501 |

| 22.9  | IMS G201 device configuration                     | 503 |

| 22.10 | Hardware interfaces                               | 516 |

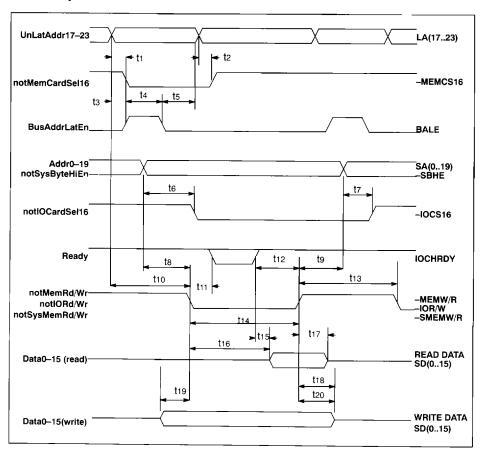

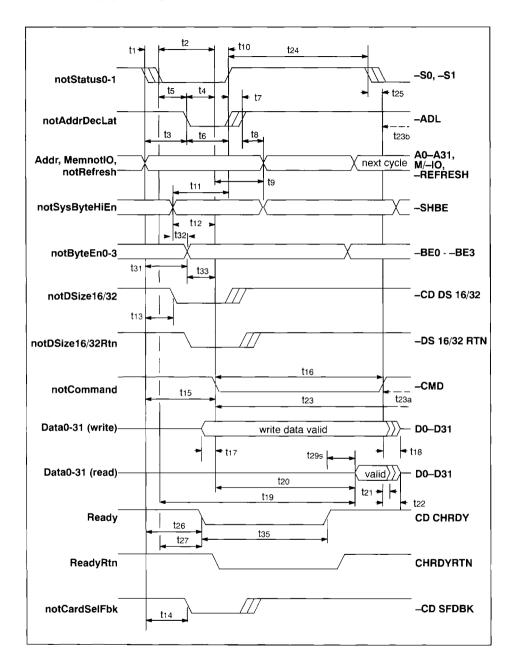

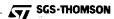

| 22.11 | Timing reference guide for AT bus mode            | 527 |

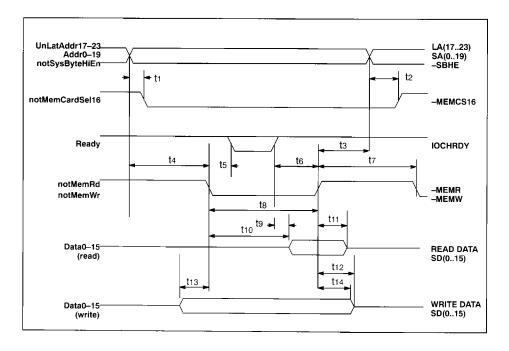

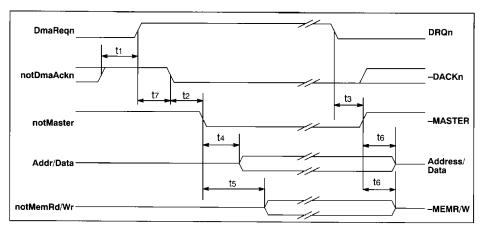

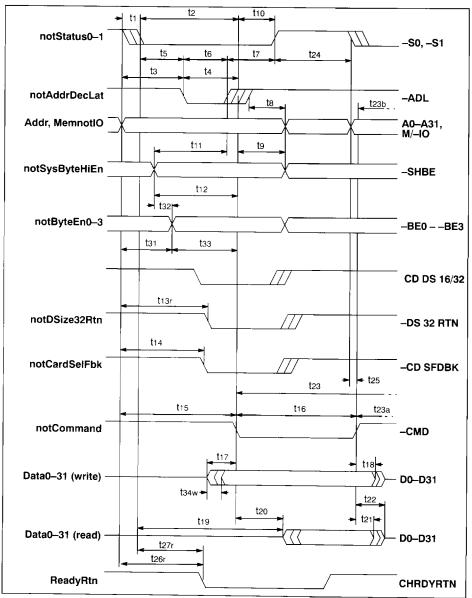

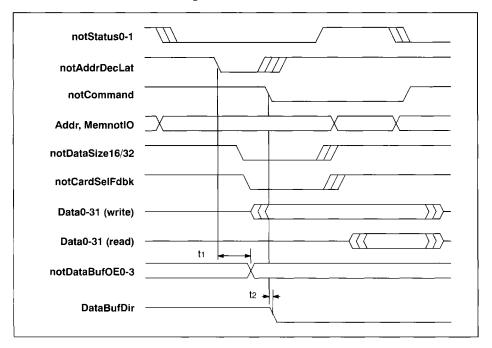

| 22.12 | Timing reference guide for Micro Channel bus mode | 531 |

| 22.13 | Electrical specifications                         | 557 |

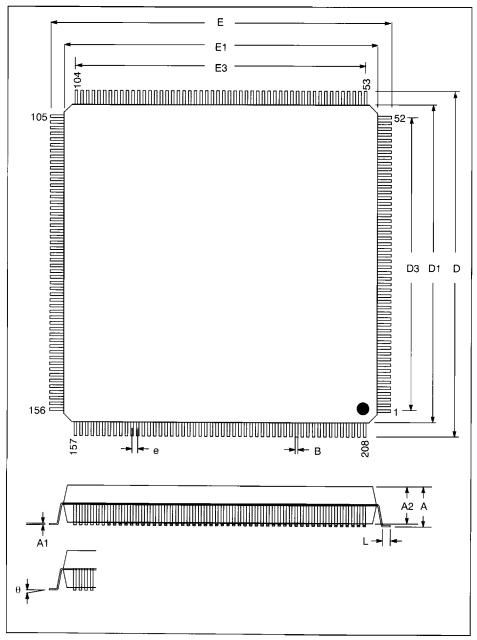

| 22.14 | Package specifications                            | 560 |

| 22.15 | Ordering information                              | 567 |

## 22.1 IMS G201 description

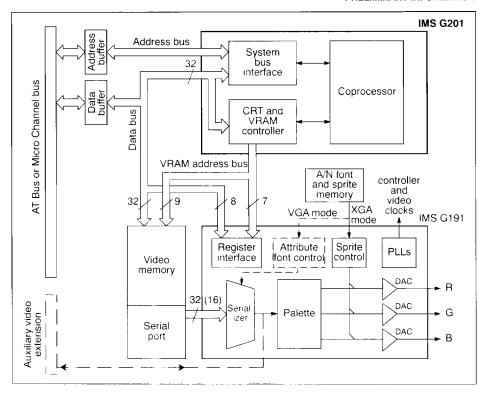

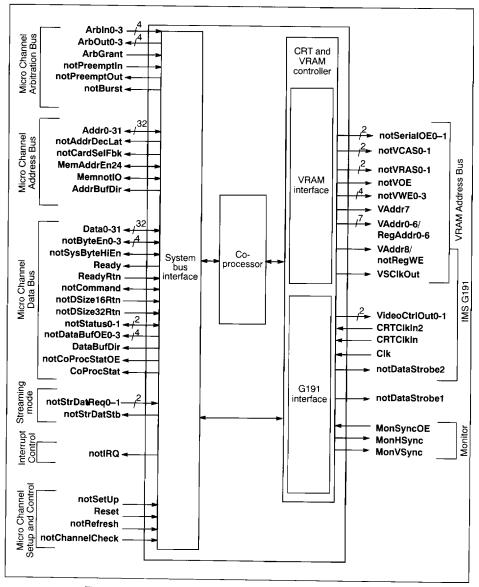

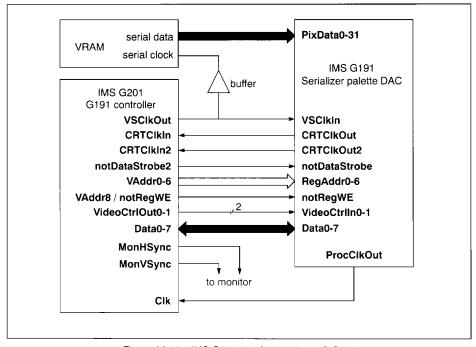

The IMS G201 display controller chip comprises the system bus interface, drawing coprocessor, and the memory and display controller components of the G201/G191 chipset based XGA subsystem.

#### System bus interface modes

The IMS G201 can be set to operate in one of two modes: AT bus mode or Micro Channel mode.

In AT bus mode it is designed to interface with an AT bus standard and supports a 16 bit or an 8 bit interface. It supports both slave and master operations for a 16 bit interface or slave operations only for an 8 bit interface. A block diagram showing the IMS G201 in AT bus mode is given in Section 22.1.1.

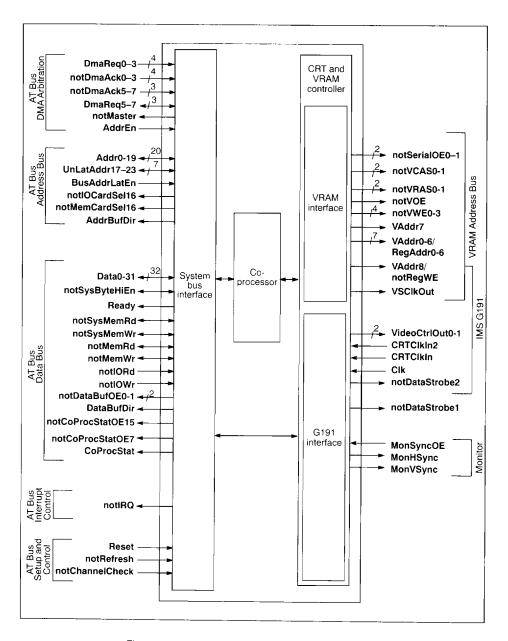

In Micro Channel bus mode the IMS G201 is designed to interface to a Micro Channel bus standard and supports a 32 or a16 bit interface. It operates both as slave and master. Streaming data (100ns cycle) operation is supported when the IMS G201 is a master only. A block diagram showing the IMS G201 in Micro Channel bus mode is given in Section 22.1.2.

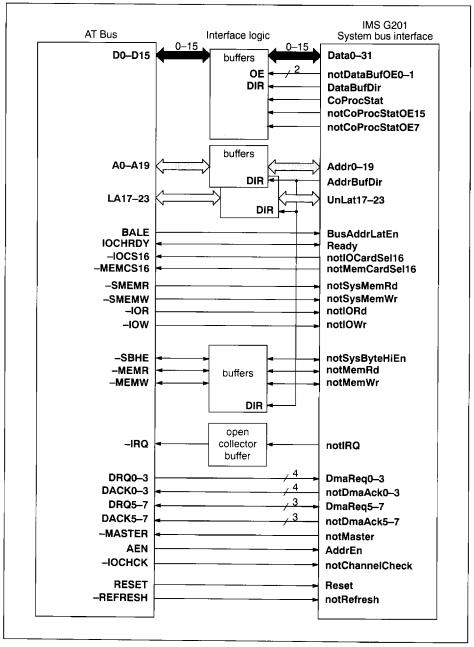

## 22.1.1 Detailed IMS G201 block diagram for AT bus mode

Figure 22.1 shows the main functional units and all pin connections of the IMS G201 in AT bus mode.

Figure 22.1 IMS G201 block diagram for AT bus mode

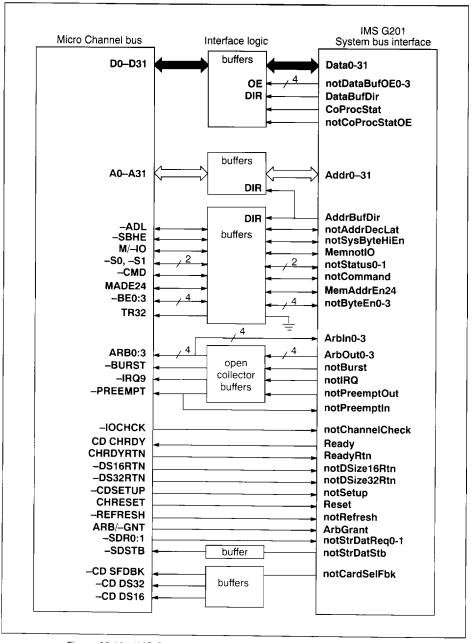

# 22.1.2 Detailed IMS G201 block diagram for Micro Channel bus mode

Figure 22.2 shows the main functional units and all pin connections of the IMS G201 in Micro Channel bus mode.

Figure 22.2 IMS G201 block diagram for Micro Channel bus mode

# 22.2 Pin function reference guide

Signal names are prefixed by not if they are active low, otherwise they are active high.

## 22.2.1 System bus interface

The pins on the system bus interface are dual function. The function of the pins is dependent on whether it is interfacing to an AT bus or a Micro Channel bus. The sub-section below lists the pin descriptions when the IMS G201 is operating in AT bus mode, this is followed by a separate sub-section detailing the pins when in Micro Channel mode.

#### AT bus mode

#### AT bus Address bus

| Pin name        | I/O | Signal description                                                                                                                                                                                                                                                                       |  |  |  |

|-----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Addr0-19        | I/O | These address signals are generated by the microprocessor or DMA controller and are gated on the system bus when <b>BusAddrLatEn</b> is high. They are used by the AT bus interface logic for register decoding.                                                                         |  |  |  |

| UnLatAddr17-23  | I/O | These signals generate memory decodes for 16 bit, 1 wait state, memory cycles and may be derived from the system microprocessor or other arbitrated devices or DMA controllers.                                                                                                          |  |  |  |

| BusAddrLatEn    | 1   | This signal indicates a valid microprocessor or DMA address and is used for address latching.                                                                                                                                                                                            |  |  |  |

| notiOCardSel16  | 0   | This signal indicates to the system that the current data transfer is a 16 bit 1 wait state, I/O cycle. It is derived from the decode of <b>UnLa-tAddr0–15</b> and is driven with a tri-state driver capable of sinking 20mA.                                                            |  |  |  |

| notMemCardSel16 | 0   | This signal indicates to the system that the current data transfer is a 16 bit 1 wait state, memory cycle. It is derived from the decode of UnLatAddr17–23 and is driven with a tri-state driver capable of sinking 20mA.                                                                |  |  |  |

| AddrBufDir      | 0   | This pin controls the direction of an external 3 state bidirectional buffer isolating the IMS G201 from the AT bus. Active high signifie the AT bus is driving the IMS G201 pins (G201 is the slave), and active low signifies that IMS G201 is driving the AT bus (G201 is the master). |  |  |  |

#### AT bus Arbitration bus

| Pin name     | I/O | Signal description                                                                                                                                                                                                                 |  |  |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| DmaReq5-7    | I/O | These signals asynchronously request a bus master service. They are prioritized with <b>DmaReq5</b> having highest priority and <b>DmaReq7</b> having lowest.                                                                      |  |  |

| notDmaAck5–7 | 1   | A DMA request is is serviced after an arbitration acknowledge generated on <b>notDmaAck5–7</b> .                                                                                                                                   |  |  |

| DmaReq0–3    |     | The 8-bit DMA resources are used to monitor DMA activity on the bufor Pacing control.                                                                                                                                              |  |  |

| notDmaAck0–3 | ı   | A DMA request is is serviced after an arbitration acknowledge generated on <b>notDmaAck0–3</b> . The 8-bit DMA resources are used to monitor DMA activity on the bus for internal Pacing control of the IMS G201.                  |  |  |

| notMaster    | 0   | This signal is used with a <b>DmaReq</b> line to gain control of the syste Typically an arbitrating controller (the IMS G201) on the I/O chan may assert this signal to allow control of the system address, data a control lines. |  |  |

| AddrEn       | l   | When active, the address enable signal <b>AddrEn</b> tri-states the micro-<br>processor and other devices from the I/O channel to allow DMA trans-<br>fers to take place.                                                          |  |  |

### AT bus Data bus

| Pin name  | I/O | Signal description                                                                                                                                                                                                                                                                                                                         |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data0-15  | 1/0 | The <b>Data15</b> signal line represents the most significant bit and <b>Data0</b> the least significant bit of the AT data bus. The data pins are shared by the VRAM random data port and the AT bus. The data pins may connect directly to the VRAM but must be isolated from the AT bus by suitable bi-directional three-state drivers. |

| Data16-31 |     | This portion of the data bus completes the unbuffered 32-bit connection ( <b>Data0-31</b> ) to the VRAM random port.                                                                                                                                                                                                                       |

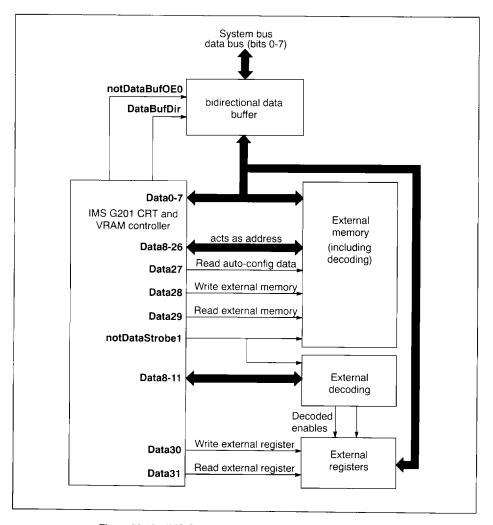

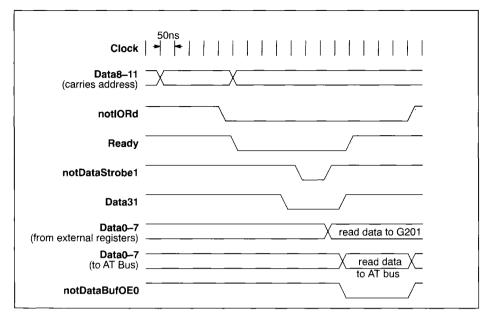

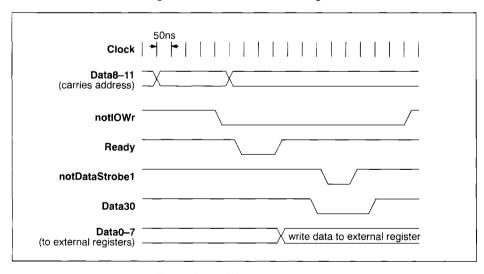

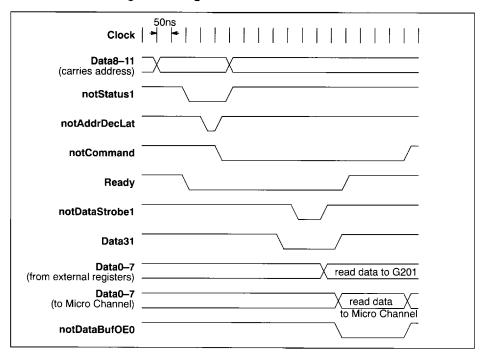

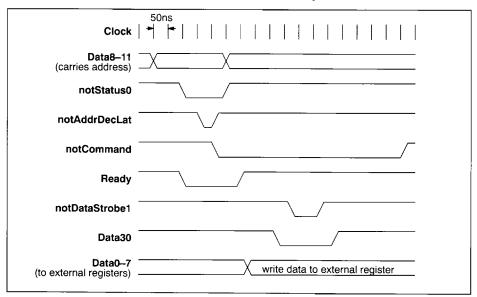

| Data8-11  |     | Data8-11 are also used to carry an address for external registers.                                                                                                                                                                                                                                                                         |

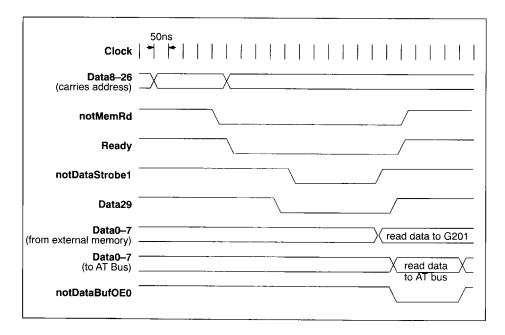

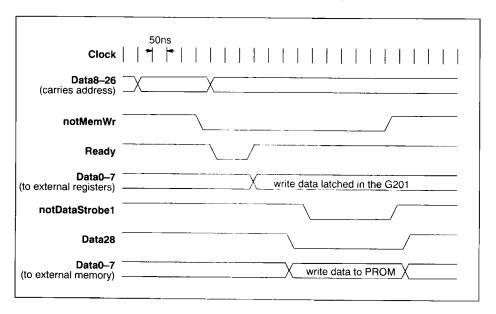

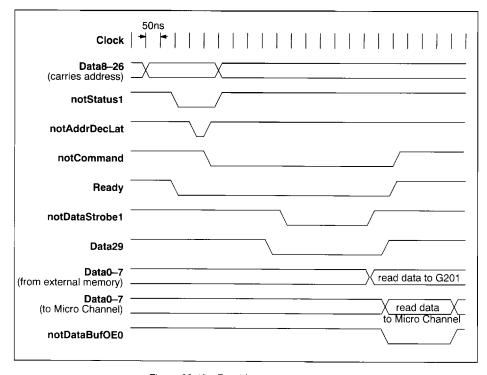

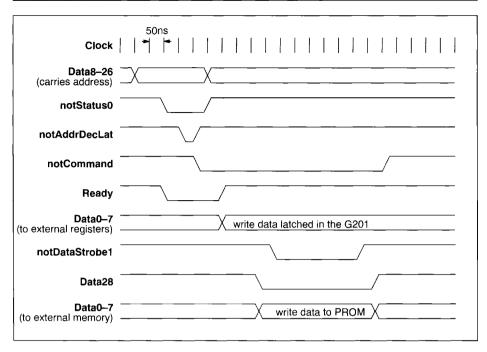

| Data8-26  |     | Data8-26 are also used to carry an address for external memory (typically EPROM). Data23-26 correspond to bits 2-5 in the ROM paging register in AT bus mode.                                                                                                                                                                              |

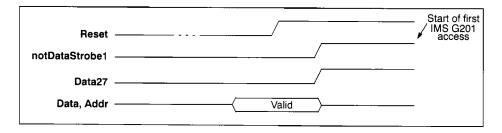

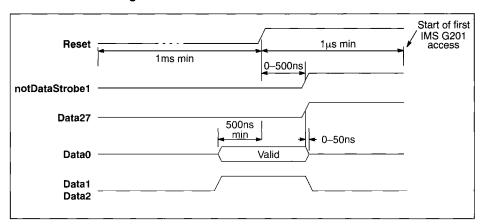

| Data27    |     | Data27 (with notDataStrobe1) is also a strobe qualifier for chip configuration data.                                                                                                                                                                                                                                                       |

| Data28    |     | <b>Data28</b> is also a strobe qualifier for writes to external memory. A low on this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external memory write.                                                                                                                                                             |

| Data29    |     | <b>Data29</b> is also a strobe qualifier for reads from external memory. A low on this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external memory read.                                                                                                                                                             |

| Data30    |     | <b>Data30</b> is also a strobe qualifier for external register writes. A low on this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external register write.                                                                                                                                                            |

| Data31    |     | Data31 is also a strobe qualifier for external register reads. A low on this signal when the notDataStrobe1 pin pulses low indicates an external register read.                                                                                                                                                                            |

| Pin name          | I/O | Signal description                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| notSysByteHIEn    | I/O | System byte high enable signal indicates the transfer of data on the high byte of the data bus (Data8-15). 16 bit devices use notSysByteHIEn to condition the respective data buffers.                                                                                                                                                       |  |  |  |

| Ready             | 1/0 | The <b>Ready</b> signal allows resources to indicate to the bus owner that additional cycle time is required. If the <b>Ready</b> signal is not driven inactive, the cycle either is a no wait state or a standard cycle. If the <b>Ready</b> signal is driven inactive, the cycle length is extended until the line is driven active again. |  |  |  |

| notSysMemRd       | I   | This signal instructs memory devices to drive data onto the data bus. <b>notSysMemRd</b> is active only when the memory decode is within the low 1Mbyte of memory space.                                                                                                                                                                     |  |  |  |

| notSysMemWr       | 1   | This signal instructs memory devices to store the data present on the data bus. <b>notSysMemWr</b> is active only when the memory decode is within the low 1Mbyte of memory space.                                                                                                                                                           |  |  |  |

| notMemRd          | I/O | This signal instructs the memory devices to drive data onto the data bus. <b>notMemRd</b> is active on all memory read cycles.                                                                                                                                                                                                               |  |  |  |

| notMemWr          | I/O | This signal instructs the memory devices to store data present on the data bus. <b>notMemWr</b> is active on all memory read cycles.                                                                                                                                                                                                         |  |  |  |

| notIORd           | 1   | This signal instructs an I/O device to drive its data onto the data bus.                                                                                                                                                                                                                                                                     |  |  |  |

| notlOWr           | 1   | This signal instructs an I/O device to store data on the data bus.                                                                                                                                                                                                                                                                           |  |  |  |

| notDataBufOE0-1   | 0   | A low on this signal puts the AT data bus isolation buffer in the active state; a high puts it in high impedance state. Bit 0 controls data bus bits 0:7, bit 1 controls data bus bits 8:15.                                                                                                                                                 |  |  |  |

| <b>DataBufDir</b> | 0   | This signal controls the direction of an external bidirectional three state transceiver isolating the AT data bus from the shared VRAM data bus. A low indicates drive towards the AT data bus. A high indicates drive towards the IMS G201 and VRAM.                                                                                        |  |  |  |

| notCoProcStatOE15 | 0   | When active low this signal enables the output of a 3-state driver that connects the <b>CoProcStat</b> pin to bit 15 of the AT data bus.                                                                                                                                                                                                     |  |  |  |

| notCoProcStatOE7  | 0   | When active low this signal enables the output of a 3-state driver that connects the <b>CoProcStat</b> pin to bit 7 of the AT data bus.                                                                                                                                                                                                      |  |  |  |

| CoProcStat        | 0   | The CoProcStat signal indicates whether the coprocessor is busy (active high), or not (active low). The signal in conjunction with not-CoProcStatOE7 and notCoProcStatOE15 provides a means of testing the coprocessor status without interrupting the coprocessor to allow the host CPU to use shared VRAM data bus.                        |  |  |  |

# AT bus Interrupt control

| Pin name I/O |   | Signal description |

|--------------|---|--------------------|

| notiRQ       | 0 | Interrupt request  |

## AT bus Setup and control

| Pin name        | 1/0 | I/O Signal description                                                             |  |  |  |  |

|-----------------|-----|------------------------------------------------------------------------------------|--|--|--|--|

| notRefresh      |     | This signal is used to indicate a memory refresh operation is in progress.         |  |  |  |  |

| notChannelCheck |     | This signal is a general error condition. It can be driven active by any resource. |  |  |  |  |

| Reset           | 1   | Bus reset                                                                          |  |  |  |  |

| Clk             | 1   | Clock                                                                              |  |  |  |  |

#### Micro Channel mode

For a full description of the functions of the Micro Channel pins refer to the *IBM PS/2 hardware technical reference manual*.

#### Micro Channel Address bus

| Pin name      | I/O | Signal description                                                                                                                                                                                                                                      |  |  |  |

|---------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Addr0-31      | 1/0 | Address bus to communicate with the Micro Channel address bus.  Addr0 is the least significant bit (LSB) and Addr31 is the most significant bit (MSB). These lines must be buffered externally to meet minimum drive requirements of the Micro Channel. |  |  |  |

| MemAddrEn24   | I/O | Memory address enable 24 bits. This line indicates when an extended address is used on the bus. When <b>MemAddrEn24</b> is active this indicates that an unextended 24 bit address for less than or equal to 16 Mbytes is being presented.              |  |  |  |

| notCardSelFbk | 0   | Card selected feedback. When the controlling master (e.g. i386 processor) addresses the G201, the G201 drives <b>notCardSelFbk</b> active to indicate its presence at the address specified.                                                            |  |  |  |

| notAddrDecLat | I/O | Address latch bus signal.                                                                                                                                                                                                                               |  |  |  |

| MemnotiO      | I/O | Pin to distinguish between a memory cycle and an input/output (I/O) cycle. When <b>MemnotlO</b> is high a memory cycle is in progress, when low an I/O is in progress.                                                                                  |  |  |  |

| AddrBufDir    | 0   | This pin controls the direction of external buffers between the IMS G201 host address bus pins and the micro channel bus. Active low indicates drive towards the host system bus, and active high towards the IMS G201.                                 |  |  |  |

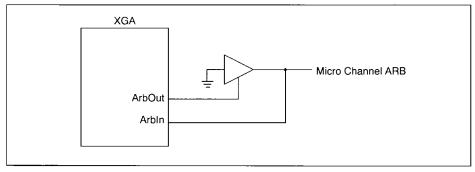

### Micro Channel Arbitration bus

| Pin name      | I/O | Signal description                                                                                                                                                                                                                                                                                           |  |  |  |

|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ArbOut0-3     | 0   | These outputs drive the Micro Channel arbitration bus priority levels. These signals must be buffered by an open collector device to meet Micro Channel requirements.                                                                                                                                        |  |  |  |

| Arbin0-3      | 1   | These inputs are the Arbitration bits from the Micro Channel bus to enable the IMS G201 to control the bus in bus master mode.                                                                                                                                                                               |  |  |  |

| ArbGrant      | 1   | Arbitration grant signal.                                                                                                                                                                                                                                                                                    |  |  |  |

| notPreemptOut | 0   | This is the output portion of the Micro Channel —PREEMPT signal. This signal must be buffered by an open collector or three-state device to comply with Micro Channel convention.                                                                                                                            |  |  |  |

| notPreemptin  | J   | notPreemptIn is logically tied directly to the Micro Channel —PRE-EMPT signal. This signal in conjunction with notPreemptOut mimics the open collector driver specified for —PREEMPT in the Micro Channel definition. It is used when the IMS G201 is operating in burnaster mode.                           |  |  |  |

| notBurst      | 0   | This signal indicates to the central arbitration control point the extended use of the channel for transferring a block of data. This type of data transfer is called a burst cycle. This signal must be buffered by an open collector or three-state device to comply with the Micro Channel specification. |  |  |  |

#### Micro Channel Data bus

| Pin name        | I/O | Signal description                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Data0-31        | I/O | Data bits 0 to 31. <b>Data0</b> is the LSB and <b>Data31</b> is the MSB. The data pins are shared by the VRAM random data port and the Micro Channel data bus. They may connect directly to the VRAM but must be isolated from the Micro Channel by suitable bidirectional three-state drivers.                                                                                                                                           |  |  |  |

| Data8-11        |     | Data8-11 are also used to carry an address for external registers.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Data8-26        |     | Data8-26 are also used to carry an address for external memory (typically EPROM). Data21-26 correspond to bits 0-5 in the ROM paging register in Micro Channel bus mode.                                                                                                                                                                                                                                                                  |  |  |  |

| Data27          |     | Data27 (with notDataStrobe1) is also a strobe qualifier for chip configuration data.                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Data28          |     | <b>Data28</b> is also a strobe qualifier for writes to external memory. A low on this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external memory write.                                                                                                                                                                                                                                                            |  |  |  |

| Data29          |     | <b>Data29</b> is also a strobe qualifier for reads from external memory. A low on this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external memory read.                                                                                                                                                                                                                                                            |  |  |  |

| Data30          |     | <b>Data30</b> is also a strobe qualifier for external register writes. A low of this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external register write.                                                                                                                                                                                                                                                           |  |  |  |

| Data31          |     | <b>Data31</b> is also a strobe qualifier for external register reads. A low on this signal when the <b>notDataStrobe1</b> pin pulses low indicates an external register read.                                                                                                                                                                                                                                                             |  |  |  |

| DataBufDir      | 0   | This signal controls the direction of an external bidirectional three state transceiver isolating the Micro Channel data bus from the shared VRAM data bus. A low indicates drive towards the Micro Channel data bus. A high indicates drive towards the IMS G201 and VRAM.                                                                                                                                                               |  |  |  |

| notDataBufOE0-3 | 0   | A low on this signal puts the external Micro Channel data bus isolation buffer in the active state; a high puts it in high impedance state. Bit 0 controls data bus bits 0:7, bit 1 controls data bus bits 8:15, bit 2 controls data bus bits 16:23, and bit 3 controls data bus bits 24:31.                                                                                                                                              |  |  |  |

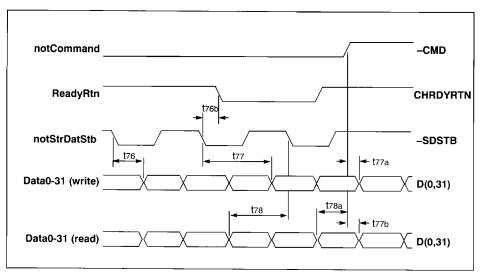

| notCommand      | 1/0 | This signal is used to define when data is valid on the data bus.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Ready           | 0   | This normally active signal is pulled inactive (not ready) by the IMS G201 to allow additional time to complete a Micro Channel operation.                                                                                                                                                                                                                                                                                                |  |  |  |

| ReadyRtn        | 1   | A positive AND of all the Micro Channel CD CHRDY (Ready) signals.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| CoProcStat      | 0   | The <b>CoProcStat</b> pin is an external output of 7 (BSY) of the External Polling Register (offset 11 in coprocessor address space). This provides an additional method of reading the coprocessor busy status without halting its operation (as would happen if the status was read via the coprocessor data bus). <b>CoProcStat</b> should be connected through a tri-state buffer to <b>Data15</b> (or <b>Data7</b> on an 8 bit bus). |  |  |  |

| notCoProcStatOE | 0   | This pin provides the enable input for the tri-state buffer that connects the <b>CoProcStat</b> pin to bit 15 of the host data bus (host side of the data buffer's transceivers).                                                                                                                                                                                                                                                         |  |  |  |

| Pin name       | 1/0 | Signal description                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                    |            |            |              |   |  |

|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|---|--|

| notStatus0-1   | I/O | define<br>memo                                                                                                                                                                                                                                                         | Status bits 0 and 1. These lines indicate the start of a cycle and also define the type of cycle. Used in conjunction with the <b>MemnotIO</b> pin memory read/write operations are distinguished from I/O read/write operations as defined below: |            |            |              |   |  |

|                | 1   |                                                                                                                                                                                                                                                                        | MemnotlO                                                                                                                                                                                                                                           | notStatus0 | notStatus1 | Function     | ] |  |

|                |     |                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                  | 0          | 1          | I/O write    |   |  |

|                |     |                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                  | 1          | 0          | I/O read     |   |  |

|                |     |                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                  | 0          | 1          | memory write |   |  |

|                |     |                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                  | 1          | 0          | memory read  |   |  |

| notDSize16Rtn  | 1   | Data size 16 bits return. This signal is provided to allow the control-<br>ling master to monitor the data size information.                                                                                                                                           |                                                                                                                                                                                                                                                    |            |            |              |   |  |

| notDSize32Rtn  | 1   | Data size 32 bits return. This signal is provided to allow the controlling master to monitor the data size information.                                                                                                                                                |                                                                                                                                                                                                                                                    |            |            |              |   |  |

| notSysByteHiEn | I/O | System byte high enable. This line indicates and enables transfer of data on the high byte of the data bus ( <b>Data8-15</b> ) and is used with <b>Addr0</b> to distinguish between high byte transfers ( <b>Data8-15</b> ) and low byte transfers ( <b>Data0-7</b> ). |                                                                                                                                                                                                                                                    |            |            |              |   |  |

| notByteEn0-3   | I/O | Byte e                                                                                                                                                                                                                                                                 | Byte enables (used in conjunction with 32-bit bus cycles).                                                                                                                                                                                         |            |            |              |   |  |

## Micro Channel Interrupt control

| Pin name | I/O | Signal description |

|----------|-----|--------------------|

| notIRQ   | 0   | Interrupt request  |

## Micro Channel Setup and control

| Pin name I/O Signal description |   | Signal description                                                                 |

|---------------------------------|---|------------------------------------------------------------------------------------|

| notRefresh                      |   | This signal is used to indicate a memory refresh operation is in progress.         |

| notChannelCheck                 | 1 | This signal is a general error condition. It can be driven active by any resource. |

| notSetup                        | 1 | Micro Channel bus setup                                                            |

| Reset                           | 1 | Bus reset                                                                          |

| Clk                             | 1 | Clock                                                                              |

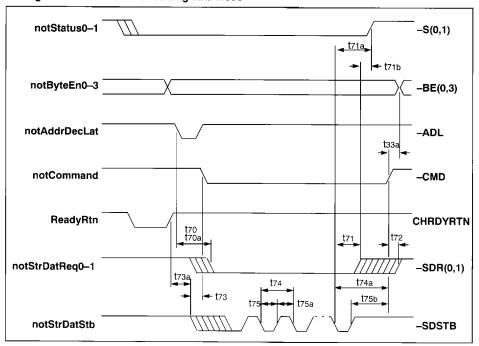

## Micro Channel Streaming mode

| Pin name                                                                                                | I/O                                                                                                                                                                    | Signal description                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| notStrDatStb                                                                                            | O Connects to the Micro Channel –SD STB signal. notStrD driven by the IMS G201 (acting as the bus master) and so clock, delimiting words in a streaming data transfer. |                                                                                                                                                                                                 |

| notStrDatReq0-1  I Connects to the Micro Channel –SDR(0,1) en by the bus slave, following the activatio |                                                                                                                                                                        | Connects to the Micro Channel –SDR(0,1) signals. –SDR(0,1) are driven by the bus slave, following the activation of the Address Data Latch signal, to indicate that it supports streaming data. |

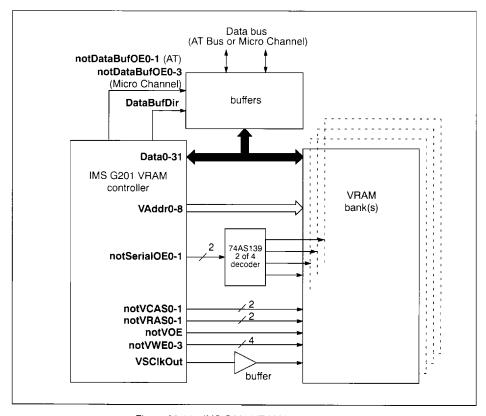

## 22.2.2 VRAM interface

| Pin name             | I/O | Signal description                                                                                                                                                                                                                             |  |  |

|----------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

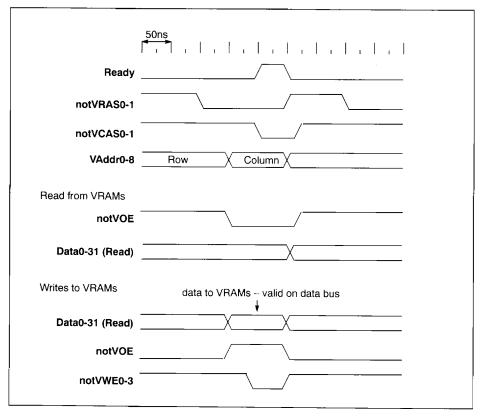

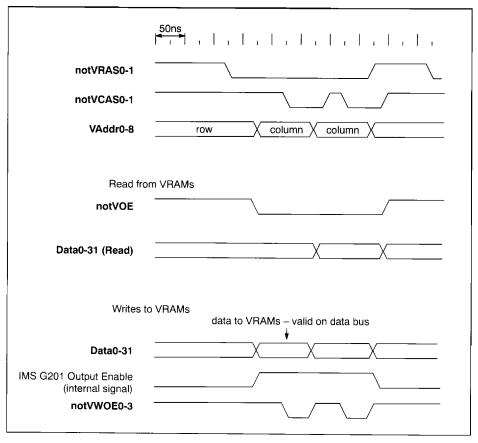

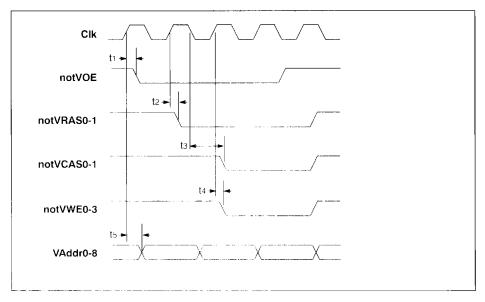

| VAddr0-8             | 0   | These pins have different functions depending on the operation.                                                                                                                                                                                |  |  |

|                      |     | VAddr0-8 carry the row and column addresses to the VRAMs to be strobed by the appropriate RAS or CAS signal.                                                                                                                                   |  |  |

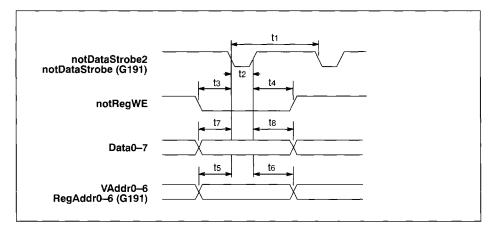

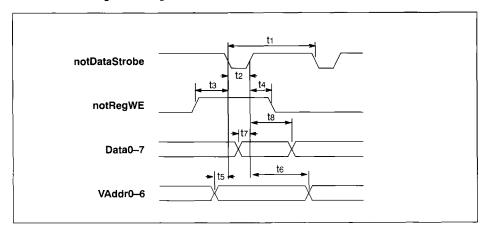

| VAddr0-6             |     | VAddr0-6 lines are also used to send the address of the IMS G191 parameter registers to the IMS G191.                                                                                                                                          |  |  |

| VAddr8 /<br>notRegWE |     | VAddr8 is also used as a notRegWE pin to indicate to the IMS G191 whether the IMS G191 addressed register is being written to or read from. A high on this signal indicates a read from the register, a low indicates a write to the register. |  |  |

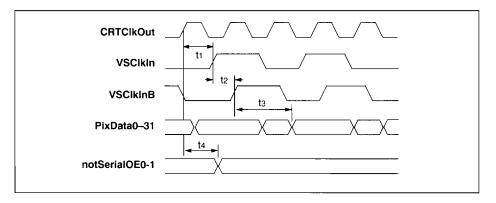

| notSerialOE0-1       | 0   | Serial output enable strobes for multiplexing data from any one of four VRAM serial ports.                                                                                                                                                     |  |  |

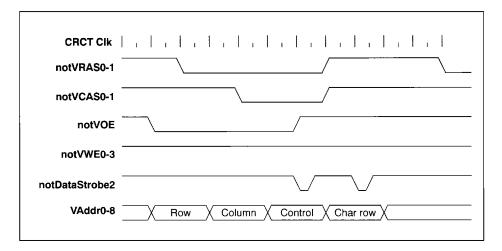

| notVCAS0-1           | 0   | VRAM column address strobes.                                                                                                                                                                                                                   |  |  |

| notVRAS0-1           | 0   | VRAM row address strobes.                                                                                                                                                                                                                      |  |  |

| notVWE0-3            | 0   | Write Enable control for VRAM data. A low indicates a write operation. Bit 0 controls <b>Data 0-7</b> Bit 1 controls <b>Data 8-15</b> Bit 2 controls <b>Data 16-23</b> Bit 3 controls <b>Data 24-31</b>                                        |  |  |

| notVOE               | 0   | This signal connects to the <b>TRANSFER/OUTPUT ENABLE</b> of the VRAM. It enables the VRAM outputs at the appropriate times as well as defining serializer load cycles to the VRAM.                                                            |  |  |

| VSCIkOut             | 0   | This signal causes shift cycles on the VRAM serial ports. The IMS G201 controls the shift timing based on bits per pixel and prescaling of the master clock source from the IMS G191.                                                          |  |  |

## 22.2.3 IMS G191 interface

| Pin name              | I/O | Signal description                                                                                                                                                                                                                                                                                                                    |

|-----------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

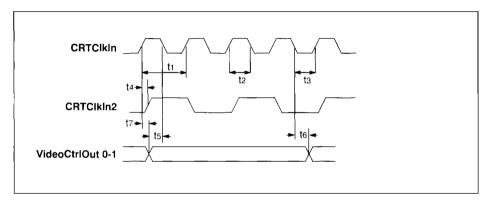

| VideoCtrlOut0-1       | 0   | These pins represent the horizontal scan line state. Table 22.8 (page 502) shows the decoding of the bits.                                                                                                                                                                                                                            |

| notDataStrobe2        | 0   | This signal is used to strobe data from the IMS G201 to the IMS G191. It is used to communicate register contents programmed by the host processor and decoded in the IMS G201. A low sent on this pin to the IMS G191 indicates that the IMS G191 should perform the action defined by the <b>VAddr0-6</b> and <b>notRegWE</b> pins. |

| CRTCIkin<br>CRTCikin2 | 1   | CRTC clocks. These clocks are sourced by the IMS G191 and are used by the IMS G201 to generate all video related timings.                                                                                                                                                                                                             |

| MonHSync              | 0   | This is the monitor horizontal sync pulse. It can be programmed to pulse either positive or negative. It enters the high impedance state when <b>MonSyncOE</b> is high.                                                                                                                                                               |

| MonVSync              | 0   | This is the monitor vertical sync pulse. It can be programmed to pulse either positive or negative. It enters the high impedance state when <b>MonSyncOE</b> is high.                                                                                                                                                                 |

| MonSyncOE             | 1   | A low on this input will cause the <b>MonHSync</b> and <b>MonVSync</b> to three-state their outputs.                                                                                                                                                                                                                                  |

# 22.2.4 Supplies

| Pin name | I/O | ignal description |  |  |  |  |

|----------|-----|-------------------|--|--|--|--|

| VDD      |     | VDD               |  |  |  |  |

| GND      |     | GND               |  |  |  |  |

## 22.2.5 Miscellaneous

| Pin name I/O Si |   | Signal description                                                                                                     |  |  |  |

|-----------------|---|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| notDataStrobe1  | 0 | This signal strobes low to cause reads and writes to/from the external memory (typically PROM) and external registers. |  |  |  |

| HoldToGND       |   | Must be connected to GND                                                                                               |  |  |  |

| HoldToVDD       |   | Must be connected to VDD                                                                                               |  |  |  |

| N/C             |   | No Connect (this refers to unused pins). Do not wire this pin.                                                         |  |  |  |

## 22.3 Coprocessor

The coprocessor provides hardware drawing assist functions. These functions can be performed on graphics data in both video memory and system memory.

The coprocessor updates memory independent of the system microprocessor. A virtual memory feature allows the coprocessor to perform linear to physical address conversion in a manner consistent with the paging operation in the 80X86 processor family. The instructions are written to a set of memory-mapped registers (see Section 22.7.1): the coprocessor then executes the drawing function.

The coprocessor functions are summarized below:

- Pixel Block Transfer (PxBlt) This function provides a four term block transfer capability of an

entire bit map, or part of a bit map, from one location to another. This transfer can be: within video

memory, within system memory, or between system and video memory.

- Line draw This function draws lines, with a programmable style, into a bit map in video memory

or system memory.

- Area fill This function fills an outlined area with a programmable pattern. It can be performed

on an area outline in video or system memory.

- Logical and arithmetic pixel mixes These functions provide logical and arithmetic operators that

can be used against data in video or system memory.

- Scissoring This function provides a rectangular mask function, which can be used instead of the mask map.

- Map masking This function provides control over updates to each pixel for all drawing functions.

- X, Y addressing This function allows a pixel to be specified by its X and Y coordinates within

a pixel map, instead of its linear address in memory.

- Virtual addressing When enabled, this function causes the coprocessor function to utilize a page table of a form identical to the 80X86 processor family page table. A translation look aside buffer is kept on chip to speed conversion of addresses.

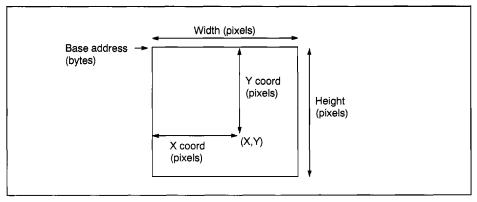

## 22.3.1 Pixels, pixel maps and X, Y addressing

The drawing coprocessor works on pixels within pixel maps. A pixel map is an area of memory at a given address (the base address) with a defined width, height and pixel format. Pixels can have 1, 2, 4, 8 or 16 bits. The pixels can be ordered within bytes in one of two ways: left to right or vice versa. The XGA allows pixel maps of any arbitrary size up to 4096×4096 pixels.

The coprocessor is programmed using X, Y coordinates that are automatically converted into linear memory addresses (using the defined width and pixel size) before accessing the physical memory (see Figure 22.3).

Figure 22.3 Pixels are addressed using X,Y coordinates within pixel maps

The programmer can define up to four pixel maps at one time. Three maps (A, B and C) are general purpose; the other is always used as the mask map. When starting a drawing operation, the programmer tells the coprocessor which maps are to be used as the source, the pattern, and the destination. In this way, map A, for example, could be the display pixel map. It could then be used as source, destination, or both, without having to move the pixel map parameters from one set of registers to another.

### 22.3.2 Pixel maps in system memory

A certain amount of space is available in the non-displayed (off-screen) areas of video memory. This is often used for storing fonts and off-screen pixel maps. GUIs, however, make extensive use of off-screen pixel maps (for example, for pull-down menus), and may be called upon to use fonts that are too large to fit in off-screen video memory. When the off-screen video memory is full, the GUI device driver can use normal system memory. With previous adapters, this generally meant processing the pixels using the system processor which is slow compared to special drawing hardware, especially if the operation is not a simple copy. It also ties up the processor and prevents it from preparing for the next drawing operation.

The XGA uses bus-mastership on the bus (AT bus or Micro Channel) to overcome these problems. The drawing coprocessor's power can be used on pixel data anywhere in system or video memory.

To support paged memory environments, where the paging unit in the 80386 or 80486 is turned on, the XGA includes its own paging unit, using page tables of the same form. The XGA can operate using the main page tables used by the operating environment (with its cooperation), or on tables built by device drivers or applications themselves.

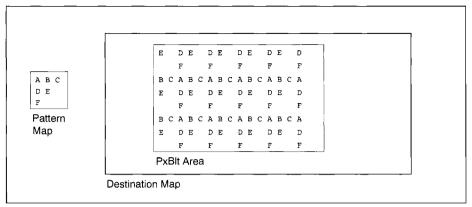

#### 22.3.3 Pixel block transfer (PxBlt)

The PxBlt function works with four operands: the source, the pattern, the destination and mask. The source may come from a pixel map to copy data, or from color registers to set the destination to a particular color. The pattern may come from a pixel map, indirectly from the source, or it may be disabled.

For each pixel, the source and destination are combined using a Mix function selected by the 1-bit-per-pixel pattern. A 0 in the pattern selects the background mix, and a 1 selects the foreground mix. A full set of logical mixes is provided, supporting OS/2 and Windows Raster Operations (ROPs), with a selection of arithmetic mixes. Fast text drawing is crucial to windowing environments and other interactive applications. The pattern can select between foreground and background colors, allowing a 1-bit-per-pixel text font in the pattern map to be rapidly expanded to colored characters in the destination.

The pattern and the source have another common feature. The X, Y addresses for these maps automatically wrap when they reach either side or top and bottom. This allows a small pattern to be "tiled" over a large area in the destination using a single operation (see Figure 22.4).

Figure 22.4 Patterns are automatically tiled

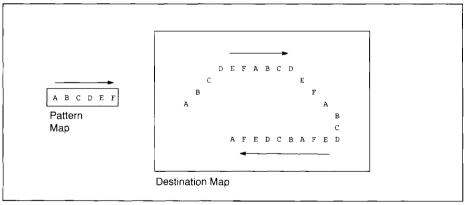

#### 22.3.4 Lines

The coprocessor draws lines using the Bresenham line-drawing algorithm. All pixels of a line can be drawn, or the first or last pixel can be suppressed to draw poly lines correctly.

As with PxBlt, the pattern and source X, Y coordinates wrap at the edge of the maps. Line drawing, however, is different. While the X, Y coordinates of the destination move along the required path, the coordinates in the source and pattern move horizontally - left to right only. A simple 1-pixel-high pattern is drawn along the line, as shown in Figure 22.5.

Figure 22.5 Line patterns are also pixel maps

Short lines can be drawn with simpler commands using 'short stroke vectors', line segments up to 16 pixels long, and in one of eight directions (the X axis, the Y axis and the 45° lines in between).

#### 22.3.5 Area fill

The coprocessor allows arbitrary areas to be filled rapidly. The area is defined by an outline drawn in a 1-bit-per-pixel map. The outline is drawn using special versions of the line drawing functions (including short strokes).

When the outline is complete, a special PxBlt fills the inside of the defined figure. A parity fill algorithm is used, where a rectangle is scanned from left to right, starting from outside the figure, and alternately moving in and out of the figure as each successive boundary is crossed. The area can also be filled with a pattern if required.

#### 22.3.6 Scissoring and map masking

The coprocessor can, under programmer control, automatically 'scissor' (that is, not draw) pixels that an operation attempts to draw outside a specified area. That area can be a simple rectangle, or a more complex shape defined in a pixel map (the mask map), with a pattern of 1's and 0's (1 allows the corresponding pixel in the destination to be changed; a 0 protects that pixel). This function can be used, for example, when drawing into a background window that is partially obscured by other windows.

#### 22.3.7 State save and restore

In a multi-tasking environment, the system processor must change tasks from time to time. When changing tasks, the state of the current task must be saved so that it can be restored and continued at a later time. The state of the coprocessor can be rapidly saved and restored, making multi-tasking operation possible.

The coprocessor's operation can be suspended at any time and later resumed. Once suspended, the entire state of the coprocessor, including internal registers not visible in the address space, can be saved to memory by reading repeatedly from two 32 bit I/O ports. The 80X86 string input (INS) instruction can be used for this. The state is restored by writing the previously saved state data back into the same ports (using the OUTS instruction). Once resumed, the operation will continue from exactly the point at which it was suspended.

## 22.4 System bus interface

This portion of the IMS G201 display controller provides control of the interface between the video subsystem and the system microprocessor. It decodes the addresses for VGA and XGA I/O registers and the memory addresses for the coprocessor memory-mapped registers and video memory. It also provides controls that allow access to: registers in the IMS G191 serializer palette DAC, data in the sprite memory, ROM, and external registers.

The system bus interface is designed to interface to an AT bus or a Micro Channel. For interfacing to an AT bus it supports: both slave and master operations for a 16 bit interface; slave operations only for an 8 bit interface. For interfacing to a Micro Channel it supports both slave and master operations for a 32 bit or a16 bit interface. Refer to Section 22.10.1 detailing the hardware interfaces for further information on the system bus interface.

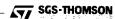

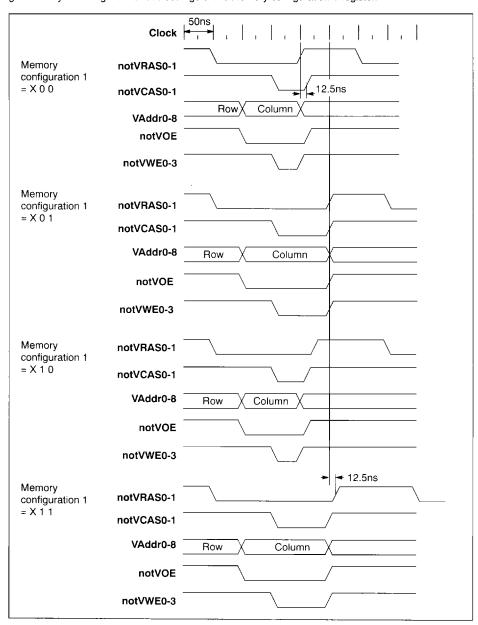

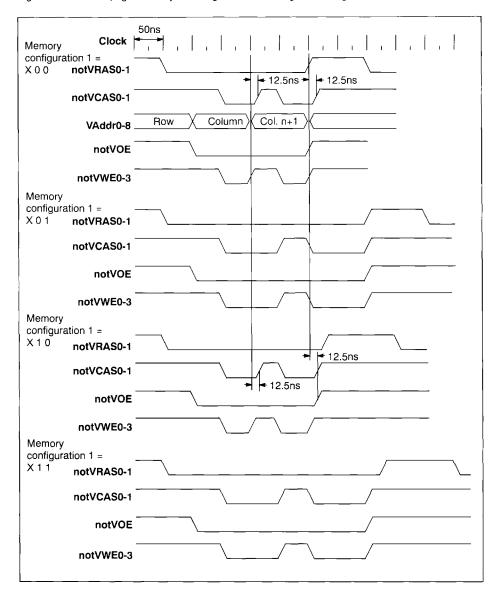

### 22.5 CRT and VRAM controller

The memory controller controls accessing of the VRAM. It supports memory either 16 or 32 bits wide. The minimum implementation is 512 Kbytes.

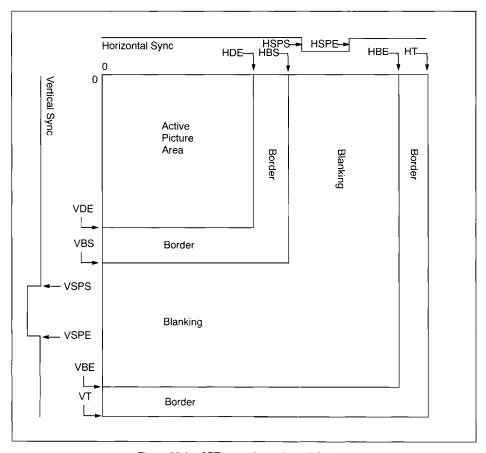

The CRT controller (CRTC) generates all the timing signals required to drive the serializer and the display. It consists of two counters, one for horizontal parameters, and one for vertical parameters, and a series of registers. The counters run continuously, and when the count value reaches that specified in one of the associated registers, the event controlled by that register occurs.

## 22.5.1 Extended mode CRT controller register interpretations

A pictorial representation of the function of each of the CRT controller registers is shown in Figure 22.6.

Figure 22.6 CRT controller register definitions

|      | Horizontal scan registers            | Vertical scan registers |                                    |  |

|------|--------------------------------------|-------------------------|------------------------------------|--|

| HT   | Horizontal total register            | VT                      | Vertical total register            |  |

| HDE  | Horizontal display end register      | VDE                     | Vertical display end register      |  |

| HBS  | Horizontal blanking start register   | VBS                     | Vertical blanking start register   |  |

| HBE  | Horizontal blanking end register     | VBE                     | Vertical blanking end register     |  |

| HSPS | Horizontal sync pulse start register | VSPS                    | Vertical sync pulse start register |  |

| HSPE | Horizontal sync pulse end register   | VSPE                    | Vertical sync pulse end register   |  |

Table 22.1 Registers which control a horizontal and a vertical scan of the display

The XGA can be programmed to inform the host processor of the start and the end of the Active Picture Area using a system interrupt. An enable and a status bit exist for each interrupt.

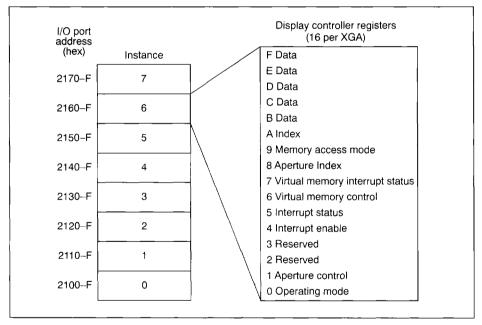

# 22.6 XGA I/O-mapped and memory-mapped registers

XGA is controlled using a combination of I/O-mapped and memory-mapped registers. I/O-mapped registers are those that appear in the I/O address space of an 80X86 processor, and are accessed using IN, OUT, or other I/O instructions. Memory-mapped registers appear in the memory address space of an 80X86 processor, and are accessed using standard memory operations with all the available combinations of registers and addressing modes. In addition, many I/O-mapped registers are indexed (that is, the register is selected using an index in one I/O port, and the data for all indexed registers is written through a second I/O port). This technique, used also by the VGA, reduces the I/O address space required.

Memory-mapped registers are generally used to control the drawing coprocessor, where frequent access requires good performance. I/O-mapped registers (indexed and direct) are used for the remainder (mainly setup registers, where performance is less important). Table 22.2 shows the XGA direct access I/O registers.

| I/O port<br>address                  | Register                        | Read/<br>Write | Description                                                                                                                                                                                                 |  |

|--------------------------------------|---------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 21x0                                 | Operating mode                  | R/W            | Defines display mode (VGA, 132 or XGA)                                                                                                                                                                      |  |

| 21x1                                 | Aperture control                | R/W            | Controls a 64K aperture through which the XGA memory can be accessed in the system address space. This window gives real mode applications and operating systems a means of accessing the XGA video memory. |  |

| 21x2                                 |                                 |                | Reserved                                                                                                                                                                                                    |  |

| 21x3                                 |                                 |                | Reserved                                                                                                                                                                                                    |  |

| 21x4                                 | Interrupt enable                | R/W            | Contains bits to enable/disable the interrupt conditions that can be generated by the subsystem.                                                                                                            |  |

| 21x5                                 | Interrupt status                | R/W            | Indicates the interrupt status bits that can be generated by the subsystem and used to reset the corresponding interrupts.                                                                                  |  |

| 21x6                                 | Virtual memory control          | R/W            | This register is directly mapped to the I/O address space.                                                                                                                                                  |  |

| 21x7                                 | Virtual memory interrupt status | R/W            | This register is directly mapped to the I/O address space.                                                                                                                                                  |  |

| 21x8                                 | Aperture index                  | R/W            | Used to provide address bits to the video memory when the aperture in system address space being used is smaller than the amount of video memory installed.                                                 |  |

| 21x9                                 | Memory access mode              | R/W            | Controls pixel ordering when the video memory is being accessed by the system (not the coprocessor). Intel or Motorola order can be selected. This register also controls the number of bits per pixel.     |  |

| 21xA                                 | Index                           | R/W            | Selects which indexed Extended Graphics Mode register is accessed when any address (base+B) to (base+F) is read or written.                                                                                 |  |

| 21xB<br>21xC<br>21xD<br>21xE<br>21xF | Data                            | R/W            | These registers are used when reading and writing to the register indexed by the Index register (21xA). The read/write operation can be of byte, word, or double-word size using these data registers.      |  |

Table 22.2 XGA direct access I/O registers

Multiple XGA adapters (multiple instances) can be used in a system. Each instance has an instance number and has its registers mapped at different addresses. The memory-mapped registers are located at some point within the address range C0000 and DFFFF. The precise location is set by a system dependent configuration process, such as the PS/2 Micro Channel auto-configuration.

It is recommended that instance 0 is not used on AT bus systems, as for some implementations this board number can cause bus conflicts. When using instance 0 on Micro Channel bus systems do not allow the 4MByte video memory aperture to start at address 0xxx, as this will conflict with DOS. Similarly when using instance 7 on Micro Channel bus systems do not allow the 4MByte video memory aperture to reside at the top of the system address space as this conflicts with some systems' BIOS RAM re-map.

When multiple XGA subsystems are installed in a system, the memory-mapped registers for all instances can be mapped within the same 1 Kbyte block of address space. The allocation of addresses is the responsibility of the system configuration process, which ensures that there is no conflict between installed adapters (XGA or others).

Figure 22.7 illustrates how the I/O registers are located. Base address of the sixteen I/O registers of an XGA is 21x0, where x is the instance number. Figure 22.7 shows instance 6.

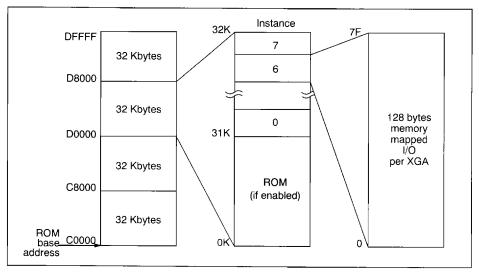

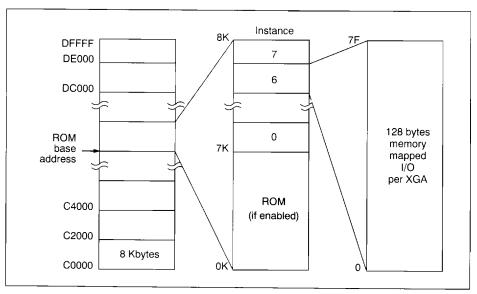

Figures 22.8 and 22.9 illustrate how the memory-mapped registers are located for an AT bus and a Micro Channel bus system respectively. These figures show instance 6.

Figure 22.7 I/O port addressing of XGA registers

#### AT bus system memory-mapped registers

The memory mapped registers occupy 128 bytes of memory in the last 1 Kbyte of a 32 Kbyte address space. This may reside on a 32 Kbyte boundary anywhere between the address range C0000 and DFFFF. The purpose of having a 32 Kbyte region is that the first 31 Kbytes is required for a full BIOS held in the adaptor ROM. The motherboard (planar) implementation of the XGA does not require its own ROM, as the main motherboard ROMs contain all the necessary information, such as XGA initialization code. Adaptor options allow the specification of the BIOS ROM base address and the XGA instance number determines the location of the 128 bytes within the upper 1 Kbyte address space.

Figure 22.8 Memory mapped addressing of XGA registers for AT bus system

### Micro Channel system memory-mapped registers

Base address of the memory-mapped registers of an XGA is (ROM Base address) + 7K + (128×instance number). Figure 22.9 shows instance 6.

Figure 22.9 Memory mapped addressing of XGA registers for Micro Channel system

#### **IMS G201**

Traditionally, display adapters such as the VGA and the 8514/A have been controlled through registers mapped into the 80X86 I/O address space. Memory-mapped registers have been introduced in the XGA for controlling the drawing coprocessor, where accesses are frequent and good performance is essential.

The I/O address space in the 80X86 is limited to 64 Kbytes, so individual adapters can only use a restricted number of addresses (to avoid possible conflicts between adapters). When the adapter contains many registers (typical of a display controller), indexed register addressing schemes are often used, as noted above. Memory address space is much larger (1 Mbyte minimum in real mode), so adapters with memory-mapped registers can avoid using indexing, thus allowing direct access to all registers, and reducing code space and execution time.

When the 80386 is running in Protected mode, the processor normally checks I/O accesses by applications to ensure they are allowed. It reads the I/O Permission Bitmap, a process that adds twenty cycles to each individual I/O access. Memory-mapped registers avoid this overhead, reducing to one-tenth the time taken to start many graphics operations.

Another advantage relates to multiple display adapters. Each instance of the XGA has a different set of register addresses, as shown earlier. Software must be able to run with any possible set. The 80X86 allows base-plus-offset addressing for memory accesses, using a segment register and an immediate or register-based offset. The software would typically set the segment register to point to the first address of the memory-mapped registers, and then have immediate pointers to specific registers. I/O addresses, on the other hand, are always contained in the DX register of an 80X86 processor; no form of base-plus-offset addressing is possible. For I/O-mapped registers, DX must be calculated correctly before each access, taking time and code space.

## 22.7 IMS G201 register reference guide

The following section lists all the IMS G201 registers with a brief description of the function of each register. The complete register bit format is not included in this datasheet, this is defined in the XGA Software Programmer's Guide, document number 72 OEK 258 01. All addresses and indexes are in hexadecimal. Unspecified registers, or registers marked as 'RESERVED', are reserved and must not be written to or read from.

## 22.7.1 IMS G201 memory mapped registers

The IMS G201 coprocessor is controlled using a bank of 128 memory mapped registers. Table 22.3 shows the register memory map for the IMS G201 coprocessor in Intel register format. The register descriptions are given in Table 22.4.

| Byte 3      | Byte 2                                      | Byte 1                           | Byte 0             |    |  |

|-------------|---------------------------------------------|----------------------------------|--------------------|----|--|

|             | Page Directory                              | Base Address                     |                    | 0  |  |

|             | Current Virt                                | ual Address                      |                    | 4  |  |

| RESE        | RVED                                        | Auxiliary Coprocessor<br>Control | RESERVED           | 8  |  |

| RESE        | RVED                                        | State B len                      | State A len        | С  |  |

| RESERVED    | Pixel Map Index Coprocessor Control RESERVE |                                  | RESERVED           | 10 |  |

|             | Pixel Map n                                 | Base Pointer                     |                    | 14 |  |

| Pixel Mar   | n Height                                    | Pixel Ma                         | p n Width          | 18 |  |

|             | RESERVED                                    |                                  | Pixel Map n Format | 10 |  |

| RESE        | RVED                                        | Bresenham                        | Error Term         | 20 |  |

| RESE        | RVED                                        | Bresen                           | ham K1             | 24 |  |

| RESE        | RVED                                        | Bresen                           | ham K2             | 28 |  |

|             | Direction                                   | on Steps                         |                    | 20 |  |

|             | RESE                                        | RVED                             |                    | 30 |  |

|             | RESE                                        | RVED                             | <u> </u>           | 3. |  |

| RESERVED    |                                             |                                  |                    |    |  |

| RESERVED    |                                             |                                  |                    |    |  |

|             | RESE                                        | RVED                             |                    | 40 |  |

|             | RESE                                        | RVED                             |                    | 44 |  |

| RESERVED    | Dest Color Comp.<br>Cond.                   | Bgd Mix                          | Fgd Mix            | 48 |  |

|             | Destination Cold                            | or Compare Value                 |                    | 40 |  |

|             | Pixel E                                     | Bit Mask                         |                    | 50 |  |

|             | Carry Ch                                    | nain Mask                        |                    | 5  |  |

|             | Foreground (                                | Color Register                   |                    | 58 |  |

|             | Background                                  | Color Register                   |                    | 50 |  |

| Operation ( | Dimension 2                                 | Operation Dimension 1            |                    |    |  |

|             | RESE                                        | RVED                             |                    | 6  |  |

|             | RESE                                        | RVED                             |                    | 6  |  |

| Mask Map O  | rigin Y Offset                              | Mask Map Origin X Offset         |                    |    |  |

| Source N    | Map Y Adr                                   | Source Map X Adr                 |                    |    |  |

| Pattern N   | /lap Y Adr                                  | Pattern N                        | Map X Adr          | 7. |  |

| Dest. M     | ap Y Adr                                    | Dest. M                          | ap X Adr           | 78 |  |

|             | Pixel C                                     | peration                         |                    | 70 |  |

Table 22.3 IMS G201 coprocessor register memory map (Intel format)

| Off-<br>set | Register                           | Read/<br>Write | Description                                                                                                                                                                                                                                        |

|-------------|------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | Page Directory Base Address        | Write          | Contains a 20 bit pointer to the page in physical memory containing the current Page Directory for the current task.                                                                                                                               |

| 4           | Current Virtual Address            | Read           | Contains the faulting page address in the event of a 'Not Present' or 'Protection Interrupt' being flagged.                                                                                                                                        |

| 9           | Auxiliary Coprocessor Control      | Read           | Contains a duplicate status bit to the Coprocessor Busy bit (BSy, bit 7) of the Coprocessor Control register. The state of this bit is provided on the <b>CoProcStat</b> pin, enabling the busy status to be read without halting the coprocessor. |

| C<br>D      | State A len<br>State B len         | Read           | These registers return the length, in double words, of the two parts, A and B of the coprocessor state for save and restore.                                                                                                                       |