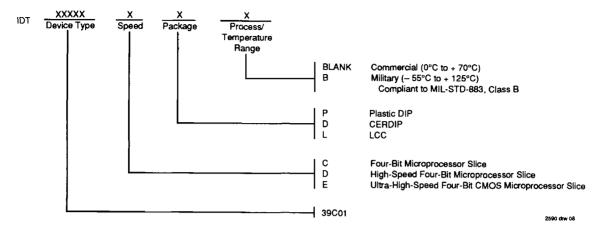

### 4-BIT CMOS MICROPROCESSOR SLICE

IDT39C01C IDT39C01D IDT39C01E

#### **FEATURES:**

- Low-power CEMOS™

- lcc (max.)Military: 35mACommercial: 30mA

#### Fast

- IDT39C01C meets 2901C speeds

- IDT39C01D 20% speed upgrade

- IDT39C01E 40% speed upgrade

- · Eight-function ALU

- Performs addition, two subtraction operations and five logic functions on two source operands

- Expandable

- Longer word lengths achieved through cascading any number of IDT39C01s

- · Four status flags

- Carry, overflow, negative and zero

- Pin-compatible and functionally equivalent to all versions of the 2901

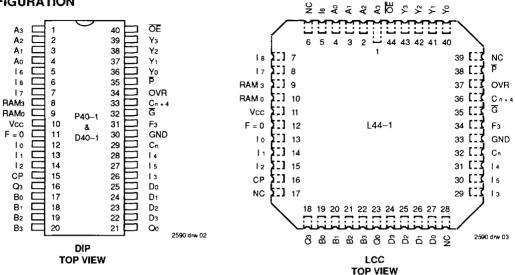

- · Available in 40-pin DIP and 44-pin LCC

- Military product available compliant to MIL-STD-883 and DESC Standard Military Drawing (SMD) 5962-88535

#### DESCRIPTION:

The IDT39C01s are high-speed, cascadable ALUs which can be used to implement CPUs, peripheral controllers and programmable microprocessors. The IDT39C01's microinstruction flexibility allows for easy emulation of most digital computers.

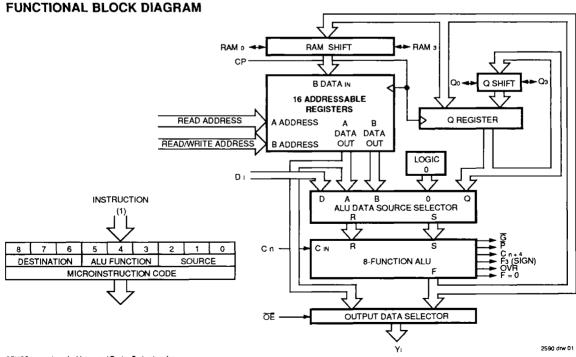

This extremely low-power yet high-speed ALU consists of a 16-word-by-4-bit dual-port RAM, a high-speed ALU and the required shifting, decoding and multiplexing logic. It is expandable in 4-bit increments, contains a flag output along with three-state data outputs, and can easily use either a ripple carry or full lookahead carry. The nine-bit microinstruction word is organized into three groups of three bits each and selects the ALU destination register, ALU source operands and the ALU function.

The IDT39C01 is fabricated using CEMOS™, a CMOS technology designed for high-performance and high-reliability. It is a pin-compatible, performance-enhanced, functional replacement for all versions of the 2901.

Military grade product is manufactured in compliance with the latest version of MIL-STD-883, Class B.

CEMOS is a trademark of Integrated Device Technology Inc.

**MILITARY AND COMMERCIAL TEMPERATURE RANGES**

**APRIL 1990**

### PIN CONFIGURATION

### PIN DESCRIPTIONS

| Ao - A3<br>Bo - B3<br>Io - I8<br>Do - D3<br>Yo - Y3 |     | the ALU will perform 1(3, 4, 5) and what data is to be deposited in the Q Register or the register file 1(6, 7, 8).  Four-bit direct data inputs which are the data source for entering external data into the device. Do is the LSB.                                                                                                                                                                                                                                                   |

|-----------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lo - la<br>Do - D3                                  | 1   | displayed through the B port. They also select the location into which new data can be written when the clock goes LOW.  Nine instruction control lines which determine what data source will be applied to the ALU I(0, 1, 2), what function the ALU will perform I(3, 4, 5) and what data is to be deposited in the Q Register or the register file I(6, 7, 8).                                                                                                                       |

| Do - D3                                             | 1   | the ALU will perform 1(3, 4, 5) and what data is to be deposited in the Q Register or the register file 1(6, 7, 8).  Four-bit direct data inputs which are the data source for entering external data into the device. Do is the LSB.                                                                                                                                                                                                                                                   |

|                                                     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Yo - Y3                                             | 0   | Four three-state output lines which when enabled display either the four outputs of the ALU or the data on the A                                                                                                                                                                                                                                                                                                                                                                        |

|                                                     |     | port of the register stack. This is determined by the destination code (6, 7, 8).                                                                                                                                                                                                                                                                                                                                                                                                       |

| F3                                                  | 0   | Most significant ALU output bit (sign-bit).                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| F = 0                                               | 0   | Open drain output which goes HIGH if the Fo - F3 ALU outputs are all LOW. This indicates that the result of an ALU operation is zero (positive logic).                                                                                                                                                                                                                                                                                                                                  |

| Cn                                                  | Ī   | Carry-in to the internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Cn+4                                                | 0   | Carry-out of the internal ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Q3<br>RAM3                                          | I/O | Bidirectional lines controlled by I(6, 7, 8). Both are three-state output drivers connected to the TTL-compatible CMOS inputs. When the destination code on I(6, 7, 8) indicates an up shift, the three-state outputs are enabled, the MSB of the Q Register is available on the Q3 pin and the MSB of the ALU output is available on the RAM3 pin. When the destination code indicates a down shift, the pins are the data inputs to the MSB of the Q Register and the MSB of the RAM. |

| Qo<br>RAMo                                          | I/O | Both bidirectional lines function identically to Q3 and RAM3 lines except they are the LSB of the Q Register and RAM.                                                                                                                                                                                                                                                                                                                                                                   |

| ŌĒ                                                  | I   | Output enable on which, when pulled HIGH, the Y outputs are OFF (high impedance). When pulled LOW, the Y outputs are enabled.                                                                                                                                                                                                                                                                                                                                                           |

| G, P                                                | 0   | Carry generate and carry propagate output of the ALU. These are used to perform a carry lookahead operation.                                                                                                                                                                                                                                                                                                                                                                            |

| OVR                                                 | 0   | Overflow. This pin is logically the Exclusive-OR of the carry-in and carry-out of the MSB of the ALU. At the most significant end of the word, this pin indicates that the result of an arithmetic two's complement operation has overflowed into the sign-bit.                                                                                                                                                                                                                         |

| СР                                                  | I   | Clock input. LOW-to-HIGH clock transitions will change the Q Register and the register file outputs. Clock LOW time is internally the write enable time for the 16 x 4 RAM which comprises the master latches of the register file. While the clock is LOW, the slave latches on the RAM outputs are closed, storing the data previously on the RAM outputs. Synchronous MASTER-SLAVE operation of the register file is achieved by this.                                               |

### **ALU SOURCE OPERAND CONTROL**

|          | Microcode |    |    |               | ource<br>ands |   |

|----------|-----------|----|----|---------------|---------------|---|

| Mnemonic | l2        | l1 | lo | Octal<br>Code | R             | s |

| AQ       | L         | L  | L  | 0             | Α             | Q |

| AB       | L         | L  | н  | 1             | Α             | 8 |

| ZQ       | L         | н  | L  | 2             | 0             | Q |

| ZB       | L.        | н  | Н  | 3             | 0             | В |

| ZA       | Н         | L  | L  | 4             | 0             | Α |

| DA       | Н         | L  | н  | 5             | D             | Α |

| DQ       | Н         | Н  | L  | 6             | D             | Q |

| DZ       | Н         | н  | Н  | 7             | D             | 0 |

#### 2590 tol 02

### **ALU FUNCTION CONTROL**

|          | Microcode |    |    |               |                 |        |

|----------|-----------|----|----|---------------|-----------------|--------|

| Mnemonic | ls        | 14 | l3 | Octal<br>Code | ALU<br>Function | Symbol |

| ADD      | L         | L  | L  | 0             | R Plus S        | R+S    |

| SUBR     | L         | L  | н  | 1             | S Minus R       | S-R    |

| SUBS     | L         | Н  | L  | 2             | R Minus S       | R-S    |

| OR       | L         | Н  | н  | 3             | RORS            | RVS    |

| AND      | н         | L  | L  | 4             | RANDS           | R۸S    |

| NOTRS    | Н         | L  | н  | 5             | R AND S         | R٨S    |

| EXOR     | Н         | н  | L  | 6             | R EX-OR S       | R⊽S    |

| EXNOR    | Н         | н  | Н  | 7             | R EX-NOR S      | RVS    |

2590 tbl 03

### **DEVICE ARCHITECTURE:**

The IDT39C01 CMOS bit-slice microprocessor is configured four bits wide and is cascadable to any number of bits (4, 8, 12, 16, etc.). Key elements which make up this four-bit microprocessor slice are: 1) the register file (16 x 4 dual-port RAM) with shifter; 2) ALU and 3) Q Register and shifter.

REGISTER FILE - RAM data is read from the A port as controlled by the 4-bit A address field input. Data, as defined by the B address field input, can be simultaneously read from the B port of the RAM. This same code can be applied to the A select and B select field with the identical data appearing at both the RAM A port and B port outputs, simultaneously. New data is written into the file (word) defined by the B address field of the RAM when activated by the RAM write enable. The RAM data input field is driven by a 3-input multiplexer that is used to shift the ALU output data (F). It is capable of shifting the data up one position, down one position or not shifting at all. The other inputs to the multiplexer are from the RAM3 and RAMo I/O pins. For a shift up operation, the RAM3 output buffer is enabled and the RAMo multiplexer input is enabled. During a shift down operation, the RAMo output buffer is enabled and the RAM3 multiplexer input is enabled. Four-bit latches hold the RAM data while the clock is LOW, with the A port output and B port output each driving separate latches. The data to be written into the RAM is applied from the ALU F output.

ALU — The ALU can perform three binary arithmetic and five logic operations on the two 4-bit input words S and R. The S input field is driven from a 3-input multiplexer and the R input field is driven from a 2-input multiplexer, with both having an inhibit capability. Both multiplexers are controlled by the lo, l1, l2 inputs. This multiplexer configuration enables the user to select various pairs of the A, B, D, Q and "0" inputs as source operands to the ALU. Microinstruction inputs (I3, I4, I5) are

used to select the ALU function. This high-speed ALU also incorporates a carry-in (Cn) input, carry propagate ( $\overline{P}$ ) output, carry generate ( $\overline{G}$ ) output and carry-out (Cn+4) all aimed at accelerating arithmetic operations by the use of carry look ahead logic. The overflow output pin (OVR) will be HIGH when arithmetic operations exceed the two's complement number range. The ALU data outputs (F0, F1, F2, F3) are routed to the RAM, Q Register inputs and the Y outputs under control of the I6, I7, Is control signal inputs. The MSB of the ALU is output as F3 so the user can examine the sign-bit without enabling the three-state outputs. An open drain output, F = 0, is HIGH when F0 = F1 = F2 = F3 = 0 so the user can determine when the ALU output is zero by wire-ORing these outputs together.

Q REGISTER — The Q Register is a separate 4-bit file intended for multiplication and division routines and can also be used as an accumulator or holding register for other types of applications. It is driven from a 3-input multiplexer. In the no-shift mode, the multiplexer enters the ALU data into the Q Register. In either the shift-up or shift-down mode, the multiplexer selects the Q Register data appropriately shifted up or down. The Q shifter has two ports, Qo and Q3, which operate comparably to the RAM shifter. They are controlled by the I6, I7, I8 inputs.

The clock input of the IDT39C01 controls the RAM, Q Register and A and B data latches. When enabled, the data is clocked into the Q Register on the LOW-to-HIGH transition. When the clock is HIGH, the A and B latches are open and pass data that is present at the RAM outputs. When the clock is LOW, the latches are closed and retain the last data entered. When the clock is LOW and RAM EN is enabled, new data will be written into the RAM file defined by the B address field.

### ALU DESTINATION CONTROL(1)

|          | Microcode |    |    | RAM<br>Function |       | Q Register<br>Function |       | RAM<br>Shifter |             | Q<br>Shifter     |      |     |     |

|----------|-----------|----|----|-----------------|-------|------------------------|-------|----------------|-------------|------------------|------|-----|-----|

| Mnemonic | ls        | 17 | 16 | Octal<br>Code   | Shift | Load                   | Shift | Load           | Y<br>Output | RAM <sub>0</sub> | RAM3 | Qo  | Q3  |

| QREG     | L         | L  | L  | 0               | Х     | NONE                   | NONE  | F→Q            | F           | ×                | ×    | Х   | Х   |

| NOP      | L         | L  | Н  | 1               | Х     | NONE                   | Х     | NONE           | F           | х                | х    | ×   | Х   |

| RAMA     | L         | Н  | L  | 2               | NONE  | F→B                    | X     | NONE           | Α           | Х                | Х    | Х   | Х   |

| RAMF     | L         | Н  | Н  | 3               | NONE  | F→B                    | Х     | NONE           | F           | ×                | Х    | X   | Х   |

| RAMQD    | Н         | L  | L  | 4               | DOWN  | F/2 → B                | DOWN  | Q/2 → Q        | F           | Fo               | lNз  | Qo  | INз |

| RAMD     | Н         | L  | Н  | 5               | DOWN  | F/2 → B                | х     | NONE           | F           | Fo               | lNз  | Qo  | Х   |

| RAMQU    | Н         | Н  | L  | 6               | UP    | 2F → B                 | UP    | 2Q → Q         | F           | IN <sub>0</sub>  | Fз   | INo | Q3  |

| RAMU     | Н         | Н  | Н  | 7               | ÜP    | 2F → B                 | х     | NONE           | F           | INo              | Fз   | Х   | Qз  |

NOTE:

2590 tb | 04

### SOURCE OPERAND AND ALU FUNCTION MATRIX<sup>(1)</sup>

|          |                     |           | l2, 1, 0 Octal |       |        |        |           |           |        |

|----------|---------------------|-----------|----------------|-------|--------|--------|-----------|-----------|--------|

|          |                     | 0         | 1              | 2     | 3      | 4      | 5         | 6         | 7      |

| Octal    | ALU                 |           |                |       | ALU    | Source |           |           |        |

| l5, 4, 3 | Function            | A, Q      | A, B           | 0, Q  | 0, B   | 0, A   | D, A      | D, Q      | D, 0   |

| 0        | Cn = L<br>R Plus S  | A + Q     | A + B          | a     | В      | A      | D + A     | D + Q     | D      |

|          | Cn ≃ H              | A+Q+1     | A + B + 1      | Q+1   | B + 1  | A + 1  | D + A + 1 | D+Q+1     | D+1    |

| 1        | Cn = L<br>S Minus R | Q – A – 1 | B – A – 1      | Q – 1 | B – 1  | A 1    | A - D - 1 | Q – D – 1 | -D − 1 |

|          | Cn = H              | Q – A     | B – A          | Q     | В      | A      | A – D     | Q – D     | _D     |

| 2        | Cn = L<br>R Minus S | A – Q – 1 | A – B – 1      | Q - 1 | -B - 1 | -A − 1 | D - A - 1 | D – Q – 1 | D – 1  |

|          | Cn = H              | A – Q     | A – B          | -Q    | -B     | -A     | D – A     | D – Q     | D      |

| 3        | RORS                | AVQ       | A V B          | Q     | В      | Α      | DVA       | DVQ       | D      |

| 4        | RANDS               | AΛQ       | AΛB            | 0     | 0      | 0      | DΛA       | DΛQ       | 0      |

| 5        | R AND S             | ĀΛQ       | ĀΛB            | a.    | В      | Α      | DΛA       | DΛQ       | 0      |

| 6        | R EX-OR S           | AVQ       | ΑVΒ            | Q     | В      | Α      | D 7 A     | DVQ       | D      |

| 7        | R EX-NOR S          | Ā∇Q       | ΑVΒ            | ä     | B      | Ã      | DΫĀ       | DVQ       | D      |

5.1

NOTE:

1. + = Plus; - = Minus; Λ = AND; ∇ = EX-OR; ∀ = OR.

2590 to 05

4

<sup>1</sup> X = Don't care. Electrically, the shift pin is a TTL input internally connected to a three-state output which is in the high-impedance state. B = Register Addressed by B inputs.

UP is toward MSB; DOWN is toward LSB.

### E

### **ALU LOGIC MODE FUNCTIONS**

| Oc               | tal              |        |                                              |

|------------------|------------------|--------|----------------------------------------------|

| l5, 4, 3         | l2, 1, 0         | Group  | Function                                     |

| 4<br>4<br>4<br>4 | 0<br>1<br>5<br>6 | AND    | A                                            |

| 3<br>3<br>3<br>3 | 0<br>1<br>5<br>6 | OR     | A V Q<br>A V B<br>D V A<br>D V Q             |

| 6<br>6<br>6      | 0<br>1<br>5<br>6 | EX-OR  | A 7 Q<br>A 7 B<br>D 7 A<br>D 7 Q             |

| 7<br>7<br>7<br>7 | 0<br>1<br>5<br>6 | EX-NOR | A V Q<br>A V B<br>D V A<br>D V Q             |

| 7<br>7<br>7<br>7 | 2<br>3<br>4<br>7 | INVERT | <u>Q</u><br><u>В</u><br><b>A</b><br><u>D</u> |

| 6666             | 2<br>3<br>4<br>7 | PASS   | Q<br>B<br>A<br>D                             |

| 3<br>3<br>3      | 2<br>3<br>4<br>7 | PASS   | Q<br>B<br>A<br>D                             |

| 4<br>4<br>4<br>4 | 2<br>3<br>4<br>7 | "ZERO" | 0<br>0<br>0                                  |

| 5<br>5<br>5<br>5 | 0<br>1<br>5<br>6 | MASK   | Ā Λ Q<br>Ā Λ B<br>D Λ A<br>D Λ Q             |

|                  |                  |        | 2590 tbl 06                                  |

### **ALU ARITHMETIC MODE FUNCTIONS**

| Oc                                   | tal                                  | Cn                     | = L                                                                  | Cn                     | = H                                                |

|--------------------------------------|--------------------------------------|------------------------|----------------------------------------------------------------------|------------------------|----------------------------------------------------|

| l5, 4, 3                             | 12, 1, 0                             | Group                  | Function                                                             | Group                  | Function                                           |

| 0<br>0<br>0                          | 0<br>1<br>5<br>6                     | ADD                    | A + Q<br>A + B<br>D + A<br>D + Q                                     | ADD<br>plus one        | A+Q+1<br>A+B+1<br>D+A+1<br>D+Q+1                   |

| 0 0 0                                | 2<br>3<br>4<br>7                     | PASS                   | Q B A D                                                              | Increment              | Q+1<br>B+1<br>A+1<br>D+1                           |

| 1<br>1<br>1<br>2                     | 2<br>3<br>4<br>7                     | Decrement              | Q - 1<br>B - 1<br>A - 1<br>D - 1                                     | PASS                   | Ø ∰ ≼ D                                            |

| 2<br>2<br>2                          | 2<br>3<br>4<br>7                     | 1's Comp.              | -Q - 1<br>-B - 1<br>-A - 1<br>-D - 1                                 | 2's Comp.<br>(Negate)  | Q # 4 p                                            |

| 1<br>1<br>1<br>1<br>2<br>2<br>2<br>2 | 0<br>1<br>5<br>6<br>0<br>1<br>5<br>6 | Subtract<br>(1's Comp) | Q-A-1<br>B-A-1<br>A-D-1<br>Q-D-1<br>A-Q-1<br>A-B-1<br>D-A-1<br>D-Q-1 | Subtract<br>(2's Comp) | Q - A<br>B - D<br>Q - D<br>A - D<br>A - D<br>D - Q |

2590 tb | 07

### DEFINITIONS(1)

| Po = Ro + So                                    |

|-------------------------------------------------|

| P1 = R1 + S1                                    |

| $P_2 = R_2 + S_2$                               |

| P3 = R3 + S3                                    |

| Go = RoSo                                       |

| G1 = R1S1                                       |

| G2 = R2S2                                       |

| G3 = R3S3                                       |

| C4 = G3 + P3G2 + P3P2G1 + P3P2P1G0 + P3P2P1P0Cn |

| C3 = G2 + P2G1 + P2P1G0 + P2P1P0Cn              |

NOTE:

2590 tol 08

## LOGIC FUNCTIONS FOR $\overline{G}$ , $\overline{P}$ , Cn + 4 AND OVR (1)

| l5, 4, 3 | Function | P                 | G                                | C n + 4                                    | OVR                    |

|----------|----------|-------------------|----------------------------------|--------------------------------------------|------------------------|

| 0        | R+S      | P3P2P1P0          | G3 + P3G2 + P3P2G1 + P3P2P1G0    | C4                                         | C3 ∇ C4                |

| 1        | S-R      |                   | Same as R + S equations, but sub | stitute Ri for Ri in definition            | s                      |

| 2        | R-S      | -                 | Same as R + S equations, but sub | stitute Si for Si in definition            | s                      |

| 3        | RVS      | LOW               | P3P2P1P0                         | P3P2P1P0 + Cn                              | P3P2P1P0 + Cn          |

| 4        | R۸S      | LOW               | G3 + G2 + G1 + G0                | G3 + G2 + G1 + G0 + Cn                     | G3 + G2 + G1 + G0 + Cr |

| 5        | R۸S      | LOW               | Same as R V S equation           | ons, but substitute Rifor Ri               | in definitions         |

| 6        | R⊽S      |                   | Same as RVS equations, but sub   | stitute Ri for Ri in definition            | s                      |

| 7        | RÝS      | G3 + G2 + G1 + G0 | G3 + P3G2 + P3P2G1 + P3P2P1P0    | G3 + P3G2 + P3P2G1<br>+ P3P2P1P0 (G0 + Cn) | (2)                    |

NOTES:

$\begin{array}{lll} 1 & += \mathsf{OR}. \\ 2. & & [\bar{\mathsf{P}}_2 + \bar{\mathsf{G}}_2\bar{\mathsf{P}}_1 + \bar{\mathsf{G}}_2\bar{\mathsf{G}}_1\bar{\mathsf{P}}_0 + \bar{\mathsf{G}}_2\bar{\mathsf{G}}_1\bar{\mathsf{G}}_0\mathsf{C}_n] \ \nabla \ [\bar{\mathsf{P}}_3 + \bar{\mathsf{G}}_3\bar{\mathsf{P}}_2 + \bar{\mathsf{G}}_3\bar{\mathsf{G}}_2\bar{\mathsf{P}}_1 + \bar{\mathsf{G}}_3\bar{\mathsf{G}}_2\bar{\mathsf{G}}_1\bar{\mathsf{P}}_0 + \bar{\mathsf{G}}_3\bar{\mathsf{G}}_2\bar{\mathsf{G}}_1\bar{\mathsf{C}}_n] \end{array}$

### ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                                  | Com'l.              | Mil.                | Unit |

|--------|-----------------------------------------|---------------------|---------------------|------|

| Vcc    | Power Supply<br>Voltage                 | -0.5 to +7.0        | -0.5 to +7.0        | ٧    |

| VTERM  | Terminal Voltage with Respect to Ground | -0.5 to<br>Vcc +0.5 | -0.5 to<br>Vcc +0.5 | ٧    |

| Та     | Operating<br>Temperature                | 0 to +70            | -55 to +125         | °C   |

| TBIAS  | Temperature<br>Under Bias               | -55 to +125         | -65 to +135         | ç    |

| Тѕтс   | Storage<br>Temperature                  | -55 to +125         | -65 to +150         | ů    |

| Рт     | Power Dissipation                       | 1.0                 | 1.0                 | W    |

| lout   | DC Output Current                       | 30                  | 30                  | mA   |

### CAPACITANCE (TA = +25°C, f = 1.0MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Unit |

|--------|--------------------------|------------|------|------|

| Cin    | Input Capacitance        | VIN = OV   | 5    | pF   |

| Cour   | Output Capacitance       | Vout = 0V  | 7    | pF   |

NOTE:

2590 tbl 26

#### NOTE:

1 Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating

# conditions for extended periods may affect reliability. DC ELECTRICAL CHARACTERISTICS

Commercial: TA =  $0^{\circ}$ C to  $+70^{\circ}$ C, Vcc =  $5.0V \pm 5\%$ ; Military: TA =  $-55^{\circ}$ C to  $+125^{\circ}$ C, Vcc =  $5.0V \pm 10\%$

| Symbol | Parameter                          | Test Co                                | nditions              | Min. | Typ. <sup>(3)</sup> | Max. | Unit      |

|--------|------------------------------------|----------------------------------------|-----------------------|------|---------------------|------|-----------|

| Lін    | Input HIGH Current<br>(All Inputs) | Vcc = Max.<br>Vin = Vcc                |                       | -    | 0.1                 | 5    | μА        |

| l II.  | Input LOW Current<br>(All Inputs)  | Vcc = Max.<br>Vin = GND                |                       |      | -0.1                | -5   | μА        |

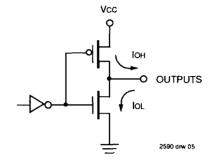

| Vон    | Output High Voltage                | Vcc = Min.                             | IOH = -1.0mA (MIL.)   | 2.4  | 4.3                 | _    | V         |

|        |                                    | Vin = VIH or VIL                       | IOH = -1.6mA (COM'L.) | 2.4  | 4.3                 | -    |           |

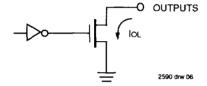

| Vol    | Output Low Voltage                 | Vcc = Min.                             | IOL = 16mA (MIL.)     | _    | 0.3                 | 0.5  | ٧         |

|        |                                    | VIN = VIH or VIL                       | IOL = 20mA (COM'L.)   |      | 0.3                 | 0.5  | <u></u> . |

| Vін    | Input HIGH Level                   | Guaranteed Logic HIGH                  | Levei <sup>(1)</sup>  | 2.0  | _                   | _    | ٧         |

| VIL    | Input LOW Level                    | Guaranteed Logic LOW I                 | Level <sup>(1)</sup>  | _    | _                   | 0.8  | ٧         |

| loz    | Output Leakage Current             | Vcc = Max.                             | Vout = 0V             | _    | -0.1                | -10  | μА        |

|        |                                    |                                        | Vout = Vcc (Max.)     | _    | 0.1                 | 10   |           |

| los    | Output Short Circuit Current       | VCC = Max.<br>VOUT = 0V <sup>(2)</sup> |                       | -30  | -                   | -    | mA        |

### NOTES:

1. These input levels provide zero noise immunity and should only be static tested in a noise-free environment.

2. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

3. Vcc = 5.0V at TA +25°C.

2590 tbl 11

<sup>1.</sup> This parameter is sampled and not 100% tested.

2590 tbl 12

### DC ELECTRICAL CHARACTERISTICS (Cont'd.)

Commercial: TA = 0°C to +70°C, Vcc =  $5.0V \pm 5\%$ ; Military: TA = -55°C to +125°C, Vcc =  $5.0V \pm 10\%$

VLC = 0.2V; VHC = VCC -0.2V

| Symbol | Parameter                                   | Test Condi                        | tions <sup>(1)</sup> |        | Min. | Typ. (3) | Max. | Unit  |

|--------|---------------------------------------------|-----------------------------------|----------------------|--------|------|----------|------|-------|

| Іссан  | Quiescent Power Supply Current              | Vcc = Max.                        |                      |        | ļ    | 0.5      | 5.0  | mA    |

|        | CP = H (CMOS Inputs)                        | VHC ≤ VIH, VIL ≤ VLC              |                      |        |      |          |      |       |

|        |                                             | fcP = 0, CP = H                   |                      |        |      |          |      |       |

| ICCOL  | Quiescent Power Supply Current              | Vcc = Max.                        |                      |        | 1    | 0.5      | 5.0  | mA    |

|        | CP = L (CMOS Inputs)                        | VHC ≤ VIH, VIL ≤ VLC              |                      |        |      |          |      |       |

|        |                                             | fcP = 0, CP = L                   |                      |        |      |          |      |       |

| Ісст   | Quiescent Input Power Supply <sup>(4)</sup> | Vcc = Max., VIH = 3.4V            |                      |        | 1    | 0.3      | 0.5  | mA/   |

|        | Current (per Input @ TTL High)              | fCP = 0                           |                      |        |      |          |      | Input |

| ICCD   | Dynamic Power Supply Current                | Vcc = Max.                        |                      | MIL.   | 1    | 1.5      | 2.5  | mA/   |

|        |                                             | VHC ≤ VIH, VIL ≤ VLC              |                      | COM'L. | -    | 1.0      | 2.0  | MHz   |

|        |                                             | Outputs Open, OE = L              |                      |        |      |          |      |       |

| Icc    | Total Power Supply Current <sup>(5)</sup>   | Vcc = Max                         | 1DT39C01C            | MIL.   | 1    | _        | 30   | mA.   |

|        |                                             | Outputs Open, OE = L              | fcP = 10MHz          | COM'L. | 1    |          | 25   | ]     |

|        |                                             | CP = 50 % Duty cycle              | IDT39C01D            | MIL.   | -    | -        | 35   | ļ     |

|        |                                             | VHC ≤ VIH, VIL ≤ VLC              | fcP = 15MHz          | COM'L. | 1    | _        | 30   |       |

|        |                                             | 50% Data Duty Cycle               | IDT39C01E            | MIL.   | 1    | -        | 40   |       |

|        |                                             |                                   | fcP = 17.5MHz        | COM'L. | -    | _        | 35   |       |

|        |                                             | Vcc = Max                         | IDT39C01C            | MIL.   | -    | -        | 35   |       |

|        |                                             | Outputs Open, $\overline{OE}$ = L | fcP = 10MHz          | COM'L. | -    | -        | 30   |       |

|        |                                             | CP = 50 % Duty Cycle              | IDT39C01D            | MIL.   | 1    | _        | 40   |       |

|        |                                             | VIH = 3.4V, VIL = 0.4V            | fcp = 15MHz          | COM'L. |      | _        | 35   |       |

|        |                                             | 50% Data Duty Cycle               | IDT39C01E            | MIL.   | -    | _        | 45   |       |

|        |                                             |                                   | fcP = 17.5MHz        | COM'L. | -    | _        | 40   |       |

#### NOTES:

These input levels should only be static tested in a noise-free environment.

- 2. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

- 3. Vcc = 5 0V at TA +25°C

- 4. IccT is derived by measuring the total current with all the inputs tied together at 3.4V, subtracting out IccOH, then dividing by the total number of inputs.

- 5. Total Supply Current is the sum of the Quiescent current and the Dynamic current (at either CMOS or TTL input levels). For all conditions, the Total Supply Current can be calculated by using the following equation:

ICC = ICCOH (CDH) +ICCOL (1 - CDH) + ICCT (NT x DH) + ICCD (fCP)

CDH = Clock duty cycle high period

DH = Data duty cycle TTL high period (VIN = 3.4V)

NT = Number of dynamic inputs driven at TTL levels

fcp = Clock input frequency

### **CMOS TESTING CONSIDERATIONS**

There are certain testing considerations which must be taken into account when testing high-speed CMOS devices in an automatic environment. These are:

- Proper decoupling at the test head is necessary. Placement of the capacitor set and the value of capacitors used is critical in reducing the potential erroneous failures resulting from large Vcc current changes. Capacitor lead length must be short and as close to the DUT power pins as possible.

- All input pins should be connected to a voltage potential during testing. If left floating, the device may begin to oscillate causing improper device operation and possible latchup.

- 3) Definition of input levels is very important. Since many inputs may change coincidentally, significant noise at the device pins may cause the VIL and VIH levels not to be met until the noise has settled. To allow for this testing/board induced noise, IDT recommends using VIL ≤ 0V and VIH ≥ 3V for AC tests.

- 4) Device grounding is extremely important for proper device testing. The use of multi-layer performance boards with radial decoupling between power and ground planes is required. The ground plane must be sustained from the performance board to the DUT interface board. All unused interconnect pins must be properly connected to the ground pin. Heavy gauge stranded wire should be used for power wiring and twisted pairs are recommended to minimize inductance.

## AC ELECTRICAL CHARACTERISTICS IDT39C01C

### (Military and Commercial Temperature Ranges)

The tables below specify the guaranteed performance of the IDT39C01C over the  $-55^{\circ}$ C to  $+125^{\circ}$ C and  $0^{\circ}$ C to  $+70^{\circ}$ C temperature ranges. VCC is specified at  $5V \pm 10\%$  for military temperature range and  $5V \pm 5\%$  for commercial temperature range. All times are in nanoseconds and are measured at the 1.5V signal level. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads.

## CYCLE TIME AND CLOCK CHARACTERISTICS

|                                                                            | Mil. | Com'l. | Unit |

|----------------------------------------------------------------------------|------|--------|------|

| Read-Modity-Write Cycle (from selection of A, B registers to end of cycle) | 32   | 31     | ns   |

| Maximum Clock Frequency to<br>shift Q (50% duty cycle,<br>I = 432 or 632)  | 31   | 32     | MHz  |

| Minimum Clock LOW Time                                                     | 15   | 15     | ns   |

| Minimum Clock HIGH Time                                                    | 15   | 15     | ns   |

| Minimum Clock Period                                                       | 32   | 31     | ns   |

2590 tbl 13

## COMBINATIONAL PROPAGATION DELAYS(1) CL = 50pF

|                           | 1    |        |      |        |      |        |      | To     | Outp | out    | _    |        | _    |            |      |          |      |

|---------------------------|------|--------|------|--------|------|--------|------|--------|------|--------|------|--------|------|------------|------|----------|------|

|                           | 1    | Y      |      | F3     | С    | n + 4  | 7    | 5, P   | F    | = 0    | o    | VR     |      | AMo<br>AM3 | ĺ    | Q0<br>Q3 |      |

| From Input                | Mil. | Com'l.     | Mil. | Com'l.   | Unit |

| A, B Address              | 48   | 40     | 48   | 40     | 48   | 40     | 44   | 37     | 48   | 40     | 48   | 40     | 48   | 40         | -    | -        | ns   |

| D                         | 37   | 30     | 37   | 30     | 37   | 30     | 34   | 30     | 40   | 38     | 37   | 30     | 37   | 30         | -    | 1        | ns   |

| Cn                        | 25   | 22     | 25   | 22     | 21   | 20     | -    | -      | 28   | 25     | 25   | 22     | 28   | 25         | -    | +        | ns   |

| lo, 1, 2                  | 40   | 35     | 40   | 35     | 40   | 35     | 44   | 37     | 44   | 37     | 40   | 35     | 40   | 35         | ı    | _        | ns   |

| 13, 4, 5                  | 40   | 35     | 40   | 35     | 40   | 35     | 40   | 35     | 40   | 38     | 40   | 35     | 40   | 35         | -    | _        | ns   |

| l6, 7, 8                  | 29   | 25     | _    | _      | _    |        | 1    | ~      | ı    | _      | -    | -      | 29   | 26         | 29   | 26       | ns   |

| A Bypass<br>ALU (I = 2XX) | 40   | 35     | -    | -      | -    | _      | -    | _      | 1    | -      | 1    | 1      | 1    | -          | 1    | -        | ns   |

| Clock ✓                   | 40   | 35     | 40   | 35     | 40   | 35     | 40   | 35     | 40   | 35     | 40   | 35     | 40   | 35         | 33   | 28       | ns   |

### SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP INPUT)

|                       | CP:   | CP: tpwL          |                   |                 |         |                       |               |        |      |  |  |  |  |  |

|-----------------------|-------|-------------------|-------------------|-----------------|---------|-----------------------|---------------|--------|------|--|--|--|--|--|

|                       |       | p Time<br>e H → L |                   | l Time<br>H → L |         | p Time<br>I L → H     | Hold<br>After |        |      |  |  |  |  |  |

| Input                 | Mil.  | Com'l.            | Mil.              | Com'i.          | MII.    | Com'l.                | Mil.          | Com'i. | Unit |  |  |  |  |  |

| A, B Source Address   | 15    | 15                | 2                 | 1 (3)           | 30,15 + | · tPWL <sup>(4)</sup> | 2             | 1      | ns   |  |  |  |  |  |

| B Destination Address | 15    | 15                | _                 | Do not c        | 2       | 1                     | ns            |        |      |  |  |  |  |  |

| D                     | _ (1) | -                 | _                 | _               | 25      | 25                    | 0             | 0      | ns   |  |  |  |  |  |

| Cn                    |       | _                 | _                 | _               | 20      | 20                    | 0             | 0      | ns   |  |  |  |  |  |

| 10, 1, 2              | _     | _                 | -                 | -               | 30      | 30                    | 0             | 0      | ns   |  |  |  |  |  |

| 13, 4, 5              | -     | <del>-</del>      | _                 | _               | 30      | 30                    | 0             | 0      | ns   |  |  |  |  |  |

| <b>l</b> 6, 7, 8      | 10    | 10                | Do not change (2) |                 |         |                       | 0             | 0      | ns   |  |  |  |  |  |

| RAM0,3, Q0,3          |       | <u> </u>          | _                 | -               | 12      | 12                    | 0             | 0      | ns   |  |  |  |  |  |

NOTES:

2590 tbl 15

- 1. A dash indicates a propagation delay or set-up time constraint does not exist.

- 2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation.

- Source addresses must be stable prior to the H → L transition to allow time to access the source data before the latches close. The A address may then

be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed

during the clock LOW time.

- 4. The set-up time prior to the clock L → H transition is to allow time for data to be accessed, passed through the ALU and returned to the RAM. It includes all the time from stable A and B addresses to the clock L → H transition, regardless of when the H → L transition occurs.

### **OUTPUT ENABLE/DISABLE TIMES**

(CL = 5pF, measured to 0.5V

change of Vour in nanoseconds)

|       |        | Ena  | ble    | Dis  | able   |

|-------|--------|------|--------|------|--------|

| Input | Output | Mil. | Com'l. | Mil. | Com'l. |

| ŌĒ    | Y      | 25   | 23     | 25   | 23     |

## AC ELECTRICAL CHARACTERISTICS IDT39C01D

### (Military and Commercial Temperature Ranges)

The tables below specify the guaranteed performance of the IDT39C01D over the  $-55^{\circ}$ C to  $+125^{\circ}$ C and  $0^{\circ}$ C to  $+70^{\circ}$ C temperature ranges. VCC is specified at  $5V \pm 10\%$  for military temperature range and  $5V \pm 5\%$  for commercial temperature range. All times are in nanoseconds and are measured at the 1.5V signal level. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads.

# CYCLE TIME AND CLOCK CHARACTERISTICS

|                                                                                  | Mil. | Com'l. | Unit |

|----------------------------------------------------------------------------------|------|--------|------|

| Read-Modify-Write Cycle (from<br>selection of A, B registers to end<br>of cycle) | 27   | 23     | ns   |

| Maximum Clock Frequency to<br>shift Q (50% duty cycle,<br>I = 432 or 632)        | 37   | 43     | MHz  |

| Minimum Clock LOW Time                                                           | 13   | 11     | ns   |

| Minimum Clock HIGH Time                                                          | 13   | 11     | ns   |

| Minimum Clock Period                                                             | 27   | 23     | ns   |

2590 fbl 17

### COMBINATIONAL PROPAGATION DELAYS(1) CL = 50pF

|                           |      |        |      |        |       |        |      | To     | Outp | out    |      |        |              |        |          |        |      |

|---------------------------|------|--------|------|--------|-------|--------|------|--------|------|--------|------|--------|--------------|--------|----------|--------|------|

|                           | Y    |        | F3   |        | Cn +4 |        | G, P |        | F=0  |        | OVR  |        | RAMo<br>RAM3 |        | Qo<br>Q3 |        |      |

| From Input                | Mil. | Com'l. | Mil. | Com'i. | Mil.  | Com'l. | Mił. | Com'l. | Mil. | Com'l. | Mil. | Com'l. | Mil.         | Com'l. | Mil.     | Com'l. | Unit |

| A, B Address              | 33   | 30     | 33   | 30     | 33    | 30     | 33   | 30     | 33   | 30     | 33   | 30     | 33           | 30     |          |        | ns   |

| D                         | 24   | 21     | 23   | 20     | 23    | 20     | 21   | 20     | 25   | 24     | 24   | 21     | 25           | 22     | -        | -      | ns   |

| Cn                        | 18   | 17     | 17   | 16     | 14    | 14     | -    | -      | 19   | 18     | 17   | 16     | 19           | 18     | -        | -      | ns   |

| lo, 1, 2                  | 28   | 26     | 27   | 25     | 26    | 24     | 28   | 24     | 29   | 25     | 27   | 24     | 27           | 25     | -        | -      | ns   |

| 13, 4, 5                  | 27   | 26     | 27   | 24     | 26    | 24     | 26   | 24     | 27   | 26     | 26   | 24     | 27           | 26     |          |        | ns   |

| <b>l</b> 6, 7, 8          | 18   | 16     | -    | -      | -     |        | -    | _      | -    | _      | _    | -      | 21           | 21     | 21       | 21     | ns   |

| A Bypass<br>ALU (I = 2XX) | 26   | 24     | -    | _      | -     | -      |      | _      | -    | -      | -    | _      | ı            | 1      | -        | -      | ns   |

| Clock /                   | 27   | 24     | 26   | 23     | 26    | 23     | 25   | 23     | 27   | 24     | 26   | 24     | 27           | 24     | 20       | 19     | ns   |

5.1

### SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP INPUT)

|                       | CP:   | CP: 1PWL          |                          |          |                                 |                                 |               |        |      |  |  |  |  |

|-----------------------|-------|-------------------|--------------------------|----------|---------------------------------|---------------------------------|---------------|--------|------|--|--|--|--|

|                       |       | p Time<br>e H → L | Hold Time<br>After H → L |          |                                 | Time<br>L → H                   | Hold<br>After |        |      |  |  |  |  |

| input                 | Mil.  | Com'l.            | Mit.                     | Com'l.   | Mil.                            | Com'i.                          | Mil.          | Com'l. | Unit |  |  |  |  |

| A, B Source Address   | 11    | 10                | 0                        | 0 (3)    | 24, 11 +<br>tPWL <sup>(4)</sup> | 21, 10 +<br>tPWL <sup>(4)</sup> | 2             | 1      | ns   |  |  |  |  |

| B Destination Address | 11    | 10                |                          | Do not c | 2                               | 1                               | ns            |        |      |  |  |  |  |

| D                     | _ (1) |                   | _                        | _        | 16                              | 16                              | 0             | 0      | ns   |  |  |  |  |

| Cn                    | _     | _                 |                          | -        | 13                              | 13                              | 0             | 0      | ns   |  |  |  |  |

| 10, 1, 2              | _     | <b>—</b>          | _                        | T -      | 19                              | 19                              | 0             | 0      | ns   |  |  |  |  |

| 13, 4, 5              | _     | -                 | -                        | _        | 19                              | 19                              | 0             | 0      | ns   |  |  |  |  |

| l6, 7, 8              | 7     | 7                 |                          | Do not c | hange <sup>(2)</sup>            |                                 | 0             | 0      | ns   |  |  |  |  |

| RAM0,3, Q0,3          | _     |                   | _                        |          | 9                               | 9                               | 0             | 0      | ns   |  |  |  |  |

#### NOTES:

- 1. A dash indicates a propagation delay or set-up time constraint does not exist.

- 2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation.

- 3. Source addresses must be stable prior to the H -> L transition to allow time to access the source data before the latches close. The A address may then be changed. The Bladdress could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 4. The set-up time prior to the clock L → H transition is to allow time for data to be accessed, passed through the ALU and returned to the RAM. It includes all the time from stable A and B addresses to the clock  $L \to H$  transition, regardless of when the  $H \to L$  transition occurs.

### **OUTPUT ENABLE/DISABLE TIMES**

(CL = 5pF, measured to 0.5V

change of Vout in nanoseconds)

|       |        | Ena  | ble    | Dis  | able   |

|-------|--------|------|--------|------|--------|

| Input | Output | Mil. | Com'l. | Mil. | Com'l. |

| ŌĒ    | Υ      | 16   | 14     | 18   | 16     |

2590 tbl 20

## AC ELECTRICAL CHARACTERISTICS IDT39C01E

### (Military and Commercial Temperature Ranges)

The tables below specify the guaranteed performance of the IDT39C01E over the  $-55^{\circ}$ C to  $+125^{\circ}$ C and  $0^{\circ}$ C to  $+70^{\circ}$ C temperature ranges. VCC is specified at  $5V \pm 10\%$  for military temperature range and  $5V \pm 5\%$  for commercial temperature range. All times are in nanoseconds and are measured at the 1.5V signal level. The inputs switch between 0V and 3V with signal transition rates of 1V per nanosecond. All outputs have maximum DC current loads.

## CYCLE TIME AND CLOCK CHARACTERISTICS

|                                                                            | Mil. | Com'l. | Unit |

|----------------------------------------------------------------------------|------|--------|------|

| Read-Modify-Write Cycle (from selection of A, B registers to end of cycle) | 21   | 20     | ns   |

| Maximum Clock Frequency to<br>shift Q (50% duty cycle,<br>I = 432 or 632)  | 46   | . 50   | MHz  |

| Minimum Clock LOW Time                                                     | 10   | 8      | ns   |

| Minimum Clock HIGH Time                                                    | 10   | 8      | ns   |

| Minimum Clock Period                                                       | 21   | 20     | ns   |

2500 512

### COMBINATIONAL PROPAGATION DELAYS (1) CL = 50pF

|                           |      | To Output |      |        |      |        |      |             |      |        |      |        |      |            |      |                                  |      |

|---------------------------|------|-----------|------|--------|------|--------|------|-------------|------|--------|------|--------|------|------------|------|----------------------------------|------|

|                           |      | Y         |      | F3     | С    | n + 4  | 7    | 5, <b>P</b> | F    | = 0    | c    | VR     |      | AMo<br>AM3 |      | Q <sub>0</sub><br>Q <sub>3</sub> |      |

| From Input                | Mil. | Com'l.    | Mil. | Com'l. | Mil. | Com'l. | Mil. | Com'l.      | Mil. | Com'l. | Mil. | Com'l. | Mil. | Com'l.     | Mil. | Com'l.                           | Unit |

| A, B Address              | 26   | 22        | 26   | 22     | 26   | 22     | 26   | 21          | 29   | 25     | 26   | 22     | 26   | 22         | _    | -                                | ns   |

| D                         | 18   | 16        | 17   | 15     | 17   | 15     | 16   | 15          | 22   | 20     | 18   | 16     | 19   | 16         | -    | _                                | ns   |

| Cn                        | 13   | 13        | 13   | 12     | 10   | 10     | _    | _           | 16   | 15     | 13   | 12     | 14   | 13         | -    | _                                | ns   |

| 10, 1, 2                  | 21   | 20        | 20   | 19     | 19   | 18     | 21   | 18          | 25   | 21     | 20   | 18     | 20   | 19         | _    | _                                | ns   |

| 13, 4, 5                  | 20   | 20        | 20   | 18     | 19   | 18     | 19   | 18          | 23   | 23     | 19   | 18     | 20   | 20         | _    | -                                | ns   |

| <b>l</b> 6, 7, 8          | 13   | 12        | -    | -      | _    | -      | -    | -           | -    | -      | _    | -      | 16   | 16         | 16   | 16                               | ns   |

| A Bypass<br>ALU (I = 2XX) | 26   | 24        | _    | _      | -    | -      | _    | -           | _    | _      | _    | _      | -    | -          | -    | _                                | ns   |

| Clock /                   | 20   | 18        | 19   | 17     | 19   | 17     | 19   | 17          | 25   | 22     | 19   | 18     | 20   | 18         | 15   | 15                               | ns   |

### SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP INPUT)

| CP:   | 7                                            | <u> </u>                                                   | —— tpv                                                                                                                                     | VL ———                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                                      |                                                        |

|-------|----------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

|       |                                              | Hold Time<br>After H → L                                   |                                                                                                                                            |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                        |                                                        |

| Mil.  | Com'l.                                       | Mil.                                                       | Com'l.                                                                                                                                     | Mil.                                                                                                                                                                                                                                                | Com'l.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Mil.                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Com'i.                                                 | Unit                                                   |

| 8     | 7                                            | 0                                                          | 0 (3)                                                                                                                                      | 18, 8 +<br>tPWL <sup>(4)</sup>                                                                                                                                                                                                                      | 15, 7 +<br>tPWL <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                      | ns                                                     |

| 8     | 7                                            | Do not change (2)                                          |                                                                                                                                            |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                      | ns                                                     |

| _ (1) |                                              | _                                                          |                                                                                                                                            | 12                                                                                                                                                                                                                                                  | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                      | ns                                                     |

| _     | -                                            | -                                                          | _                                                                                                                                          | 10                                                                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                      | ns                                                     |

| _     | -                                            | _                                                          | _                                                                                                                                          | 14                                                                                                                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                      | ns                                                     |

| _     | -                                            | _                                                          | -                                                                                                                                          | 14                                                                                                                                                                                                                                                  | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                      | ns                                                     |

| 5     | 5                                            |                                                            | Do not c                                                                                                                                   | hange <sup>(2)</sup>                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                      | ns                                                     |

| _     | _                                            | _                                                          | _                                                                                                                                          | 9                                                                                                                                                                                                                                                   | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                      | ns                                                     |

|       | Set-u<br>Before<br>Mil.<br>8<br>8<br>(1)<br> | Set-up Time Before H → L  Mil. Com'l.  8 7  8 7  - (1) 5 5 | Set-up Time     Hold After       Before H → L     After       Mil.     Com'l.     Mil.       8     7     0       8     7     -       - (1) | CP:         Set-up Time Before H → L       Hold Time After H → L         Mil.       Com'l.       Mil.       Com'l.         8       7       0       0 (3)         8       7       Do not c         — (1)       — — — — — — — — — — — — — — — — — — — | Set-up Time<br>Before H → L         Hold Time<br>After H → L         Set-up<br>Before           Mil.         Com'l.         Mil.         Com'l.         Mil.           8         7         0         0 (3)         18, 8 +<br>tPWL (4)           8         7         Do not change (2)           — (1)         —         —         12           —         —         —         10           —         —         —         14           —         —         —         14           5         5         Do not change (2) | CP:         Set-up Time         Before H → L       After H → L       Set-up Time         Mil.       Com'l.       Mil.       Com'l.         8       7       0       0 (3)       18, 8 + 15, 7 + 19WL (4)       15, 7 + 19WL (4)         8       7       Do not change (2)       12       12         — (1)       — — — — — — — — — — — — 10       10       10         — — — — — — — — — — — — — 14       14       14         — — — — — — — — — — — — — — — — — — — | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

#### NOTES:

- 1. A dash indicates a propagation delay or set-up time constraint does not exist.

- 2. Certain signals must be stable during the entire clock LOW time to avoid erroneous operation.

- 3. Source addresses must be stable prior to the H  $\rightarrow$  L transition to allow time to access the source data before the latches close. The A address may then be changed. The B address could be changed if it is not a destination; i.e., if data is not being written back into the RAM. Normally A and B are not changed during the clock LOW time.

- 4. The set-up time prior to the clock L → H transition is to allow time for data to be accessed, passed through the ALU and returned to the RAM. It includes all the time from stable A and B addresses to the clock  $L \to H$  transition, regardless of when the  $H \to L$  transition occurs.

2590 tol 25

### **OUTPUT ENABLE/DISABLE TIMES**

(CL = 5pF, measured to 0.5V

change of Vout in nanoseconds)

|       |        | Enable |        | Dis  | able     |

|-------|--------|--------|--------|------|----------|

| Input | Output | Mil.   | Com'l. | Mil. | Com'l.   |

| ŌĒ    | Y      | 14     | 10     | 12   | 12       |

|       |        |        |        |      | 0500 #10 |

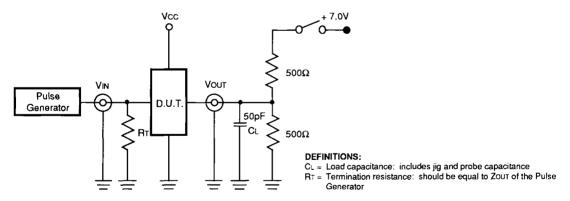

### **AC TEST CONDITIONS**

| Input Pulse Levels Input Rise/Fall Times Input Timing Reference Levels Output Reference Levels | GND to 3.0V<br>1V/ns<br>1.5V<br>1.5V |

|------------------------------------------------------------------------------------------------|--------------------------------------|

| Output Load                                                                                    | See Figure 4                         |

| Test            | Switch |