# **AK5393**

## Enhanced Dual Bit ΔΣ 96kHz 24-Bit ADC

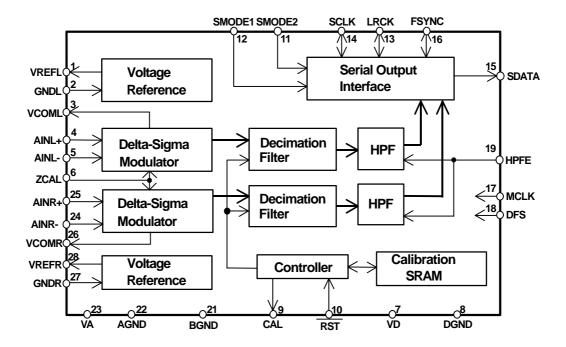

#### 概要

AK5393は108kHzまでのサンプリングレートに対応す &4ビット,128倍オーバサンプリング2ch A/Dコンバータです。 変調器には新開発のエンハンスト・デュアルビット方式を採用、従来のシングルビット方式の優れた低歪み特性に加えて、さらに広いダイナミックレンジを実現しています。AK5393のアナログ入力は完全差動形式になっており、ハイエンドのディジタルオーディオ信号処理アプリケーションに最適です。またAK5393の電源はアナログ5V、ディジタル3.3Vに対応しており、容易に3.3VのロジックICとI/F可能です。

## 特長

- □ サンプリングレート: 1kHz~108kHz

- □ 完全差動入力

- ☐ S/(N+D): 105dB

- ☐ DR: 117dB

- ☐ S/N: 117dB

- □ 高性能直線位相ディジタルフィルタ内蔵

通過域: 0~21.768kHz (@fs=48kHz)

通過域リップル: 0.001dB

阻止域減衰量: 110dB

- □ HPFとオフセットキャリプレーション内蔵

- □ 電源電圧: 5V ± 5%(アナログ), 3~5.25V(ディジタル)

- □ 消費電力: 470mW

- □ パッケージ 28ピンSOP

- □ AK5392ピン互換

## ■ オーダリングガイド

AK5393-VS -10~+70°C 28pin SOP AKD5393 AK5393 Evaluation Board

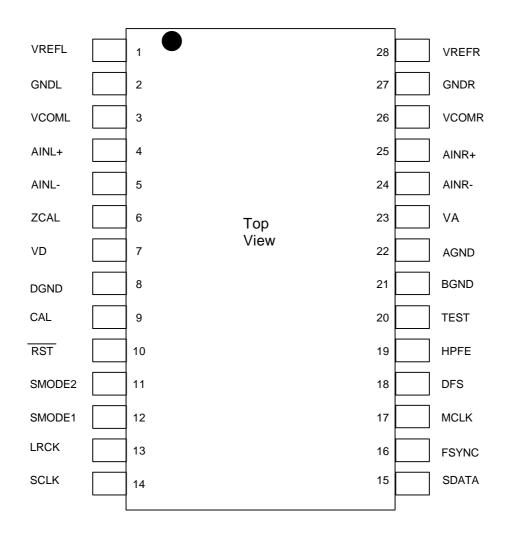

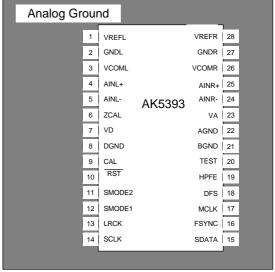

## ■ ピン配置

## ■ AK5392との互換性

|                          | AK5392      | AK5393 |

|--------------------------|-------------|--------|

| Pin 18                   | CMODE       | DFS    |

| fs (max)                 | 54kHz       | 108kHz |

| MCLK (DFS ="L"@fs=48kHz) | 256fs/384fs | 256fs  |

| MCLK (DFS ="H"@fs=96kHz) | 対応しない       | 128fs  |

# ピン配置

| No. | Pin Name | I/O | Function                                             |

|-----|----------|-----|------------------------------------------------------|

| 1   | VREFL    | О   | Lch基準電圧出力ピン, 3.75V                                   |

|     |          |     | GNDLとの間に10μFの電解コンデンサと0.1μFのセラミックコンデンサ                |

|     |          |     | を接続します。                                              |

| 2   | GNDL     | -   | Lch基準グランドピン, 0V                                      |

| 3   | VCOML    | О   | Lchコモン電圧ピン, 2.75V                                    |

| 4   | AINL+    | I   | Lchアナログ正入力ピン                                         |

| 5   | AINL-    | I   | Lchアナログ負入力ピン                                         |

| 6   | ZCAL     | I   | ゼロキャリブレーションピン                                        |

|     |          |     | オフセットキャリブレーションに使う基準信号を選択します。                         |

|     |          |     | "L": VCOML, VCOMR<br>"H":アナログ入力ピン ( AINL ± ,AINR ± ) |

|     | 110      |     |                                                      |

| 7   | VD       | -   | ディジタル部 電源ピン,3.3V                                     |

| 8   | DGND     | -   | ディジタル部 グランドピン                                        |

| 9   | CAL      | О   | キャリブレーションステータスピン                                     |

|     |          |     | "H"のときオフセットキャリブレーション中を示します。<br>                      |

|     |          |     | RST ピンが"H"になるとキャリブレーションが開始され、                        |

|     |          |     | DFS ="L"時には8704LRCKサイクル後"L"になります。                    |

|     |          |     | DFS ="H"時には17408LRCKサイクル後"L"になります。                   |

| 10  | RST      | I   | リセットピン                                               |

|     |          |     | "L"のときディジタル部がパワーダウンされます。"H"になる                       |

|     |          |     | とオフセットキャリブレーションが開始されます。電源投入時                         |

|     |          |     | 一度はキャリブレーションを起動して下さい。                                |

| 11  | SMODE2   | I   | シリアルインタフェースモード選択ピン                                   |

| 12  | SMODE1   | I   | MSBファースト, 2'sコンプリメント<br>SMODE2 SMODE1 MODE LRCK      |

|     |          |     | SMODE2 SMODE1 MODE LRCK L Slave mode : 前詰め : H/L     |

|     |          |     | L H Master mode : 疑似I <sup>2</sup> S : H/L           |

|     |          |     | H L Slave mode : $I^2S$ : L/H                        |

|     |          |     | H H Master mode : I <sup>2</sup> S : L/H             |

| 13  | LRCK     | I/O | L/Rチャネル選択クロックピン                                      |

|     |          |     | SMODE1="H"のとき、リセット時はSMODE2="L"では"H"で、                |

|     |          |     | SMODE2="H"では"L"です。                                   |

| 14 | SCLK  | I/O | シリアルデータクロックピン                                       |

|----|-------|-----|-----------------------------------------------------|

| 17 | SCER  | 1/0 | このピンの立ち下がりで出力データが1ビット出力されます。                        |

|    |       |     | Slave mode:                                         |

|    |       |     | 48fs以上のクロックが必要です。                                   |

|    |       |     | Master mode:                                        |

|    |       |     | 128fs(DFS ="L")、64fs(DFS ="H")のクロックが出力されます。         |

|    |       |     | リセット時は"L"です。                                        |

| 15 | SDATA | О   | シリアルデータ出力ピン                                         |

|    |       |     | MSBファースト, 2'sコンプリメント。リセット時は"L"です。                   |

| 16 | FSYNC | I/O | フレーム同期クロックピン                                        |

|    |       |     | Slave mode:                                         |

|    |       |     | "H"のときSDATAの出力がイネーブルされます。I <sup>2</sup> SモードではDon't |

|    |       |     | careです。                                             |

|    |       |     | Master mode:                                        |

|    |       |     | 2fsのクロックが出力されます。リセット時は"L"です。                        |

| 17 | MCLK  | I   | マスタクロック入力ピン                                         |

|    |       |     | 256fs at DFS ="L", 128fs at DFS ="H"                |

| 18 | DFS   | I   | 倍速サンプリングモード選択ピン                                     |

|    |       |     | "L": 通常速                                            |

|    |       |     | "H": 倍速                                             |

| 19 | HPFE  | I   | HPFイネーブルピン                                          |

|    |       |     | "L": OFF                                            |

|    |       |     | "H": ON                                             |

| 20 | TEST  | I   | テストピン (pull-down pin)                               |

|    |       |     | GNDに接続して下さい。                                        |

| 21 | BGND  | -   | 基板グランドピン, 0V                                        |

| 22 | AGND  | -   | アナログ部 グランドピン, 0V                                    |

| 23 | VA    | -   | アナログ部 電源ピン, 5V                                      |

| 24 | AINR- | I   | Rchアナログ正入力ピン                                        |

| 25 | AINR+ | I   | Rchアナログ負入力ピン                                        |

| 26 | VCOMR | 0   | Rchコモン電圧ピン, 2.75V                                   |

| 27 | GNDR  | -   | Rch基準グランドピン , 0V                                    |

| 28 | VREFR | 0   | Rch基準電圧出力ピン, 3.75V                                  |

|    |       |     | GNDRとの間に10μFの電解コンデンサと0.1μFのセラミックコンデンサ               |

|    |       |     | を接続し ます。                                            |

|    |       |     |                                                     |

注)全てのディジタル入力ピンはオープンにしないで下さい。

## 絶対最大定格

(AGND,BGND,DGND=0V; Note 1)

| Parameter                              | Symbol       | min  | max    | Units |

|----------------------------------------|--------------|------|--------|-------|

| Power Supplies: Analog                 | VA           | -0.3 | 6.0    | V     |

| Digital                                | VD           | -0.3 | 6.0    | V     |

| BGND-DGND  (Note 2)                    | $\Delta GND$ | -    | 0.3    | V     |

| Input Current, Any Pin Except Supplies | IIN          | -    | ±10    | mA    |

| Analog Input Voltage                   | VINA         | -0.3 | VA+0.3 | V     |

| Digital Input Voltage                  | VIND         | -0.3 | VD+0.3 | V     |

| Ambient Temperature (power applied)    | Ta           | -10  | 70     | °C    |

| Storage Temperature                    | Tstg         | -65  | 150    | °C    |

Notes: 1. 電圧は全てグランドピンに対する値です。

2. AGND, BGND, DGNDは、同じアナロググランドに接続して下さい。

注意:この値を超えた条件で使用した場合、ICを破壊することがあります。

また通常の動作は保証されません。

## 推奨動作条件

(AGND,BGND,DGND=0V; Note 1)

| Parameter       |         | Symbol | min  | typ | max  | Units |

|-----------------|---------|--------|------|-----|------|-------|

| Power Supplies: | Analog  | VA     | 4.75 | 5.0 | 5.25 | V     |

| (Note 3)        | Digital | VD     | 3.0  | 3.3 | 5.25 | V     |

Notes: 1. 電圧は全てグランドピンに対する値です。

3. VAとVD間の電源立ち上げシーケンスを考慮する必要はありません。

本データシートに記載されている条件以外のご使用に関しては、当社では責任負いかねますので十分ご注意下さい。

## アナログ特性

(特記なき場合はTa=25 ; VA=5.0V; VD=3.3V; AGND,BGND,DGND=0V; fs=48kHz; 信号周波数=1kHz; 24ピット出力測定帯域=10Hz~20kHz)

| Parameter              |                         |            | min  | typ   | max   | Units                 |

|------------------------|-------------------------|------------|------|-------|-------|-----------------------|

| Resolution             |                         |            |      |       | 24    | Bits                  |

| <b>Analog Input Ch</b> | aracteristics:          |            |      |       |       |                       |

| S/(N+D)                | fs=48kHz                | -1dBFS     | 98   | 105   |       | dB                    |

|                        |                         | -20dBFS    | -    | 94    |       | dB                    |

|                        |                         | -60dBFS    | -    | 54    |       | dB                    |

|                        | fs=96kHz                | -1dBFS     | 96   | 103   |       | dB                    |

|                        | BW=40kHz                | -20dBFS    | -    | 85    |       | dB                    |

|                        |                         | -60dBFS    | -    | 45    |       | dB                    |

| Dynamic Range (        | (-60dBFS with A-V       | Veighted ) | 112  | 117   |       | dB                    |

| S/N (A-We              | eighted)                |            | 112  | 117   |       | dB                    |

| Interchannel Isola     | tion                    |            | 110  | 120   |       | dB                    |

| Interchannel Gain      | Mismatch                |            |      | 0.1   | 0.5   | dB                    |

| Gain Drift             |                         |            |      |       | 150   | ppm/°C                |

| Offset Error           | after calibration, H    | PF=OFF     |      | ±200  | ±1000 | LSB <sub>24</sub>     |

| 8                      | after calibration, H    | PF=ON      |      | ±1    |       | LSB <sub>24</sub>     |

| Offset Drift           | (HI                     | PF=OFF)    | -    | ±10   | -     | LSB <sub>24</sub> /°C |

| Offset Calibration     | Range (H                | PF=OFF)    |      | ±50   |       | mV                    |

| Input Voltage (A       | AIN+)-(AIN-)            |            | ±2.3 | ±2.45 | ±2.6  | V                     |

| Input Impedance        |                         |            | 2.4  | 4     |       | kΩ                    |

| <b>Power Supplies</b>  |                         |            |      |       |       |                       |

| Power Supply Cur       | rrent                   |            |      |       |       |                       |

| VA                     |                         |            |      | 90    | 130   | mA                    |

| VD (fs                 | VD (fs=48kHz; DFS ="L") |            |      | 6     | 9     | mA                    |

| (fs:                   | =96kHz; DFS ="H         | ')         |      | 9     | 14    | mA                    |

| Power Dissipation      | 1                       |            |      | 470   | 680   | mW                    |

| Power Supply Rej       | ection (Note 4          | )          |      | 70    |       | dB                    |

Notes: 4. 電源電圧に対し周波数1kHz、振幅20mVppの正弦波を加算入力した場合、 その入力振幅に対する出力振幅の減衰量で規定します。

### ディジタルフィルタ特性(fs=48kHz)

(Ta=25°C; VA=5.0V±5%; VD=3.0~5.25V; fs=48kHz, DFS ="L")

| Parameter               |              |         | Symbol | min    | typ  | max    | Units |

|-------------------------|--------------|---------|--------|--------|------|--------|-------|

| ADC Digital Filter(Deci | mation LPF   | ):      |        |        |      |        |       |

| Passband                | (1)          | Note 5) | PB     | 0      |      | 21.768 | kHz   |

| Stopband                | (1)          | Note 5) | SB     | 26.232 |      |        | kHz   |

| Passband Ripple         |              |         | PR     |        |      | ±0.001 | dB    |

| Stopband Attenuation    | ion (Note 6) |         | SA     | 110    |      |        | dB    |

| Group Delay Distortion  |              |         | ΔGD    |        | 0    |        | us    |

| Group Delay             | (N           | Note 7) | GD     |        | 38.7 |        | 1/fs  |

| ADC Digital Filter(HPF  | ·):          |         |        |        |      |        |       |

| Frequency response      | (Note 5)     | -3dB    | FR     |        | 1.0  |        | Hz    |

|                         |              | -0.1dB  |        |        | 6.5  |        | Hz    |

### ディジタルフィルタ特性(fs=96kHz)

(Ta=25°C; VA=5.0V±5%; VD=3.0~5.25V; fs=96kHz, DFS ="H")

| Parameter             |                               | Symbol | min | typ    | max  | Units  |      |

|-----------------------|-------------------------------|--------|-----|--------|------|--------|------|

| ADC Digital Filter(D  |                               |        |     |        |      |        |      |

| Passband              | (Note                         | e 5)   | PB  | 0      |      | 43.536 | kHz  |

| Stopband              | (Note                         | e 5)   | SB  | 52.464 |      |        | kHz  |

| Passband Ripple       |                               |        | PR  |        |      | ±0.003 | dB   |

| Stopband Attenuation  | Stopband Attenuation (Note 8) |        | SA  | 110    |      |        | dB   |

| Group Delay Distortio | n                             |        | ΔGD |        | 0    |        | us   |

| Group Delay           | (Note                         | : 7)   | GD  |        | 38.8 |        | 1/fs |

| ADC Digital Filter(H  |                               |        |     |        |      |        |      |

| Frequency response    | (Note 5)                      | -3dB   | FR  |        | 2.0  |        | Hz   |

|                       |                               | -0.1dB |     |        | 13.0 |        | Hz   |

- Notes: 5. 通過域、阻止域の周波数は fs (システムサンプリングレート)に比例します。

- $6.~\mathrm{fs}$ = $48\mathrm{KHz}$ のときアナログ変調器は $6.144\mathrm{MHz}$ でアナログ入力をサンプリングします。サンプリング周波数の整数倍の帯域 ( n x  $6.144\mathrm{MHz}$  ±  $21.768\mathrm{kHz}$  ;n= $0,1,2,3\cdots$  ) では入力信号はディジタルフィルタによって減衰されません。

- 7. ディジタルフィルタによる演算遅延で、アナログ信号が入力されてから両チャネルの24ビットデータが出力レジスタにセットされるまでの時間です。HPF: ONのときは40.7/fs(DFS = "L"), 40.8/fs(DFS = "H") typ.です。

- 8. fs=96KHzのときアナログ変調器は6.144MHzでアナログ入力をサンプリングします。サンプリング周波数の整数倍の帯域 ( n x 6.144MHz  $\pm 43.536$ kHz ;n= $0,1,2,3\cdots$  ) では入力信号はディジタルフィルタによって減衰されません。

## DC特性

$(Ta=25^{\circ}C; VA=5.0V\pm5\%; VD=3.0 \sim 5.25V)$

| Parameter                            | Symbol | min    | typ | max    | Units |

|--------------------------------------|--------|--------|-----|--------|-------|

| High-Level Input Voltage             | VIH    | 70% VD | -   | -      | V     |

| Low-Level Input Voltage              | VIL    | -      | -   | 30% VD | V     |

| High-Level Output Voltage Iout=-20µA | VOH    | VD-0.1 | -   | -      | V     |

| Low-Level Output Voltage Iout=20µA   | VOL    | -      |     | 0.1    | V     |

| Input Leakage Current                | Iin    | -      | =   | ±10    | μA    |

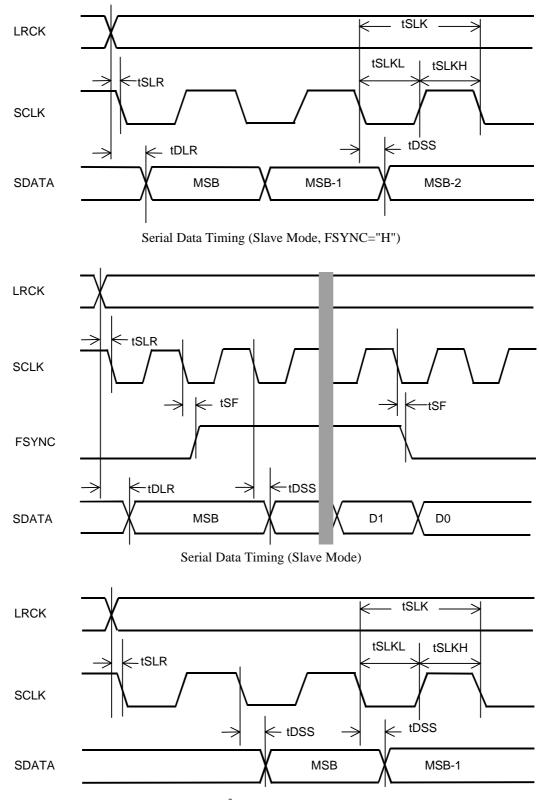

#### **SWITCHING CHARACTERISTICS**

$(Ta=25^{\circ}C; VA=5.0V\pm5\%; VD=3.0 \sim 5.25V; C_L=20pF)$

| Parameter                           | Symbol | min   | typ    | max    | Units |

|-------------------------------------|--------|-------|--------|--------|-------|

| Control Clock Frequency             |        |       |        |        |       |

| Master Clock 256fs:                 | fCLK   | 0.256 | 12.288 | 13.824 | MHz   |

| Pulse width Low                     | tCLKL  | 29    |        |        | ns    |

| Pulse width High                    | tCLKH  | 29    |        |        | ns    |

| Serial Data Output Clock (SCLK)     | fSLK   |       | 6.144  | 6.912  | MHz   |

| Channel Select Clock (LRCK)         | fs     | 1     | 48     | 108    | kHz   |

| duty cycle                          |        | 25    |        | 75     | %     |

| Serial Interface Timing (Note 9)    |        |       |        |        |       |

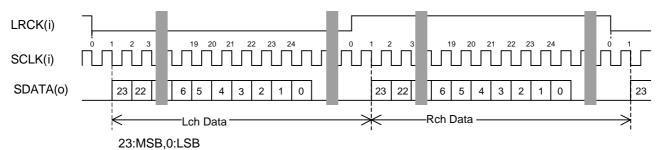

| Slave Mode(SMODE1="L")              |        |       |        |        |       |

| SCLK Period                         | tSLK   | 144.7 |        |        | ns    |

| SCLK Pulse width Low                | tSLKL  | 65    |        |        | ns    |

| Pulse width High                    | tSLKH  | 65    |        |        | ns    |

| SCLK falling to LRCK Edge (Note 10) | tSLR   | -45   |        | 45     | ns    |

| LRCK Edge to SDATA MSB Valid        | tDLR   |       |        | 45     | ns    |

| SCLK falling to SDATA Valid         | tDSS   |       |        | 45     | ns    |

| SCLK falling to FSYNC Edge          | tSF    | -45   |        | 45     | ns    |

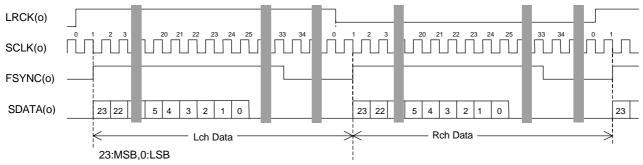

| Master Mode(SMODE1="H")             |        |       |        |        |       |

| SCLK Frequency (DFS ="L")           | fSLK   |       | 128fs  |        | Hz    |

| SCLK Frequency (DFS ="H")           | fSLK   |       | 64fs   |        | Hz    |

| duty cycle                          |        |       | 50     |        | %     |

| FSYNC Frequency                     | fFSYNC |       | 2fs    |        | Hz    |

| duty cycle                          |        |       | 50     |        | %     |

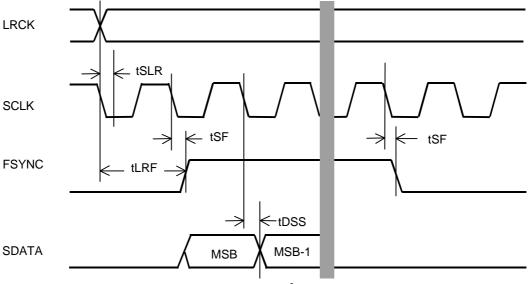

| SCLK falling to LRCK Edge           | tSLR   | -20   |        | 20     | ns    |

| LRCK Edge to FSYNC rising           | tLRF   |       | 1      |        | tslk  |

| SCLK falling to SDATA Valid         | tDSS   |       |        | 45     | ns    |

| SCLK falling to FSYNC Edge          | tSF    | -20   |        | 20     | ns    |

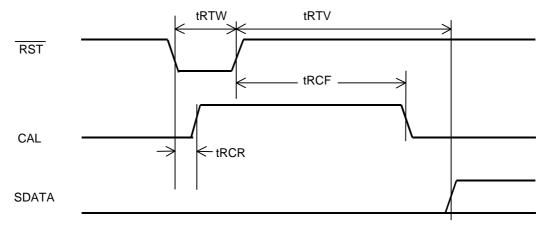

| Reset/Calibration timing            |        |       |        |        |       |

| RST Pulse width                     | tRTW   | 150   |        |        | ns    |

| RST falling to CAL rising           | tRCR   |       |        | 50     | ns    |

| RST rising to CAL falling (Note 11) | tRCF   |       | 8704   |        | 1/fs  |

| RST rising to SDATA Valid (Note 11) | tRTV   |       | 8960   |        | 1/fs  |

Notes: 9. シリアルデータインタフェースの項を参照して下さい。

<sup>10.</sup> この規格値はLRCKのエッジとSCLKの" "が重ならないように規定しています。

<sup>11.</sup> RST を立ち上げてからのLRCKクロックの" "の回数です。規格値はマスタモードでの値。 スレーブモードでは1-LRCKクロック(1/fs)長くなります。また、DFS ="H"時は tRCF=17408,tRTV=17920になります。

## ■ タイミング波形

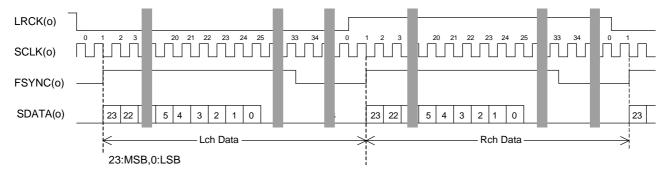

Serial Data Timing (I<sup>2</sup>S Slave Mode, FSYNC = Don't Care)

Serial Data Timing (Master Mode & I<sup>2</sup>S Master Mode, DFS ="L")

Reset & Calibration Timing

#### 機能説明

#### ■ システムクロック

AK5393に必要とされるクロックは、MCLK, LRCK(fs), SCLKです。MCLKとLRCKは同期する必要がありますが位相を合わせる必要はありません。通常速モード(DFS ="L")ではMCLKは256fsで、倍速モード(DFS="H")ではMCLKは128fsです。表 1 に標準のオーディオレートに対してAK5393に必要とされる各クロックの周波数を示します。

AK5393ではLRCKクロックによる位相検出回路を内蔵しているため、動作中に各クロックの周波数変更等で内部タイミングがずれた場合は自動的にリセットがかかり、位相合わせが行われます。そのため電源投入時以外は外部からリセットをかける必要はありません。

パワーダウン時(RST ="L")以外は、各外部クロック (MCLK, SCLK, LRCK) を止めてはいけません。これらのクロックが供給されない場合、内部にダイナミックなロジックを使用しているため、過電流が流れ、動作が異常になる可能性があります。

| Speed      | Normal(DFS ="L") | Double(DFS ="H") |

|------------|------------------|------------------|

| LRCK (max) | 54kHz            | 108kHz           |

| SCLK       | ~128fs           | ~64fs            |

| MCLK       | 256fs            | 128fs            |

表1.システムクロック

| fs      | MCLK       | SCLK      |

|---------|------------|-----------|

| 32.0kHz | 8.1920MHz  | 4.0960MHz |

| 44.1kHz | 11.2896MHz | 5.6448MHz |

| 48.0kHz | 12.2880MHz | 6.1440MHz |

| 96.0kHz | 12.2880MHz | 6.1440MHz |

表2.システムクロック周波数例

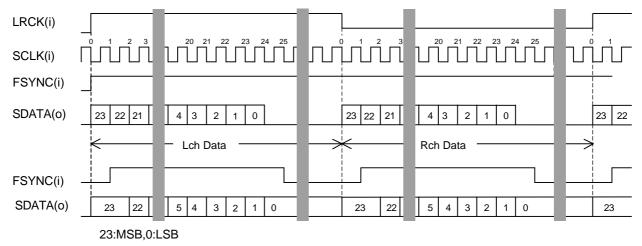

#### ■ シリアルデータインタフェース

AK5393は4種類のデータフォーマットが SMODE2,SMODE1ピンで選択できます。データの出力チャネルは LRCKクロックで決まり、fsのレートで両チャネルのデータが出力されます。A/D変換データはSCLKに同期してSDATAピンからSMODE2,SMODE1ピンの設定に従って出力されます。出力データのフォーマットは2'sコンプリメント、MSBファーストです。

| Figure   | SMODE2 | SMODE1 | Mode                         | LRCK            |

|----------|--------|--------|------------------------------|-----------------|

| Figure 1 | L      | L      | Slave Mode                   | Lch = H, Rch =L |

| Figure 2 | L      | Н      | Master Mode                  | Lch =H, Rch =L  |

| Figure 3 | Н      | L      | I <sup>2</sup> S Slave Mode  | Lch =L, Rch =H  |

| Figure 4 | Н      | Н      | I <sup>2</sup> S Master Mode | Lch =L, Rch =H  |

表3.シリアルインタフェース

図1.データタイミング(スレーブモード)

図2.データ出力タイミング(マスターモード、 DFS ="L" 時)

図3. データ出力タイミング (I2S スレーブモード時, FSYNC: Don't care.)

図4.データ出力タイミング(I<sup>2</sup>Sマスターモード、DFS ="L"時)

M0038-J-04 2000/4

## ■ オフセットキャリブレーション

RST ピンを"L"にすると、ディジタル部のみパワーダウンモードになります。"H"になるとオフセットキャリブレーションが開始されます。オフセットキャリブレーションは電源投入時必ず一度起動して下さい。

オフセットキャリブレーション中は各チャネルの入力を測定し、オフセット補正用のデータとしてキャリブレーションメモリに記録されます。キャリブレーション後のデータはこのオフセット値を差し引いた値で補正され出力されます。キャリブレーション中の入力はZCALのレベルによってアナログ入力ピン(AIN+/-)か、VCOMピンのどちらかで与えられます。ZCALが"H"のときはアナログ入力ピンの電圧が測定され、"L"のときはVCOMピンの電圧が測定されます。CAL出力はキャリブレーション中"H"です。

### ■ ディジタルHPF

AK5393はDCオフセットキャンセルのためにディジタルHPFも内蔵します。HPFのfcは、fs=48kHz 時1Hzになっており、周波数応答はfsに比例します。

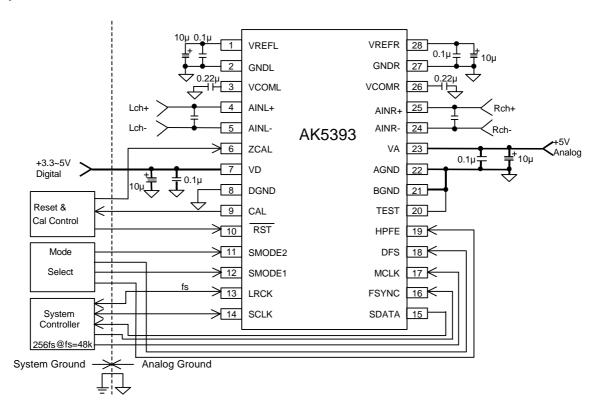

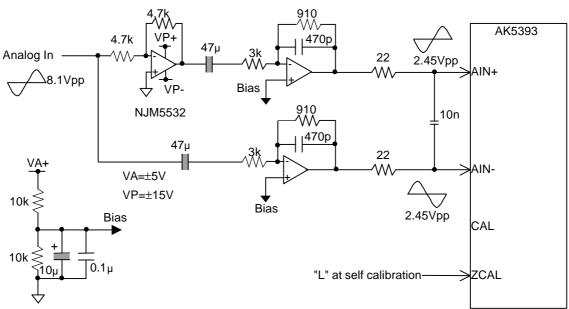

### システム設計

システム接続例を図5に示します。具体的な回路と測定例については評価用ボード(AKD5393)を参照して下さい。

図5.システム接続例

#### Notes:

- LRCK = fs, SCLK = 64fs.

- VAとVDの配線は、レギュレータ等の低インピーダンスから分けて下さい。

- AGND, BGND, DGND は同じアナロググランドに接続して下さい。

- プルダゥスグルアップピン以外の入力はオープンにしないで下さい。

図6.グランドレイアウト

#### 1. グランドと電源のデカップリング

電源とグランドの取り方には十分注意して下さい。アナロググランドとディジタルグランドは分けて配線しPCボード上の電源に近いところで接続して下さい。小容量のデカップリングコンデンサはなるべく電源ピンの近くに接続して下さい。

#### 2. 内蔵基準電圧源とVCOM

A/D変換の基準電圧はVREFL/Rピンの電圧とGNDL/Rピンの電圧の差です。GNDL/RはAGNDに接続し、VREFL/Rピンには高周波ノイズを除去するために0.1μFのセラミックコンデンサと10μF以下の電解コンデンサをVREFL/RとGNDL/R間に接続して下さい。特にセラミックコンデンサはピンにできるだけ近づけて接続して下さい。さらにディジタル信号、特にクロックは変調器へのカップリングをさけるためVREFL/Rピンからできるだけ離して下さい。また、VREFL/Rピンから電流をとってはいけません。

VCOMはアナログ信号のコモン電圧として使われます。このピンには高周波ノイズを除去するために $0.22\mu$ FのセラミックコンデンサをAGNDとの間にピンにできるだけ近づけて接続して下さい。さらにディジタル信号、特にクロックは変調器へのカップリングをさけるためVCOMピンからできるだけ離して下さい。また、VCOMピンから電流をとってはいけません。

#### 3. アナログ入力

アナログ入力信号は各チャンネルの差動入力ピンから変調器に入力されます。入力電圧はAIN+とAIN-の差の電圧になります。入力レンジは $\pm 2.45$ Vpp(typ)です。AK5393はAGNDからVAまでの電圧を入力することができます。出力コードのフォーマットは2'sコンプリメント (2の補数)で正のフルスケール以上の入力電圧に対しては7FFFFH(@24bit)、負のフルスケール以下に対しては800000H(@24bit)、無入力時の理想値は000000H(@24bit)です。DCオフセットはオフセットキャリブレーションを実行することでキャンセルされます。

AK5393は128fs(6.144MHz @fs=48kHz,DFS="L")でアナログ入力をサンプリングします。ディジタルフィルタは、128fsの整数倍を除く阻止域以上のノイズを全て除去します。ほとんどのオーディオ信号では128fs付近に大きなノイズをもつことはありませんので簡単なRCフィルタで128fs付近のノイズを十分減衰させることができます。

AK5393のアナログ電源電圧は $\pm$ 5Vになっており、アナログ入力ピン(AIN $\pm$ /-)には、VA $\pm$ 0.3V以上、AGND-0.3V以下の電圧と $\pm$ 10mA以上の電流を入力してはいけません。過大電流の流入は内部の保護回路の破壊、さらにはラッチアップを引き起こし、ICの破壊に至ります。従って、周辺のアナログ回路の電源電圧が、 $\pm$ 15V等の場合はアナログ入力ピンを絶対最大定格以上の信号から保護する必要があります。

図7は入力バッファ回路例です。反転・反転回路によるゲイン-10dBの差動入力回路です。AIN+/-間の10nFは、変調器のクロックフィードスルーを取るためのコンデンサです。また、 $22\Omega$ とあわせて約360kHzのカットオフをもつLPFになっています。前段アンプは約370kHzのカットオフをもつLPFになっています。この例では内部オフセットのみをセルフキャリブレーションでキャンセルしています。詳細は評価ボードを参照して下さい。

図7. 入力バッファ回路例 1

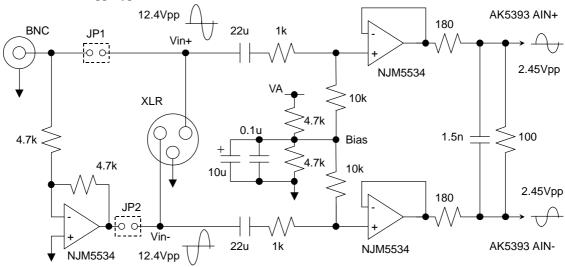

図 8はAK5393のアナログ入力回路例2 ( $1^{st}$  order HPF; fc=0.66Hz,表4  $1^{st}$  order LPF; fc=590kHz, gain=-14dB,表5)です。シングルエンドで入力する場合は差動入力する場合に比べて反転バッファが一つ増えます。(図ではシングルエンドの場合は JP1, JP2ショート、差動の場合はJP1, JP2オープン)。この回路の入力レベルは +/-12.4Vppです。 (AK5393: +/-2.45Vpp Typ.).

図8. 入力バッファ回路例 2

| fin                | 1Hz     | 10Hz    |

|--------------------|---------|---------|

| Frequency Response | -1.56dB | -0.02dB |

表4. Frequency Response of HPF

| fin                | 20kHz    | 40kHz   | 6.144MHz |

|--------------------|----------|---------|----------|

| Frequency Response | -0.005dB | -0.02dB | -15.6dB  |

表5. Frequency Response of LPF

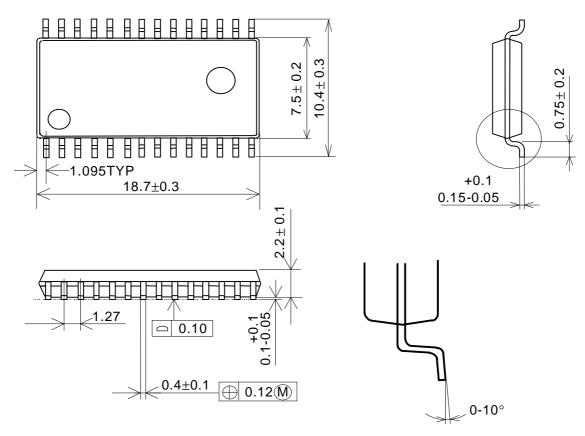

## パッケージ

# 28pin SOP (Unit: mm)

## ■ 材質・メッキ仕様

パッケージ材質: エポキシ系樹脂

リードフレーム材質:銅

リードフレーム処理:半田メッキ

### マーキング仕様

XXXBYYYYC の内容

XXXB: ロット番号 (X: 数字, B: 英字)YYYYC: 製造時期 (Y: 数字, C: 英字)

#### 重要な注意事項 -

- 本書に記載された製品、及び、製品の仕様につきましては、製品改善のために予告なく変更することがあります。従いまして、ご使用を検討の際には、本書に掲載した情報が最新のものであることを弊社営業担当、あるいは弊社特約店営業担当にご確認下さい。

- 本書に掲載された情報・図面の使用に起因した第三者の所有する特許権、工業所有権、その他の権利に 対する侵害につきましては、当社はその責任を負うものではありませんので、ご了承下さい。

- 本書記載製品が、外国為替及び、外国貿易管理法に定める戦略物資役務を含む)に該当する場合、輸出する際に同法に基づく輸出許可が必要です。

- 医療機器、安全装置、航空宇宙用機器、原子力制御用機器など、その装置 機器の故障や動作不良が、 直接または間接を問わず、生命、身体、財産等へ重大な損害を及ぼすことが通常予想されるような極めて 高い信頼性を要求される用途に弊社製品を使用される場合は、必ず事前に弊社代表取締役の書面による 同意をお取り下さい。

- この同意書を得ずにこうした用途に弊社製品を使用された場合、弊社は、その使用から生ずる損害等の責任を一切負うものではありませんのでご了承下さい。

- お客様の転売等によりこの注意事項の存在を知らずに上記用途に弊社製品が使用され、その使用から損害等が生じた場合は全てお客様にてご負担または補償して頂きますのでご了承下さい