# **Description**

The  $\mu$ PB8282 and  $\mu$ PB8283 are 8-bit latches with three-state output buffers. The  $\mu$ PB8282 is non-inverting and the  $\mu$ PB8283 inverts the input data. These devices are ideal for demultiplexing the address/data buses on the 8085A/8086 microprocessors. The  $\mu$ PB8282/83 are fabricated using NEC's Schottky bipolar process.

#### **Features**

- Support μPB8080, 8085A, 8048, 8086 family systems

- □ Transparent during active strobe

- ☐ Fully parallel 8-bit data register and buffer

- High output drive capability (32 mA) for driving the system data bus

- ☐ Three-state outputs

## **Ordering Information**

| Part<br>Number | Package Type       | Output Drive<br>Capability |

|----------------|--------------------|----------------------------|

| µPB8282C       | 20-pin plastic DIP | 32 mA                      |

| μPB8283C       | 20-pin plastic DIP | 32 mA                      |

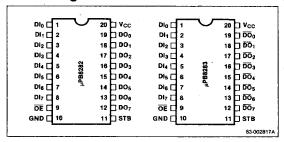

#### Pin Identification

| No.   | Symbol                                                                           | Function      |  |

|-------|----------------------------------------------------------------------------------|---------------|--|

| 1-8   | DI <sub>O</sub> -DI <sub>7</sub>                                                 | Data in       |  |

| 9     | ŌĒ                                                                               | Output enable |  |

| 10    | GND                                                                              | Ground        |  |

| 11    | STB                                                                              | Strobe        |  |

| 12-19 | (μPB8282) <u>D0</u> 7- <u>D0</u> 0<br>(μPB8283) <del>D0</del> 7- <del>D0</del> 0 | Data out      |  |

| 20    | Vcc                                                                              | Power supply  |  |

## Pin Configurations

# Pin Functions

# OE (Output Enable)

This active low input control signal enables the contents of the data latches onto the data output pins ( $B_0$ - $B_7$ ). When  $\overline{OE}$  goes high, the output buffers become high impedance.

#### STB (Strobe)

This input control pulse strobes data at input  $A_0$ - $A_7$  into the data latches. Data is latched at STB's high to low transition. When active high, STB admits input data.

#### Dl<sub>0</sub>-Dl<sub>7</sub> (Data In)

When data that satisfies the STB strobe setup time requirements is input to these pins, it is latched into the data latches.

# $DO_0$ -DO<sub>7</sub> ( $\mu$ PB8282) (Data Out) $DO_0$ -DO<sub>7</sub> ( $\mu$ PB8283)

When  $\overline{\text{OE}}$  is active (low), it outputs data to the DO<sub>0</sub>-DO<sub>7</sub> pins. When  $\overline{\text{OE}}$  is inactive high, DO<sub>0</sub>-DO<sub>7</sub> are high impedance. Enabling or disabling the output buffers will not cause negative-going transients to appear on the data output bus.

#### GND (Ground)

This is the ground.

## V<sub>CC</sub> (Power Supply)

This is the +5 V power supply.

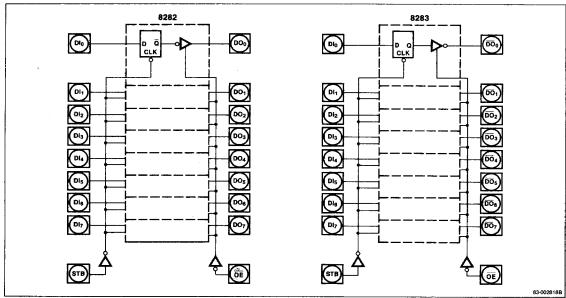

# **Block Diagrams**

## **Functional Description**

The  $\mu$ PB8282/83 are 8-bit latches with three-state output buffers. Data on the inputs is latched into the data latches on a high-to-low transition of the STB line. When STB is high, the latches appear transparent. The  $\overline{OE}$  input enables the latched data to be transferred to the output pins. When  $\overline{OE}$  is high, the outputs are put in the three-state condition.  $\overline{OE}$  will not cause transients to appear on the data outputs.

## **Absolute Maximum Ratings**

$T_A = 25^{\circ}C$

| Operating temperature          | 0°C to +70°C    |

|--------------------------------|-----------------|

| Storage temperature            | -65°C to +150°C |

| All output and supply voltages | -0.5 to +7 V    |

| All input voltages             | -1.0 V to 5.5 V |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Characteristics**

$T_A = 0$ °C to +70°C;  $V_{CC} = +5 \text{ V} \pm 10\%$

| Parameter              | Symbol          | Limits |      |      | Test                                                                                          |  |

|------------------------|-----------------|--------|------|------|-----------------------------------------------------------------------------------------------|--|

|                        |                 | Min    | Max  | Unit | Conditions                                                                                    |  |

| Input clamp<br>voltage | V <sub>C</sub>  |        | -1   | ٧    | $I_C = -5 \text{ mA}$                                                                         |  |

| Power supply current   | ¹cc             |        | 160  | mΑ   |                                                                                               |  |

| Forward input current  | 1 <sub>F</sub>  |        | -0.2 | mA   | $V_F = 0.45 \text{ V}$                                                                        |  |

| Reverse input current  | I <sub>R</sub>  |        | 50   | μΑ   | V <sub>R</sub> = 5.25 V                                                                       |  |

| Output low voltage     | V <sub>OL</sub> |        | 0.45 | ٧    | I <sub>OL</sub> = 32 mA                                                                       |  |

| Output high voltage    | V <sub>OH</sub> | 2.4    |      | ٧    | $I_{OH} = -5 \text{ mA}$                                                                      |  |

| Output off current     | loff            |        | ±50  | μΑ   | $V_{OFF} = 0.45 \text{ to } 5.25 \text{ V}$                                                   |  |

| Input low voltage      | VIL             |        | 0.8  | ٧    | $V_{CC} = 5.0 \text{ V (1)}$                                                                  |  |

| Input high voltage     | VIH             | 2.0    |      | ٧    | $V_{CC} = 5.0 \text{ V (1)}$                                                                  |  |

| Input capacitance      | C <sub>IN</sub> |        | 12   | pF   | $V_{B AS} = 2.5 \text{ V},$<br>$V_{CC} = 5 \text{ V}, T_A = 25^{\circ}\text{C}$<br>F = 1  MHz |  |

#### Note:

(1) Output loading  $I_{OL} = 32$  mA,  $I_{OH} = -5$  mA,  $C_L = 300$  pF

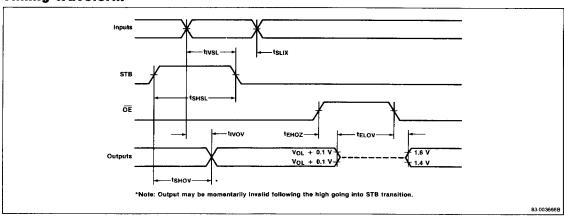

# **AC Characteristics**

$T_A$  = 0°C to +70°C;  $V_{CC}$  = 5 V ± 10%  $I_{OL}$  = 32 mA,  $I_{OH}$  = -5 mA,  $C_L$  = 300 pF

|                                                 |                   | Limits   |          |          |

|-------------------------------------------------|-------------------|----------|----------|----------|

| Parameter                                       | Symbol            | Min      | Max      | Unit     |

| Input to output delay —Inverting —Non-inverting | tivov             | 5<br>5   | 22<br>30 | ns<br>ns |

| STB to output delay —Inverting —Non-inverting   | <sup>†</sup> shov | 10<br>10 | 40<br>45 | ns<br>ns |

| Output disable time                             | t <sub>EHOZ</sub> | 5        | 22       | ns       |

| Output enable time                              | t <sub>ELOV</sub> | 10       | 30       | ns       |

| Input to STB setup time                         | t <sub>IVSL</sub> | 0        |          | ns       |

| Input to STB hold time                          | t <sub>SLIX</sub> | 25       |          | ПS       |

| STB high time                                   | tshsl             | 15       |          | ns       |

| input, output rise time                         | tilih, toloh      |          | 20       | ns       |

| Input, output fall time                         | tiHIL, toHOL      |          | 12       | ns       |

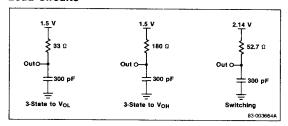

## **Load Circuits**

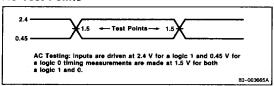

#### **AC Test Points**

# **Timing Waveform**