### **General Description**

The MAX4291/MAX4292/MAX4294 family of micropower operational amplifiers operates from a +1.8V to +5.5V single supply or ±0.9V to ±2.75V dual supplies and has Rail-to-Rail® input/output capabilities. These amplifiers provide a 500kHz gain-bandwidth product and 120dB open-loop voltage gain while using only 100µA of supply current per amplifier. The combination of low input offset voltage (±200µV) and high-open-loop gain makes them ideal for low-power/low-voltage, highprecision portable applications.

The MAX4291/MAX4292/MAX4294 have an input common-mode range that extends to each supply rail, and their outputs swing to within 46mV of the rails with a  $2k\Omega$ load. Although the minimum operating voltage is specified at +1.8V, these devices typically operate down to +1.5V. The combination of ultra-low-voltage operation, rail-to-rail inputs/output, and low-power consumption makes these devices ideal for any portable/two-cell battery-powered system.

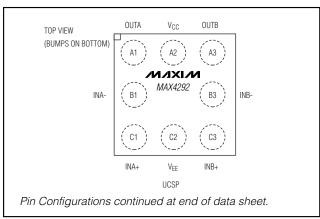

The single MAX4291 is offered in an ultra-small 5-pin SC70 package. The dual MAX4292 is offered in a space-saving 8-bump, 1.5mm X 1.5mm footprint, chipscale package (UCSPTM).

## **Applications**

2-Cell Battery-Operated Systems Portable Electronic Equipment Battery-Powered Instrumentation Digital Scales Strain Gauges Sensor Amplifiers Cellular Phones

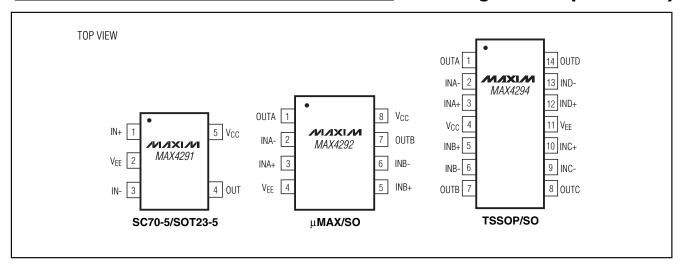

## **Pin Configurations**

#### **Features**

- ♦ Ultra-Low Voltage Operation—Guaranteed Down to +1.8V

- ♦ 100µA Supply Current per Amplifier

- ♦ 500kHz Gain-Bandwidth Product

- ♦ 120dB Open-Loop Voltage Gain (R<sub>L</sub> = 100kΩ)

- ♦ 0.017% THD + Noise at 1kHz

- ♦ Rail-to-Rail Input Common-Mode Range

- ♦ Rail-to-Rail Output Drives 2kΩ Load

- ♦ No Phase Reversal for Overdriven Inputs

- ◆ Unity-Gain Stable for Capacitive Loads up to 100pF

- ♦ 200µV Input Offset Voltage (MAX4292/MAX4294)

- ♦ Single in Small 5-Pin SC70

- Available in Ultra-Small Packages 5-Pin SC70 (MAX4291) 8-Bump UCSP (MAX4292)

### **Ordering Information**

| PART         | TEMP. RANGE    | PIN-<br>PACKAGE | TOP<br>MARK |

|--------------|----------------|-----------------|-------------|

| MAX4291EXK-T | -40°C to +85°C | 5 SC70-5        | AAD         |

| MAX4291EUK-T | -40°C to +85°C | 5 SOT23-5       | ADML        |

| MAX4292EBA-T | -40°C to +85°C | 8 UCSP          | AAJ         |

| MAX4292EUA   | -40°C to +85°C | 8 µMAX          | _           |

| MAX4292ESA   | -40°C to +85°C | 8 SO            | _           |

| MAX4294ESD   | -40°C to +85°C | 14 SO           | _           |

| MAX4294EUD   | -40°C to +85°C | 14 TSSOP        | _           |

UCSP Reliability is integrally linked to the user's assembly methods, circuit board material, and environment. Refer to the UCSP Reliability Notice in the UCSP Reliability section of this data sheet for more information.

#### Selector Guide

| PART    | AMPLIFIERS | PIN-PACKAGE        |

|---------|------------|--------------------|

| MAX4291 | 1          | 5-pin SC70/SOT23   |

| MAX4292 | 2          | 8-pin μMAX/SO/UCSP |

| MAX4294 | 4          | 14-pin SO/TSSOP    |

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd. UCSP is a trademark of Maxim Integrated Products, Inc.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage (V <sub>CC</sub> to V <sub>EE</sub> )(V <sub>CC</sub> + 0.3V) to |            |

|---------------------------------------------------------------------------------|------------|

| Current into IN_+, IN                                                           |            |

| Output Short-Circuit Duration                                                   | Continuous |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)                           |            |

| 5-Pin SC70 (derate 2.5mW/°C above +70°C)                                        | 200mW      |

| 5-Pin SOT23 (derate 7.1mW/°C above +70°C)                                       | 571mW      |

| 8-Bump UCSP (derate 4.7mW/°C above +70°C)                                       | 379mW      |

| 8-Pin µMAX (derate 4.10mW/°C above +70°C)  | 330mW          |

|--------------------------------------------|----------------|

| 8-Pin SO (derate 5.88mW/°C above +70°C)    | 471mW          |

| 14-Pin SO (derate 8.33mW/°C above +70°C)   | 667mW          |

| 14-Pin TSSOP (derate 6.3mW/°C above +70°C) | 500mW          |

| Operating Temperature Range                | -40°C to +85°C |

| Junction Temperature                       | +150°C         |

| Storage Temperature Range                  | 65°C to +150°C |

| Lead Temperature (soldering, 10s)          | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +1.8V \text{ to } +5.5V, V_{EE} = V_{CM} = 0, V_{OUT} = V_{CC} / 2, R_L = 100k\Omega \text{ connected to } V_{CC} / 2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                          | SYMBOL          |                                          | CONDITIONS                   | MIN | TYP  | MAX   | UNITS |

|------------------------------------|-----------------|------------------------------------------|------------------------------|-----|------|-------|-------|

| Supply Voltage Range               | Vcc             | Inferred from I                          | PSRR test                    | 1.8 |      | 5.5   | V     |

| Quiescent Supply Current           | IQ              | $V_{CC} = 1.8V$                          |                              |     | 100  | 210   | μΑ    |

| (per Amplifier)                    | iQ              | $V_{CC} = 5.0V$                          |                              |     | 100  | 255   | μΑ    |

| Input Offset Voltage               | Vos             | MAX4291                                  |                              |     | ±400 | ±2500 | μV    |

| Input Onset Voltage                | VOS             | MAX4292/MA                               | X4294                        |     | ±200 | ±1200 | μv    |

| Input Bias Current                 | IB              | Vcc = 5.0V, 0                            | ≤ V <sub>CM</sub> ≤ 5.0V     |     | ±15  | ±60   | nA    |

| Input Offset Current               | IOS             | $V_{CC} = 5.0V, 0$                       | ≤ V <sub>CM</sub> ≤ 5.0V     |     | ±1   | ±7    | nA    |

| Differential Input Resistance      | RIN             | IV <sub>IN+</sub> - V <sub>IN-</sub> I < | $IV_{IN+} - V_{IN-}I < 10mV$ |     | 0.75 |       | МΩ    |

| Input Common-Mode Voltage<br>Range | V <sub>CM</sub> | Inferred from                            | Inferred from CMRR test      |     |      | Vcc   | V     |

|                                    |                 | Tested for<br>0 ≤ V <sub>CM</sub> ≤      | MAX4291                      | 50  | 80   |       | dB    |

| Common-Mode Rejection Ratio        | CMRR            | 1.8V;<br>V <sub>CC</sub> = 1.8V          | MAX4292/MAX4294              | 57  | 80   |       | QD.   |

| Common Mode Rejection Hatte        | OWN II I        | Tested for<br>0 ≤ V <sub>CM</sub> ≤      | MAX4291                      | 60  | 90   |       | dB    |

|                                    |                 | 5.0V,<br>V <sub>CC</sub> = 5.0V          | MAX4292/MAX4294              | 66  | 90   |       | GD.   |

| Power-Supply Rejection Ratio       | PSRR            |                                          |                              | 77  | 100  |       | dB    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +1.8V \text{ to } +5.5V, V_{EE} = V_{CM} = 0, V_{OUT} = V_{CC} / 2, R_L = 100k\Omega \text{ connected to } V_{CC} / 2, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                    | SYMBOL         |                              | CONDITIONS                                                     | MIN | TYP | MAX | UNITS   |

|------------------------------|----------------|------------------------------|----------------------------------------------------------------|-----|-----|-----|---------|

|                              |                | V <sub>CC</sub> = 1.8V       | $R_L = 100k\Omega,$ $0.02V \le V_{OUT} \le V_{CC} - 0.02V$     | 80  | 120 |     |         |

|                              | Av             | VCC = 1.6V                   | $R_L = 2k\Omega,$ $0.1V \le V_{OUT} \le V_{CC} - 0.1V$         | 80  | 110 |     | dB      |

| Large-Signal Voltage Gain    | AV             | Voc - 5 0V                   | $R_L = 100k\Omega$ ,<br>$0.02V \le V_{OUT} \le V_{CC} - 0.02V$ | 80  | 130 |     | αв      |

|                              |                | V <sub>CC</sub> = 5.0V       | $R_L = 2k\Omega,$ $0.1V \le V_{OUT} \le V_{CC} - 0.1V$         | 80  | 120 |     |         |

| Output Voltage Swing High    | VoH            | VOH Specified as IVCC - VOHI | $R_L = 100k\Omega$ to $V_{CC}/2$                               |     | 2   | 20  | mV      |

| Output voitage Swillg Flight |                |                              | $R_L = 2k\Omega$ to $V_{CC}/2$                                 |     | 15  | 40  |         |

| Output Voltage Swing Low     | VOL            | Specified as                 | $R_L = 100k\Omega$ to $V_{CC}$ / 2                             |     | 25  | 80  | mV      |

| Output voltage Swing Low     | VOL            | IVEE - VOLI                  | $R_L = 2k\Omega$ to $V_{CC}/2$                                 |     | 46  | 120 | IIIV    |

| Output Short-Circuit Current | IOUT(SC)       | Sourcing or sin              | king                                                           |     | 20  |     | mA      |

| Channel-to-Channel Isolation | CHISO          | Specified at f =             | 10kHz (MAX4292/MAX4294 only)                                   |     | 83  |     | dB      |

| Gain Bandwidth Product       | GBW            |                              |                                                                |     | 500 |     | kHz     |

| Phase Margin                 | фМ             |                              |                                                                |     | 65  |     | degrees |

| Gain Margin                  | G <sub>M</sub> |                              |                                                                |     | 12  |     | dB      |

| Slew Rate                    | SR             |                              |                                                                |     | 0.2 |     | V/µs    |

| Input Voltage Noise Density  | en             | f = 10kHz                    |                                                                |     | 70  |     | nV/√Hz  |

| Input Current Noise Density  | in             | f = 10kHz                    | f = 10kHz                                                      |     |     |     | pA/√Hz  |

| Capacitive-Load Stability    |                | $A_{VCL} = +1V/V$            | no sustained oscillations                                      |     | 100 |     | pF      |

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +1.8V \text{ to } +5.5V, V_{EE} = V_{CM} = 0, V_{OUT} = V_{CC} / 2, R_L = 100k\Omega \text{ connected to } V_{CC} / 2, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.})$  (Note 1)

| PARAMETER                | SYMBOL | CONDITIONS              | MIN | TYP | MAX   | UNITS |

|--------------------------|--------|-------------------------|-----|-----|-------|-------|

| Supply Voltage Range     | Vcc    | Inferred from PSRR test | 1.8 |     | 5.5   | V     |

| Quiescent Supply Current | lo     | V <sub>CC</sub> = 1.8V  |     |     | 240   | μA    |

| (per Amplifier)          | IQ     | V <sub>CC</sub> = 5.0V  |     |     | 270   | μΑ    |

| Input Offset Voltage     | Voc    | MAX4291                 |     |     | ±3000 | uV    |

| Input Onset Voltage      | Vos    | MAX4292/MAX4294         |     |     | ±2000 | μν    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +1.8V \text{ to } +5.5V, V_{EE} = V_{CM} = 0, V_{OUT} = V_{CC} / 2, R_L = 100k\Omega$  connected to  $V_{CC} / 2, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.) (Note 1)

| PARAMETER                          | SYMBOL          |                                           | CONDITIONS                                                                                        | MIN                                                                                       | TYP      | MAX | UNITS |    |

|------------------------------------|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------|-----|-------|----|

| Input Offset Voltage Drift         | TCVos           |                                           |                                                                                                   |                                                                                           | 1.2      |     | μV/°C |    |

| Input Bias Current                 | lΒ              | Vcc = 5.0V, 0                             | ≤ V <sub>CM</sub> ≤ 5.0V                                                                          |                                                                                           |          | ±90 | nA    |    |

| Input Offset Current               | los             | $V_{CC} = 5.0V, 0$                        | ≤ V <sub>CM</sub> ≤ 5.0V                                                                          |                                                                                           |          | ±10 | nA    |    |

| Input Common-Mode Voltage<br>Range | VcM             | Inferred from C                           | CMRR test                                                                                         | 0                                                                                         |          | Vcc | V     |    |

|                                    |                 | Tested for<br>0 ≤ V <sub>CM</sub> ≤ 1.8V, | MAX4291                                                                                           | 50                                                                                        |          |     | dB    |    |

| Common-Mode Rejection Ratio        | CMRR            | VCC = 1.8V                                | MAX4292/MAX4294                                                                                   | 53                                                                                        |          |     | GB    |    |

| Common-wode Nejection natio        | Civil ii i      | Tested for 0 ≤ V <sub>CM</sub> ≤ 5.0V,    | MAX4291                                                                                           | 60                                                                                        |          |     | dB    |    |

|                                    |                 | $V_{CC} = 5.0V$                           | MAX4292/MAX4294                                                                                   | 62                                                                                        |          |     | UB    |    |

| Power-Supply Rejection Ratio       | PSRR            |                                           |                                                                                                   | 75                                                                                        |          |     | dB    |    |

|                                    |                 | Vcc = 1.8V                                | $\begin{aligned} R_L &= 100 k \Omega, \\ 0.02 V &\leq V_{OUT} \leq V_{CC} - 0.02 V \end{aligned}$ | 80                                                                                        |          |     |       |    |

| Lorgo Signal Valtago Coin          | Av -            | VCC = 1.0V                                | VGC = 1.0V                                                                                        | $\begin{aligned} R_L &= 2k\Omega, \\ 0.1V &\leq V_{OUT} \leq V_{CC} - 0.1V \end{aligned}$ | 80       |     |       | dB |

| Large-Signal Voltage Gain          |                 | V00 - 5 0V                                | $R_L = 100k\Omega,$<br>0.02V $\leq V_{OUT} \leq V_{CC} - 0.02V$                                   | 80                                                                                        |          |     | иь    |    |

|                                    |                 | V <sub>C</sub> C = 5.0V                   | VCC = 5.0V                                                                                        | $R_{L} = 2k\Omega,$ $0.1V \le V_{OUT} \le V_{CC} - 0.1V$                                  | 80       |     |       |    |

| Output Voltage Swing High          | Vou             | Specified as                              | $R_L = 100k\Omega$ to $V_{CC}/2$                                                                  |                                                                                           |          | 20  | mV    |    |

| Output voltage swillig high        | Voн             | IV <sub>CC</sub> – V <sub>OH</sub> I      | $R_L = 2k\Omega$ to $V_{CC}/2$                                                                    |                                                                                           |          | 40  | ] mv  |    |

| Output Voltage Swing Low           | V <sub>OL</sub> | Specified as                              | $R_L = 100k\Omega$ to $V_{CC}/2$                                                                  |                                                                                           |          | 80  | mV    |    |

|                                    | VOL             | IVEE – VOLI                               | $R_L = 2k\Omega$ to $V_{CC}/2$                                                                    |                                                                                           | <u> </u> | 120 | ]     |    |

Note 1: All devices are 100% tested at  $T_A = +25^{\circ}C$ . All temperature limits are guaranteed by design.

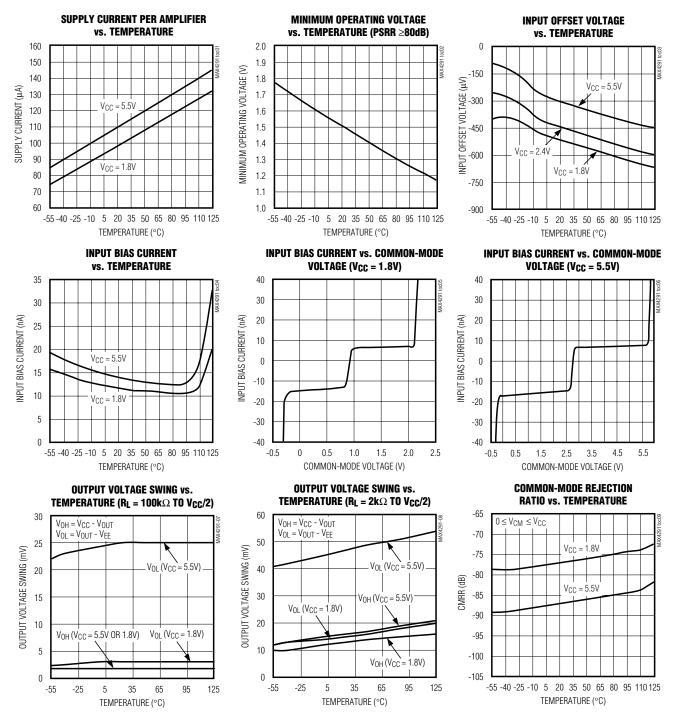

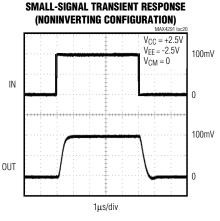

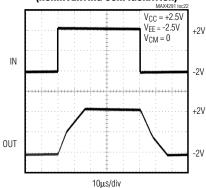

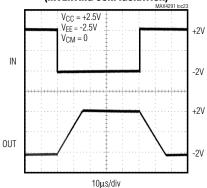

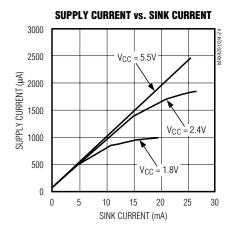

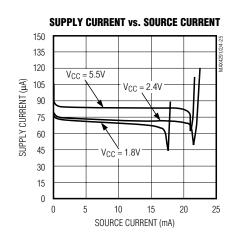

## **Typical Operating Characteristics**

$(V_{CC} = +2.4V, V_{EE} = V_{CM} = 0, V_{OUT} = V_{CC}/2, no load, T_A = +25$ °C, unless otherwise noted.)

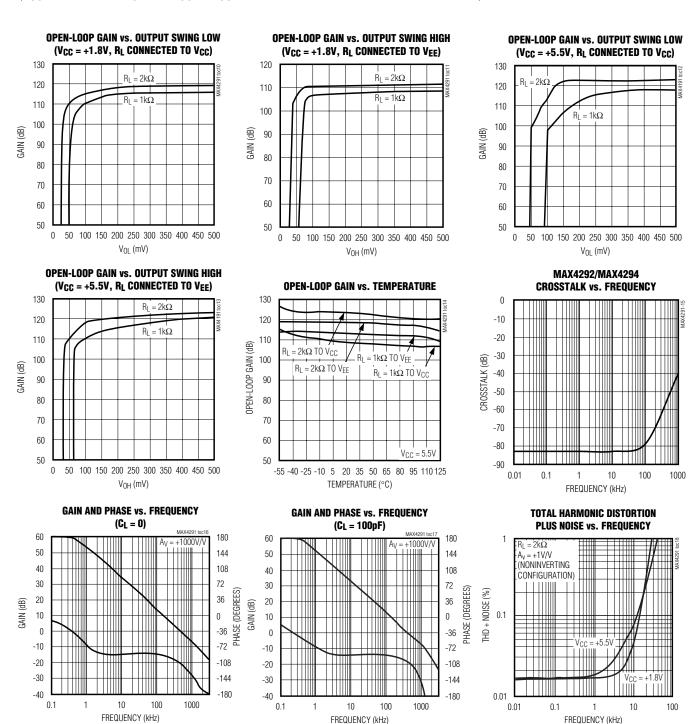

## Typical Operating Characteristics (continued)

(VCC = +2.4V, VEE = VCM = 0, VOUT = VCC / 2, no load, TA = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

$(V_{CC} = +2.4V, V_{EE} = V_{CM} = 0, V_{OUT} = V_{CC}/2, \text{ no load}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# LARGE-SIGNAL TRANSIENT RESPONSE (NONINVERTING CONFIGURATION)

# LARGE-SIGNAL TRANSIENT RESPONSE (INVERTING CONFIGURATION)

### **Pin Description**

|         | PIN     |        |          |                 |                                                                 |

|---------|---------|--------|----------|-----------------|-----------------------------------------------------------------|

| MAX4291 | MAX4292 |        | MAX4294  | NAME            | FUNCTION                                                        |

| WAX4291 | μMAX/SO | UCSP   | WIAA4294 |                 |                                                                 |

| 1       | _       | _      | -        | IN+             | Noninverting Input                                              |

| 2       | 4       | C2     | 11       | VEE             | Negative Supply. Connect to ground for single-supply operation. |

| 3       | _       | _      | _        | IN-             | Inverting Input                                                 |

| 4       | -       | _      | -        | OUT             | Amplifier Output                                                |

| 5       | 8       | A2     | 4        | V <sub>CC</sub> | Positive Supply                                                 |

| _       | 1, 7    | A1, A3 | 1, 7     | OUTA, OUTB      | Outputs for Amplifiers A and B                                  |

| -       | 2, 6    | B1, B3 | 2, 6     | INA-, INB-      | Inverting Inputs to Amplifiers A and B                          |

| -       | 3, 5    | C1, C3 | 3, 5     | INA+, INB+      | Noninverting Inputs to Amplifiers A and B                       |

| -       | _       | -      | 8, 14    | OUTC, OUTD      | Outputs for amplifiers C and D                                  |

| -       | -       |        | 9, 13    | INC-, IND-      | Inverting Inputs to Amplifiers C and D                          |

| -       | _       | _      | 10, 12   | INC+, IND+      | Noninverting Inputs to Amplifiers C and D                       |

## **Detailed Description**

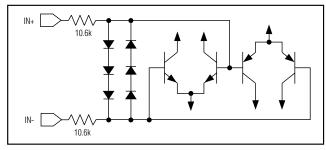

#### Rail-to-Rail Input Stage

The MAX4291/MAX4292/MAX4294 have rail-to-rail inputs and output stages that are specifically designed for low-voltage, single-supply operation in the smallest package possible. The input stage consists of separate NPN and PNP differential stages, which operate together to provide a common-mode range extending to both supply rails. The crossover region of these two pairs occurs halfway between VCC and VEE. The input offset voltage is typically ±200µV (MAX4292/MAX4294). Low operating supply voltage, low supply current, rail-to-rail common-mode input range, and rail-to-rail outputs make this family of operational amplifiers (op amps) an excellent choice for precision or general-purpose, low-voltage, battery-powered systems.

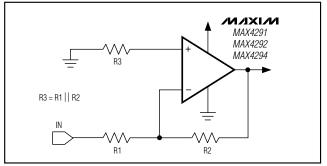

Since the input stage consists of NPN and PNP pairs, the input bias current changes polarity as the common-mode voltage passes through the crossover region. Match the effective impedance seen by each input to reduce the offset error caused by input bias currents flowing through external source impedances (Figures 1a and 1b).

The combination of high source impedance plus input capacitance (amplifier input capacitance plus stray

Figure 1a. Minimizing Offset Error Due to Input Bias Current (Noninverting)

Figure 1b. Minimizing Offset Error Due to Input Bias Current (Inverting)

| Table 1. MAX4291 Characteristics with | Typical Battery | / Systems |

|---------------------------------------|-----------------|-----------|

|---------------------------------------|-----------------|-----------|

| BATTERY TYPE                       | RECHARGE-<br>ABLE | VFRESH<br>(V) | VEND-OF-LIFE (V) | CAPACITY, AA SIZE<br>(mA-h) | MAX4291<br>OPERATING TIME IN<br>NORMAL MODE<br>(h) |

|------------------------------------|-------------------|---------------|------------------|-----------------------------|----------------------------------------------------|

| Alkaline (2 cells)                 | No                | 3.0           | 1.8              | 2000                        | 20,000                                             |

| Nickel-Cadmium (2 cells)           | Yes               | 2.4           | 1.8              | 750                         | 7500                                               |

| Lithium-Ion<br>(1 cell)            | Yes               | 3.5           | 2.7              | 1000                        | 10,000                                             |

| Nickel-Metal-<br>Hydride (2 cells) | Yes               | 2.4           | 1.8              | 1000                        | 10,000                                             |

Figure 2. Input Protection Circuit

capacitance) creates a parasitic pole that produces an underdamped signal response. Reducing input capacitance or placing a small capacitor across the feedback resistor improves response in this case.

The MAX4291/MAX4292/MAX4294 family's inputs are protected from large differential input voltages by internal 10.6k $\Omega$  series resistors and back-to-back triplediode stacks across the inputs (Figure 2). For differential input voltages (much less than 1.8V), input resistance is typically 0.75M $\Omega$ . For differential input voltages greater than 1.8V, input resistance is around 21.2k $\Omega$ , and the input bias current can be approximated by the following equation:

$$I_{BIAS} = \frac{(V_{DIFF} - 1.8V)}{21.2k\Omega}$$

In the region where the differential input voltage approaches 1.8V, the input resistance decreases exponentially from  $0.75 M\Omega$  to  $21.2 k\Omega$  as the diode block begins to conduct. Conversely, the bias current increases with the same curve.

In unity-gain configuration, high slew rate input signals may capacitively couple to the output through the triple-diode stacks.

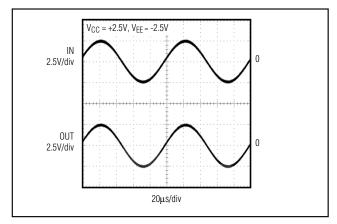

Figure 3. Rail-to-Rail Input/Output Voltage Range

#### Rail-to-Rail Output Stage

The MAX4291/MAX4292/MAX4294 output stage can drive up to a  $2k\Omega$  load and still swing to within 46mV of the rails. Figure 3 shows the output voltage swing of a MAX4291 configured as a unity-gain buffer, powered from a  $\pm 2.5 \text{V}$  supply. The output for this setup typically swings from (VEE + 25mV) to (VCC - 2mV) with a  $100k\Omega$  load.

## Applications Information

#### **Power-Supply Considerations**

The MAX4291/MAX4292/MAX4294 operate from a single  $\pm 1.8V$  to  $\pm 5.5V$  supply (or dual  $\pm 0.9V$  to  $\pm 2.75V$  supplies) and consume only  $\pm 1.8V$  of supply current per amplifier. A high power-supply rejection ratio of 100dB allows the amplifiers to be powered directly off a decaying battery voltage, simplifying design and extending battery life.

The MAX4291/MAX4292/MAX4294 are ideally suited for use with most battery-powered systems. Table 1 lists a

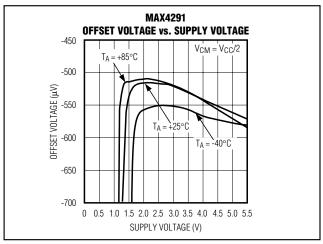

Figure 4. Offset Voltage vs. Supply Voltage

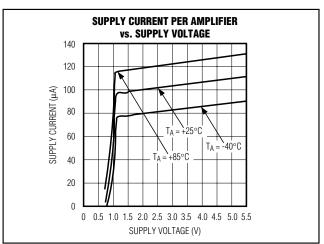

Figure 5. Supply Current per Amplifier vs. Supply Voltage

variety of typical battery types showing voltage when fresh, voltage at end-of-life, capacity, and approximate operating time from a MAX4291 (assuming nominal conditions).

Although the amplifiers are fully guaranteed over temperature for operation down to a +1.8V single supply, even lower voltage operation is possible in practice. Figures 4 and 5 show the offset voltage and supply current as a function of supply voltage and temperature.

#### **Load-Driving Capability**

The MAX4291/MAX4292/MAX4294 are fully guaranteed over temperature and supply voltage range to drive a maximum resistive load of  $2k\Omega$  to VCC/2, although heavier loads can be driven in many applications. The rail-to-rail output stage of the amplifier can be modeled

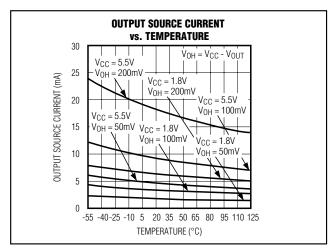

Figure 6a. Output Source Current vs. Temperature

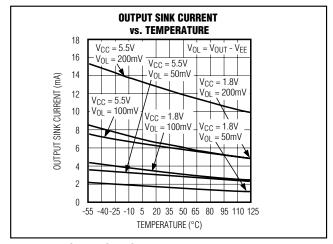

Figure 6b. Output Sink Current vs. Temperature

as a current source when driving the load toward V $_{\rm CC}$ , and as a current sink when driving the load toward V $_{\rm EE}$ . The limit of this current source/sink varies with supply voltage, ambient temperature, and lot-to-lot variations of the units.

Figures 6a and 6b show the typical current source and sink capabilities of the MAX4291/MAX4292/MAX4294 family as a function of supply voltage and ambient temperature. The contours on the graph depict the output current value, based on driving the output voltage to within 50mV, 100mV, and 200mV of either power-supply rail.

For example, a MAX4291 running from a single +1.8V supply, operating at  $T_A = +25$ °C can source 3.5mA to

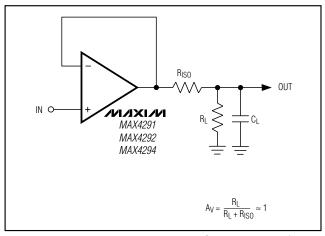

Figure 7a. Using a Resistor to Isolate a Capacitive Load from the Op Amp

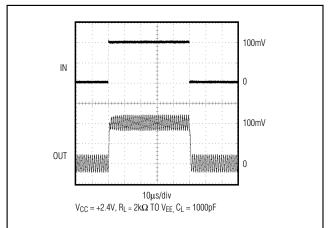

Figure 7b. Pulse Response Without Isolating Resistor

within 100mV of VCC and is capable of driving a  $485\Omega$  load resistor to VFF:

$$R_L = \frac{(1.8V - 0.1V)}{3.5mA} = 485\Omega \text{ to } V_{EE}$$

The same application can drive a 220k $\Omega$  load resistor when terminated in VCC/2 (+0.9V in this case).

#### **Driving Capacitive Loads**

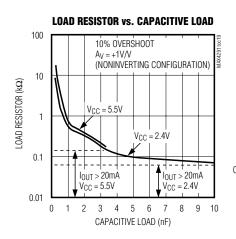

The MAX4291/MAX4292/MAX4294 are unity-gain stable for loads up to 100pF (see the Load Resistor vs. Capacitive Load graph in the *Typical Operating Characteristics*). Applications that require greater capacitive drive capability should use an isolation

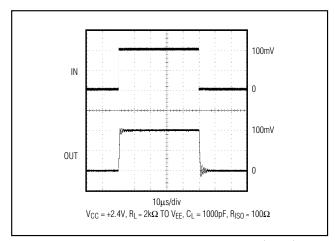

Figure 7c. Pulse Response with Isolating Resistor (100 $\Omega$ )

resistor between the output and the capacitive load (Figure 7). Note that this alternative results in a loss of gain accuracy because R<sub>ISO</sub> forms a voltage divider with the load resistor.

#### **Power-Supply Bypassing and Layout**

The MAX4291/MAX4292/MAX4294 family operates from either a single +1.8V to +5.5V supply or dual  $\pm 0.9V$  to  $\pm 2.75V$  supplies. For single-supply operation, bypass the power supply with a 100nF capacitor to VEE (in this case GND). For dual-supply operation, both the VCC and the VEE supplies should be bypassed to ground with separate 100nF capacitors.

Good PC board layout techniques optimize performance by decreasing the amount of stray capacitance at the op amp's inputs and output. To decrease stray capacitance, minimize trace lengths and widths by placing external components as close as possible to the op amp. Surface-mount components are an excellent choice.

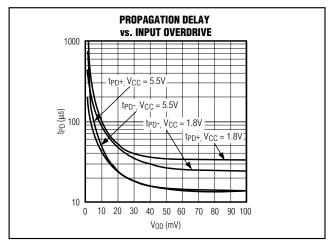

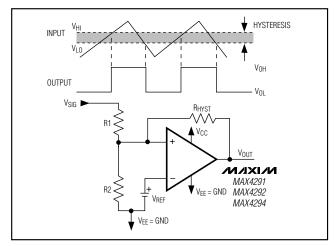

# Using the MAX4291/MAX4292/MAX4294 as Comparators

Although optimized for use as operational amplifiers, the MAX4291/MAX4292/MAX4294 can also be used as rail-to-rail I/O comparators. Typical propagation delay depends on the input overdrive voltage, as shown in Figure 8. External hysteresis can be used to minimize the risk of output oscillation. The positive feedback circuit, shown in Figure 9, causes the input threshold to change when the output voltage changes state. The two thresholds create a hysteresis band that can be calculated by the following equations:

Figure 8. Propagation Delay vs. Input Overdrive

$$\begin{split} &V_{HYST} = V_{HI} - V_{LO} \\ &V_{HI} = \left[1 + \frac{R1}{R2} + \frac{R1}{R_{HYST}}\right] V_{REF} \\ &V_{LO} = V_{HI} - \left(\frac{R1}{R_{HYST}}\right) V_{CC} \end{split}$$

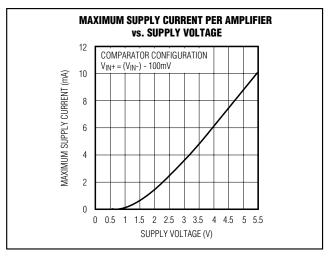

When the output of the comparator is low, the supply current increases. The output stage has biasing circuitry to monitor the output current. When the amplifier is used as a comparator, the output stage is overdriven and the current through the biasing circuitry increases to maximum. For the MAX4291, typical supply currents increase to 1.5mA with  $V_{CC} = 1.8V$  and to 9mA when  $V_{CC} = 5.0V$  (Figure 10).

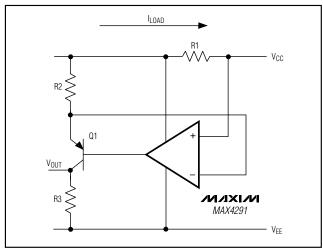

# Using the MAX4291/MAX4292/MAX4294 as Low-Power Current Monitors

The MAX4291/MAX4292/MAX4294 are ideal for applications powered from a two-cell battery stack. Figure 11 shows an application circuit in which the MAX4291 is used for monitoring the current of a two-cell battery stack. In this circuit, a current load is applied, and the voltage drop at the battery terminal is sensed.

The voltage on the load side of the battery stack is equal to the voltage at the emitter of Q1 due to the feedback loop containing the op amp. As the load current increases, the voltage drop across R1 and R2 increases. Thus, R2 provides a fraction of the load current (set by the ratio of R1 and R2) that flows into the

Figure 9. Hysteresis Comparator Circuit

Figure 10. Maximum Supply Current per Amplifier vs. Supply Voltage

emitter of the PNP transistor. Neglecting PNP base current, this current flows into R3, producing a ground-referenced voltage proportional to the load current. To minimize errors, scale R1 to give a voltage drop that is large enough in comparison to the op amp's Vos.

Calculate the output voltage of the application using the following equation:

$$V_{OUT} = \left[I_{LOAD} \times \left(\frac{R1}{R2}\right)\right] \times R3$$

For a 1V output and a current load of 50mA, the choice of resistors can be R1 =  $2\Omega$ , R2 =  $100k\Omega$ , and R3 =  $1M\Omega$ .

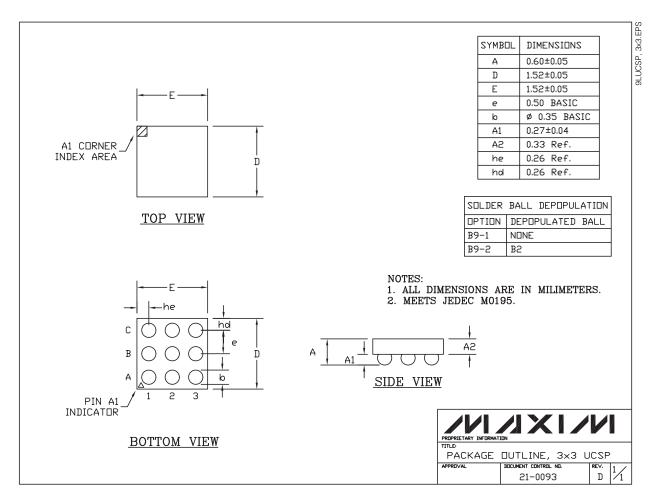

#### **UCSP Information**

#### **Layout Issues**

Design the layout for the IC to be as compact as possible to minimize parasitics. The chip-scale IC package uses a bump pitch of 0.5mm (19.7mil) and bump diameter of 0.3 (~12mil). Therefore, lay out the solder-pad spacing on 0.5mm (19.7mil) centers, using a pad size of 0.25mm (~10mil) and a solder mask opening of 0.33mm (13mil). Round or square pads are permissible. Connect multiple vias from the ground plane as close to the ground pins as possible.

Install capacitors as close as possible to the IC supply voltage pin. Place the ground end of these capacitors near the IC GND pins to provide a low-impedance return path for the signal current.

#### **Prototype Chip Installation**

Alignment keys on the PC board, around the area where the chip is located, will be helpful in the prototype assembly process. It is better to align the chip on the board before any other components are placed, and then place the board on a hot plate or hot surface until the solder starts melting. Remove the board from the hot plate without disturbing the position of the chip and let it cool down to room temperature before processing the board further.

#### **UCSP Reliability**

The chip-scale package represents a unique packaging form factor that may not perform as well as a packaged product through traditional mechanical reliability tests. UCSP reliability is integrally linked to the user's assembly methods, circuit board material, and usage environment. The user should closely review these areas when considering use of a chip-scale package.

Performance through operating-life test and moisture resistance remains uncompromised. The wafer-fabrication process primarily determines the performance. Mechanical stress performance is a greater consideration for chip-scale packages. Chip-scale packages are attached through direct solder contact to the user's PC board, foregoing the inherent stress relief of a packaged product lead frame. Solder joint contact integrity must be considered. Comprehensive reliability tests have been performed and are available upon request. In conclusion, the UCSP performs reliably through environmental stresses.

Figure 11. Current Monitor for a 2-Cell Battery Stack

#### **Marking Information**

## Pin Configurations (continued)

## **Chip Information**

MAX4291 TRANSISTOR COUNT: 149 MAX4292 TRANSISTOR COUNT: 356 MAX4294 TRANSISTOR COUNT: 747

PROCESS: BiCMOS

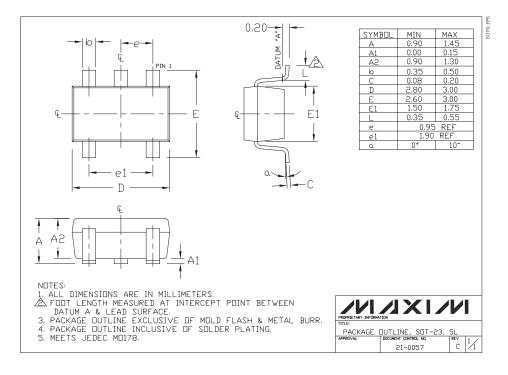

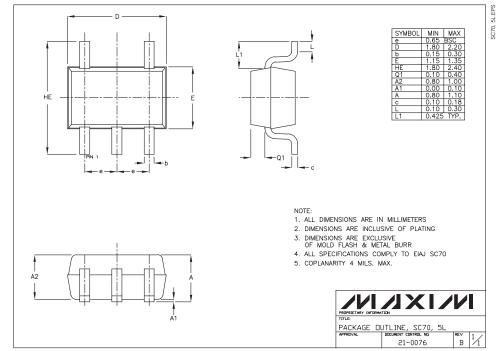

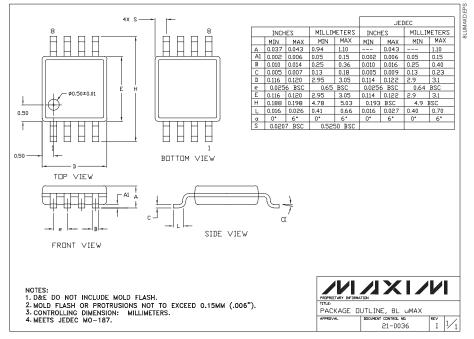

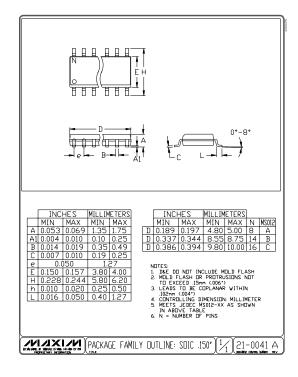

## Package Information

### Package Information (continued)

Note: The MAX4292 does not have an exposed pad.

## Package Information (continued)

Note: The MAX4294 does not have an exposed pad.

## Package Information (continued)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

18 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600