**TENTATIVE**

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

#### 8-MBIT (1M $\times$ 8 BITS / 512K $\times$ 16 BITS) CMOS FLASH MEMORY

#### DESCRIPTION

The TC58FVT800/B800 is a 8,388,608-bit, 3.0-V read-only electrically erasable and programmable flash memory organized as 1,048,576 words  $\times$  8 bits or as 524,288 words  $\times$  16 bits. The TC58FVT800/B800 features commands for Read, Program and Erase operations to allow easy interfacing with microprocessors. The commands are based on the JEDEC standard. The Program and Erase operations are automatically executed in the chip. The device has Chip, Block and Multi-Block

Erase capability.

The TC58FVT800/B800 is available in either a 44-pin plastic SOP or a 48-pin TSOP package to suit

a variety of design applications.

#### **FEATURES**

- Power Supply VDD = 2.7 V to 3.6 V

- Organization  $1M \times 8$  bits /  $512K \times 16$  bits

- Modes

Auto Program, Auto Chip Erase Auto Block Erase, Auto Multiple Block Erase Erase Suspend/Resume, Block Protection

- Data Polling/Toggle Bit

Block Erase Architecture  $1 \times 16$  Kbytes /  $2 \times 8$  Kbytes /  $1 \times 32$  Kbytes /  $15 \times 64$  Kbytes

- Boot Block Architecture TC58FVT800F/FT --- Top Boot Block TC58FVB800F/FT - Bottom Boot Block

- Mode Control

- Compatible with JEDEC standard commands

- Erase/Program Cycles 105 Cycles typ.

- Access Time

Power Dissipation

(Standby TTL level) (Standby CMOS level) 250 μA  $10 \mu A$ 30 mA (Read operation)

(Program / Erase Operations)  $40 \, \mathrm{mA}$

Package

TC58FVT800F/B800F : SOP44 - P - 600 - 1.27 (Weight: 2.0 g typ.) TC58FVT800FT/B800FT : TSOP48 - P - 1220 - 0.50

(Weight: 0.53 g typ.)

PIN ASSIGNMENT (TOP VIEW)

| RDY/BSY d 1     | 44 RESET      |                         |                                   |

|-----------------|---------------|-------------------------|-----------------------------------|

|                 |               | A15 ☐ 1 ┌               | 48 Þ <u>A16</u>                   |

| A18 🗗 2         | 43 P WE       | A14 ቑ 2 ♥               | 47 Þ BYTE                         |

| A17 🗗 3         | 42 P A8       | A13 🗗 3                 | 46 Þ ∨ss                          |

| A7 d 4          | 41 Þ A9       | A12                     | 45 P DQ15/A-1                     |

| A6 🗗 5          | 40 Þ A10      | A11 5 5                 | 44 E DQ7.                         |

| A5 🗗 6          | 39 Þ A11      | A10                     | 43 D DQ14                         |

| A4 d 7          | 38 - A12      | A9                      | 42 Þ DQ6<br>41 Þ DQ13             |

| A3 🗗 8          | 37 P A13      | ÑC 🖥 9                  | 40 F DQ5                          |

| A2 🗗 9          | 36 P A14      | NC = 10<br>WE = 11      | 39 Þ DQ12                         |

| A1 d 10         | 35 P A15      | <u>WE</u>               | 39 P DQ12<br>38 P DQ4<br>37 P VDD |

| A0 d 11         | 34 P A16      | RESET = 12              | 37 E VDD                          |

| Œ d 12          | 33 P BYTE     | NC 5 13                 | 36 P DQ11                         |

|                 | I             | NC 5 14                 | 35 Þ DÓ3<br>34 Þ DÓ10             |

| <u>Vss</u> = 13 | 32 P Vss      | RDY/BSY = 15            | 34 E DQ10                         |

| <u>OE</u>       | 31 P DQ15/A-1 | A18 🖣 16                | 33 P DQ2                          |

| DQ0 d 15        | 30 Þ DQ7      | A17 F 17                | 33                                |

| DQ8 = 16        | 29 DQ14       | A7 🗗 18                 | 31 þ DQ1                          |

|                 | 1 3           | A6 🛭 19                 | 30 Þ DQ8                          |

| DQ1 🖣 17        | 28 P DQ6      | A5 🖣 20                 | 29 Þ DQ0                          |

| DQ9 🗗 18        | 27 P DQ13     | A4 🛭 21                 | 29   <u>DÔ</u> 0<br>28   OE       |

| DQ2 🗗 19        | 26 DQ5        | A3 🖣 22                 | 27 Þ Vss                          |

| DQ10 = 20       | 25 DQ12       | A2 5 23                 | 26 E CE                           |

| DQ3 = 21        | 24 P DQ4      | A1 9 24                 | 25 Þ A0                           |

| DQ11 = 22       | 23 - VDD      | TC58FVT800FT / E        | RROOFT (TSOP)                     |

|                 |               | 1 C 3 0 1 0 0 0 1 1 / L | 300011 (13OF)                     |

| TC58FVT800F/B   | 800F (SOP)    |                         |                                   |

## PIN NAMES

| A0 to A18       | Address Input                  |

|-----------------|--------------------------------|

| DQ0 to DQ14     | Data Input/Output              |

| DQ15/A-1        | Output (Input) / Address Input |

| CE              | Chip Enable Input              |

| ŌĒ              | Output Enable Input            |

| BYTE            | Word/Byte Select Input         |

| WE              | Write Enable Input             |

| RDY/BSY         | Ready/Busy Output              |

| RESET           | Hardware Reset Input           |

| NC              | No Connection                  |

| $V_{DD}$        | Power Supply                   |

| V <sub>SS</sub> | Ground                         |

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

- The products described in this document are subject to foreign exchange and foreign trade control laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.

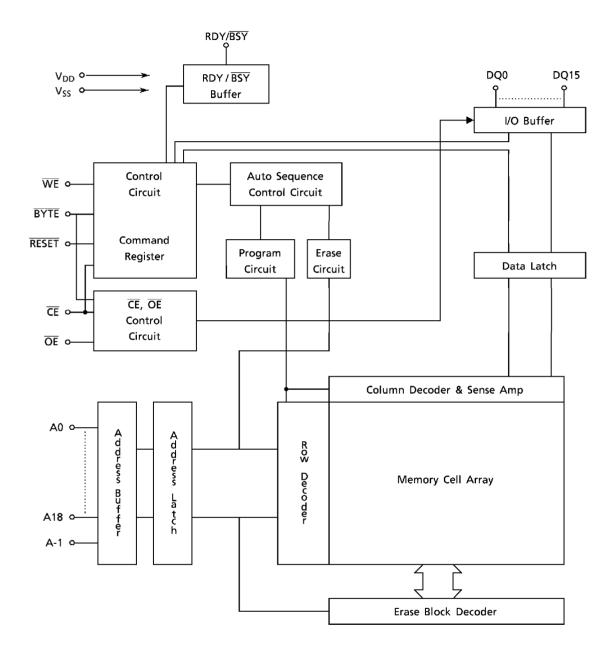

## **BLOCK DIAGRAM**

## **MODE SELECTION**

|                             |    |                 |    |                 |    |            |    |                 | BYTE MODE     | WORD MODE   |

|-----------------------------|----|-----------------|----|-----------------|----|------------|----|-----------------|---------------|-------------|

| MODE                        | CE | ŌĒ              | WE | Α9              | A6 | <b>A</b> 1 | A0 | RESET           | DQ0 to DQ7 1) | DQ0 to DQ15 |

| Read                        | L  | L               | Н  | Α9              | A6 | A1         | Α0 | Н               | Dout          | Dout        |

| ID Read (Manufacturer Code) | L  | L               | Н  | V <sub>ID</sub> | L  | ٦          | L  | Н               | Code          | Code        |

| ID Read (Device Code)       | L  | L               | Н  | V <sub>ID</sub> | L  | L          | Н  | Н               | Code          | Code        |

| Standby                     | Н  | *               | *  | *               | *  | *          | *  | Н               | High-Z        | High-Z      |

| Output Disable              | *  | Н               | Н  | *               | *  | *          | *  | *               | High-Z        | High-Z      |

| Write                       | L  | Н               | L  | A9              | A6 | <b>A</b> 1 | A0 | н               | Din           | Din         |

| Block Protect               | L  | V <sub>ID</sub> | L  | V <sub>ID</sub> | L  | Н          | L  | Н               | *             | *           |

| Verify Block Protect        | L  | L               | Н  | V <sub>ID</sub> | L  | Н          | L  | Н               | Code          | Code        |

| Temporary Block Unprotect   | *  | *               | *  | *               | *  | *          | *  | V <sub>ID</sub> | *             | *           |

| Hardware Reset/Standby      | *  | *               | *  | *               | *  | *          | *  | L               | High-Z        | High-Z      |

Notes: \* :  $V_{IH}$  or  $V_{IL}$

1) DQ8 to DQ15 are High-Z in Byte mode.

## **ID CODE TABLE**

| CODE TYPE           |                 | A18 to A12       | A6              | A1              | A0              | CODE (HEX) 1)      |

|---------------------|-----------------|------------------|-----------------|-----------------|-----------------|--------------------|

| Manufacturer Code   |                 | *                | V <sub>IL</sub> | V <sub>IL</sub> | $V_{IL}$        | 00 <b>98</b> H     |

| Device              | TC58FVT800      | *                | V <sub>IL</sub> | V <sub>IL</sub> | $V_{IH}$        | 004FH              |

| Code                | Code TC58FVB800 |                  | V <sub>IL</sub> | V <sub>IL</sub> | $V_{IH}$        | 00CEH              |

| Verfy Block Protect |                 | BA <sup>2)</sup> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Data <sup>3)</sup> |

Notes: \*:  $V_{IH}$  or  $V_{IL}$

1) DQ8 to DQ15 are High-Z in Byte mode

2) BA: Block Address

3) 0001H – Protected Block 0000H – Unprotected Block BYTE = V<sub>IL</sub> : Byte mode BYTE = V<sub>IH</sub> : Word mode

## **COMMAND DEFINITIONS**

| COMMAND<br>SEQUENCE      |       | BUS<br>WRITE<br>CYCLES | FIRST BUS<br>WRITE CYCLE |                    | SECOND BUS<br>WRITE CYCLE |      | THIRD BUS<br>WRITE CYCLE |             | FOURTH BUS READ/WRITE CYCLE |                  | FIFTH BUS<br>WRITE CYCLE |      | SIXTH BUS<br>WRITE CYCLE |      |

|--------------------------|-------|------------------------|--------------------------|--------------------|---------------------------|------|--------------------------|-------------|-----------------------------|------------------|--------------------------|------|--------------------------|------|

| 3202.11                  |       | REQ'D                  | Addr.                    | Data               | Addr.                     | Data | Addr.                    | Data        | Addr.                       | Data             | Addr.                    | Data | Addr.                    | Data |

| Read/Reset               |       | 1                      | ххххн                    | F0H                |                           |      |                          |             |                             |                  |                          |      |                          |      |

| Read/Reset               | Word  | 3                      | 5555H                    | ААН                | 2AAAH                     | 55H  | 5555H                    | F0H         | RA 1)                       | RD <sup>2)</sup> |                          |      |                          |      |

|                          | Byte  |                        | ААААН                    |                    | 5555H                     |      | ААААН                    |             |                             |                  |                          |      |                          |      |

| ID Read/<br>Verify Block | Word  | 3                      | 5555H                    | AAH                | 2AAAH                     | 55H  | 5555H                    | 90H         | IA 3)                       | ID 4)            |                          |      |                          |      |

| Protect                  | Byte  |                        | ААААН                    |                    | 5555H                     |      | ААААН                    |             |                             |                  |                          |      |                          |      |

| Auto                     | Word  | 4                      | 5555H                    | AAH                | 2AAAH                     | 55H  | 5555H                    | A0H         | PA <sup>5)</sup>            | PD <sup>6)</sup> |                          |      |                          |      |

| Program                  | Byte  |                        | ААААН                    |                    | 5555H                     |      | ААААН                    |             |                             |                  |                          |      |                          |      |

| Auto                     | Word  | 6                      | 5555H                    | ААН                | 2AAAH                     | 55H  | 5555H                    | 80H         | 5555H                       | ААН              | 2АААН                    | 55H  | 5555H                    | 10H  |

| Chip Erase               | Byte  |                        | ААААН                    |                    | 5555H                     |      | ААААН                    |             | ААААН                       |                  | 5555H                    |      | ААААН                    |      |

| Auto                     | Word  | 6                      | 5555H                    | ААН                | 2AAAH                     | 55H  | 5555H                    | <b>8</b> 0H | 5555H                       | ААН              | 2AAAH                    | 55H  | BA <sup>7)</sup>         | 30H  |

| Block Erase              | Byte  |                        | ААААН                    |                    | 5555H                     |      | ААААН                    |             | ААААН                       |                  | 5555H                    |      |                          |      |

| Block                    | Word  | 6                      | 5555H                    | ААН                | 2AAAH                     | 55H  | 5555H                    | 9AH         | 5555H                       | ААН              | 2AAAH                    | 55H  | 5555H                    | 9AH  |

| Protect                  | Byte  |                        | ААААН                    |                    | 5555H                     |      | ААААН                    |             | ААААН                       |                  | 5555H                    |      | ААААН                    |      |

| Block Erase Suspend A    |       |                        | Addr: V <sub>II</sub>    | or V <sub>II</sub> | _, Data: E                | 30H  |                          |             |                             |                  |                          |      |                          |      |

| Block Erase Re           | esume |                        | Addr: V <sub>II</sub>    | H or VII           | _, Data: 3                | 30H  |                          |             |                             |                  |                          |      |                          |      |

Notes: The system should generate the following address patterns:

Word mode: 5555H or 2AAAH to addresses A14 to A0 Byte mode: AAAAH or 5555H to addresses A14 to A-1

DQ8 to DQ15 are ignored in Word mode.

1) RA: Read Address

2) RD: Read Data

3) IA : ID Address (A6, A1, A0) 00H = Manufacturer Code

01H = Device Code

02H = Verify Block Protect (A18 to A12 = Block Address)

4) ID : ID Data

0098H – Manufacturer Code 004FH – Device Code (TC58FVT800) 00CEH – Device Code (TC58FVB800)

0001H - Protected Block 0000H - Unprotected Block

5) PA : Program Address6) PD : Program Data7) BA : Block Address

Addresses are A18 : A1 in Byte mode ( $\overline{BYTE} = V_{|L}$ ) Addresses are A18 : A0 in Word mode ( $\overline{BYTE} = V_{|H}$ )

#### HARDWARE STATUS FLAGS

|             | STATUS                       |     |        | DQ5 | DQ3 | RDY/BSY |

|-------------|------------------------------|-----|--------|-----|-----|---------|

| In Progress | Auto Programming             | DQ7 | Toggle | 0   | 0   | 0       |

|             | Auto Erase (Erase Hold Time) | 0   | Toggle | 0   | 0   | 0       |

|             | Auto Erase                   | 0   | Toggle | 0   | 1   | 0       |

| Time Limits | Auto Programming             | DQ7 | Toggle | 1   | 1   | 0       |

| Exceeded    | Auto Erase                   | 0   | Toggle | 1   | 1   | 0       |

Notes: 1. DQ outputs cell data and RDY/BSY outputs 1 when the operation has completed.

2. DQ0, DQ1 and DQ2 pins are reserved for future use.

3. DQ8 to DQ15 : Output 0 or 1 in Word mode.

4. DQ0 to DQ2 and DQ4: Output 0.

## **BLOCK ERASE ADDRESS TABLES**

TC58FVT800 (Top Boot Block)

| BLOCK # | A 10 | A 17 | A 16 | A 1 F | 0.1.4 | A 12 | A 12 | BYTE MO          | DE        | WORD MC          | DE        |

|---------|------|------|------|-------|-------|------|------|------------------|-----------|------------------|-----------|

| BLOCK # | A18  | A17  | A16  | A15   | A14   | A13  | A12  | ADDRESS RANGE    | SIZE      | ADDRESS RANGE    | SIZE      |

| BA0     | L    | L    | L    | L     | *     | *    | *    | 00000H to 0FFFFH | 64 Kbytes | 00000H to 07FFFH | 32K words |

| BA1     | L    | L    | L    | Н     | *     | *    | *    | 10000H to 1FFFFH | 64 Kbytes | 08000H to 0FFFFH | 32K words |

| BA2     | L    | L    | Н    | L     | *     | *    | *    | 20000H to 2FFFFH | 64 Kbytes | 10000H to 17FFFH | 32K words |

| BA3     | L    | L    | Н    | Н     | *     | *    | *    | 30000H to 3FFFFH | 64 Kbytes | 18000H to 1FFFFH | 32K words |

| BA4     | L    | Н    | L    | L     | *     | *    | *    | 40000H to 4FFFFH | 64 Kbytes | 20000H to 27FFFH | 32K words |

| BA5     | L    | Н    | L    | Н     | *     | *    | *    | 50000H to 5FFFFH | 64 Kbytes | 28000H to 2FFFFH | 32K words |

| BA6     | L    | Н    | Н    | L     | *     | *    | *    | 60000H to 6FFFFH | 64 Kbytes | 30000H to 37FFFH | 32K words |

| BA7     | L    | Н    | Н    | Η     | *     | *    | *    | 70000H to 7FFFFH | 64 Kbytes | 38000H to 3BFFFH | 32K words |

| BA8     | Н    | L    | L    | L     | *     | *    | *    | 80000H to 8FFFFH | 64 Kbytes | 40000H to 47FFFH | 32K words |

| BA9     | Н    | L    | L    | Н     | *     | *    | *    | 90000H to 9FFFFH | 64 Kbytes | 48000H to 4FFFFH | 32K words |

| BA10    | Н    | L    | Н    | L     | *     | *    | *    | A0000H to AFFFFH | 64 Kbytes | 50000H to 57FFFH | 32K words |

| BA11    | Н    | L    | Н    | Н     | *     | *    | *    | B0000H to BFFFFH | 64 Kbytes | 58000H to 5FFFFH | 32K words |

| BA12    | Н    | Н    | L    | L     | *     | *    | *    | C0000H to CFFFFH | 64 Kbytes | 60000H to 67FFFH | 32K words |

| BA13    | Н    | Н    | L    | Н     | *     | *    | *    | D0000H to DFFFFH | 64 Kbytes | 68000H to 6FFFFH | 32K words |

| BA14    | Н    | Н    | Н    | L     | *     | *    | *    | E0000H to EFFFFH | 64 Kbytes | 70000H to 77FFFH | 32K words |

| BA15    | Н    | Н    | Н    | Н     | L     | *    | *    | F0000H to F7FFFH | 32 Kbytes | 78000H to 7BFFFH | 16K words |

| BA16    | Н    | Н    | Н    | Н     | Н     | L    | L    | F8000H to F9FFFH | 8 Kbytes  | 7C000H to 7CFFFH | 4K words  |

| BA17    | Н    | Н    | Н    | Н     | Н     | L    | Н    | FA000H to FBFFFH | 8 Kbytes  | 7D000H to 7DFFFH | 4K words  |

| BA18    | Н    | Н    | Н    | Н     | Н     | Н    | *    | FC000H to FFFFFH | 16 Kbytes | 7E000H to 7FFFFH | 8K words  |

TC58FVB800 (Bottom Boot Block)

|           | 1   |     | 1   |     |         |     |      | DVTE MO          | D.F.      | ) NODD 146       | ND.E      |

|-----------|-----|-----|-----|-----|---------|-----|------|------------------|-----------|------------------|-----------|

| BLOCK #   | A18 | A17 | A16 | A15 | A14     | A13 | A12  | BYTE MO          | DE        | WORD MC          | DE        |

| 320 0.1 " | 70  | , , | 70  | 75  | , , , , | 75  | 71.2 | ADDRESS RANGE    | SIZE      | ADDRESS RANGE    | SIZE      |

| BA0       | L   | L   | L   | L   | L       | L   | *    | 00000H to 03FFFH | 16 Kbytes | 00000H to 01FFFH | 8K words  |

| BA1       | L   | L   | L   | L   | L       | Н   | L    | 04000H to 05FFFH | 8 Kbytes  | 02000H to 02FFFH | 4K words  |

| BA2       | L   | L   | L   | L   | L       | Н   | Н    | 06000H to 07FFFH | 8 Kbytes  | 03000H to 03FFFH | 4K words  |

| BA3       | L   | L   | L   | L   | Η       | *   | *    | 08000H to 0FFFFH | 32 Kbytes | 04000H to 07FFFH | 16K words |

| BA4       | L   | L   | L   | Н   | *       | *   | *    | 10000H to 1FFFFH | 64 Kbytes | 08000H to 0FFFFH | 32K words |

| BA5       | L   | L   | Н   | L   | *       | *   | *    | 20000H to 2FFFFH | 64 Kbytes | 10000H to 17FFFH | 32K words |

| BA6       | L   | L   | Н   | Н   | *       | *   | *    | 30000H to 3FFFFH | 64 Kbytes | 18000H to 1FFFFH | 32K words |

| BA7       | L   | Н   | L   | L   | *       | *   | *    | 40000H to 4FFFFH | 64 Kbytes | 20000H to 27FFFH | 32K words |

| BA8       | L   | Н   | L   | Н   | *       | *   | *    | 50000H to 5FFFFH | 64 Kbytes | 28000H to 2FFFFH | 32K words |

| BA9       | L   | Н   | Н   | L   | *       | *   | *    | 60000H to 6FFFFH | 64 Kbytes | 30000H to 37FFFH | 32K words |

| BA10      | L   | Н   | Н   | Н   | *       | *   | *    | 70000H to 7FFFFH | 64 Kbytes | 38000H to 3FFFFH | 32K words |

| BA11      | Н   | L   | L   | L   | *       | *   | *    | 80000H to 8FFFFH | 64 Kbytes | 40000H to 47FFFH | 32K words |

| BA12      | Н   | L   | L   | Н   | *       | *   | *    | 90000H to 9FFFFH | 64 Kbytes | 48000H to 4FFFFH | 32K words |

| BA13      | Н   | L   | Н   | L   | *       | *   | *    | A0000H to AFFFFH | 64 Kbytes | 50000H to 57FFFH | 32K words |

| BA14      | Н   | L   | Н   | Н   | *       | *   | *    | B0000H to BFFFFH | 64 Kbytes | 58000H to 5FFFFH | 32K words |

| BA15      | Н   | Н   | L   | L   | *       | *   | *    | C0000H to CFFFFH | 64 Kbytes | 60000H to 67FFFH | 32K words |

| BA16      | Н   | Н   | L   | Н   | *       | *   | *    | D0000H to DFFFFH | 64 Kbytes | 68000H to 6FFFFH | 32K words |

| BA17      | Н   | Н   | Н   | Ĺ   | *       | *   | *    | E0000H to EFFFFH | 64 Kbytes | 70000H to 77FFFH | 32K words |

| BA18      | Н   | Н   | Н   | Н   | *       | *   | *    | F0000H to FFFFFH | 64 Kbytes | 78000H to 7FFFFH | 32K words |

\* :  $V_{IH}$  or  $V_{IL}$  Addresses are A18 : A1 in Byte mode ( $\overline{BYTE} = V_{IL}$ ) Addresses are A18 : A0 in Word mode ( $\overline{BYTE} = V_{IH}$ )

## **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | PARAMETER                        | RANGE                                    | UNIT   |

|---------------------|----------------------------------|------------------------------------------|--------|

| $V_{DD}$            | V <sub>DD</sub> Supply Voltage   | -0.6 to 4.6                              | V      |

| V <sub>IN</sub>     | Input Voltage                    | $-0.6 \text{ to V}_{DD} + 0.5 (\le 4.6)$ | V      |

| V <sub>DQ</sub>     | Input / Output Voltage           | $-0.6 \text{ to V}_{DD} + 0.5 (\le 4.6)$ | V      |

| P <sub>D</sub>      | Power Dissipation                | 0.6                                      | w      |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s)     | 260                                      | °C     |

| T <sub>STG</sub>    | Storage Temperature              | -55 to 150                               | °C     |

| T <sub>OPR</sub>    | Operating Temperature            | -40 to 85                                | °C     |

| N <sub>EW</sub>     | Erase/Program Cycling Capability | 100,000                                  | Cycles |

| V <sub>IDH</sub>    | Maximum Input Voltage 1)         | 13.0                                     | V      |

| I <sub>OSHORT</sub> | Output Short Circuit Current 2)  | 100                                      | mA     |

<sup>1)</sup> V<sub>IDH</sub> supply for more than 10 seconds is not recommended. The device could be damaged.

## CAPACITANCE (Ta = 25°C, f = 1 MHz)

| SYMBOL           | PARAMETER               | CONDITION              | TYP. | MAX | UNIT |

|------------------|-------------------------|------------------------|------|-----|------|

| C <sub>IN</sub>  | Input Pin Capacitance   | V <sub>IN</sub> = 0 V  | 4    | 8   | РF   |

| C <sub>OUT</sub> | Output Pin Capacitance  | V <sub>OUT</sub> = 0 V | 10   | 12  | РF   |

| C <sub>IN2</sub> | Control Pin Capacitance | V <sub>IN</sub> = 0 V  | 8    | 10  | РF   |

This parameter is periodically sampled and is not tested for every device.

## RECOMMENDED DC OPERATING CONDITIONS (Ta = -40 to 85°C)

| SYMBOL          | PARAMETER                                | MIN                 | MAX                   | UNIT |

|-----------------|------------------------------------------|---------------------|-----------------------|------|

| $V_{DD}$        | V <sub>DD</sub> Supply Voltage           | 2.7                 | 3.6                   |      |

| V <sub>IH</sub> | Input High Level Voltage                 | 0.7 V <sub>DD</sub> | V <sub>DD</sub> + 0.5 | v    |

| V <sub>IL</sub> | Input Low Level Voltage                  | -0.3 <sup>1</sup>   | 0.8                   | ,    |

| V <sub>ID</sub> | Voltage for ID Read and Block Protect 2) | 11.4                | 12.6                  |      |

<sup>1) -2</sup> V (pulse width of 20 ns Max)

Outputs should be shorted for no more than one second. No more than one output should be shorted at a time.

<sup>2)</sup>  $V_{\text{IDH}}$  supply for more than 10 seconds is not recommended. The device could be damaged.

# <u>DC CHARACTERISTICS</u> (Ta = -40 to $85^{\circ}$ C, $V_{DD}$ = 2.7 to 3.6 V)

| SYMBOL            | PARAMETER                               | CONDITION                                                                                      | MIN                    | MAX | UNIT |

|-------------------|-----------------------------------------|------------------------------------------------------------------------------------------------|------------------------|-----|------|

| lu                | Input Leakage Current                   | $0 V \leq V_{IN} \leq V_{DD}$                                                                  | -                      | ± 1 |      |

| I <sub>LO</sub>   | Output Leakage Current                  | $0 V \leq V_{OUT} \leq V_{DD}$                                                                 |                        | ± 1 | μΑ   |

| V <sub>OH1</sub>  | Output High Voltage (TTL)               | I <sub>OH</sub> = -0.4 mA                                                                      | 2.4                    | -   |      |

| M                 | Output High Valtage (CNIOS)             | I <sub>OH</sub> = -0.1 mA                                                                      | V <sub>DD</sub> - 0.4  | -   | ]    |

| V <sub>OH2</sub>  | Output High Voltage (CMOS)              | I <sub>OH</sub> = -2.5 mA                                                                      | 0.85 × V <sub>DD</sub> | -   | ]    |

| V <sub>OL</sub>   | Output Low Voltage                      | I <sub>OL</sub> = 4.0 mA                                                                       | _                      | 0.4 |      |

| I <sub>DDO1</sub> | V <sub>DD</sub> Average Read Current    | $V_{IN} = V_{IH} / V_{IL}$ , $I_{OUT} = 0 \text{ mA}$<br>$CYCLE = t_{RC} \text{ (min)}$        | _                      | 30  |      |

| I <sub>DDO2</sub> | V <sub>DD</sub> Average Program Current | $V_{IN} = V_{IH} / V_{IL}$ , $I_{OUT} = 0 \text{ mA}$                                          | -                      | 40  | mA   |

| I <sub>DDO3</sub> | V <sub>DD</sub> Average Erase Current   | $V_{IN} = V_{IH} / V_{IL}$ , $I_{OUT} = 0 \text{ mA}$                                          | -                      | 40  |      |

| I <sub>DDS1</sub> | V <sub>DD</sub> Standby Current (TTL)   | $\overline{CE} = \overline{RESET} = V_{IH} \text{ or } \overline{RESET} = V_{IL}$              | _                      | 250 |      |

| I <sub>DDS2</sub> | V <sub>DD</sub> Standby Current (CMOS)  | $\overline{CE} = \overline{RESET} = V_{DD} \pm 0.2 V$ or $\overline{RESET} = V_{SS} \pm 0.2 V$ | _                      | 10  | μΑ   |

| I <sub>ID</sub>   | High Voltage Input Current              | $11.4 \text{ V} \leq \text{ V}_{\text{ID}} \leq 12.6 ^{-1}$                                    | _                      | 200 |      |

| V <sub>LKO</sub>  | Low V <sub>DD</sub> Lock-out Voltage    | -                                                                                              |                        | 2.5 | V    |

<sup>1)</sup> Less than 10 seconds

## **AC TEST CONDITIONS**

| PARAMETER                                   | CONDITION                            |  |  |  |

|---------------------------------------------|--------------------------------------|--|--|--|

| Input Pulse Level                           | 2.4 V / 0.4 V                        |  |  |  |

| Input Pulse Rise and Fall Time (10% to 90%) | 5 ns                                 |  |  |  |

| Timing Measurement Reference Level (Input)  | 1.5 V / 1.5 V                        |  |  |  |

| Timing Measurement Reference Level (Output) | 1.5 V / 1.5 V                        |  |  |  |

| Output Load                                 | C <sub>L</sub> (100 pF) + 1 TTL Gate |  |  |  |

## AC CHARACTERISTICS AND OPERATING CONDITIONS

|                    | PARAMETER                                                           | -85                                        |     | -10    |                       | -12        |     |         |

|--------------------|---------------------------------------------------------------------|--------------------------------------------|-----|--------|-----------------------|------------|-----|---------|

|                    |                                                                     | $Ta = -40 \text{ to } 85 ^{\circ}\text{C}$ |     |        |                       |            |     | T       |

| SYMBOL             |                                                                     | $V_{DD} = 3.0 \text{ to } 3.6 \text{ V}$   |     |        | V <sub>DD</sub> = 2.7 | 7 to 3.6 V |     | UNIT    |

|                    |                                                                     | MIN                                        | MAX | MIN    | MAX                   | MIN        | MAX |         |

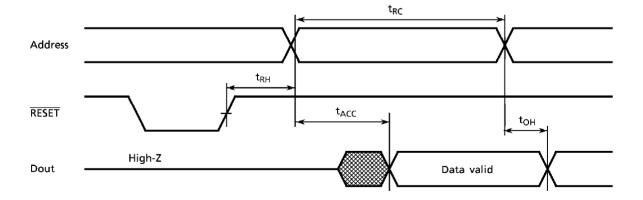

| t <sub>RC</sub>    | Read Cycle Time                                                     | <b>8</b> 5                                 | _   | 100    | _                     | 120        | -   | ns      |

| t <sub>ACC</sub>   | Address Access Time                                                 | _                                          | 85  | -      | 100                   | -          | 120 | ns      |

| t <sub>CE</sub>    | CE Access Time                                                      | _                                          | 85  | -      | 100                   | -          | 120 | ns      |

| t <sub>OE</sub>    | OE Access Time                                                      | -                                          | 35  | -      | 40                    | -          | 50  | ns      |

| t <sub>CEE</sub>   | CE to Output Low-Z                                                  | 0                                          | -   | 0      | -                     | 0          | _   | ns      |

| t <sub>OEE</sub>   | OE to Output Low-Z                                                  | 0                                          | -   | 0      | -                     | 0          | -   | ns      |

| t <sub>OEH</sub>   | OE Hold Time (Read)                                                 | 0                                          | -   | 0      | -                     | 0          | -   | ns      |

| toH                | Output Data Hold Time                                               | 0                                          | -   | 0      | _                     | 0          | _   | ns      |

| t <sub>DF1</sub>   | CE to Output High-Z                                                 | _                                          | 30  | -      | 30                    | _          | 30  | ns      |

| t <sub>DF2</sub>   | OE to Output High-Z                                                 | _                                          | 30  | -      | 30                    | _          | 30  | ns      |

| t <sub>CMD</sub>   | Command Write Cycle Time                                            | 85                                         | -   | 100    | -                     | 120        | _   | ns      |

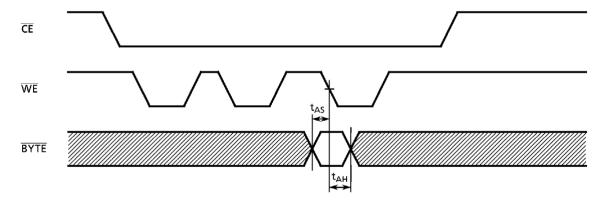

| t <sub>AS</sub>    | Address Setup Time                                                  | 0                                          | -   | 0      | -                     | 0          | _   | ns      |

| t <sub>AH</sub>    | Address Hold Time                                                   | 45                                         | -   | 50     | -                     | 50         | -   | ns      |

| t <sub>DS</sub>    | Data Setup Time                                                     | 45                                         | -   | 50     | _                     | 60         | _   | ns      |

| t <sub>DH</sub>    | Data Hold Time                                                      | 0                                          | _   | 0      | _                     | 0          | _   | ns      |

| t <sub>WELH</sub>  | WE Low Level Hold Time *                                            | 45                                         | _   | 50     | _                     | 50         | _   | ns      |

| t <sub>WEHH</sub>  | WE High Level Hold Time *                                           | 20                                         | _   | 20     | _                     | 20         | _   | ns      |

| t <sub>CES</sub>   | CE Setup Time to WE Active *                                        | 0                                          | _   | 0      | -                     | 0          | _   | ns      |

| t <sub>CEH</sub>   | CE Hold Time from WE High Level *                                   | 0                                          | _   | 0      | _                     | 0          | _   | ns      |

| t <sub>OES</sub>   | OE Setup to WE Active                                               | 0                                          | _   | 0      | _                     | 0          | _   | ns      |

| t <sub>OEHP</sub>  | OE Hold Time (Toggle/Data Polling)                                  | 10                                         | _   | 10     | _                     | 10         | _   | ns      |

| t <sub>OEHT</sub>  | OE High Level Hold Time (Toggle)                                    | 20                                         | _   | 20     | _                     | 20         | _   | ns      |

| t <sub>PPW</sub>   | Auto Program Time                                                   | 16 **                                      | _   | 16 **  | _                     | 16 **      | _   | μS      |

| t <sub>PCEW</sub>  | Auto Chip Erase Time                                                | 28 **                                      | _   | 28 **  | _                     | 28 **      | _   | S       |

| t <sub>PBEW</sub>  | Auto Block Erase Time                                               | 1.5 **                                     | _   | 1.5 ** | _                     | 1.5 **     | _   | s       |

| t <sub>VDS</sub>   | V <sub>DD</sub> Setup Time                                          | 500                                        | _   | 500    | _                     | 500        | _   | μS      |

| t <sub>BUSY</sub>  | Program / Erase Valid to RDY / BSY Delay                            | 35                                         | _   | 40     | _                     | 50         | _   | ns      |

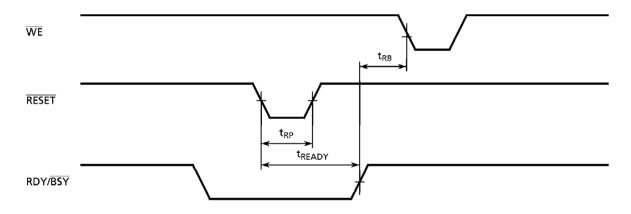

| t <sub>RP</sub>    | RESET Low Level Hold Time                                           | 500                                        | _   | 500    | _                     | 500        | _   | ns      |

| t <sub>READY</sub> | RESET Low Level to Read Mode                                        |                                            | 20  | _      | 20                    | _          | 20  | μS      |

| t <sub>RB</sub>    | RDY/BSY Recovery Time                                               | 0                                          | _   | 0      | _                     | 0          | _   | ns      |

|                    | RESET Recovery Time                                                 | 500                                        | _   | 500    | _                     | 500        | _   | ns      |

| t <sub>RH</sub>    | CE Setup time BYTE Transition                                       | 5                                          |     | 5      |                       | 5          | _   | ns      |

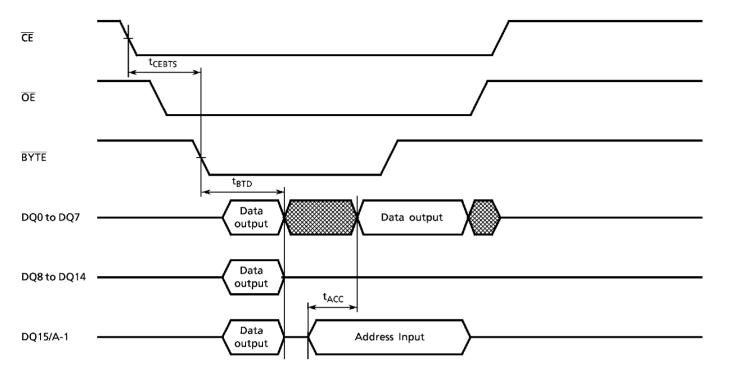

| t <sub>CEBTS</sub> | BYTE to Output High-Z                                               |                                            | 30  |        | 30                    | _          | 30  | ns      |

| t <sub>BTD</sub>   | V <sub>ID</sub> Transition Time                                     | 4                                          | -   | 4      | -                     | 4          | -   |         |

| t <sub>VPT</sub>   | V <sub>ID</sub> Setup Time                                          | 4                                          |     | 4      |                       | 4          | _   | μS      |

| t <sub>VPS</sub>   |                                                                     | 8                                          | _   | 8      | _                     | 8          |     | <i></i> |

| t <sub>VPH</sub>   | OE Hold Time (Block Protect) WE Low Level Hold Time (Block Protect) | 100                                        | -   | 100    | -                     |            | -   | μS      |

| t <sub>PPLH</sub>  | •                                                                   | 0                                          |     |        |                       | 100        | _   | μS      |

| t <sub>PAS</sub>   | Protect Address Setup Time                                          |                                            | _   | 0      | _                     | 0          | -   | ns      |

| t <sub>PAH</sub>   | Protect Address Hold Time                                           | 0                                          | -   | 0      | -                     | 0          | -   | ns      |

| t <sub>CESP</sub>  | CE Setup Time (Block Protect)                                       | 4                                          | _   | 4      | _                     | 4          | _   | μS      |

| t <sub>CEHP</sub>  | CE Hold Time (Block Protect)                                        | 8                                          | _   | 8      | -                     | 8          | -   | μS      |

## **OPERATING MODES**

#### READ MODE

When the device is set to Read mode, it acts as an asynchronous ROM with an access time of 85/100/120 ns. The device is set to Read mode at power-on or when an Auto-Program/Erase operation completes. A software or hardware reset is necessary to return the device to Read mode when an Auto Program/Erase operation fails.

#### STANDBY MODE

There are two methods of entering Standby mode: the first involves using both  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$  and the second using only  $\overline{\text{RESET}}$ .

The first method involves using  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$  for mode control. If  $V_{DD} \pm 0.2~V$  (CMOS level) is applied to  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$  when the device is operating in Read mode, the current is reduced below 10  $\mu$ A. Similarly, if  $V_{IH}$  (TTL level) is applied to  $\overline{\text{CE}}$  and  $\overline{\text{RESET}}$ , the current is reduced below 250  $\mu$ A. When using  $\overline{\text{CE}}$  for control, make sure that the device is operating in Read mode; otherwise, it is not possible to enter Standby mode.

The second method involves using only  $\overline{RESET}$  for mode control. IF  $V_{SS}\pm0.2$  V (CMOS level) is applied to  $\overline{RESET}$  when the device is operating in Read mode, the current is reduced below 10  $\mu$ A. Similarly, if  $V_{IL}$  (TTL level) is applied to  $\overline{RESET}$ , the current is reduced below 250  $\mu$ A. The difference the control method using  $\overline{CE}$  described above, is that if  $V_{IL}$  is applied to  $\overline{RESET}$  when the device is operating in any mode other than Read mode, it enters Standby mode after stopping the operating which is currently being executed. This is a hardware reset and is described later.

In standby mode, DQ is put in high-impedance state.

#### COMMAND WRITE

The TC58FVT800/B800 utilizes the JEDEC command control standard for a single power supply E²PROM. A command is executed by inputting an address and data into the Command register. The command is entered by a  $\overline{WE}$  Control Write ( $\overline{WE}$  pulse with  $\overline{CE} = V_{IL}$  and  $\overline{OE} = V_{IH}$ ) or a  $\overline{CE}$  Control Write ( $\overline{CE}$  pulse with  $\overline{WE} = V_{IL}$  and  $\overline{OE} = V_{IH}$ ). The address is latched on the falling edge of either  $\overline{WE}$  or  $\overline{CE}$ . I/O0 to 7 are valid for data input and I/O8 to 15 are ignored.

A command is when the Reset command is input. The device then enters Read Mode. When an undefined command is input, the Command register is reset and the device enters Read mode.

#### RESET (Software Reset)

The device does not enter Read mode automatically when a command such as Auto Program/Erase or ID Read is not correctly executed (for example, if Program or Erase fails). The Reset or Read Command is necessary to return the device to Read mode. The Reset and Read commands must also be used to reset the Command register.

#### RESET (Hardware Reset)

A hardware reset is used for aborting Auto mode operations such as Auto Program/Erase and for resetting the operation mode. The device enters Read mode 20  $\mu$ s after a 500-ns Low level input pulse to the  $\overline{RESET}$  pin. Data may be corrupted if the device is reset during an Auto mode operation.

After a hardware reset the device enters Read mode when  $\overline{RESET} = V_{IH}$  and Standby mode when  $\overline{RESET} = V_{IL}$ . The I/O pins are High-Impedance when  $\overline{RESET} = V_{IL}$ . The Read operation sequence and input of any command are allowed after the device enters Read mode.

#### ID READ MODE

The ID Read mode is used to establish the device type. The ID Read mode is set either from the Command mode by inputting a 90H command or from the EPROM mode by applying  $V_{\rm ID}$  to the A9 pin.

When A0, A1 and A6 =  $V_{\rm IL}$ , the data that is read is the manufacturer code (0098H). When A0 =  $V_{\rm IH}$  and A1 and A6 =  $V_{\rm IL}$ , the data that is read is the device code (4FH). The access time for an ID Read is the same as that of a normal Read operation. I/O8 to 15 are in High-Impedance state in Byte mode. Either a reset command or a hardware reset is necessary to return the device to Read mode.

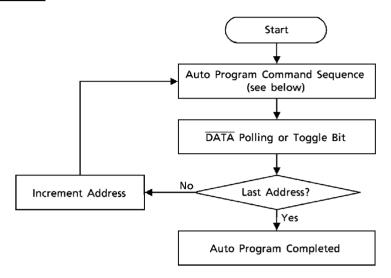

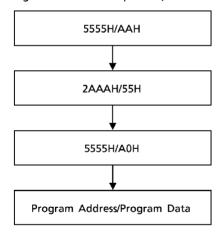

#### AUTO PROGRAM MODE

The TC58FVT800/B800 can be programmed in either byte or word units. The Auto Program mode is set using the Program command. The program address is latched on the falling edge of the  $\overline{WE}$  signal and data is latched on the rising edge of the fourth bus cycle. Auto programming starts on the rising edge of the  $\overline{WE}$  signal in the fourth bus cycle. The Program and Program Verify commands are automatically executed by the chip. The device status during programming is determined from the Hardware Sequence flag.

Programming of a protected block is ignored. The device enters Read mode  $3 \mu s$  after the rising edge of the  $\overline{WE}$  signal in the fourth bus cycle.

The device allows the programming of memory cells from 1 to 0. The programming of Memory cells from 0 to 1 will fail. A cell must be erased to turn it from 0 to 1.

If an Auto Program operation fails, the device remains in programming state and does not automatically return to Read mode. The device status can be determined from the setting of the Hardware Sequence flag. Either a Reset command or a hardware reset is necessary to return the device to Read mode after a failure.

If a programming operation fails, please do not try to use the block which contains the address to which data could not be programmed.

#### Auto Chip Erase Mode

The Auto Chip Erase mode is set using the Chip Erase command. The Auto Chip Erase operation starts on the rising edge of WE in the sixth bus cycle. All memory cells are automatically preprogrammed to 0, erased and verified as erased by the chip. The device status is determined from the Hardware Sequence flag.

Command inputs are ignored during an Auto Chip Erase. The hardware reset allows interruption of an Auto Chip Erase operation. The Auto Chip Erase operation does not complete correctly when interrupted. Hence a further Erase operation is necessary.

An attempt to erase a protected block is ignored. If all blocks are protected, the Auto Erase operation will not be executed and the device will enter Read mode  $100 \,\mu s$  after the rising edge of the  $\overline{WE}$  signal in the sixth bus cycle.

If an Auto Chip Erase operation fails, the device remains in, erasing state and does not return to Read mode. The device status is determined from the Hardware Sequence flag. Either a Reset command or a hardware reset is necessary to return the device to Read mode after a failure.

#### Auto Block / Multi Block Erase Mode

The Auto Block and Multi Block Erase modes are set using the Block Erase command. The block address is latched on the falling edge of the  $\overline{WE}$  signal in the sixth bus cycle. The Block Erase starts as soon as the hold time has elapsed after the rising edge of the  $\overline{WE}$  signal. All memory cells in the selected block are automatically programmed to 0, erased and verified as erased by the chip. The Multi Block Erase operation allows erasing of multiple blocks. Any additional block addresses or Multi Block Erase commands must be input within the Erase Hold Time - that is, within 50  $\mu$ s of any  $\overline{WE}$  signal rising edge. The device status can be determined from the setting of the Hardware Sequence flag.

Commands (except Erase Suspend) are ignored during a Block/Multi Block Erase operation. The operation can be aborted by a hardware reset. The Auto Erase operation does not complete correctly when aborted, therefore, a further Erase operation is necessary.

An attempt to erase a protected block is ignored. If all the selected blocks are protected, the Auto Erase operation is not executed and the device returns to Read mode 100  $\mu$ s after the rising edge of the  $\overline{\text{WE}}$  signal in the last bus cycle.

If an Auto Erase operation fails, the device remains in erasing state and does not return to Read mode. The device status is determined from the Hardware Sequence flag. Either a Reset command or a hardware reset is necessary to return the device to Read mode after a failure.

#### Erase Suspend/Resume Mode

The Erase Suspend mode is used to read data from a block not selected for erasing. The Erase Suspend command is allowed during a Block Erase operation or during the Block Erase Hold Time; it is ignored in other operation modes. A Block Erase operation is also suspended if the Suspend command is input during the Block Erase Hold Time. The device is reset if any command other than Suspend is input. The suspended device recognizes only Read and Resume commands.

The device enters Suspend mode 15  $\mu$ s after the Erase Suspend command is input. The device then enters a pseudo-Read Mode. Data can be read out from an unselected block but is invalid if the address is set to a block selected for erasing. The device status can be determined from the Hardware Sequence flag. DQ6 (the toggle bit) stops toggling and RDY/BSY outputs 1 once the device is set to pseudo-Read mode. The host processor must track the current device mode since there is no way of telling whether the device is in pseudo-or ordinary Read mode. The device remains in pseudo-Read mode even if a Suspend command is input.

The device restarts the Block Erase operation after receiving a Resume command. The device returns to the status in which the Suspend command was input. The DQ6 output toggles and RDY/BSY outputs a 0.

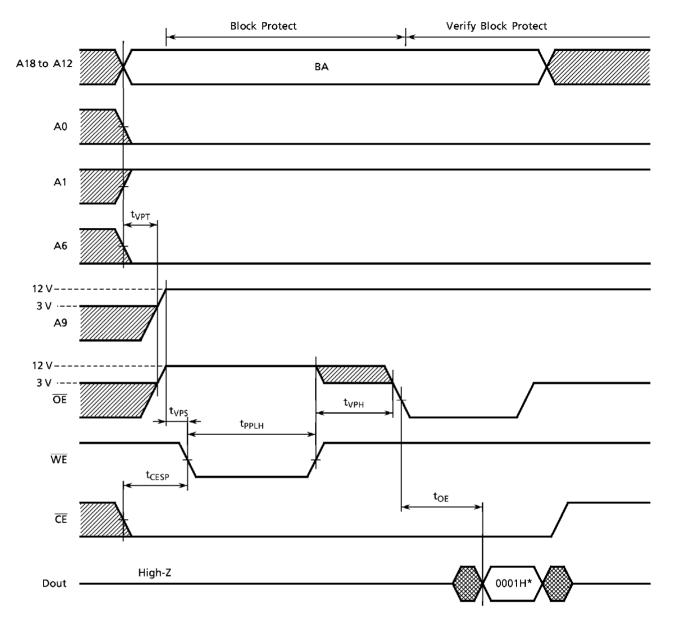

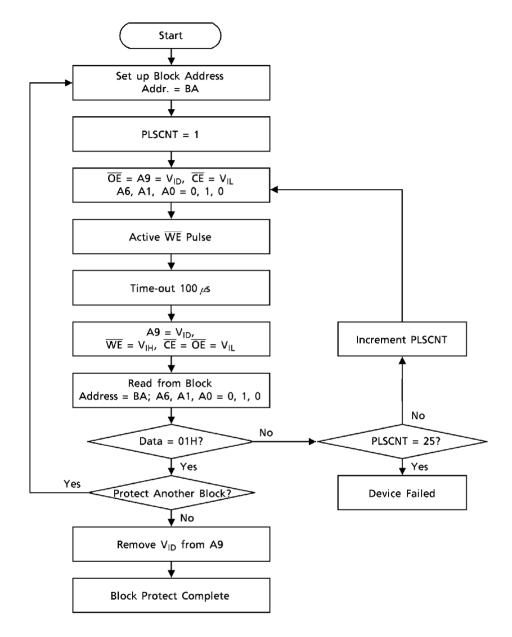

#### BLOCK PROTECT

The TC58FVT800/B800 has a block protection feature to prevent programing and erasing of protected blocks. Block protection is enabled by either hardware protection (1) or a software command mode (2). The initial device is shipped with all blocks unprotected.

- (1) A blocks is protected when:  $A9 = \overline{OE} = V_{ID}$ ,  $\overline{CE} = V_{IL}$ ,  $A0 / A6 = V_{IL}$ ,  $A1 = V_{IH}$ ; the block address is set using A12 to A18. The block protect data is programmed within tppLH of the  $\overline{WE}$  signal going Low.

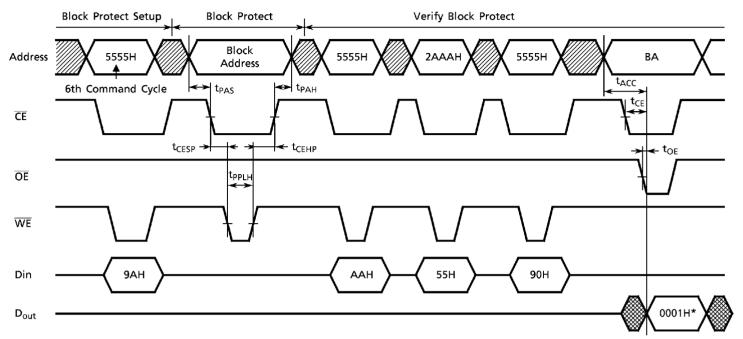

- (2) A block can also be protected using a software command. Block protection is executed by setting the  $\overline{WE}$  signal to Low for  $t_{PPLH}$  while  $\overline{CE} = V_{IL}$ . After the command input in the sixth bus cycle A12 to A18 = the block address. Block protection can be verified using the Verify Block Protect command.

#### TEMPORARY BLOCK UNPROTECTION

The TC58FVT800/B800 has a temporary block unprotection feature which disables block protection for all protected blocks. Unprotection is enabled by applying  $V_{ID}$  to the  $\overline{RESET}$  pin. In this state any block can be programmed or erased. The device returns to the previous condition after  $V_{ID}$  is removed from the  $\overline{RESET}$  pin. That is, previously protected blocks are protected again.

#### VERIFY BLOCK PROTECT

The Verify Block Protect command is used to check whether a block is protected or unprotected. Verify Block Protect is enabled either through hardware (1) or by a software command (2). In Word mode 0001H is output when the block is protected and 0000H is output when it is unprotected. I/O8 to 15 are High-Impedance in Byte mode.

- (1) Verify Block Protection is enabled when:  $A9 = V_{ID}$ , A0 and  $A6 = V_{IL}$  and  $A1 = V_{IH}$ . A12 to A18 = the block address.

- (2) Verify Block Protection can also be enabled using a software command.

#### HARDWARE SEQUENCE FLAG

The TC58FVT800/B800 has a Hardware Sequence flag which allows the device status to be determined during Auto operation. The output data is read out with the same timing as Read mode at  $\overline{CE} = \overline{OE} = V_{IL}$ . RDY/ $\overline{BSY}$  outputs either High or Low.

The device re-enters the Read mode automatically after Auto operation has completed successfully. The device status is read out from the Hardware Sequence flag and the operation result is verified by comparing the read-out data to the original data.

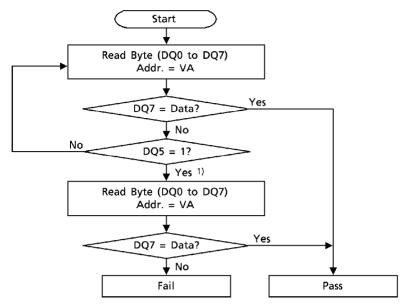

#### DQ7 (DATA Polling)

The device status can be determined using the data polling function during an Auto Program or Auto Erase operation.  $\overline{DATA}$  polling begins on the rising edge of  $\overline{WE}$  in the last bus cycle. In an Auto Program operation, DQ7 outputs inverted data during the programming operation and outputs real data after programming has finished. In an Auto Erase operation, DQ7 outputs 0 during the Erase operation and outputs 1 when the Erase operation has finished. If an Auto Program operation fails, DQ7 simply outputs the data.

The latched address is reset after an operation has finished. The polling data is asynchronous with the  $\overline{OE}$  signal.

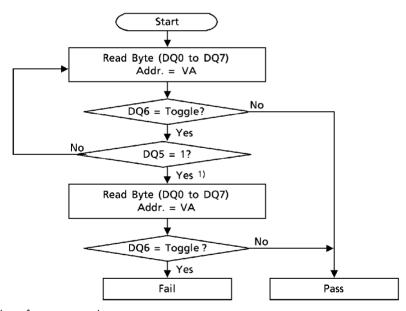

#### DQ6 (Toggle Bit)

The device status can be determined by the Toggle Bit function during an Auto Program or Auto Erase operation. In an Auto Program operation the Toggle bit begins toggling on the rising edge of  $\overline{WE}$  in the last bus cycle. In an Auto Erase operation The Toggle bit begins toggling as soon as the Erase Hold Time has elapsed after the rising edge of the  $\overline{WE}$  signal in the last bus cycle. DQ6 alternately outputs a 0 or a 1 for each attempt ( $\overline{OE}$  access) while  $\overline{CE} = V_{IL}$  while the device is busy. When the internal operation has been completed, toggling stops and valid memory cell data can be read by subsequent reading. If the operation failed, the DQ6 output toggles.

DQ6 toggles for around  $3\,\mu s$  when an attempt is made to execute an Auto Program operation on a protected block. It then stops toggling. DQ6 toggles for around  $100\,\mu s$  when an attempt is made to execute an Auto Erase operation on a protected block. It then stops toggling. After toggling stops the device returns to Read mode.

#### DQ5 (Internal Time-out)

DQ5 outputs a 1 when the Internal Timer has timed out during a Program or Erase operation. This indicates that the operation has not completed within the allotted time.

An attempt to program 1 into a cell containing 0 will fail (see Auto Program mode). DQ5 outputs 1 in this case. Either a hardware reset or a software Reset command is required to put the device into Read mode.

#### DQ3 (Block Erase Timer)

The Block Erase operation starts 50  $\mu$ s (Erase Hold Time) after the rising edge of  $\overline{\text{WE}}$  in the last command cycle. DQ3 outputs a 0 during the Block Erase Hold Time and a 1 when the Erase operation starts. Additional Block Erase commands can only be accepted during this Block Erase Hold Time. Each Block Erase command received within this hold time resets the timer, allowing additional blocks to be marked for erasing. DQ3 outputs a 1 if the Program or Erase operation fails.

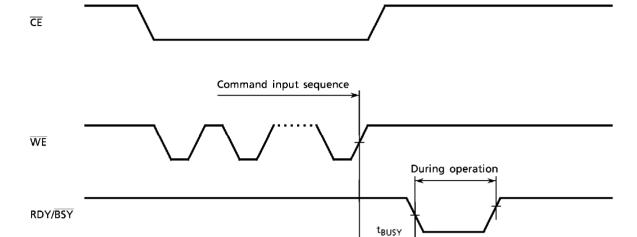

#### RDY/BSY (READY/BUSY)

TC58FVT800/B800 has a RDY/BSY signal to indicate the device status to the host processor. A 0 (Busy state) indicates that an Auto Program or Auto Erase operation is in progress. A 1 (Ready state) indicates that the operation has finished and that the device can accept a new command. The RDY/BSY signal outputs a 0 when an operation has failed.

The RDY/BSY signal outputs a 0 after the rising edge of WE in the last command cycle of a Program operation and during the Erase Hold Time after the last command cycle of an Erase operation.

During an Auto Block Erase operation, commands other than Erase Suspend are ignored. The RDY/ $\overline{BSY}$  signal outputs a 1 during an Erase Suspend operation. The output buffer for the RDY/ $\overline{BSY}$  pin is an open drain type circuit, allowing a wired-OR connection. A pull-up resistor needs to be inserted between  $V_{DD}$  and the RDY/ $\overline{BSY}$  pin.

#### DATA PROTECTION

The TC58FVT800/B800 utilizes a JEDEC standard command sequence which protects data against accidental alteration due to noise.

#### V<sub>DD</sub> Lock-out Voltage

The device is reset when  $V_{DD}$  is less than  $V_{LKO}$  to protect memory cell data against  $V_{DD}$  noise, and during power-up and power-down. An Auto Program or Erase operation stops when  $V_{DD}$  drops below  $V_{LKO}$ . An Erase Suspend operation is reset and an Erase operation stops if the device is in Suspend mode. An operation will not complete correctly if it is interrupted by  $V_{DD}$  Lock-out.

#### WE Glitch Pulses

Glitches must be suppressed (to less than 5 ns) in order for operation to proceed smoothly.

#### Protection at Power-on

A command is not recognized on the rising edge of  $\overline{WE}$  if  $V_{DD}$  rises from 0 V to the operating voltage while  $\overline{WE} = V_{IL}$ ,  $\overline{CE} = V_{IL}$  and  $\overline{OE} = V_{IH}$ . In this case the device is reset and enters Read mode.

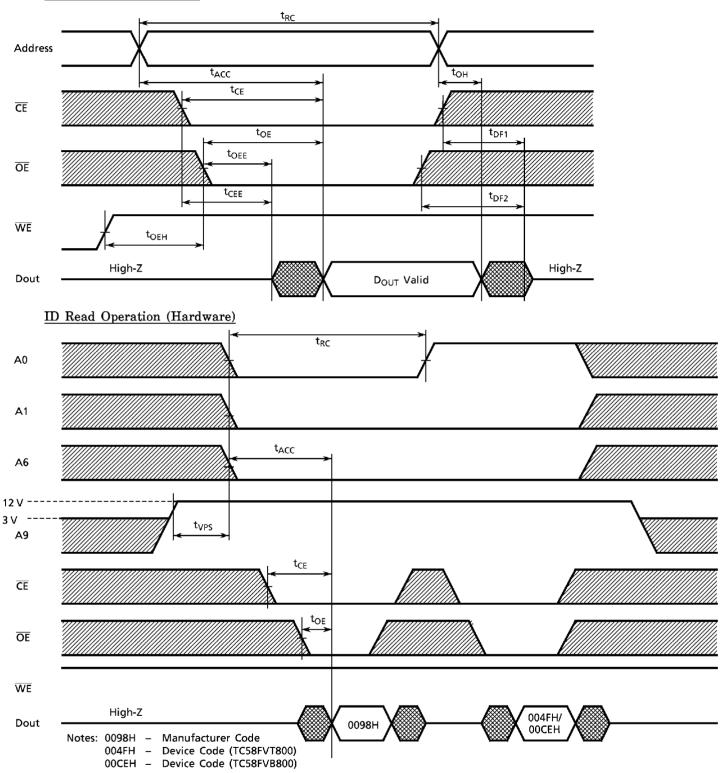

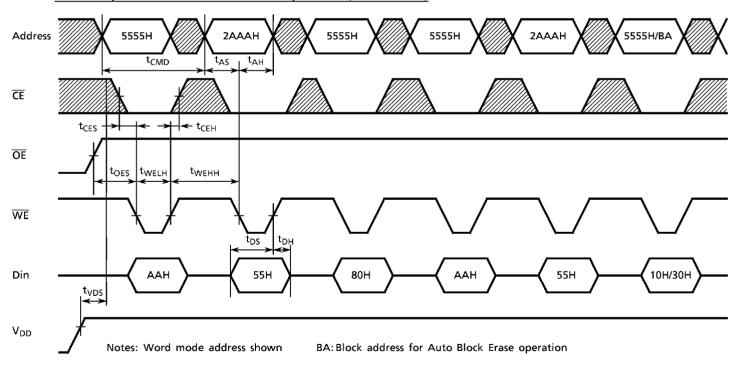

## **TIMING DIAGRAMS**

## Read/ID Read Operation

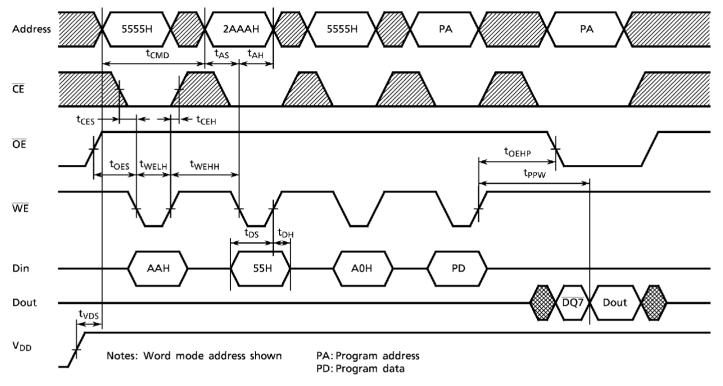

## Auto Program Operation (WE Control)

## Auto Chip Erase / Auto Block Erase Operation (WE Control)

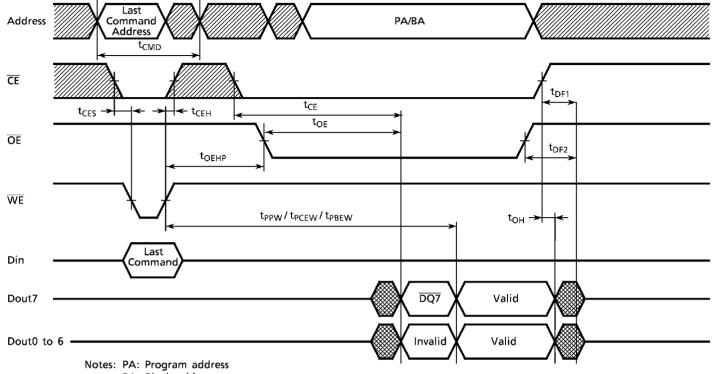

## DATA Polling during Program/Erase Operation

BA: Block address

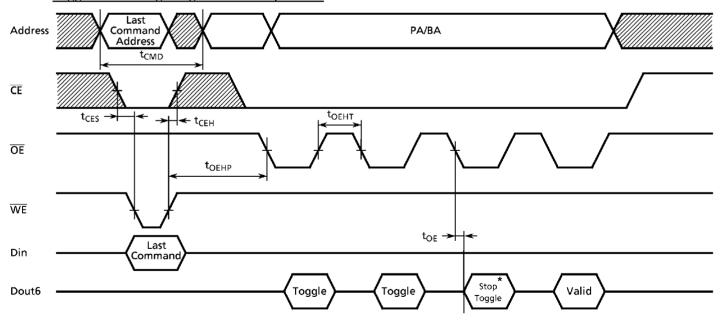

## Toggle Bit during Program/Erase Operation

Dout6 stops toggling when the last command has completed.

Notes: PA: Program address BA: Block address

## RDY/BSY during Auto Program/Erase Operation

## Hardware Reset Operation

## Read after RESET

## BYTE during Read Operation

## BYTE during Write Operation

## Block Protect Operation (Hardware)

BA: Block address

\*: 0001H indicates that block is protected.

## **TOSHIBA**

## Block Protect (Software)

BA: Block address

\* : 0001H indicates that block is protected.

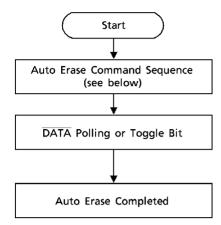

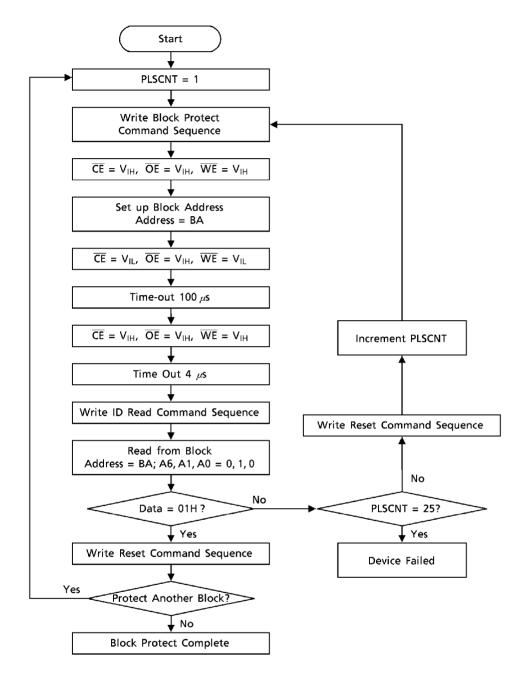

## **FLOWCHARTS**

## Auto Program

## Auto Program Command Sequence (Address/Command)

Note: Word mode command sequence is shown.

#### Auto Erase

Auto Chip Erase Command Sequence Auto Block/Multiple Block (Address/Command) Erase Command Sequence (Address/Command) 5555H/AAH 5555H/AAH 2AAAH/55H 2AAAH/55H 5555H/80H 5555H/80H 5555H/AAH 5555H/AAH 2AAAH/55H 2AAAH/55H 5555H/10H Block Address/30H Block Address/30H Additional Block Erase commands are optional Block Address/30H

Note: Word mode command sequence is shown.

## DQ7 DATA Polling

VA: Byte address for programming.

Any of the addresses within the block being erased during a Block Erase operation.

Don't care during a Chip Erase operation

Note: 1) DQ7 must be rechecked even if DQ5 = 1 because DQ7 may change at the same time as DQ5.

#### DQ6 Toggle Bit

VA: Byte address for programming.

Any of the addresses within the block being erased during a Block Erase operation.

Don't care during a Chip Erase operation

Any address not within the current block during an Erase Suspend operation

Note: 1) DQ6 must be rechecked even if DQ5 = 1 because DQ6 may stop toggling at the same time that DQ5 changes to 1.

#### Block Protect (Hardware)

BA: Block address

#### Block Protect (Software)

BA: Block Address

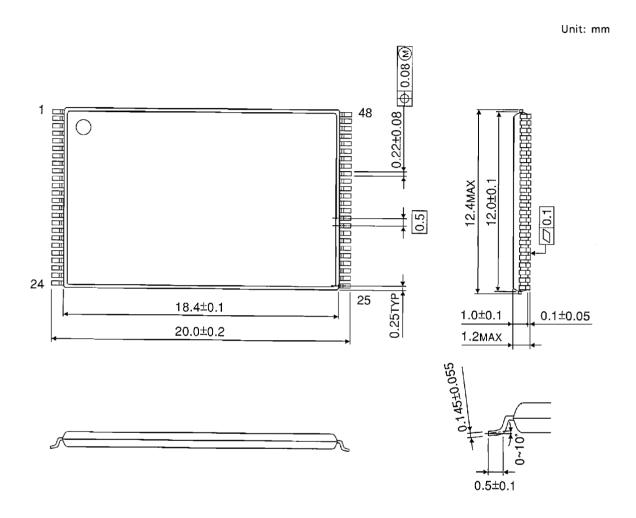

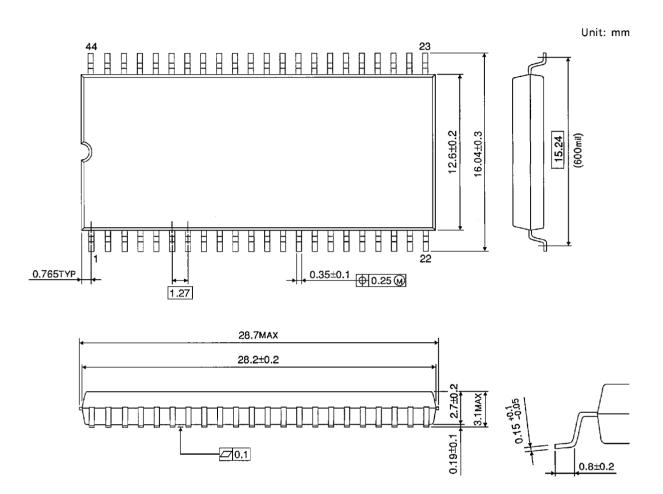

## **PACKAGE DIMENSIONS**

• Plastic SOP

SOP44-P-600-1.27

## **PACKAGE DIMENSIONS**

• Plastic TSOP

TSOP I 48-P-1220-0.50