### MIL-PRF-38534 CERTIFIED

# 29 AMP, 75V, 3 PHASE MOSFET BRIDGE WITH INTELLIGENT INTEGRATED GATE DRIVE

#### 4707 Dey Road Liverpool, N.Y. 13088

# FEATURES:

- 75 Volt Motor Supply Voltage

- <sup>•</sup> 29 Amp Output Switch Capability, All N-Channel MOSFET Output Bridge

- 100% Duty Cycle High Side Conduction Capable

- Suitable for PWM Applications from DC to 100KHz

- Shoot-Through/Cross Conduction Protection

- Undervoltage Lockout Protection

- Programmable Dead-Time Control

- Low Active Enable for Bridge Shutdown Control

- ' Isolated Package Design for High Voltage Isolation Plus Good Thermal Transfer

- Available with Three Lead Bend Options

- Contact MSK for MIL-PRF-38534 Qualification Status

#### **DESCRIPTION:**

The MSK 4301 is a 3 phase MOSFET bridge plus drivers in a convenient isolated hermetic package. The hybrid is capable of 29 amps of output current and 75 volts of DC bus voltage. It has a full line of protection features, including undervoltage lockout protection of the bias voltage, cross conduction control and a user programmable dead-time control for shoot-through elimination. In addition, the bridge may be shut down by using the Enable control. The MSK 4301 provides good thermal conductivity for the MOSFETs due to the electrically isolated package design that allows direct heat sinking of the device without insulators.

4301

(315) 701-6751

1

#### ABSOLUTE MAXIMUM RATINGS 6

| V + High Voltage Supply $\overset{(7)}{\sim}$ 3V transient to +75V |

|--------------------------------------------------------------------|

| V <sub>BIAS</sub> Bias Supply                                      |

| VIND Logic Input Voltages0.3V to VBIAS +0.3V                       |

| Iout Continuous Output Current                                     |

| IPK Peak Output Current                                            |

| AØ, BØ, CØ                                                         |

| $R_{\text{SENSE}}$                                                 |

#### θJc Thermal Resistance MOSFETS @ 125°C. . 0.8°C/W

- $T_{ST}$  Storage Temperature Range . . . .-65°C to +150°C

- $T_{LD}$  Lead Temperature Range . . . . . . . . . . . . + 300 °C

- (10 Seconds) Tc Case Operating Temperature

| Parameter                                 | Test Conditions                      | GroupA(4) | MSK4301H/E ③ |      |       | MSK43012 |      |       | Units |

|-------------------------------------------|--------------------------------------|-----------|--------------|------|-------|----------|------|-------|-------|

|                                           |                                      | Subgroup  | Min.         | Тур. | Max.  | Min.     | Тур. | Max.  | Units |

| CONTROL SECTION                           |                                      |           |              |      |       |          |      |       |       |

| VBIAS Quiescent Current                   | All Inputs Off                       | 1,2,3     | -            | 2.5  | 8     | -        | 2.5  | 8     | mAmp  |

| VBIAS Operating Current                   | f=20KHz, 50% Duty Cycle              | 1,2,3     | -            | 20   | 25    | -        | 20   | 25    | mAmp  |

| Undervoltage Threshold (Falling)          |                                      | 1         | 5.6          | 6.6  | 7.6   | 5.6      | 6.6  | 7.6   | Volts |

| Undervoltage Threshold (Rising)           |                                      | 1         | 6.1          | 7.1  | 8.1   | 6.1      | 7.1  | 8.1   | Volts |

| Low Level Input Voltage (1)               |                                      | -         | -            | -    | 0.8   | -        | -    | 0.8   | Volts |

| High Level Input Voltage $(1)$            |                                      | -         | 2.7          | -    | -     | 2.7      | -    | -     | Volts |

| Low Level Input Current (1)               | VIN = OV                             | -         | 60           | 100  | 135   | 60       | 100  | 135   | μAmp  |

| High Level Input Current $(1)$            | VIN = 5V                             | -         | - 1          | -    | + 1   | -1       | -    | + 1   | μAmp  |

| OUTPUT BRIDGE                             |                                      |           |              |      |       |          |      |       |       |

| Drain-Source Breakdown Voltage $(1)$      | $I_D = 250 \mu A$ , All Inputs Off   | -         | 75           | -    | -     | 75       | -    | -     | V     |

| Drain-Source Leakage Current (1)          | $V_{DS} = 75V$                       | -         | -            | -    | 250   | -        | -    | 250   | μAmp  |

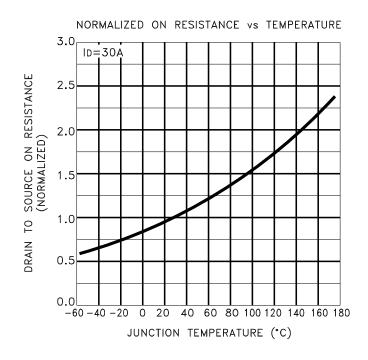

| Drain-Source On Resistance (Each FE       | T) ID = 29A                          | 1         | -            | -    | 0.022 | -        | -    | 0.022 | Ω     |

| Drain-Source On Resistance (1)            |                                      | _         | _            | -    | 0.013 | _        | -    | 0.013 | Ω     |

| (Each FET, For Thermal Calculations Only) |                                      | -         | _            | -    | 0.015 | -        | -    | 0.013 | 52    |

| SWITCHING CHARACTERISTICS                 |                                      |           |              |      |       |          |      |       |       |

| Rise Time 1                               | V + = 28V                            | -         | -            | 120  | -     | -        | 120  | -     | nSec  |

| Fall Time (1)                             | ID = 29A                             | -         | -            | 81   | -     | -        | 81   | -     | nSec  |

| Turn-On Prop Delay (Lower) (1)            | SWR Resistor =∞                      | 4         | -            | 0.5  | 2     | -        | 0.5  | 3     | μSec  |

| Turn-Off Prop Delay (Lower)               | SWR Resistor =∞                      | 4         | -            | 5    | 8     | -        | 5    | 10    | μSec  |

| Turn-On Prop Delay (Upper) ()             | SWR Resistor =∞                      | 4         | -            | 5    | 8     | -        | 5    | 10    | μSec  |

| Turn-Off Prop Delay (Upper) $\widehat{1}$ | SWR Resistor =∞                      | 4         | -            | 0.5  | 2     | -        | 0.5  | 3     | μSec  |

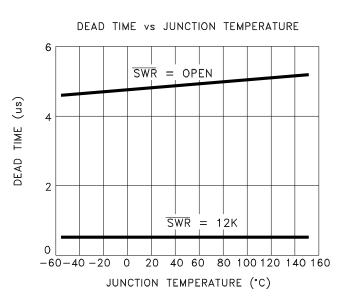

| Dead Time                                 | <del>SWR</del> =∞                    | 4         | 3.0          | 5.0  | 7.0   | 3.0      | 5.0  | 7.0   | μSec  |

| Dead Time                                 | $\overline{\text{SWR}} = 12\text{K}$ | 4         | 0.3          | 1.0  | 1.2   | 0.3      | 1.0  | 1.2   | μSec  |

| SOURCE-DRAIN DIODE CHARACTERIST           | ICS                                  |           |              |      |       |          |      |       |       |

| Forward Voltage $\widehat{\mathbb{1}}$    | ISD = 29A                            | -         | -            | 1.05 | 1.30  | -        | 1.05 | 1.30  | Volts |

| Reverse Recovery Time 1                   | IsD = 29A, di/dt = $100A/\mu S$      | -         | -            | 120  | -     | -        | 120  | -     | nSec  |

#### ELECTRICAL SPECIFICATIONS

NOTES:

① Guaranteed by design but not tested. Typical parameters are representative of actual device performance but are for reference only.

- 2 Industrial grade and "E" suffix devices shall be tested to subgroups 1 and 4 unless otherwise specified.

- 3 Military grade devices ("H" Suffix) shall be 100% tested to Subgroups 1, 2, 3 and 4.

- ④ Subgroups 5 and 6 testing available upon request.

- (5) Subgroup 1, 4 TA = TC =  $+25^{\circ}C$

2, 5 TA = TC =  $+125^{\circ}C$

3, 6 TA = TC =  $-55^{\,o}$

(6) Continuous operation at or above absolute maximum ratings may adversly effect the device performance and/or life cycle.

When applying power to the device, apply the low voltage followed by the high voltage or alternatively, apply both at the same time Do not apply high voltage without low voltage present.

# **APPLICATION NOTES**

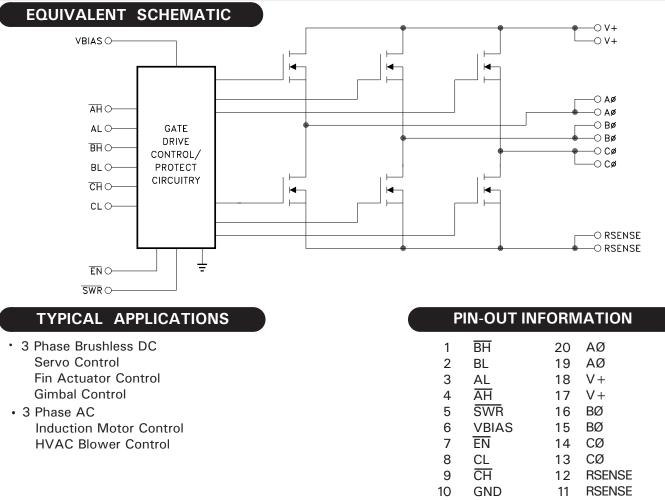

#### MSK 4301 PIN DESCRIPTIONS

**AL,BL,CL** - Are the lowside logic level digital inputs. These three inputs control the three lowside bridge transistors. If the highside inputs are low, then the lowside inputs will control both the lowside and the highside of the bridge, with deadtime set by the SWR resistor. EN will override these inputs, forcing all outputs low. These inputs can be driven by logic up to 15V (less than VBIAS). An internal pullup to VBIAS will hold each input high if the pins are not driven.

$\overline{AH},\overline{BH},\overline{CH}$  - Are the highside logic level digital inputs. These three inputs control the three highside bridge transistors. Unless the deadtime is disabled by connecting  $\overline{SWR}$  to ground, the lowside input of each phase will override the corresponding highside input. If  $\overline{SWR}$  is the lowside input of each phase will override the corresponding highside input. In this condition, tied to ground, deadtime is disabled and the outputs follow the inputs. In this condition, shoot-through must be avoided externally.  $\overline{EN}$  will override all inputs, forcing outputs low.

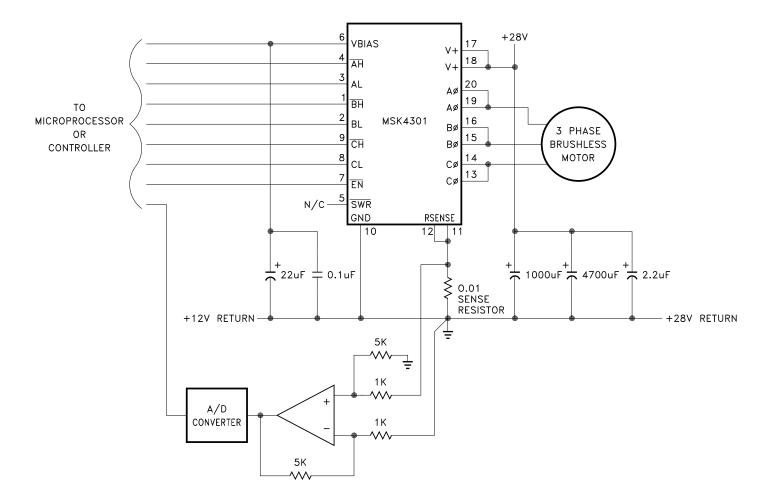

**VBIAS** - Is the positive supply for the gate drive. This pin should be decoupled to ground with at least a  $22\mu$ F capacitor in parallel with a 0.1 $\mu$ F ceramic capcitor.

**GROUND** - Is the return for the VBIAS supply. This pin should be connected to the return of the lowside MOSFETs or the bottom of the sense resistor at the bottom of the bridge. The gate drive current must return through this pin, so trace lengths should be kept to a minimum. All grounds should be returned to the bottom of the bridge or sense resistor in a star fashion. This will eliminate ground loops.

**SWR** - Is the pin for controlling the deadtime between the top and bottom transistors of the bridge. By connecting a pullup resistor between this pin and VBIAS, various deadtimes can be obtained. There is and internal 100K $\Omega$  pullup resistor connected internally. By adding additional resistors in externally, reduced deadtimes can be achieved. By connecting this pin directly to ground, all deadtime is eliminated. However, care must be taken to assure that deadtime is being generated by the logic circuitry driving the inputs. Shoot-through can occur (both the top and bottom transistors on at the same time for a given phase, causing a short on the V + supply to ground) destroying the bridge.

V + - Is the power connection for the top of the output bridge. These pins must be bypassed by a capacitor to ground of a least  $10\mu$ F per amp preferrably  $100\mu$ F per amp of output current mini mum, high quality high frequency bypass capacitance to help suppress switching noise. Connect both pins for proper current sharing.

$A\ddot{y}$ ,  $B\ddot{y}$ ,  $C\ddot{y}$  - Are the output pins for the three phases of power bridge. Connect both pins for proper current sharing.

**EN** - Is the enabling input for the bridge. This digital input, when pulled low, will enable the bridge, following the inputs from AL, BL, CL and AH, BH, CH inputs. When pulled high, it will override all other inputs and disable the bridge. It is internally pulled high to VBIAS, and can be driven by logic levels up to VBIAS.

**RSENSE** - Are the connections to the bottom of the bridge. All power flowing through the bridge will flow through this point, and can be sensed by connecting a sense resistor from here to ground. The sense resistor will develop a voltage proportional to the current flowing. Size the value and power rating of the sense resistor according to the voltage necessary. 3 volts is the maximum voltage between this point and ground, or damage to the hybrid will result. Connect both pins for proper current sharing.

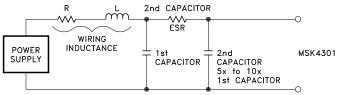

### BUS VOLTAGE FILTER CAPACITORS

The size and placement of the capacitors for the main voltage bus for the motor will have an effect on the noise filtered throughout the rest of the system. Series RLC tuned circuit is being created by the inductance of the wire (about 30nH per inch), the filter capacitance, and all of the resistances (wire resistance and the capacitor ESR) of the overall power circuit. Voltage spikes from the back EMF if the motor ride on top of the bus voltage. All of this must be taken into account when laying out the system. A first capacitor of high quality and low ESR should be placed as close to the hybrid circuit as possible. Along with that, a capacitor of 5x to 10x the first value should be added (and that second capacitor should have some ESR) and/or a resistor should be added to help with the damping of the voltage spikes. Be careful of the ripple current in all the capacitors. Excessive ripple current, beyond what the capacitor is rated for, will destroy the capacitor.

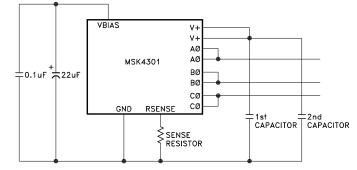

#### BIAS SUPPLY BYPASS CAPACITORS

It is recommended that at least  $22\mu$ F of capacitance for bypassing the VBIAS voltage that supplies the drive circuitry for the MSK 4301, along with  $0.1\mu$ F for helping the high frequency current pulses needed by the gate driver. If an extremely long risetime is exhibited by the turn on of the FETs, the extra high frequency capacitance will help.

#### GENERAL LAYOUT

Good high frequency PC layout techniques are a must. Traces wide enough for the current delivered, and placement of the big capacitors close to the MSK 4301 are very important. The path for the RSENSE connection through any sense resistor back to the GND pins must be as short as possible. This path is the gate drive current path for all the FETs on the lower half of each phase. A short, low inductance path will aid in the switching time of those FETs.

# LOW POWER STARTUP

When starting up the circuit utilizing the MSK 4301 for the first time, it is very important to keep certain things in mind. Because of the small size of the bridge, there is no internal short circuit protection and a short circuit will destroy the bridge. Any required short circuit protection must be built outside the bridge. Current and voltage limit the power supply feeding the V + pins to the bridge, and monitor the current for any signs of short circuiting, or shoot-through currents. If there are large current spikes at the beginning of each switching cycle, there may be shoot through. Try raising the resistor value of the SWR. This will lengthen the deadtime and stop shoot-through.

# TYPICAL APPLICATION SCHEMATIC

#### TYPICAL PERFORMANCE CURVES

Rev. H 11/10

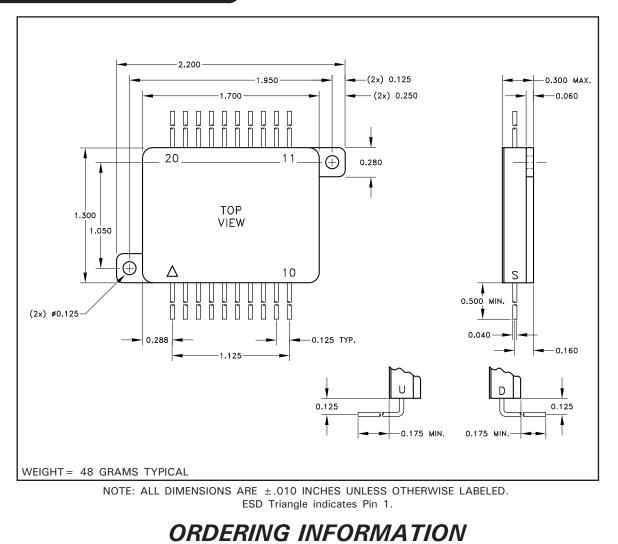

### MECHANICAL SPECIFICATIONS

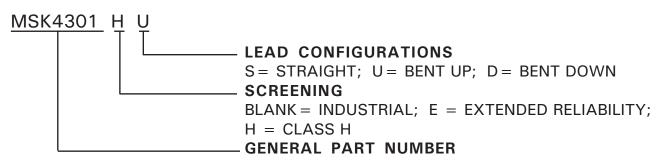

The above example is a Military grade hybrid with leads bent up.

M.S. Kennedy Corp. 4707 Dey Road, Liverpool, New York 13088 Phone (315) 701-6751 FAX (315) 701-6752 www.mskennedy.com

The information contained herein is believed to be accurate at the time of printing. MSK reserves the right to make changes to its products or specifications without notice, however, and assumes no liability for the use of its products. Please visit our website for the most recent revision of this datasheet. Contact MSK for MIL-PRF-38534 qualification status.