# TDC1141 Monolithic Digital To Analog Converter

10 Bit, 50Msps, 12ns Settling Time

The TDC1141 is an ECL compatible, 10-bit monolithic D/A converter capable of converting digital data into an analog current or voltage at data rates in excess of 50 Megasamples-per second (Msps).

The analog circuitry has been optimized for dynamic performance, with very low glitch energy. The output is able to drive a  $50\Omega$  load with 1V output levels while maintaining large spurious-free-dynamic range.

Data registers are incorporated on the TDC1141. This eliminates data skew encountered with external registers and latches and minimizes the glitches that can adversely affect many applications.

### **Features**

- 10-Bit Resolution

- 50 Msps Data Rate

- ECL Inputs

- Very Low Glitch With No Track And Hold Circuit Needed

- Dual +4dBm (1V Into 50Ω) Outputs Make Output Amplifiers Unnecessary In Many Applications

# **Applications**

- Direct Digital RF Signal Generation

- Test Signal Generation

- Arbitrary Waveform Synthesis

- Broadcast And Studio Video

- High-Resolution A/D Converters

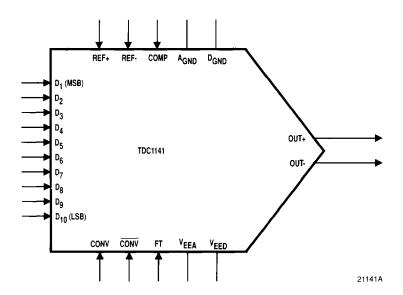

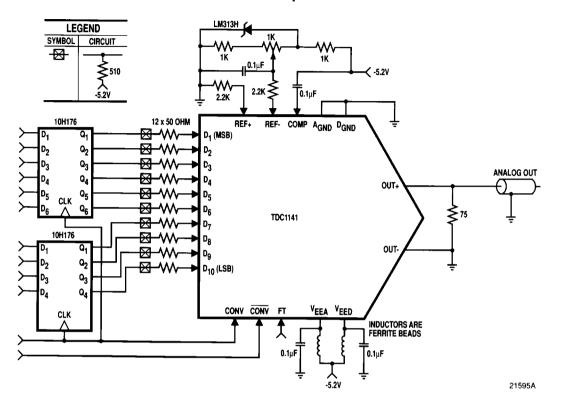

### Interface Diagram

105

#### **Functional Block Diagram**

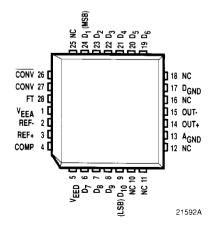

#### **Pin Assignments**

28 Leaded Plastic Chip Carrier - R3

# **Functional Description**

### **General Description**

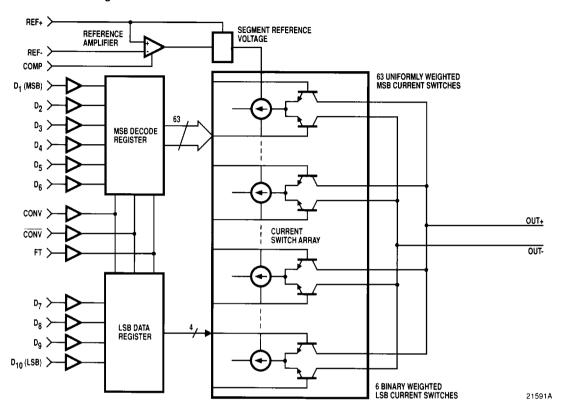

The TDC1141 consists of five major circuit sections: the LSB data register, the MSB decode block, the decoded MSB register, the current switch array, and the reference amplifier. All data bits are registered just before the current switches to minimize the temporal skew that would generate glitches.

#### **Power and Grounds**

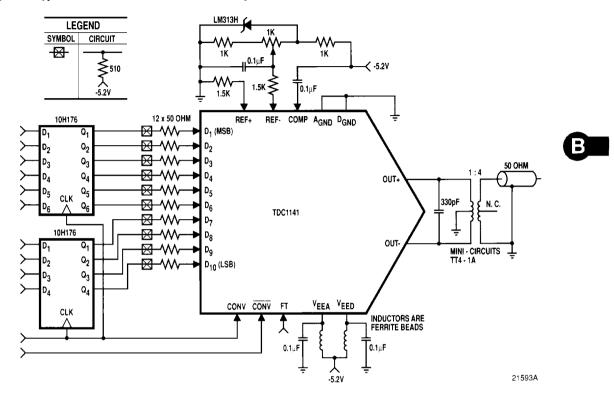

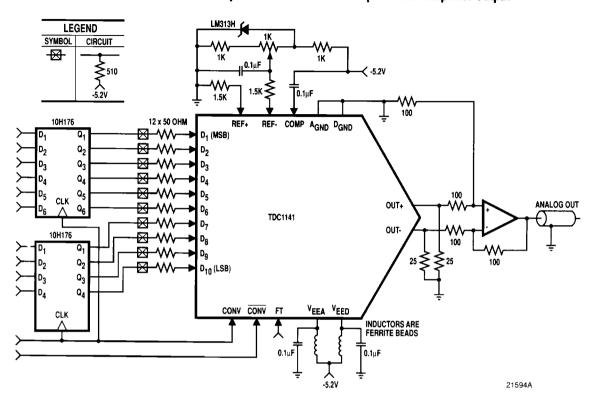

The TDC1141 requires a single –5.2V power supply. This supply is divided into analog (VEEA) and digital (VEED) supply pins which should be decoupled from each other. An example of this decoupling is shown in the *Typical Interface Circuit*. The 0.1µF decoupling capacitors should be placed as close as possible to the power pins. The

inductors are simple ferrite beads and are neither critical in value nor always required.

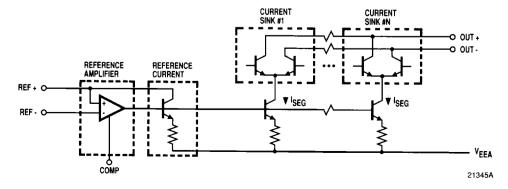

### **Reference and Compensation**

The TDC1141 has two reference inputs: REF+ and REF—. These are the inverting and noninverting inputs of the internal reference amplifier. An externally generated reference voltage is applied to the REF—pin. Current flows into the REF+ pin through an external current setting resistor (RREF). This current is the reference current (IREF) which serves as an internal reference for the current source array. The output current for an input code N from OUT+ is related to IREF through the following relationship:

$$IOUT = N \times \frac{IREF}{16}$$

Where N is the input code to the D/A converter

This means that with an IREF that is nominally 625 $\mu$ A, the full-scale output is 40mA, which will drive a 50 $\Omega$  load in parallel with a 50 $\Omega$  transmission line (25 $\Omega$  load total) with a 1V peak to peak signal. The impedance seen by the REF– and REF+ pins should be approximately equal so that the effect of amplifier input bias current is minimized.

The internal reference amplifier is externally compensated to ensure stability. A  $0.1\mu F$  capacitor should be connected between the COMP pin and VFFA.

### **Digital Inputs**

All digital inputs including the FT, CONV and Data Inputs are compatible with ECL logic. Input registers are provided on the data input lines to minimize the effect of glitching caused by data skew.

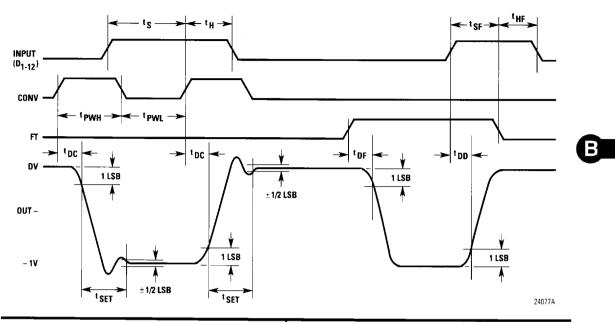

# **Clock and Feedthrough Control**

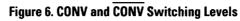

The TDC1141 requires a differential ECL clock signal (CONVert and CONVert). Even though complementary operation is preferred, a single-ended signal may be used if either unused CONV input is biased at a DC voltage midway between the active input's V<sub>IH</sub> and V<sub>IL</sub> levels.

Data is synchronously entered on the rising edge of CONV (the falling edge of  $\overline{CONV}$ ). The CONV input is ignored in the Feedthrough (FT = HIGH) mode.

The Feedthrough (FT) pin is normally held LOW, in which case the TDC1141 operates in a clocked mode (the output changes only after a clock rising edge). An internal pull-down resistor is provided, and this pin may be left open for clocked operation. For certain applications, such as high-precision successive approximation A/D converters, output delay may be more important than glitch performance. In these cases, the FT pin may be brought HIGH, which makes the input registers transparent. This allows the analog output to change immediately and asynchronously in response to the digital input, without the need for a clock.

# $(\mathbf{B}_{\perp})$

### Analog Outputs

Two simultaneous and complementary analog outputs are provided. Both of these outputs are full-power current sources. By loading the current source outputs with a resistive load, they may be used as voltage outputs. OUT+ provides a 0 to -40mA output current (0 to -1V when terminated in 25 $\Omega$ ) as the input code varies from 00 0000 0000 to 11 1111 1111. OUT- varies in a complementary manner from -40 to 0mA (-1 to 0V when terminated with 25 $\Omega$ ) over the same code range. (See the *Input Coding Table*.) The output current is proportional to the reference current and the input code.

#### **No Connect**

These pins have no internal connection and should be left open for optimal performance.

# **Package Interconnections**

| Signal<br>Type                                                                                                                                                                                                                                                                      | Signal Function Value<br>Name |                          | Value           | R3 Package<br>Pins |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------|-----------------|--------------------|

| Power                                                                                                                                                                                                                                                                               | AGND                          | Analog Ground            | 0.0V            | 13                 |

|                                                                                                                                                                                                                                                                                     | DGND                          | Digital Ground           | 0.0V            | 17                 |

|                                                                                                                                                                                                                                                                                     | VEEA                          | Analog Supply Voltage    | −5.2V           | 1                  |

|                                                                                                                                                                                                                                                                                     | VEED                          | Digital Supply Voltage   | −5.2V           | 5                  |

| Reference                                                                                                                                                                                                                                                                           | REF-                          | Reference Voltage Input  | -1.0V           | 2                  |

|                                                                                                                                                                                                                                                                                     | REF+                          | Reference Current Input  | −625µA          | 3                  |

|                                                                                                                                                                                                                                                                                     | COMP                          | Compensation Capacitor   | 0.1μF, see text | 4                  |

| VEEA Analog Supply Voltage VEED Digital Supply Voltage Reference REF- Reference Voltage Input REF+ Reference Current Input COMP Compensation Capacitor  Data Inputs D1 (MSB) Most Significant Bit D2 D3 D4 D5 D6 D7 D8 D9 D10 (LSB) Least Significant Bit  Feedthrough Mode control | ECL                           | 24                       |                 |                    |

|                                                                                                                                                                                                                                                                                     | D <sub>2</sub>                |                          | ECL             | 23                 |

|                                                                                                                                                                                                                                                                                     | D <sub>3</sub>                | *                        | ECL             | 22                 |

|                                                                                                                                                                                                                                                                                     | D <sub>4</sub>                |                          | ECL             | 21                 |

|                                                                                                                                                                                                                                                                                     | D <sub>5</sub>                |                          | ECL             | 20                 |

|                                                                                                                                                                                                                                                                                     | D <sub>6</sub>                |                          | ECL             | 19                 |

|                                                                                                                                                                                                                                                                                     | D <sub>7</sub>                |                          | ECL             | 6                  |

|                                                                                                                                                                                                                                                                                     | D8                            |                          | ECL             | 7                  |

|                                                                                                                                                                                                                                                                                     | Dg                            |                          | ECL             | 8                  |

|                                                                                                                                                                                                                                                                                     | D <sub>10</sub> (LSB)         | Least Significant Bit    | ECL             | 9                  |

| Feedthrough                                                                                                                                                                                                                                                                         | FT                            | Feedthrough Mode control | ECL             | 28                 |

| Convert                                                                                                                                                                                                                                                                             | CONV                          | Convert (Clock) Input    | ECL             | 27                 |

|                                                                                                                                                                                                                                                                                     | CONV                          | Convert Complement       | ECL             | 26                 |

| Analog Output                                                                                                                                                                                                                                                                       | OUT+                          | Analog Output            | 0 to 40mA       | 14                 |

|                                                                                                                                                                                                                                                                                     | OUT-                          | Analog Output            | 40 to 0mA       | 15                 |

| No Connect                                                                                                                                                                                                                                                                          | NC                            | No Internal Connection   | Open            | 10,11,12,16,18,25  |

# Input Coding Table<sup>1</sup>

| Input Data   |           |                        |           |          |  |

|--------------|-----------|------------------------|-----------|----------|--|

| MSB LSB      | OUT+ (mA) | V <sub>OUT+</sub> (mV) | OUT- (mA) | VOUT(mV) |  |

| 00 0000 0000 | 0.000     | 0.00                   | 40.000    | -1000.00 |  |

| 00 0000 0001 | 0.039     | -0.97                  | 39.961    | -998.05  |  |

| 00 0000 0010 | 0.078     | -1.95                  | 39.922    | -998.05  |  |

| •            | •         | •                      | •         | •        |  |

| •            | •         | •                      | •         | •        |  |

| •            | •         | •                      | •         | •        |  |

| 0111 1111 11 | 19.961    | -499.03                | 20.000    | -500.00  |  |

| 1000 0000 00 | 20.000    | -500.00                | 19.961    | -499.03  |  |

| •            | •         | •                      | •         | •        |  |

| •            | •         | •                      | •         | •        |  |

| •            | •         | •                      | •         | •        |  |

| 1111 1111 01 | 39.922    | -998.05                | 0.078     | -1.95    |  |

| 1111 1111 10 | 39.961    | -999.03                | 0.039     | -0.97    |  |

| 1111 1111 11 | 40.000    | -1000.00               | 0.000     | 0.0      |  |

Note: 1. IREF =  $625\mu$ A,  $R_{LOAD} = 25\Omega$

**Figure 1. Timing Diagram**

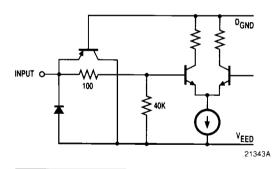

Figure 2. Equivalent Input Circuit (Data and FT)

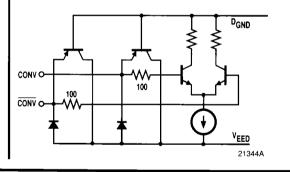

Figure 3. Equivalent Input Circuit (CONV and CONV)

Figure 4. Equivalent Reference and Output Circuits

TRW LSI Products Inc.

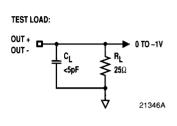

# Figure 5. Standard Test Load

# Absolute maximum ratings (beyond which the device may be damaged)1

| Supply Voltage | S                                                          |                 |

|----------------|------------------------------------------------------------|-----------------|

| VEEA           | (Measured to AGND)                                         | 7.0 to +0.5     |

| VEEA           | (Measured to VEED)                                         |                 |

| VEED           | (Measured to DGND)                                         |                 |

| AGND           | (Measured to DGND)                                         |                 |

| nputs          |                                                            |                 |

| CONV, C        | ONV, FT, D <sub>1-12</sub> (Measured to DGND) <sup>2</sup> | VEED to +0.5    |

| REF+, RE       | F-, Applied Voltage                                        |                 |

|                | (Measured to AGND) <sup>2</sup>                            | VEEA to +0.5    |

| REF+, RE       | F–, Current, Externally Forced <sup>3,4</sup>              | ±3m/            |

| Outputs        |                                                            |                 |

| OUT+, OL       | JT-, Applied Voltage                                       |                 |

|                | (Measured to AGND) <sup>2</sup>                            |                 |

| OUT+, OL       | JT-, Current, Externally Forced <sup>3,4</sup> .           |                 |

| Short-Cir      | cuit Duration (Single Output to GND)                       | unlimite        |

| emperature     |                                                            |                 |

| Operatin       | g, ambient                                                 |                 |

|                | (Plastic Package)                                          | 20 to +90°0     |

|                | (Ceramic Package)                                          | 60 to +150°C    |

| Junction       |                                                            |                 |

|                | (Plastic Package)                                          | +140°0          |

|                | (Ceramic Package)                                          | + <b>200</b> °0 |

| Lead, So       | Idering (10 Seconds)                                       | +300°C          |

|                |                                                            |                 |

Notes:

- Absolute maximum ratings are limiting values applied individually while other parameters are within specified operating conditions. Functional

operation under any of these conditions is NOT implied. Device performance and reliability are guaranteed only if the Operating Conditions are

not exceeded.

- 2. Applied voltage must be current limited to specified range

- 3. Forcing voltage must be limited to specified range.

- 4. Current is specified as conventional current flowing into the device.

# B

# **Operating conditions**

|                |                                            | 1     | emperature Ra | ange  |       |

|----------------|--------------------------------------------|-------|---------------|-------|-------|

| Parameter      |                                            |       | 1             |       |       |

|                |                                            | Min   | Nom           | Max   | Units |

| FS             | Clock Frequency                            | 0     |               | 50    | Msps  |

| VEED           | Negative Supply Voltage (Measured to DGND) | -4.9  | -5.2          | -5.5  | ٧     |

| VEEA           | Negative Supply Voltage (Measured to AGND) | -4.9  | -5.2          | -5.5  | ٧     |

| VAGND          | Analog Ground Voltage (Measured to DGND)   | -0.1  | 0.0           | 0.1   | ٧     |

| VEEA           | Negative Supply Voltage (Measured to VEED) | -20   | 0             | 20    | mV    |

| tPWL           | CONV Pulse Width LOW (FS≥40 Msps)          | 10.5  |               |       | ns    |

|                | CONV Pulse Width LOW (FS<40 Msps)          | 11    |               |       | ns    |

| tPWH           | CONV Pulse Width HIGH (FS≥40 Msps)         | 8     |               |       | ns    |

|                | CONV Pulse Width HIGH (FS<40 Msps)         | 9     |               |       | ns    |

| ts             | Setup Time, Data to CONV                   | 17    |               |       | ns    |

| tH             | Hold Time                                  | 0     |               |       | ns    |

| tsf            | Setup Time, Data to FT                     | 7     |               |       | ns    |

| tHF            | Hold Time, Data to FT                      | 24    |               |       | ns    |

| VIL            | Input Voltage, Logic LOW                   |       |               | -1.55 | ٧     |

| ViH            | Input Voltage, Logic HIGH                  | -1.05 |               |       | V     |

| VREF           | Reference Voltage (REF–)                   | -0.7  | -1.0          | -1.3  | ٧     |

| IREF           | Reference Current (REF+)                   | 400   | 625           | 700   | μΑ    |

| СС             | Compensation Capacitor                     | 0.01  | 0.1           |       | μF    |

| T <sub>A</sub> | Ambient Temperature, Still Air             | 0     |               | 70    | °C    |

Note. 1. A common power supply isolated with ferrite bead inductors is recommended for VEEA and VEED. This is shown in the Typical Interface Circuits.

# Electrical characteristics within specified operating conditions

| -      |                             |                                   | Temperature Range |      |       |

|--------|-----------------------------|-----------------------------------|-------------------|------|-------|

|        |                             |                                   | Standard          |      | Units |

| Paran  | neter                       | Test Conditions                   | Min Max           |      |       |

| IEEA+I | IEED                        | VEEA=VEED=Max,static TA=0 to 70°C |                   | -180 | mA    |

|        |                             | T <sub>A</sub> =70°C              |                   | -150 | mA    |

| CREF   | Reference Input Capacitance |                                   |                   | 15   | pF    |

| CI     | Digital Input Capacitance   |                                   |                   | 15   | pF    |

| Voc    | Compliance Voltage          |                                   | -1.2              | 1.2  | ٧     |

| RO     | Output Resistance           |                                   | 12                |      | kΩ    |

| CO     | Output Capacitance          |                                   |                   | 45   | pF    |

| 10     | Full-Scale Output Current   | I <sub>REF</sub> =625μA           | 40                |      | mA    |

| IJڍ    | Input Current, Logic LOW    | VEE=Max, VI=0.4V                  | -10               | 200  | μА    |

| liH .  | Input Current, Logic HIGH   | VEE=Max, VI=2.4V                  | -10               | 200  | μμΑ   |

# **Switching characteristics**

|        | _                      |                         | Temperature Range |         |    |       |

|--------|------------------------|-------------------------|-------------------|---------|----|-------|

|        |                        |                         | Standard          |         |    |       |

| Parame | eter                   | Test Conditions         | Min               | Тур Мах |    | Units |

| tDC    | Clock to Output Delay  | VEEA, VEED=Min, FT=LOW  |                   |         | 20 | ns    |

| tDD    | Data to Output Delay   | VEEA, VEED=Min, FT=HIGH |                   |         | 25 | ns    |

| tDF    | FT to Output Delay     | VEEA, VEED=Min          |                   |         | 30 | ns    |

| tR     | Risetime <sup>1</sup>  | 90% to 10% of FSR,      |                   | 2       | 4  | ns    |

|        |                        | FT=L0W                  | İ                 |         |    |       |

| tF     | Falltime <sup>1</sup>  | 10% to 90% of FSR,      |                   | 2       | 4  | ns    |

|        |                        | FT=L0W                  |                   |         |    |       |

| tSET   | Settling Time, Voltage | FT=LOW, Full-Scale      |                   | 12      | 20 | ns    |

|        |                        | Voltage transition      |                   |         |    |       |

|        |                        | on IOUT to 0.1% FSR     |                   |         |    |       |

Note 1. Clocked Mode

# System performance characteristics

|           |                              |                                                | Ten      | nperature R | ange  |               |

|-----------|------------------------------|------------------------------------------------|----------|-------------|-------|---------------|

|           |                              |                                                | Standard |             |       |               |

| Parameter |                              | Test Conditions                                | Min      | Тур         | Max   | Units         |

| ELD       | Differential Linearity Error | VEEA, VEED, IREF = Nom<br>TDC1141              |          |             | ±0.1  | %             |

|           |                              | TDC1141-1                                      |          |             | ±0.05 | %             |

| ELI       | Integral Linearity Error     | VEEA, VEED, IREF = Nom <sup>1</sup><br>TDC1141 |          |             | ±0.1  | %             |

|           |                              | TDC1141-1                                      |          |             | ±0.05 | %             |

| Vos       | REF+ to REF- Offset Voltage  |                                                | -10      |             | +10   | mV            |

| lΒ        | REF- Input Bias Current      |                                                |          | 5           | μА    |               |

| EG        | Absolute Gain Error          | VEEA, VEED, IREF = Nom                         | -5       |             | 5     | %             |

| OF        | Output Offset Current        | VEEA, VEED= Max, D1-12 = LOW                   | -5       |             | +5    | μΑ            |

| PSRR      | Power Supply Rejection Ratio | VEEA, VEED, IREF = Nom2                        |          |             | -50   | dB            |

| PSS       | Power Supply Sensitivity     | VEEA, VEED = ±4%, IREF = Nom                   |          |             | -140  | μ <b>A</b> /V |

| GΑ        | Peak Glitch Area             |                                                |          |             | 40    | pV- sec       |

Note 1. OUT- connected to AGND, OUT- driving virtual ground:

2. 120Hz, 600mV p-p ripple on VEE and VCC

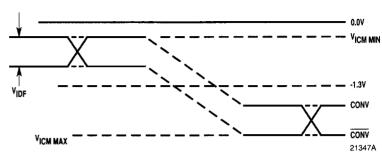

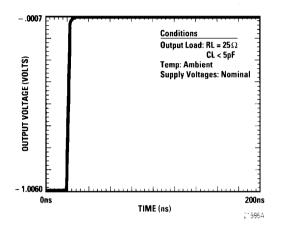

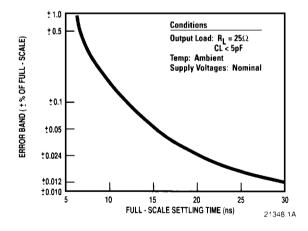

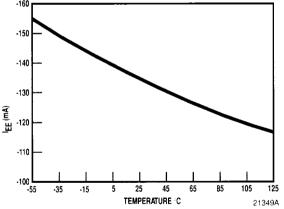

**Typical Performance Curves** (Typical Settling Time Charactersitics)

# A. Full-Scale Output Transition, Rising Edge

# B. Full-Scale Output Transition, Falling Edge

# $(\mathbf{E}_{\mathbf{E}})$

# C. Typical Settling Time vs. Settling Accuracy

# D. Typical Supply Current vs. Temperature

TDC1141 7786

## **Applications Information**

There are three major D/A architectures: segmented, weighted current sources, and R-2R. In segmentated D/A converters there is one current source for each possible output level. The current sources are equally weighted and for an input code of N, N current sources are turned on. An N bit segmented D/A has 2N current sources. A weighted current source D/A has one current source for each bit of input with a binary weighting for the current sources. In an R-2R D/A, there is one current source per bit, and a resistor network which scales the current sources to have a binary weighting.

When transitioning from a code of 0111111111 to 1000000000, both the R-2R D/A and Binary weighted D/A are turning some current sources on while turning others off. If the timing is not perfect, there is a moment where all current sources are either on or off, resulting in a glitch. In a segmented architecture, 511 of the current sources remain on, and one more is turned on to increment the output with no possibility of a glitch.

The TDC1141 uses a hybrid architecture with the 6 MSBs segmented, and the 4 LSBs from a R-2R network. The result is a converter which has very low glitch energy, and a moderate die size.

## **Layout, Power and Grounding**

The layout of grounds in any system is an important design consideration. Separate analog and digital grounds are provided on the TDC1141. All ground pins should be connected to a common low-noise, low-impedance groundplane. This groundplane should be common for the TDC1141 and all of its immediate interface circuitry, which includes all of the reference circuitry, the output load circuitry, and all of the power supply decoupling components.

The digital driving logic should use a separate system ground, and this ground should be connected (typically through a ferrite bead inductor) to the analog groundplane in only one place. The analog and digital grounds may be connected in other ways if required by the user's system grounding plan, however, the voltage differential between the AGND and DGND pins must be held to within  $\pm 0.1$  Volt.

# **Output Termination**

The recommended output termination is  $25\Omega$ . This can be provided by placing a  $50\Omega$  source resistor between the output pin and ground, then driving a  $50\Omega$  transmission line. With this load, the output voltage range of the converter is 0 to -1.0V. If a load is capacitively coupled to the TDC1141, it is recommended that a  $25\Omega$  load at DC, as seen by the TDC1141, continue to be maintained. The output voltage should be kept within the output compliance voltage range,  $V_{OC}$ , as specified in the *Electrical Characteristics Table*, or the accuracy may be impaired.

See Figure 8 for a suggested circuit for achieving a bipolar output voltage range. Optimum DC linearity is obtained by using a differential output either with a balun, or an operational amplifier in the differential mode. If it is desired that the TDC1141 be operated in a single ended fashion, the unused output should be connected directly to ground as is shown in Figure 9. The CONV signal provided to the TDC1141 must be as free from clock jitter as possible. Clock litter is the random cycle-to-cycle variation in clock period. CONV clock jitter will effectively appear at the output as phase noise. A value of 10ps or less for clock iitter is recommended for the highest performance applications. Ordinary crystal oscillators are satisfactory. High-performance synthesizers, such as the HP8662, used to trigger a precision pulse generator, are also satisfactory, although not as litter free as a crystal oscillator.

#### Driving a 75 $\Omega$ Transmission line

The TDC1141 has been optimized to operate with a reference current of 625 $\mu$ A. Significantly increasing or decreasing this current may degrade the performance of the device. If it is desired that the device drive a 37.5 $\Omega$  load (75 $\Omega$  source termination driving 75 $\Omega$  transmission line) rather than the 25 $\Omega$  suggested load, then VREF should be held at 1V and IREF reduced to 417 $\mu$ A. This will result in a 1V p-p voltage being generated at the DAC output.

Figure 7. Typical Interface Circuit with Balun Output

Figure 8. Typical Interface Circuit with Bipolar, Differential Mode Operational Amplifier Output

117

Figure 9. Typical Interface Circuit with Resistive Load Output

#### **Ordering Information**

| Product Number | Temperature Range           | Screening  | Package              | Package Marking |  |

|----------------|-----------------------------|------------|----------------------|-----------------|--|

| TDC1141R3C     | T <sub>A</sub> =0°C to 70°C | Commercial | Plastic Chip Carrier | 1141R3C         |  |

| TDC1141R3C1    | T <sub>A</sub> =0°C to 70°C | Commercial | Plastic Chip Carrier | 1141R3C-1       |  |

All parameters contained in this specification are guaranteed by design, characterization, sample testing or 100% testing as appropriate. TRW reserves the right to change products and specifications without notice. This information does not convey any license under patent rights of TRW Inc. or others.

#### **Life Support Policy**

TRW LSI Products Inc. components are not designed for use in life support applications, wherein a failure or malfunction of the component can reasonably be expected to result in personal injury. The user of TRW LSI Products Inc. components in life support applications assumes all risk of such use and indemnifies TRW LSI Products Inc. against all damages

TRW LSI Products Inc.

# **D/A Converters**