# QuickLogic PolarPro® II Device Data Sheet

Combining Low Power, Performance, Density, and Embedded RAM

# **Device Highlights**Low Power Programmable Logic

- As low as **TBD** μA

- 0.18 μm, six layer metal CMOS process

- 1.5 V or 1.8 V core voltage, 1.8/2.5/3.3 V drive capable I/Os

- Up to 27 kilobits of SRAM

- Up to 85 I/Os available

- Up to 150,000 system gates

- Nonvolatile, instant-on

- IEEE 1149.1 boundary scan testing compliant

#### **Embedded Dual-Port SRAM**

- Up to four dual-port 4-kilobit and four 2-kilobit high performance SRAM blocks

- True dual-port capability for RAM and FIFOs

- Embedded synchronous/asynchronous FIFO controller

- Configurable and cascadable aspect ratio

## Programmable I/O

- Bank programmable slew rate control

- Eight independent I/O banks capable of supporting multiple I/O standards in one device

- Bank programmable I/O standards: LVTTL, LVCMOS, LVCMOS18, and PCI

#### **Advanced Clock Network**

- Multiple low skew clock networks

- 1 dedicated global clock network

- 4 programmable global clock networks

- Quadrant-based segmentable clock networks

- 20 quad clock networks per device

- 4 quad clock networks per quadrant

- 1 dedicated clock network per quadrant

- One user Configurable Clock Manager (CCM)

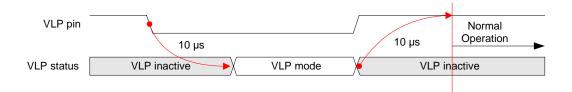

#### Very Low Power (VLP) Mode

- QuickLogic PolarPro II has a special VLP pin which can enable a low power sleep mode that significantly reduces the overall power consumption of the device by placing the device in standby

- Enter VLP mode from normal operation in less than 10 μs (typical)

- Exit from VLP mode to normal operation in less than 10 µs (typical)

#### **Security Links**

There are several security links to disable JTAG access to the device. Programming these optional links completely disables access to the device from the outside world and provides an extra level of design security not possible in SRAM-based FPGAs.

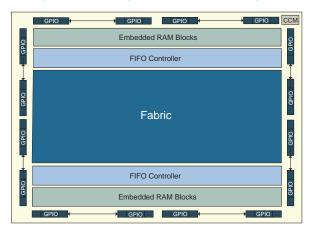

Figure 1: QuickLogic PolarPro II Block Diagram

# Ultra-Low Power FPGA Combining Performance, Density, and Embedded RAM

Table 1: PolarPro II QL2P150

|                  | Features       |         |

|------------------|----------------|---------|

|                  | Max Gates      | 150,000 |

|                  | Logic Cells    | 864     |

|                  | Max I/O        | 85      |

| RAM Modules      |                | 8       |

| FIFO Controllers |                | 8       |

| RAM bits         |                | 27,648  |

| CCMs             |                | 1       |

| Packages         | TFBGA (0.5 mm) | 121     |

| Packages         | TFBGA (0.4 mm) | 121     |

#### **Process Data**

The QuickLogic PolarPro II is fabricated on a  $0.18\mu$ , six layer metal CMOS process. The core voltage is 1.5~V or 1.8~V. The I/O voltage input tolerance and output drive can be set as 1.8~V, 2.5~V, and 3.3~V.

# **Programmable Logic Architectural Overview**

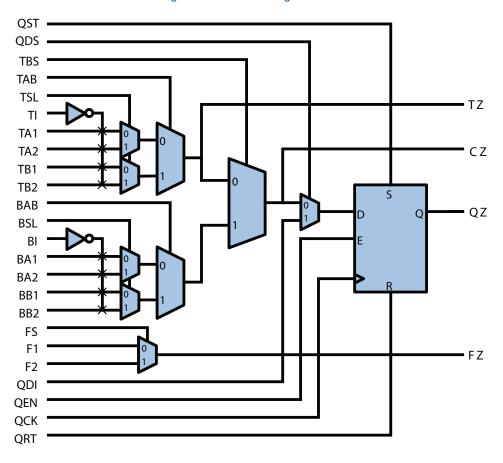

The QuickLogic PolarPro II logic cell structure presented in **Figure 2** is a single register, multiplexer-based logic cell. It is designed for wide fan-in and multiple, simultaneous output functions. The cell has a high fan-in, fits a wide range of functions with up to 24 simultaneous inputs (including register control lines), and four outputs (three combinatorial and one registered). The high logic capacity and fan-in of the logic cell accommodates many user functions with a single level of logic delay.

The QuickLogic PolarPro II logic cell can implement:

- Two independent 3-input functions

- Any 4-input function

- 8 to 1 mux function

- Independent 2 to 1 mux function

- Single dedicated register with clock enable, active high set and reset signals

- Direct input selection to the register, which allows combinatorial and register logic to be used separately

- Combinatorial logic that can also be configured as an edge-triggered master-slave D flip-flop

Figure 2: PolarPro II Logic Cell

### **RAM Modules**

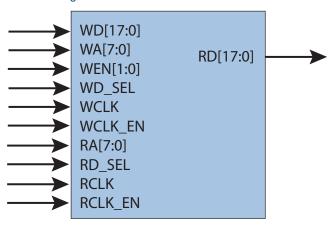

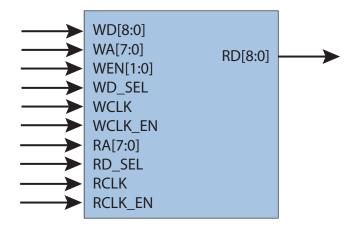

The PolarPro II QL2P150 device has four 4-kilobit (4608 bits) as shown in **Figure 3**, and four 2-kilobit (2304) RAM blocks as shown in **Figure 4**.

The RAM features include:

- · Independently configurable read and write data bus widths

- Independent read and write clocks

- Maximum of two RAM blocks can be concatenated horizontally or vertically

- 4 kilobits for two 2-kilobit RAM blocks and 8 kilobits for two 4-kilobit RAM blocks

- Write byte enables

- Selectable pipelined or non-pipelined read data

- True dual-port RAM functionality

- Clock disabling during idle operation

Figure 3: 4-Kilobit Dual-Port RAM Block

Figure 4: 2-Kilobit Dual-Port RAM Block

**Table 2** describes the RAM interface signals.

Table 2: RAM Interface Signals

| Signal Name | Function           |  |  |  |

|-------------|--------------------|--|--|--|

| Inputs      |                    |  |  |  |

| WD          | Write Data         |  |  |  |

| WA          | Write Address      |  |  |  |

| WEN         | Write Enable       |  |  |  |

| WD_SEL      | Write Chip Select  |  |  |  |

| WCLK        | Write Clock        |  |  |  |

| WCLK_EN     | Write Clock Enable |  |  |  |

| RA          | Read Address       |  |  |  |

| RD_SEL      | Read Chip Select   |  |  |  |

| RCLK        | Read Clock         |  |  |  |

| RCLK_EN     | Read Clock Enable  |  |  |  |

|             | Output             |  |  |  |

| RD          | Read Data          |  |  |  |

The read and write data buses of a RAM block can be arranged to variable bus widths. The bus widths can be configured using the RAM Wizard available in QuickWorks, QuickLogic's development software. The selection of the RAM depth and width determines how the data is addressed.

The RAM blocks also support data concatenation. Designers can cascade multiple RAM modules to increase the depth or width by connecting corresponding address lines together and dividing the words between modules. Generally, this requires the use of additional programmable logic resources. However, when concatenating only two 4-kilobit RAM blocks or two 2-kilobit RAM blocks, they can be concatenated horizontally or vertically without using any additional programmable fabric resources.

For example, two internal 4-kilobit dual-port RAM blocks can be concatenated vertically to create a 512x18 RAM block or horizontally to create a 256x36 RAM block. **Figure 5** displays a block diagram of 4-kilobit RAM blocks horizontal and vertical concatenation.

512x18 Dual-Port RAM 256x36 Dual-Port RAM WD[35:0] WD[17:0] WA[7:0] WA[8:0] RD[35:0] RD[17:0] WEN[1:0] WEN[1:0] WD SEL WD\_SEL WCLK WCLK WCLK EN WCLK EN RA[7:0] RA[8:0] RD\_SEL RD SEL **RCLK RCLK** RCLK\_EN RCLK\_EN Horizontal Concatenation

Figure 5: 4-Kilobit Horizontal and Vertical Concatenation Examples

**Vertical Concatenation**

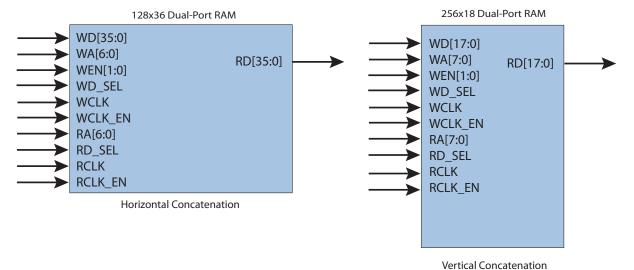

For example, two internal 2-kilobit dual-port RAM blocks can be concatenated vertically to create a 256x18 RAM block or horizontally to create a 128x36 RAM block. **Figure 6** displays a block diagram of 2-kilobit RAM blocks horizontal and vertical concatenation.

Figure 6: 2-Kilobit Horizontal and Vertical Concatenation Examples

Table 3 shows the various RAM configurations supported by the PolarPro II 4-kilobit RAM modules.

Table 3: Available 4-Kilobit RAM Configurations

| Device  | Number of RAM Blocks | Depth | Width | Description               |

|---------|----------------------|-------|-------|---------------------------|

|         | 1                    | 256   | 1-18  | No concantenation         |

|         | 1                    | 512   | 1-9   | No concantenation         |

| QL2P150 | 2                    | 256   | 1-36  | Horizontal concantenation |

|         | 2                    | 512   | 1-18  | Vertical concantenation   |

|         | 2                    | 1024  | 1-9   | Vertical concantenation   |

**Table 4** shows the various RAM configurations supported by the PolarPro II 2-kilobit RAM modules.

Table 4: Available 2-Kilobit RAM Configurations

| Device  | Number of<br>RAM Blocks | Depth | Width | Description               |

|---------|-------------------------|-------|-------|---------------------------|

|         | 1                       | 128   | 1-18  | No concantenation         |

|         | 1                       | 256   | 1-9   | No concantenation         |

| QL2P150 | 2                       | 128   | 1-36  | Horizontal concantenation |

|         | 2                       | 256   | 1-18  | Vertical concantenation   |

|         | 2                       | 512   | 1-9   | Vertical concantenation   |

#### **True Dual-Port RAM**

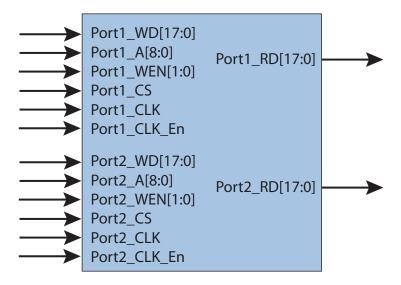

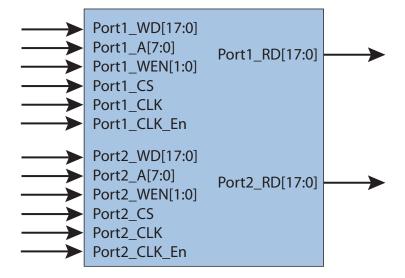

PolarPro II dual-port RAM modules can also be concatenated to generate true dual-port RAMs. The true dual-port RAM module's Port1 and Port2 have completely independent read and write ports, and separate read and write clocks. This allows Port1 and Port2 to have different data widths and clock domains. It is important to note that there is no circuitry preventing a write and read operation to the same address space at the same time. Therefore, it is up to the designer to ensure that the same address is not read from and written to simultaneously, otherwise the data is considered invalid. Likewise, the same address must not be written to from both ports at the same time. However, it is possible to read from the same address.

Figure 7 shows an example of a 512x18 true dual-port RAM.

Figure 7: 512x18 4-Kilobit True Dual-Port RAM Block

Figure 8 shows an example of a 256x18 true dual-port RAM.

Figure 8: 256x18 2-Kilobit True Dual-Port RAM Block

**Table 5** describes the true dual-port RAM interface signals.

Table 5: True Dual-Port RAM Interface Signals

| Port  | Signal Name  | Function      |  |

|-------|--------------|---------------|--|

|       | Inputs       |               |  |

|       | Port1_WD     | Write Data    |  |

|       | Port1_A      | Write Address |  |

|       | Port1_WEN    | Write Enable  |  |

| Port1 | Port1_CS     | Chip Select   |  |

|       | Port1_CLK    | Clock         |  |

|       | Port1_CLK_En | Clock Enable  |  |

|       |              | Output        |  |

|       | Port1_RD     | Read Data     |  |

|       |              | Inputs        |  |

|       | Port2_WD     | Write Data    |  |

|       | Port2_A      | Write Address |  |

|       | Port2_WEN    | Write Enable  |  |

| Port2 | Port2_CS     | Chip Select   |  |

|       | Port2_CLK    | Clock         |  |

|       | Port2_CLK_En | Clock Enable  |  |

|       |              | Output        |  |

|       | Port2_RD     | Read Data     |  |

**Table 6** lists the 4-kilobit true dual-port RAM configurations that are available.

Table 6: Available 4-Kilobit True Dual-Port RAM Configurations

| Device      | Depth | Width |

|-------------|-------|-------|

| QL2P150     | 512   | 1-18  |

| , stant 100 | 1024  | 1-9   |

**Table 7** lists the 2-kilobit true dual-port RAM configurations that are available.

Table 7: Available 2-Kilobit True Dual-Port RAM Configurations

| Device  | Depth | Width |

|---------|-------|-------|

| QL2P150 | 256   | 1-18  |

|         | 512   | 1-9   |

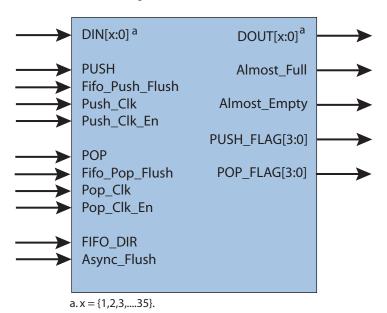

### **Embedded FIFO Controllers**

Every RAM block can be implemented as a synchronous or asynchronous FIFO. There are built-in FIFO controllers that allow for varying depths and widths without requiring programmable fabric resources.

The PolarPro II FIFO controller features include:

- x9, x18 and x36 data bus widths.

- Independent PUSH and POP clocks

- Independent programmable data width on PUSH and POP sides-

- Configurable synchronous or asynchronous FIFO operation

- 4-bit PUSH and POP level indicators to provide FIFO status outputs for each port

- Pipelined read data to improve timing

- Switchable clock domain between PUSH and POP side during asynchronous operation

- Clock disabling during idle operation

- Asynchronous reset (apart from the synchronous FLUSH) going to the pointers

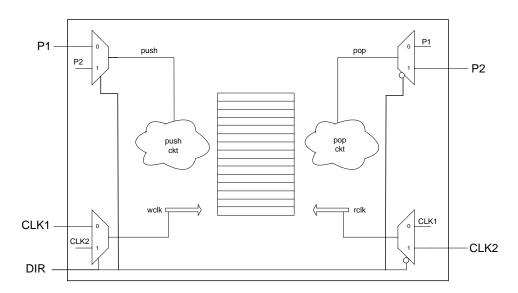

Figure 9 shows an example a FIFO module.

Figure 9: FIFO Module

**Table 8** lists the FIFO configurations that are available.

Table 8: Available FIFO Configurations

| Device   | Number of RAM Blocks    | Depth | Supported Widths |

|----------|-------------------------|-------|------------------|

|          | 1 (2-kilobit RAM block) | 128   | 1-18 bits        |

|          | 1 (2-kilobit RAM block) | 256   | 1-9 bits         |

|          | 2 (2-kilobit RAM block) | 128   | 1-36 bits        |

|          | 2 (2-kilobit RAM block) | 256   | 1-18 bits        |

| QL2P150  | 2 (2-kilobit RAM block) | 512   | 1-9 bits         |

| QLZF 150 | 1 (4-kilobit RAM block) | 256   | 1-18 bits        |

|          | 1 (4-kilobit RAM block) | 512   | 1-9 bits         |

|          | 2 (4-kilobit RAM block) | 256   | 1-36 bits        |

|          | 2 (4-kilobit RAM block) | 512   | 1-18 bits        |

|          | 2 (4-kilobit RAM block) | 1024  | 1-9 bits         |

**Table 9** lists the FIFO controller interface signals.

Table 9: FIFO Interface Signals

|                     |              |           | 3                                             |  |

|---------------------|--------------|-----------|-----------------------------------------------|--|

| Signal Name         | Width (bits) | Direction | Function                                      |  |

| PUSH Signals        |              |           |                                               |  |

| DIN                 | 1 to 36      | I         | Data bus input                                |  |

| PUSH                | 1            | I         | Initiates a data push                         |  |

| Fifo_Push_Flush     | 1            | I         | Empties the FIFO                              |  |

| Push_Clk            | 1            | I         | Push data clock                               |  |

| Push_Clk_En         | 1            | I         | Push clock enable                             |  |

|                     |              | POP Sigr  | nals                                          |  |

| DOUT                | 1 to 36      | 0         | Data bus output                               |  |

| POP                 | 1            | I         | Initiates a data pop                          |  |

| Fifo_Pop_Flush      | 1            | I         | Empties the FIFO                              |  |

| Pop_Clk             | 1            | I         | Pop data clock                                |  |

| Pop_Clk_En          | 1            | I         | Pop clock enable                              |  |

| Common PORT Signals |              |           |                                               |  |

| Fifo_Dir            | 1            | I         | Push-Pop domain switching                     |  |

| Async_Flush         | 1            | I         | Asynchronous input to flush FIFO              |  |

| Status Flags        |              |           |                                               |  |

| Almost_Full         | 1            | 0         | Asserted when FIFO has one location available |  |

| Almost_Empty        | 1            | 0         | Asserted when FIFO has one location used      |  |

| PUSH_FLAG           | 4            | 0         | FIFO PUSH level indicator                     |  |

| POP_FLAG            | 4            | 0         | FIFO POP level indicator                      |  |

**Table 10** and **Table 11** highlight the corresponding FIFO level indicator for each 4-bit value of the PUSH\_FLAG and POP\_FLAG outputs.

Table 10: FIFO PUSH Level Indicator Values

| Value  | Status                                          |

|--------|-------------------------------------------------|

| 0000   | Full                                            |

| 0001   | Empty                                           |

| 0010   | Room for more than one-half                     |

| 0011   | Room for more than one-forth                    |

| 0100   | Room for less than one-forth to 64 <sup>a</sup> |

| 1010   | Room for 32 to 63 <sup>a</sup>                  |

| 1011   | Room for 16 to 31                               |

| 1100   | Room for 8 to 15                                |

| 1101   | Room for 4 to 7                                 |

| 1110   | Room for 2 to 3                                 |

| 1111   | Room for 1                                      |

| Others | Reserved                                        |

a. For a FIFO depth of 256, Value 0100 will not be asserted. The PUSH flag will shift directly from 0011 to 1010 as data is pushed. For a FIFO depth of 128, Values 0100 and 1010 will not be asserted. The PUSH flag will shift directly from 0011 to 1011 as data is pushed.

Table 11: FIFO POP Level Interface Signals

| Value  | Status                                              |

|--------|-----------------------------------------------------|

| 0000   | Empty                                               |

| 0001   | 1 entry in FIFO                                     |

| 0010   | At least 2 entries in FIFO                          |

| 0011   | At least 4 entries in FIFO                          |

| 0100   | At least 8 entries in FIFO                          |

| 0101   | At least 16 entries in FIFO                         |

| 0110   | At least 32 entries in FIFO <sup>a</sup>            |

| 1000   | 64 entries to less than one-forth full <sup>a</sup> |

| 1101   | One-forth or more full                              |

| 1110   | One-half or more full                               |

| 1111   | Full                                                |

| Others | Reserved                                            |

a. For a FIFO depth of 256, Value 1000 will not be asserted. The POP Flag will shift directly from 1101 to 0110 as data is popped. For a FIFO depth of 128, Values 1000 and 0110 will not be asserted. The POP flag will shift directly from 1101 to 0101 as data is popped.

### **PUSH-POP Domain Switching**

During asynchronous operation, the FIFO works in a half-duplex manner, meaning PUSH on one clock domain and POP on the other clock domain. To provide each domain the PUSH and POP capability, a DIR port is added to choose what function each clock domain will have. The DIR port determines the functions of P1 and P2, and the clock assigned to PORT1 and PORT2 of the FIFO. After the direction switches, the FIFO pointers must be reset.

**Figure 10** shows the PUSH-POP domain switching operation.

Figure 10: PUSH-POP Domain Switching

**Table 12** shows the PUSH-POP direction switching.

Table 12: PUSH-POP Direction Switching

| DIR | Direction                 |

|-----|---------------------------|

| 0   | CLK1/P1 PUSH, CLK2/P2 POP |

| 1   | CLK1/P1 POP, CLK2/P2 PUSH |

#### **FIFO Synchronous Flush Procedure**

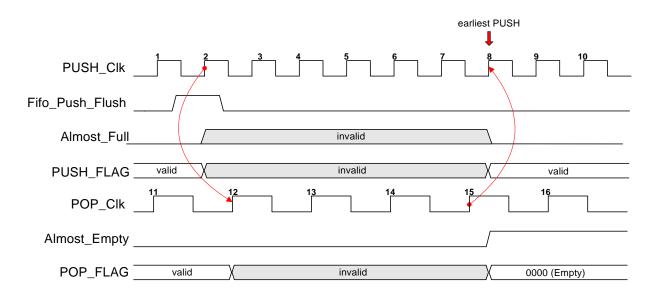

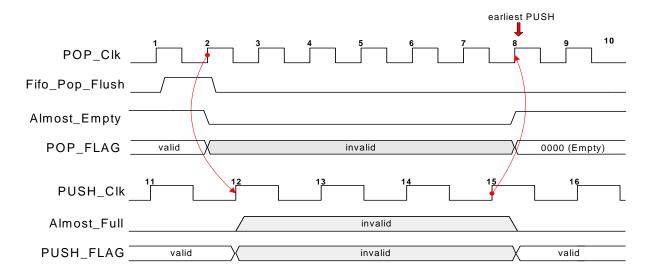

Both PUSH and POP domains are provided with a flush input signal synchronized to their respective clocks. When a flush is triggered from one side of the FIFO, the signal propagates and re-synchronizes internally to the other clock domain. During a flush operation, the values of the FIFO flags are invalid for a specific number of cycles (see **Figure 11** and **Figure 12**).

As shown in **Figure 11**, when the **Fifo\_Push\_Flush** asserts, the **Almost\_Full** and **PUSH\_FLAG** signals become invalid until the FIFO can flush the data with regards to the Push clock domain as well as the Pop clock domain. After the **Fifo\_Push\_Flush** is asserted, the next rising edge of the Pop clock starts the Pop flush routine.

**Figure 11** illustrates a FIFO Flush operation. After the **Fifo\_Push\_Flush** is asserted at 2 (**PUSH\_Clk**), four POP clock cycles (12 through 15) are required to update the **POP\_FLAG**, and **PUSH\_FLAG** signals. The **Almost\_Empty** signal is asserted to indicate that the push flush operation has been completed. On the following rising edge of the **PUSH\_Clk** (8), the **PUSH\_FLAG** is accordingly updated to reflect the successful flush operation.

Figure 11: FIFO Flush from PUSH Side

**Figure 12** illustrates a POP flush operation. After the **Fifo\_Pop\_Flush** is asserted at 2 (**POP\_Clk**), four PUSH clock cycles (12 through 15) are required to update the **POP\_FLAG**, and **PUSH\_FLAG** signals. The **Almost\_Empty** signal is asserted to indicate that the pop flush operation has been completed. On the following rising edge of the **POP\_Clk** (8), the **POP\_FLAG** is updated accordingly to reflect the successful flush operation.

Figure 12: FIFO Flush from POP Side

**Figure 11** and **Figure 12** are only true for this particular PUSH-POP clock frequency combination. The clock frequency and phase difference between POP\_Clk and PUSH\_Clk can cause an additional flush delay of one clock cycle in either domain because of the asynchronous relationship between the two clocks.

#### **Asynchronous Flush**

Apart from the synchronous flush controls, an asynchronous flush is provided through the port ASYNC\_FLUSH. Assertion of this signal flushes the FIFO PUSH and POP pointers.

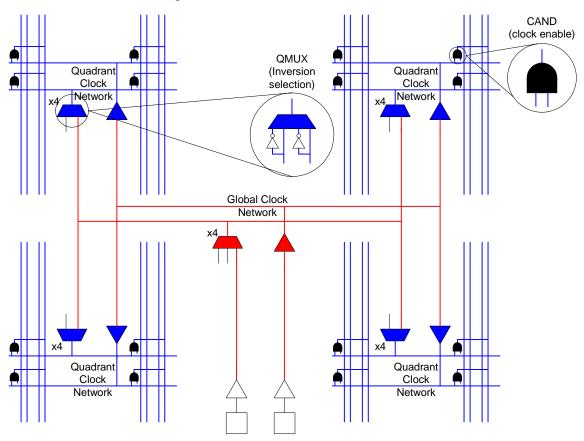

#### **QL2P150 Clock Network Architecture**

#### **Clock Network Architecture**

The PolarPro II clock network architecture consists of a 2-level H-tree network as shown in **Table 13**. The first level of each clock tree spans from the clock input pad to the global clock network and to the center of each quadrant of the chip. The second level spans from the quadrant clock network to every logic cell inside that quadrant. There are five global clocks in the global clock network, and five quadrant clocks in each quadrant clock network. All global clocks drive the quadrant clock network inputs.

The quadrant clock network passes either the original input clock or an inverted version of the input clock to the column clock buffer. The column clock buffer allows dynamically enabling or disabling all clocks in the column level. The global clocks can drive RAM block clock inputs and reset, set, enable, and clock inputs to I/O registers. Furthermore, the quadrant clock outputs can be routed to all logic cell inputs.

Figure 13: PolarPro II Clock Network Architecture

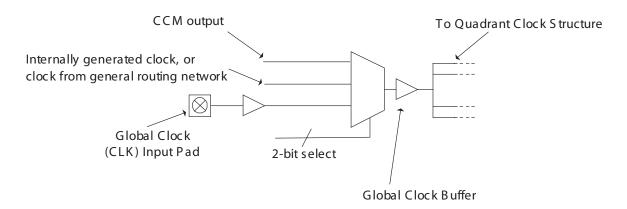

Of the five global clock networks:

- Two can be either driven directly by clock pads, Configurable Clock Manager (CCM) outputs, or internally generated signals. These two global clocks go through 3-input global clock muxes located in the middle of the die. See **Figure 14** for a diagram of a 3-input global clock mux.

- Two can be either driven directly by clock pads or internally generated signals.

- One is a dedicated global clock network that goes directly to the quadrant clock network and is used as a dedicated fast clock.

Figure 14: Global Clock Structure

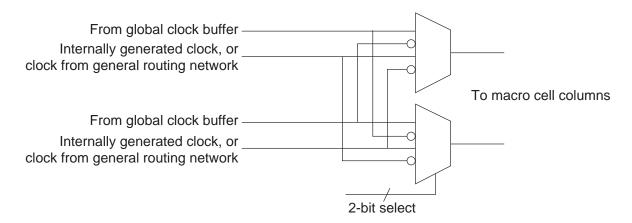

**Figure 15** illustrates the quadrant HSCK 4-input mux.

Figure 15: Quadrant Clock Structure

The quadrant HSCK mux is located at the middle of the quadrant. These 4-input HSCK muxes output inverted or non-inverted output from global HSCK, or inverted or non-inverted quad level HSCK depending on the 2-bit select line.

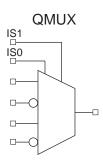

A quadrant HSCK mux can be implemented in Verilog, VHDL, and schematic designs by instantiating the quadrant HSCK mux macro, QMUX. **Figure 16** shows the schematic representation of the QMUX macro.

Figure 16: QMUX Macro

It is important to note that the select lines for the global clock and quadrant clock muxes are static signals and cannot be changed dynamically during device operation.

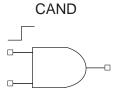

Using the column clock buffers, all clocks can be dynamically disabled at the column level. Column clock buffers can be implemented in Verilog, VHDL, and schematic designs by instantiating the column clock buffer macro, CAND. **Figure 17** shows the schematic representation of the CAND macro.

Figure 17: CAND Macro

## **Dynamic Clock Enable**

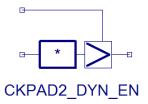

The QuickLogic PolarPro II QL2P150 devices provide a powerful dynamic clock enable feature that allows designers to dynamically enable and disable clocks routed into the QuickLogic device. Associated with each of the five clock inputs is a clock enable, which is an interface signal that can be either dynamically controlled via a routable signal or tied high or low. Once an incoming clock is disabled, the clock is driven low internally. All the logic that is driven by the clock is held at the state when the clock was disabled. If a reset signal is passed through the clock pad, the dynamic disable should not be used.

As an additional feature, PolarPro II devices have built-in deglitching circuitry to prevent clock glitching during transitions so that clocks can be enabled or disabled asynchronously without the possibility of false edge detection within the internal logic. The dynamic clock disable feature can be implemented in Verilog, VHDL, and schematic designs by instantiating the dynamic clock enable macro, CKPAD2\_DYN\_EN. **Figure 18** shows the schematic representation of the dynamic clock enable macro.

Figure 18: Clock Pad Macro for Dynamic Clock Enable

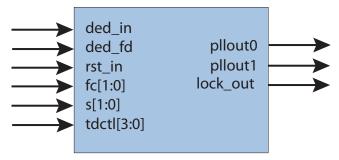

## **Configurable Clock Manager (CCM)**

The CCM features include:

- Input frequency range from 10 MHz to 150 MHz

- Output frequency range from 25 MHz to 200 MHz

- Output jitter is less than 200 ps peak-to-peak

- Two outputs: pullout0 (with 0° phase shift), and pullout1 (with an option of 0°, 90°, 180°, or 270° phase shift plus a programmable delay).

- Programmable delay allows delays up to 2.5 ns at 250 ps intervals (typical)

- Fixed feedback path

- Output frequency lock time in less than  $10 \mu s$

Figure 19: Configurable Clock Manager

The reset signal can be routed from a clock pad or generated using internal logic. The lock\_out signal can be routed to internal logic and/or an output pad. CCM clock outputs can drive the global clock networks, as well as any general purpose I/O pin. Once the CCM has synchronized the output clock to the incoming clock, the lock\_out signal will be asserted to indicate that the output clock is valid. Lock detection requires at least 10 µs after reset to assert lock\_out. The PolarPro II CCMs have three modes of operation, based on the input frequency and desired output frequency. **Table 13** indicates the features of each mode.

Table 13: CCM PLL Mode Frequencies

| Output<br>Frequency | Input Frequency<br>Range | Output Frequency<br>Range | PLL Mode  |

|---------------------|--------------------------|---------------------------|-----------|

| x1                  | 25 MHz to 150 MHz        | 25 MHz to 150 MHz         | PLL_MULT1 |

| x2                  | 15 MHz to 100 MHz        | 30 MHz to 200 MHz         | PLL_MULT2 |

| x4                  | 10 MHz to 50 MHz         | 40 MHz to 200 MHz         | PLL_MULT4 |

#### **CCM Signals**

**Table 14** provides the name, direction, function and description of the CCM ports.

Table 14: CCM Signals

| Signal Name | Direction | Function Description        |                                                                                                                                                      |  |

|-------------|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             |           | Routa                       | ble Ports                                                                                                                                            |  |

| ded_in      | I         | Dedicated Input             | Clock pad CCM input source.                                                                                                                          |  |

| rst_in      | I         | Reset                       | Active high reset: If rst_in is asserted, pllout0 and pllout1 are reset to 0. This signal must be asserted and then released for lock_out to assert. |  |

| pllout0     | 0         | 0° Phase Clock              | 0° phase clock output.                                                                                                                               |  |

| pllout1     | 0         | Configurable Phase<br>Clock | 0°, 90°,180°, or 270° phase clock output with programmable delay.                                                                                    |  |

| lock_out    | 0         | Lock Detect                 | Active high lock detection signal. Active when the pllout signals correctly output the configured functionality.                                     |  |

|             |           | Stati                       | c Ports                                                                                                                                              |  |

| fc[1:0]     | ı         | Phase Shift Control         | Determines whether pllout1 is 0°, 90°, 180°, or 270° degrees out of phase with pllout0 <sup>a</sup> .                                                |  |

| s[1:0]      | I         | Set Mode                    | Determines pllout1 and pllout0 frequency multiplier (x1, x2, or x4).                                                                                 |  |

| tdctl[3:0]  | ı         | Time Delay Control          | Pllout1 programmable delay, configurable in 250 ps increments up to a maximum of 2.5 ns.  NOTE: 250 ps can vary depending on process variation.      |  |

a. The pllout1 output can vary up to -5% with respect to the pllout0 output. Therefore, QuickLogic recommends thorough post-layout simulation in order to verify satisfactory operation of the CCMs.

**Table 15**, and **Table 16** and **Table 17** give the values used to configure the Set Mode, and Phase Shift Control and Time Delay Control bits.

Table 15: Set Mode Values

| s[1:0] | Multiplier |

|--------|------------|

| 00     | x1         |

| 01     | x2         |

| 10     | x4         |

| 11     | Reserved   |

Table 16: Phase Shift Control Values

| fc[1:0] | Phase Shift<br>(Deg.) |

|---------|-----------------------|

| 00      | 0                     |

| 01      | 90                    |

| 10      | 180                   |

| 11      | 270                   |

Table 17: Time Delay Control Values

| tdctl[3:0] | Time Delay<br>(ps) |

|------------|--------------------|

| 0000       | 0                  |

| 0001       | 250                |

| 0010       | 500                |

| 0011       | 750                |

| 0100       | 1000               |

| 0101       | 1250               |

| 0110       | 1500               |

| 0111       | 1750               |

| 1000       | 2000               |

| 1001       | 2250               |

| 1010       | 2500               |

| 1011       | Reserved           |

| 1100       | Reserved           |

| 1101       | Reserved           |

| 1110       | Reserved           |

| 1111       | Reserved           |

#### **CCM Configurations**

The main purpose of the CCM is to align the clock arrival times of two separate clock destinations, whether it is within the FPGA or external to the chip. The difference between the two clock destinations is referred to as clock skew. To correct for clock skew the CCMs can be configured to shift the phase and/or delay of the pllout1 clock output.

In most cases the desired phase or added delay can be accomplished by configuring both the clock source input and feedback input as dedicated. In the case of a dedicated clock source and dedicated feedback, the QuickLogic development software calculates and generates all of the required routing delays to produce the requested configuration.

Table 18: Available Configurations

| Clock               | Feedback           | Example Usage                                                 | Comments                                       |

|---------------------|--------------------|---------------------------------------------------------------|------------------------------------------------|

| Dedicated clock pad | Dedicated feedback | Standard PLL application. Reduce set-up or clock-to-out time. | If the clock pad and destination are in phase. |

For more information on CCMs and how to use them in QuickWorks, refer to <u>Application Note 87 Configurable Clock Managers</u>.

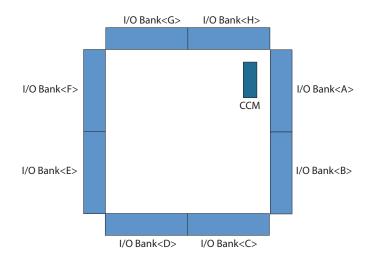

## Simultaneously Switching Outputs (SSOs) While Using a CCM

SSOs are outputs that transition at the same time in the same direction (either from VCC to GND or GND to VCC). To ensure that the CCM never loses lock over all possible frequencies of operation, designers must follow the guidelines specified in this section when using the FPGA outputs as SSOs. These guidelines include the number of SSOs placed adjacent to the CCM and the quality of the power filtering circuit sourcing the CCM block.

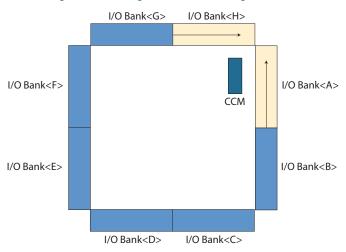

**Figure 20** shows a basic layout of the eight I/O banks available in PolarPro II devices and the relative placement of the CCM.

Figure 20: Basic Layout of I/O Banks and CCMs

SSOs placed in I/O Bank<A> and I/O Bank<H> in close proximity to the CCM can affect the CCM's functionality.

**NOTE:** To define the boundary of operation when using SSOs in conjunction with the CCM add SSOs starting from the far end of a bank relative to the CCM's location.

Figure 21: Adding SSOs When Using the CCM

To ensure proper operation of the CCM:

- 1. Limit the number of SSOs in I/O Bank<A> and I/O Bank<H> that are synchronous to the CCM (i.e., clocked by CCM outputs).

- 2. Limit the number of SSOs in I/O Bank<A> and I/O Bank<H> that are asynchronous to CCM (i.e., not clocked by CCM<B> outputs).

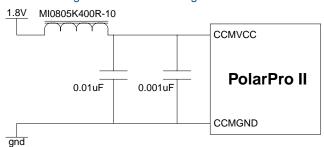

- **3.** The power supply to the CCMs must have adequate noise filtering circuits. QuickLogic Reference Design boards use the noise filtering circuit shown in **Figure 22**.

Figure 22: Noise Filtering Circuit

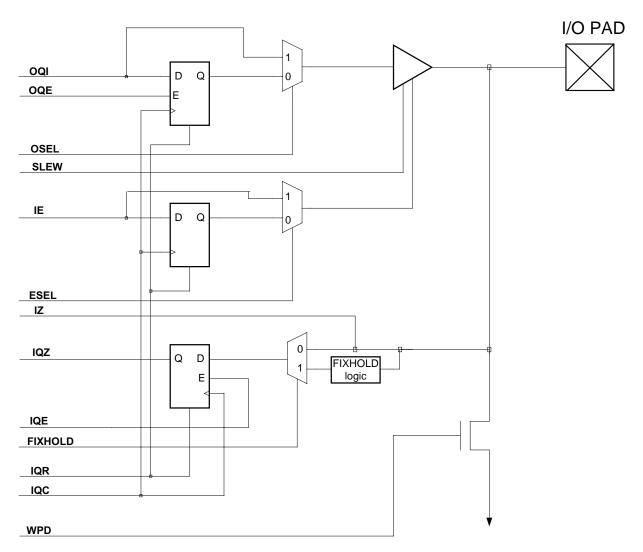

# **General Purpose Input Output (GPIO) Cell Structure**

The GPIO features include:

- Direct or registered input with input path select

- Direct or registered output with output path select

- Direct or registered output enable with OE path select

- Input buffer enable to reduce power

- Programmable pull-down control

- Configurable slew rate

- Support for JTAG boundary scan

Figure 23: PolarPro II GPIO Cell

With bi-directional I/O pins and global clock input pins, the PolarPro II device maximizes I/O performance, functionality, and flexibility. All input and I/O pins are  $1.8\ V$ ,  $2.5\ V$ , and  $3.3\ V$  tolerant and comply with the specific I/O standard selected. For single-ended I/O standards, the corresponding VCCIO bank input specifies the input tolerance and the output drive voltage. A weak pull-down function can be configured for an individual I/O. **Table 19** lists the GPIO interface signals.

Table 19: GPIO Interface Signals

| Signal Name | Direction | Function                                                                               |

|-------------|-----------|----------------------------------------------------------------------------------------|

|             | R         | outable Signals                                                                        |

| OQI         | I         | Output path input                                                                      |

| OQE         | I         | Output register enable signal                                                          |

| IE          | I         | Enable path input                                                                      |

| IZ          | 0         | Input path combinatorial output to routing                                             |

| IQZ         | 0         | Input path register output to routing                                                  |

| IQE         | I         | Input register enable signal                                                           |

| IQC         | I         | Register clock                                                                         |

| IQR         | I         | Register reset                                                                         |

| PAD         | I/O       | I/O pad                                                                                |

|             |           | Static Signals                                                                         |

| ESEL        | I         | Enable register/combinatorial path select '1': combinatorial '0': register             |

| OSEL        | I         | Output register/combinatorial path select '1': combinatorial '0': register             |

| SLEW        | I         | SLEW selection '0': Slow slew '1': Fast slew                                           |

| FIX_HOLD    | I         | Input delay path selection '0' : Non-delay '1' : Delayed                               |

| WPD         | I         | Weak pull-down '0' : Disable - no weak pull-down '1' : Enable - weak pull-down enabled |

## **Programmable Pull-Down**

PolarPro II I/O support Weak Pull-Down. A programmable Weak Pull-Down resistor is available on each I/O. The I/O Weak Pull-Down eliminates the need for external pull-down resistors. When WPD= 1 Weak Pull-Down is enabled.

#### **Programmable Slew Rate**

Each I/O has programmable slew rate capability. The PolarPro II GPIOs allow up to two different slew rate speeds (slow and fast). Slow slew rates can be used to reduce noise caused by I/O switching.

I/O interface standards are programmable on a per bank basis. **Table 20** illustrates the I/O bank configurations available. Each I/O bank is independent of other I/O banks and each I/O bank has its own VCCIO supply inputs. A mixture of different I/O standards can be used on a PolarPro II device. However, there is a limitation as to which I/O standards can be supported within a given bank. Only standards that share a common VCCIO can be shared within the same bank (e.g., PCI and LVTTL).

| I/O Standard | VCCIO Voltage | Application          |

|--------------|---------------|----------------------|

| LVTTL        | 3.3 V         | General Purpose      |

| LVCMOS25     | 2.5 V         | General Purpose      |

| LVCMOS18     | 1.8 V         | General Purpose      |

| PCI          | 3.3 V         | PCI Bus Applications |

Table 20: I/O Standards and Applications

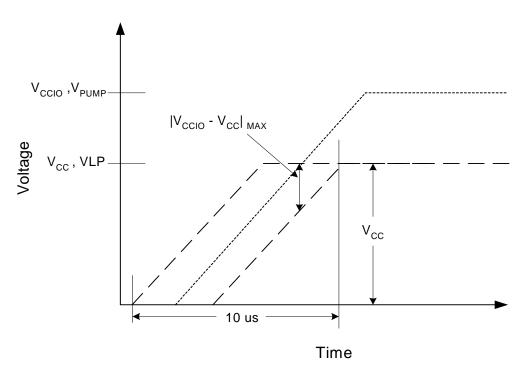

## Very Low Power (VLP) Mode

The QuickLogic PolarPro II devices have a unique feature, referred to as VLP mode, which reduces power consumption by placing the device in standby. Specifically, VLP mode can bring the total standby current down to less than  $10~\mu A$  at room temperature when no incoming signals are toggled. The active low VLP pin controls VLP mode. For normal operation, the VLP pin must be driven to a voltage anywhere between 1.8~V and 3.3~V. At 1.8~V, the VPUMP pin can be tied to 3.3~V for data retention in VLP mode, or to 0~V which does not allow data retention in VLP mode and draws additional current during normal operation. If VLP is tied to 1.5~V, the VPUMP pin must be tied to 3.3~V for VLP mode to be operational.

When the PolarPro II device goes into VLP mode, the following occurs:

- All logic cell registers and GPIO registers values are held

- All RAM cell data is retained

- The outputs from all GPIO to the internal logic are tied to '0'

- GPIO outputs drive the previous values

- GPIO output enables retain the previous values

- Clock pad inputs are gated

- CCM is held in the reset state

During the transition from VLP mode to normal operation, the VLP pin can draw up to 1.5 mA. Consequently, if using a pull-up resistor, use a pull-up resistor with a value that is less than 2 K $\Omega$ . The entire operation from normal mode to VLP mode requires 10  $\mu$ s. As the device exits out of VLP mode, which also takes 10  $\mu$ s, the data from the registers, RAM, and GPIO are used to recover the functionality of the device. Furthermore, since the CCM was in a reset state during VLP mode, it must re-acquire the correct output signal before asserting lock\_out. Figure 24 displays the delays associated with entering and exiting VLP mode.

Figure 24: Typical VLP Mode Timing

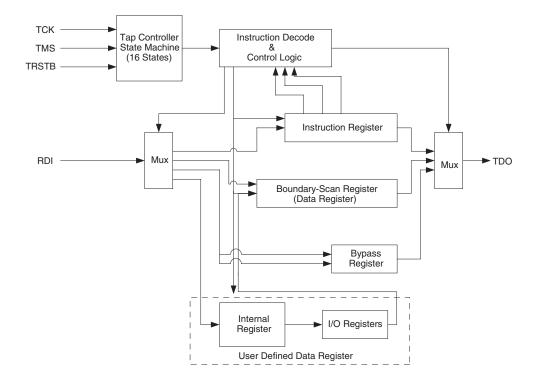

# **Joint Test Access Group (JTAG) Information**

Figure 25: JTAG Block Diagram

QuickLogic's PolarPro II devices comply with IEEE standard 1149.1, the Standard Test Access Port and Boundary Scan Architecture. The JTAG boundary scan test methodology allows complete observation and control of the boundary pins of a JTAG-compatible device through JTAG software. A Test Access Port (TAP) controller works in concert with the Instruction Register (IR), which allow users to run three required tests along with several user-defined tests. JTAG tests allow users to reduce system debug time, reuse test platforms and tools, and reuse subsystem tests for comprehensive verification of higher level system elements.

The 1149.1 standard requires the following three tests:

- Extest Instruction. The Extest Instruction performs a printed circuit board (PCB) interconnect test. This test places a device into an external boundary test mode, selecting the boundary scan register to be connected between the TAP Test Data In (TDI) and Test Data Out (TDO) pins. Boundary scan cells are preloaded with test patterns (through the Sample/Preload Instruction), and input boundary cells capture the input data for analysis.

- Sample/Preload Instruction. The Sample/Preload Instruction allows a device to remain in its functional mode, while selecting the boundary scan register to be connected between the TDI and TDO pins. For this test, the boundary scan register can be accessed through a data scan operation, allowing users to sample the functional data entering and leaving the device.

- Bypass Instruction. The Bypass Instruction allows data to skip a device boundary scan entirely, so the

data passes through the bypass register. The Bypass instruction allows users to test a device without passing

through other devices. The bypass register is connected between the TDI and TDO pins, allowing serial

data to be transferred through a device without affecting the operation of the device.

#### **JTAG BSDL Support**

- Boundary Scan Description Language (BSDL)

- Machine-readable data for test equipment to generate testing vectors and software

- BSDL files available for all device/package combinations from QuickLogic

- Extensive industry support available and ATVG (Automatic Test Vector Generation)

# **Electrical Specifications**

#### **DC Characteristics**

The DC Specifications are provided in Table 21 through Table 24.

Table 21: Absolute Maximum Ratings

| Parameter         | Value           | Parameter                             | Value              |

|-------------------|-----------------|---------------------------------------|--------------------|

| VCC Voltage       | -0.5 V to 2.2 V | ESD Pad Protection                    | TBD                |

| VCCIO Voltage     | -0.5 V to 4.0 V | Leaded Package<br>Storage Temperature | -65° C to + 150° C |

| Input Voltage     | -0.5 V to 4.0 V | Laminate Package (BGA)                | -55° C to + 125° C |

| Latch-up Immunity | ±100 mA         | Storage Temperature                   | -55 C t0 + 125 C   |

Table 22: Recommended Operating Range

| Symbol | Parameter                   | Industrial |      | Comr | Unit |      |

|--------|-----------------------------|------------|------|------|------|------|

|        | Farameter                   | Min.       | Max. | Min. | Max. | Onit |

| VCC    | Supply Voltage              | 1.43       | 1.89 | 1.43 | 1.89 | V    |

| VCCIO  | I/O Input Tolerance Voltage | 1.71       | 3.60 | 1.71 | 3.60 | V    |

| TJ     | Junction Temperature        | -40        | 100  | 0    | 85   | °C   |

Table 23: DC Characteristics

| Symbol             | Parameter                         | Conditions        | Min. | Тур. | Max. | Units         |

|--------------------|-----------------------------------|-------------------|------|------|------|---------------|

| l <sub>l</sub>     | I or I/O Input Leakage Current    | VI = VCCIO or GND | TBD  | TBD  | TBD  | μA            |

| I <sub>OZ</sub>    | 3-State Output Leakage Current    | VI = VCCIO or GND |      |      |      | μA            |

| Cı                 | I/O Input Capacitance             | VCCIO = 3.6 V     |      |      |      | pF            |

| C <sub>CLOCK</sub> | Clock Input Capacitance           | VCCIO = 3.6 V     |      |      |      | pF            |

| I <sub>REF</sub>   | Quiescent Current on INREF        | -                 |      |      |      | μA            |

|                    |                                   | VCCIO = 3.6 V     |      |      |      | μA            |

| I <sub>PD</sub>    | Current on programmable pull-down | VCCIO = 2.75 V    |      |      |      | μA            |

|                    |                                   | VCCIO = 1.89 V    |      |      |      | μA            |

|                    |                                   | VCCIO = 3.6 V     |      |      |      | μA            |

| I <sub>PU</sub>    | Current on programmable pull-up   | VCCIO = 2.75 V    |      |      |      | μA            |

|                    |                                   | VCCIO = 1.89 V    |      |      |      | μA            |

| I <sub>VLP</sub>   | Quiescent Current on VLP pin      | VLP=3.3           |      |      |      | μA            |

| I <sub>CCM</sub>   | Quiescent Current on each CCMVCC  | VCC=1.89 V        |      |      |      | μA            |

|                    | Quiescent Current                 | VLP=GND           |      |      |      | μA            |

| I <sub>VCC</sub>   | Quiescent Current                 | VLP=3.3V          |      |      |      | μA            |

|                    |                                   | VCCIO = 3.6 V     |      |      |      | μA            |

| I <sub>VCCIO</sub> | Quiescent Current on VCCIO        | VCCIO = 2.75 V    |      |      |      | μA            |

|                    |                                   | VCCIO = 1.89 V    |      |      |      | <b>TBD</b> μA |

Table 24: DC Input and Output Levels<sup>a</sup>

| Symbol   | INF              | REF              |                  | V <sub>IL</sub>  | ٧                       | ін —             | V <sub>OL</sub>  | V <sub>OH</sub>  | I <sub>OL</sub> | I <sub>OH</sub> |

|----------|------------------|------------------|------------------|------------------|-------------------------|------------------|------------------|------------------|-----------------|-----------------|

| Symbol   | V <sub>MIN</sub> | V <sub>MAX</sub> | V <sub>MIN</sub> | V <sub>MAX</sub> | V <sub>MIN</sub>        | V <sub>MAX</sub> | V <sub>MAX</sub> | V <sub>MIN</sub> | mA              | mA              |

| LVTTL    | n/a              | n/a              | -0.3             | 0.8              | 2.2                     | VCCIO + 0.3      | 0.4              | 2.4              | 2.0             | -2.0            |

| LVCMOS2  | n/a              | n/a              | -0.3             | 0.7              | 1.7                     | VCCIO + 0.3      | 0.7              | 1.7              | 2.0             | -2.0            |

| LVCMOS18 | n/a              | n/a              | -0.3             | 0.63             | 1.2                     | VCCIO + 0.3      | 0.7              | 1.7              | 2.0             | -2.0            |

| PCI      | n/a              | n/a              | -0.3             | 0.3 x VCCIO      | 0.6 x V <sub>CCIO</sub> | VCCIO + 0.5      | 0.1 x VCCIO      | 0.9 x VCCIO      | 1.5             | -0.5            |

a. The data provided in **Table 24** represents the JEDEC and PCI specification. QuickLogic devices either meet or exceed these requirements.

#### **AC Characteristics**

All AC data is TBD

# **Package Thermal Characteristics**

The PolarPro II device is available for Commercial (0°C to 85°C Junction), Industrial (-40°C to 100°C Junction), and Military (-55°C to 125°C Junction) temperature ranges.

Thermal Resistance Equations:

$$\begin{array}{l} \theta_{JC} = \left( \begin{smallmatrix} T_J & - & T_C \end{smallmatrix} \right) / P \\ \theta_{JA} = \left( \begin{smallmatrix} TJ & - & TA \end{smallmatrix} \right) / P \\ P_{MAX} = \left( \begin{smallmatrix} T_{JMAX} & - & T_{AMAX} \end{smallmatrix} \right) / \theta_{JA} \end{array}$$

Parameter Description:

$\theta_{JC}$ : Junction-to-case thermal resistance

$\theta_{\text{JA}}$ : Junction-to-ambient thermal resistance

T<sub>J</sub>: Junction temperature

T<sub>A</sub>: Ambient temperature

P: Power dissipated by the device while operating

P<sub>MAX</sub>: The maximum power dissipation for the device

$T_{JMAX}$ : Maximum junction temperature

T<sub>AMAX</sub>: Maximum ambient temperature

**NOTE:** Maximum junction temperature  $(T_{JMAX})$  is 125°C. To calculate the maximum power dissipation for a device package look up  $\theta_{JA}$  from **Table 25**, pick an appropriate  $T_{AMAX}$  and use:

$$P_{MAX} = (125^{\circ}C - T_{AMAX})/\theta_{JA}$$

Table 25: Package Thermal Characteristics

| Package Description |              |                     |           |       | neta-JA (° C/ | W)      |

|---------------------|--------------|---------------------|-----------|-------|---------------|---------|

| Device              | Package Code | Package Type        | Pin Count | 0 LFM | 200 LFM       | 400 LFM |

| QL2P150             | PU           | TFBGA (6 mm x 6 mm) | 121       | TBD   | TBD           | TBD     |

| QL2P150             | PD           | TFBGA (5 mm x 5 mm) | 121       | TBD   | TBD           | TBD     |

## **Moisture Sensitivity Level**

All PolarPro II devices are Moisture Sensitivity Level 3.

Table 26: Solder Composition

| Lead Type  | Pb-Free                      |

|------------|------------------------------|

| BGA Solder | Sn3AgCu:Sn4AgCu <sup>a</sup> |

a. Sn3AgCu:Sn4AgCu means that Ag can range from 3% to 4%. Cu is always 0.5%.

# **Power-Up Sequencing**

Figure 26: Power-Up Sequencing

**Figure 26** shows an example where all VCCIO = 3.3 V, VPUMP = 3.3 V and VLP = 1.8 V. When powering up a PolarPro II device, VCC, VCCIO rails must take  $10 \mu s$  or longer to reach the maximum value (refer to **Figure 26**). Ramping VCC and VCCIO faster than  $10 \mu s$  can cause the device to behave improperly.

It is also important to ensure VCCIO and VLP are within 500 mV of VCC when ramping up the power supplies. In the case where VCCIO or VLP are greater than VCC by more than 500 mV an additional current draw can occur as VCC passes its threshold voltage. In a case where VCC is greater than VCCIO by more than 500 mV the protection diodes between the power supplies become forward biased. If this occurs then there will be an additional current load on the power supply. Having the diodes on can cause a reliability problem, since it can wear out the diodes and subsequently damage the internal transistors.

## **Programming Stipulation**

For PolarPro II devices to correctly program, there must not be any race conditions or internally generated free-running oscillators in the design. This will cause an ICC programming failure during the programming process. QuickLogic cannot guarantee the operation of any device that fails programming. Therefore, race conditions and free-running oscillators must be removed from designs so that PolarPro II devices can correctly pass programming.

# **Pin Descriptions**

Table 27: Pin Descriptions

| Pin                        | Direction | Function                                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------------------------|-----------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Dedicated Pin Descriptions |           |                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| GPIO(H:A)                  | I/O       | General purpose input/output pin               | The I/O pin is a bi-directional pin, configurable to either an input-only, output-only, or bi-directional pin. The letter inside the parenthesis means that the I/O is located in the bank with that letter. If an I/O is not used, the development software provides the option of tying that pin to GND, VCCIO, or Hi-Z.                                                                                                               |  |  |  |  |  |

| CLK(H:G)<br>CLK(D:C)       | I         | Global clock network pin low skew global clock | This pin provides access to a distributed network capable of driving the CLOCK, SET, RESET, all inputs to the logic cell, Read and Write clocks, Read and Write enables of the embedded RAM blocks, and I/O inputs.                                                                                                                                                                                                                      |  |  |  |  |  |

| DEDCLK(H)                  | I         | Dedicated clock network pin low skew clock     | This pin provides access to a distributed network capable of driving the CLOCK, SET, RESET, all inputs to the logic cell, Read and Write clocks, Read and Write enables of the embedded RAM blocks, and I/O inputs. The voltage tolerance of this pin is specified by VCCIO.                                                                                                                                                             |  |  |  |  |  |

| CCMIN(H)                   | I         | CCM clock input                                | Input clock for CCM. The voltage tolerance for this pin is specified by VCCIO(H).                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| CCMVCC                     | I         | Power supply pin for CCM                       | CCM input voltage level. Configurable as 1.8 V only.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| CCMGND                     | I         | Ground pin for CCM                             | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| VLP                        | I         | Voltage low power                              | Active low. Therefore, when VLP is 0 V, the device will go into low power mode. Tie VLP to any voltage between 1.8 V and 3.3 V to disable low power mode.                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| VPUMP                      | I         | Charge Pump Disable                            | This pin disables the internal charge pump, which lowers static power consumption. To disable the charge pump, connect VPUMP to 3.3 V. VPUMP must be connected to 3.3 V for data retention to work in VLP mode.  If VCC is 1.5 V, VPUMP must be tied to 3.3 V for VLP mode to be available.                                                                                                                                              |  |  |  |  |  |

| VCC                        | I         | Power supply pin                               | Connect to 1.8 V or 1.5 V supply. When VCC is 1.5 V, it will adversely affect the timing by 40%.                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| VCCIO(H:A)                 | I         | Input voltage tolerance pin                    | This pin provides the flexibility to interface the device with either a 3.3 V, 2.5 V, or 1.8 V device. The letter inside the parenthesis means that the VCCIO is located in the bank with that letter. Every I/O pin in the same bank will be tolerant of the same VCCIO input signals and will drive VCCIO level output signals. Even if certain VCCIO banks are not used, all VCCIO pins must be driven when the device is powered up. |  |  |  |  |  |

| GND                        | I         | Ground pin                                     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

Table 27: Pin Descriptions (Continued)

| Pin   | Direction Function    |                           | Description                                                                                                   |  |  |  |  |  |

|-------|-----------------------|---------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | JTAG Pin Descriptions |                           |                                                                                                               |  |  |  |  |  |

| TDI   | ı                     | Test data in for JTAG     | Hold HIGH during normal operation. Connect to VCCIO(D) if unused.                                             |  |  |  |  |  |

| TRSTB | I                     | Active low reset for JTAG | Hold LOW during normal operation. Connect to GND if unused. During JTAG, a high voltage is based on VCCIO(D). |  |  |  |  |  |

| TMS   | ı                     | Test mode select for JTAG | Hold HIGH during normal operation. Connect to VCCIO(D) if not used for JTAG.                                  |  |  |  |  |  |

| TCK   | ı                     | Test clock for JTAG       | Hold HIGH or LOW during normal operation. Connect to VCCIO(D) or GND if not used for JTAG.                    |  |  |  |  |  |

| TDO   | 0                     | Test data out for JTAG    | Must be left unconnected if not used for JTAG. The output voltage drive is specified by VCCIO(D).             |  |  |  |  |  |

#### Recommended Unused Pin Terminations for PolarPro II Devices

All unused, general purpose I/O pins can be tied to VCCIO, GND, or Hi-Z (high impedance) internally. By default, QuickLogic QuickWorks software ties unused I/Os to GND.

Terminate the rest of the pins at the board level as recommended in Table 28.\_

Table 28: Recommended Unused Pin Terminations

| Signal Name | Recommended Termination                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK <x></x> | Connect to GND or VCCIO(x) if unused.                                                                                                                                                     |

| VLP         | Tie VLP to any voltage between 1.8 V and 3.3 V to disable low power mode.                                                                                                                 |

| CCMVCC      | If a CCM is not used, the corresponding CCMVCC must be tied to 1.8V. When a CCM is not used, the software tools will automatically configure the device to hold the CCM in a reset state. |

| TDI         | Connect to VCCIO(D) if not used for JTAG.                                                                                                                                                 |

| TRSTB       | Connect to GND if not used for JTAG.                                                                                                                                                      |

| TMS         | Connect to VCCIO(D) if not used for JTAG                                                                                                                                                  |

| TCK         | Connect to VCCIO(D) or GND if not used for JTAG.                                                                                                                                          |

| TDO         | Must be left unconnected if not used for JTAG.                                                                                                                                            |

### PolarPro II QL2P150 - 121 (6 mm x 6 mm) TFBGA Pinout Table

Table 29: QL2P150 - 121 (6 mm x 6 mm) TFBGA Pinout Table

| Pin | Function                | Pin | Function | Pin | Function | Pin | Function       |

|-----|-------------------------|-----|----------|-----|----------|-----|----------------|

| A1  | VCC                     | C10 | GPIO(H)  | F8  | VCC      | J6  | GND            |

| A2  | GPIO(G)                 | C11 | GPIO(A)  | F9  | GPIO(A)  | J7  | GPIO(C)        |

| А3  | GPIO(G)                 | D1  | GPIO(F)  | F10 | GPIO(A)  | J8  | GPIO(C)        |

| A4  | GPIO(G)                 | D2  | GPIO(F)  | F11 | GPIO(A)  | J9  | GPIO(B)        |

| A5  | CLK(G)/GPIO(G)          | D3  | GPIO(F)  | G1  | TCK      | J10 | GPIO(B)        |

| A6  | DEDCLK(H)/GPIO(H)       | D4  | VCCIO(G) | G2  | VCCIO(D) | J11 | GPIO(B)        |

| A7  | GPIO(H)                 | D5  | VCC      | G3  | GPIO(D)  | K1  | GND            |

| A8  | CCMIN(H)/CLK(H)/GPIO(H) | D6  | GPIO(F)  | G4  | VCC      | K2  | GPIO(E)        |

| A9  | GPIO(H)                 | D7  | GPIO(A)  | G5  | VCCIO(F) | K3  | GPIO(D)        |

| A10 | GPIO(H)                 | D8  | GPIO(C)  | G6  | GND      | K4  | GPIO(D)        |

| A11 | VCC                     | D9  | GPIO(H)  | G7  | GND      | K5  | TDI            |

| B1  | VLP                     | D10 | GPIO(A)  | G8  | VCC      | K6  | GPIO(D)        |

| B2  | GPIO(G)                 | D11 | GPIO(A)  | G9  | TRSTB    | K7  | GPIO(C)        |

| В3  | GPIO(G)                 | E1  | GPIO(F)  | G10 | GPIO(B)  | K8  | GPIO(C)        |

| B4  | GPIO(G)                 | E2  | GPIO(F)  | G11 | GPIO(B)  | K9  | GPIO(C)        |

| B5  | GPIO(G)                 | E3  | GPIO(F)  | H1  | GPIO(E)  | K10 | GPIO(B)        |

| B6  | TMS                     | E4  | GPIO(F)  | H2  | GPIO(E)  | K11 | GPIO(B)        |

| B7  | GPIO(H)                 | E5  | VCCIO(H) | Н3  | GPIO(E)  | L1  | VCC            |

| B8  | GPIO(H)                 | E6  | GND      | H4  | GPIO(E)  | L2  | GPIO(D)        |

| В9  | GPIO(H)                 | E7  | GND      | Н5  | VCCIO(E) | L3  | GPIO(D)        |

| B10 | CCMGND                  | E8  | VCCIO(A) | H6  | GND      | L4  | TDO            |

| B11 | GND                     | E9  | VCCIO(B) | H7  | VCCIO(D) | L5  | CLK(C)/GPIO(C) |

| C1  | GPIO(F)                 | E10 | GPIO(A)  | H8  | VCCIO(C) | L6  | CLK(D)/GPIO(D) |

| C2  | GPIO(G)                 | E11 | GPIO(A)  | Н9  | VCCIO(D) | L7  | GPIO(C)        |

| C3  | GPIO(G)                 | F1  | GPIO(E)  | H10 | GPIO(B)  | L8  | GPIO(C)        |

| C4  | GPIO(G)                 | F2  | GPIO(F)  | H11 | GPIO(B)  | L9  | VPUMP          |

| C5  | GPIO(G)                 | F3  | GPIO(F)  | J1  | GPIO(E)  | L10 | GND            |

| C6  | GPIO(H)                 | F4  | GND      | J2  | GPIO(E)  | L11 | VCC            |

| C7  | GPIO(H)                 | F5  | GND      | J3  | GPIO(E)  |     |                |

| C8  | GPIO(A)                 | F6  | GND      | J4  | GPIO(D)  |     |                |

| C9  | CCMVCC                  | F7  | GND      | J5  | GPIO(D)  |     |                |

### PolarPro II QL2P150 - 121 (5 mm x 5 mm) TFBGA Pinout Table

Table 30: QL2P150 - 121 (5 mm x 5 mm) TFBGA Pinout Table

| Pin       | Function                | Pin | Function | Pin | Function | Pin | Function       |

|-----------|-------------------------|-----|----------|-----|----------|-----|----------------|

| A1        | GPIO(G)                 | C10 | GPIO(A)  | F8  | VCCIO(A) | J6  | GPIO(C)        |

| A2        | GPIO(G)                 | C11 | GPIO(A)  | F9  | TRSTB    | J7  | GPIO(C)        |

| А3        | GPIO(G)                 | D1  | GPIO(F)  | F10 | GPIO(A)  | J8  | GPIO(C)        |

| A4        | GPIO(G)                 | D2  | GPIO(F)  | F11 | GPIO(A)  | J9  | GPIO(C)        |

| A5        | CLK(G)/GPIO(G)          | D3  | GPIO(F)  | G1  | GPIO(E)  | J10 | GPIO(B)        |

| A6        | DEDCLK(H)/GPIO(H)       | D4  | VCCIO(F) | G2  | GPIO(E)  | J11 | GPIO(B)        |

| A7        | GPIO(H)                 | D5  | VCC      | G3  | GPIO(E)  | K1  | GPIO(E)        |

| A8        | CCMIN(H)/CLK(H)/GPIO(H) | D6  | VCCIO(G) | G4  | TDO      | K2  | GPIO(D)        |

| A9        | GPIO(H)                 | D7  | TMS      | G5  | GND      | K3  | GPIO(D)        |

| A10       | GPIO(H)                 | D8  | VCCIO(H) | G6  | GND      | K4  | GPIO(D)        |

| A11       | VCC                     | D9  | GPIO(A)  | G7  | VCCIO(D) | K5  | GPIO(D)        |

| B1        | VLP/VCCIO(D)            | D10 | GPIO(A)  | G8  | VCC      | K6  | GPIO(C)        |

| B2        | GPIO(G)                 | D11 | GND      | G9  | GPIO(B)  | K7  | GPIO(C)        |

| В3        | GPIO(G)                 | E1  | GPIO(F)  | G10 | GPIO(B)  | K8  | GPIO(C)        |

| B4        | GPIO(G)                 | E2  | GPIO(F)  | G11 | GPIO(B)  | K9  | GPIO(C)        |

| B5        | GPIO(G)                 | E3  | GPIO(F)  | H1  | GPIO(E)  | K10 | GPIO(B)        |

| В6        | GPIO(H)                 | E4  | TCK      | H2  | GPIO(E)  | K11 | GPIO(B)        |

| B7        | GPIO(H)                 | E5  | VCCIO(D) | Н3  | GPIO(E)  | L1  | GND            |

| B8        | GPIO(H)                 | E6  | GND      | H4  | VCCIO(D) | L2  | GPIO(D)        |

| В9        | GPIO(H)                 | E7  | GND      | H5  | VCC      | L3  | GPIO(D)        |

| B10       | CCMGND                  | E8  | VCC      | Н6  | VCCIO(C) | L4  | GPIO(D)        |

| B11       | CCMVCC                  | E9  | GPIO(A)  | H7  | TDI      | L5  | CLK(D)/GPIO(D) |

| C1        | GPIO(F)                 | E10 | GPIO(A)  | H8  | VCCIO(B) | L6  | CLK(C)/GPIO(C) |

| C2        | GPIO(F)                 | E11 | GPIO(A)  | Н9  | GPIO(B)  | L7  | GND            |

| C3        | GPIO(G)                 | F1  | GND      | H10 | GPIO(B)  | L8  | GPIO(C)        |

| C4        | GPIO(G)                 | F2  | GPIO(F)  | H11 | GPIO(B)  | L9  | GPIO(C)        |

| C5        | GPIO(G)                 | F3  | GPIO(F)  | J1  | GPIO(E)  | L10 | VPUMP/VCCIO(D) |

| C6        | GPIO(H)                 | F4  | VCCIO(E) | J2  | GPIO(E)  | L11 | VCC            |

| <b>C7</b> | GPIO(H)                 | F5  | GND      | J3  | GPIO(E)  |     |                |

| C8        | GPIO(H)                 | F6  | GND      | J4  | GPIO(D)  |     |                |

| C9        | GPIO(A)                 | F7  | GND      | J5  | GPIO(D)  |     |                |

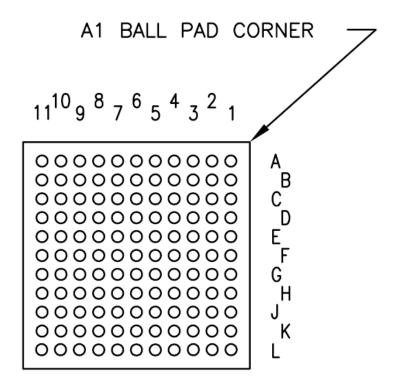

#### PolarPro II QL2P150 - 121 TFBGA Pinout Diagram

#### Top

QuickLogic°

PolarPro II

QL2P150-PUN121C

#### **Bottom**

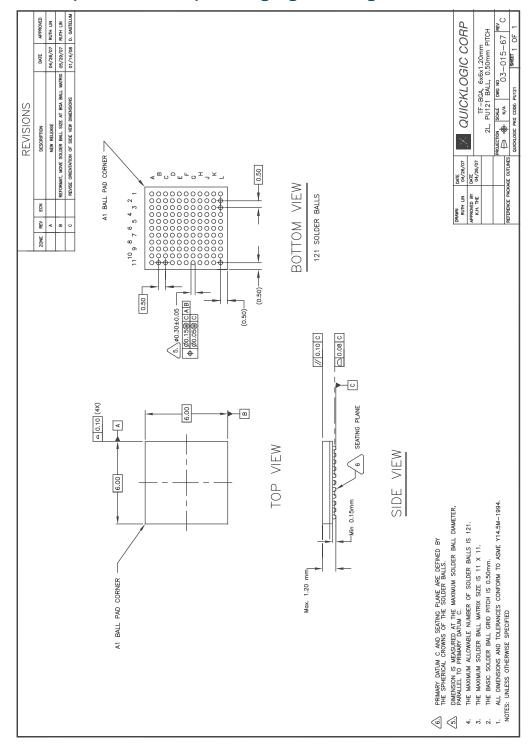

# **Package Mechanical Drawing**

## 121 TFBGA (6 mm x 6 mm) Packaging Drawing

# 121 TFBGA (5 mm x 5 mm) Packaging Drawing

**TBD**

# **Packaging Information**

The PolarPro II QL2P150 device packaging information is presented in **Table 31**.

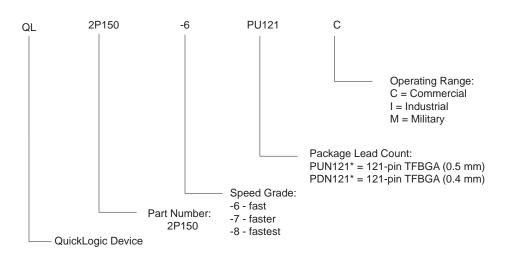

Table 31: QL2P150 Packaging Options

|                                  | Device                                        |    |         |  |  |

|----------------------------------|-----------------------------------------------|----|---------|--|--|

| Device Information               | QL2P150                                       |    |         |  |  |

|                                  | Pin                                           | Pb | Pb-Free |  |  |

| Dockers Definitions              | 121 TFBGA<br>(6 mm x 6 mm)<br>Pitch - 0.50 mm |    | x       |  |  |

| Package Definitions <sup>a</sup> | 121 TFBGA<br>(5 mm x 5 mm)<br>Pitch - 0.40 mm |    | х       |  |  |

a. TFBGA = Thin Profile Fine Pitch Ball Grid Array

## **Ordering Information**

<sup>\*</sup> Lead-free packaging is denoted by the character 'N' preceding the number of pins.

#### **Contact Information**

Phone: (408) 990-4000 (US)

(905) 940-4149 (Canada) +(44) 1932-57-9011 (Europe) +(852) 2297-2297 (Asia)

E-mail: <a href="mailto:info@quicklogic.com">info@quicklogic.com</a>

Sales: <a href="mailto:www.quicklogic.com/sales">www.quicklogic.com/sales</a>

Support: <a href="mailto:www.quicklogic.com/support">www.quicklogic.com/support</a>

Internet: www.quicklogic.com

## **Revision History**

| Revision | Date       | Originator and Comments                         |

|----------|------------|-------------------------------------------------|

| А        | March 2008 | Jason Lew and Kathleen Murchek - First release. |

#### **Notice of Disclaimer**

QuickLogic is providing this design, product or intellectual property "as is." By providing the design, product or intellectual property as one possible implementation of your desired system-level feature, application, or standard, QuickLogic makes no representation that this implementation is free from any claims of infringement and any implied warranties of merchantability or fitness for a particular purpose. You are responsible for obtaining any rights you may require for your system implementation. QuickLogic shall not be liable for any damages arising out of or in connection with the use of the design, product or intellectual property including liability for lost profit, business interruption, or any other damages whatsoever. QuickLogic products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use QuickLogic products in these types of equipment or applications.

QuickLogic does not assume any liability for errors which may appear in this document. However, QuickLogic attempts to notify customers of such errors. QuickLogic retains the right to make changes to either the documentation, specification, or product without notice. Verify with QuickLogic that you have the latest specifications before finalizing a product design.

# **Copyright and Trademark Information**

Copyright © 2008 QuickLogic Corporation. All Rights Reserved.

The information contained in this document is protected by copyright. All rights are reserved by QuickLogic Corporation. QuickLogic Corporation reserves the right to modify this document without any obligation to notify any person or entity of such revision. Copying, duplicating, selling, or otherwise distributing any part of this product without the prior written consent of an authorized representative of QuickLogic is prohibited.

QuickLogic and the QuickLogic logo, and QuickWorks are registered trademarks of QuickLogic Corporation; PolarPro and SpDE are trademarks of QuickLogic Corporation.