# Am29LV400T/Am29LV400B Data Sheet

#### INTRODUCTION

This amendment supersedes information in the Am29LV400 data sheet. PID 20514B.

This amendment will be available online via AMD's World Wide Web site (http://www.amd.com), in addition to the literature ordering hotline. All changes contained in this document will be included in the next release of the Flash Products Data Book/Handbook.

#### **DOCUMENT ORGANIZATION**

Table 1 lists the data book pages affected by this document and contains a description of changes for each page.

The remainder of this document contains the change pages. In the footer of the change pages are two page numbers. The page number in parenthesis lists the corresponding page in the data book.

Table 1. Am29LV400 Data Sheet Changes

| Amend-<br>ment<br>Page | Data<br>Sheet<br>Page | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                      | 1                     | Distinctive Characteristics: Rearranged bullets. Renamed "2.7 to 3.6 volt, extended voltage range" to "Single power supply operation." Under "Single power supply operation" and "High performance" bullets, defined standard and extended voltage ranges and added 90 ns speed option. Combined "Advanced power management" and "Low current consumption" bullets into new "Ultra low power consumption" bullet. Under that bullet, revised the typical standby and automatic sleep mode current specifications from 1 μA to 200 nA; revised read current specification from 10 mA to 2 mA/MHz. Combined "Sector protection" and "Flexible sector architecture" bullets. Under flexible sector architecture bullet, added temporary sector unprotect feature description. Combined Embedded Program and Embedded Erase bullets under new "Embedded Algorithms" bullet; removed TM designations. Clarified descriptions of sector protection, erase suspend/resume, hardware reset pin, ready/busy pin, and data polling and toggle bits.  General Description:  Added text on new speed option and voltage range to the second paragraph. |

| 4                      | 3                     | Product Selector Guide: Added -90R voltage range and speed option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4                      | 5                     | Pin Configuration: Added new voltage range to $V_{\rm CC}$ specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

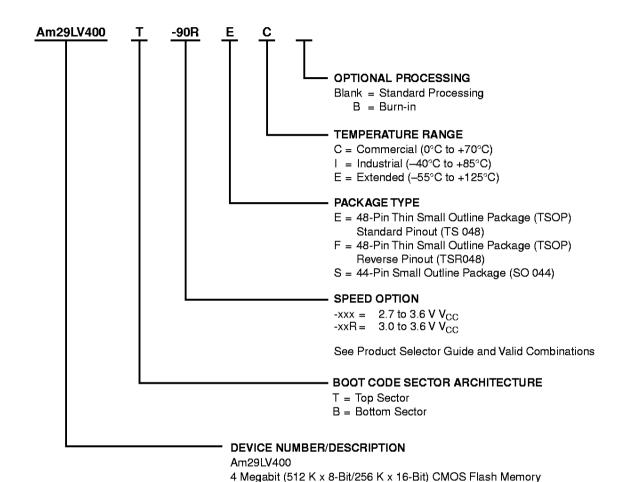

| 5                      | 6                     | Ordering Information, Standard Products: The -90R speed option is now listed in the example. Revised "Speed Option" section to indicate both voltage ranges.  Valid Combinations: Added -90R speed option and voltage range.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6                      | 8                     | Automatic Sleep Mode: Revised addresses stable time to 200 ns and current draw to 200 nA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Publication# 20514 Rev: B Amendment/1 Issue Date: May 1997

Table 1. Am29LV400 Data Sheet Changes (Continued)

| Amend-<br>ment | Data<br>Sheet |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page           | Page          | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6              | 13            | Table 6, Command Definitions: Grouped address designators PA, PD, RA, RD, and SA under the legend heading. Modified SA definition to accommodate the sector protect verify command. Since unlock addresses only require address bits A0–A10 to be valid, the number of hexadecimal digits in the unlock addresses were changed from four to three. The remaining upper address bits are don't care. Removed "H" designation from hexadecimal values in table and replaced with new Note 1. Revised Notes 5 and 6 to indicate when commands are valid; are now Notes 4 and 5. Expanded autoselect section to show each function separately: manufacturer ID, device ID, and sector protect verify. Added Note 3 to explain sector protect codes. In Note 8, changed A13 to A11, added "unless otherwise noted"; is now Note 6.                                                              |

| 7              | 19            | RESET: Hardware Reset Pin: Fourth paragraph: Revised standby mode specification to 200 nA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

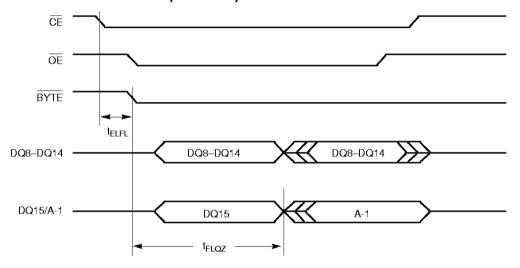

| 7              | 20            | Figure 5, Timing Diagram for Byte Mode Configuration: Corrected labels on DQ8-DQ14 waveform, were missing "4".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7              | 27            | Operating Ranges:  V <sub>CC</sub> Supply Voltages: Added 3.0 to 3.6 V voltage range and -90R speed option.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8              | 28            | DC Characteristics: CMOS Compatible: Changed $I_{\rm CC1}$ from 30 mA maximum at 6 MHz to 16 mA maximum at 5 MHz and 4 mA maximum at 1 MHz. Changed $I_{\rm CC2}$ from 35 mA to 30 mA maxImum. In the $V_{\rm OL}$ specification, changed the $I_{\rm OL}$ test condition from 5.8 mA to 4.0 mA. In Note 1, changed 6 MHz to 5 MHz. In Note 3, changed address stable time from 300 ns to 200 ns; changed typical automatic sleep mode current from 1 $\mu$ A to 200 nA.                                                                                                                                                                                                                                                                                                                                                                                                                   |

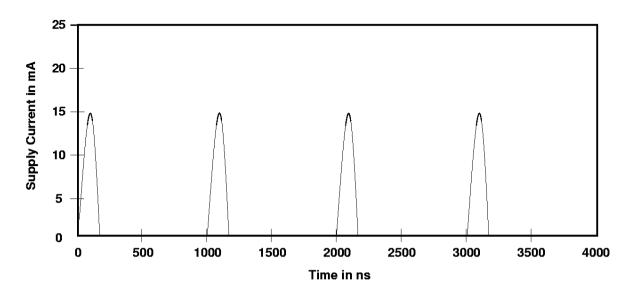

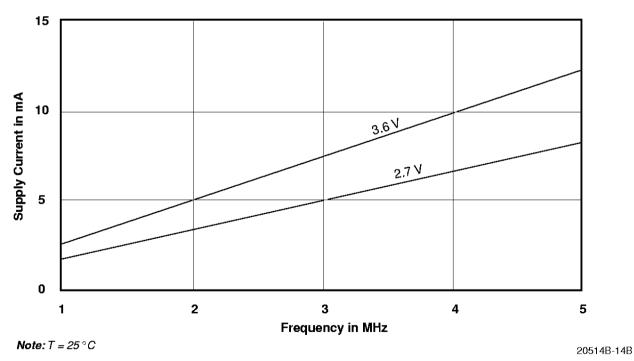

| 9              | 28 <b>A</b>   | Figure 10A, I <sub>CC</sub> Current vs. Time, and Figure 10B, I <sub>CC</sub> vs. Frequency: Figure 8A illustrates current draw during the Automatic Sleep Mode after the addresses are stable. Figure 8B shows how frequency affects the current draw curves for both voltage ranges.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

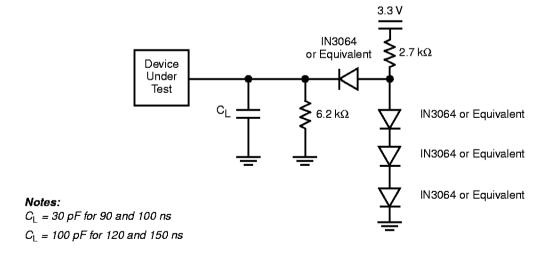

| 10             | 29            | AC Characteristics: Read Only Operations Characteristics: Added -90R column.  Test Conditions, Figure 11: Added 90 ns speed to C <sub>L</sub> note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11             | 30            | AC Characteristics: Write/Erase/Program Operations: Added the -90R column.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

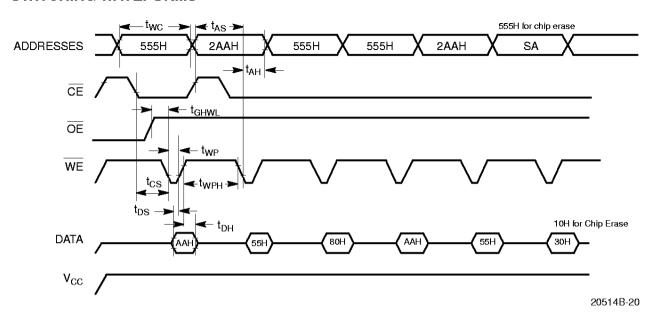

| 12             | 33            | Figure 16, AC Waveforms for Chip/Sector Erase Operations: Changed 5555H to 555H in addresses waveform to match command definitions (Table 6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

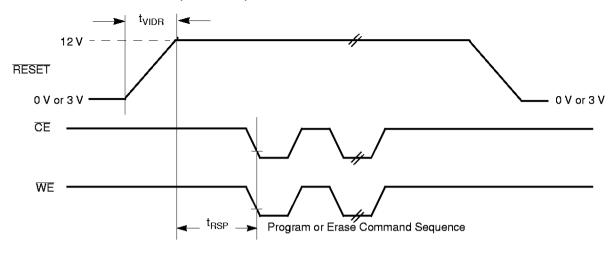

| 13             | 36            | Figure 23, Temporary Sector Unprotect Diagram: Corrected callouts on RESET waveform to "0 V or 3 V".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 13             | 37            | AC Characteristics:  Alternate CE Controlled Writes: Added the -90R column. Changed t <sub>AH</sub> from 45 to 50 ns for -100, from 50 to 65 ns for -150. Changed t <sub>DS</sub> from 50 to 65 ns for -150. Changed t <sub>CP</sub> from 50 to 65 ns for -150.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

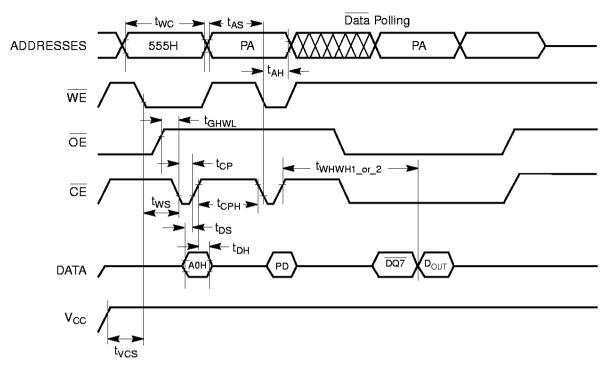

| 14             | 38            | Figure 24, Alternate CE Controlled Write Operation Timings: Changed 5555H to 555H in addresses waveform to match command definitions (Table 6).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15             | 39            | Erase and Programming Performance:  Added typical chip erase specification. Renamed erase/program cycles specification to erase/program endurance. Corrected to indicate 1,000,000 cycle endurance is typical, not maximum; also that 100,000 cycle endurance is minimum, not typical. Revised Note 1 to include write endurance; moved Note 1 references in table to table head. Consolidated and moved Note 1 and Note 3 references in table to table head. Combined Note 2 and Note 5 into new Note 1, which applies to the entire table; revised to indicate that DQ5=1 after any maximum time. Comments for program and erase now straddle parameter rows. Corrected comment for byte programming (comment for "byte programming time" was incorrectly listed). Separated the two sentences in Note 4 into new Notes 4 and 5; added corresponding note references to comment section. |

# Am29LV400T/Am29LV400B

# 4 Megabit (524,288 x 8-Bit/262,144 x 16-Bit) CMOS 3.0 Volt-only Sector Architecture Flash Memory

#### DISTINCTIVE CHARACTERISTICS

#### ■ Single power supply operation

- Extended voltage range: 2.7 to 3.6 volt read and write operations for battery-powered applications

- Standard voltage range: 3.0 to 3.6 volt read and write operations and for compatibility with high performance 3.3 volt microprocessors

#### ■ High performance

- Extended voltage range: access times as fast as 100 ns

- Standard voltage range: access times as fast as 90 ns

#### ■ Ultra low power consumption

- Automatic Sleep Mode: 200 nA typical

- Standby mode: 200 nA typical

- Read mode: 2 mA/MHz typical

- Program/erase mode: 20 mA typical

#### **■** Flexible sector architecture

- One 16 Kbyte, two 8 Kbyte, one 32 Kbyte, and seven 64 Kbyte sectors (byte mode)

- One 8 Kword, two 4 Kword, one 16 Kword, and seven 32 Kword sectors (word mode)

- Supports control code and data storage on a single device

- Sector Protection features:

- A hardware method of locking a sector to prevent any program or erase operations within that sector

- Temporary Sector Unprotect feature allows code changes in previously locked sectors

# Top or bottom boot block configurations available

#### ■ Embedded Algorithms

- Embedded Erase algorithms automatically preprogram and erase the entire chip or any combination of designated sectors

- Embedded Program algorithms automatically write and verify bytes or words at specified addresses

#### Minimum 100,000 write cycle guarantee per sector

#### Package option

- 48-pin TSOP

- 44-pin SO

#### ■ Compatibility with JEDEC standards

- Pinout and software compatible with singlepower supply Flash

- Superior inadvertent write protection

#### ■ Data Polling and toggle bits

Provides a software method of detecting program or erase operation completion

#### ■ Ready/Busy pin

Provides a hardware method of detecting program or erase cycle completion

#### ■ Erase suspend/resume feature

Provides the ability to suspend the erase operation in any sector, read data from or program data to any other sector, then return to the original sector and complete the initial erase operation

#### ■ Hardware reset pin (RESET)

Hardware method to reset the device to the read mode

#### **GENERAL DESCRIPTION (PARAGRAPH 2)**

The Am29LV400 provides two levels of performance. The first level offers access times as fast as 100 ns with a  $V_{\rm CC}$  range as low as 2.7 volts, which is optimal for battery powered applications. The second level offers a 90 ns access time, optimizing performance in

systems where the power supply is in the regulated range of 3.0 to 3.6 volts. To eliminate bus contention, the device has separate chip enable  $(\overline{CE})$ , write enable  $(\overline{WE})$ , and output enable  $(\overline{OE})$  controls.

#### **PRODUCT SELECTOR GUIDE**

| Family Part Number                                | Am29LV400T/Am29LV400B |      |      |      |  |  |

|---------------------------------------------------|-----------------------|------|------|------|--|--|

| Ordering Part Number: V <sub>CC</sub> = 3.0-3.6 V | -90R                  |      |      |      |  |  |

| $V_{CC} = 2.7 - 3.6 \text{ V}$                    |                       | -100 | -120 | -150 |  |  |

| Max access time (ns)                              | 90                    | 100  | 120  | 150  |  |  |

| CE access time (ns)                               | 90                    | 100  | 120  | 150  |  |  |

| OE access time (ns)                               | 40                    | 40   | 50   | 55   |  |  |

#### **PIN CONFIGURATION**

A0-A17 = 18 addresses

DQ0-DQ14 = 15 data inputs/outputs

DQ15/A-1 = DQ15 data input/output,

A-1 address mux

BYTE = Selects 8-bit or 16-bit mode

CE= Chip enableOE= Output enableWE= Write enable

RESET = Hardware reset pin, active low

$RY/\overline{BY}$  = Ready/Busy output

$V_{CC}$  = Standard voltage range

(3.0 V to 3.6 V) for -90R

Extended voltage range

(2.7 to 3.6 V) for -100, -120, -150

$V_{SS}$  = Device ground

NC = Pin not connected internally

#### ORDERING INFORMATION

#### **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

3.0 Volt-only Program and Erase

| Valid Combinations                                               |                                                         |  |  |  |  |  |  |

|------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|--|

| Am29LV400T-90R,<br>Am29LV400B-90R<br>V <sub>CC</sub> = 3.0–3.6 V | EC, EI, FC, FI, SC, SI                                  |  |  |  |  |  |  |

| Am29LV400T-100,<br>Am29LV400B-100                                |                                                         |  |  |  |  |  |  |

| Am29LV400T-120,<br>Am29LV400B-120                                | SC, SI, SE, SEB,<br>EC, EI, EE, EEB,<br>FC, FI, FE, FEB |  |  |  |  |  |  |

| Am29LV400T-150,<br>Am29LV400B-150                                | ,,,                                                     |  |  |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

### **USER BUS OPERATIONS (PAGE 8)**

#### **Automatic Sleep Mode**

Advanced power management features such as the automatic sleep mode minimize Flash device energy consumption. This is extremely important in battery-powered applications. The Am29LV400 automatically enables the low-power, automatic sleep mode when addresses remain stable for 200 ns. Automatic sleep mode is independent of the CE, WE, and OE control signals. Typical sleep mode current draw is 200 nA (for CMOS-compatible operation). Standard address access timings provide new data when addresses are changed. While in sleep mode, output data is latched and always available to the system.

#### **TABLE 6, COMMAND DEFINITIONS (PAGE 13)**

Table 6. Am29LV400 Command Definitions

| Command<br>Sequence<br>Read/Reset   |       | Bus<br>Write<br>Cycles |       | t Bus<br>Cycle | Read | nd Bus<br>/Write<br>cle |      | us Write<br>cle | Fourti<br>Read/<br>Cy | Write | Write Fifth Bus<br>de Write Cycle |      | Sixth Bus<br>Write Cycle |      |

|-------------------------------------|-------|------------------------|-------|----------------|------|-------------------------|------|-----------------|-----------------------|-------|-----------------------------------|------|--------------------------|------|

| (Note 2)                            |       | Řeq'd                  | Addr  | Data           | Addr | Data                    | Addr | Data            | Addr                  | Data  | Addr                              | Data | Addr                     | Data |

| Reset/Read Word                     | Word  | . 1                    | XXX   | XXF0           | BA   | RD                      |      |                 |                       |       |                                   |      |                          |      |

|                                     | Byte  | ·                      | ,,,,, | F0             |      |                         |      |                 |                       |       |                                   |      |                          |      |

| Autoselect                          | Word  | 3                      | 555   | XXAA           | 2AA  | XX55                    | 555  | XX90            | X00                   | XX01  |                                   |      |                          |      |

| Manufacturer ID                     | Byte  | 3                      | 2AA   | AA             | 555  | 55                      | 2AA  | 90              | X00                   | 01    |                                   |      |                          |      |

| Autoselect                          | Word  |                        | 555   | XXAA           | 2AA  | XX55                    | 555  | XX90            | X01                   | 22DA  |                                   |      |                          |      |

| Device ID<br>(Top Boot Block)       | Byte  | 3                      | 2AA   | AA             | 555  | 55                      | 2AA  | 90              | X01                   | DA    |                                   |      |                          |      |

| Autoselect                          | Word  |                        | 555   | XXAA           | 2AA  | XX55                    | 555  | XX90            | X01                   | 225B  |                                   |      |                          |      |

| Device ID<br>(Bottom Boot<br>Block) | Byte  | 3                      | 2AA   | AA             | 555  | 55                      | 2AA  | 90              | X01                   | 5B    |                                   |      |                          |      |

|                                     | Word  |                        | 555   | XXAA           | 2AA  | XX55                    | 555  | XX90            |                       | XX00  |                                   |      |                          |      |

| Autoselect                          | vvora |                        | 200   | XXAA           | ZAA  | VV22                    | 555  | XX90            | SA                    | XX01  |                                   |      |                          |      |

| Sector Protect<br>Verify (Note 3)   | Б.    | 3                      | 044   |                | FFF  |                         | 044  | 00              | X02                   | 00    |                                   |      |                          |      |

| Joiny (Holo o)                      | Byte  |                        | 2AA   | AA             | 555  | 55                      | 2AA  | 90              |                       | 01    |                                   |      |                          |      |

| D                                   | Word  | 4                      | 555   | XXAA           | 2AA  | XX55                    | 555  | XXA0            |                       | DD.   |                                   |      |                          |      |

| Program                             | Byte  | 4                      | 2AA   | AA             | 555  | 55                      | 2AA  | A0              | PA                    | PD    |                                   |      |                          |      |

| 01: E                               | Word  | _                      | 555   | XXAA           | 2AA  | XX55                    | 555  | XX80            | 555                   | XXAA  | 2AA                               | XX55 | 555                      | XX10 |

| Chip Erase                          | Byte  | 6                      | 2AA   | AA             | 555  | 55                      | 2AA  | 80              | 2AA                   | AA    | 555                               | 55   | 2AA                      | 10   |

|                                     | Word  | _                      | 555   | XXAA           | 2AA  | XX55                    | 555  | XX80            | 555                   | XXAA  | 2AA                               | XX55 |                          | XX30 |

| Sector Erase                        | Byte  | 6                      | 2AA   | AA             | 555  | 55                      | 2AA  | 80              | 2AA                   | AA    | 555                               | 55   | SA                       | 30   |

| Erase Suspend                       | Word  | _                      |       | XXB0           |      |                         |      |                 |                       |       |                                   |      |                          |      |

| (Note 4)                            | Byte  | 1                      | XXX   | B0             |      |                         |      |                 |                       |       |                                   |      |                          |      |

| Erase Resume                        | Word  |                        |       | XX30           |      |                         |      |                 |                       |       |                                   |      |                          |      |

| (Note 5)                            | Byte  | 1                      | XXX   | 30             |      |                         |      |                 |                       |       |                                   |      |                          |      |

#### Legend:

RA = Address of the memory location to be read.

RD = Data read from location RA during read operation.

PA = Address of the memory location to be programmed. Addresses are latched on the falling edge of the WE or CE pulse.

PD = Data to be programmed at location PA. Data is latched on the rising edge of WE or CE pulse.

SA = Address of the sector to be erased or verified. Address bits A17-A12 uniquely select any sector.

- All values are in hexadecimal.

- 2. See Tables 1 and 2 for description of bus operations.

- 3. The data is 00h for an unprotected sector and 01h for a protected sector. The complete bus address is composed of the sector address on A17-A12 and 02h on A7-A0.

- 4. Read and program functions in non-erasing sectors are allowed in the Erase Suspend mode. The Erase Suspend command is valid only during a sector erase operation.

- 5. The Erase Resume command is valid only during the Erase Suspend mode.

- 6. Unless otherwise noted, address bits A17-A11 = X = don't care.

#### **WRITE OPERATION STATUS (PAGE 19)**

#### **RESET: Hardware Reset Pin**

The RESET pin is an active low signal. A logic '0' on this pin will force the device out of any mode that is currently executing back to the reset state. This allows a system reset to take effect immediately without having to wait for the device to finish a long execution cycle. To avoid a potential bus contention during a system reset, the device is isolated from the data I/O bus by tri-stating the data output pins for the duration of the RESET pulse.

If RESET is asserted during a program or erase operation. the RY/BY pin will remain low until the reset operation is internally complete. This will require between 1 µs and 20 µs. Hence the RY/BY pin can be used to signal that the reset operation is complete. Otherwise, allow for the maximum reset time of 20 µs. If RESET is asserted when a program

or erase operation is not executing (RY/BY pin is high), the reset operation will be complete within 500 ns.

Asserting RESET during a program or erase operation leaves erroneous data stored in the address locations being operated on at the time of device reset. These locations need updating after the reset operation is complete. See Figure 3 for timing specifications.

The device enters I<sub>CC4</sub> standby mode (200 nA) when V<sub>SS</sub>  $\pm$  0.3 V is applied to the RESET pin. The device can enter this mode at any time, regardless of the logical condition of the CE pin. Furthermore, entering I<sub>CC4</sub> during a program or erase operation leaves erroneous data in the address locations being operated on at the time of the RESET pulse. These locations need updating after the device resumes standard operations. After the RESET pin goes high, a minimum latency period of 50 ns must occur before a valid read can take place.

#### WORD/BYTE CONFIGURATION (PAGE 20)

Figure 5. Timing Diagram for Byte Mode Configuration

#### **OPERATING RANGES (PAGE 27)**

| Cam   | mercial | 10 | Dovice |   |

|-------|---------|----|--------|---|

| COIII | merciai | w  | Device | 5 |

Ambient Temperature (T<sub>A</sub>) . . . . . . . . 0°C to +70°C

Industrial (I) Devices

Ambient Temperature (T<sub>A</sub>) . . . . . . . . -40°C to +85°C

Extended (E) Devices

Ambient Temperature (T<sub>A</sub>) . . . . . . . -55°C to +125°C

V<sub>CC</sub> Supply Voltages

$V_{CC}$  for Am29LV400T/B-90R . . . . . . . +3.0 V to 3.6 V

V<sub>CC</sub> for Am29LV400T/B-100,

Operating ranges define those limits between which the functionality of the device is guaranteed.

20514B-9

#### **DC CHARACTERISTICS**

#### **CMOS** Compatible

| Parameter<br>Symbol | Parameter Description                                    | Test Conditi                                                              | ons                   | Min                   | Max                   | Unit       |

|---------------------|----------------------------------------------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|-----------------------|------------|

| l <sub>LI</sub>     | Input Load Current                                       | $V_{IN} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC max}$                  |                       |                       | ±1.0                  | μΑ         |

| l <sub>LIT</sub>    | A9 Input Load Current                                    | V <sub>CC</sub> = V <sub>CC max</sub> ; A9 =                              | 13.0 V                |                       | 35                    | μА         |

| lLO                 | Output Leakage Current                                   | $V_{OUT} = V_{SS}$ to $V_{CC}$ ,<br>$V_{CC} = V_{CC max}$                 |                       |                       | ±1.0                  | μΑ         |

|                     |                                                          | CE = V <sub>IL</sub> , OE = V <sub>IH</sub> ,                             | 5 MHz                 |                       | 16                    |            |

|                     | V <sub>CC</sub> Active Current (Note 1)                  | Byte Mode                                                                 | 1 MHz                 |                       | 4                     |            |

| l <sub>CC1</sub>    |                                                          | CE = V <sub>IL</sub> , OE = V <sub>IH</sub> ,                             | 5 MHz                 |                       | 16                    | m <b>A</b> |

|                     |                                                          | Word Mode 1 MHz                                                           |                       |                       | 4                     |            |

| I <sub>CC2</sub>    | V <sub>CC</sub> Active Current (Notes 2 and 4)           | CE = V <sub>IL</sub> , OE = V <sub>IH</sub>                               |                       |                       | 30                    | mA         |

| I <sub>CC3</sub>    | V <sub>CC</sub> Standby Current                          | V <sub>CC</sub> = V <sub>CC max</sub> ;<br>CE, RESET = V <sub>CC</sub> ±0 | ).3 V                 |                       | 5                     | μΑ         |

| I <sub>CC4</sub>    | V <sub>CC</sub> Reset Current                            | $V_{CC} = V_{CC \text{ max}};$ RESET = $V_{SS} \pm 0.3 \text{ N}$         | /                     |                       | 5                     | μА         |

| I <sub>CC5</sub>    | Automatic Sleep Mode (Note 3)                            | $V_{IH} = V_{CC} \pm 0.3 V;$<br>$V_{IL} = V_{SS} \pm 0.3 V$               |                       |                       | 5                     | μА         |

| V <sub>IL</sub>     | Input Low Voltage                                        |                                                                           |                       | -0.5                  | 0.8                   | ٧          |

| V <sub>IH</sub>     | Input High Voltage                                       |                                                                           |                       | 0.7 x V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | ٧          |

| V <sub>ID</sub>     | Voltage for Autoselect and Temporary<br>Sector Unprotect | V <sub>CC</sub> = 3.3 V                                                   |                       | 11.5                  | 12.5                  | ٧          |

| V <sub>OL</sub>     | Output Low Voltage                                       | $I_{OL}$ = 4.0 mA, $V_{CC}$ = $V_{CC min}$                                |                       |                       | 0.45                  | ٧          |

| V <sub>OH1</sub>    |                                                          | $I_{OH}$ = -2.0 mA, $V_{CC}$ = $V_{CC min}$                               |                       | 0.85 V <sub>CC</sub>  |                       | ٧          |

| V <sub>OH2</sub>    | Output High Voltage                                      | $I_{OH} = -100  \mu A,  V_{CC} = -100  \mu A$                             | = V <sub>CC min</sub> | V <sub>CC</sub> -0.4  |                       |            |

| V <sub>LKO</sub>    | Low V <sub>CC</sub> Lock-Out Voltage (Note 4)            |                                                                           |                       | 2.3                   | 2.5                   | ٧          |

#### Notes:

- The I<sub>CC</sub> current listed includes both the DC operating current and the frequency dependent component (at 5 MHz). The frequency component typically is less than 2 mA/MHz, with OE at V<sub>IH</sub>.

- 2.  $I_{CC}$  active while Embedded Erase or Embedded Program is in progress.

- 3. Automatic sleep mode enables the low power mode when addresses remain stable for 200 ns. Typical sleep mode current is 200 nA.

- 4. Not 100% tested.

- 5. For Am29LV400-xxx,  $V_{CC}$  = 2.7 to 3.6 V. For Am29LV400-xxR,  $V_{CC}$  = 3.0 V to 3.6 V.

# **DC CHARACTERISTICS (CONTINUED)**

Note: Addresses are switching at 1 MHz

20514B-14A

Figure 10A. I<sub>CC</sub> Current vs. Time

Figure 10B. I<sub>CC</sub> vs. Frequency

#### **AC CHARACTERISTICS**

## **Read-Only Operations Characteristics**

| Parameter Symbols |                    |                                                                                                                     |                                                    |      | Spe  | e 1) |      |      |      |

|-------------------|--------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|------|------|------|------|------|

| JEDEC             | Standard           | Description                                                                                                         | Test Se                                            | etup | -90R | -100 | -120 | -150 | Unit |

| t <sub>AVAV</sub> | t <sub>RC</sub>    | Read Cycle Time (Note 3)                                                                                            |                                                    | Min  | 90   | 100  | 120  | 150  | ns   |

| t <sub>AVQV</sub> | t <sub>ACC</sub>   | Address to Output Delay                                                                                             | $\frac{\overline{CE}}{\overline{OE}} = V_{IL}$ Max |      | 90   | 100  | 120  | 150  | ns   |

| t <sub>ELQV</sub> | t <sub>CE</sub>    | Chip Enable to Output Delay                                                                                         | e to Output Delay $\overline{OE} = V_{IL}$ Max     |      | 90   | 100  | 120  | 150  | ns   |

| t <sub>GLQV</sub> | t <sub>OE</sub>    | Output Enable to Output Delay                                                                                       |                                                    | Max  | 40   | 40   | 50   | 55   | ns   |

| t <sub>EHQZ</sub> | t <sub>DF</sub>    | Chip Enable to Output High Z (Notes 2, 3)                                                                           |                                                    | Max  | 30   | 30   | 30   | 40   | ns   |

| t <sub>GHQZ</sub> | t <sub>DF</sub>    | Output Enable to Output High Z (Notes 2, 3)                                                                         |                                                    | Max  | 30   | 30   | 30   | 40   | ns   |

| t <sub>AXQX</sub> | t <sub>OH</sub>    | Output Hold Time From Addresses, $\overline{\text{CE}}$ or $\overline{\text{OE}}$ , Whichever Occurs First (Note 3) |                                                    | Min  | 0    | 0    | 0    | 0    | ns   |

|                   | t <sub>Ready</sub> | RESET Pin Low to Read Mode (Note 3)                                                                                 |                                                    | Max  | 20   | 20   | 20   | 20   | μs   |

#### Notes:

1. Test Conditions

Input Rise and Fall Times: 5 ns Input Pulse Levels: 0.0 V to 3.0 V Timing Measurement Reference Level:

Input: 1.5 V Output: 1.5 V

- 2. Output Driver Disable Time

- 3. Not 100% tested.

20514B-15

Figure 11. Test Conditions

#### **AC CHARACTERISTICS**

# Write (Erase/Program) Operations

| Paramet            | er Symbols                           |                                      |                                                     |        |     |      |      |      |      |      |

|--------------------|--------------------------------------|--------------------------------------|-----------------------------------------------------|--------|-----|------|------|------|------|------|

| JEDEC              | Standard                             | Description                          |                                                     |        |     | -90R | -100 | -120 | -150 | Unit |

| t <sub>AVAV</sub>  | t <sub>WC</sub>                      | Write Cycle Time                     | (Note 2)                                            |        | Min | 90   | 100  | 120  | 150  | ns   |

| t <sub>AVWL</sub>  | t <sub>AS</sub>                      | Address Setup T                      | ime                                                 |        | Min | 0    | 0    | 0    | 0    | ns   |

| t <sub>WLAX</sub>  | t <sub>AH</sub>                      | Address Hold Tir                     | ne                                                  |        | Min | 50   | 50   | 50   | 65   | ns   |

| t <sub>DVWH</sub>  | t <sub>DS</sub>                      | Data Setup Time                      | Data Setup Time                                     |        |     | 50   | 50   | 50   | 65   | ns   |

| t <sub>WHDX</sub>  | t <sub>DH</sub>                      | Data Hold Time                       |                                                     |        | Min | 0    | 0    | 0    | 0    | ns   |

|                    | t <sub>OES</sub>                     | Output Enable S                      | etup Time (Note 2)                                  | )      | Min | 0    | 0    | 0    | 0    | ns   |

|                    |                                      | Output Enable                        | Read (Note 2)                                       |        | Min | 0    | 0    | 0    | 0    | ns   |

|                    | t <sub>OEH</sub>                     | Hold Time                            | Toggle and Data Polling (Note 2)                    |        | Min | 10   | 10   | 10   | 10   | ns   |

| t <sub>GHWL</sub>  | t <sub>GHWL</sub>                    |                                      | Read Recovery Time Before Write (OE High to WE Low) |        |     | 0    | 0    | 0    | 0    | ns   |

| t <sub>ELWL</sub>  | t <sub>CS</sub>                      | CE Setup Time                        | CE Setup Time                                       |        |     | 0    | 0    | 0    | 0    | ns   |

| t <sub>WHEH</sub>  | t <sub>CH</sub>                      | CE Hold Time                         |                                                     |        | Min | 0    | 0    | 0    | 0    | ns   |

| t <sub>WLWH</sub>  | t <sub>WP</sub>                      | Write Pulse Widt                     | Write Pulse Width                                   |        |     | 50   | 50   | 50   | 65   | ns   |

| t <sub>WHDL</sub>  | t <sub>WPH</sub>                     | Write Pulse Widt                     | h High                                              |        | Min | 30   | 30   | 30   | 35   | ns   |

|                    |                                      | D                                    | Byte                                                |        | Тур | 9    | 9    | 9    | 9    |      |

| twhwh1             | twhwh1                               | Programming Op                       | beration                                            | Word   | Тур | 11   | 11   | 11   | 11   | μs   |

| t <sub>WHWH2</sub> | t <sub>WHWH2</sub>                   | Sector Erase Op                      | eration (Note 1)                                    |        | Тур | 1    | 1    | 1    | 1    | sec  |

|                    | t <sub>VCS</sub>                     | V <sub>CC</sub> Setup TIme           |                                                     |        | Min | 50   | 50   | 50   | 50   | μs   |

|                    | t <sub>RB</sub>                      | Write Recovery                       | Time from RY/BY                                     |        | Min | 0    | 0    | 0    | 0    | ns   |

|                    | t <sub>RH</sub>                      | RESET High Tim                       | e Before Read                                       |        | Min | 50   | 50   | 50   | 50   | ns   |

|                    | t <sub>RPD</sub>                     | RESET To Powe                        | r Down Time                                         |        | Min | 20   | 20   | 20   | 20   | μs   |

|                    | t <sub>BUSY</sub>                    | Program/Erase \                      | alid to RY/BY Dela                                  | ıy     | Min | 90   | 90   | 90   | 90   | ns   |

|                    | t <sub>ELFL</sub> /t <sub>ELFH</sub> | CE to BYTE Swi                       | tching Low or High                                  | ı      | Max | 5    | 5    | 5    | 5    | ns   |

|                    | t <sub>FLQZ</sub>                    | BYTE Switching                       | Low to Output HIG                                   | H Z    | Min | 30   | 30   | 40   | 40   | ns   |

|                    | t <sub>FHQV</sub>                    | BYTE Switching High to Output Active |                                                     |        | Min | 30   | 30   | 40   | 40   | ns   |

|                    | t <sub>VIDR</sub>                    | Rise Time to V <sub>ID</sub>         | Rise TIme to V <sub>ID</sub>                        |        |     | 500  | 500  | 500  | 500  | ns   |

|                    | t <sub>RP</sub>                      | RESET Pulse W                        | idth                                                |        | Min | 500  | 500  | 500  | 500  | ns   |

|                    | t <sub>RRB</sub>                     | RESET Low to F                       | Y/BY High                                           |        | Max | 20   | 20   | 20   | 20   | μs   |

|                    | t <sub>RSP</sub>                     | RESET Setup Til<br>Unprotect         | me for Temporary S                                  | Sector | Min | 4    | 4    | 4    | 4    | μs   |

#### Notes:

- 1. The duration of the program or erase operation is variable and is calculated in the internal algorithms.

- 2. Note 100% tested.

# **SWITCHING WAVEFORMS**

Note: SA is the sector address for Sector Erase

Figure 16. AC Waveforms for Chip/Sector Erase Operations

# **SWITCHING WAVEFORMS (PAGE 36)**

20514B-27

Figure 23. Temporary Sector Unprotect Timing Diagram

#### **AC CHARACTERISTICS**

# Write (Erase/Program) Operations

#### Alternate CE Controlled Writes

| Paramet            | ter Symbols                                        |                                   |                             |         |     |      |      |      |      |      |

|--------------------|----------------------------------------------------|-----------------------------------|-----------------------------|---------|-----|------|------|------|------|------|

| JEDEC              | Standard                                           | Description                       |                             |         |     | -90R | -100 | -120 | -150 | Unit |

| t <sub>AVAV</sub>  | t <sub>WC</sub>                                    | Write Cycle Time                  | (Note 2)                    |         | Min | 90   | 100  | 120  | 150  | ns   |

| t <sub>AVWL</sub>  | t <sub>AS</sub>                                    | Address Setup T                   | Address Setup Time          |         |     | 0    | 0    | 0    | 0    | ns   |

| t <sub>ELAX</sub>  | t <sub>AH</sub>                                    | Address Hold Tin                  | ne                          |         | Min | 50   | 50   | 50   | 65   | ns   |

| t <sub>DVEH</sub>  | t <sub>DS</sub>                                    | Data Setup Time                   |                             |         | Min | 50   | 50   | 50   | 65   | ns   |

| t <sub>EHDX</sub>  | t <sub>DH</sub>                                    | Data Hold Time                    |                             |         | Min | 0    | 0    | 0    | 0    | ns   |

|                    | toes                                               | Output Enable Se                  | etup Time                   |         | Min | 0    | 0    | 0    | 0    | ns   |

|                    |                                                    | Otot. [  -  -                     | Read (Note 2)               |         | Min | 0    | 0    | 0    | 0    | ns   |

|                    | t <sub>OEH</sub> Output Enable Toggle and (Note 2) |                                   | Toggle and Data<br>(Note 2) | Polling | Min | 10   | 10   | 10   | 10   | ns   |

| t <sub>GHEL</sub>  | t <sub>GHEL</sub>                                  | Read Recovery 7<br>(OE High to WE | Ime Before Write<br>Low)    |         | Min | 0    | 0    | 0    | 0    | ns   |

| t <sub>WLEL</sub>  | t <sub>ws</sub>                                    | WE Setup Time                     |                             |         | Min | 0    | 0    | 0    | 0    | ns   |

| t <sub>EHWH</sub>  | t <sub>WH</sub>                                    | WE Hold Time                      |                             |         | Min | 0    | 0    | 0    | 0    | ns   |

| t <sub>ELEH</sub>  | t <sub>CP</sub>                                    | CE Pulse Width                    |                             |         | Min | 50   | 50   | 50   | 65   | ns   |

| t <sub>EHEL</sub>  | t <sub>CPH</sub>                                   | CE Pulse Width I                  | High                        |         | Min | 30   | 30   | 30   | 35   | ns   |

|                    | _                                                  | Drogrammin - O-                   | Byte                        |         | Тур | 9    | 9    | 9    | 9    |      |

| twhwh1             | twhwh1                                             | Programming Op                    | reration                    | Тур     | 11  | 11   | 11   | 11   | μs   |      |

| t <sub>WHWH2</sub> | t <sub>WHWH2</sub>                                 | Sector Erase Op                   | eration (Note 1)            |         | Тур | 1    | 1    | 1    | 1    | sec  |

|                    | t <sub>FLQZ</sub>                                  | BYTE Switching (Note 2)           | Low to Output HIC           | GH Z    | Min | 30   | 30   | 30   | 30   | ns   |

#### Notes

- 1. The duration of the program or erase operation is variable and is calculated in the internal algorithms.

- 2. Does not include the preprogramming time.

- 3. Not 100% tested.

#### **SWITCHING WAVEFORMS**

#### Notes:

- 1. PA is address of the memory location to be programmed.

- 2. PD is data to be programmed at byte address.

- 3.  $\overline{DQ7}$  is the complement of the data written to the device.

- 4. D<sub>OUT</sub> is the data written to the device.

- 5. Figure indicates last two bus cycles of four bus cycle sequence.

20514B-28

Figure 24. Alternate  $\overline{\text{CE}}$  Controlled Write Operation Timings

#### **ERASE AND PROGRAMMING PERFORMANCE**

| Parameter               |           | Typ (Note 2) | Max (Note 3) | Unit   | Comments                          |

|-------------------------|-----------|--------------|--------------|--------|-----------------------------------|

| Sector Erase Time       |           | 1            | 15           | s      | Excludes 00h programming          |

| Chip Erase Time         |           | 11           |              | s      | prior to erasure (Note 4)         |

| Byte Programming Time   |           | 9            | 300          | μs     |                                   |

| Word Programming Time   |           | 11           | 360          | μs     | Excludes system level             |

| Chip Programming Time   | Byte Mode | 4.5          | 13.5         | S      | overhead (Note 5)                 |

| Word Mode               |           | 2.9          | 8.7          | S      |                                   |

| Erase/Program Endurance |           | 1,000,000    |              | cycles | Minimum 100,000 cycles guaranteed |

#### Notes:

- The typical program and erase times are considerably less than the maximum times since most words/bytes program or erase significantly faster than the worst case word/byte. The device enters the failure mode (DQ5="1") only after the maximum times given are exceeded. See the section on DQ5 for further information.

- Except for erase and program endurance, the typical program and erase times assume the following conditions: 28°C, 3.0 V

V<sub>CC</sub>, 100,000 cycles. Additionally, programming typicals assume checkerboard pattern.

- 3. Under worst case conditions of 90 °C,  $V_{CC}$  = 2.7 V, 100,000 cycles.

- 4. In the pre-programming step of the Embedded Erase algorithm, all bytes are programmed to 00h before erasure.

- System-level overhead is the time required to execute the four-bus-cycle sequence for the program command. See Table 6 for further information on command definitions.

#### Trademarks

Copyright © 1997 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD logo, and combinations thereof are registered trademarks of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.