## **PRELIMINARY**

Notice: This is not a final specification. Some parametric limits are subject to change.

# M37416M2-XXXSP/FP

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## **DESCRIPTION**

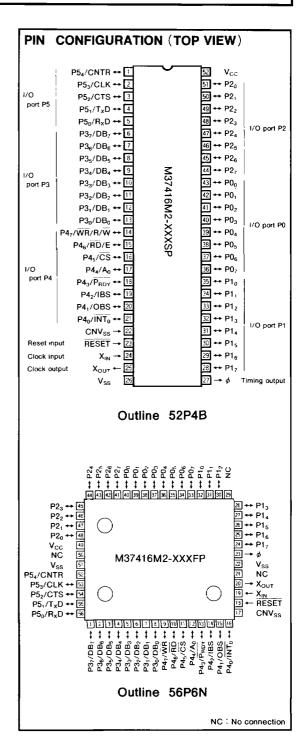

The M37416M2-XXXSP is a single-chip microcomputer designed with CMOS silicon gate technology. It is housed in a 52-pin shrink plastic molded DIP (flat package type also available). This single-chip microcomputer is useful for office automation equipment and other consumer applications.

In addition to its simple instruction sets, the ROM, RAM, and I/O addresses are placed on the same memory map to enable easy programming.

The differences between the M37416M2-XXXSP and the M37416M2-XXXFP are the package outline and power dissipation ability (absolute maximum ratings).

## **FEATURES**

| • | Number of basic instructions                                            | 69              |

|---|-------------------------------------------------------------------------|-----------------|

| • | Memory size ROM ······                                                  | ···· 4096 bytes |

|   | RAM                                                                     | ····· 128 bytes |

| • | <ul> <li>Instruction execution time</li> </ul>                          |                 |

|   | 1µs (minimum instructions at 8M                                         | Hz frequency)   |

| • | <ul> <li>Single power supply f(X<sub>IN</sub>)=8MHz·········</li> </ul> | 5v±10%          |

| • | <ul> <li>Power dissipation</li> </ul>                                   |                 |

|   | normal operation mode (at 8MHz freque                                   | ncy) ···· 50mW  |

| • | Subroutine nesting64                                                    | levels (max.)   |

| • | Interrupt                                                               | 8               |

| • | 8-bit timer · · · · · · · · · · · · · · · · · · ·                       | 2               |

| • | Programmable I/O ports                                                  |                 |

|   | (Ports P0, P1, P2, P3, P4, P5) ······                                   | 45              |

| • | UART (full duplex)                                                      | 1               |

| • | Master CPU bus interface · · · · · · · · · · · · · · · · · · ·          | ······1 byte    |

|   | Comparator                                                              |                 |

| • | Key on wake up · · · · · · · · · · · · · · · · · ·                      | 8               |

#### **APPLICATION**

Office automation equipment Key pad, Key board

# MITSUBISHI MICROCOMPUTERS M37416M2-XXXSP/FP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## FUNCTIONS OF M37416M2-XXXSP

| Parameter                   |                                  |        | Functions                                                                                       |  |  |  |

|-----------------------------|----------------------------------|--------|-------------------------------------------------------------------------------------------------|--|--|--|

| Number of basic instruction | tions                            |        | 69                                                                                              |  |  |  |

| Instruction execution tim   | ie                               |        | 1μs (minimum instructions, at 8MHz frequency)                                                   |  |  |  |

| Clock frequency             |                                  |        | 8MHz                                                                                            |  |  |  |

| Memory size ROM             |                                  |        | 4096 bytes                                                                                      |  |  |  |

| Memory size                 | RAM                              |        | 128 bytes                                                                                       |  |  |  |

|                             | P0 <sub>0</sub> ~P0 <sub>7</sub> | 1/0    | 8-bit×1                                                                                         |  |  |  |

|                             | P1 <sub>0</sub> ~P1 <sub>7</sub> | 1/0    | 8-bit×1                                                                                         |  |  |  |

| Input/Output ports          | P2 <sub>0</sub> ~P2 <sub>7</sub> | 1/0    | 8-bit×1 (common with comparator input and key on wake up)                                       |  |  |  |

| mpar output ports           | P3 <sub>0</sub> ~P3 <sub>7</sub> | 1/0    | 8-bit×1 (common with data bus of system bus interface)                                          |  |  |  |

|                             | P40~P47                          | 1/0    | 8-bit×1 (common with control ports of system bus interface and INT <sub>0</sub> )               |  |  |  |

|                             | P50~P54                          | 1/0    | 5-bit×1 (common with UART)                                                                      |  |  |  |

| UART                        |                                  |        | 1 with programmable baud rate generator                                                         |  |  |  |

| Timers                      |                                  |        | 8-bit×2 (with 8-bit prescaler)                                                                  |  |  |  |

| Comparator                  |                                  |        | 8-bitX1 (port P2) Built-in 3-bit DAC (can be used as variable V <sub>TH</sub> input port)       |  |  |  |

| Subroutine nesting          |                                  |        | 64 levels (max.)  System bus interrupt 1, UART interrupt 1. Timer interrupt 1, INTo interrupt 1 |  |  |  |

| Interrupt                   |                                  |        |                                                                                                 |  |  |  |

| System bus interface bu     | ifter                            |        | 1-byte (separate input and output buffers)                                                      |  |  |  |

| Clock generating circuit    |                                  |        | Built-in (Ceramic or quartz crystal oscillator)                                                 |  |  |  |

| Supply voltage              |                                  |        | 5V±10%                                                                                          |  |  |  |

|                             | at operation                     |        | 50mW                                                                                            |  |  |  |

| D dississation              | at wait mode                     |        | 5mW                                                                                             |  |  |  |

| Power dissipation           |                                  | Ta=25℃ | 0.05mW                                                                                          |  |  |  |

|                             | at stop mode                     | Ta=70℃ | 0.5mW                                                                                           |  |  |  |

| Input/Output                | Input/Output voltage             |        | V <sub>SS</sub> -0.3~V <sub>CC</sub> +0.3                                                       |  |  |  |

| characteristics             | Output current                   |        | ±5mA (max.)                                                                                     |  |  |  |

| Operating temperature       | range                            |        | -10~70°C                                                                                        |  |  |  |

| Device structure            |                                  |        | CMOS silicon gate                                                                               |  |  |  |

| Ossbans                     | M37416M2-XXXSP                   |        | 52-pin shrink plastic molded DIP                                                                |  |  |  |

| Package                     | M37416M2-XXXFP                   |        | 56-pin plastic molded QFP                                                                       |  |  |  |

# MITSUBISHI MICROCOMPUTERS M37416M2-XXXSP/FP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## PIN DESCRIPTION

| Pin                                  | Name            | Input/<br>Output | Functions                                                                                                                                                                                                                                                        |

|--------------------------------------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>cc</sub> ,<br>V <sub>ss</sub> | Supply voltage  |                  | Power supply inputs 5V $\pm$ 10% to V <sub>CC</sub> . and 0V to V <sub>SS</sub> .                                                                                                                                                                                |

| CNV <sub>ss</sub>                    | CNVss           |                  | This is usually connected to V <sub>SS</sub> .                                                                                                                                                                                                                   |

| RESET                                | Reset input     | Input            | To enter the reset state, the reset input pin must be kept at a "L" for more than 2µs (under normal V <sub>CC</sub> conditions). If more time is needed for the crystal oscillator to stabilize, this "L" condition should be maintained for the required time.  |

| X <sub>IN</sub>                      | Clock input     | Input            | This chip has an internal clock generating circuit. To control generating frequency, an external ceramic or a quartz crystal oscillator is connected between the X <sub>N</sub> and X <sub>OUT</sub> pins. If an external clock is used, the clock               |

| X <sub>OUT</sub>                     | Clock output    | Output           | source should be connected the X <sub>IN</sub> pin and the X <sub>OUT</sub> pin should be left open.                                                                                                                                                             |

| φ                                    | Timing output   | Output           | This is the timing output pin.                                                                                                                                                                                                                                   |

| CNTR                                 | Timer I/O       | 1/0              | This is an I/O pin for the timer X.                                                                                                                                                                                                                              |

| ÎNT <sub>1</sub>                     | Interrupt input | Input            | This is the highest order interrupt input pin.                                                                                                                                                                                                                   |

| P0 <sub>0</sub> ~P0 <sub>7</sub>     | I/O port P0     | 1/0              | Port P0 is an 8-bit I/O port with directional registers allowing each I/O bit to be individually programmed as input or output. The output structure is CMOS output.                                                                                             |

| P1 <sub>0</sub> ~P1 <sub>7</sub>     | I/O port P1     | 1/0              | Port P1 is an 8-bit I/O port and has basically the same function as port P0.                                                                                                                                                                                     |

| P2 <sub>0</sub> ~P2 <sub>7</sub>     | ł/O port P2     | 1/0              | Port P2 is an 8-bit I/O port and has basically the same function as port P0. Analog input of comparator or key on wake up function can be selected with a program.                                                                                               |

| P3 <sub>0</sub> ~P3 <sub>7</sub>     | I/O port P3     | 1/0              | Port P3 is an 8-bit I/O port and has basically the same function as port P0. This port functions as an 8-bit data bus for the master CPU when slave mode is selected with a program.                                                                             |

| P4 <sub>0</sub> ~P4 <sub>7</sub>     | I/O port P4     | 1/0              | Port P4 is an 8-bit I/O port and has basically the same function as port P0. P4 <sub>1</sub> ~P4 <sub>7</sub> change to a control bus for the master CPU when slave mode is selected with a program. P4 <sub>0</sub> can be used as external interruptinput pin. |

| P5 <sub>0</sub> ~P5 <sub>4</sub>     | I/O port P5     | 1/0              | Port P5 is an 8-bit I/O port and has basically the same function as port P0. UART function, CNTR input and timer output can be selected with a program.                                                                                                          |

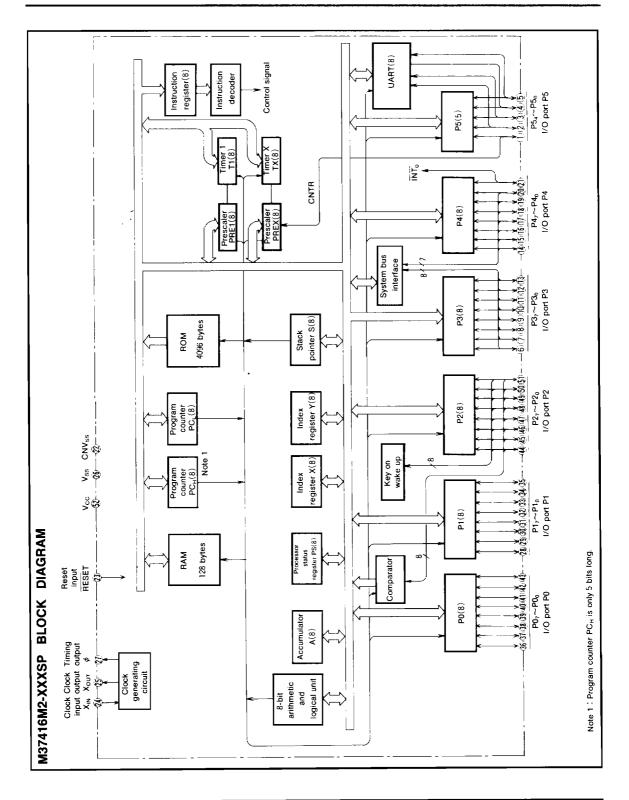

#### **BASIC FUNCTION BLOCKS**

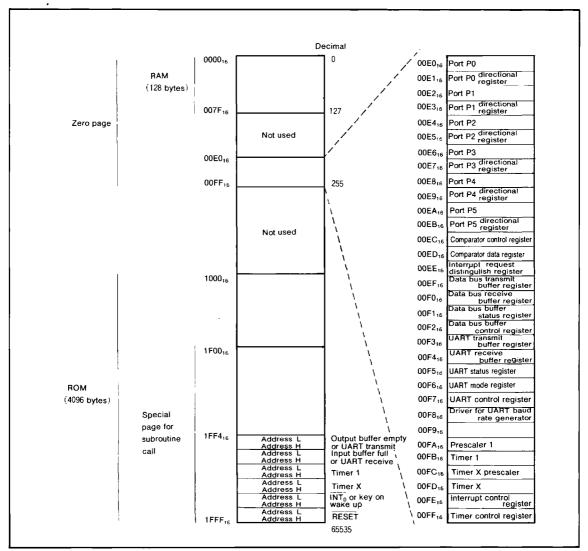

## **MEMORY**

A memory map for the M37416M2-XXXSP is shown in Figure 1. Addresses  $1000_{16}$  to 1FFF $_{16}$  are assigned to the built-in ROM area which consists of 4096 bytes.

Addresses 1F00<sub>16</sub> to 1FFF<sub>16</sub> are a special address area (special page). By using the special page addressing mode of the JSR instruction, subroutines addressed on this page can be called with only 2 bytes. Addresses 1FF4<sub>16</sub> to 1FFF<sub>16</sub> are vector addresses used for the reset and inter-

rupts (see interrupt chapter). Addresses  $0000_{16}$  to  $00FF_{16}$  are the zero page address area. By using the zero page addressing mode, this area can also be accessed with 2 bytes. The use of these addressing methods will greatly reduce the object size required. The RAM, I/O port, timer, etc., are assigned to this area.

Addresses 0000<sub>16</sub> to 007F<sub>16</sub> are assigned to the built-in RAM and respectively consist of 128 bytes of static RAM. In addition to data storage, this RAM is used for the stack during subroutine calls and interrupts.

Fig. 1 Memory map

## M37416M2-XXXSP/FP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## **CENTRAL PROCESSING UNIT (CPU)**

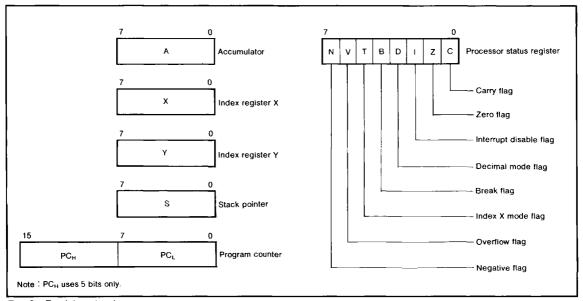

The CPU consists of 6 registers and is shown in Figure 2.

## **ACCUMULATOR (A)**

The 8-bit accumulator (A) is the main register of the microcomputer. Data operations such as data transfer, Input/Output, etc., are executed mainly through accumulator.

## INDEX REGISTER X (X)

The index register X is an 8-bit register.

In the index addressing mode, the value of the OPERAND added to the contents of the register X, specifies the real address. When the T flag in the processor status register is set to "1", the index register X itself becomes the address for the second OPERAND.

## INDEX REGISTER Y (Y)

The index register Y is an 8-bit register.

In the index addressing mode, the value of the OPERAND added to the contents of the register Y specifies the real address.

## STACK POINTER (S)

The stack pointer (S) is an 8-bit register that contains the address of the next location in the stack. It is mainly used during interrupts and subroutine calls. The stack pointer is not automatically initialized after reset and should be initialized by the program using the TXS instruction.

The location of the stack can be determined by the stack page bit (bit 4 at address  $00FF_{16}$ ). When bit 4 is "0" and the contents of the stack pointer is  $XX_{16}$ , the stack address is set to  $00XX_{16}$ . When bit 4 is "1", the stack address is set to  $01XX_{16}$ . When using this microcomputer in the single-chip mode, the stack page bit must be "0" and the stack pointer should be set at the bottom address of the internal RAM.

When an interrupt occurs, the higher 8 bits of the program counter are pushed into the stack first, and then the lower 8 bits of the program counter are pushed into the stack. After each byte is pushed into the stack, the stack pointer is decremented by one. Next, the contents of the processor status register are pushed into the stack. When the return from interrupt instruction (RTI) is executed, the program counter are processor status register data is pulled off the stack in reverse order from above.

The Accumulator is never pushed into the stack automatically. A Push Accumulator instruction (PHA) is provided to execute this function. Restoring the Accumulator to its previous value is accomplished by the Pull Accumulator instruction (PLA). It is executed in reverse order of the PHA instruction.

Fig. 2 Register structure

The contents of the Processor Status Register (PS) are pushed (pulled) to (from) the stack with the PHP and PLP instructions, respectively. Only the program counter is pushed into the stack during a subroutine call. Therefore, any registers that should not be destroyed should be pushed into the stack manually. The RTS instruction is used to return from a subroutine.

## PROGRAM COUNTER (PC)

The 16-bit program counter consists of two 8-bit registers PC<sub>H</sub> and PC<sub>L</sub>. The program counter is used to indicate the address of the next instruction to be executed.

## PROCESSOR STATUS REGISTER (PS)

The processor status register is composed entirely of flags used to indicate the condition of the processor immediately after an operation. Branch operations can be performed by testing the Carry flag (C), Zero flag (Z), Overflow flag (V) or the Negative flag (N). Each bit of the register is explained below.

## 1. Carry flag (C)

The carry flag contains the carry or borrow generated by the Arithmetic and Logical operation Unit (ALU) immediately after an operation. It also changed by the shift and rotate instructions. The set carry (SEC) and clear carry (CLC) instructions allow direct access for setting and clearing this flag.

## 2. Zero flag (Z)

This flag is used to indicate if the immediate operation generated a zero result or not. If the result is zero, the zero flag will be set to "1". If the result is not zero, the zero flag will be set to "0".

#### 3. Interrupt disable flag (1)

This flag is used to disable all interrupts. This is accomplished by setting the flag to "1". When an interrupt, this flag is automatically set to "1" to prevent other interrupts from interfering until the current interrupt is completed. The SEI and CLI instructions are used to set and clear this flag, respectively.

## 4. Decimal mode flag (D)

The decimal mode flag is used to define whether addition and subtraction are executed in binary or decimal. If the decimal mode flag is set to "1", the operations are executed in decimal, if the flag is set to "0", the operations are executed in binary. Decimal correction is automatically executed. The SED and CLD instructions are used to set and clear this flag, respectively.

## 5. Break flag (B)

When the BRK instruction is executed, the same operations are performed as in an interrupt. The address of the interrupt vector of the BRK instruction is the same as that of the lowest priority interrupt. The contents of the B flag can be checked to determine which condition caused the interrupt. If the BRK instruction caused the interrupt, the break flag will be "1", otherwise it will be "0".

## 6. Index X mode flag (T)

When the T flag is "1", operations between memories are executed directly without passing through the accumulator. Operations between memories involving the accumulator are executed when the T flag is "0" (i.e., operation results between memories 1 and 2 are stored in the accumulator). The address of memory 1 is specified by the contents of the index register X, and that of memory 2 is specified by the normal addressing mode. The SET and CLT instructions are used to set and clear the index X mode flag, respectively.

## 7. Overflow flag (V)

The overflow flag functions when one byte is added or subtracted as a signed binary number. When the result exceeds +127 or -128, the overflow flag is set to "1". When the BIT instruction is executed, bit 6 of the memory location is input to the overflow flag. The overflow flag is reset by the CLV instruction and there is no set instruction.

#### 8. Negative flag (N)

The negative flag is set whenever the result of a data transfer or operation is negative (bit 7 is set to "1"). Whenever the BIT instruction is executed, bit 7 of the memory location is input to the negative flag. There are no instructions for directly setting or resetting the negative flag.

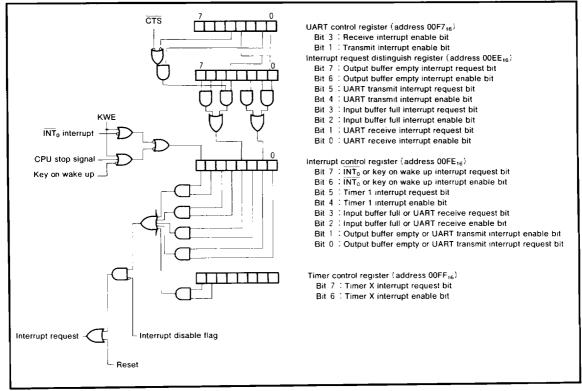

## **INTERRUPTS**

Interrupts can be caused by 9 different events.

Interrupts are vectored interrupts with priorities shown in Table 1. Reset is also included in the table because its operation is similar to an interrupt.

When an interrupt is accepted, the registers are pushed as described in the stack pointer (S) section above, interrupt inhibit flag I is set, and the program jumps to the address specified in the vector table. The reset and BRK instruction interrupt can never be inhibited. Other interrupts are disabled when the interrupt inhibit flag is set.

All interrupts except the BRK instruction interrupt have an interrupt request bit and an interrupt enable bit.

Interrupts other than the BRK instruction interrupt and reset are accepted when the interrupt enable bit is "1", interrupt request bit is "1", and the interrupt inhibit bit is "0". There are two interrupt (three for UART transmit and UART receive) the interrupt becomes enable when both enable bits are "0".

The value of bit 3 of the data bus buffer control register (address  $00F2_{16}$ ) determines whether the interrupt is from  $\overline{INT_0}$  or from key on wake up. Only  $\overline{INT_0}$  interrupt is effective when this bit is "1" at power down condition by STP or WIT instruction. When this bit is "1", interrupt is caused by inputting "L" level to any port P2 using input mode. The

value of bit 1 and bit 3 of interrupt request distinguish register (address  $00EE_{16}$ ) determine whether the interrupt is from input buffer full or from UART receive. When bit 3 is "1", the interrupt is from the input buffer full interrupt, and bit 1 is "1", the interrupt is from UART receive. Also bit 5 and bit 7 of interrupt request distinguish register determine whether the interrupt is from output buffer empty or from UART transmit. When bit 7 is "1", the interrupt is from output buffer empty and when bit 5 is "1", the interrupt is from UART transmit.

Table 1. Interrupt vector address and priority

| Interrupt                                | Priority | Vector address                          |

|------------------------------------------|----------|-----------------------------------------|

| RESET                                    | 1        | FFFF <sub>16</sub> , FFFE <sub>16</sub> |

| INT <sub>0</sub> or key on<br>wake up    | 2        | FFFD <sub>16</sub> , FFFC <sub>16</sub> |

| Timer X                                  | 3        | FFFB <sub>16</sub> , FFFA <sub>16</sub> |

| Timer 1                                  | 4        | FFF9 <sub>16</sub> , FFF8 <sub>16</sub> |

| Input bus buffer full or<br>UART receive | 5        | FFF7 <sub>16</sub> , FFF6 <sub>16</sub> |

| Output bus buffer full or UART transmit  | 6        | FFF5 <sub>16</sub> , FFF4 <sub>16</sub> |

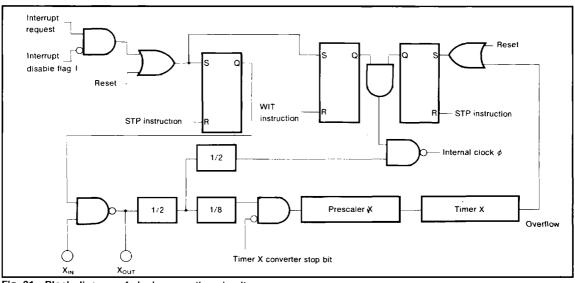

Fig. 3 Interrupt control

When the two interrupt requests, which are the same priority, are at the same sampling, the priority process is processed by interrupt request distinguish register.

These request bits can be reset by a program but can not be set. The interrupt requests bits which are in the interrupt control register and timer control register are reset automatically when interrupts are accepted. But the interrupt request bits which are in the interrupt request distinguish register are not reset automatically, so they must be reset by software. The contents of the B flag must be checked to determine if the BRK instruction caused or not.

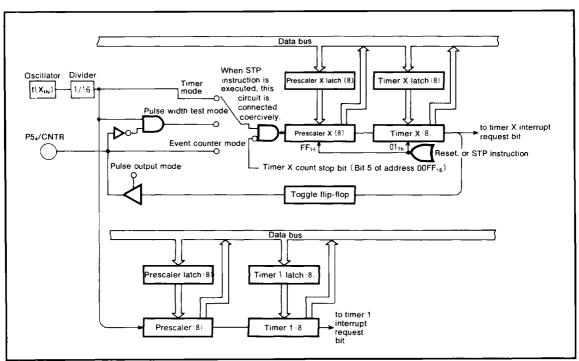

#### TIMER

The M37416M2-XXXSP has two timers; timer X, and timer 1. Timer X has four modes which can be selected by bit 2 and 3 of the timer control register. When the timer X count stop bit (bit 5) is set to "1", the timer X will stop regardless of which mode it is in. A block diagram of timer X, and timer 1 is shown in Figure 4. The CNTR pin is common with P54 and can not be used when this pin is used as normal port.

The prescaler has an 8-bit programmable latch used as a frequency divider. The division ratio is defined as 1/(n+1), where n is the decimal contents of the prescaler latch. All timers are down-count timers which are reloaded from the timer latch following the zero cycle of the timer (i.e. the cycle after the timer counts to zero).

The timer interrupt request bit is set to "1" during the next clock pulse after the timer reaches zero. The interrupt and timer control registers are located at addresses  $00FE_{16}$  and  $00FF_{16}$ , respectively (see interrupt section). The prescaler latch and timer latch can be loaded with any number except zero.

Fig. 4 Block diagram of timer X and timer 1

The four modes of timer X as follows:

#### (1) Timer mode [00]

In this mode the clock is driven by the oscillator frequency divided by 16. When the timer down-counts to zero, the timer interrupt request bit is set to "1" and the contents of the timer's latch is reloaded into the timer and the counting begins again.

(2) Pulse output mode (01) In this mode, the polarity of the P5<sub>4</sub>/CNTR signal is re-

versed each time the timer down-counts to zero.

(3) Event counter mode [10]

This mode operates in the same manner as the timer mode except the clock source is input to the CNTR pin. This mode will allow an interrupt to be generated whenever a specified number of external events have been generated. The timer down-counts every rising edge of the clock source.

## (4) Pulse width measurement mode [11]

This mode measures the pulse width (between lows) input to the P5<sub>4</sub>/CNTR pin. The timer, driven by the oscillator frequency divided by 16, continues counting during the low cycle of the CNTR pin. When the timer contents reaches "0", the interrupt request bit is set to "1", the timer's reload latch is reloaded and the counting resumes.

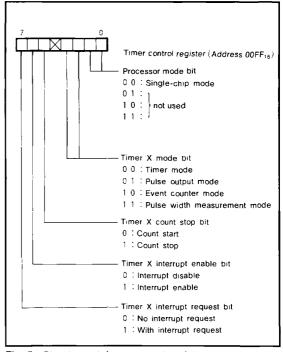

The structure of the timer control register is shown in Figure 5.

When the STP instruction is executed, or after reset, the prescaler and timer latch are set to FF<sub>16</sub> and 01<sub>16</sub>, respectively. Also, when the STP instruction is executed, the oscillator's frequency (divided by 16) will become the counting source, regardless of the timer X mode setting. This state will be released when the timer X interrupt request bit is set to "1", or after a reset. Timer X will then enter the mode specified by its mode bits. For more details on the STP instruction, refer to the oscillation circuit section.

Fig. 5 Structure of timer control register

## **BUS INTERFACE**

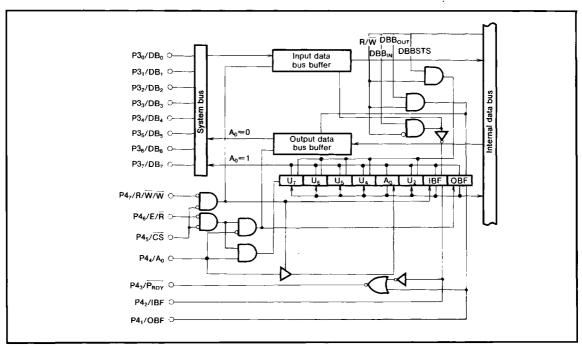

The M37416M2-XXXSP is equipped with a bus interface that is functionally similar to the M5L8041-XXXSP. Its operation can be controlled with control signals from the master CPU (slave mode).

The M37416M2-XXXSP bus interface, can be connected directly to either a  $R/\overline{W}$  type CPU or separate  $\overline{RD}$ ,  $\overline{WR}$  type CPU. Figure 7 shows a block diagram of the bus interface function

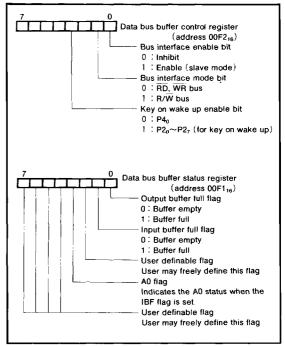

Slave mode is selected with data bus buffer control register (address 00F2<sub>16</sub>) bit 0 and 1 as shown in Figure 6.

An input buffer full interrupt occurs when data is received from the master CPU and an output buffer empty interrupt occurs when data is read by the master CPU.

In slave mode, ports  $P3_0 \sim P3_7$  become a tri-state data bus used to transfer data, commands, and status to and from the master CPU.

Furthermore, ports  $P4_4 \sim P4_7$  become master CPU control signal input pins and  $P4_1 \sim P4_3$  becomes a slave status output pins.

## [Data bus buffer status register] DBBSTS

This is an 8-bit register. Bits 0, 1, and 3 are read-only bits indicating the status of the data bus buffer. Bits 2, 4, 5, 6, and 7 are read/write enabled user-definable flags that can be set with a program. The host CPU can only read these flags by setting the A0 pin to "H".

Fig. 6 Structure of bus interface relation registers

Fig. 7 Bus interface circuit diagram

#### · Output buffer full flag OBF

This flag is set when data is written in the output data bus buffer and cleared when the host CPU reads the data in the output data bus buffer. It is initialized to "1" at reset and cleared to "0" when the slave mode is selected with the bus interface enable bit set.

#### · Input buffer full flag IBF

This flag is set when the host CPU writes data in the input data bus buffer and cleared when the slave CPU reads the data in the input data bus buffer. This bit is initialized to "0" at reset.

Execute the dummy write instruction to the input data bus buffer to clear this flag from the slave CPU side. The contents of input data bus buffer is not change because it is read only register.

## Ao flag

The level of the  $A_0$  pin is latched when the host CPU writes data in the input data bus buffer.

## [Input data bus buffer] DBBIN

Data on the data bus is latched in DBBIN when there is a write request from the host CPU. The data in DBBIN can be read from the data bus buffer register (SFR address  $00F0_{16}$ ).

## [Output data bus buffer] DBBOUT

Data is written in DBBOUT by writing data in data bus buffer register (SFR address  $00EF_{16}$ ). The data in DBBOUT is output to the data bus (P5) when the host CPU issues a read request with setting the  $A_0$  pin to "L".

Table 2. Control I/O pin functions when bus interface function is selected

| Pin             | Name             | Bus interface mode bit | input/<br>Output | Function                                                                                                                                                                                                                |  |  |

|-----------------|------------------|------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P4 <sub>1</sub> | OBF              |                        | Output           | Status output. OBF signal is output.                                                                                                                                                                                    |  |  |

| P4 <sub>2</sub> | IBF              | _                      | Output           | Status output. IBF signal is output.                                                                                                                                                                                    |  |  |

| P4 <sub>3</sub> | P <sub>RDY</sub> | _                      | Output           | Status output. The NOR of OBF and IBE is outnput.                                                                                                                                                                       |  |  |

| P4 <sub>4</sub> | Ao               |                        | Input            | Address input. Used to select between DBBSTS and DBBOUT during host CPU read. Also used to identify commands and data during write.                                                                                     |  |  |

| P4 <sub>5</sub> | cs               | _                      | Input            | Chip select input. Used to select the data bus buffer Select when "L".                                                                                                                                                  |  |  |

| P4 <sub>6</sub> | Ā                | 0                      | Input            | Timing signal used by the host CPU to read data from the data bus buffer.                                                                                                                                               |  |  |

|                 | E                | 1                      | Input            | Inputs a timing signal E or inverse of $\phi$ .                                                                                                                                                                         |  |  |

| P4 <sub>7</sub> | w                | 0                      | Input            | Timing signal used by the host CPU to write data to the data bus buffer                                                                                                                                                 |  |  |

|                 | R/W              | 1                      | Input            | Input R/W signal used to control the data transfer direction. When this signal is "L", data bus buffer write is synchronized with the E signal. When it is "H", data bus buffer read is synchronized with the E signal. |  |  |

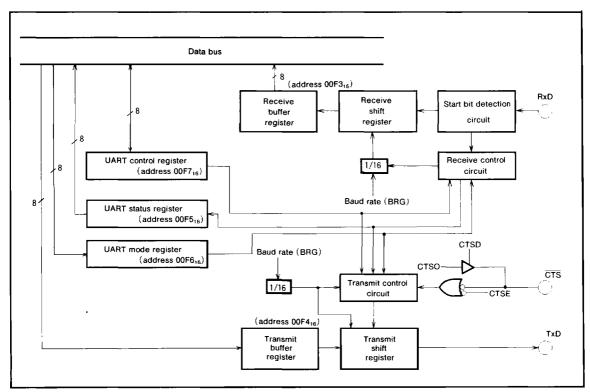

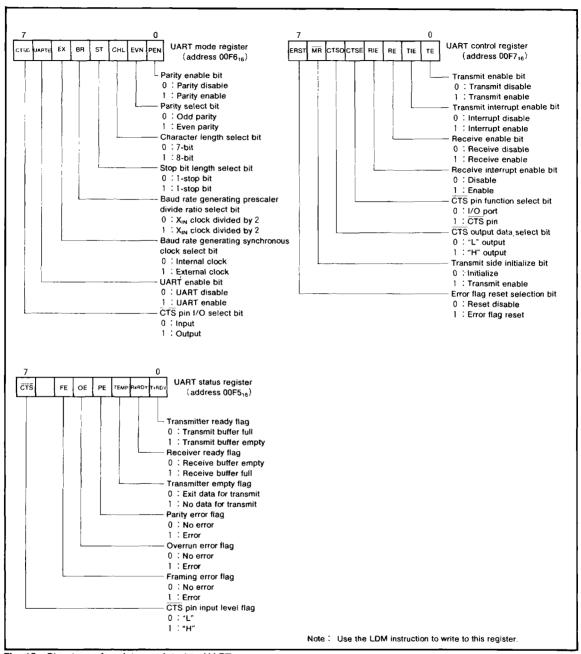

### **UART**

The M37416M2-XXXSP contains one channel UART. It has three pins (TxD (transmit output), RxD (receive input) and  $\overline{CTS}$  (clear to send)). The three pins RxD, TxD and  $\overline{CTS}$  are common with P50, P51 and P52 respectively. P50  $\sim$  P52 are selected to UART function pins when UART enable bit (bit 6 of UART mode register) to "1". And it also has a CLK pin (the input pin of the external clock for band rate generation). This pin is selected as CLK function when the synchronous clock for band rate generating synchronous clock select bit (bit 5 of UART mode register) is set to "1". An interrupt can be generated at receive and transmit independently.

[Receive operation]

Setting the receive enable bit (bit 2 of the UART control register) to "1" puts the system in the receive ready state. When there is no input of receive data, "H" is input to RxD pin. When the falling edge is input to RxD pin and "L" input is detected twice consecutively by sampling with the clock having a frequency 16 times the baud rate, the start bit is triggered. Then, sampling is performed three time in the middle of the start bit. When "L" is detected twice or more, the receive operation begins, capturing the data bits into the receive shift register. If "L" has not been detected twice or more, start bit detection begins again. When the data bits and parity bit have been captured into the receive shift register and the stop bit is detected, the receive data is transferred from the receive shift register to the receive buffer register, setting the receiver ready flag (bit 1 of the UART status register). If a parity error occurred, the parity error flag is set. The framing error flag is set when the first stop bit is found "L". If the previous data has not been read out of the receive buffer register, the overrun error flag is set, clearing the previous data. Execute the dummy write instruction to the receive buffer register to clear the receiver ready flag. The contents of receive buffer register is not changed because it is read only register. Each error flag can be reset by writing "1" to the error flag reset bit (bit 7 of the UART control register). Any of these errors does not affect the receive operation. The data bit, the parity bit, and the stop bit are sampled three times in the middle of them each. When "L" or "H" is detected twice or more, "0" or "1" is determined respectively.

Each time a receive operation has been completed, setting the receiver ready flag, the UART receive interrupt request bit (bit 1 of the interrupt request distinguish register) is set. An interrupt is acknowledged when the two UART receive interrupt enable bits (Bit 0 of interrupt request distinguish register, bit 2 of interrupt control register and bit 3 of UART control register) are all "1" and the interrupt disable flag 1 is "0". The UART receive interrupt request bit which is in interrupt control register (address 00FE<sub>16</sub>) is reset when a UART receive interrupt is acknowledged.

Setting the receive enable bit (bit 2 of the UART control register) to "0" puts the system in the receive stopped state. At this time, the receiver ready flag is "0" (ready), the receive shift register is in the stopped state, and the start bit detection is stopped.

## [Transmit operation]

When the send data is written to the transmit buffer register, the start bit, the parity bit, and the stop bit are added to the data, which is transferred to the transmit shift register. The transmit shift register begins shift when it becomes enable for transmission, sending the serial data to TxD pin. For the description of the transmit enable state, see Table 3. In the transmit enable state, each time transmission of the stop bit of the serial data being transmitted has been completed, it is checked whether the next data has been written to the transmit buffer register. If the data is found written, transmission of the next data begins. If the data is found not written, TxD pin is held at "H" until the next transmit data is written, setting the transmitter empty flag. When the transmit enable state is cleared during transmission, the transmission is stopped after completing the transmission of the transmit data so far written to the transmit buffer register.

When the transmitter ready flag (bit 0 of the UART status register) is "1", it indicates that the transmit buffer is ready

for writing data. The immediately preceding data is transferred from the transmit buffer register to the transmit shift register. Every time the start bit is output from TxD pin, this flag is set. Every time the transmitter ready flag is set, the UART transmit interrupt request bit (bit 5 of the interrupt request distinguish register) is set. An interrupt is acknowledged when three UART transmit interrupt enable bits (bit 1 of the UART control register, bit 4 of the interrupt request distinguish register and bit 1 of interrupt control register) are all "1" and the interrupt disable flag I is "0". Interrupt request bit (bit 1 of interrupt control register) is reset when the UART transmit interrupt is accepted.

Note that an interrupt occurs only in the transmit ready state.

Bit 6 of the UART control register initializes the UART transmit side. When this bit "0", the transmit side is in the initial state.

Table 3. Bit and pin status when transmission is ready

| TE | CTSE | CTS | TE :  |

|----|------|-----|-------|

| 4  | 0    | X   | CTSE: |

|    | 1    | L   | CTS : |

TE : UART transmit enable bit

CTSE: CTS pin function selection bit

CTS : CTS pin input level

Fig. 8 UART block diagram

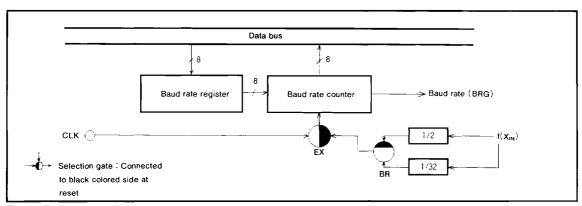

## [UART divider for baud rate generator]

This is an 8-bit programmable divider which generates the baud rate for the UARTi receive or transmit operation.

When the setting value is  $N_{BR}$  (0 to 255), the divide ratio becomes  $1/(N_{BR}+1)$ . There are three count sources;  $X_{IN}$  clock divided by 2,  $X_{IN}$  clock divided by 32, and the external clock. Choose sources by bits 4 and 5 of the UARTi mode register. Table 4 shows the baud rate calculation and example for each bit combination.

When the external clock is used, the frequency of the input clock must be below 1.6 MHz. Writing to the baud rate generating divider must be performed when bits 2 and 6 of the UARTi control register are both "0".

Table 4. Baud rate calculation and example

| EX | BR | Calculation                                           | Count source                    | Baud rate  |

|----|----|-------------------------------------------------------|---------------------------------|------------|

| 0  | 0  | baud rate(bps)= $\frac{f_{(X_{IN})}}{32(N_{BR}+1)}$   | 1(X <sub>IN</sub> )=8.0 MHz     | 250000 bps |

| 0  | 1  | baud rate(bps) = $\frac{f_{ X_{IN} }}{512(N_{BR}+1)}$ | f(X <sub>IN</sub> )=7. 3728 MHz | 4800 bps   |

| 1  |    | baud rate(bps) = $\frac{f(CLK)}{16(N_{BR}+1)}$        | f(X <sub>IN</sub> )=1,536 MHz   | 9600 bps   |

EX : Clock selection bit for baud rate generator

R Divide ratio selection bit for baud rate generator

Fig. 9 Baud rate generating circuit

## M37416M2-XXXSP/FP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

## [CTS pin]

The CTS pin can be used as the 1-bit I/O port when bit 4 of the UART control register is "0". In this case, the input/out-put direction can be determined by bit 7 of the UART mode register and the output data can be set by bit 5 of the UART control register. Additionally, the input level can be known by bit 7 of the UART status register.

## [UART mode register]

This register except the bit 6 is write-only register and cannot be read out. Use the LDM instruction to write to this register.

## · Parity enable bit: PEN

Setting this bit to "1" adds a parity bit to the transmit data. In a receive operation, this bit is used for parity evaluation.

#### · Parity select bit: EVN

This bit specifies the parity bit to be generated in a transmit operation and the parity bit to be evaluated in a receive operation. Depending on the content of this bit, the number of 1's in data is made even or odd.

## · Character length select bit: CHL

This bit specifies the character length of data.

## · Stop bit length select bit: ST

This bit specifies the stop bit length.

## Baud rate generating prescaler divide ratio select bit: BR

When this bit is "0", the signal obtained by dividing  $X_{\text{IN}}$  clock by 2 becomes the count source of the baud rate divider. When this bit is "1", the signal is obtained by dividing the clock by 32.

# - Baud rate generating synchronous clock selection bit: EX

This bit specifies baud rate synchronous clock. When this bit is "1", external clock is input from the clock pin.

## · UART enable bit: UARTE

P50~P52 is selected UART function when this bit is "1".

#### · CTS pin I/O select bit: CTSD

When this bit is "0", the CTSi pin is the input pin.

When this bit is "1", the pin is the output pin. To use the  $\overline{\text{CTS}}$  pin as the  $\overline{\text{CTS}}$  input, set "0".

## [UART control register]

#### · Transmit enable bit: TE

Setting this bit to "1" enables a transmit operation.

## · Transmit interrupt enable bit: TIE

When this bit is "1", the interrupt in a transmit operation is enabled.

#### · Receive enable bit: RE

Setting this bit to "1" enables a receive operation.

#### · Receive interrupt enable bit: RIE

When this bit is "1", the interrupt in a receive operation is enabled.

## · CTS pin function select bit: CTSE

When this bit is "1", the CTS pin becomes the CTS input.

#### · CTS output data select bit: CTSO

When this bit is "0", "L" is output. When it is "1", "H" is output.

#### · Transmit side initialize bit: MR

When this bit is "0", the transmit side is initialized.

## · Error flag reset select bit: ERST

Setting this bit to "1" resets all error flags. When this bit is read. "0" is always read.

## [UART status register]

## · Transmitter ready flag: TxRDY

When this flag is "1", it indicates that the transmit buffer register is empty and ready for writing transmit data.

## · Receiver ready flag: RxRDY

When this flag is "1", it indicates that the receive buffer register is holding receive data. When the receive buffer register is read, it is cleared.

## · Transmitter empty flag: TEMP

When this flag is "1", it indicates that neither the transmit shift register nor the transmit buffer register hold the data to be transmitted.

## · Parity error flag: PE

This bit is set to "1" when the parity of the received data is different from the parity which was set.

## · Overrun error flag: OR

When this flag is "1", it indicates that, before the data in the receive buffer register is read, the next data is transferred from the receive shift register to the receive buffer register and the previous data is lost.

#### · Framing error flag: FE

This flag is set to "1" when the stop bit is found "L" when data is transferred from the receive shift register to the receive buffer register.

## · CTS pin input level flag: CTS

When the input level of the  $\overline{CTS}$  pin is "L", "0" is read, when it is "H", "1" is read.

# MITSUBISHI MICROCOMPUTERS M37416M2-XXXSP/FP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 10 Structure of registers related to UART

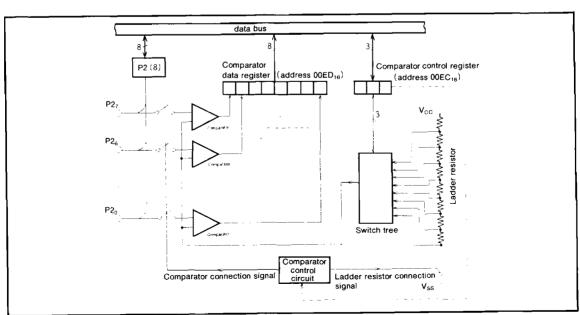

## COMPARATOR CIRCUIT

The comparator circuit is shown in Figure 11. The comparator circuit consists of the switch tree, ladder resistor, comparator, comparator control circuit, comparator control register (address  $00EC_{16}$ ), comparator data register (address  $00FD_{16}$ ), and analog signal input pins,  $P2_0 \sim P2_7$ .

These analog input pins are common with the digital input/output terminal to the data bus.

The 3-bit comparator register can generate  $1/8V_{\rm CC}$ -step internal analog voltage, based on the settings of bits 0 to 2. Table 5 gives the relation between the descriptions of comparator register bits 0 to 2 and the generated internal analog voltage. The comparator result of the analog input voltage and the internal analog voltage is stored in the comparator data register.

The digital value corresponding to the internal analog voltage to be compared is written in the comparator control register (address 00FC<sub>16</sub>), bits 0 to 2. The voltage comparision starts as soon as the writing is completed. 4-cycle (required for comparating) later, the result of comparision is stored in the comparator data register. Each bit of comparator data register is "1" when analog input voltage > internal analog voltage and "0" when analog input voltage < internal analog voltage.

When voltage is compared to by setting bits 0 to 2 of the comparator register "0", each bit of the comparator data register becomes "1" regardless of the analog input voltage. The reference voltage is generated for 4 cycles, when ladder resistor is ON. The ladder resistor is OFF for current power save, when the comparator does not operate.

Since the comparator consists of the capacitive coupled configuration,  $f\left(X_{IN}\right)$  is needed larger than 1MHz during comparision.

Table 5. Relationship between the contents of comparator register and internal voltage

| Comp  | arator re | gister | Internal analog voltage                 |

|-------|-----------|--------|-----------------------------------------|

| bit 2 | bit 1     | bit 0  | Internal analog votage                  |

| 0     | 0         | 1      | 1/8V <sub>cc</sub> -1/16V <sub>cc</sub> |

| 0     | 1         | 0      | 2/8V <sub>cc</sub> -1/16V <sub>cc</sub> |

| 0     | 1         | 1      | 3/8V <sub>cc</sub> -1/16V <sub>cc</sub> |

| 1     | 0         | 0      | 4/8V <sub>CC</sub> -1/16V <sub>CC</sub> |

| 1     | 0         | 1      | 5/8V <sub>cc</sub> -1/16V <sub>cc</sub> |

| 1     | 1         | 0      | 6/8V <sub>cc</sub> -1/16V <sub>cc</sub> |

| 1     | 1         | 1      | 7/8V <sub>cc</sub> -1/16V <sub>cc</sub> |

Fig. 11 Comparator circuit

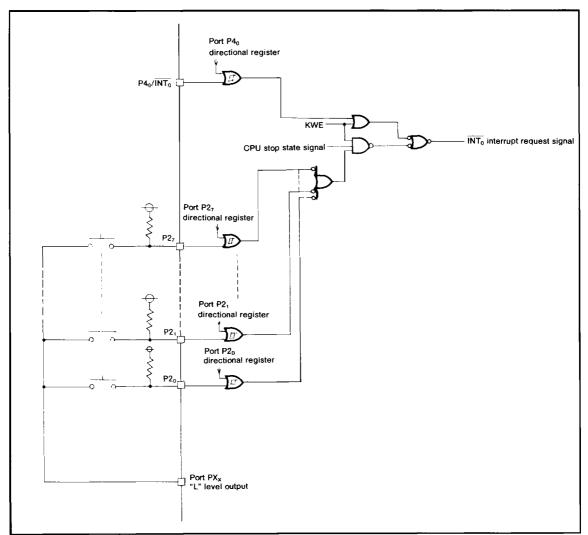

## KEY ON WAKE UP

"Key on wake up" is one way of returning from a power down state caused by the STP or WIT instruction. If any terminal of port P2 has a "L" level applied, after bit 3 of the data bus buffer control register (KWE) is set to "1", an interrupt is generated and the microcomputer is returned to the normal operating state. As shown in Figure 12, a key matrix can be connected to port P2 and the microcomputer can be returned to a normal state by pushing any key.

The key on wake up interrupt is common with the  $\overline{\text{INT}_0}$  interrupt. When KWE is set to "1", the key on wake up function is selected. However, key on wake up cannot be used in the normal operating state. When the microcomputer is in the normal operating state, both key on wake up and  $\overline{\text{INT}_0}$  are invalid.

In order to enter the power down state generated by the STP or WIT instruction at the interrupt disable flag (I) is "0" and KWE is "1", all of port P2 must be input "H".

Fig. 12 Block diagram of port P2 and P32, and example of wired at used key on wake up

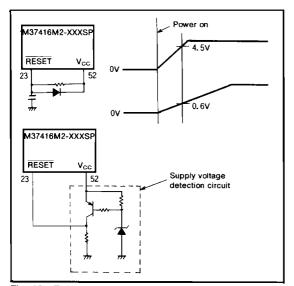

## RESET CIRCUIT

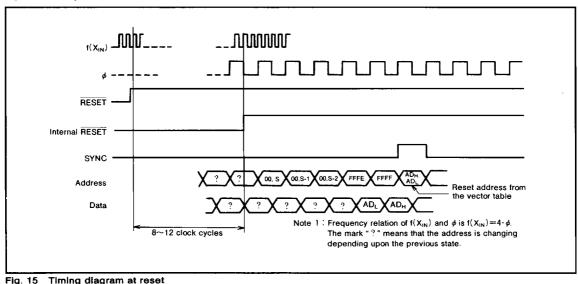

The M37416M2-XXXSP is reset according to the sequence shown in Figure 15. It starts the program from the address formed by using the content of address 1FFF<sub>16</sub> as the high order address and the content of the address 1FFE<sub>16</sub> as the low order address, when the RESET pin is held at "L" level for more than  $2\mu s$  while the power voltage is in the recommended operating condition and the crystal oscillator oscillation is stable and then returned to "H" level. The internal initializations following reset are shown in Figure 14. An example of the reset circuit is shown in Figure 13. When the power on reset is used, the RESET pin must be held "L" until the oscillation of X<sub>IN</sub>-X<sub>OUT</sub> becomes stable.

Example of reset circuit

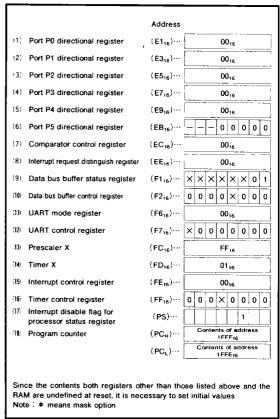

Fig. 14 Internal state of microcomputer at reset

Fig. 15

# MITSUBISHI MICROCOMPUTERS M37416M2-XXXSP/FP

#### SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### I/O PORTS

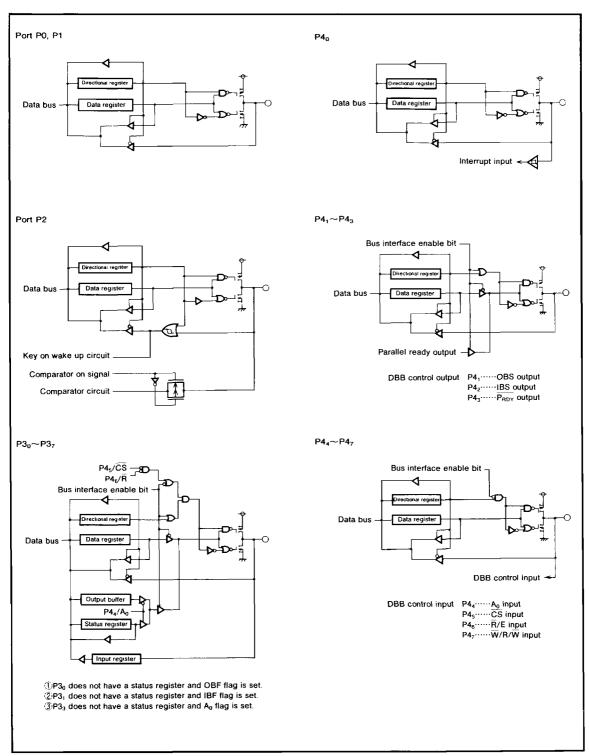

#### (1) Port P0

Port P0 is an 8-bit I/O port with CMOS output.

As shown in the memory map (Figure 1), port P0 can be accessed at zero page memory address  $00E0_{16}$ . Port P0 has a directional register (address  $00E1_{16}$ ) which can be used to program each individual bit as input ("0") or as output ("1"). If the pins are programmed as output, the output data is latched to the port register and then output. When data is read from the output port the output pin level is not read, only the latched data in the port register is read. This allows a previously output value to be read correctly even though the output voltage level is shifted up or down. Pins set as input are in the floating state and the signal levels can thus be read. When data is written into the input port, the data is latched only to the port latch and the pin still remains in the floating state.

#### (2) Port P1

Port P1 has the same function as port P0. The I/O level is TTL compatible.

#### (3) Port P2

Port P2 has the same function as P0. Following the execution of STP or WIT instruction, P2 can be used to generate the "wake up mode". This mode is used to bring the microcomputer back in its normal operating mode after being in the power-down mode. Also this port has comparator function. For more detailes, see the comparator information.

#### (4) Port P3

This is an 8-bit I/O port with function similar to port P0. When slave mode is selected with a program, all ports change to the data bus for the master CPU. In this case, port input/output is unaffected by the directional register. The I/O level is TTL compatible.

#### (5) Port P4

This is an 8-bit input/output port with function similar to port P0. When slave mode is selected with a program, ports P4<sub>1</sub>~P4<sub>7</sub> change to the control bus for the bus interface function. In this case, port input/output is unaffected by the directional register.

Port P4<sub>0</sub> are shared with the external interrupt input pin  $(\overline{INT_0})$ . The  $\overline{INT_0}$  interrupt constantly monitors the status of this port and generates an interrupt at a valide edge. Therefore, if the  $\overline{INT_0}$  interrupt is not used, it must be disabled and if it is used, this port must be set to input. The I/O level of port P4 is TTL compatible except the case that the input level of some ports which function as  $\overline{INT_0}$ . A<sub>0</sub> or  $\overline{CS}$  are CMOS compatible.

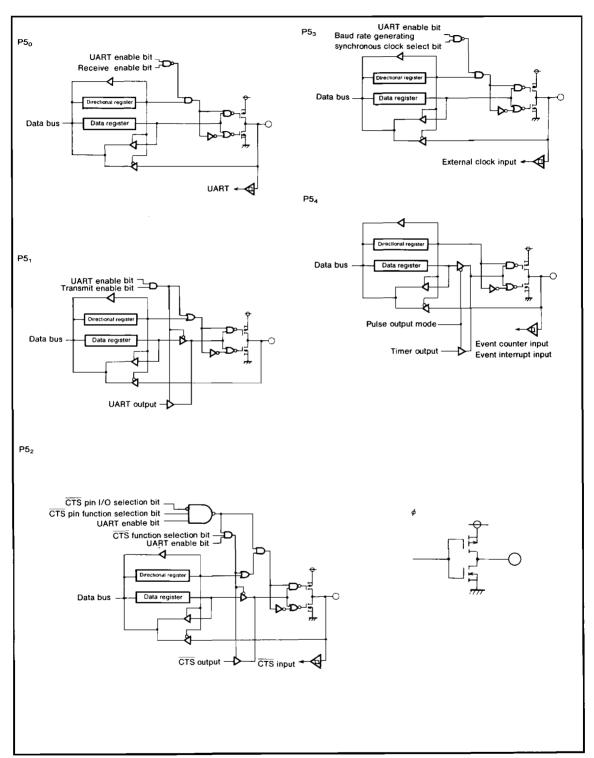

#### (6) Port P5

Port P5 is an 5-bit I/O port with function similar to port P0. All pins have program selectable dual functions. When a UART function is selected, the input and output from pins  $P5_0 \sim P5_3$  are determined by the contents of the UART mode register and UART control register. Port  $P5_4$  is common with CNTR pin.

The I/O level is TTL compatible except the case when some ports which function as RxD,  $\overline{\text{CTS}}$ , CLK and CNTR are CMOS compatible.

#### (7) Clock φ output pin

This is the timing output pin. When selected the main clock  $(X_{\text{IN}}-X_{\text{OUT}})$  as the internal system clock, the clock frequency divided by four is outputed.

"H" is output from this pin when STP or WIT instruction is executed.

# M37416M2-XXXSP/FP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 16 Ports P0~P6 block diagram

# M37416M2-XXXSP/FP

## SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Fig. 17 Ports P5 and  $\phi$  block diagram

## **CLOCK GENERATING CIRCUIT**

The built-in clock generating circuits are shown in Figure 21

When the STP instruction is executed, the oscillation of internal clock  $\phi$  is stopped in the "H" state.

Also, the prescaler X and timer X are loaded with  $FF_{16}$  and  $01_{16}$ , respectively. The oscillator (dividing by 16) is then connected to the prescaler input. This connection is cleard when timer X overflows or the reset is in, as discussed in the timer section.

The oscillator is restarted when an interrupt is accepted. However, the internal clock  $\phi$  keeps its "H" level until timer X overflows.

This is because the oscillator needs a set-up period if a ceramic or a quartz crystal oscillator is used.

When the WIT instruction is executed, the internal clock  $\phi$  stops in the "H" level but the oscillator continues running. This wait state is cleared when an interrupt is accepted. Since the oscillation does not stop, the next instructions are executed at once.

To return from the stop or the wait status, the interrupt enable bit must be set to "1" before executing STP or WIT instruction. Especially, to return from the stop status, the timer X count stop bit (bit 5 of address 00FF<sub>16</sub>) must be set to "0" before executing STP instruction.

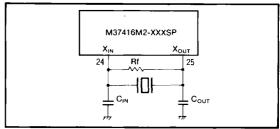

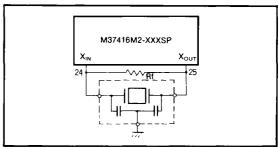

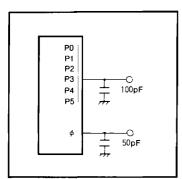

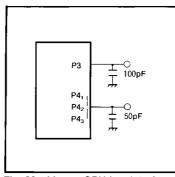

The circuit example using a ceramic oscillator (or a quartz crystal oscillator) is shown in Figures 18 and 19.

The constant capacitance will differ depending on which oscillator is used, and should be set to the manufactures suggested value.

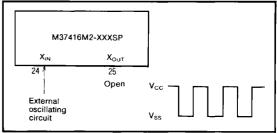

The example of external clock uasge is shown in Figure 20.  $X_{\rm IN}$  is the input, and  $X_{\rm OUT}$  is open.

ig. 18 External ceramic resonator circuit

Fig. 19 External ceramic resonator (capacity built-in type) circuit

Fig. 20 External clock input circuit

Fig. 21 Block diagram of clock generating circuit

## PROGRAMMING NOTES

- (1) The frequency ratio of the timer and the prescaler is 1/(n+1).

- (2) Even though the BBC and BBS instructions are executed after the interrupt request bits are modified (by the program), those instructions are only valid for the contents before the modification. Also, at least one instruction cycle must be used (such as a NOP) between the modification of the interrupt request bits and the execution of the BBC and BBS instructions.

- (3) When the timer X or timer 1 is input the clock except φ/4 or it divided by timer, read the contents of these timers either while the input of these timers are not changing or after counting of timers are stopped.

- (4) After the ADC and SBC instructions are executed (in decimal mode), one instruction cycle (such as a NOP) is needed before the SEC, CLC, or CLD instructions are executed.

- (5) A NOP instruction must be used after the execution of a PLP instruction.

- (6) The STP instruction must be executed after setting timer X count enable bit to enable "0", timer X interrupt enable bit to inhibit ("0"), and timer X interrupt request bit to no request ("0").

- (7) Use the LDA (immidiate, T=1) instruction to modify the interrupt request distinguish register. SEB and CLB instructions can be used only when interrupts in the register are not generated at executing these instructions.

- (8) Do not write any data into an address where no register nor port is assigned.

- (9) The power current is max. 10mA in DC. However, because a rush current and a bus charge-discharge current flow transiently, a bypass capacitor must be connected between V<sub>SS</sub> and V<sub>CC</sub>.

#### DATA REQUIRED FOR MASK ORDERING

Please send the following data for mask orders.

- mask ROM order confirmation form

- · mark specification form

- ROM data ······ EPROM 3 sets

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol          | Parameter                                                                                                                                                                                                                                         | Conditions             | Ratings                   | Unit |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------|------|

| V <sub>CC</sub> | Supply voltage                                                                                                                                                                                                                                    |                        | −0.3~ 7                   | V    |

| Vi              | Input voltage X <sub>IN</sub> , RESET                                                                                                                                                                                                             | W/46                   | -0.3~7                    | V    |

| Vı              | Input voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> , P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>4</sub> , CNV <sub>SS</sub> | Output transistors are | -0.3~V <sub>cc</sub> +0.3 | V    |

| V <sub>O</sub>  | Output voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>7</sub> , X <sub>OUT</sub> , \$\phi\$                         | at "off" state.        | -0.3~V <sub>cc</sub> +0.3 | V    |

| Pd              | Power dissipation                                                                                                                                                                                                                                 | T <sub>a</sub> = 25℃   | 1000(Note 1)              | mW   |

| Topr            | Operating temperature                                                                                                                                                                                                                             |                        | -10~70                    | °C   |

| Tstg            | Storage temperature                                                                                                                                                                                                                               |                        | -40~125                   | C    |

Note 1: 500mW in case of the flat package

## RECOMMENDED OPERATING CONDITIONS

$(V_{CC}=5V\pm10\%, T_a=-10\sim70^{\circ}C \text{ unless otherwise noted})$

| Symbol                | Parameter                                                                                                                                                                                                                               |                    | Limits |                      | Unit |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|----------------------|------|

| Symbol                | Parameter                                                                                                                                                                                                                               | Min.               | Тур.   | Max.                 | Unit |

| Vcc                   | Supply voltage                                                                                                                                                                                                                          | 4.5                | 5      | 5. 5                 | V    |

| Vss                   | Supply voltage                                                                                                                                                                                                                          |                    | 0      | T                    | V    |

| V <sub>IH</sub>       | "H" input voltage RESET, XIN, CNVSS (Note 2)                                                                                                                                                                                            | 0.8V <sub>CC</sub> |        | Vcc                  | V    |

| V <sub>IH</sub>       | "H" input voltage P1 <sub>2</sub> ~P1 <sub>7</sub> , P3 <sub>6</sub> ~P3 <sub>7</sub> , P4 <sub>6</sub> ~P4 <sub>7</sub> , P5 <sub>5</sub> ~P5 <sub>4</sub> , (expect Note 2)                                                           | 2.0                |        | V <sub>cc</sub>      | V    |

| V <sub>IH</sub>       | "H" input voltage P0 <sub>0</sub> ~P0 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> (Note 3)                                                                                                                                          | 0.7V <sub>CC</sub> |        | V <sub>CC</sub>      | V    |

| V <sub>IL</sub>       | "L" input voltage CNV <sub>SS</sub> (Note 2)                                                                                                                                                                                            | 0                  |        | 0.2V <sub>CC</sub>   | v    |

| VIL                   | "L" input voltage P1 <sub>0</sub> ~P1 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> , P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>4</sub> , (expect Note 2)                                                           | 0                  |        | 0.8                  | V    |

| V <sub>IL</sub>       | "L" input voltage P0 <sub>0</sub> ~P0;                                                                                                                                                                                                  | 0                  |        | 0.3V <sub>CC</sub>   | V    |

| VIL                   | "L" input voltage P2 <sub>0</sub> ~P2 <sub>7</sub> (Note 3)                                                                                                                                                                             | Ö                  |        | 0. 26V <sub>CC</sub> | V    |

| VIL                   | "L" input voltage RESET                                                                                                                                                                                                                 | 0                  |        | 0.12V <sub>GC</sub>  | V    |

| V <sub>IL</sub>       | "L" input voltage X <sub>IN</sub>                                                                                                                                                                                                       | 0                  |        | 0.16V <sub>CC</sub>  | V    |

| l <sub>ou(peak)</sub> | "L" peak output current P0 <sub>0</sub> ~P0 <sub>7</sub> . P1 <sub>6</sub> ~P1 <sub>7</sub> . P2 <sub>0</sub> ~P2 <sub>7</sub> . P3 <sub>0</sub> ~P3 <sub>7</sub> . P5 <sub>0</sub> ~P5 <sub>4</sub> . P6 <sub>0</sub> ~P6 <sub>7</sub> |                    |        | 10                   | mA   |

| lou:avg)              | "L" average output current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>4</sub> (Note 4)                        |                    |        | 5                    | mA   |

| I <sub>он</sub> peak: | "H" peak output current $P0_0\sim P0_7,\ P1_0\sim P1_7,$ $P2_0\sim P2_7,\ P3_0\sim P3$ $P5_0\sim P5_4$                                                                                                                                  |                    |        | -10                  | mA   |

| loн:avg)              | "H" average output current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>4</sub> (Note 4)                        |                    |        | -5 I                 | mA   |

| f(XIN)                | Internal clock oscillating frequency                                                                                                                                                                                                    | 1                  |        | 8                    | MH.  |

Note 2 : Ports operating as special function pins  $INT_0(P4_0)$ ,  $A_0(P4_0)$ ,  $\overline{CS}(P4_5)$ ,  $RxD(P5_0)$ ,  $CTS(P5_2)$ ,  $CLK(P5_3)$ , CNTR

- 3 : See comparator characteristics for input voltage as comparator input

- 4 : The total of I<sub>OL</sub> of Port P0, P1, P2 and φ should be 40mA (max.).

The total of IoL of Port P3 and P5 should be 40mA (max)

The total of  $I_{OH}$  of Port P0, P1, P2 and  $\phi$  should be 40mA (max.).

The total of I<sub>OH</sub> of Port P3 and P5 should be 40mA (max.)

# **ELECTRIC CHARACTERISTICS** ( $V_{CC}$ =5 $V\pm10\%$ , $V_{SS}$ = 0 V, $T_a$ =-10 $\sim$ 70°C, $f(X_{IN})$ =8MHz)

| C                     | Description                                                                                                                                                                                                                                                | T                                                    | Test conditions                       |                    | Limits |       |      |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------|--------------------|--------|-------|------|

| Symbol                | Parameter                                                                                                                                                                                                                                                  | rest                                                 |                                       |                    | Тур.   | Max.  | Unit |

| V <sub>OH</sub>       | "H" output voltage $\phi$                                                                                                                                                                                                                                  | $I_{OH} = -2 \text{ mA}$                             |                                       | V <sub>cc</sub> -1 |        |       | v    |

| V <sub>OH</sub>       | "H" output voltage $P0_0 \sim P0_7$ , $P1_0 \sim P1_7$ , $P2_0 \sim P2_7$ . $P3_0 \sim P3_7$ , $P5_0 \sim P5_4$                                                                                                                                            | I <sub>OH</sub> = - 5 mA                             |                                       | V <sub>CC</sub> -1 |        |       | ٧    |

| Vol                   | "L" output voltage $P0_0 \sim P0_7$ , $P1_0 \sim P1_7$ , $P2_0 \sim P2_7$ , $P3_0 \sim P3_7$ , $P5_0 \sim P5_4$                                                                                                                                            | I <sub>OL</sub> =2 mA                                |                                       |                    |        | 0. 45 | ٧    |

| V <sub>OL</sub>       | "L" output voltage P0 <sub>0</sub> ~P0 <sub>7</sub> . P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> . P5 <sub>0</sub> ~P5 <sub>4</sub>                                                            | I <sub>OL</sub> =5 mA                                |                                       |                    |        | 1     | ٧    |

| $v_{\tau+}-v_{\tau-}$ | Hysteresis P2 <sub>0</sub> ~P2 <sub>7</sub> , INT <sub>0</sub> (P4 <sub>0</sub> ), A <sub>0</sub> (P4 <sub>4</sub> ), CS(P4 <sub>5</sub> ),<br>RxD(P5 <sub>0</sub> ), CTS(P5 <sub>2</sub> ), CLK(P5 <sub>3</sub> ), CNTR                                   | Function input leve                                  | 1                                     | 0.3                |        | 1     | ٧    |

| $V_{T+} - V_{T-}$     | Hysteresis RESET                                                                                                                                                                                                                                           |                                                      |                                       |                    |        | 0.7   | V    |

| $V_{\tau+}-V_{\tau-}$ | Hysteresis X <sub>IN</sub>                                                                                                                                                                                                                                 |                                                      |                                       | 0.1                |        | 0.5   | V    |

| I₁∟                   | *L" input current P0 <sub>0</sub> ~P0 <sub>7</sub> . P1 <sub>0</sub> ~P1 <sub>7</sub> . P2 <sub>0</sub> ~P2 <sub>7</sub> . P3 <sub>0</sub> ~P3 <sub>7</sub> . P4 <sub>0</sub> ~P4 <sub>7</sub> . P5 <sub>0</sub> ~P5 <sub>4</sub> . RESET. X <sub>IN</sub> | $\mathbf{v}_{i} = \mathbf{v}_{ss}$                   |                                       | -5                 |        | 5     | μA   |

| I <sub>IH</sub>       | "H" input current P0 <sub>0</sub> ~P0 <sub>7</sub> , P1 <sub>0</sub> ~P1 <sub>7</sub> , P2 <sub>0</sub> ~P2 <sub>7</sub> , P3 <sub>0</sub> ~P3 <sub>7</sub> , P4 <sub>0</sub> ~P4 <sub>7</sub> , P5 <sub>0</sub> ~P5 <sub>4</sub> , RESET, X <sub>IN</sub> | V <sub>I</sub> =V <sub>CC</sub>                      |                                       | 5                  |        | 5     | μА   |

| VRAM                  | RAM retention voltage                                                                                                                                                                                                                                      | At stop mode                                         |                                       | 2                  |        |       | V    |

|                       |                                                                                                                                                                                                                                                            | f(X <sub>IN</sub> )=8MHz At system operation         | comparator not operation              | į                  |        | 10    |      |

| Icc                   | Supply current                                                                                                                                                                                                                                             | f(X <sub>IN</sub> )=8MHz, Con<br>At system operation | nparator is operation,<br>square wave | T                  |        | 15    | mA   |

|                       |                                                                                                                                                                                                                                                            | At stop mode                                         | Ta=25°C                               |                    |        | 1     |      |

|                       |                                                                                                                                                                                                                                                            | (Note 5)                                             | Ta=70℃                                | -                  |        | 10    | μА   |

Note 6  $\stackrel{\cdot}{\cdot}$  Output pin  $\phi$  is open,  $V_{SS}$  is inputs to ports. Comparator conversion is complete condition.

## COMPARATOR CHARACTERISTICS ( $v_{cc}$ =5 $v\pm$ 5%, $v_{cc}$ =0v, $t_a$ =25°C, $t(x_{in})$ =8mHz)

| Parameter                     | 1    | Unit |                       |      |

|-------------------------------|------|------|-----------------------|------|

| Parameter                     | Min. | Тур. | Max.                  | Unit |

| Resolution                    |      | -    | (1/8)V <sub>CC</sub>  | V    |

| Internal analog voltage error |      | !    | ±(1/8)V <sub>CC</sub> | V    |

| Analog input voltage          | 0    |      | V <sub>CC</sub>       | V    |

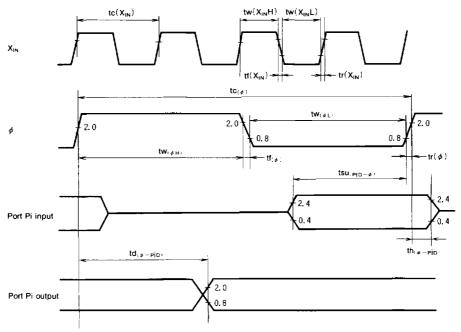

## TIMING REQUIREMENTS

Port/single-chip mode (V<sub>cc</sub>=5V±10%, V<sub>ss</sub>=0V, T<sub>a</sub>=-10~70°C, unless otherwise noted)

| Symbol                            | Parameter                            | Test condition | Limits |      |      | Unit |

|-----------------------------------|--------------------------------------|----------------|--------|------|------|------|

|                                   |                                      | rest continion | Min.   | Typ. | Max. | Unit |

| tsu(POD-#)                        | Port P0 input setup time             |                | 200    |      |      | ns   |

| tsu(P1D-#)                        | Port P1 input setup time             |                | 200    |      |      | ns   |

| t <sub>SU(P2D</sub> -ø)           | Port P2 input setup time             |                | 200    |      |      | ns   |

| t <sub>SU(P3D-#)</sub>            | Port P3 input setup time             |                | 200    |      |      | ns   |

| tsu(P4D+#)                        | Port P4 input setup time             |                | 200    |      |      | ns   |

| t <sub>SU(P5D-#)</sub>            | Port P5 input setup time             |                | 200    |      |      | ns   |

| th(ø                              | Port P0 input hold time              |                | 40     |      |      | ns   |

| th(ø-PID)                         | Port P1 input hold time              |                | 40     |      |      | ns   |

| th(ø-P2D)                         | Port P2 input hold time              | Fig.22         | 40     |      |      | ns   |

| th(ø-Pap)                         | Port P3 input hold time              |                | 40     |      |      | ns   |

| th(øP4D)                          | Port P4 input hold time              |                | 40     |      |      | ns   |

| th(#-P5D)                         | Port P5 input hold time              |                | 40     |      |      | ns   |

| t <sub>C</sub> (X <sub>IN</sub> ) | External clock input cycle time      |                | 125    |      | 1000 | ns   |

| tw(XINL)                          | External clock input "L" pulse width |                | 30     |      |      | ns   |

| tw(XINH)                          | External clock input "H" pulse width |                | 30     |      |      | ns   |

| t <sub>r</sub> (X <sub>IN</sub> ) | External clock rising edge time      |                |        |      | 20   | ns   |

| tf(XIN)                           | External clock falling edge time     |                |        |      | 20   | ns   |

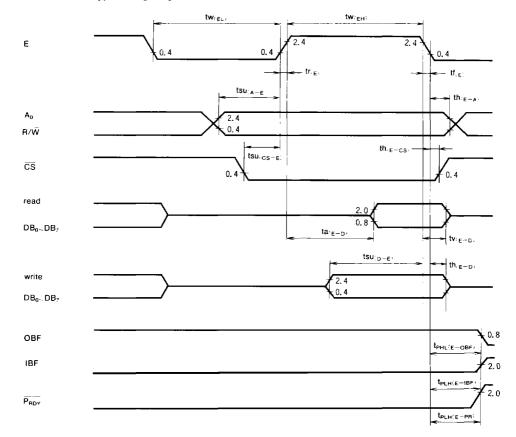

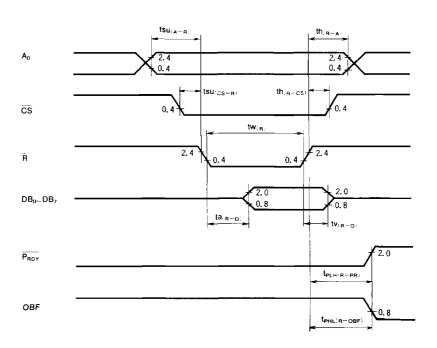

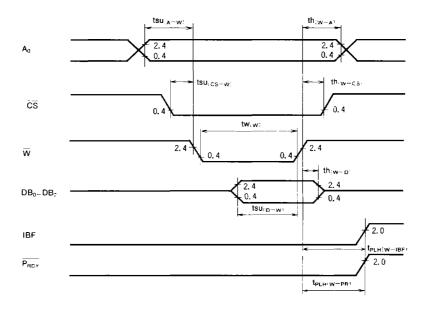

# Master CPU bus interface timing ( $\overline{R}$ and $\overline{W}$ separation type mode)

$(V_{CC}=5V\pm10\%, V_{SS}=0V, T_a=-10\sim70^{\circ}C, unless otherwise noted)$