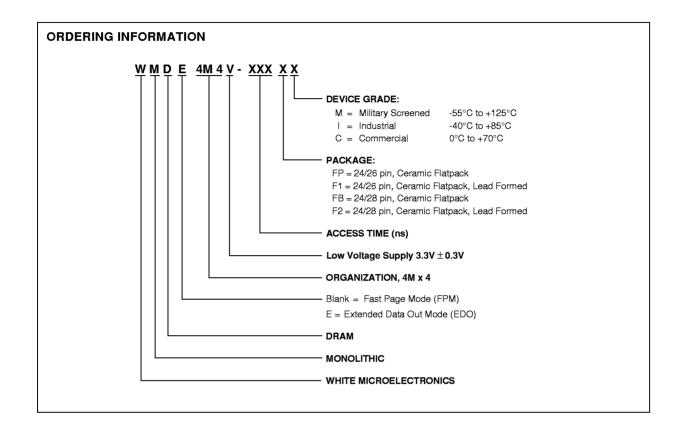

## 4Mx4 CMOS EDO Dynamic RAM 3.3V ADVANCED\*

## **FEATURES**

- Fast Access Time (trac): 70, 80, 100ns

- Power Supply:  $3.3V \pm 0.3V$

- Packaging:

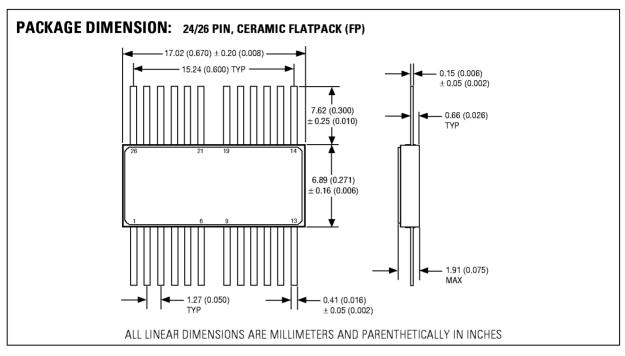

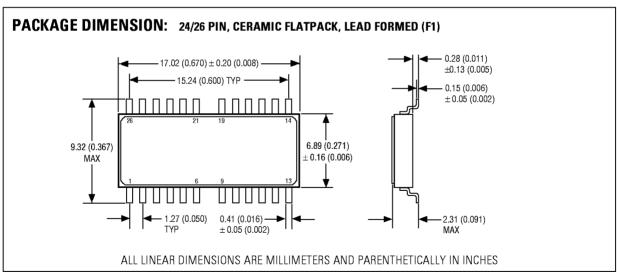

- 24/26 pin Ceramic Flatpack (FP)

- 24/26 pin Ceramic Flatpack, Lead Formed (F1)

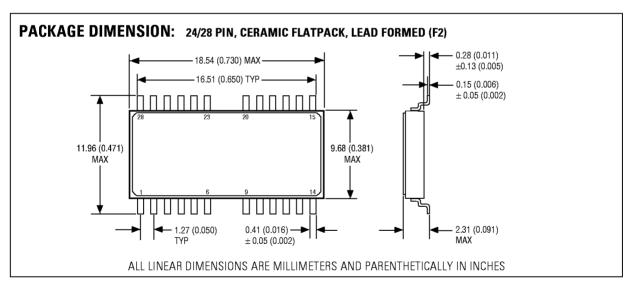

- 24/28 pin Ceramic Flatpack (FB)

- 24/28 pin Ceramic Flatpack, Lead Formed (F2)

- Commercial, Industrial and Military Temperature Ranges

- Extended Data Out (EDO) Page Mode Access Cycle.

- TTL-Compatible Inputs and Outputs

- RAS-Only Refresh

- CAS Before BAS Befresh

- Common I/O

- 2K Cycle Refresh = 32ms

- Low Active Power Dissipation

- Low Standby Power Dissipation

- \* This data sheet describes a product that may or may not be under development and is subject to change or cancellation without notice.

#### PIN CONFIGURATION FOR WMD4M4-XXX 24/26 pin (FP, F1) 24/28 pin (FB, F2) **TOP VIEW TOP VIEW** 26 GND Vcc ∏ 1 28 GND Vcc ∏1 1/00 🛮 2 1/00 🛮 2 25 1/03 27 1/03 24 1/02 1/01 🛮 3 26 1/02 WE 🛮 4 23 | CAS WE I 4 25 T CAS RAS ∏5 22 | OE RAS I 5 24 H OE 21 A9 NC I 6 23 H A9 NC **□**6 A10 **□**8 19 A8 A0 🛮 9 18 T A7 A10 🛮 9 20 A8 17 🛮 A6 A1 **□**10 A0 🛮 10 19 A7 A2 🛮 11 16 A5 A1 🛮 11 18 🛮 A6 A3 🛮 12 15 🛮 A4 A2 🛮 12 17 🛮 A5 14 GND Vcc **□**13 A3 🛮 13 16 🗖 A4 15 GND

## **PIN DESCRIPTION**

| <b>A</b> 0-10   | Address Inputs        |

|-----------------|-----------------------|

| I/ <b>O</b> 0-3 | Data Input/Outputs    |

| ŌĒ              | Output Enable         |

| WE              | Write Enable          |

| RAS             | Row Address Strobe    |

| CAS             | Column Address Strobe |

| Vcc             | +3.3V Power Supply    |

| GND             | Ground                |

| NC              | Not Connected         |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                    | Symbol | Min  | Max  | Unit |

|------------------------------|--------|------|------|------|

| Operating Temperature        | Та     | -55  | +125 | °C   |

| Storage Temperature          | Тѕтс   | -65  | +150 | °C   |

| Short Circuit Output Current | los    |      | 50   | mA   |

| Power Dissipation            | Po     |      | 1    | W    |

| Supply Voltage Range         | Vcc    | -1.0 | 4.6  | ٧    |

| Voltage Range on any Pin*    | VT     | -1.0 | 5.5  | ٧    |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

| Parameter              | Symbol | Min  | Max  | Unit |

|------------------------|--------|------|------|------|

| Supply Voltage         | Vcc    | 3.0  | 3.6  | ٧    |

| Input High Voltage     | Vih    | 2.0  | 5.5  | ٧    |

| Input Low Voltage      | VIL    | -1.0 | +0.8 | ٧    |

| Operating Temp. (Com.) | Та     | 0    | +70  | °C   |

| Operating Temp. (Ind.) | Ta     | -40  | +85  | °C   |

| Operating Temp. (Mil.) | TA     | -55  | +125 | ∘C   |

## CAPACITANCE

$(TA = 25^{\circ}C)$

| Parameter                                        | Symbol | Max | Unit |

|--------------------------------------------------|--------|-----|------|

| Ao-10 Input Capacitance                          | CI(A)  | 6   | pF   |

| RAS and CAS Input Capacitance                    | CI(RC) | 7   | pF   |

| OE Input Capacitance                             | CI(OE) | 7   | pF   |

| WE Input Capacitance                             | CI(WE) | 7   | pF   |

| I/O Capacitance<br>(CAS = Viн to Disable Output) | C1/0   | 8   | pF   |

This parameter is guaranteed by design but not tested.

## **TRUTH TABLE**

|                        |           |                               |     |     |     | Addı | ess | Data In/Out       |

|------------------------|-----------|-------------------------------|-----|-----|-----|------|-----|-------------------|

| Function               |           | RAS                           | CAS | WE  | ŌĒ  | tr   | tc  | 1/00-3            |

| Standby                |           | Н                             | H→X | Χ   | Х   | Х    | Х   | High-Z            |

| Read                   |           | L                             | L   | Н   | L   | ROW  | COL | Data-Out          |

| Early Write            |           | L                             | L   | Ц   | Χ   | ROW  | COL | Data-In           |

| Read Write             |           | L                             | L   | H→L | L→H | ROW  | COL | Data-Out, Data-In |

| EDO-Page-Mode Read     | 1st cycle | L                             | H→L | Н   | L   | ROW  | COL | Data-Out          |

|                        | 2nd cycle | L                             | H→L | Н   | L   | n/a  | COL | Data-Out          |

| EDO-Page-Mode          | 1st cycle | L                             | H→L | ١   | Х   | ROW  | COL | Data-In           |

| Early Write            | 2nd cycle | L                             | H→L | Ш   | Х   | n/a  | COL | Data-In           |

|                        | Any cycle | L                             | L→H | H   | Ш   | n/a  | n/a | Data-Out          |

| EDO-Page-Mode          | 1st cycle | L                             | H→L | H→L | L→H | ROW  | COL | Data-Out, Data-In |

| Read-Write             | 2nd cycle | L                             | H→L | H→L | L→H | n/a  | COL | Data-Out, Data-In |

| RAS-Only Refresh       |           | L                             | Н   | Х   | Х   | ROW  | n/a | High-Z            |

| Hidden Refresh (Read)  |           | $L\rightarrow H\rightarrow L$ | L   | Н   | L   | ROW  | COL | Data-Out          |

| Hidden Refresh (Write) |           | L→H→L                         | L   | Ĺ   | Х   | ROW  | COL | Data-In           |

| CBR Refresh            |           | H→L                           | L   | H   | X   | Х    | Х   | High-Z            |

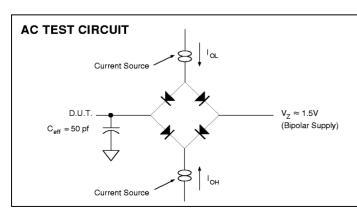

## **AC TEST CONDITIONS**

| Parameter                        | Тур                | Unit |

|----------------------------------|--------------------|------|

| Input Pulse Levels               | VIL = 0, VIH = 2.5 | ٧    |

| Input Rise and Fall              | 5                  | пѕ   |

| Input and Output Reference Level | 1.5                | ٧    |

| Output Timing Reference Level    | 1.5                | ٧    |

#### NOTES:

Vz is programmable from -2V to +7V.

IOL & IOH programmable from 0 to 16mA.

Tester Impedance  $Z_0 = 75 \Omega$ .

Vz is typically the midpoint of VoH and VoL.

IOL & IOH are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

<sup>\*</sup> All voltage values are with respect to GND.

#### DC CHARACTERISTICS

$(Vcc = 3.3V, Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                         | Test Condition                        | Symbol | Min | Max | Units      |

|-----------------------------------|---------------------------------------|--------|-----|-----|------------|

| High Level Output Voltage         | Іон = -2mA                            | Vон    | 2.4 |     | V          |

| Low Level Output Voltage          | loL = 2mA                             | Vol    |     | 0.4 | V          |

| Input Current (Leakage)           | Vi = 0V to +3.6V<br>All others = 0V   | lı     |     | 10  | μА         |

| Output current (Leakage)          | VO = 0V to Vcc, data floating         | lo     |     | 20  | μА         |

| Read or Write Cycle Current (1,2) | Vcc = 3.6V, minimum cycle             | lcc1   |     | 80  | m <b>A</b> |

| Standby Current                   | RAS and CAS = Vін, output open        | lcc2   |     | 2   | m <b>A</b> |

| Average Page Current (1,2)        | RAS = VIL, CAS cycling, minimum cycle | Icc4   |     | 80  | m <b>A</b> |

#### NOTES:

- 1. Icc1 and Icc4 depend on cycle rate.

- 2. Icc1 and Icc4 depend on output loading, specified values are obtained with the output open.

## AC CHARACTERISTICS FOR READ ONLY OPERATIONS

$(Vcc = 3.3V \pm 0.3V, Ta = -55^{\circ}C \text{ to } +125^{\circ}C) \text{ Note } 1$

| Parameter                                                 | Symbol |     | <u>-70</u> |     | <u>30</u> | <u>-100</u> |     | Units |

|-----------------------------------------------------------|--------|-----|------------|-----|-----------|-------------|-----|-------|

|                                                           |        | Min | Max        | Min | Max       | Min         | Max |       |

| Access Time from CAS (2,3)                                | tcac   |     | 20         |     | 20        |             | 25  | ns    |

| Access Time from RAS (2,4)                                | trac   |     | 70         |     | 80        |             | 100 | ns    |

| Column Address Access Time (2)                            | tcaa   |     | 35         |     | 40        |             | 50  | ns    |

| Access Time from CAS Precharge                            | tcpa   |     | 40         |     | 40        |             | 50  | ns    |

| Access Time from $\overline{0E}$ (2)                      | toea   |     | 20         |     | 20        |             | 25  | ns    |

| Output Low Impedance Time from CAS Low (5)                | tcLz   | 0   |            | 0   |           | 0           |     | ns    |

| Output Disable Time after CAS High (6)                    | toff   | 0   | 15         | 0   | 20        | 0           | 20  | ns    |

| Output Disable Time after $\overline{\text{OE}}$ High (6) | toisoe | 0   | 15         | 0   | 20        | 0           | 20  | ns    |

#### NOTES:

- An initial pause of 100μs is required after power-up, followed by eight RAS refresh cycles (RAS-only or CBR with WE High), before proper device operation is

ensured. The eight RAS cycle wake-ups should be repeated any time the tree requirement is exceeded.

- 2. Measured with a load circuit equivalent to 2tttl loads 100pF, Vol = 0.8V and VoH = 2.0V.

- 3. Assumes that trcp ≥ trcp (max).

- Assumes that trcp ≤ trcp (max).

- 5. Guaranteed by design, but not tested.

- 6. torF (max) defines the time at which the output achieves the high impedance state (IOUT ≤ ±10μA) and is not reference to VoH (min) or VoL (max).

#### **AC OPERATIONS AND CHARACTERISTICS**

$(Vcc = 3.3V \pm 0.3V, TA = -55°C to +125°C)$

| Parameter                                   | Symbol | -7  | <u>70</u> | <u>-1</u> | <u>30</u> | -1  | <u>00</u> | Units |

|---------------------------------------------|--------|-----|-----------|-----------|-----------|-----|-----------|-------|

|                                             |        | Min | Max       | Min       | Max       | Min | Max       |       |

| Refresh Cycle                               | tref   |     | 32        |           | 32        |     | 32        | ms    |

| RAS Precharge Time                          | trp    | 50  |           | 60        |           | 80  |           | ns    |

| RAS to CAS Delay Time (9)                   | trco   | 20  | 50        | 20        | 60        | 25  | 75        | ns    |

| Delay CAS High to RAS Low                   | tcrp   | 5   |           | 5         |           | 5   |           | ns    |

| CAS Precharge Time (Non Page Mode)          | tcp    | 10  |           | 10        |           | 10  |           | ns    |

| Column Address Delay Time from RAS Low (10) | trad   | 15  | 35        | 15        | 40        | 20  | 50        | ns    |

| Row Address Setup Time                      | tasr   | 0   |           | 0         |           | 0   |           | ns    |

| Column Address Setup Time (11)              | tasc   | 0   |           | 0         |           | 0   |           | ns    |

| Row Address Hold Time                       | trah   | 10  |           | 10        |           | 15  |           | пѕ    |

| Column Address Hold Time                    | tcah   | 15  |           | 15        |           | 20  |           | пѕ    |

| Transition Time (12)                        | tт     | 2   | 30        | 2         | 30        | 2   | 30        | ns    |

#### NOTES:

- 7. The timing requirements are assumed  $t_T = 5$ ns.

- 8. ViH (min) and ViL (max) are reference levels for measuring timing of input signals.

- 9. trcD (max) is specified as a reference point only. If trcD is less than trcD (max), access time is trac. If trcD is greater than trcD (max), access time is defined as tcac and tcaa as shown in note 3.

- 10. trap (max) is specified as a reference point only. If trap ≥ trap (max), access time is assumed by tcaa for read cycle.

- 11. tasc (max) is specified as a reference point only of address access time.

- 12. tT is measured between ViH (min) and VIL (max).

## **AC CHARACTERISTICS FOR READ OPERATIONS**

$(Vcc = 3.3V \pm 0.3V, Ta = -55^{\circ}C \text{ to } +125^{\circ}C) \text{ Notes } 1, 13, 14$

| Parameter                                       | Symbol | -5  | <u>-70</u> <u>-80</u> |     | 30      | <u>-1</u> | 00      | Units |

|-------------------------------------------------|--------|-----|-----------------------|-----|---------|-----------|---------|-------|

|                                                 |        | Min | Max                   | Min | Max     | Min       | Max     |       |

| Read Cycle Time                                 | trc    | 130 |                       | 150 |         | 190       |         | ns    |

| RAS Low Pulse Width                             | tras   | 70  | 100,000               | 80  | 100,000 | 100       | 100,000 | пѕ    |

| CAS Low Pulse Width                             | tcas   | 15  | 100,000               | 20  | 100,000 | 25        | 100,000 | пѕ    |

| CAS Hold Time after RAS Low                     | tcsH   | 55  |                       | 65  |         | 85        |         | пѕ    |

| RAS Hold Time after CAS Low                     | trsh   | 15  |                       | 15  |         | 20        |         | пѕ    |

| Read Setup Time before CAS Low                  | trcs   | 0   |                       | 0   |         | 0         |         | пѕ    |

| Read Hold Time after CAS High (1)               | trch   | 0   |                       | 0   |         | 0         |         | пѕ    |

| Read Hold Time after RAS High (1)               | trrh   | 0   |                       | 0   |         | 0         |         | пѕ    |

| Column Address to RAS Setup                     | tral   | 35  |                       | 40  |         | 50        |         | пѕ    |

| Precharge to CAS Active                         | trpc   | 5   |                       | 5   |         | 5         |         | пѕ    |

| Delay Time, Data to $\overline{\text{OE}}$ Low  | TDOEL  | 0   |                       | 0   |         | 0         |         | пѕ    |

| Delay Time, $\overline{\text{OE}}$ High to Data | toehd  | 20  |                       | 20  |         | 25        |         | ns    |

## NOTES:

1. Either trich or trink must be satisfied for a read cycle.

#### **AC CHARACTERISTICS FOR WRITE OPERATIONS**

$(Vcc = 3.3V \pm 0.3V, TA = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                       | Symbol | -   | <u>70</u> | <u>-80</u> |         | <u>-100</u> |         | Units |

|-------------------------------------------------|--------|-----|-----------|------------|---------|-------------|---------|-------|

|                                                 |        | Min | Max       | Min        | Max     | Min         | Max     |       |

| Write Cycle Time                                | twc    | 130 |           | 150        |         | 190         |         | ns    |

| RAS Low Pulse Width                             | tras   | 70  | 100,000   | 80         | 100,000 | 100         | 100,000 | п\$   |

| CAS Low Pulse Width                             | tcas   | 15  | 100,000   | 20         | 100,000 | 25          | 100,000 | п\$   |

| CAS Hold Time after RAS Low                     | tcsн   | 55  |           | 65         |         | 85          |         | пѕ    |

| RAS Hold Time after CAS Low                     | trsh   | 15  |           | 15         |         | 20          |         | пѕ    |

| Write Setup Time before CAS Low (1)             | twcs   | 0   |           | 0          |         | 0           |         | пѕ    |

| Write Hold Time after CAS Low                   | twch   | 12  |           | 15         |         | 20          |         | пѕ    |

| CAS Hold Time after WE Low                      | tcwL   | 15  |           | 20         |         | 25          |         | пѕ    |

| RAS Hold Time after WE Low                      | trwL   | 15  |           | 20         |         | 25          |         | пѕ    |

| Write Pulse Width                               | twp    | 12  |           | 15         |         | 20          |         | пş    |

| Data Setup Time (1)                             | tos    | 0   |           | 0          |         | 0           |         | пş    |

| Data Hold Time after CAS Low (1)                | tон    | 12  |           | 15         |         | 20          |         | пѕ    |

| Delay Time, $\overline{\text{OE}}$ High to Data | toehd  | 20  |           | 20         |         | 25          |         | пѕ    |

| OE Hold Time after WE Low                       | thwoe  | 20  |           | 20         |         | 25          |         | пѕ    |

twcs, trwo, tcwo, and tawo do not define the limits of operation, but are included as electrical characteristics only.

When twcs ≥ twcs (min), an early write cycle is performed, and the data output keeps the high-impedance state. When trwo ≥ trwo (min), tcwo ≥ tcwo (min) and tawo ≥ tawo (min), a read write cycle is performed, and the data of the selected address will be read out on the data output. If neither of the above conditions is satisfied, the condition of the output (at the access time and until CAS goes back to Viii) is indeterminate.

## **AC CHARACTERISTICS FOR READ-WRITE OPERATIONS**

$(Vcc = 3.3V \pm 0.3V. Ta = -55^{\circ}C to +125^{\circ}C)$

| Parameter                                         | Symbol | -   | <u>70</u> | -   | <u>80</u> | -1  | 100     | Units |

|---------------------------------------------------|--------|-----|-----------|-----|-----------|-----|---------|-------|

|                                                   |        | Min | Max       | Min | Max       | Min | Max     |       |

| Read-ModifyWrite Cycle Time                       | trwc   | 180 |           | 200 |           | 220 |         | пѕ    |

| RAS Low Pulse Width                               | trasrw | 70  | 100,000   | 80  | 100,000   | 100 | 100,000 | пѕ    |

| CAS Low Pulse Width                               | tcasrw | 20  | 100,000   | 20  | 100,000   | 25  | 100,000 | пѕ    |

| CAS Hold Time after RAS Low                       | tcshrw | 55  |           | 65  |           | 85  |         | nş    |

| RAS Hold Time after CAS Low                       | trshrw | 15  |           | 15  |           | 20  |         | ns    |

| Read Setup Time before CAS Low                    | trcs   | 0   |           | 0   |           | 0   |         | пѕ    |

| <del>CAS</del> Low to <del>WE</del> Low Delay (1) | tcwp   | 45  |           | 45  |           | 50  |         | ns    |

| RAS Low to WE Low Delay (1)                       | trwd   | 90  |           | 105 |           | 120 |         | ns    |

| CAS Hold after WE Low                             | tcwL   | 15  |           | 20  |           | 25  |         | ns    |

| RAS Hold after WE Low                             | trwl   | 15  |           | 20  |           | 25  |         | ns    |

| Write Pulse Width                                 | twp    | 12  |           | 15  |           | 20  |         | ns    |

| Data Setup Time                                   | tos    | 0   |           | 0   |           | 0   |         | ns    |

| Data Hold Time after CAS Low                      | toн    | 12  |           | 15  |           | 20  |         | ns    |

| Address to WE Low Delay (1)                       | tawd   | 65  |           | 70  |           | 80  |         | пѕ    |

| Delay Time, $\overline{\text{OE}}$ High to Data   | toehd  | 20  |           | 20  |           | 25  |         | ns    |

| OE Hold Time after Write Low                      | thwoe  | 20  |           | 20  |           | 25  |         | ns    |

<sup>1.</sup> twos, trwo, towo, and tawo do not define the limits of operation, but are included as electrical characteristics only.

When twos ≥ twos (min), an early write cycle is performed, and the data output keeps the high-impedance state. When trwo ≥ trwo (min), towo ≥ trwo (min) and tawo ≥ tawo (min), a read write cycle is performed, and the data of the selected address will be read out on the data output. If neither of the above conditions is satisfied, the condition of the output (at the access time and until CAS goes back to Viii) is indeterminate.

## **PAGE MODE OPERATIONS**

$(Vcc = 3.3V \pm 0.3V, TA = -55^{\circ}C \text{ to } +125^{\circ}C)$

| Parameter                                 | Symbol | <u>-70</u> |         | <u>-80</u> |         | <u>-100</u> |         | Units |

|-------------------------------------------|--------|------------|---------|------------|---------|-------------|---------|-------|

|                                           |        | Min        | Max     | Min        | Max     | Min         | Max     |       |

| EDO Page Mode Cycle Time                  | tpc    | 35         |         | 40         |         | 50          |         | пѕ    |

| EDO Page Mode for R/W, R/M/W Cycle Time   | tprwc  | 85         |         | 90         |         | 100         |         | пѕ    |

| RAS Low Pulse Width for Read, Write Cycle | trasp  | 70         | 100,000 | 80         | 100,000 | 100         | 100,000 | пѕ    |

| CAS Low Pulse Width for Read Cycle        | tcas   | 15         | 100,000 | 20         | 100,000 | 25          | 100,000 | пѕ    |

| CAS Pulse Width (Page Mode)               | tcp    | 10         |         | 10         |         | 10          |         | пѕ    |

| RAS Hold Time after CAS Low               | trsh   | 15         |         | 15         |         | 20          |         | пѕ    |

## WRITE REFRESH OPERATIONS \*

$(Vcc = 3.3V \pm 0.3V, TA = -55^{\circ}C \text{ to } +125^{\circ}C)$

| Parameter                            | Symbol | <u>-70</u> |     | <u>-80</u> |     | <u>-100</u> |     | Units |

|--------------------------------------|--------|------------|-----|------------|-----|-------------|-----|-------|

|                                      |        | Min        | Max | Min        | Max | Min         | Max |       |

| CAS Setup for CAS before RAS Refresh | tcsr   | 5          |     | 10         |     | 10          |     | ns    |

| CAS Hold for CAS before RAS Refresh  | tchr   | 15         |     | 15         |     | 15          |     | пѕ    |

| Precharge to CAS Active              | trpc   | 5          |     | 5          |     | 5           |     | ns    |

| Write Setup Time                     | twrp   | 10         |     | 10         |     | 10          |     | ns    |

| Write Hold Time                      | twr    | 10         |     | 10         |     | 10          |     | ns    |

<sup>\*</sup> Eight or more CAS before RAS cycles are necessary for proper operation of  $\overline{\text{CAS}}$  before  $\overline{\text{RAS}}$  refresh mode.

## **GENERAL DESCRIPTION**

The 4M x 4 DRAM is a randomly accessed, solid-state memory containing 16,777,216 bits organized in a x4 configuration.  $\overline{RAS}$  is used to latch the row address. Once the page has been opened by  $\overline{RAS}$ ,  $\overline{CAS}$  is used to latch the column address. Read and Write cycles are selected with the  $\overline{WE}$  input. A logic High on  $\overline{WE}$  dictates Read mode while a logic Low on  $\overline{WE}$  dictates Write mode. During a Write cycle, data-in (I) is latched by the falling edge of  $\overline{WE}$  or  $\overline{CAS}$ , whichever occurs last. If  $\overline{WE}$  goes Low prior to  $\overline{CAS}$  going Low, the output pins remain open (High-Z) until the next  $\overline{CAS}$  cycle, regardless of  $\overline{OE}$ .

A logic High on  $\overline{WE}$  dictates Read mode while logic Low on  $\overline{WE}$  dictates Write mode. During a Write cycle, data-in is latched by the falling edge of  $\overline{WE}$  or  $\overline{CAS}$ , whichever occurs last. An Early Write occurs when  $\overline{WE}$  is taken Low prior to  $\overline{CAS}$  falling. A Late Write or Read-Modify-Write occurs when  $\overline{WE}$  falls after  $\overline{CAS}$  was taken Low. During Early Write cycles, the outputs (0) will remain High-Z regardless of the state of  $\overline{OE}$ . During Late Write or Read-Modify-Write cycles,  $\overline{OE}$  must be taken High to disable the data outputs prior to applying input data. If a Late Write or Read-Modify-Write is attempted while keeping  $\overline{OE}$  Low, no write will occur, and the data outputs will drive read data from the accessed location.

The four data inputs and the four data outputs are routed through four pins using common I/O, and pin direction is controlled by  $\overline{WE}$  and  $\overline{OE}$ .

## **PAGE ACCESS**

Page operations allow faster data operations (Read, Write or Read-Modify-Write) within a row-address-defined page boundary. The Page cycle is always initiated with a row address strobed-in by  $\overline{RAS}$  followed by a column address strobed-in by  $\overline{CAS}$ .  $\overline{CAS}$  may be toggled-in by holding  $\overline{RAS}$  Low and strobing-in different column addresses, thus executing faster memory cycles. Returning  $\overline{RAS}$  High terminates the Page Mode operation, i.e. closes the page.

## **EDO PAGE MODE**

The 4M x 4 EDO DRAM provides EDO Page Mode, which is an accelerated Fast Page Mode cycle. The primary advantage of EDO is the availability of data-out even after  $\overline{CAS}$  returns High. EDO allows  $\overline{CAS}$  precharge time (tcr) to occur without the output data going invalid. This elimination of  $\overline{CAS}$  output control allows pipeline Reads.

Fast Page Mode DRAMs have traditionally turned the output buffers off (High-Z) with the rising edge of CAS. EDO Page Mode DRAMs operate like Fast Page Mode DRAMs, except data will remain valid or become valid after CAS goes High during Reads, provided RAS and OE are held Low. If OE is pulsed while RAS and CAS are Low, data will toggle from valid data to High-Z and back to the same valid data. If OE is toggled or pulsed after CAS goes High while RAS remains Low, data will transition to and remain High-Z. WE can also perform the function of disabling the output devices under certain conditions.

During an application, if the I/O outputs are wire OR'd  $\overline{OE}$  must be used to disable idle banks of DRAMs. Alternatively, pulsing  $\overline{WE}$  to the idle banks during  $\overline{CAS}$  high time will also High-Z the outputs. Independent of  $\overline{OE}$  control, the outputs will disable after toff, which is referenced from the rising edge of  $\overline{RAS}$  or  $\overline{CAS}$ , whichever occurs last.

## REFRESH

Preserve correct memory cell data by maintaining power and executing any  $\overline{RAS}$  cycle (Read, Write) or  $\overline{RAS}$  refresh CYCLE ( $\overline{RAS}$ -only, CBR, or Hidden) so that all combinations of  $\overline{RAS}$  addresses (2,048) are executed within tREF (max), regardless of sequence. The CBR Refresh cycle will invoke the internal refresh counter for automatic  $\overline{RAS}$  addressing.

## **STANDBY**

Returning RAS and CAS High terminates a memory cycle and decreases chip current to a reduced standby level. The chip is preconditioned for the next cycle during the RAS High time.

# PACKAGE DIMENSION: 24/28 PIN, CERAMIC FLATPACK (FB) 18.54 (0.730) MAX 3.81 (0.150) 0.15 (0.006) ŤΥΡ ± 0.05 (0.002) 7.62 (0.300) 0.48 (0.019) 0.25 (0.010) 9.68 (0.381) MAX 1.91 (0.075) MAX 1.27 (0.050) TYP - 0.41 (0.016) ± 0.05 (0.002) ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES