# **DS1077** EconOscillator/Divider

### www.maxim-ic.com

## **FEATURES**

- Processor-controlled or standalone solidstate oscillator

- Frequency changes on-the-fly

- Dual low-iitter, synchronous fixed frequency outputs

- 2-wire serial interface

- Frequency outputs 8.1kHz to 133MHz

- $\pm 0.5\%$  variation over temp (+25°C to +70°C)

- $\pm 0.5\%$  initial tolerance

- Nonvolatile (NV) frequency settings

- Single 5V supply

- No external components

- Power-down mode

- Synchronous output gating

## STANDARD FREQUENCY OPTION

| Note: x denotes | s package option |         |

|-----------------|------------------|---------|

| DS1077x-133     | 133.333MHz to    | 16.2kHz |

| DS1077x-125     | 125.000MHz to    | 15.2kHz |

| DS1077x-120     | 120.000MHz to    | 14.6kHz |

| DS1077x-100     | 100.000MHz to    | 12.2kHz |

| DS1077x-66      | 66.666MHz to     | 8.1kHz  |

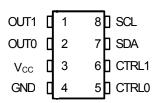

## PIN ASSIGNMENT

150mil SO 118mil µSOP Package

### PIN DESCRIPTION

| OUT1     | <ul> <li>Main Oscillator Output</li> </ul> |

|----------|--------------------------------------------|

| OUT0     | - Reference Output                         |

| $V_{CC}$ | - Power Supply Voltage                     |

| GND      | - Ground                                   |

| CTRL1    | <ul> <li>Control Pin for OUT1</li> </ul>   |

| CTRL0    | - Control Pin for OUT0                     |

| SDA      | - 2-Wire Serial Data                       |

|          | Input/Output                               |

| SCL      | - 2-Wire Serial Clock                      |

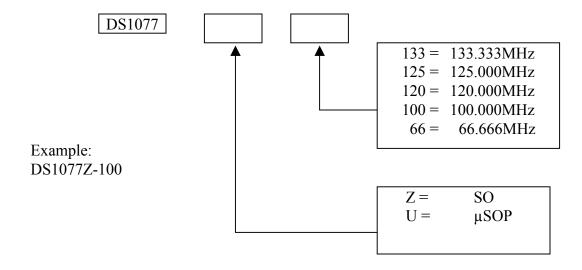

### ORDERING INFORMATION

Note: XXX denotes frequency option 8-Pin 150mil SO DS1077Z-XXX DS1077U-XXX 8-Pin 118mil µSOP

### DESCRIPTION

The DS1077 is a dual-output, programmable, fixed-frequency oscillator requiring no external components for operation. The DS1077 can be used as a processor-controlled frequency synthesizer or as a standalone oscillator. The two synchronous output operating frequencies are user-adjustable in submultiples of the master frequency through the use of two on-chip programmable prescalers and a divider. The specific output frequencies chosen are stored in NV (EEPROM) memory. The DS1077 defaults to these values upon power-up.

The DS1077 features a 2-wire serial interface that allows in-circuit on-the-fly programming of the programmable prescalers (P0 & P1) and divider (N) with the desired values being stored in NV (EEPROM) memory. Design changes can be accommodated in-circuit on-the-fly by simply programming different values into the device (or reprogramming previously programmed devices). Alternatively, for fixed frequency applications, previously programmed devices can be used and no connection to the serial interface is required. Pre-programmed devices can be ordered in customerrequested frequencies.

The DS1077 is available in 8-pin SO or µSOP packages, allowing the generation of a clock signal easily, economically, and using minimal board area. Chip-scale packaging is also available on request.

1 of 21

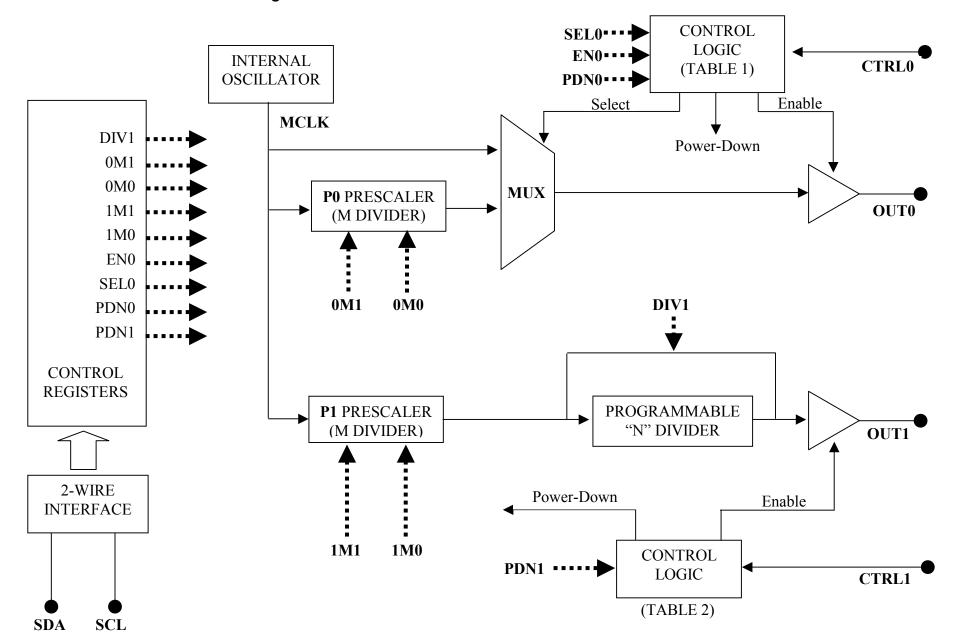

# **BLOCK DIAGRAM 1077** Figure1

### **OVERVIEW**

A block diagram of the DS1077 is shown in Figure 1. The DS1077 consists of four major components: 1) Internal Master Oscillator, 2) Prescalers, 3) Programmable Divider, and 4) Control Registers.

The internal oscillator is factory-trimmed to provide a master frequency (Master CLK) that can be routed directly to the outputs (OUT0 & OUT1) or through separate prescalers (P0 & P1). OUT1 can also be routed through an additional divider (N).

The Prescaler (P0) divides the Master Clock by 1, 2, 4, or 8 to be routed directly to the OUT0 pin.

The Prescaler (P1) divides the Master Clock by 1, 2, 4, or 8, which can be routed directly to the OUT1 pin or to the Divider (N) input, which is then routed to the OUT1 pin.

The Programmable Divider (N) divides the Prescaler Output (P1) by any number selected between 2 and 1025 to provide the Main Output (OUT1) or it can be bypassed altogether by use of the DIV1 register bit. The value of N is stored in the DIV register.

The Control Registers are user-programmable through a 2-wire serial interface to determine operating frequency (values of P0, P1, & N) and modes of operation. The register values are stored in EEPROM and therefore only need to be programmed to alter frequencies and operating modes.

## PIN DESCRIPTIONS

**Output 1 (OUT1)**—This pin is the main oscillator output; its frequency is determined by the control register settings for the prescaler P1 (mode bits 1M1 & 1M0) and divider N (DIV word).

**Output 0 (OUT0)**—A reference output, OUT0, is taken from the output of the reference select Mux. Its frequency is determined by the control register settings for CTRL0 and values of Prescaler P0 (mode bits 0M1 & 0M0) (see Table 1).

**Control Pin 0 (CTRL0)**—A multifunctional input pin that can be selected as a MUX SELECT, OUTPUT ENABLE and/or a POWER-DOWN. Its function is determined by the user-programmable control register values EN0, SEL0, and PDN0 (see Table 1).

**Control Pin 1 (CTRL1)**—A multifunctional input pin that can be selected as a OUTPUT ENABLE and/or a POWER-DOWN. Its function is determined by the user-programmable control register value of PDN1 (see Table 2).

Serial Data Input/Output (SDA)—Input/Output pin for the 2-wire serial interface used for data transfer.

**Serial Clock Input (SCL)**—Input pin for the 2-wire serial interface used to synchronize data movement on the serial interface.

## **DEVICE MODE USING OUT0** Table 1

| ENO<br>(BIT) | SEL0<br>(BIT) | PDN0<br>(BIT) | CTRL0<br>(PIN) | OUTO<br>(PIN) | CTRL0<br>FUNCTION | DEVICE<br>MODE |

|--------------|---------------|---------------|----------------|---------------|-------------------|----------------|

| 0            | 0             | 0             | 1              | HI-Z          | POWER-            | POWER-DOWN     |

| 0            | 0             | 0             | 0              | HI-Z          | DOWN*             | ACTIVE         |

| 0            | 1             | 0             | 1              | MCLK/M        | MUX SELECT        | ACTIVE         |

| U            | 1             | U             | 0              | MCLK          | MOX SELECT        | ACTIVE         |

| 1            | 0             | 0             | 1              | HI-Z          | OUTPUT            | ACTIVE         |

| 1            | U             | U             | 0              | MCLK          | ENABLE            | ACTIVE         |

| 1            | 1             | 0             | 1              | HI-Z          | OUTPUT            | ACTIVE**       |

| 1            | 1             | U             | 0              | MCLK/M        | ENABLE            | ACTIVE         |

| X            | 0             | 1             | 1              | HI-Z          | POWER-            | POWER-DOWN     |

| Λ            | U             | 1             | 0              | MCLK          | DOWN              | ACTIVE         |

| X            | 1             | 1             | 1              | HI-Z          | POWER-            | POWER-DOWN     |

| Λ            | 1             | 1             | 0              | MCLK/M        | DOWN              | ACTIVE         |

<sup>\*</sup>This mode is for applications where OUT0 is not used, but CTRL0 is used as a device shutdown.

## **DEVICE MODE USING OUT1** Table 2

| PDN1<br>(BIT) | CTRL1<br>(PIN) | CTRL1<br>FUNCTION | OUT1    | DEVICE MODE |

|---------------|----------------|-------------------|---------|-------------|

| 0             | 0              | OUTPUT ENABLE     | OUT CLK | ACTIVE**    |

| 0             | 1              | OUTPUT ENABLE     | HI-Z    | ACTIVE**    |

| 1             | 0              | POWER-DOWN        | OUT CLK | ACTIVE      |

| 1             | 1              | POWER-DOWN        | HI-Z    | POWER-DOWN  |

<sup>\*\*</sup>Default Condition

### NOTE:

Both CTRL0 and CTRL1 can be configured as power-downs. They are internally "OR" connected so that either of the control pins can be used to provide a power-down function for the whole device, subject to appropriate settings of the PDN0 and PDN1 register bits (see Table 3).

<sup>\*\*</sup>Default Condition

## SHUTDOWN CONTROL WITH PDN0 AND PDN1 Table 3

| PDN0  | PDN1  | SHUTDOWN CONTROL |

|-------|-------|------------------|

| (BIT) | (BIT) |                  |

| 0     | 0     | NONE*            |

| 0     | 1     | CTRL1            |

| 1     | 0     | CTRL0            |

| 1     | 1     | CTRL0 OR CTRL1   |

<sup>\*</sup>CTRL0 performs a power-down if SEL0 and EN0 are both 0 (see Table 1).

## REGISTER FUNCTIONS

The user programmable registers can be programmed by the user to determine the mode of operation (MUX), operating frequency (DIV), and bus settings (BUS). Details of how these registers are programmed can be found in a later section; in this section the functions of the registers are described. The register settings are nonvolatile, the values being stored automatically or as required in EEPROM when the registers are programmed via the SDA and SCL pins.

## **MUX WORD**

| N       | MS | В    |      |      |     |     |     | LSB | MSB |      |   |   |   |   | LS | В |

|---------|----|------|------|------|-----|-----|-----|-----|-----|------|---|---|---|---|----|---|

| Name    | *  | PDN1 | PDN0 | SEL0 | EN0 | 0M1 | 0M0 | 1M1 | 1M0 | DIV1 | - | - | ı | - | -  | - |

| Default | 0  | 0    | 0    | 1    | 1   | 0   | 0   | 0   | 0   | 0    | X | X | X | X | X  | X |

| setting |    |      |      |      |     |     |     |     |     |      |   |   |   |   |    |   |

first data byte second data byte

## DIV1 (bit)

This bit allows the output of the Prescaler P1 to be routed directly to the OUT1 pin (DIV1 = 1). The N divider is bypassed so the programmed value of N is ignored. If DIV1 = 0 (default) the N divider functions normally.

## 0M1, 0M0, 1M1, 1M0 (bits)

These bits set the prescalers P0 and P1, to divide by 1, 2, 4, or 8 (see Table 4).

## PRESCALER DIVISOR M SETTINGS Table 4

| 0M1 | 0М0 | Prescaler<br>P0 Divisor<br>"M" | 1M1 | 1M0 | Prescaler<br>P1 Divisor<br>"M" |

|-----|-----|--------------------------------|-----|-----|--------------------------------|

| 0   | 0   | 1**                            | 0   | 0   | 1**                            |

| 0   | 1   | 2                              | 0   | 1   | 2                              |

| 1   | 0   | 4                              | 1   | 0   | 4                              |

| 1   | 1   | 8                              | 1   | 1   | 8                              |

<sup>\*\*</sup>Default Condition

<sup>\*</sup>This bit must be set to zero.

DS1077

EN0 (bit) (Default EN0 = 1)

1) If EN0 = 1 and PDN0 = 0 the CTRL0 pin functions as an Output Enable for OUT0, the frequency of the output being determined by the SEL0 bit.

- 2) If PDN0 = 1, the EN0 bit is ignored, CTRL0 will function as a power-down, and output OUT0 will always be enabled on power-up, its frequency being determined by the SEL0 bit.

- 3) If EN0 = 0 the function of CTRL0 is determined by the SEL0 and PDN0 bits (see Table 1).

SEL0 (Default SEL0 = 1)

- 1) If SEL0 = 1 and EN0 = PDN0 = 0, the CTRL0 pin determines the state of the MUX (i.e., the output frequency of OUT0).

- 2) If CTRL0 = 0 the output will be the Master clock frequency.

- 3) If CTRL0 = 1 the output will be the output frequency of the M prescaler.

- 4) If either EN0 or PDN0 = 1 then SEL0 determines the frequency of OUT0 when it is enabled.

- 5) If SEL0 = 0 the output will be the Master clock frequency.

- 6) If SEL0 = 1 the output will be the output frequency of the M prescaler (see Table 1).

PDN0 (Default PDN0 = 0)

- 1) This bit (if set to 1) causes CTRL0 to perform a power-down function, regardless of the setting of the other bits.

- 2) If PDN0 = 0 the function of CTRL0 is determined by the values of EN0 and SEL0.

### NOTE:

When EN0 = SEL0 = PDN0 = 0, CTRL0 also functions as a power-down. This is a special case where all the OUT0 circuitry is disabled even when the device is powered up for power to saving when OUT0 is not used (see Table 1).

PDN1 (Default PDN1 = 0)

- 1) If PDN1 = 1, CTRL1 will function as a power-down.

- 2) If PDN1 = 0, CTRL1 functions as an output enable for OUT1 only (see Table 2.)

## NOTE (ON OUTPUT ENABLE AND POWER-DOWN):

- 1) Both enables are "smart" and wait for the output to be low before going to Hi-Z.

- 2) Power-down sequence first disables both outputs before powering down the device.

- 3) On power-up the outputs are disabled until the clock has stabilized (~8000 cycles).

- 4) In power-down mode, the device cannot be programmed.

- 5) A power-down command must persist for at least two cycles of the lowest output frequency plus 10µs.

## **DIV WORD**

| MSB |    |    |    |    |    |    | LSB | MSB |    |   |   |   |   |   | LSB |

|-----|----|----|----|----|----|----|-----|-----|----|---|---|---|---|---|-----|

| N9  | N8 | N7 | N6 | N5 | N4 | N3 | N2  | N1  | N0 | X | X | X | X | X | X   |

first data byte

second data byte

## Ν

These ten bits determine the value of the programmable divider (N). The range of divisor values is from 2 to 1025, and is equal to the programmed value of N plus 2 (see Table 5).

## PROGRAMMABLE DIVISOR N VALUES Table 5

| BIT VALUE       | DIVISOR (N) |  |  |  |  |  |

|-----------------|-------------|--|--|--|--|--|

| 0 000 000 000** | 2           |  |  |  |  |  |

| 0 000 000 001   | 3           |  |  |  |  |  |

| -               | -           |  |  |  |  |  |

| -               | -           |  |  |  |  |  |

| -               | -           |  |  |  |  |  |

| -               | -           |  |  |  |  |  |

| 1 111 111 111   | 1025        |  |  |  |  |  |

<sup>\*\*</sup>Default Condition

## **BUS WORD**

| Name            | ı  | -  | -  | -  | WC | A2 | A1 | A0 |

|-----------------|----|----|----|----|----|----|----|----|

| Factory Default | 0* | 0* | 0* | 0* | 0  | 0  | 0  | 0  |

<sup>\*</sup>These bits are reserved and must be set to zero.

A0, A1, A2 (Default Setting = 000)

These are the device select bits that determine the address of the device.

## WC (Default Setting WC = 0)

This bit determines when/if the EEPROM is written to after register contents have been changed.

If WC = 0 the EEPROM is written automatically after a write register command.

If WC = 1 the EEPROM is only written when the "WRITE" command is issued.

Regardless of the value of the WC bit, when the BUS register (A0, A1, A2) is written, the current value in all registers (DIV, MUX, and BUS) are immediately written to the EEPROM.

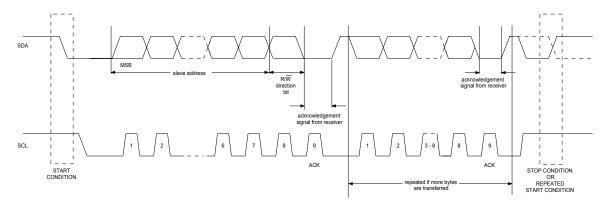

### 2-WIRE SERIAL DATA BUS

The DS1077 supports a bidirectional 2-wire bus and data transmission protocol. A device that sends data onto the bus is defined as a transmitter, and a device receiving data as a receiver. The device that controls the message is called a "master." The devices that are controlled by the master are "slaves." The bus must be controlled by a master device that generates the serial clock (SCL), controls the bus access, and generates the START and STOP conditions. The DS1077 operates as a slave on the 2-wire bus. Connections to the bus are made via the open-drain I/O lines, SDA and SCL. A pull-up resistor ( $5k\Omega$ ) is connected to SDA.

The following bus protocol has been defined (See Figure 2):

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is high will be interpreted as control signals.

Accordingly, the following bus conditions have been defined:

**Bus not busy:** Both data and clock lines remain HIGH.

**Start data transfer:** A change in the state of the data line from HIGH to LOW while the clock is HIGH defines a START condition.

**Stop data transfer:** A change in the state of the data line from LOW to HIGH while the clock line is HIGH defines the STOP condition.

**Data valid:** The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions is not limited, and is determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit

Within the bus specifications a regular mode (100kHz clock rate) and a fast mode (400kHz clock rate) are defined. The DS1077 works in both modes.

**Acknowledge:** Each receiving device, when addressed, is obliged to generate an acknowledge after the byte has been received. The master device must generate an extra clock pulse, which is associated with this acknowledge bit.

A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. When the DS1077 EEPROM is being written to, it will not be able to perform additional responses. In this case, the slave DS1077 will send a not-acknowledge to any data transfer request made by the master. It will resume normal operation when the EEPROM operation is complete.

A master must signal an end-of-data to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

## DATA TRANSFER ON 2-WIRE SERIAL BUS Figure 2

Figure 2 details how data transfer is accomplished on the 2-wire bus. Depending upon the state of the  $R/\overline{W}$  bit, two types of data transfer are possible:

- 1) **Data transfer from a master transmitter to a slave receiver.** The first byte transmitted by the master is the slave address. Next, follows a number of data bytes. The slave returns an acknowledge bit after each received byte.

- 2) **Data transfer from a slave transmitter to a master receiver.** The first byte (the slave address) is transmitted by the master. The slave then returns an acknowledge bit. Next, follows a number of data bytes transmitted by the slave to the master. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a not acknowledge is returned.

The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus will not be released.

The DS1077 may operate in the following two modes:

- 1) **Slave receiver mode:** Serial data and clock are received through SDA and SCL. After each byte is received, an acknowledge bit is transmitted. START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after the slave address and direction bit have been received.

- 2) **Slave transmitter mode:** The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit will indicate that the transfer direction is reversed. Serial data is transmitted on SDA by the DS1077 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer.

## **SLAVE ADDRESS**

A control byte is the first byte received following the START condition from the master device. The control byte consists of a 4-bit control code; for the DS1077, this is set as 1011 binary for read and write operations. The next three bits of the control byte are the device select bits (A2, A1, A0) and can be written to the EEPROM. They are used by the master device to select which of eight devices are to be accessed. The select bits are in effect the three least significant bits of the slave address. The last bit of the control byte  $(R/\overline{W})$  defines the operation to be performed. When set to a one a read operation is selected, and when set to a zero, a write operation is selected. Following the START condition, the DS1077 monitors the SDA bus, checking the device type identifier being transmitted. Upon receiving the 1011 code (changeable with one mask) and appropriate device select bits, the slave device outputs an acknowledge signal on the SDA line.

#### 2-WIRE SERIAL COMMUNICATION WITH DS1077 Figure 3 Send a "Standalone" Command Start Address Byte DS1077 Command Byte DS1077 Stop **ACK ACK** Write MSB of a Two-Byte Register SDA Address Byte DS1077 Command Byte MSByte DS1077 Stop Start DS1077 ACK ACK ACK Write to a Two-Byte Register SCL MSByte Address Byte Command Byte DS1077 DS1077 LSByte Start DS1077 DS1077 Stop ACK ACK **ACK** ACK Write a Single Byte to an Addressed Register SCL SDA Control Byte Command Byte **Byte Address** DS1077 Data Byte Start DS1077 DS1077 DS1077 Stop **ACK ACK** ACK ACK Write Multiple Bytes to an Addressed Register SCL SDA Starting Byte Address Control Byte DS1077 Command Byte DS1077 DS1077 Start DS1077 Byte n ACK **ACK** ACK ACK Byte (n+1) DS1077 Byte N DS1077 Stop ACK ACK

#### 2-WIRE SERIAL COMMUNICATION WITH DS1077 Figure 3 (continued) Read Single Byte Register or MSB from a Two-Byte Register SCL SDA Start Control Byte DS1077 Command Byte DS1077 Repeated Control Byte DS1077 **MSByte** Master Stop ACK Start ACK NACK **ACK** Read from a Two-Byte Register SCL SDA Control Byte DS1077 Repeated Control Byte DS1077 MSByte Start DS1077 Command Byte Master Start ACK ACK ACK ACK Master Stop LSByte NACK Read Multiple Bytes from an Addressed Register SCL SDA Control Byte DS1077 Starting Byte Address DS1077 Repeated Control Byte Start DS1077 Command Byte DS1077 ACK ACK ACK Byte n Master Master Stop Byte (n+1) Master Byte N ACK **ACK** NACK

### **COMMAND SET**

Data and control information is read from and written to the DS1077 in the format shown in Figure 3. To write to the DS1077, the master will issue the slave address of the DS1077 and the R/W bit will be set to 0. After receiving an acknowledge, the bus master provides a command protocol. After receiving this protocol, the DS1077 will issue an acknowledge, and then the master may send data to the DS1077. If the DS1077 is to be read, the master must send the command protocol as before, and then issue a repeat START condition and then the control byte again, this time with the R/W bit set to 1 to allow reading of the data from the DS1077. The command set for the DS1077 is as follows:

## Access DIV [01]

If R/W is 0, this command writes to the DIV register. After issuing this command, the next data byte value is to be written into the DIV register.

If  $R/\overline{W}$  is 1, the next data byte read is the value stored in the DIV register.

## **Access MUX [02]**

If R/W is 0, this command writes to the MUX register. After issuing this command, the next data byte value is to be written into the MUX register.

If R/W is 1, the next data byte read is the value stored in the MUX register.

## Access BUS [0D]

If R/W is 0, this command writes to the BUS register. After issuing this command, the next data byte value is to be written into the BUS register.

If  $R/\overline{W}$  is 1, the next data byte read is the value stored in the BUS register.

## Write E2 [3F]

If WC = 0 the EEPROM is automatically written to at the end of each command. This is a DEFAULT condition. In this case the command WRITE E2 is not needed.

If WC = 1, the EEPROM is written when the WRITE E2 command is issued. On receipt of the WRITE E2 command the contents of the BUS, DIV, and MUX registers are written into the EEPROM, thus locking in the register settings.

**EXCEPTION:** The BUS, DIV, and MUX registers are always automatically written to EEPROM after a write to the BUS register regardless of the value of the WC bit.

### APPLICATION INFORMATION

## **Power-Supply Decoupling**

To achieve best results, decouple the power supply with  $0.01\mu F$  and  $0.1\mu F$  high-quality, ceramic, surface-mount capacitors as close as possible to  $V_{CC}/GND$  of the device. Surface-mount components minimize lead inductance, which improves performance, and ceramic capacitors tend to have adequate high-frequency response for decoupling applications.

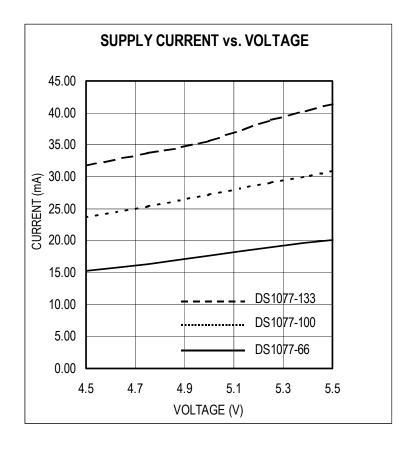

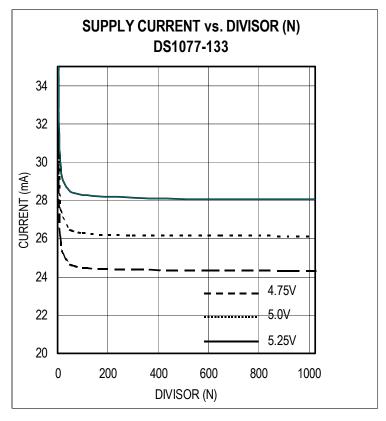

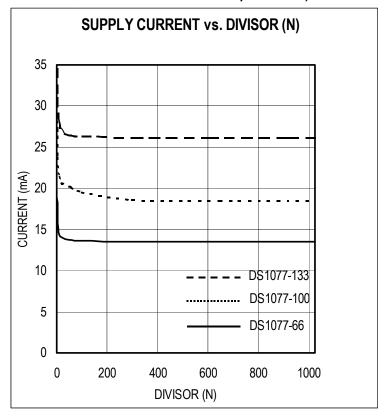

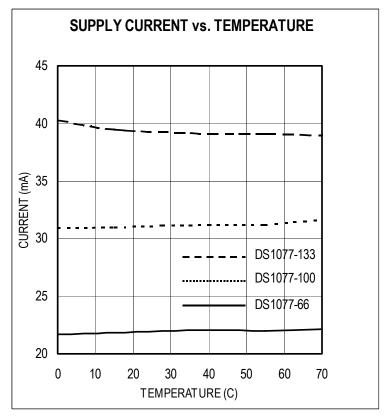

## **Current Consumption**

The active supply current can be significantly reduced by disabling OUT0 when not required and setting its prescaler to divide by 8. Likewise, bypassing OUT1's divider (and using only the prescaler) also significantly reduces the supply current.

## ABSOLUTE MAXIMUM RATINGS

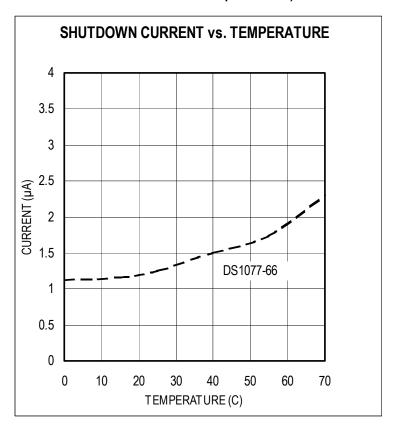

**Standby Current**

(Power-Down)

Voltage on Any Pin Relative to Ground -0.5V to 6.0V Operating Temperature Range -40°C to +85°C Programming Temperature Range  $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature Range -55°C to +125°C

Soldering Temperature See IPC/JEDEC J-STD-020A Specification

## DC ELECTRICAL CHARACTERISTICS

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, V_{CC} = 5V \pm 5\%)$ **PARAMETER SYMBOL CONDITION** MIN **TYP** MAX UNITS **NOTES** V  $V_{CC}$ 4.75 5 5.25 1 Supply Voltage High-Level Output  $I_{OH} = -4mA$ , Voltage V 2.4  $V_{OH}$  $V_{CC} = \min$ (OUT1,OUT0) Low-Level Output Voltage  $V_{OL}$  $I_{OL} = 4mA$ 0.4 V (OUT1,OUT0) High-Level Input  $V_{CC}$ + Voltage (CTRL1, 2.1 V  $V_{IH}$ 0.3VCTRL0) High-Level Input  $V_{CC}$ + 0.7VccV  $V_{IH}$ 0.3VVoltage (SDA, SCL) Low-Level Input V Voltage  $V_{\mathrm{IL}}$ -0.3V0.8 (CTRL1, CTRL0) Low-Level Input Voltage  $V_{\rm IL}$ -0.3V0.3Vcc (SDA, SCL) High-Level Input  $I_{IH}$ Current  $V_{IH} = V_{CC} =$ 1 μA (CTRL1, CTRL0, 5.25V SDA, SCL) Low-Level Input  $I_{\Pi}$ Current  $V_{CC} = 5.25V$ , -1 μA (CTRL1, CTRL0,  $V_{II} = 0$ SDA, SCL)  $C_L = 15pF$ Supply Current  $I_{CC}$ (Active) (Both Outputs) 50 10 mA

$(-40^{\circ}\text{C to } +85^{\circ}\text{C})$

Power-Down

Mode

2

5

μA

$I_{CCQ}$

**AC ELECTRICAL CHARACTERISTICS**  $(T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{CC} = 5\text{V } \pm 5\%)$

| PARAMETER                                  | SYMBOL                     | CONDITION                                                                               | MIN   | TYP  | MAX     | UNITS      | NOTES |

|--------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------|-------|------|---------|------------|-------|

| TAKANETEK                                  | STAIDOL                    |                                                                                         | 14111 | 111  | 1417424 | UNITS      | HOTES |

|                                            |                            | $V_{CC} = 5V, 25^{\circ}C$                                                              | -0.5  | 0    | +0.5    |            |       |

| Output Frequency                           |                            | $V_{CC} = 5V, 70^{\circ}C$                                                              | -0.5  | 0    | +0.5    |            |       |

| Tolerance Over<br>Temperature              | Δfo                        | $V_{CC} = 5V$ ,<br>-40°C to +25°C                                                       | -3.3  |      | +2.7    | %          | 11    |

|                                            |                            | $V_{CC} = 5V$ ,<br>+25°C to +85°C                                                       | -1.4  |      | +1.4    |            |       |

| Output Frequency<br>Tolerance Over Voltage | A.C.                       | $V_{CC} = 4.75V,$<br>25°C                                                               | -1.0  | -0.7 |         | %          |       |

|                                            | Δfo                        | $V_{CC} = 5.25V,$<br>25°C                                                               |       | +0.7 | +1.0    | <b>%</b> 0 |       |

| Combined Freq. Variation                   | Δfo                        | Over Temp<br>(0°C to +70°C)<br>& Voltage                                                | -1.65 |      | +1.25   | %          |       |

| Output Frequency Min                       | $f_{ m OUT}$               |                                                                                         | 8.13  |      |         | kHz        | 2     |

| Output Frequency Max                       | 1001                       |                                                                                         |       |      | 133     | MHz        |       |

| Power-Up Time                              | $t_{ m POR} + t_{ m STAB}$ |                                                                                         |       | 0.1  | 1       | ms         | 5     |

| Enable OUT1 from PDN                       | $t_{STAB}$                 |                                                                                         |       | 0.1  | 1       | ms         | 3     |

| Enable OUT0 from PDN                       | $t_{STAB}$                 |                                                                                         |       | 0.1  | 1       | ms         | 3     |

| OUT1 Hi-Z from PDN                         | $t_{\rm HiZ}$              |                                                                                         |       |      | 1       | ms         | 3     |

| OUT0 Hi-Z from PDN                         | $t_{\rm HiZ}$              |                                                                                         |       |      | 1       | ms         | 3     |

| Load Capacitance                           | $C_{\mathrm{L}}$           |                                                                                         |       | 15   | 50      | pF         | 4     |

| Output Duty Cycle (OUT1, OUT0)             |                            |                                                                                         | 40    |      | 60      | %          |       |

| Output Jitter                              |                            | f <sub>OUT</sub> =133MHz<br>M=1; DIV1=1<br>C <sub>L</sub> =12pF<br>3 sigma pk-to-<br>pk |       | 30   |         | psec       |       |

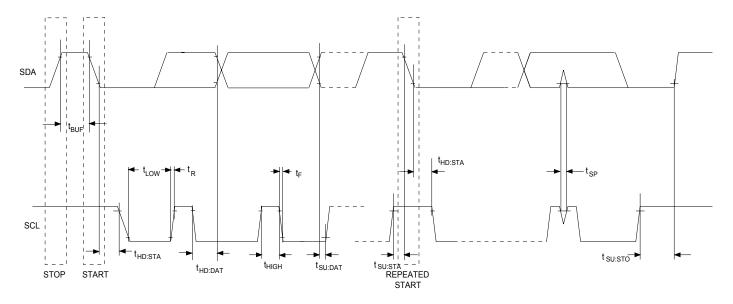

## **AC ELECTRICAL CHARACTERISTICS: 2-WIRE INTERFACE**

$(-40^{\circ}\text{C to } +85^{\circ}\text{C}; V_{CC} = 5\text{V} \pm 5\%)$

|                       |                                           |               | ,                      |     |      | <b>⊃, ∨</b> ℃∵ | <u> </u> |

|-----------------------|-------------------------------------------|---------------|------------------------|-----|------|----------------|----------|

| PARAMETER             | SYMBOL                                    | CONDITION     | MIN                    | TYP | MAX  | UNITS          | NOTES    |

| SCL Clock Frequency   | $f_{_{ m SCL}}$                           | Fast Mode     |                        |     | 400  | kHz            |          |

|                       | SCL                                       | Standard Mode |                        |     | 100  |                |          |

| Bus Free Time         | $t_{	ext{BUF}}$                           | Fast Mode     | 1.3                    |     |      | μs             |          |

| Between a STOP        | Bor                                       | Standard Mode | 4.7                    |     |      |                |          |

| and START Condition   |                                           |               |                        |     |      |                |          |

| Hold Time (Repeated)  | $t_{\text{HD:STA}}$                       | Fast Mode     | 0.6                    |     |      | μs             | 6        |

| START Condition       |                                           | Standard Mode | 4.0                    |     |      |                |          |

| LOW Period of SCL     | $t_{LOW}$                                 | Fast Mode     | 1.3                    |     |      | μs             |          |

|                       |                                           | Standard Mode | 4.7                    |     |      |                |          |

| HIGH Period of SCL    | $t_{\scriptscriptstyle{\mathrm{HIGH}}}$   | Fast Mode     | 0.6                    |     |      | μs             |          |

|                       |                                           | Standard Mode | 4.0                    |     |      |                |          |

| Set-Up Time for a     | t <sub>SU:STA</sub>                       | Fast Mode     | 0.6                    |     |      | μs             |          |

| Repeated START        | 50.5111                                   | Standard Mode | 4.7                    |     |      |                |          |

| Data Hold Time        | $t_{_{ m HD:DAT}}$                        | Fast Mode     | 0                      |     | 0.9  | μs             | 7,8      |

|                       |                                           | Standard Mode | 0                      |     |      |                |          |

| Data Set-Up Time      | $t_{\scriptscriptstyle{\mathrm{SU:DAT}}}$ | Fast Mode     | 100                    |     |      | ns             |          |

|                       | 201211                                    | Standard Mode | 250                    |     |      |                |          |

| Rise Time of Both     | $t_{_{ m R}}$                             | Fast Mode     | $20 + 0.1C_{\rm B}$    |     | 300  | ns             | 9        |

| SDA and SCL Signals   |                                           | Standard Mode | 20 + 0.1C <sub>B</sub> |     | 1000 |                |          |

| Fall Time of Both SDA | $t_{_{\mathrm{F}}}$                       | Fast Mode     | $20 + 0.1C_{\rm B}$    |     | 300  | ns             | 9        |

| and SCL Signals       |                                           | Standard Mode | 20 + 0.1C <sub>B</sub> |     |      |                |          |

| Set-Up Time For STOP  | t <sub>su:sto</sub>                       | Fast Mode     | 0.6                    |     |      | μs             |          |

|                       | 50.510                                    | Standard Mode | 4.0                    |     |      |                |          |

| Capacitive Load for   | $C_{B}$                                   |               |                        |     | 400  | pF             | 9        |

| Each Bus Line         |                                           |               |                        |     |      |                |          |

| Input Capacitance     | $C_{_{\mathrm{I}}}$                       |               |                        | 5   |      | pF             |          |

## **NONVOLATILE MEMORY CHARACTERISTICS**

| PARAMETER | SYMBOL | CONDITION | MIN    | TYP | MAX | UNITS | NOTES |

|-----------|--------|-----------|--------|-----|-----|-------|-------|

| Writes    |        | +85°C     | 10,000 |     |     |       |       |

### NOTES:

- 1) All voltages are referenced to ground.

- 2) 8.13kHz is obtained from a -66MHz standard part.

- 3) PDN is a power-down signal applied to either CTRL0 or CTRL1 pins as appropriate.

- 4) Output voltage swings may be impaired at high frequencies combined with high output loading.

- 5) After this period, the first clock pulse is generated.

- 6) A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the  $V_{IH\ MIN}$  of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

- 7) The maximum  $t_{HD:DAT}$  has only to be met if the device does not stretch the LOW period  $(t_{LOW})$  of the SCL signal.

- 8) A fast mode device can be used in a standard mode system, but the requirement  $t_{SU:DAT} \ge 250$ ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{RMAX} + t_{SU:DAT} = 1000$ ns + 250ns = 1250ns before the SCL line is released.

- 9) C<sub>B</sub> is the total capacitance of one bus line in pF.

- 10) OUT0 and OUT1 are operating at oscillator master frequency without divider.

- 11) Typical frequency shift due to aging is  $\pm 0.5\%$ . Aging stressing includes Level 3 preconditioning with 1000 temperature cycles of -55°C to +125°C, 336hr max  $V_{CC}$  biased +125°C bake. Level 3 preconditioning consists of a 24hr +125°C storage bake, 192hr moisture soak at +30°C/60% R.H., and three solder reflow passes.

## **TIMING DIAGRAM**

## ORDERING INFORMATION

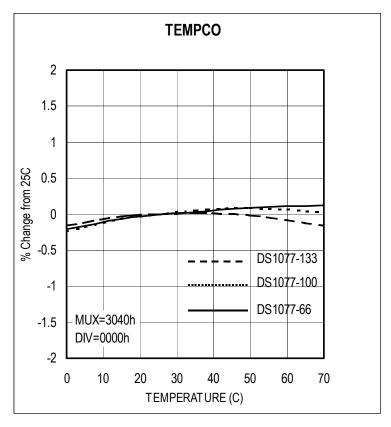

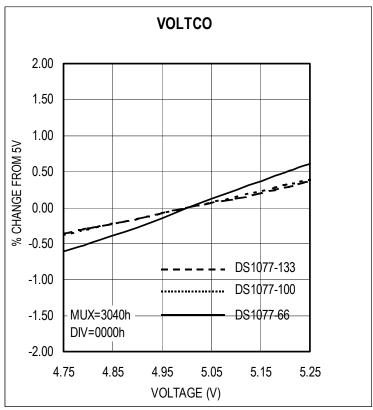

## **TYPICAL OPERATING CHARACTERISTICS**

( $V_{CC}$  = 5.0V, T = +25°C, unless otherwise specified)

# TYPICAL OPERATING CHARACTERISTICS (continued)

( $V_{CC}$  = 5.0V, T = +25°C, unless otherwise specified)

# TYPICAL OPERATING CHARACTERISTICS (continued)

( $V_{CC}$  = 5.0V, T = +25°C, unless otherwise specified)

# TYPICAL OPERATING CHARACTERISTICS (continued)

$(V_{CC} = 5.0V, T = +25^{\circ}C, unless otherwise specified)$

WHAT'S NEW PRODUCTS SOLUTIONS DESIGN APPNOTES SUPPORT

**BUY**

**COMPANY MEMBERS**

# **DS1077**

## **Part Number Table**

### Notes:

- 1. See the <u>DS1077 QuickView Data Sheet</u> for further information on this product family or download the <u>DS1077 full</u> <u>data sheet</u> (PDF, 316kB).

- 2. Other options and links for purchasing parts are listed at: <a href="http://www.maxim-ic.com/sales">http://www.maxim-ic.com/sales</a>.

- 3. <u>Didn't Find What You Need?</u> Ask our applications engineers. Expert assistance in finding parts, usually within one business day.

- 4. Part number suffixes: T or T&R = tape and reel; += RoHS/lead-free; #= RoHS/lead-exempt. More: See <u>full data sheet</u> or <u>Part Naming Conventions</u>.

- 5. \* Some packages have variations, listed on the drawing. "PkgCode/Variation" tells which variation the product uses.

| Part Number     | Free<br>Sample | Buy<br>Direct | Package: TYPE PINS SIZE  DRAWING CODE/VAR *                                | Temp         | RoHS/Lead-Free?<br>Materials Analysis                   |

|-----------------|----------------|---------------|----------------------------------------------------------------------------|--------------|---------------------------------------------------------|

| DS1077Z-120+T&R |                |               | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4* | -40C to +85C | RoHS/Lead-Free: Yes<br>Materials Analysis               |

| DS1077Z-100+T&R |                |               | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4* | -40C to +85C | RoHS/Lead-Free: <u>Yes</u><br><u>Materials Analysis</u> |

| DS1077Z-203     |                |               | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4* | -40C to +85C | RoHS/Lead-Free: No<br>Materials Analysis                |

| DS1077Z-203/T   | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4*        | -40C to +85C RoHS/Lead-Free: No<br>Materials Analysis             |

|-----------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|

| DS1077Z-100+    | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis              |

| DS1077Z-120+    | SOIC;8 pin;150<br>Dwg: <u>56-G2008-001C</u> (PDF)<br>Use pkgcode/variation: S8+4* | -40C to +85C RoHS/Lead-Free: <u>Yes</u> <u>Materials Analysis</u> |

| DS1077Z-133+    | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis              |

| DS1077Z-66+     | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis              |

| DS1077Z-125+    | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis              |

| DS1077Z-133     | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4*        | -40C to +85C RoHS/Lead-Free: No<br>Materials Analysis             |

| DS1077Z-125     | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4*        | -40C to +85C RoHS/Lead-Free: No<br>Materials Analysis             |

| DS1077Z-120     | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4*        | -40C to +85C RoHS/Lead-Free: No<br>Materials Analysis             |

| DS1077Z-125+T&R | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8+4*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis              |

| DS1077Z-66      | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4*        | -40C to +85C RoHS/Lead-Free: No<br>Materials Analysis             |

| DS1077Z-100     | SOIC;8 pin;150<br>Dwg: 56-G2008-001C (PDF)<br>Use pkgcode/variation: S8-4*   | -40C to +85C RoHS/Lead-Free: No<br>Materials Analysis |

|-----------------|------------------------------------------------------------------------------|-------------------------------------------------------|

| DS1077U-66+T&R  | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-133+    | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-125+    | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-120+    | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-100+    | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-66+     | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-133+T&R | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-125+T&R | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-120+T&R | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8+1*        | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-100+T&R | uSOP;8 pin;118<br>Dwg: <u>21-0036J</u> (PDF)<br>Use pkgcode/variation: U8+1* | -40C to +85C RoHS/Lead-Free: Yes  Materials Analysis  |

| DS1077U-100/T&R            | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

|----------------------------|------------------------------------------------------------------------------|----------------------------------------------------|

| DS1077U-66/T&R             |                                                                              | -40C to +85C RoHS/Lead-Free: No                    |

| DS1077U-125/T&R            | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-120/T&R            | uSOP;8 pin;118<br>Dwg: <u>21-0036J</u> (PDF)<br>Use pkgcode/variation: U8-1* | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-133                | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-125                | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-120                | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-100                | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-66                 | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| DS1077U-133/T&R            | uSOP;8 pin;118<br>Dwg: 21-0036J (PDF)<br>Use pkgcode/variation: U8-1*        | -40C to +85C RoHS/Lead-Free: No Materials Analysis |

| Didn't Find What You Need? |                                                                              |                                                    |

# CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy