Agilent HDMP-0422 Single Port Bypass Circuit with CDR & Data Valid Detection Capability for Fibre Channel Arbitrated Loops Data Sheet

### Description

The HDMP-0422 is a Single Port Bypass Circuit (PBC) with Clock and Data Recovery (CDR) capability included. This integrated circuit provides a low-cost, lowpower physical-layer solution for Fibre Channel Arbitrated Loop (FC-AL) disk array configurations. By using a PBC such as the HDMP-0422, hard disks may be pulled out or swapped while other disks in the array are available to the system.

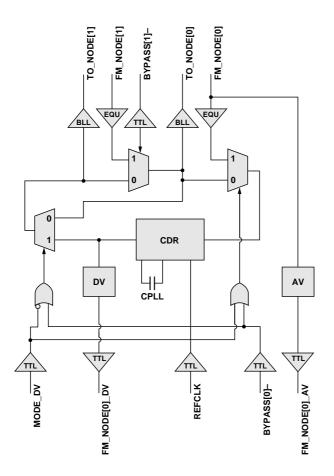

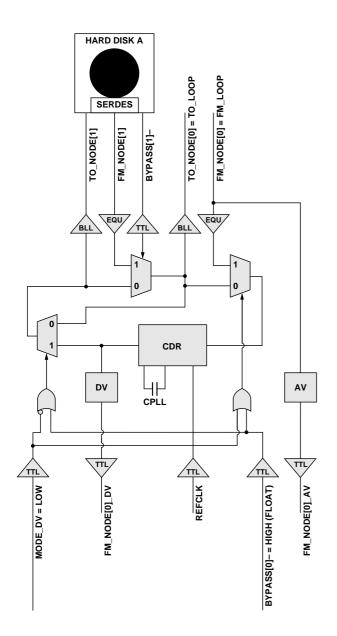

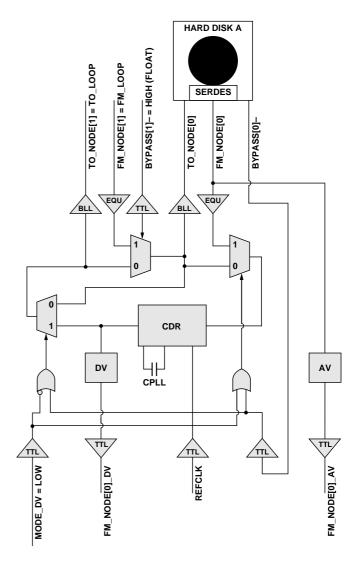

A PBC consists of multiple 2:1 multiplexers daisy chained along with a CDR. Each port has two modes of operation: "disk in loop" and "disk bypassed." When the "disk in loop" mode is selected, the loop goes into and out of the disk drive at that port. For example, data goes from the HDMP-0422's TO NODE[n] $\pm$  differential output pins to the Disk Drive Transceiver IC's (e.g. an HDMP-1636A) Rx differential input pins. Data from the Disk Drive Transceiver IC's Tx differential outputs goes to the HDMP-0422's FM\_NODE[n]± differential input pins. Figures 2 and 3 show connection diagrams for disk drive array applications.

When the "disk bypassed" mode is selected, the disk drive is either absent or non-functional and the loop bypasses the hard disk.

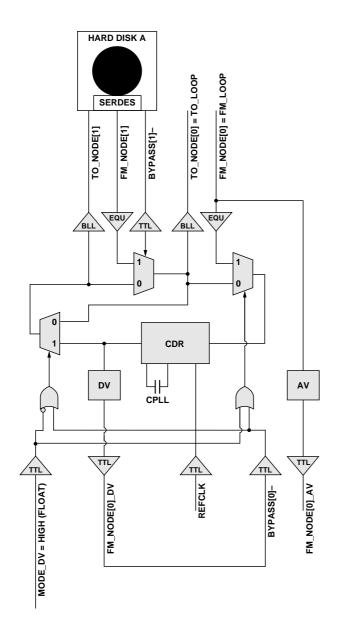

The "disk bypassed" mode is enabled by pulling the BYPASS[n]pin low. Leave BYPASS[n]floating to enable the "disk in loop" mode. HDMP-0422s may be cascaded with other members of the HDMP-04XX/HDMP-05XX family through the appropriate FM NODE[n] $\pm$  and TO NODE[n] $\pm$  pins to accommodate any number of hard disks (see Figure 4). The unused cells in the HDMP-0422 may be bypassed by using pulldown resistors on the BYPASS[n]- pins for these cells.

An HDMP-0422 may also be used as two 1:1 buffers, one with a CDR and one without. For example, an HDMP-0422 may be placed in front of a CMOS ASIC to clean the jitter of the outgoing signal (CDR path) and to better read the incoming signal (non-CDR paths). In addition, the HDMP-0422 may be configured as one 2:1 multiplexers or as one 1:2 buffers.

#### Features

- Supports 1.0625 GBd Fibre Channel operation

- Supports 1.25 GBd Gigabit Ethernet (GE) operation

- Single PBC/CDR in one package

- CDR location determined by choice of cable input/output

- Amplitude valid and data valid detection (Fibre channel rate only) on FM\_NODE[0] input

- Equalizers on all inputs

- High-speed LVPECL I/O

- Buffered Line Logic (BLL) outputs (no external bias resistors required)

- 0.46 W typical power at V<sub>CC</sub> = 3.3 V

- 24 Pin, low-cost SSOP package

#### Applications

- RAID, JBOD, BTS cabinets

- One 2:1 muxes

- One 1:2 buffers

- $1 \ge N$  Gigabit serial buffer

- $N \ge 1$  Gigabit serial mux

*CAUTION:* As with all semiconductor ICs, it is advised that normal static precautionsb be taken in the handling and assembly of this component to prevent damage and/or degradation which may be induced by electrostatic discharge (ESD).

Figure 1. Block diagram of HDMP-0422.

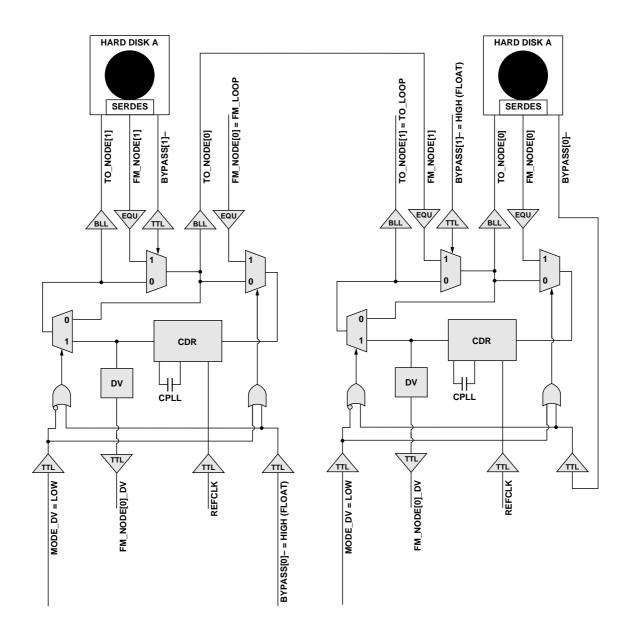

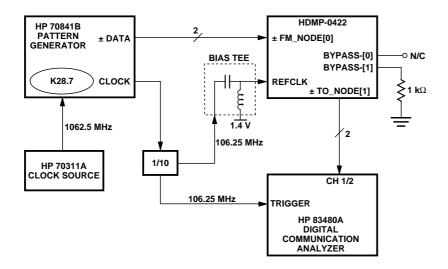

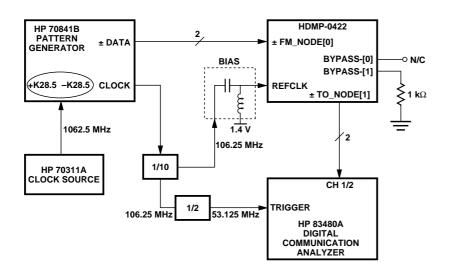

The HDMP-0422 design allows for CDR placement at any location with respect to a hard disk slot. For example, if hard disk A is connected to PBC cell 1, while BYPASS[0]- is left to float high (see Figure 2), the CDR function will be performed before entering the hard disk at slot A. To obtain a CDR function after slot A (see Figure 3), connect hard disk A to PBC cell 0, while floating BYPASS[1]- high. Refer to Table 1 for both pin connections.

#### CDR

The Clock and Data Recovery (CDR) block is responsible for frequency and phase locking onto the incoming serial data stream and resampling the incoming data based on the recovered clock. An automatic locking feature allows the CDR to lock onto the input data stream without external training controls. It does this by continually frequency locking onto the 106.25 MHz reference clock (REFCLK) and then phase locking onto the input data stream. Once bit locked, the CDR generates a high-speed sampling clock. This clock is used to sample or repeat the incoming data to produce the CDR output. The CDR jitter specifications listed in this data sheet assume an input that has been 8B/10B encoded. The CDR will also lock onto data encoded using other algorithms as long as there is DC balance and a sufficient number of transitions.

#### **REFCLK INPUT**

The LVTTL REFCLK input provides a reference oscillator for frequency acquisition of the CDR. The REFCLK frequency should be within  $\pm$  100 ppm of one-tenth of the incoming data rate in baud  $(106.25 \text{ MHz} \pm 100 \text{ ppm for FC-} \text{AL running at } 1.0625 \text{ GBd}).$

#### **BLL OUTPUT**

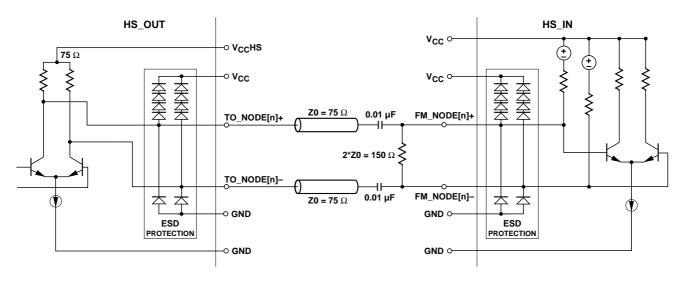

All TO\_NODE[n]± high-speed differential outputs are driven by a Buffered Line Logic (BLL) circuit that has on-chip source termination, so no external bias resistors are required. The BLL Outputs on the HDMP-0422 are of equal strength and can drive lengthy FR-4 PCB trace.

Unused outputs should not be left unconnected. Ideally, unused outputs should have their differential pins shorted together with a short PCB trace. If longer traces or transmission lines are connected to the output pins, the lines should be differentially terminated with an appropriate resistor. The value of the termination resistor should match the PCB trace differential impedance.

#### ΕΩU INPUT

All FM NODE[n] $\pm$  high-speed differential inputs have an Equalization (EQU) buffer to offset the effects of skin loss and dispersion on PCBs. An external termination resistor is required across all high-speed inputs. The value of the termination resistor should match the PCB trace differential impedance. Alternatively, instead of a single resistor, two resistors in series, with an AC ground between them, can be connected differentially across the FM NODE[n]± inputs. The latter configuration attenuates high-frequency common mode noise.

## **BYPASS**[n]- INPUT

The active low BYPASS[n]- inputs control the data flow through the HDMP-0422. All BYPASS pins are LVTTL and contain internal pull-up circuitry. To bypass a port, the appropriate BYPASS[n]- pin should be connected to GND through a 1  $k\Omega$  resistor. Otherwise, the BYPASS[n]- inputs should be left to float, as the internal pull-up circuitry will force them high.

## FM\_NODE[0]\_DV OUTPUT

The Data Valid (DV) block detects if the incoming data at  $FM_NODE[0]\pm$  is valid Fibre Channel data. The DV block checks for sufficient K28.5+ characters (per Fibre Channel framing rules) and for run length violations (per 8B/10B encoding) on the data coming out of the CDR.

The FM\_NODE[0]\_DV output is pulled low if a run length violation (RLV) occurs, or if there are no commas detected (NCD) over a specific time interval. It is pulled high if no errors are detected. A RLV error is defined as any consecutive sequence of 1s or 0s greater than five in the serial bit stream. An NCD error indicates the absence of the seven-bit pattern (0011111) present in the positive disparity comma (K28.5+) character. A K28.5+ character should occur at the beginning of every Fibre Channel frame of 2148 bytes (or 21480 serial bits), as well as many times within and between frames. If this seven-bit pattern is not found within a 215 bit  $(\sim 31 \,\mu s)$  interval, an NCD error is generated. A counter within the chip tracks the  $2^{15}$  bit intervals.

Any RLV and NCD errors are stored during the  $2^{15}$  bit interval. The FM\_NODE[0]\_DV output is pulled low at the start of the  $2^{15}$  bit interval after errors are detected. Once low, FM\_NODE[0]\_DV remains in that state until an entire  $2^{15}$  bit interval has no RLV or NCD errors. At the start of the  $2^{15}$  bit interval subsequent to no RLV or NCD errors being detected, FM\_NODE[0]\_DV is pulled high.

## MODE\_DV INPUT

The active high Data Valid Mode input selects Fibre Channel data checking of the FM\_NODE[0]± inputs. This is accomplished by having MODE\_DV override the BYPASS[0]- control (see Figure 1), thereby forcing the data into the CDR to come from the FM NODE[0]± inputs. The MODE\_DV pin is an LVTTL input and contains internal pull-up circuitry. To select Data Valid Mode, float MODE\_DV high. Otherwise, MODE\_DV should be connected to GND through a 1 k $\Omega$  resistor.

When MODE\_DV is high, the user is able to use the BYPASS[0]- input to bypass invalid Fibre Channel data from the rest of the loop. For example, if FM\_NODE[0]\_DV is connected to the BYPASS[0]input, data from the CDR will only be routed to TO\_NODE[1]± if the data has no RLV or NCD errors. If the DV block detects errors, the signal at TO\_NODE[0]± will be routed to the TO\_NODE[1]± outputs (see Figure 5).

## FM\_NODE[0]\_AV OUTPUT

The Amplitude Valid (AV) block detects if the incoming data on FM NODE [0]± is valid by examining the differential amplitude of that input. The incoming data is considered valid, and FM NODE[0] AV is driven high, as long as the amplitude is greater than 400 mV (differential peak-to-peak). FM NODE[0] AV is driven low as long as the amplitude of the input signal is less than 100 mV (differential peak-to-peak). When the amplitude of the input signal is between 100-400 mV (differential peak-to-peak), the FM NODE[0] AV output is undefined.

# **Table 1. Pin Connection Diagram to Achieve Desired CDR Location**(see Figures 2, 3)

| Hard Disks              | Α  | Α  |  |

|-------------------------|----|----|--|

| Connection to PBC cells | 1  | 0  |  |

| CDR position (x)        | хА | Ax |  |

| Cell connected to Cable | 0  | 1  |  |

${\bf x}$  denotes CDR position with respect to hard disks.

Figure 2. Connection diagram for CDR at first cell.

Figure 3. Connection diagram for CDR at last cell.

Figure 4. Connection diagram for multiple HDMP-0422s.

Figure 5. Connection diagram for bypassing invalid Fibre Channel data.

## I/O Type Definitions

| Definition                           |  |

|--------------------------------------|--|

| LVTTL Input                          |  |

| LVTTL Output                         |  |

| High Speed Output, LVPECL compatible |  |

| High Speed Input                     |  |

| External Circuit Node                |  |

| Power Supply or Ground               |  |

|                                      |  |

## **Pin Definitions**

| Pin Name                                                 | Pin                  | Pin Type | Pin Description                                                                                                                                                                              |

|----------------------------------------------------------|----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TO_NODE[0]+<br>TO_NODE[0]-<br>TO_NODE[1]+<br>TO_NODE[1]- | 20<br>21<br>05<br>04 | HS_OUT   | Serial Data Outputs: High-speed outputs to a hard disk drive or to a cable.                                                                                                                  |

| FM_NODE[0]+<br>FM_NODE[0]-<br>FM_NODE[1]+<br>FM_NODE[1]- | 23<br>24<br>02<br>01 | HS_IN    | Serial Data Inputs: High-speed inputs from a hard disk drive or from a cable.                                                                                                                |

| BYPASS[0]-<br>BYPASS[1]-                                 | 17<br>08             | I-LVTTL  | <b>Bypass Inputs:</b> For "disk bypassed" mode, connect BYPASS[n]- to GND through a 1 k $\Omega$ resistor. For "disk in loop" mode, float HIGH.                                              |

| REFCLK                                                   | 14                   | I-LVTTL  | <b>Reference Clock:</b> A user-supplied clock reference used for frequency acquisition in the Clock and Data Recovery (CDR) circuit.                                                         |

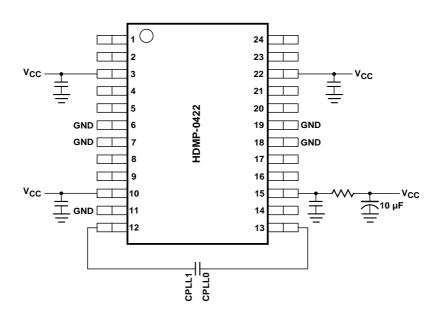

| CPLL1<br>CPLL0                                           | 12<br>13             | C        | <b>Loop Filter Capacitor:</b> A loop filter capacitor for the internal Clock and Data Recovery (CDR) circuit must be connected across the CPLL1 and CPLL0 pins. Recommended value is 0.1 μF. |

| FM_NODE[0]_DV                                            | 09                   | 0-LVTTL  | <b>Data Valid:</b> Indicates Fibre Channel compliant data on FM_NODE[n] $\pm$ inputs when HIGH. Indicates either a run length violation or a no comma detected error when LOW.               |

| MODE_DV                                                  | 11                   | I-LVTTL  | Data Valid Mode: To allow data valid detection, float MODE_DV HIGH. Otherwise, connect to GND through a 1 k $\Omega$ resistor.                                                               |

| FM_NODE[0]_AV                                            | 16                   | 0-LVTTL  | <pre>Amplitude Valid: Indicates acceptable signal amplitude on the FM_NODE[n]± inputs. If (FM_NODE[n]+ - FM_NODE[n]-) &gt;= 400 mV peak-to-peak,</pre>                                       |

| GND                                                      | 06<br>07<br>18<br>19 | S        | <b>Ground:</b> Normally 0 V. See Figure 13 for Recommended Power Supply Filtering.                                                                                                           |

| V <sub>CC</sub> A                                        | 15                   | S        | <b>Analog Power Supply:</b> Normally 3.3 V. Used to provide a clean supply to the Clock and Data Recovery (CDR) circuit. See Figure 13 for Recommended Power Supply Filtering.               |

| VccHS[0]<br>VccHS[1]                                     | 22<br>03             | S<br>S   | <b>High Speed Supply:</b> Normally 3.3 V. Used only for high-speed outputs (TO_NODE[n]). See Figure 13 for Recommended Power Supply Filtering.                                               |

| V <sub>CC</sub>                                          | 10                   | S        | <b>Logic Power Supply:</b> Normally 3.3 V. Used for internal logic. See Figure 13 for Recommended Power Supply Filtering.                                                                    |

### **Absolute Maximum Ratings**

$T_A = 25^{\circ}$ C, except as specified. Operation in excess of any of these conditions may result in permanent damage to this device. Continuous operation at these minimum or maximum ratings is not recommended.

| Symbol                | Parameter                          | Units | Min. | Max.                                 |

|-----------------------|------------------------------------|-------|------|--------------------------------------|

| Vcc                   | Supply Voltage                     | V     | -0.5 | 4.0                                  |

| V <sub>IN,LVTTL</sub> | LVTTL Input Voltage                | V     | -0.5 | V <sub>CC</sub> + 0.5 <sup>[1]</sup> |

| Vin,hs_in             | HS_IN Input Voltage (Differential) | mV    | 200  | 2000                                 |

| Io,lvttl              | LVTTL Output Sink/Source Current   | mA    |      | ±13                                  |

| T <sub>stg</sub>      | Storage Temperature                | °C    | -65  | +150                                 |

| <br>Tj                | Junction Temperature               | °C    | 0    | +125                                 |

#### Note:

1. Must remain less than or equal to absolute maximum V\_CC voltage of 4.0 V.

## **DC Electrical Specifications**

$V_{CC} = 3.15 \text{ V} \text{ to } 3.45 \text{ V}.$

| Symbol                | Parameter                                                                   | Units | Min. | Тур. | Max. |

|-----------------------|-----------------------------------------------------------------------------|-------|------|------|------|

| Vih,lvttl             | LVTTL Input High Voltage Range                                              | V     | 2.0  |      |      |

| VIL,LVTTL             | LVTTL Input Low Voltage Range                                               | V     |      |      | 0.8  |

| Voh,lvttl             | LVTTL Output High Voltage Range, I $_{0H}$ = -400 $\mu A$                   | V     | 2.2  |      | Vcc  |

| Vol,lvttl             | LVTTL Output Low Voltage Level, I <sub>OL</sub> = 1 mA                      | V     | 0    |      | 0.6  |

| I <sub>IH,LVTTL</sub> | Input High Current (Magnitude), V $_{ m IN}$ = 2.4 V, V $_{ m CC}$ = 3.45 V | μA    |      |      | 40   |

| IIL,LVTTL             | Input Low Current (Magnitude), $V_{IN}$ = 0.4 V, $V_{CC}$ = 3.45 V          | μA    |      |      | -600 |

| lcc                   | Total Supply Current, T <sub>A</sub> = 25°C                                 | mA    |      | 140  |      |

## **AC Electrical Specifications**

$V_{CC} = 3.15 \text{ V} \text{ to } 3.45 \text{ V}.$

|                                                                         | Units                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Min.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Тур.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Total Loop Latency from FM_NODE[0] to TO_NODE[0]                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Per Cell Latency from FM_NODE[1] to TO_NODE[0]                          | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input LVTTL Rise Time Requirement, 0.8 V to 2.0 V                       | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input LVTTL Fall Time Requirement, 2.0 V to 0.8 V                       | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Output TTL Rise Time, 0.8 V to 2.0 V, 10 pF Load                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Output TLL Fall Time, 2.0 V to 0.8 V, 10 pF Load                        | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HS_OUT Single-Ended Rise Time, 20% to 80%                               | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HS_OUT Single-Ended Fall Time, 20% to 80%                               | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HS_OUT Differential Rise Time, 20% to 80%                               | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HS_OUT Differential Fall Time, 20% to 80%                               | ps                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| HS_IN Required Pk-Pk Differential Input Voltage                         | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| HS_OUT Pk-Pk Differential Output Voltage (Z0 = 75 $\Omega$ , Figure 10) | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                         | Per Cell Latency from FM_NODE[1] to TO_NODE[0]Input LVTTL Rise Time Requirement, 0.8 V to 2.0 VInput LVTTL Fall Time Requirement, 2.0 V to 0.8 VOutput TTL Rise Time, 0.8 V to 2.0 V, 10 pF LoadOutput TLL Fall Time, 2.0 V to 0.8 V, 10 pF LoadOutput TLL Fall Time, 2.0 V to 0.8 V, 10 pF LoadHS_OUT Single-Ended Rise Time, 20% to 80%HS_OUT Differential Rise Time, 20% to 80%HS_OUT Differential Rise Time, 20% to 80%HS_IN Required Pk-Pk Differential Input Voltage | Per Cell Latency from FM_NODE[1] to TO_NODE[0]nsInput LVTTL Rise Time Requirement, 0.8 V to 2.0 VnsInput LVTTL Fall Time Requirement, 2.0 V to 0.8 VnsOutput TTL Rise Time, 0.8 V to 2.0 V, 10 pF LoadnsOutput TLL Fall Time, 2.0 V to 0.8 V, 10 pF LoadnsOutput TLL Fall Time, 2.0 V to 0.8 V, 10 pF LoadnsHS_OUT Single-Ended Rise Time, 20% to 80%psHS_OUT Differential Rise Time, 20% to 80%psHS_OUT Differential Rise Time, 20% to 80%psHS_IN Required Pk-Pk Differential Input VoltagemV | Per Cell Latency from FM_NODE[1] to TO_NODE[0]nsInput LVTTL Rise Time Requirement, 0.8 V to 2.0 VnsInput LVTTL Fall Time Requirement, 2.0 V to 0.8 VnsOutput TTL Rise Time, 0.8 V to 2.0 V, 10 pF LoadnsOutput TLL Fall Time, 2.0 V to 0.8 V, 10 pF LoadnsMS_OUT Single-Ended Rise Time, 20% to 80%psHS_OUT Single-Ended Fall Time, 20% to 80%psHS_OUT Differential Rise Time, 20% to 80%psHS_OUT Differential Rise Time, 20% to 80%psHS_OUT Differential Rise Time, 20% to 80%psHS_IN Required Pk-Pk Differential Input VoltagemV200 | Per Cell Latency from FM_NODE[1] to TO_NODE[0]ns2.0Input LVTTL Rise Time Requirement, 0.8 V to 2.0 Vns2.0Input LVTTL Fall Time Requirement, 2.0 V to 0.8 Vns2.0Output TTL Rise Time, 0.8 V to 2.0 V, 10 pF Loadns1.7Output TLL Fall Time, 2.0 V to 0.8 V, 10 pF Loadns1.7Output TLL Fall Time, 2.0 V to 0.8 V, 10 pF Loadns200HS_OUT Single-Ended Rise Time, 20% to 80%ps200HS_OUT Differential Rise Time, 20% to 80%ps200HS_OUT Differential Rise Time, 20% to 80%ps200HS_OUT Differential Fall Time, 20% to 80%ps200HS_IN Required Pk-Pk Differential Input VoltagemV2001200 |

### **Guaranteed Operating Rates**

| $V_{CC} = 3.15$ | V to 3.45 V.     |             |                  |  |

|-----------------|------------------|-------------|------------------|--|

| FC Serial (     | Clock Rate (MBd) | GE Serial ( | Clock Rate (MBd) |  |

| Min.            | Max.             | Min.        | Max.             |  |

| 1,040           | 1,080            | 1,240       | 1,260            |  |

## **CDR Reference Clock Requirements**

V<sub>CC</sub> = 3.15 V to 3.45 V.

| Symbol | Parameter                            | Units | Min. | Тур.   | Max. |

|--------|--------------------------------------|-------|------|--------|------|

| f      | Nominal Frequency (Fibre Channel)    | MHz   |      | 106.25 |      |

| f      | Nominal Frequency (Gigabit Ethernet) | MHz   |      | 125    |      |

| Ftol   | Frequency Tolerance                  | ppm   | -100 |        | +100 |

| Symm   | Symmetry (Duty Cycle)                | %     | 40   |        | 60   |

# **Locking Characteristics** $V_{CC} = 3.15 \text{ V}$ to 3.45 V.

| $v_{\rm U}$ = 3.13 v to 3.43 v. |       |      |

|---------------------------------|-------|------|

| Parameter                       | Units | Max. |

| Bit Sync Time (phase lock)      | bits  | 2500 |

| Frequency Lock at Powerup       | μs    | 500  |

## **Output Jitter Characteristics**

$V_{CC} = 3.15 \text{ V to } 3.45 \text{ V}.$

| Symbol            | Parameter                                    | Units | Тур. | Max. |

|-------------------|----------------------------------------------|-------|------|------|

| RJ <sup>[1]</sup> | Random Jitter at TO_NODE pins (1 sigma rms)  | ps    | 5    |      |

| DJ <sup>[1]</sup> | Deterministic Jitter at TO_NODE pins (pk-pk) | ps    | 20   |      |

Note:

1. Please refer to Figures 7 and 8 for jitter measurement setup information.

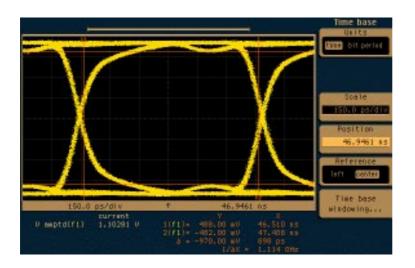

Figure 6. Eye diagram of TO\_NODE[1]± high speed differential output (50  $\Omega$  termination). Note: Measurement taken with a 2<sup>7</sup>-1 PRBS input to FM\_NODE[0]±

#### **Jitter Measurement Configurations**

Figure 7. Setup for measurement of Random Jitter.

Figure 8. Setup for measurement of Deterministic Jitter.

## Simplified I/O Cells

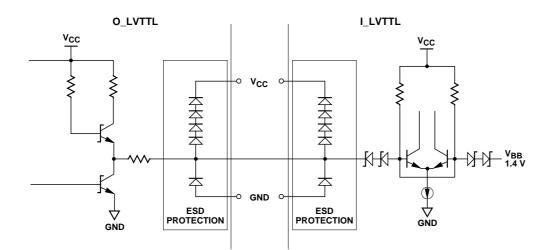

Figure 9. O-LVTTL and I-LVTTL simplified circuit schematic.

NOTE: 1. FM\_NODE[n] INPUTS SHOULD NEVER BE CONNECTED TO GROUND AS PERMANENT DAMAGE TO THE DEVICE MAY RESULT.

Figure 10. HS\_OUT and HS\_IN simplified circuit schematic.

#### **Package Information**

Power Dissipation and Thermal Resistance.  $V_{CC}$  = 3.15 V to 3.45 V.

| Symbol              | Parameter                            | Units | Тур. | Max. |

|---------------------|--------------------------------------|-------|------|------|

| PD                  | Power Dissipation                    | mW    | 460  |      |

| $\Theta_{jc}^{[1]}$ | Thermal Resistance, Junction to Case | °C/W  | 14   |      |

Note:

Based on independent package testing by Agilent. Θ<sub>ja</sub> for this device is 57°C/W. Θ<sub>ja</sub> is measured on a standard 3x3" FR4 PCB in a still air environment. To determine the actual junction temperature in a given application, use the following equation:

$T_j = T_C + (\Theta_{ja} \times P_D)$ , where  $T_C$  is the case temperature measured on the top center of the package and  $P_D$  is the power being dissipated.

| ltem                                                                         | Details              |  |  |

|------------------------------------------------------------------------------|----------------------|--|--|

| Package Material Plastic Shrink Small Outline (SSOP) Per JESD Pub 95, MO-150 |                      |  |  |

| Lead Finish Material                                                         | 85% Tin, 15% Lead    |  |  |

| Lead Finish Thickness                                                        | 200-800 micro-inches |  |  |

| Lead Skew                                                                    | 0.15 mm max          |  |  |

| Lead Coplanarity (Seating Plane)                                             | 0.10 mm max          |  |  |

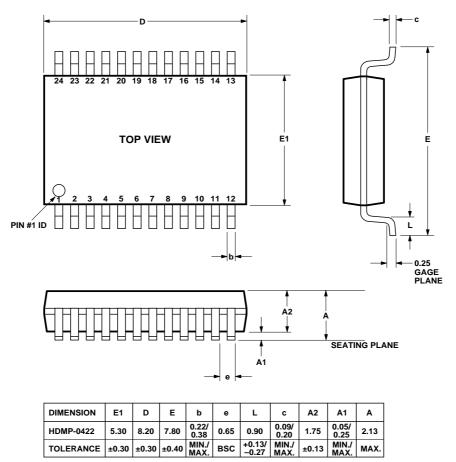

## **Mechanical Dimensions**

ALL DIMENSIONS ARE IN MILLIMETERS

Figure 11. HDMP-0422 package drawing.

#### Pin Diagram and Recommended Supply Filtering

nnn-nn = WAFER LOI – BUILD NUMBER Rz.zz = DIE REVISION S = SUPPLIER CODE YYWW = DATE CODE (YY = YEAR, WW = WORK WEEK) COUNTRY = COUNTRY OF MANUFACTURE

Figure 12. HDMP-0422 package layout and marking, top view.

CAPACITORS = 0.1  $\mu\text{F},$  RESISTOR = 10  $\Omega$  (EXCEPT WHERE NOTED).

Figure 13. Recommended power supply filtering.

#### www.agilent.com/semiconductors

For product information and a complete list of distributors, please go to our web site. For technical assistance call: Americas/Canada: +1 (800) 235-0312 or (916) 788-6763 Europe: +49 (0) 6441 92460 China: 10800 650 0017 Hong Kong: (+65) 6756 2394 India, Australia, New Zealand: (+65) 6755 1939 Japan: (+81 3) 3335-8152(Domestic/International), or 0120-61-1280(Domestic Only) Korea: (+65) 6755 1989 Singapore, Malaysia, Vietnam, Thailand, Philippines, Indonesia: (+65) 6755 2044 Taiwan: (+65) 6755 1843 Data subject to change. Copyright © 2003 Agilent Technologies, Inc. Obsoletes 5988-8561EN June 17, 2003

5988-9759EN