MARVELL

# 88EM8080/88EM8081

LED Power Supply Controller for Flyback Converters with Power Factor Correction

## Datasheet

Customer Use

Doc. No. MV-S106340-01, Rev. B August 6, 2010

Document Classification: Proprietary

Datasheet

| Docum       | Document Conventions                  |                                           |  |  |  |

|-------------|---------------------------------------|-------------------------------------------|--|--|--|

|             | Note: Provides related information or | information of special importance.        |  |  |  |

| ļ           | Caution: Indicates potential damage t | to hardware or software, or loss of data. |  |  |  |

| Ą           | Warning: Indicates a risk of personal | injury.                                   |  |  |  |

| Docum       | Document Status                       |                                           |  |  |  |

| Doc Status: | Preliminary Information               | Technical Publication: 0.xx               |  |  |  |

For more information, visit our website at: www.marvell.com

#### Disclaimer

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2; 2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof are controlled for national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a plant, not to export to EAR Country Groups D:1 or E:2 the direct product of the plant or major component thereof, if such direct product is controlled for national security reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such information agrees that they shall be deemed to have manually signed this document in connection with their receipt of any such information.

Copyright © 1999–2009. Marvell International Ltd. All rights reserved. Marvell, Moving Forward Faster, the Marvell logo, Alaska, AnyVoltage, DSP Switcher, Fastwriter, Ferceon, Libertas, Link Street, PHYAdvantage, Prestera, TopDog, Virtual Cable Tester, Yukon, and ZJ are registered trademarks of Marvell or its affiliates. CarrierSpan, LinkCrypt, Powered by Marvell Green PFC, Qdeo, QuietVideo, Sheeva, TwinD, and VCI are trademarks of Marvell or its affiliates. Protection Stevens and VCI are trademarks of Marvell or its affiliates. Protection Stevens and VCI are trademarks of Marvell or its affiliates.

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items contained within this document. Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use Marvell products in these types of equipment or applications.

<sup>1)</sup> Not to re-export or release any such information consisting of technology, software or source code controlled for national security reasons by the U.S. Export Control

## LED Power Supply Controller for Flyback Converters with Power Factor Correction

#### Marvell. Moving Forward Faster

## **PRODUCT OVERVIEW**

The Marvell<sup>®</sup> 88EM8080/88EM8081 device is a high performance LED power supply controller for flyback converters with output regulation and power factor correction. The 88EM8080/8081 control algorithm uses Average Current Mode Control (ACMC) for power factor correction (PFC) in LED lighting applications with low harmonic distortion and good noise immunity. The Marvell proprietary adaptive loop control achieves high power factor under high input voltage and low load conditions. Through Marvell's innovative digital signal processing (DSP) solution, the LED controller with the PFC function provides the customer with the smallest package, the lowest system cost, the lowest total harmonic distortion (THD) and the best power factor for LED lighting applications.

Both devices work at fixed frequencies, 88EM8080 at 60kHz while 88EM8081 at 120kHz. The IC operates under Continuous Conduction Mode (CCM) or Discontinuous Conduction Mode (DCM) or both combined together operating in Mixed Mode. The internal voltage loop compensation and current loop control guarantee system stability and thus reduce the exernal component count and costs.

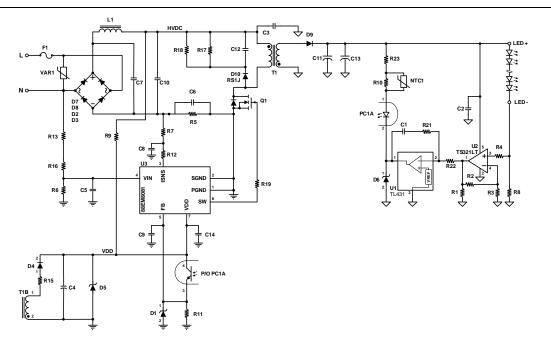

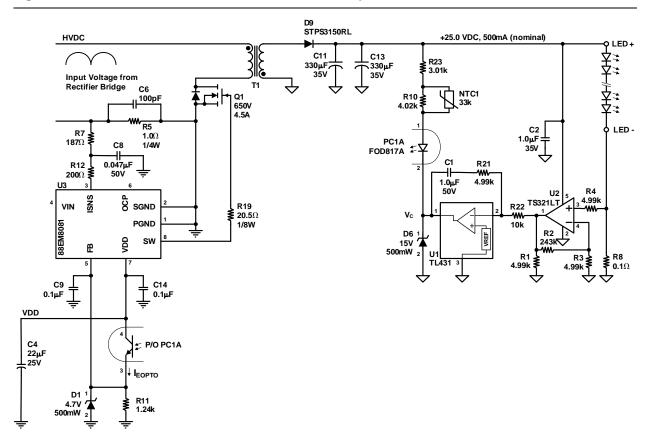

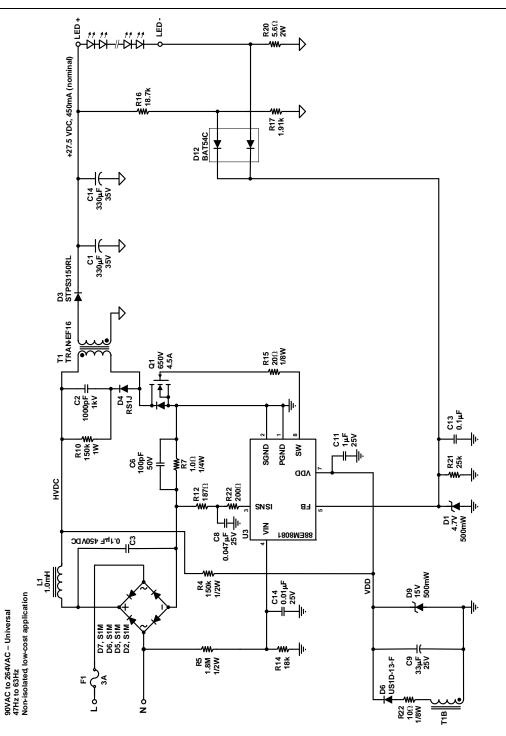

The 8-pin SOIC package further facilitates the application design process by saving board space. The resultant simple system design and minimum cost makes 88EM8080/88EM8081 the ideal choice for LED applications with PFC. Figure 1 shows

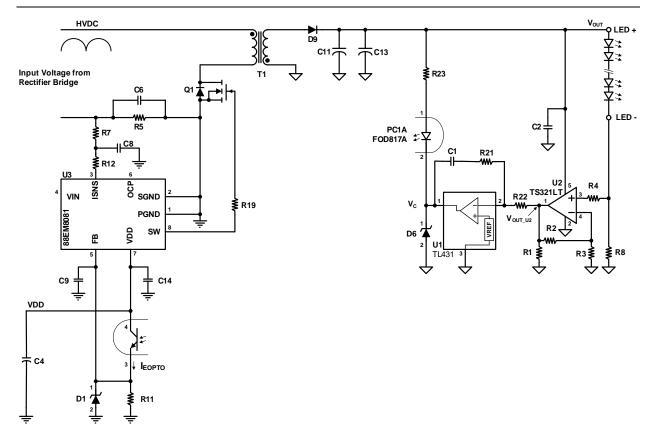

#### Figure 1: Universal Isolated LED Driver with PFC

88EM8080/88EM8081

a reference schematic for a universal isolated LED driver with PFC using the 88EM8080/88EM8081 device.

#### **General Features**

- Mixed Mode CCM and DCM operation

- Average current mode control

- Adaptive control loop achieves high power factor and low THD for a wide range of voltage and load conditions

- Adaptive over current protection for universal voltage

- Fixed switching frequency

- 1.2A (typical) driver capability

- Minimal external components required

- Under voltage lockout (UVLO)

- Over voltage protection (OVP)

- Thermal shutdown

- Input line frequency range from 45Hz to 65Hz

#### Applications

- LED home and facility lighting

- LED street lamps

Datasheet

THIS PAGE INTENTIONALLY LEFT BLANK

# **Table of Contents**

| Table  | e of Contents                                                                                                                                                                                                                                                                         | 5  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| List o | of Figures                                                                                                                                                                                                                                                                            | 7  |

| List o | of Tables                                                                                                                                                                                                                                                                             | 9  |

| 1      | Signal Description                                                                                                                                                                                                                                                                    | 11 |

| 1.1    | Pin Configurations                                                                                                                                                                                                                                                                    | 11 |

| 1.2    | Pin Descriptions                                                                                                                                                                                                                                                                      | 11 |

| 2      | Electrical Specifications                                                                                                                                                                                                                                                             | 15 |

| 2.1    | Absolute Maximum Ratings                                                                                                                                                                                                                                                              | 15 |

| 2.2    | Electrical Characteristics                                                                                                                                                                                                                                                            | 16 |

| 3      | Functional Description                                                                                                                                                                                                                                                                | 19 |

| 3.1    | Overview                                                                                                                                                                                                                                                                              | 19 |

| 3.2    | VDD – Bias Power Input                                                                                                                                                                                                                                                                | 20 |

| 3.3    | PGND and SGND                                                                                                                                                                                                                                                                         | 20 |

| 3.4    | SW – Switched PWM Output for Gate Drive                                                                                                                                                                                                                                               | 20 |

| 3.5    | VIN – Input Voltage Sensing<br>3.5.1 Brown-out Protection                                                                                                                                                                                                                             |    |

| 3.6    | <ul> <li>FB – Output Voltage / Current Feedback</li></ul>                                                                                                                                                                                                                             |    |

| 3.7    | ISNS – Current Sensing / Over Current Protection         3.7.1       ISNS – Peak Current Sensing         3.7.2       ISNS – Average Current Mode Control         3.7.3       ISNS – Adaptive Over Current Protection         3.7.4       OCP – Cycle by Cycle Over Current Protection |    |

| 3.8    | Mixed Modes of Operation                                                                                                                                                                                                                                                              | 24 |

| 3.9    | Compensation and Adaptive Control Loop                                                                                                                                                                                                                                                | 24 |

| 3.10   | Over Temperature Protection                                                                                                                                                                                                                                                           | 24 |

| 4      | Functional Characteristics                                                                                                                                                                                                                                                            |    |

| 4.1    | V <sub>DD</sub> Characteristics                                                                                                                                                                                                                                                       |    |

| 4.2    | V <sub>FB</sub> Characteristics for Over Voltage Protection                                                                                                                                                                                                                           |    |

| 4.3    | Switching Frequency Characteristics                                                                                                                                                                                                                                                   |    |

| 4.4    | Over Current Threshold Characteristics                                                                                                                                                                                                                                                | 29 |

88EM8080/88EM8081

Datasheet

| 5   | Design and Applications Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 5.1 | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

| 5.2 | Input Voltage Resistor Divider on VIN Pin<br>5.2.1 Brown-out Protection<br>5.2.2 Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                      |

| 5.3 | Output LED Current Control         5.3.1       Non-isolated Output LED Current Control         5.3.1.1       R1 and R2 Resistor Divider Design         5.3.1.2       RC Filter Design         5.3.1.3       Design of Operational Amplifier Circuit         5.3.2       Low-Cost LED Current Control with Non-isolated Output         5.3.3       LED Current Control with Isolated Output         5.3.4       Isolated LED Current Control - Circuit Design         5.3.5       NTC Compensation Circuit Design         5.3.5.1       Design Equations         5.3.5.2       Simplified Engineering Design Procedure | 35<br>36<br>36<br>36<br>37<br>37<br>38<br>40<br>42<br>42<br>43<br>45 |

| 5.4 | <ul> <li>Current Sensing and Over Current Protection</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| 5.5 | SW Pin to MOSFET Gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                                                                   |

| 5.6 | VDD, Signal (SGND) and Power (PGND) Grounds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51                                                                   |

| 5.7 | Non-isolated LED Driver         5.7.1       Non-isolated LED Driver Schematic         5.7.2       Non-isolated LED Driver Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 53<br>53                                                             |

| 5.8 | Isolated LED Driver         5.8.1       Isolated LED Driver Schematic.         5.8.2       Isolated LED Driver Description.         5.8.3       12.5W Universal Isolated LED Driver Test Results         5.8.3.1       Efficiency and Power Factor.         5.8.3.2       Start-up Waveforms         5.8.3.3       Steady State Waveforms.                                                                                                                                                                                                                                                                            |                                                                      |

| 6   | Mechanical Drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| 6.1 | Mechanical Drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

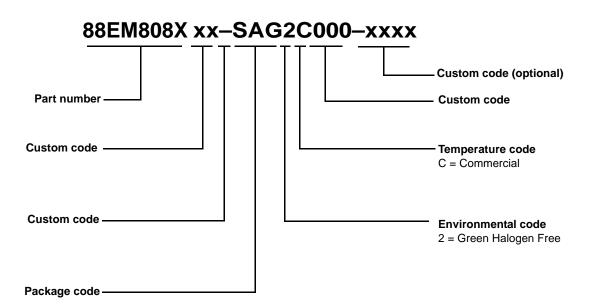

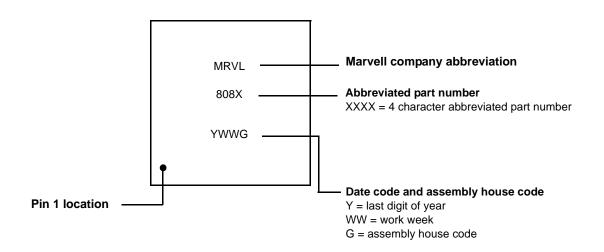

| 7   | Part Order Numbering/Package Marking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                                   |

| 7.1 | Part Order Numbering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61                                                                   |

| 7.2 | Package Markings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62                                                                   |

| A   | Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 63                                                                   |

# **List of Figures**

|   | Figure 1:  | Universal Isolated LED Driver with PFC                             | 3    |

|---|------------|--------------------------------------------------------------------|------|

| 1 | Signal De  | scription                                                          | . 11 |

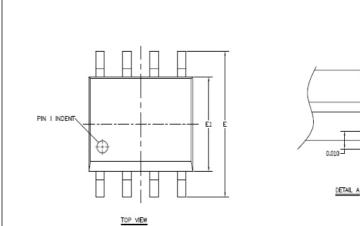

|   | Figure 2:  | SOIC-8 Pin Diagram (Top View)                                      | 11   |

| 2 | Electrical | Specifications                                                     | 15   |

| 3 | Functiona  | al Description                                                     | 19   |

|   | Figure 3:  | Top Level Block Diagram                                            | 19   |

| 4 | Functiona  | al Characteristics                                                 | 25   |

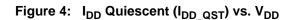

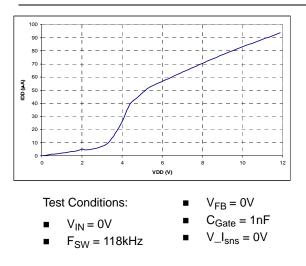

|   | Figure 4:  | I <sub>DD</sub> Quiescent (IDD_QST) vs. V <sub>DD</sub>            | 25   |

|   | Figure 5a: | I <sub>DD</sub> vs. V <sub>DD</sub> (V <sub>DD_ON</sub> )          | 25   |

|   | Figure 5b: | I <sub>DD</sub> vs. V <sub>DD</sub> (V <sub>DD_ON</sub> )          | 25   |

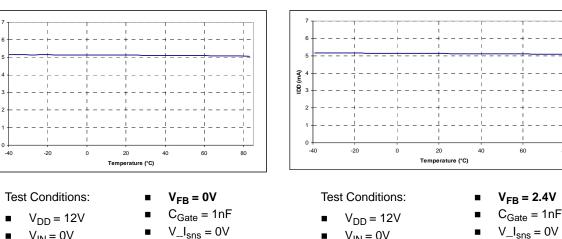

|   | Figure 6a: | I <sub>DD</sub> Operation (IDD_OP) vs. Temperature                 | 26   |

|   | Figure 6b: | I <sub>DD</sub> Operation (IDD_OP) vs. Temperature                 | 26   |

|   | Figure 7:  | VDD On/Off vs. Temperature                                         | 26   |

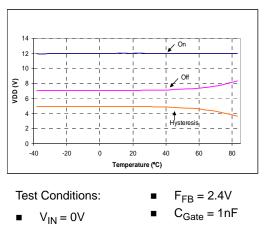

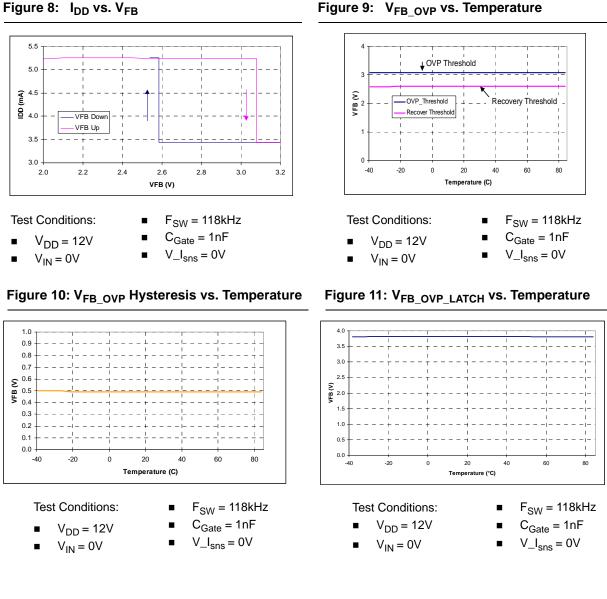

|   | Figure 8:  | I <sub>DD</sub> vs. V <sub>FB</sub>                                | 27   |

|   | Figure 9:  | VFB_OVP vs. Temperature                                            | 27   |

|   | Figure 10: | VFB_OVP Hysteresis vs. Temperature                                 | 27   |

|   | Figure 11: | VFB_OVP_LATCH vs. Temperature                                      | 27   |

|   | Figure 12: | Normal Regulation Reference (VFB_REG) vs. Temperature              | 28   |

|   | Figure 13: | Switching Frequency vs. Temperature                                | 28   |

|   | Figure 14: | Over Current (VIOVER) vs. Input Voltage VIN Peak Value)            | 29   |

|   | Figure 15: | Over Current (VIOVER) vs. Temperature                              | 29   |

| 5 | Design ar  | nd Applications Information                                        | 31   |

|   | Figure 16: | Internal Block for Zero-cross Detection, Brown-out Protection      | 32   |

|   | Figure 17: | Peak Detecting Signal for Predictive Sinusoidal AC Voltage         | 33   |

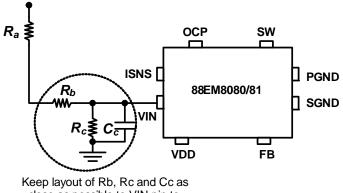

|   | Figure 18: | Input Voltage Resistor Divider Layout Guidelines                   | 34   |

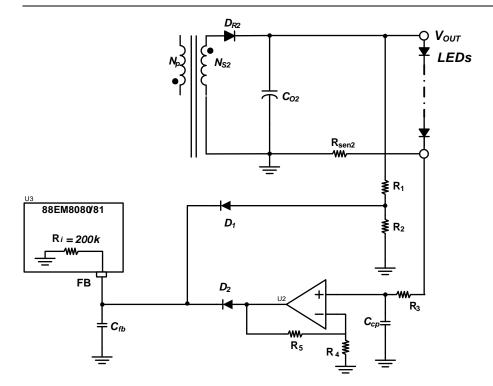

|   | Figure 19: | Non-Isolated Feedback Loop Schematic                               | 35   |

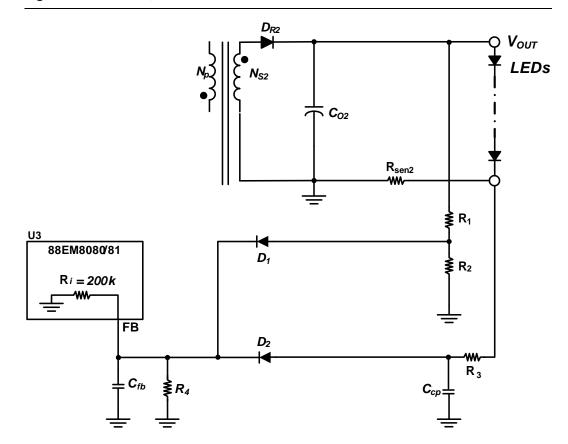

|   | Figure 20: | Low-cost, Non-isolated LED Current Control                         | 37   |

|   | Figure 21: | Isolated LED Current Control                                       | 38   |

|   | Figure 22: | Isolated LED Current Control with NTC Compensation                 | 42   |

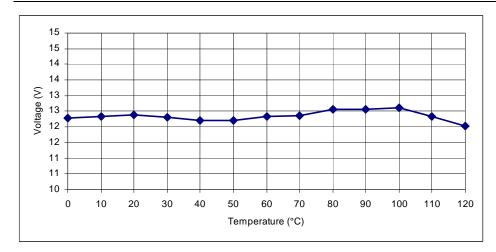

|   | Figure 23: | The Error Amplifier Output Voltage (VC) vs. Temperature            | 44   |

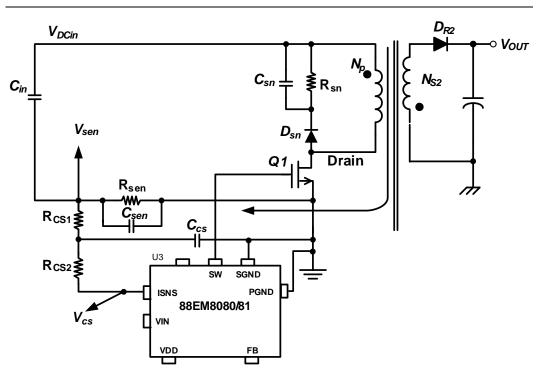

|   | Figure 24: | Current Sensing Circuit                                            | 46   |

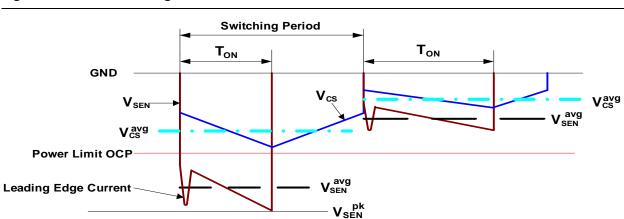

|   | Figure 25: | Current Sensing and Over Current Protection Waveforms              | 48   |

|   | Figure 26: | Current Sensing and Cycle by Cycle Over Current Protection Circuit | 49   |

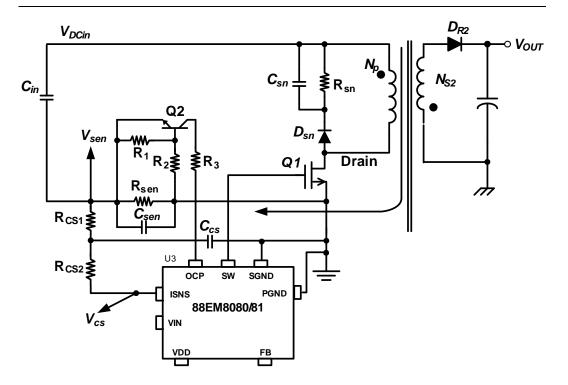

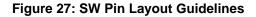

|   | Figure 27: | SW Pin Layout Guidelines                                           | 51   |

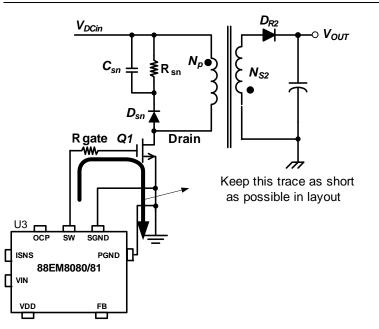

|   | Figure 28: | VDD Decoupling Capacitor and Ground Layout Guidelines              | 52   |

|   | Figure 29: | 1W Non-isolated LED Driver Schematic                               | 53   |

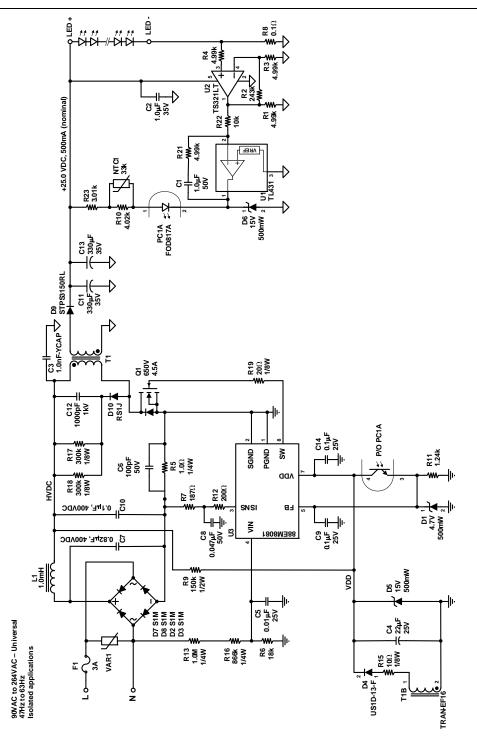

|   | Figure 30: | 12.5W Universal Isolated LED Driver Schematic | 55 |

|---|------------|-----------------------------------------------|----|

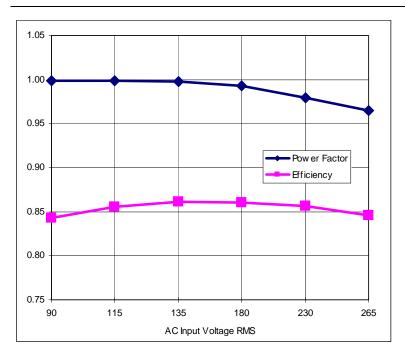

|   | Figure 31: | Efficiency, Power Factor                      | 57 |

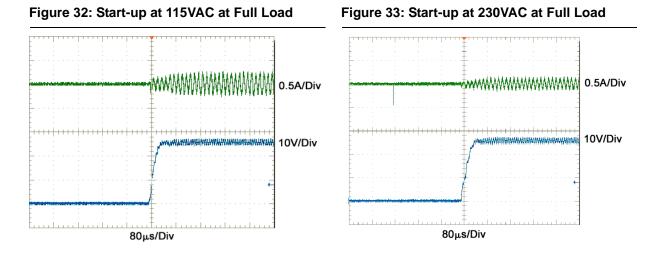

|   | Figure 32: | Start-up at 115VAC at Full Load               | 58 |

|   | Figure 33: | Start-up at 230VAC at Full Load               | 58 |

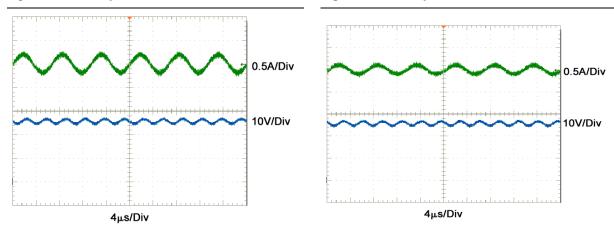

|   | Figure 34: | Steady State at 115VAC at Full Load           | 58 |

|   | Figure 35: | Steady State at 230VAC at Full Load           | 58 |

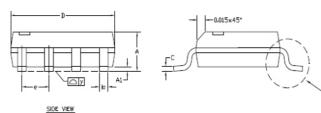

| 6 | Mechanic   | al Drawings                                   | 59 |

|   | Figure 36: | 8-Lead SOIC Mechanical Drawing                | 59 |

| 7 | Part Orde  | r Numbering/Package Marking                   | 61 |

|   | Figure 37: | Sample Ordering Part Number                   | 61 |

|   | Figure 38: | Package Marking                               | 62 |

|   |            |                                               |    |

# **List of Tables**

| 1 | Signal D  | escription                                                          | 11 |

|---|-----------|---------------------------------------------------------------------|----|

|   | Table 1:  | Pin Definitions                                                     | 11 |

|   | Table 2:  | Pin Descriptions                                                    | 12 |

| 2 | Electrica | Il Specifications                                                   | 15 |

|   | Table 3:  | Absolute Maximum Ratings                                            | 15 |

|   | Table 4:  | Electrical Characteristics                                          | 16 |

| 3 | Function  | al Description                                                      | 19 |

|   | Table 5:  | Functional Summary                                                  | 19 |

| 4 | Function  | al Characteristics                                                  | 25 |

| 5 | Design a  | Ind Applications Information                                        | 31 |

|   | Table 6:  | Comparison between Critical Transition Mode and Mixed Mode Controls | 32 |

|   | Table 7:  | Current Sensing Circuit                                             | 47 |

|   | Table 8:  | Current Sensing Resistor Selection Reference                        | 47 |

|   | Table 9:  | Efficiency and Power Factor Test Results                            | 57 |

| 6 | Mechani   | cal Drawings                                                        | 59 |

| 7 | Part Ord  | er Numbering/Package Marking                                        | 61 |

|   | Table 10: | 88EM8080/88EM8081 Part Order Options                                | 61 |

|   | Table 11: | Revision History                                                    | 63 |

THIS PAGE INTENTIONALLY LEFT BLANK

# **1** Signal Description

# 1.1 Pin Configurations

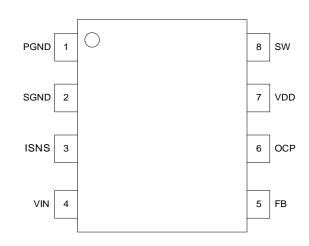

Figure 2: SOIC-8 Pin Diagram (Top View)

# 1.2 Pin Descriptions

#### Table 1: Pin Definitions

| Pin # | Pin Name | Pin Type | Pin Description         |

|-------|----------|----------|-------------------------|

| 1     | PGND     | GND      | Power Ground            |

| 2     | SGND     | GND      | Signal Ground           |

| 3     | ISNS     | Input    | Current Sense           |

| 4     | VIN      | Input    | Voltage Input           |

| 5     | FB       | Input    | Feedback                |

| 6     | OCP      | Input    | Over Current Protection |

| 7     | VDD      | Supply   | IC Supply Voltage       |

| 8     | SW       | Output   | Switch                  |

### Table 2: Pin Descriptions

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PGND     | <ul> <li>Power Ground</li> <li>Connected to the source of the primary MOSFET.</li> <li>The PCB trace from the power ground to the source of the primary MOSFET must be kept as short as possible.</li> <li>To avoid any switching noise interruption on signal processing, PGND and SGND remain seperate inside the IC.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2     | SGND     | <ul> <li>Signal Ground</li> <li>Must be connected to the power ground with the Kelvin sensing connection (typically connected to the source of the external MOSFET) so that SGND has dedicated trace and connections and provides clean signal integrity.</li> <li>To avoid any switching noise interruption on signal processing, SGND and PGND remain seperate inside the IC.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3     | ISNS     | <ul> <li>Current Sense</li> <li>Used for current shaping and for over current protection.</li> <li>Sense resistor varies for different loads.<br/>Examples - 0.15Ω at 120W rated load and 0.6Ω for 30W rated load.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4     | VIN      | <ul> <li>Voltage Input</li> <li>Connects to resistance divider at input AC line "phase" to GND. Voltage applied is a half rectified sine wave scaled down by the input resistance divider.</li> <li>Voltage input pin is a high impedance input pin. An impedance of 2M (typical) is recommended to be designed from the input AC "phase" to GND for the VIN resistor dividor network to reduce the standby power. Higher impedance is preferred with the right PCB design on this pin signal.</li> <li>This voltage input after comparing with an internal threshold reference is used to detect the zero-cross location of the input sine wave and is also used to synthesize (regenerate) the input sine wave. This regenerated sine wave is used for the current reference.</li> <li>Brown-out protection function is also provided by this pin. A resistor devider with a 100:1 ratio from the highside resistor to the lowside resistor is corresponding to a "brown-out protection" input voltage of 50V (RMS). Increasing that ratio will increase the "brown-out voltage". Brown-out voltage is determined by R<sub>6</sub>, R<sub>13</sub> and R<sub>16</sub> as shown in Figure 1. Refer to Section 5.2 for further understanding.</li> </ul> |

| 5     | FB       | <ul> <li>Feedback</li> <li>The output voltage of 100% rated value is scaled to 2.5V at the FB Pin.</li> <li>Transition from soft-start to normal regulation is at 87.5% rated V<sub>FB</sub>. When FB pin voltage exceeds V<sub>FB_OVP</sub> the IC shuts down the SW pin driver pulse. SW pin driver pulse recovers when FB pin falls below the reference voltage, V<sub>FB_REG</sub>.</li> <li>There is another OVP latch threshold (V<sub>FB_OVP_LATCH</sub>) of 3.77V on the FB pin. When FB exceeds V<sub>FB_OVP_LATCH</sub>, latched over voltage shutdown occurs until another VDD power on resets the latch.</li> <li>The effective resistance between FB and GND is 200k (typical).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6     | OCP      | <ul> <li>Over Current Protection</li> <li>Used to turn off the MOSFET when it is pulled as logic low</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 2: Pin Descriptions

| Pin # | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | VDD      | <ul> <li>IC Supply Voltage</li> <li>Nominal voltage is 12V and the Under Voltage Lock Out (UVLO) occurs when V<sub>DD</sub> &lt; V<sub>DD_UVLO</sub> and the IC is turned off.</li> <li>The IC is turned on whenever V<sub>DD</sub> &gt; V<sub>DD_ON</sub> (typ. 11.9V).</li> <li>The maximum voltage on VDD is 16V.</li> <li>VDD should be clamped by a zener for protection in the system design. Refer to Table 4 for more details.</li> </ul> |

| 8     | SW       | <ul> <li>Switch</li> <li>PWM gate signal for the switch.</li> <li>It should be connected to the gate of external MOSFET through a gate resistor.</li> </ul>                                                                                                                                                                                                                                                                                       |

#### THIS PAGE INTENTIONALLY LEFT BLANK

# **2** Electrical Specifications

# 2.1 Absolute Maximum Ratings

#### Table 3: Absolute Maximum Ratings<sup>1</sup>

**NOTE:** Stresses above those listed in Absolute Maximum Ratings may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

| Symbol            | Parameter                                        | Min  | Max   | Units |

|-------------------|--------------------------------------------------|------|-------|-------|

| V <sub>DD</sub>   | Power Supply (Voltage to PGND=SGND)              | -0.3 | 18    | V     |

| V <sub>Isns</sub> | Voltage at ISNS pin                              | -0.5 | 0.5   | V     |

| V <sub>OCP</sub>  | Voltage at OCP pin                               | -0.3 | 5.5   | V     |

| V <sub>VIN</sub>  | Voltage at VIN pin                               | -0.3 | 5.5   | V     |

| V <sub>FB</sub>   | Voltage at FB pin                                | -0.3 | 5.5   | V     |

| I <sub>SW</sub>   | Driver Current (Instantaneous Peak)              |      | 2     | A     |

| $\theta_{JA}$     | Thermal Resistance                               |      | 156.5 | °C/W  |

| T <sub>A</sub>    | Operating Ambient Temperature Range <sup>2</sup> | -40  | 85    | °C    |

| Tj                | Maximum Junction Temperature                     |      | 125   | °C    |

| T <sub>STOR</sub> | Storage Temperature Range                        | -65  | 150   | °C    |

| V <sub>ESD</sub>  | ESD Rating <sup>3</sup>                          |      | 2     | kV    |

1. Exceeding the absolute maximum rating may damage the device.

2. Specifications over the -40°C to 85°C operating temperature ranges are assured by design, characterization and correlation with statistical process controls.

3. Devices are ESD sensitive. Handling precautions recommended. Human Body model, 1.5k $\Omega$  in series with 100pF.

# 2.2 Electrical Characteristics

#### Table 4: Electrical Characteristics

**NOTE:** A 12V supply voltage is applied and the ambient temperature  $(T_A) = 25^{\circ}C$ .

| Symbol                   | Parameter                                      | Conditions                                                             | Min  | Тур  | Max | Units |

|--------------------------|------------------------------------------------|------------------------------------------------------------------------|------|------|-----|-------|

| V <sub>DD</sub> Supply   |                                                | ·                                                                      |      |      |     |       |

| V <sub>DD</sub>          | Supply Voltage                                 |                                                                        | 7.0  | 12   | 16  | V     |

| V <sub>DD_ON</sub>       | V <sub>DD</sub> Power On Threshold             |                                                                        |      | 11.9 |     | V     |

| V <sub>DD_UVLO</sub>     | V <sub>DD</sub> Power Off Threshold<br>(UVLO)  | After V <sub>DD</sub> is powered up and running                        |      | 7.0  |     | V     |

| V <sub>DD_UVLO_HYS</sub> | V <sub>DD_UVLO</sub> Hysteresis                |                                                                        | 4.8  |      | 5   | V     |

| I <sub>DD_QST</sub>      | V <sub>DD</sub> Quiescent Current <sup>1</sup> | V <sub>DD</sub> = 12V                                                  |      | 95   |     | μΑ    |

| I <sub>DD_OP</sub>       | V <sub>DD</sub> Operating Current              | $V_{DD} = 12V;$<br>$C_{Gate} = 1nF$<br>$F_{SW} = 118kHz$<br>$V_{IN}=0$ |      | 5.2  |     | mA    |

| Thermal Shutdo           | wn                                             |                                                                        |      |      |     |       |

| T <sub>SD</sub>          | Thermal Shutdown                               |                                                                        |      | 150  |     | °C    |

| T <sub>SD_HYS</sub>      | Hysteresis for Thermal<br>Shutdown             |                                                                        | 25   |      |     | °C    |

| Output Gate Driv         | /er                                            |                                                                        |      |      |     |       |

| V <sub>G_HI</sub>        | Minimum Gate High Voltage <sup>2</sup>         | V <sub>DD</sub> = 12V<br>C <sub>Gate</sub> = 1nF<br>Sourcing 500mA     | 10.0 |      |     | V     |

| V <sub>G_LO</sub>        | Maximum Gate Low<br>Voltage <sup>3</sup>       | $V_{DD} = 12V$<br>$C_{Gate} = 1nF$<br>Sinking 500mA                    |      |      | 2.0 | V     |

| R <sub>DSON</sub>        | Gate Drive Resistance                          | Sourcing 120mA<br>T=25°C                                               |      | 2.4  |     | Ω     |

|                          | Gate Drive Resistance                          | Sinking 120mA<br>T=25°C                                                |      | 2.0  |     | Ω     |

| I <sub>SW_PK</sub>       | Driver Peak Current                            | C <sub>Gate</sub> = 10nF<br>V <sub>DD</sub> = 12V                      |      | 1.2  |     | A     |

| t <sub>R</sub>           | Rise Time                                      | C <sub>Gate</sub> = 1 nF                                               |      | 35   |     | ns    |

|                          |                                                | C <sub>Gate</sub> = 10 nF                                              |      | 125  |     | ns    |

| t <sub>F</sub>           | Fall Time                                      | C <sub>Gate</sub> = 1 nF                                               |      | 35   |     | ns    |

|                          |                                                | C <sub>Gate</sub> = 10 nF                                              |      | 145  |     | ns    |

| D <sub>MAX</sub>         | Maximum Duty Cycle                             |                                                                        |      |      | 88  | %     |

#### Table 4: Electrical Characteristics (Continued)

**NOTE:** A 12V supply voltage is applied and the ambient temperature  $(T_A) = 25^{\circ}C$ .

| Symbol                    | Parameter                                                                                       | Conditions                                                                                                          | Min | Тур  | Max | Units |

|---------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| D <sub>MIN</sub>          | Minimum Duty Cycle <sup>4</sup>                                                                 |                                                                                                                     | 3   |      |     | %     |

| Feedback/Overv            | oltage                                                                                          |                                                                                                                     |     |      | 1   | 1     |

| V <sub>FB_REG</sub>       | Normal Regulation<br>Reference                                                                  | IC powered on                                                                                                       |     | 2.55 |     | V     |

| V <sub>FB_OVP</sub>       | Over Voltage Protection<br>Threshold                                                            | At 120% of V <sub>FB_REG</sub> .                                                                                    |     | 3.04 |     | V     |

| V <sub>FB_OVP_HYS</sub>   | Over Voltage Protection<br>Hysteresis                                                           |                                                                                                                     |     | 0.49 |     | V     |

| V <sub>FB_OVP_LATCH</sub> | Over Voltage Protection<br>Latch                                                                |                                                                                                                     |     | 3.77 |     | V     |

| Current Sensing           | and Current Protection <sup>5</sup>                                                             | -                                                                                                                   |     |      |     |       |

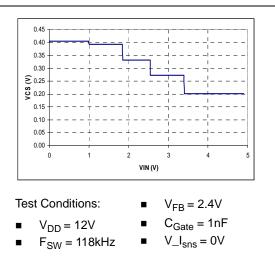

| VIOVER_TH1                | Over Current Threshold<br>Zone 1 <sup>6</sup>                                                   | Peak value of half-sine<br>voltage at V <sub>IN</sub> :<br>1.26 <v<sub>IN&lt;1.89V<sub>pk</sub><sup>7</sup></v<sub> |     | 397  |     | mV    |

| V <sub>IOVER_TH2</sub>    | Over Current Threshold<br>Zone 2 <sup>5</sup>                                                   | Peak value of half-sine<br>voltage at V <sub>IN</sub> :<br>1.89 <v<sub>IN&lt;2.59V<sub>pk</sub><sup>8</sup></v<sub> |     | 329  |     | mV    |

| V <sub>IOVER_TH3</sub>    | Over Current Threshold<br>Zone 3 <sup>5</sup>                                                   | Peak value of half-sine<br>voltage at V <sub>IN</sub> :<br>2.59< V <sub>IN</sub> <3.43V <sub>pk</sub> <sup>9</sup>  |     | 269  |     | mV    |

| V <sub>IOVER_TH4</sub>    | Over Current Threshold<br>Zone 4 <sup>5</sup>                                                   | Peak value of half-sine voltage at $V_{IN}$ :<br>3.43< $V_{IN}$ <3.85 $V_{pk}$ <sup>10</sup>                        |     | 202  |     | mV    |

| V <sub>IOVER_CYC</sub>    | Cycle by cycle current<br>protection logic input (OCP<br>pin) threshold for SW on <sup>11</sup> |                                                                                                                     |     | 1.68 |     | V     |

| 88EM8080 Switc            | hing Frequency Oscillator                                                                       |                                                                                                                     |     |      | 1   | 1     |

| F <sub>SW</sub>           | Frequency<br>(Average Mode)                                                                     |                                                                                                                     |     | 59   |     | kHz   |

| 88EM8081 Switc            | hing Frequency Oscillator                                                                       | -                                                                                                                   |     | -    |     |       |

| F <sub>SW</sub>           | Frequency<br>(Average Mode)                                                                     |                                                                                                                     |     | 118  |     | kHz   |

1.  $V_{DD}$  Quiescent Current:  $V_{DD}$  power supply current before  $V_{DD}$  first time reaches  $V_{DD_{-}ON}$ .

2. Considering the voltage drop on the internal driver MOSFET during current sourcing.

3. Considering the voltage drop on the internal driver MOSFET during current sinking.

- 4. If the duty cycle is less than 3% from the DSP calculations, one PWM cycle is skipped and this duty-cycle value is added to the next PWM duty cycle calculation.

- 5. To achieve almost constant power limit for the universal input range, current protection self-adjusts thresholds in four zones of input voltage levels. A margin of 50% compared to the rated current is considered for the threshold current values.

- 6. Threshold of negative voltage drop across  $\mathsf{R}_{\mathsf{sns}}$  due to instantaneous current

- 7. With input divider ratio of 1/100, these values are equivalent to 90 V<sub>rms</sub><V<sub>line</sub><135 V<sub>rms</sub>. (Section 5.2, equation (1))

- 8. With input divider ratio of 1/100, these values are equivalent to 135 V<sub>rms</sub>-V<sub>line</sub><185 V<sub>rms</sub>. (Section 5.2, equation (1))

- 9. With input divider ratio of 1/100, these values are equivalent to  $185 V_{rms} < V_{line} < 245 V_{rms}$ . (Section 5.2, equation (1))

- 10.With input divider ratio of 1/100, these values are equivalent to 245 V<sub>rms</sub><V<sub>line</sub><275 V<sub>rms</sub>. (Section 5.2, equation (1))

- 11.0CP falling threshold for V<sub>IOVER CYC</sub> is 1V with a hysteresis of 0.68V.

# **3** Functional Description

## 3.1 Overview

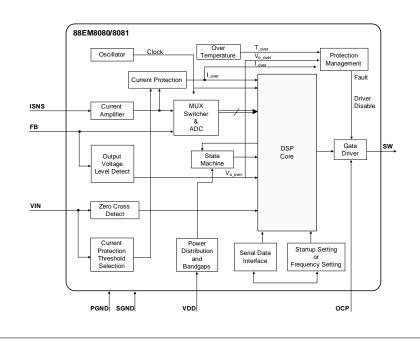

The 88EM8080/88EM8081 is a high-performance power factor correction controller for single stage flyback LED lighting applications with a minimum number of components at a low cost. The following section outlines the functions of various input and output signals of the 88EM8080/88EM8081 device as listed below in Table 5.

| Section       | Pin Name  | Function                                                                                       |

|---------------|-----------|------------------------------------------------------------------------------------------------|

| Section 3.2   | VDD       | Bias power for IC                                                                              |

| Section 3.3   | PGND/SGND | Power and signal ground is the return for power and signals                                    |

| Section 3.4   | SW        | Gate drive output                                                                              |

| Section 3.5   | VIN       | Input voltage sensing and brown-out protection                                                 |

| Section 3.6   | FB        | Inverting input of an internal error amplifier used for regulation of output voltage / current |

| Section 3.7   | ISNS      | Input current sensing used for providing PFC and for adaptive over current protection          |

| Section 3.7.3 | OCP       | Over current protection used for cycle by cycle protection                                     |

#### Table 5: Functional Summary

#### Figure 3: Top Level Block Diagram

Note

$I_{\_over},\,V_{o\_over}$  and  $T_{\_over}$  are the over current, over voltage, and over temperature signals respectively.

# 3.2 VDD – Bias Power Input

The controller needs bias power which is recieved through the VDD and PGND pins. The nominal voltage for the VDD pin is around 12 Volts and the IC will start switching as long as the VDD voltage exceeds the  $V_{DD_ON}$  Power-on threshold described in Table 4, Electrical Characteristics, on page 16. The PWM switched output at the SW pin is available after the IC is switched on. Once powered up and switching has started, the VDD voltage can reach as low as 7 Volts (typical), at which point the IC is switched off. This 7 volt threshold is the under voltage lockout (UVLO) value. Once VDD goes below the UVLO threshold voltage, VDD must climb back to the V<sub>DD\_ON</sub> threshold to start switching once again. The maximum voltage needs to be less than 16 volts which provides some margin from an absolute maximum VDD voltage rating of 18 Volts. When the IC is not switching (less than 12 volts before turn-on and less than 7 volts after turn-on), the 88EM8080/88EM8081 draws very little quiescent current which has a typical rating of 95 $\mu$ A. During switching, the operating current from the VDD source is around 5.2mA.

From a circuit design point of view, bias can be provided initially from the rectified low frequency AC input. Once the IC starts switching, bias power can be derived from the high frequency part of the circuit. As an example, an auxiliary winding on the flyback transformer can be used to provide this high frequency power. It is necessary to rectify the high frequency AC from the auxiliary winding and to have necessary filtering to reduce the high frequency ripple at the VDD pin. This approach of providing high frequency bias power after turn-on will improve the efficiency of the bias power circuitry in the steady state. It should be noted that during startup, at the instant of switching, the current drawn by the chip increases from  $95\mu$ A to 5.2mA (typical). This sudden step load of bias power will tend to decrease the VDD voltage. If the VDD voltage falls below 7 volts due to this reason, the IC will go through another starting cycle. To prevent this hiccup, adequate energy storage (capacitor) needs to be provided. The capacitors across VDD and PGND will help to keep the VDD voltage above 7 volts.

Care is also needed in the design of bias power circuit from the rectified low frequency AC side. If a simple resistance is used to charge the capacitor across VDD and PGND, the turn-on time could be longer. Variations in the bias circuit design may be accommodated to meet the specified turn-on time.

The under voltage lockout (UVLO) feature can be used to shut off the IC during a fault condition by forcing the VDD voltage to go below 7 volts. If the fault is removed, VDD voltage can be allowed to increase to VDD\_ON and the IC will go through a new starting cycle.

## 3.3 PGND and SGND

The 88EM8080/88EM8081 has separated the power ground pin (PGND) and signal ground pin (SGND) inside the IC to avoid any noise interruption during signal processing. The PGND pin should be connected to the primary MOSFET source pin and the connection trace should be as short as possible. The SGND must be connected to the PGND through a Kelvin sensing connection trace to achieve a clean signal ground.

## 3.4 SW – Switched PWM Output for Gate Drive

The SW pin is the PWM output pin for the IC. The IC has an internal totem pole drive circuit to drive the gate of an external power MOSFET through this SW pin. A gate resistor is recommended to provide damping in the external drive circuit and to minimize the parasitic ringing. The PWM output gate drive capibility is 1.2A (typical). If necessary, additional drive circuitry along with speed up circuitry can be added to the SW pin output for very high power levels.

## 3.5 VIN – Input Voltage Sensing

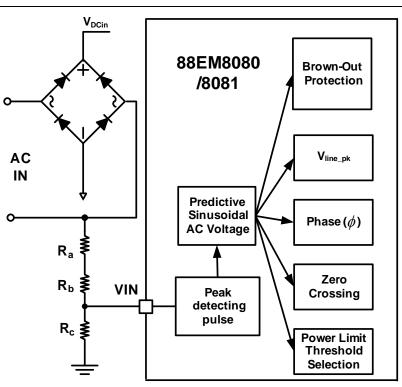

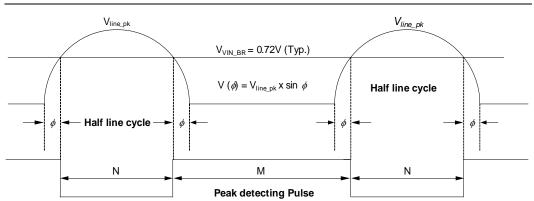

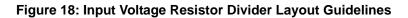

The PFC function is implemented by sensing the input current waveform and forcing the average of the input current to follow the input voltage sinusoidal waveform. A resistor divider is used between AC input and a primary reference ground to sense the input voltage. The primary reference ground is connected to the 88EM8080/88EM8081 IC reference ground and to the source pin of the external switching MOSFET Q1 as in Figure 1, Universal Isolated LED Driver with PFC, on page 3. The output of the resistor divider which is a half sinusoidal waveform is the input to the VIN pin. By sensing the input voltage waveform at the VIN pin, the controller can generate its own internal sinusoidal reference at the same frequency as the input. This is done by having an internal DC threshold (0.72 Volts), a comparator and a zero-cross detection circuit. The details of the calculations are described in Section 5.2.

It is recommended to use a high impedance divider network between the AC line to reference AC ground to sense the input voltage at the VIN pin. This will help to reduce the no load input power and will improve the efficiency in general. Due to the VIN pin being a high impedance input pin, a 10nF (typical) decoupling noise capacitor between it and ground is required.

## 3.5.1 Brown-out Protection

VIN pin is also used for the brown-out protection function. A resistor divider of 100:1 ratio from the high voltage side corresponds to a brown-out protection input voltage of around 50V RMS for the defined internal threshold of 0.72 Volts. Increasing the high voltage divider turns ratio will increase brown-out protection voltage.

# 3.6 FB – Output Voltage / Current Feedback

The 88EM8080/88EM8081 has an internal current loop and output voltage/current loop to implement the PFC and the output voltage/current regulating function. FB pin is the inverting input of a voltage error amplifier with 2.5 volts as the internal reference voltage. For steady state operation 100% of required output voltage/current is scaled to 2.5V at the feedback pin by external circuitry. For output current regulation, the much smaller voltage across the load current sensing resistor could be amplified to be 2.5V and then applied to the FB pin.

During startup, when FB pin is below 87.5% of the reference voltage, the PFC controller operates in soft-start mode. The internal voltage error amplifier switches over to normal regulation phase once the FB pin voltage reaches 87.5% of the reference value.

## 3.6.1 FB – Over Voltage Protection (OVP)

Over voltage protection is implemented through the FB pin. When the FB pin voltage exceeds VFB\_OVP threshold voltage (refer to Table 4, Electrical Characteristics, on page 16), the IC is switched off and no PWM output is available at SW pin of the IC.

## 3.6.2 FB – Regulation

#### 3.6.2.1 Output Current Regulation - Isolated Output

The general application for 88EM8080/88EM8081 is for LED current control. The LED current is passed through a series sense resistor and the voltage across that resistor is proportional to the LED current. This sense resistor needs to be very small to limit the power dissipation in the resistor. The sensed voltage is then amplified to have 2.5V at the full load current. It is applied to the TL431 type of device where the error voltage between the amplified voltage and TL431 device reference (2.5V) is amplified. An optocoupler can be used to pass the error information to the feedback pin FB on the primary side. In addition the primary current is sensed and the average current is adjusted to be sinusoidal (in phase with AC input Voltage). The amplitude of the primary current is adjusted to make the secondary LED current constant at the desired level. Because this is a single stage PFC there will be second harmonic ripple at the output. Output capacitors are added to reduce the output second harmonic ripple and also the high frequency switching ripple. The proportional and integral compensation within the IC make the system stable. The over voltage protection at the output can be achieved by clamping the output of TL431.

It is well known that CTR of an optocoupler varies with temperature and there is a CTR variation among different units of the same optocoupler. An NTC circuit can be designed to help reduce the effect of variation of CTR. The entire circuit design of the NTC circuit is provided in Section 5.3.5.

It is important to note that the IC has internal compensation for the loop stability.

#### 3.6.2.2 Output Current Regulation - Non-isolated Output

The application is similar to the isolated example (Section 3.6.2.1) except there is no optocoupler. The LED current is passed through a series sense resistor and the voltage across that resistor is proportional to the LED current. This sense resistor needs to be very small to limit the power dissipation in the resistor. The sensed voltage is then amplified to be 2.5V at the full load current. To reduce the number of components the amplifier can be eliminated. In this case, a higher valued sense resister should be used to get the sense voltage equal to 2.5V at full load. It is to be noted that this will reduce the over all efficiency of the LED driver.

To have over voltage protection, the output voltage also can be sensed and diode or'ed to the output of the current sensing circuit. Initially voltage loop takes over because the LED load needs a minimum voltage to turn on. The voltage from the current sensing side is designed to be higher than the voltage from voltage sensing diode during normal operation. Also the voltage sensing helps to limit the output voltage, if one of the LEDs becomes open for any reason. The proportional and integral compensation within the IC make the system stable.

### 3.6.2.3 Output Voltage Regulation - Isolated Output

The output voltage is sensed through a divider resistor and a TL431 type of device can be used to amplify the error voltage from a reference voltage. An optocoupler can be used to pass the error information to the feedback pin FB on the primary side for isolating the output. In addition, the primary current is sensed and the average current is adjusted to be sinusoidal (in phase with AC input Voltage). The amplitude of the primary current is adjusted to make the secondary voltage constant at the desired level. Because this is a single stage PFC there will be second harmonic ripple at the output. Output capacitors are added to reduce the output second harmonic ripple and also the high frequency switching ripple. The proportional and integral compensation within the IC make the system stable. The over voltage protection at the output can be achieved by clamping the output of TL431.

It is well known that Current Transfer Ratio (CTR) of an optocoupler varies with temperature and there is also a CTR variation among different units of the same optocoupler. An NTC circuit can be designed to help reduce the effect of variation of CTR.

It is important to note that the IC has internal compensation for the loop stability. There is no need for external compensation.

#### 3.6.2.4 Output Voltage Regulation - Non-isolated Output

When non-isolated, an opto-isolator is not necessary. The output voltage is sensed through the output divider and the output of the divider is connected directly to the feedback pin FB. The IC then controls the output voltage in the same way as for the isolated case. It is important to note that the IC has internal compensation for the loop stability.

## 3.7 ISNS – Current Sensing / Over Current Protection

## 3.7.1 ISNS – Peak Current Sensing

The 88EM8080/88EM8081 LED driver provides power factor correction (PFC) in addition to providing regulation. Regarding the PFC function, the average input current is varied to be proportional to the input voltage. This way the average input current will be sinusoidal. This input current is the same as the primary MOSFET current in a flyback circuit. Therefore, the IC can sense the MOSFET current and then use average current mode control to implement the PFC function. The voltage across the resistor in series with MOSFET (connected between MOSFET source pin and bridge diode negative DC terminal) is used as primary current sensing signal. The primary MOSFET source pin is grounded to apply a PWM signal between the gate and the source. The current sense signal in series MOSFET source therefore becomes negative with respect to ground. The IC uses this negative signal for input current control to provide the PFC function.

## 3.7.2 ISNS – Average Current Mode Control

The voltage across the primary current sense resistor is proportional to the peak value of switching current. An RC filter can be used to provide the average current. The output of the RC filter is then applied to ISNS pin. The internal current loop adjusts the duty cycle so that average current is sinusoidal. The amplitude of the sinusoidal current is adjusted by the external voltage/current loop to achieve constant output load voltage/current.

## 3.7.3 ISNS – Adaptive Over Current Protection

The average current signal at the output of the RC filter is also used for over current protection. The IC has an internal current comparator with four different internal thresholds for current protection on ISNS pin as the input voltage signal varies. The input current varies inversely with the AC input voltage. There are four different OCP thresholds at four different input voltage ranges. The different thresholds; V<sub>IOVER\_TH1</sub>, V<sub>IOVER\_TH2</sub>, V<sub>IOVER\_TH3</sub> and V<sub>IOVER\_TH4</sub> are detailed in Table 4, Electrical Characteristics, on page 16. With these four adaptive over current protection steps the IC provides almost constant power protection over the entire AC input voltage range.

## 3.7.4 OCP – Cycle by Cycle Over Current Protection

The voltage across the primary current sense resistor is proportional to the peak value of switching current. This voltage can be used for cycle by cycle over current protection by the OCP pin. When the OCP pin is pulled low the IC will shut down and there is no switched output signal at SW pin.

# 3.8 Mixed Modes of Operation

The 88EM8080/88EM8081 controller operates in Continuous Conduction Mode (CCM) or Discontinuous Mode (DCM) modes of operation. The transformer primary inductance and the load determine the modes of operation. The CCM mode will have lower peak current than the discontinuous mode of operation. At high power levels CCM is recommended because of reduction of copper losses in the transformer and also the conduction losses in the primary MOSFET. In addition CCM could reduce the input filter size. DCM mode may be recommended at lower power levels to reduce the turn-on switching losses and the Primary FET losses due to reverse recovery time and charge of the output diode.

## 3.9 Compensation and Adaptive Control Loop

The LED current control is a feedback control system. The bandwidth of the voltage loop for the single stage LED feedback control system has to be much less than twice the line frequency to provide a high power factor and low THD. The entire feedback system needs to be designed for high power factor and low THD at low line (90-132VAC) and high line (180-264VAC). Marvell has an internal proportional and integral gain control feature for the voltage loop due to Marvell's DSP Control Technology. This means by sensing the input voltage, the IC sets PI control automatically to change the bandwidth for different AC input line ranges. This innovative adaptive feature will help achieve low THD and high power factor at all lines and loads. Because of this proportional and integral control within the IC, no external compensation is required for non-isolated outputs. Minimal external compensation is required for isolated outputs mainly for the compensation on the error amplifier (TL431) at the secondary side. This compensation network provides enough attenuated and not amplified.

## 3.10 Over Temperature Protection

The 88EM8080/88EM8081 IC has an internal over temperature sensing circuit. On over temperature, the fault detection signal shuts off the PWM switching output at the SW pin.

## 4 **Functional Characteristics**

The following applies unless otherwise noted:  $V_{IN} = 60$ Hz half-wave sinusoidal from 0V to the peak voltage (V<sub>PK</sub>) given in the test conditions of each graph.  $T_A = 25^{\circ}C$ .

Figure 5b: I<sub>DD</sub> vs. V<sub>DD</sub> (V<sub>DD</sub> ON)

All measurement readings are typical.

#### 4.1 **V<sub>DD</sub>** Characteristics

Figure 5a: I<sub>DD</sub> vs. V<sub>DD</sub> (V<sub>DD ON</sub>)

VDD Falling VDD Falling VDD Rising VDD Rising **(Yuu) 001** 3 IDD (mA) 10 8 VDD (V) 12 14 6 12 14 16 VDD (V)  $V_{FB} = 0V$  $V_{FB} = 2.4V$ **Test Conditions: Test Conditions:**  $C_{Gate} = 1nF$ C<sub>Gate</sub> = 1nF  $V_{IN} = 0V$  $V_{IN} = 0V$  $V_{I_{sns}} = 0V$  $V_{I_{sns}} = 0V$  $F_{SW} = 118 kHz$

$F_{SW} = 118 kHz$

(mA)

ē

# Figure 6a: I<sub>DD</sub> Operation (I<sub>DD\_OP</sub>) vs. Temperature

Figure 7: V<sub>DD</sub> On/Off vs. Temperature

$V_{IN} = 0V$

$F_{SW} = 118 \text{kHz}$

- $F_{SW} = 118$ kHz

- $V_{I_{sns}} = 0V$

# Figure 6b: I<sub>DD</sub> Operation (I<sub>DD\_OP</sub>) vs. Temperature

80

- $V_{IN} = 0V$

- $F_{SW} = 118 \text{kHz}$ .

- $V_{I_{sns}} = 0V$

Doc. No. MV-S106340-01 Rev. B Page 26

#### **V<sub>FB</sub>** Characteristics for Over Voltage Protection 4.2

Figure 9: V<sub>FB OVP</sub> vs. Temperature

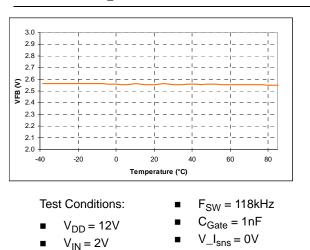

Figure 12: Normal Regulation Reference (V<sub>FB REG</sub>) vs. Temperature

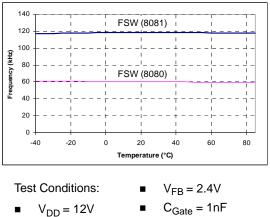

#### **Switching Frequency Characteristics** 4.3

- $V_{IN} = 0V$

- $V_{I_{sns}} = 0V$

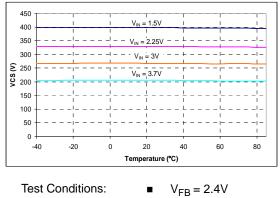

#### **Over Current Threshold Characteristics** 4.4

Figure 15: Over Current (V<sub>IOVER</sub>) vs. Temperature

- $V_{DD} = 12V$

- $F_{SW} = 118 kHz$

- $C_{Gate} = 1nF$

- $V_{I_{sns}} = 0V$

THIS PAGE INTENTIONALLY LEFT BLANK

# **Design and Applications Information**

## 5.1 Overview

The 88EM8080/88EM8081 is a PWM controller for LED applications with PFC. Flyback topology is used to simplify the two stage (front-end PFC and output stages) design to a single stage that includes Power Factor Correction (PFC) and regulation of the output. Compared to the two stage structure, a single stage with PFC is a more cost effective solution for LED lighting applications. The following sections provide guidelines for the application design, component selection, and board layout in order to improve LED application performance with PFC based on the flyback topology.

The 88EM8080/88EM8081 IC control algorithm uses Average Current Mode Control for power factor correction applications with low harmonic distortion and good noise immunity. The IC senses the output current and forces it to follow the reference LED current matching the design requirements. The chip also senses the primary current and forces the average signal of the primary current to follow the sinusoidal current reference, therefore achieving power factor correction. This is possible because the bandwidth of the outer current/voltage loop is much smaller than twice the line frequency. This IC implements the adaptive loop control so that the LED power supply achieves high power factor even under high input voltage and low load conditions. The device also provides strong gate drive capability of 1.2A (typical).

There are four analog input signals and one logic output signal for the 88EM8080/88EM8081 controller.