# 3

# PACE 1757M/ME COMPLETE EMBEDDED CPU SUBSYSTEM

#### **FEATURES**

Implements complete MIL-STD-1750A ISA including optional MMU, MFSR, and BPU functions.

- Two throughput options: P1757M 2.5MIPSUSAF Dais Mix(Inc. Fit. Pt.)@40MHz P1757ME 3.6MIPSUSAF Dais Mix(Inc. Fit. Pt.)@40MHz

- All MIL-STD-1750A data formats and address types implemented.

- P1757ME includes additional matrix and vector instructions to enhance throughput in navigation, DSP transcendental, and other complex algorithms.

- Error detection and correction and parity bit provided.

- Separate high drive external address & data busses.

- 10MHz data rate at 40MHz CPU clock

- System support functions included in P1757M:

- Arbitratorforuse intightly coupled multiprocessordesign.

Bus control provided to aid in implementation of multiprocessor systems.

- MIL-STD- 1 750A timers A & B, programmable watch dog timer and programmable bus time-out function.

- · Start up ROM support per MIL-STD-1750A.

- DMA support for logical and physical memory addresses.

- Programmable memory and I/O data wait state generation permits up to four different memory speeds in the same system.

- · Programmable address wait states.

- Sixteen levels of interrupts are provided per MIL-STD-1750A. Interrupts can be either edge- or level-sensitive.

- Fault detection and handling

- Programmable detection of unimplemented memory or illegal I/O addresses.

- Full implementation of MIL-STD-1750A fault register.

- · External address error detection.

- Testability and diagnostics.

- · First failing address and data registers.

- Built in test runs automatically at power on and after each reset. All hardware blocks and external busses examined. Hardware pass/fail for catastrophic failures. Status register indicates failed test.

- Console operating mode which allows operator to examine and change contents of registers within the CPU, any system memory location, or the I/O subsystems.

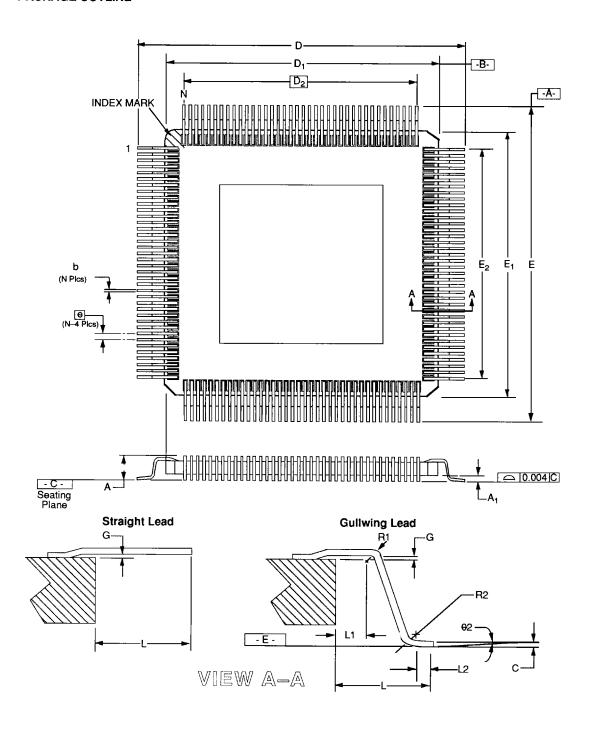

- Single 144-pin Quad straight lead or Gullwing 1.5 square inches of board surface.

- Operating temperature range 55 to +125°C; single 5V ± 10% Vcc power supply; power dissipation <1.9W (worst case at 40 MHz).

#### DESCRIPTION

All function srequired for a complete MIL-STD 1750A embedded CPU subsystem are in this single VLSI microcircuit occupying 1.5 square inches of board space with less than 1.9 watts of power dissipation at 40 MHz. Performance's PR1757M/ME is a complete, single package, 3.6 MIPS subsystem solution to embedded processor requirements.

The PACE 1757M uses the application-proven PACE 1750A microprocessor, the PACE1753, PACE1754, or the enhanced PACE1750AE microprocessor, which has additional instructions that provide high throughput for transcendental functions, navigational algorithms, and DSP functions. The PACE 1750AE is an architectural enhancement of the PACE 1750A.

Means Quality, Service and Speed

#### **PACE 1757 PINOUT**

# **AC/DC ELECTRICAL SPECIFICATIONS**

#### **MAXIMUM RATINGS**

(Above which the useful life may be impaired)

| Storage Temperature             | -65°C to +150°C     |  |  |  |

|---------------------------------|---------------------|--|--|--|

| Ambient Temperature with Power  | -55°C to +125°C     |  |  |  |

| Vcc Pin Potential to Ground Pin | -0.5V to 7.0V       |  |  |  |

| Input Voltage                   | -0.5V to Vcc + 0.5V |  |  |  |

| Input Current                   | -30 mA to 5 mA      |  |  |  |

| Voltage Applied to Inputs       | -0.5V to Vcc + 0.5V |  |  |  |

| Current Applied to any Output   | 100 mA              |  |  |  |

| Power Dissipation               | 2.5 Watts           |  |  |  |

| ӨЈА                             | 35°C/W              |  |  |  |

#### RECOMMENDED OPERATING CONDITIONS

| Grade      | Case Temperature | GND | Vcc         |

|------------|------------------|-----|-------------|

| Military   | -55°C to +125°C  | 0V  | 5.0V+/- 10% |

| Commercial | 0°C to +70°C     | 0V  | 5.0V+/- 10% |

#### DC ELECTRICAL SPECIFICATIONS

(Over recommended operating conditions)

| Symbol          | Parameter                                                                           | Min                  | Тур | Max                  | Unit | Conditions              |

|-----------------|-------------------------------------------------------------------------------------|----------------------|-----|----------------------|------|-------------------------|

| V <sub>IH</sub> | Input HIGH Level                                                                    | 2.0                  |     | V <sub>cc</sub> +0.5 | ٧    |                         |

| V <sub>IL</sub> | Input LOW Level <sup>2</sup>                                                        | -0.5                 |     | 0.8                  | V    |                         |

| V <sub>cD</sub> | Input clamp diode voltage                                                           |                      |     | -1.2                 | V    | I <sub>IN</sub> =-18mA  |

| Į.              |                                                                                     |                      |     |                      |      | V <sub>cc</sub> = Min   |

| V <sub>OH</sub> | Output HIGH Voltage                                                                 | 2.4                  |     |                      | ٧    | I <sub>OH</sub> =-8mA   |

| Ì               |                                                                                     |                      |     |                      | V    | I <sub>OH</sub> =-300μA |

|                 |                                                                                     | V <sub>cc</sub> -0.2 |     |                      |      | V <sub>cc</sub> = Min   |

| V <sub>OL</sub> | Output LOW Voltage                                                                  |                      |     | 0.5                  | ٧    | I <sub>o∟</sub> =8mA    |

|                 | Except A <sub>0</sub> -A <sub>15</sub> , EXT ADR <sub>0</sub> -EXT ADR <sub>7</sub> |                      |     | 0.2                  | V    | I <sub>oL</sub> = 300μA |

|                 |                                                                                     |                      |     |                      |      | V <sub>cc</sub> = Min   |

|                 | Output LOW Voltage                                                                  |                      |     | 0.5                  | V    | I <sub>oL</sub> =20mA   |

|                 | A <sub>0</sub> -A <sub>15</sub> , EXT ADR <sub>0</sub> -EXT ADR <sub>7</sub>        |                      |     | 0.2                  | V    | I <sub>οι</sub> =300μΑ  |

|                 |                                                                                     |                      |     |                      |      | V <sub>cc</sub> = Min   |

| I <sub>IH</sub> | Input HIGH Current except IB <sub>0</sub> -IB <sub>15</sub> ,                       |                      |     |                      |      | V <sub>IN</sub> =Vcc    |

|                 | EDC₀-EDC₅,BUS BUSY, BUS LOCK,                                                       |                      |     | 10                   | μΑ   | V <sub>cc</sub> =Max    |

|                 | EXT ADR <sub>0</sub> -EXT ADR <sub>7</sub>                                          |                      |     |                      |      |                         |

|                 | Input HIGH Current IB <sub>0</sub> -IB <sub>15</sub> , EDC <sub>0</sub> -           |                      |     |                      |      | V <sub>IN</sub> =Vcc    |

|                 | EDC₅,BUS BUSY, BUS LOCK,                                                            |                      |     | 50                   | μА   | V <sub>cc</sub> =Max    |

|                 | EXT ADR0-EXT ADR,                                                                   |                      |     |                      |      |                         |

3-75 5/5/92

# **DC ELECTRICAL SPECIFICATIONS (Continued)**

(Over recommended operating conditions)

| Symbol                  | Parameter                                                                                                                                                                                                                                                       | Min | Тур | Max                      | Unit | Conditions                                                                                       |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|--------------------------------------------------------------------------------------------------|

| I <sub>IL</sub>         | Input LOW current except IB <sub>0</sub> -IB <sub>15</sub> , EDC <sub>0</sub> -EDC <sub>5</sub> , BUS BUSY, BUS LOCK, EXT ADR <sub>0</sub> -EXT ADR <sub>7</sub> , TEST ON                                                                                      |     |     | -10                      | μА   | V <sub>IN</sub> =GND<br>V <sub>CC</sub> =Max                                                     |

|                         | Input LOW current TEST ON                                                                                                                                                                                                                                       |     |     | -500                     | μА   | V <sub>IN</sub> =V <sub>CC</sub>                                                                 |

|                         | $\begin{array}{l} \text{Input LOW currentlB}_{\text{o}}\text{-IB}_{\text{15}} \text{ , EDC}_{\text{o}}\text{-EDC}_{\text{5}}, \\ \hline \text{BUS BUSY}, \overline{\text{BUS LOCK}}, \\ \hline \text{EXT ADR}_{\text{o}}\text{-EXT ADR}_{\text{7}} \end{array}$ |     |     | -50                      |      | Vcc=Max                                                                                          |

| l <sub>ozh</sub>        | Output 3-state current Except SINGERR,<br>STRBA                                                                                                                                                                                                                 |     |     | 50                       | μА   | V <sub>our</sub> =2.4V<br>V <sub>cc</sub> =Max                                                   |

|                         | Output 3-state current SINGERR, STRBA                                                                                                                                                                                                                           |     |     | 500                      |      |                                                                                                  |

| I <sub>OZL</sub>        | Output 3-state current Except STRBD                                                                                                                                                                                                                             |     |     | -50                      | μΑ   | V <sub>о∪т</sub> =0.5V                                                                           |

|                         | Output 3-state current STRBD                                                                                                                                                                                                                                    |     |     | -500                     |      | V <sub>cc</sub> =Max                                                                             |

| I <sub>ccoc</sub>       | Quiescent Power Supply Current (CMOS Input Levels)                                                                                                                                                                                                              |     |     | 80                       | mA   | V <sub>IN</sub> <0.2V or<br>>V <sub>cc</sub> -0.2V,f=0Hz<br>Outputs open<br>V <sub>cc</sub> =Max |

| Гссат                   | Quiescent Power Supply Current (TTL Levels)                                                                                                                                                                                                                     |     |     | 210                      | mA   | V <sub>IN</sub> =3.4V, All inputs, f=0Hz Outputs open V <sub>CC</sub> =Max                       |

| I <sub>CCD</sub><br>TTL | Dynamic Power Supply Current f = 20 MHz<br>f = 30 MHz<br>f = 35 MHz<br>f = 40 MHz                                                                                                                                                                               |     |     | 280<br>310<br>325<br>340 | mA   | V <sub>IN</sub> <0.8V or >3.4V,<br>Outputs open,<br>V <sub>cc</sub> =Max                         |

| I <sub>CCD</sub>        | Dynamic Power Supply Current $f = 20 \text{ MHz}$<br>f = 30  MHz<br>f = 35  MHz<br>f = 40  MHz                                                                                                                                                                  |     |     | 150<br>180<br>195<br>210 | mA   | V <sub>IN</sub> <0.2V or<br>>V <sub>cc</sub> -0.2V<br>Outputs open,<br>V <sub>cc</sub> =Max      |

| I <sub>os</sub>         | Output Short Circuit Current (one output shorted at a time)                                                                                                                                                                                                     | -25 | _   |                          | mA   | V <sub>out</sub> =GND<br>V <sub>cc</sub> =MAX¹                                                   |

| C <sub>IN</sub>         | Input Capacitance <sup>3</sup>                                                                                                                                                                                                                                  |     | 5   |                          | pF   | Inputs Only                                                                                      |

| C <sub>out</sub>        | Output Capacitance <sup>3</sup>                                                                                                                                                                                                                                 |     | 9   |                          | pF   | Outputs(includes<br>I/O Buffers)                                                                 |

Note 1: Duration of the short should not exceed one second. Note 2: VIL=-3.0V for pulse widths less than or equal to 20ns. Note 3: This parameter is set by design and not tested.

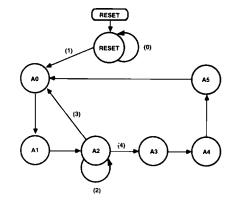

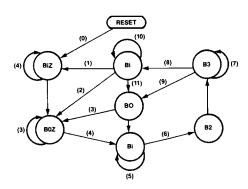

#### **TIMING GENERATOR STATE DIAGRAMS**

Two separate and almost independent state diagrams may be used to describe the PACE1757M machine cycle.

The Execution Unit performs according to a cycle of three states represented by Diagram A (the A machine) and the External Bus Unit follows a minimum cycle of four states, indicated in Diagram B (the B machine).

Referring to Diagram A, the paths are defined as follows for the Execution Unit:

- (0) External Reset true

- (1) External Reset false

- (2) ALU wait or Bus wait.

- (3) ALU Branch false

- (4) ALU Branch true

Diagram B defines the paths for the External Bus as follows:

- External Reset false

- (8) Bus Req. false

- (9) Bus Req. true and Bus Av. true

- (10) Bus Req. true and Bus Av. false

- (11) Bus Av. false

- (12) Bus Av. true

- (13) RDYA false

- (14) RDYA true

- (16) RDYD false

- (17) RDYD true and Bus Req. true and Bus Av true

- (18) RDYD true and Bus Req. false

- (19) RDYD true and Bus Req. true and Bus Av false

- (20) Bus Req. true and Bus Av. true

#### NOTE:

Bus Av = Bus grant and Bus not busy and Bus not locked.

Diagram A

Diagram B

#### DIFFERENCES BETWEEN THE PACE1757M AND PACE1757ME

The PACE1757ME, which uses the P1750AE CPU, achieves a 41% boost in performance (in clock cycles) over the PACE1757M, which uses the P1750A CPU. This reduction in clocks per instruction is because of three architectural enhancements:

- 1. The inclusion of a 24 x 24 Multiply Accumulate (MAC) array.

- 2. A reduction in non-bus cycles to 2 clocks (bus cycles remain at 4 clocks to maintain full compatibility with CPU's peripheral chips).

- 3. Branch calculation logic.

The table below shows how the MAC improves all multiply operations — both integer and floating point — by 477% to 760%.

|                                            | PAC    | E1750AE                    | P/     | Gain                       |               |

|--------------------------------------------|--------|----------------------------|--------|----------------------------|---------------|

| Instruction                                | Clocks | Execution<br>Time (40 MHz) | Clocks | Execution<br>Time (40 MHz) | # Ciks<br>(%) |

| Integer Add/Sub                            | 4      | 100ns                      | 4      | 100ns                      |               |

| Double Precision Integer Add/Sub           | 6      | 150ns                      | 9      | 225ns                      | 50            |

| Integer Multiply                           | 4      | 100ns                      | 23     | 575ns                      | 575           |

| Double Precision Integer Add/Sub           | 9      | 225ns                      | 69     | 1725ns                     | 760           |

| Floating Add/Sub                           | 18     | 450ns                      | 28     | 700ns                      | 55            |

| Extended Floating Add/Sub                  | 34     | 850ns                      | 51     | 1225ns                     | 50            |

| Floating Multiply                          | 9      | 225ns                      | 43     | 1075ns                     | 477           |

| Extended Floating Point Multiply           | 17     | 425ns                      | 96     | 2400ns                     | 564           |

| Branch (Taken)                             | 8      | 200ns                      | 12     | 300ns                      | 50            |

| Branch (Not Taken)                         | 4      | 100ns                      | 4      | 100ns                      | _             |

| Flt'g' Point Polynomial Step (Mul+Add/Sub) | 27     | 675ns                      | 71     | 1775ns                     | 263           |

| Ext Flt'g' Point Polynomial Step (Mul/Sub) | 51     | 1275ns                     | 147    | 3675ns                     | 2400          |

| DAIS Mix (MIPS)                            |        | 3.56                       | _      | 2.52                       | 41/59         |

#### PACE1757ME BUILT IN FUNCTIONS

A core set of additional instructions have been included in the PACE1757ME. These instructions use the Built-In Function (BIF) opcode space. The objective of these new opcodes is to enhance the performance of the PACE in critical application areas such as navigation, DSP, transcendentals and other LINPAK and matrix type instructions. Below is a list of the BIFs and their execution times (N = the number of elements in the vector being processed).

| Instruction                          | Mnemonic | Address<br>Mode | Number of Clocks | Notes         |

|--------------------------------------|----------|-----------------|------------------|---------------|

| Memory Parametric Dot Product—Single | VDPS     | 4F3(RA)         | 10 + 8 • N       | Interruptable |

| Memory Parametric Dot Product—Double | VDPD     | 4F1(RA)         | 10+16 • N        | Interruptable |

| 3 x 3 Register Dot Product           | R3DP     | 4F03            | 6                |               |

| Double Precision Multiply Accumulate | MACD     | 4F02            | 8                |               |

| Polynomial POLY                      | 4F06     | 7 • N - 2       |                  |               |

| Clear AccumulatorCLAC                | 4F00     | 4               |                  |               |

| Store Accumulator (32-Bit)           | STA      | 4F08            | 7                |               |

| Store Accumulator (48-Bit)           | STAL     | 4F04            | 11               |               |

| Load Accumulator (32-Bit)            | LAC      | 4F05            | 9                |               |

| Load Accumulator Long (48-Bit)       | LACL     | 4F07            | 9                |               |

| Move MMU Page Block                  | MMPG     | 4F0F            | 16+8 • N         | Privileged    |

| Load Timer A Reset Register          | LTAR     | 4F0D            | 4                |               |

| Load Timer B Reset Register          | LTBR     | 4F0E            | 4                |               |

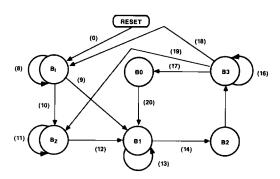

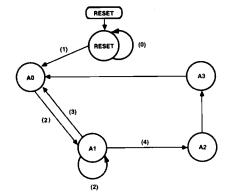

#### **TIMING GENERATOR STATE DIAGRAMS**

Two separate and almost independent state diagrams may be used to describe the PACE1757ME machine cycle.

The Execution Unit performs according to a cycle of three states represented by Diagram A (the A machine) and the External Bus Unit follows a minimum cycle of four states, indicated in Diagram B (the B machine).

Referring to Diagram A, the paths are defined as follows for the Execution Unit:

- (0) External Reset true

- (1) External Reset false

- (2) ALU wait or Bus wait.

- (3) ALU Branch false

- (4) ALU Branch true

Diagram A

Diagram B defines the paths for the External Bus as follows:

- (0) External Reset false

- (1) No Internal Bus Req.

- (2) Internal Bus Req.

- (3) Bus Busy or No Bus Grant

- (4) Bus Grant and Not Busy or Bus Locked by CPU

- (5) RDYA false

- (6) RDYA true

- (7) RDYD false

- (8) RDYD true, and no Internal Bus Request

- (9) RDYD true, Internal Bus Request pending

- (10) Bus Locked by CPU and No Internal Request

- (11) Bus Locked by CPU Internal Req.

Diagram B

#### NOTE:

Bus Av = Bus grant and Bus not busy and Bus not locked.

| P | 1 | 7 | 5 | 7 | ١ | ħ/ | ١ | ٨ | ļ |

|---|---|---|---|---|---|----|---|---|---|

|   |   |   |   |   |   |    |   |   |   |

| SIGNAL PHOPA                                | GATION DELAYS                           | 20N      | 1Hz      | 30MHz          |          | 35MHZ  |          | 40                                               | MHZ      |

|---------------------------------------------|-----------------------------------------|----------|----------|----------------|----------|--------|----------|--------------------------------------------------|----------|

| Symbol                                      | Description                             | MIN      | MAX      | MIN            | MAX      | MIN    | MAX      | MIN                                              | MAX      |

| TC(BR) <sub>L</sub>                         | BUS REQUEST                             |          | 33       |                | 25       |        | 22       |                                                  | 22       |

| TC(BR) <sub>H</sub>                         |                                         |          | 33       |                | 25       |        | 22       |                                                  | 22       |

| TBG <sub>v</sub> (C)                        | BUSGRANT - Setup                        | 5        |          | 5              |          | 5      |          | 5                                                |          |

| TC(BG) <sub>x</sub>                         | BUSGRANT - Hold                         | 5        |          | 5              |          | 5      | 1        | 5                                                |          |

| TC(BB) <sub>L</sub>                         | BUS BUSY                                |          | 25       |                | 24       |        | 22       |                                                  | 20       |

| TC(BB) <sub>H</sub>                         | BUG BUBU A                              | <u> </u> | 25       |                | 20       |        | 18       | -                                                | 17       |

| TBB <sub>v</sub> (C)<br>TC(BB) <sub>v</sub> | BUS BUSY - Setup BUS BUSY - Hold        | 5<br>5   |          | 5              |          | 5<br>5 |          | 5<br>5                                           |          |

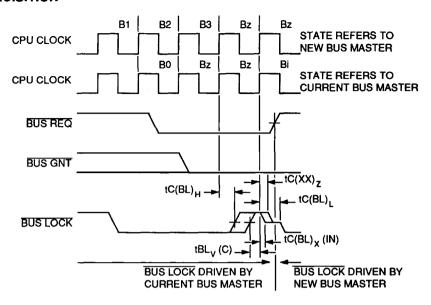

| TC(BL) <sub>L</sub>                         | BUS LOCK                                | -        |          | 5              | 05       | 3      |          | 13                                               |          |

| TC(BL) <sub>H</sub>                         | BOS LOCK                                |          | 30<br>30 |                | 25<br>20 |        | 23<br>19 |                                                  | 21<br>17 |

| TBL <sub>v</sub> (C)                        | BUS LOCK - Setup                        | 5        | 30       | 5              | 20       | 5      | 19       | 5                                                | - 17     |

| TC(BL), (IN)                                | BUS LOCK - Hold                         | 5        |          | 5              |          | 5      |          | 5                                                |          |

| TC(ST),                                     | M/O                                     | 3        | 30       | -              | 25       | 3      |          | <u>                                     </u>     | 20       |

| 10(31)                                      | R/₩                                     |          | 30       |                | 25<br>25 |        | 23       |                                                  | 20       |

|                                             | AS0:AS3, AK0:AK3, D/Ī                   |          | 25       |                | 20       |        | 23<br>20 | ( )                                              | 20       |

| TC(ST) <sub>x</sub>                         | M/ĪŌ, R/W, AS0:AS3, AK0:AK3, D/Ī        | 0        | 25       | 0              | 20       | 0      | 20       | 0                                                | 20       |

| TC(SA) <sub>H</sub>                         | STRBA                                   | l        | 22       | <del>-</del> ا | 17       |        | 16       | <del>                                     </del> | 16       |

| TC(SA)                                      | OTTEN                                   |          | 22       |                | 17       |        | 16       | 1                                                | 16       |

| TSA (IBA),                                  | Address Hold from STRBA(L)              | 5        |          | 5              | - ' '    | 5      | -10      | 5                                                | - 10     |

| TRA <sub>V</sub> (C)                        | RDYA – Setup                            | 5        | 1        | 5              | -        | 5      |          | 5                                                |          |

| TC(RA) <sub>x</sub>                         | RDYA – Hold                             | 5        |          | 5              |          | 5      |          | 5                                                |          |

| TC(SDW)                                     | STRBD                                   | Ť        | 22       | Ť              | 17       |        | 16       | ا ا                                              | 14       |

| TC(SD) <sub>H</sub>                         | 0,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |          | 22       |                | 17       |        | 16       |                                                  | 14       |

| TFC(SDR)                                    |                                         |          | 22       |                | 17       |        | 16       |                                                  | 14       |

| TIBD <sub>x</sub> (SDR) <sub>H</sub>        |                                         | 0        |          | 0              | l ''     | 0      | '`       | 0                                                | 1-4      |

| TSDW <sub>H</sub> (IBD) <sub>x</sub>        |                                         | 30       |          | 25             |          | 21     | ļ        | 17                                               |          |

| TSD <sub>i</sub> (SD) <sub>i</sub> (Write)  |                                         | 40       |          | 26             |          | 23     |          | 20                                               |          |

| TRD(RD) <sub>x</sub>                        | RDYD Setup                              | 5        |          | 5              |          | 5      | ļ        | 5                                                |          |

| TC(RD) <sub>x</sub>                         | RDYD - Hold                             | 5        |          | 5              | l .      | 5      |          | 5                                                |          |

| TC(IBA) <sub>v</sub>                        | IB0:IB15                                | ١Ť       | 30       | ۰              | 25       | Ť      | 23       | ۲                                                | 20       |

| TFC(IBA) <sub>x</sub>                       | 134.1313                                | ٥        | "        | 0              | ا "      | 0      | 20       | 0                                                | 20       |

| TIBDR <sub>v</sub> (C)                      | - Setup                                 | 5        |          | 5              |          | 5      |          | 5                                                |          |

| TC(IBD) <sub>x</sub> (Read)                 | – Hold                                  | 5        |          | 5              |          | 5      |          | 5                                                |          |

| TC(IBD) <sub>x</sub> (Write)                | DATAVALID (OUT)                         | 0        |          | 0              | •        | 0      |          | 0                                                |          |

| TFC(IBD) <sub>v</sub>                       | 5                                       | ľ        | 30       | ľ              | 25       |        | 23       | ľ                                                | 20       |

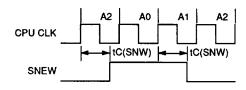

| TC(SNW)                                     | SNEW                                    |          | 30       |                | 26       |        | 24       | $\vdash$                                         | 22       |

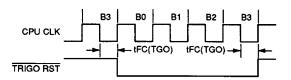

| TFC(TGO)                                    | TRIGO RST                               |          | 30       | _              | 26       |        | 24       | $\vdash$                                         | 22       |

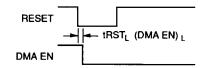

| TRST, (DMA EN),                             | DMA ENABLE                              |          | 40       |                | 35       |        | 33       |                                                  | 30       |

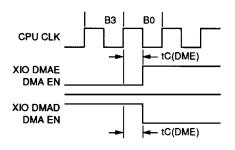

| TC(DME)                                     |                                         |          | 40       |                | 35       |        | 33       |                                                  | 30       |

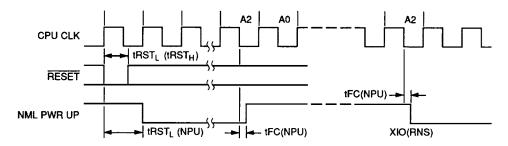

| TFC(NPU)                                    | NORMAL POWER-UP                         |          | 40       |                | 35       |        | 33       | -                                                | 30       |

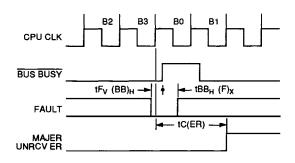

| TC(ER)                                      | CLK TO MAJER (UNRCV ER)                 |          | 60       |                | 50       |        | 47       | $\vdash$                                         | 45       |

| TRST, (NPU)                                 | RESET                                   |          | 50       |                | 40       |        | 35       |                                                  | 30       |

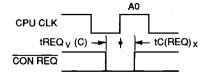

| TREQ <sub>v</sub> (C)                       | CON REQ                                 |          |          | 0              |          | 0      |          | 0                                                |          |

| TC(REQ) <sub>x</sub>                        | 30111100                                |          |          | 10             |          | 10     |          | 10                                               |          |

| TF <sub>v</sub> (BB) <sub>H</sub>           | LEVEL SENSITIVE FAULTS                  | 10<br>5  |          | 5              |          | 5      |          | 5                                                |          |

| TBB <sub>H</sub> (F) <sub>x</sub>           |                                         | 5        |          | 5              |          | 5      |          | 5                                                |          |

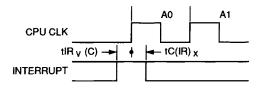

| TIR <sub>v</sub> (C)                        | IOL 1/2 INT. USR INT (0:5) - Setup      | 0        |          | ō              |          | 0      |          | 0                                                |          |

| TC(IR) <sub>x</sub>                         | PWRDN INT. LEVEL SENSITIVE - HOLD       | 10       | · '      | 10             |          | 10     |          | 10                                               |          |

| TRST, (TRST, )                              | RESET PULSE WIDTH                       | 25       |          | 20             |          | 18     |          | 15                                               |          |

| TC(XX),                                     | CLK TO TRI-STATE                        |          | 22       | _              | 17       |        | 15       | <del>                                     </del> | 13       |

Note 1: Units = ns

# SIGNAL PROPAGATION DELAYS (cont'd)

|                                          |                                   | 20N | 20MHz |         | 30MHz |     | 35MHZ |     | VIHZ |

|------------------------------------------|-----------------------------------|-----|-------|---------|-------|-----|-------|-----|------|

| Symbol                                   | Description                       | MIN | MAX   | MIN     | MAX   | MIN | MAX   | MIN | MAX  |

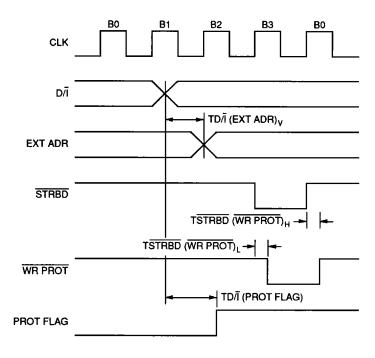

| TD/I(EXT ADR) <sub>v</sub>               | MMU Cache Hit                     |     | 25    |         | 23    |     | 23    |     | 23   |

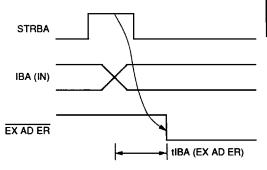

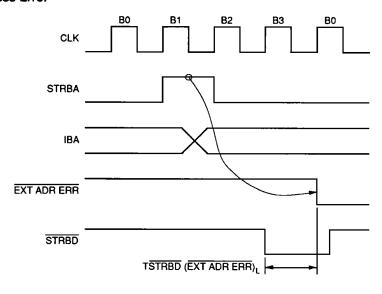

| TSTRBD(EXT ADR ER)                       | External Address Error            |     | 25    |         | 20    |     | 18    |     | 16   |

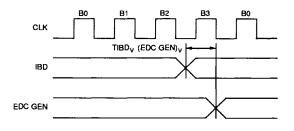

| TIBD <sub>v</sub> (EDC GEN) <sub>v</sub> | Error Connection Write Cycle      |     | 30    |         | 25    |     | 24    |     | 23   |

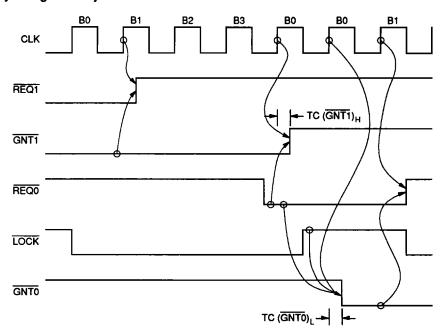

| TC(GNT)                                  | Arbiter Priority Transition       |     | 35    |         | 25    |     | 22    |     | 18   |

| TC(RDYA)                                 | Address Ready                     |     | 30    |         | 25    |     | 21    |     | 17   |

| TIBDIN(MEM PAR ER)                       | Parity Mode                       |     | 34    |         | 30    |     | 28    |     | 25   |

| TC(MEM PRT ER)                           | Memory Protect Error              |     | 50    |         | 45    |     | 43    |     | 40   |

| TSTRBD (WR PROT)                         | Write Protect Cache HIt           |     | 25    |         | 20    |     | 18    |     | 16   |

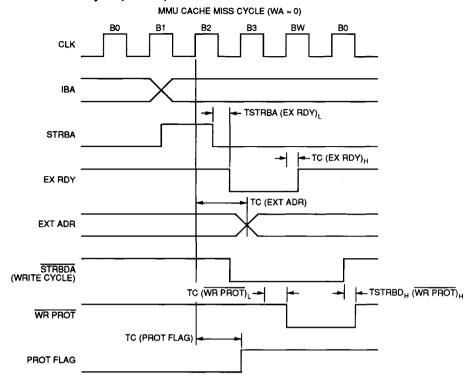

| TC(WR PROT)I                             | Write Protect Cache MIss          |     | 25    |         | 22    |     | 20    |     | 18   |

| TD/I(PROT FLAG)                          | Cache Hit (BPU Protection Error)  |     | 40    |         | 45    |     | 42    |     | 40   |

| TD/I(PROT FLAG)                          | Cache Hit (MMU Key-Lock Error)    |     | 40    |         | 35    |     | 33    |     | 30   |

| TC(PROT FLAG)                            | Cache Hit (BPU Protection Error)  |     | 25    |         | 35    |     | 33    |     | 30   |

| TC(PROT FLAG)                            | Cache Hit (MMU Key-Lock Error)    | 1   | 25    | <b></b> | 20    |     | 20    |     | 20   |

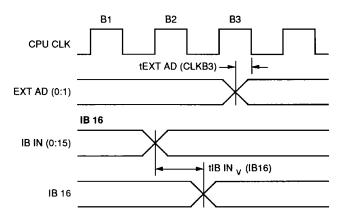

| TC(EXT ADR) <sub>v</sub>                 | Clock to EXT Address Valid (Miss) | ·   | 32    |         | 30    |     | 27    |     | 23   |

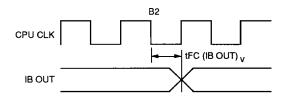

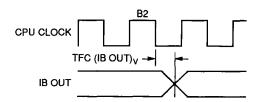

| TFC(IB OUT) <sub>v</sub>                 | Clock to EXT Address Valid (Miss) |     | 30    |         | 25    |     | 25    |     | 25   |

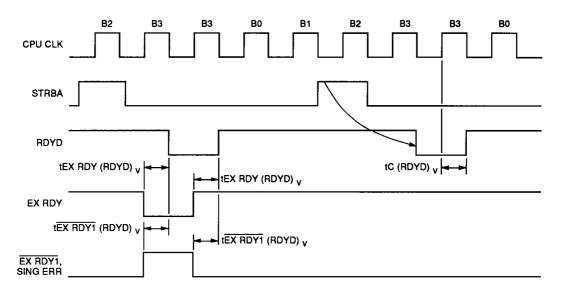

| TEX RDY1(RDYD)                           | Ready Data                        |     | 28    |         | 24    |     | 23    |     | 21   |

| TEX RDY(RDYD)                            | Ready Data                        |     | 16    |         | 13    |     | 12.5  |     | 11.5 |

| TC (RDYD) <sub>v</sub>                   | Ready Data                        |     | 28    |         | 22    |     | 19    |     | 16   |

| TSTRBAh(A) <sub>V</sub>                  | Address Valid                     |     | 29    |         | 21    |     | 20    |     | 19   |

| TIBA <sub>v</sub> (A) <sub>v</sub>       | Address Valid                     |     | 31    |         | 22    |     | 21    |     | 20   |

| TFC (R) <sub>L</sub>                     | Read Strobes                      |     | 24    |         | 18    |     | 15    |     | 12   |

| TSTRBD <sub>H</sub> (R) <sub>H</sub>     | Read Strobes                      |     | 24    |         | 18    |     | 15    |     | 12   |

| TSTRBD <sub>H</sub> (W) <sub>L</sub>     | Write Strobes                     |     | 26    |         | 20    |     | 18    |     | 15   |

| TSTRBD <sub>L</sub> (W) <sub>H</sub>     | Write Strobes                     |     | 26    |         | 20    |     | 18    |     | 15   |

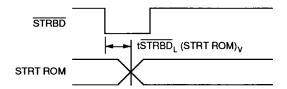

| TSTRBD(STRTROM)                          | Start-Up ROM                      | 26  |       |         | 20    |     | 18    |     | 15   |

| TC(TIM CLK)                              | Timer Clock                       | 30  |       |         | 25    |     | 23    |     | 20   |

| TEXT AD(FC B3)                           | Extended Address Set-Up           | 10  |       | 10      |       | 10  |       | 10  |      |

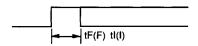

| TF(F), TI(I)                             | Edge Sensitive Pulse Width        | 5   |       | 5       |       | 5   |       | 5   |      |

| ţ, ţ                                     | Clock Rise and Fall Time          |     | 5     |         | 5     |     | 5     |     | 5    |

Units = ns

3-81 5/5/92

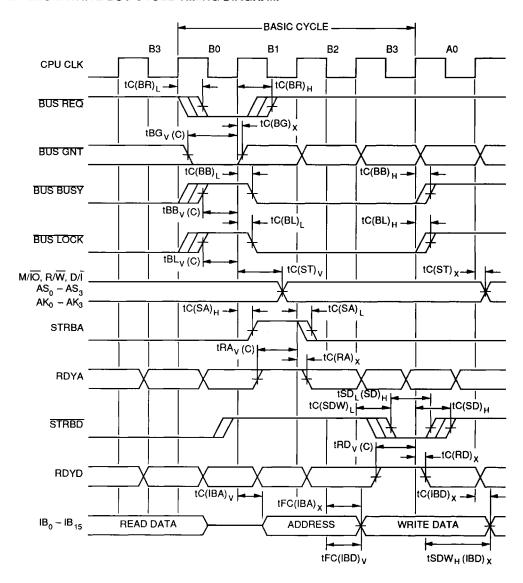

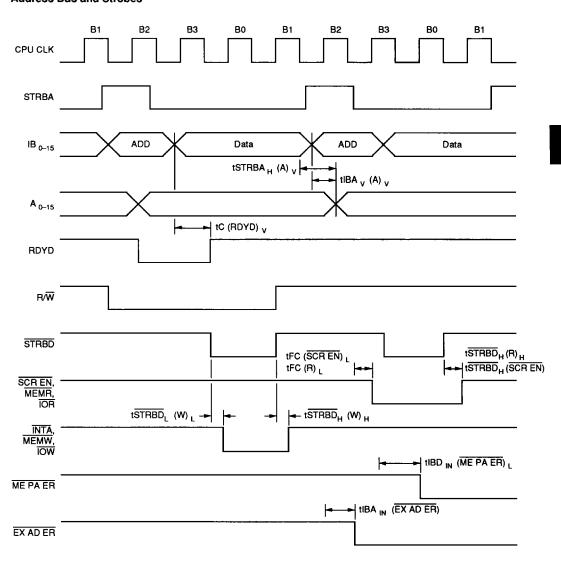

#### MINIMUM WRITE BUS CYCLE TIMING DIAGRAM

Note: All measurements of delay times on active signals relate to the 1.5 Volt level.

All timing parameters are composed of three elements as follows:

- the first, the letter T, stands for Timing,

- -- the second element represents the "from" signal, and

- the third element (in parenthesis) indicates the "to" signal.

When the CPU clock is one of the signal elements, either the rising edge "E" or the falling edge "FC" is referenced. When other signals are used as elements, an additional lower case suffix follows to indicate the *final* logical level of the signal. Suffixes are defined as follows:

L = LOW, H = HIGH, v = valid, z = Tri-State, x = Don't Care, zH = Tri-State to High, LH = Low to High.

Signal names associated with only the Read Cycle end with a "R", whereas the ones associated with only the write cycle end with a "W."

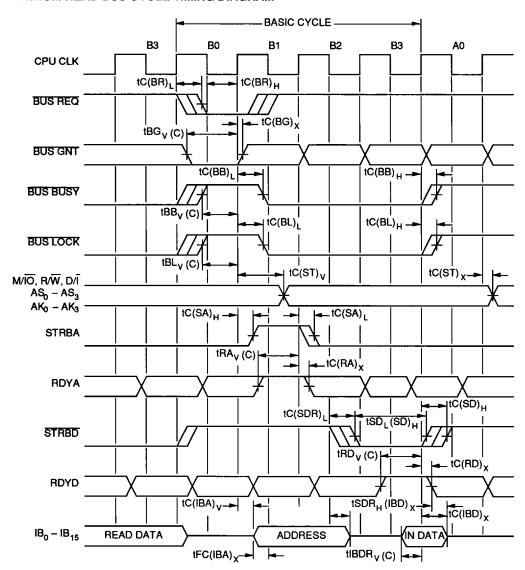

#### **MINIMUM READ BUS CYCLE TIMING DIAGRAM**

Note: All measurements of delay times on active signals relate to the 1.5 Volt level.

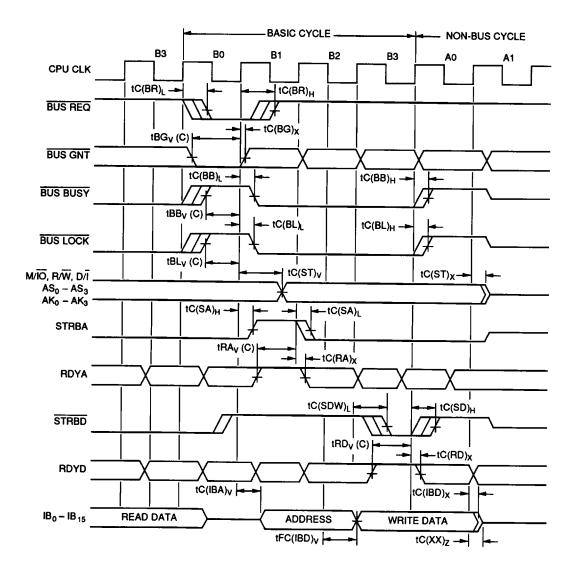

# MINIMUM WRITE BUS CYCLE, FOLLOWED BY A NON-BUS CYCLE, TIMING DIAGRAM

#### Note:

All time measurements on active signals relate to the 1.5 volt level.

#### **Address Bus and Strobes**

#### Note:

All time measurements on active signals relate to 1.5V levels.

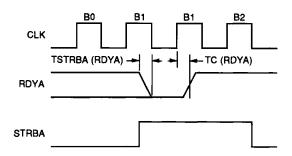

#### **RDYD TIMING**

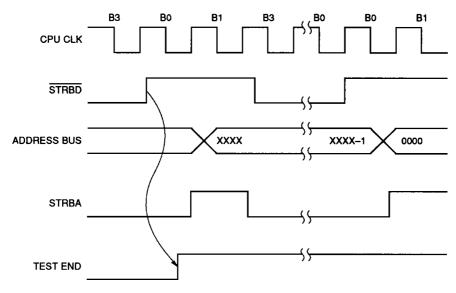

#### **TEST END TIMING<sup>1</sup>**

#### Notes:

- 1. The last two instructions executed during system test are: XIO RA, 1F44, 0 and JC 7, 0000 hex, 0. After execution of the IOW bus cycle, the XIO proceeds by filling the instruction pipe with two memory read bus cycles where the opcode 7070 hex and 0000 hex are entered to the processor. As from the end of STRBD in the second cycle, TEST END is asserted. At this point, the execution of IC starts by first issuing two fetch cycles from the "old PC" (from addresses XXXX & XXXX+1). The data will be taken from system memory (because TEST END is asserted) but both the address and data are irrelevent. Following that, IC will start filling the pipe from address 0000 hex and 0001 hex, now from the system memory to start user's program execution.

- 2. All time measurements on active signals relate to 1.5V levels.

#### **STRT ROM**

# IB BUS OUTPUT (0:15)

# **EX AD ER**

#### **EXTENDED ADDRESSES (0:1)**

Note: All time measurements on active signals relate to 1.5V levels.

3

# P1757M/ME

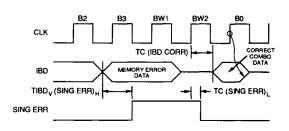

# **Error Correction (Write Cycle)**

# **Error Correction (Read Cycle)**

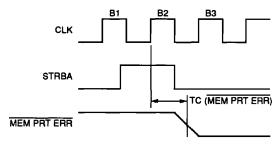

# **Memory Protect Error**

#### **Ready Address**

#### IB Bus Output (0:15)

#### **MMU Cache Hit**

#### **External Address Error**

Note:

All time measurements on active signals relate to 1.5V levels.

### MMU Cache Miss Cycle (WA = 0)

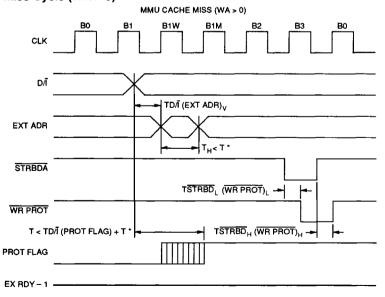

#### MMU Cache Miss Cycle (WA > 0)

<sup>\*</sup> The WR PROT/PROT FLAG signal is programmed as WR PROT or PROT FLAG. (See BPU Description), T = 1 Clock Period. Note: All time measurements on active signals relate to 1.5V levels.

# **TRIGO RST Discrete Timing**

# **DMA EN Discrete Timing**

# **Normal Power Up Discrete Timing**

# **XIO Operations**

# **SNEW Discrete Timing**

# **External Faults and Interrupts Timing**

# Edge-sensitive interrupts and faults (SYSFLT<sub>0</sub>, SYSFLT<sub>1</sub>) min. pulse width

#### Level-sensitive interrupts

Note: tC(IR)X max = 35 clocks

#### Level-sensitive faults

CON REQ

Note: All time measurements on active signals relate to the 1.5 volt level.

# Low Priority to High Priority Transition

x

# **Bus Arbitrator High Priority to Low Priority Transition**

Note: All time measurements on active signals relate to 1.5V levels.

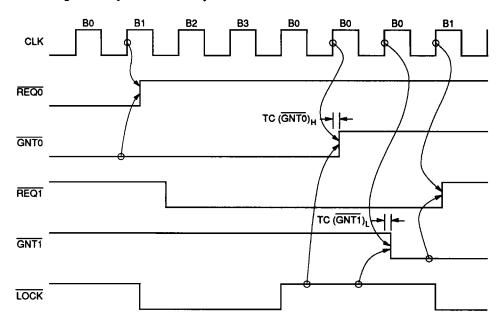

#### **BUS ACQUISITION**

#### Note:

A CPU contending for the BUS, will assert the BUS REQ line, and will acquire it when BUS GNT is asserted and the BUS is not locked (BUS LOCK is HIGH).

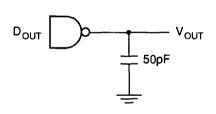

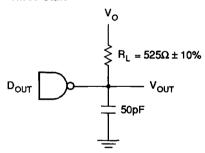

#### **SWITCHING TIME TEST CIRCUITS**

#### Standard Output (Non-Three-State)

#### Three-State

Note: All time measurements on active signals relate to the 1.5 volt level.

| Parameter        | V0                 | VMEA                   |

|------------------|--------------------|------------------------|

| t <sub>PLZ</sub> | ≥ 3V               | 0.5V                   |

| t <sub>PHZ</sub> | 0V                 | V <sub>cc</sub> – 0.5V |

| t <sub>PXL</sub> | V <sub>cc</sub> /2 | 1.5V                   |

| t <sub>PXH</sub> | V <sub>cc</sub> /2 | 1.5V                   |

# SIGNAL DESCRIPTIONS

#### **CLOCKS AND EXTERNAL REQUESTS**

| Mnemonic | Name               | Description                                                                                                              |

|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------|

| CPU CLK  | CPU Clock          | A single phase input clock signal (0-40 MHz, 40% to 60% duty cycle). This is a common input to all 3 devices.            |

| RESET    | Reset              | An active-low input which initializes the PACE1757M. Input to the P1750A/AE, P1753 and P1754.                            |

| CON REQ  | Console<br>Request | An active-low input that initiates console operations after the completion of the current instruction. Input to the CPU. |

#### **INTERRUPT INPUTS**

| Mnemonic            | Name                    | Description                                                                                                                                                                                                     |

|---------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWRDN INT           | Power Down<br>Interrupt | An interrupt request that cannot be masked or disabled. This signal is active on the positive going edge or the high level, according to the interrupt mode bit in the configuration register of the P1750A/AE. |

| USR₀INT-<br>USR₅INT | User<br>Interrupt       | Interrupt request input signals that are active on the positive going edge or the high level, according to the interrupt mode bit set in the P1750A/AE configuration register.                                  |

| IOL₁INT-<br>IOL₂INT | I/O Level<br>Interrupts | Active high interrupt requests that can be used to expand the number of user interrupts. Inputs to the P1750A/AE interrupt register.                                                                            |

#### **ERROR CONTROL**

| Mnemonic | Name                   | Description                                                                                                        |

|----------|------------------------|--------------------------------------------------------------------------------------------------------------------|

| UNRCV ER | Unrecoverable<br>Error | An active-high output that indicates the occurrence of an error classified as unrecoverable. A signal from the CPU |

| MAJ ER   | Major Error            | An active-high output that indicates the occurrence of an error classified as major. Again, from the CPU.          |

#### **DISCRETE CONTROL**

| Mnemonic  | Name                              | Description                                                                                                                                                                                                                                              |

|-----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NML PWRUP | Normal<br>Power Up                | An active-high output that is set by the CPU when it has successfully completed the built-in self-test in the initialiazation sequence. It can be reset by the I/O command RNS.                                                                          |

| SNEW      | Start New                         | An active high output that indicates a new instruction is about to start executing in the next cycle. This signal is issued by the CPU.                                                                                                                  |

| TRIGO RST | Trigger-Go<br>Reset               | An active-low discrete output. This signal can be pulsed low under program control [I/O address 400B(Hex)] and is automatically pulsed by the processor during it's initialization.                                                                      |

| STRT ROM  | Start Up Rom                      | An output follow the execution of the ESUR and DSUR, I/O commands as defined in MIL-STD-1750A. It will be at the logical level "1" after executing ESUR and at the logical "0" level after executing DSUR. Initially, it defaults to a "1" on the P1754. |

| DMA EN    | Direct Memory<br>Access<br>Enable | An active high output that indicates the DMA is enabled. It is enabled when the P1750A/AE is initialized (reset). It can be enabled or disabled under program control (I/O commands DMAE, DMAD) by the CPU.                                              |

#### **STATUS AND QUALIFIERS**

| Mnemonic | Name                              | Description                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TEST ON  | System Test<br>Enable             | An active-low input, used to enable the execution of the System Test built into the P1754, immediately after completion of the PACE 1750A/AE initialization and before fetching any instructions from the user's program.                                                                                                                                          |

| TEST END | System Test<br>End                | An active-high output indicating whether the Pace 1754 SystemTest has been completed. Whenever the System Test is disabled by the TEST ON signal, the TEST END output will be at a logical "1" immediately after reset is removed.                                                                                                                                 |

| SC₀-SC₄  | System<br>Configuration<br>Inputs | Inputs which are buffered onto IB0-IB4 when executing an I/O Read from I/O address 8410(hex).                                                                                                                                                                                                                                                                      |

| D/Ī      | Data or<br>Instruction            | A P1750A/AE output signal that indicates whether the current bus cycle access is for Data (high) or Instruction (low). It is tristate during bus cycles not assigned to this CPU. This line can be used as an additional memory address bit for systems that require separate data and program memory.                                                             |

| R/W      | Read or Write                     | A CPU output signal that indicates the direction of data flow with respect to the current bus master. A high idicates a read or input operation. A low indicates a write or output operation. This signal is tri-state during bus cycles not assigned to this CPU.                                                                                                 |

| M/IO     | Memory or I/O                     | An output signal from the CPU that indicates whether the current bus cycle is memory (high) or I/O (low). This signal is tri-state during bus cycles not assigned to this CPU.                                                                                                                                                                                     |

| RDYA_IN  | Address<br>Ready In               | An active-high input to the CPU that can be used to extend the address phase of a bus cycle. When RDYA_IN is not active, wait states are inserted by the P1750A/AE to accommodate slower memory or I/O devices. This line is usually connected to RDYA_OUT unless the memory interface logic requires the two RDYA signals remain discrete as an input and output. |

| RDYA_OUT | Address Ready<br>Out              | An active high output from the COMBO that indicates that there are no wait states requested when STRBA is active. Wait states are inserted when this signal becomes inactive during STRBA. Up to 3 wait states can be inserted by programming an internal register. Three wait states are inserted after reset (default).                                          |

| RDYD     | Data Ready                        | An active-high signal to the CPU from the PIC that extends the data phase of a bus cycle. When RDYD is not active, wait states are inserted by the P1750A/AE to acommodate slower memory or I/O devices.                                                                                                                                                           |

#### **BUS ARBITRATION**

\*

| Mnemonic          | Name        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS REQ           | Bus Request | An active-low output that indicates the CPU requires the bus. It becomes inactive when the CPU has acquired the bus and started the bus cycle.                                                                                                                                                                                                                                                                                                   |

| BUS GNT           | Bus Grant   | An active-low input from an external arbiter that indicates this CPU currently has the highest priority bus request. If the bus is not used and not locked, the CPU may begin a bus cycle, commencing with the next CPU clock. A high level will hold the the CPU in Hi Z state (Bz), tri-stating the IB bus status lines (D/Ī, R/W, M/IO), strobes(STRBA,STRBD), and all the other lines that go tri-state when this CPU does not have the bus. |

| BUS BUSY          | Bus Busy    | An active-low, bi-directional signal used to establish the beginning and end of a cycle. The trailing edge (low to high transition) is used for sampling bits into the P1750A Fault Register. It is tristate in bus cycles not assigned to this CPU. However, the CPU monitors the BUS BUSY line for latching non-CPU bus cycle faults into the Fault Register.                                                                                  |

| BUS LOCK          | Bus Lock    | An active low, bi-directional signal used to lock the bus for successive bus cycles. During non-locked bus cycles, the BUS LOCK signal mimics the BUS BUSY signal. A new master will receive a BUS GRANT only after this signal becomes inactive. It is tri-stated during bus cycles not assigned to this CPU. The following instructions will lock the bus: INCM, DECM, SB, RB, TSB, SRM, STUB and STLB.                                        |

| BUS GNT₀-BUS GNT₃ | Bus Grant   | Active-low outputs from the PIC indicating which master was granted the BUS. It remains active during BUS LOCK unless a higher master request occurs, which resets it. However, the higher master will be granted the BUS only after the current master's BUS LOCK releases the BUS.                                                                                                                                                             |

| BUS REQ,-BUS REQ, | Bus Request | Active low inputs to the PIC that indicate a requirement for the BUS from the 4 masters on the bus. The master assigned to pin $\overline{\text{BUS REQ}}_{\text{a}}$ has the highest priority. The master assigned to pin $\overline{\text{BUS REQ}}_{\text{a}}$ has the lowest priority.                                                                                                                                                       |

#### **FAULTS AND FLAGS**

| Mnemonic          | Name                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM PRT ER        | Memory Protect<br>Error                  | An active-low input generated by the MMU or BPU, or both, during attempted writes to protected memory. It is sampled by the BUS BUSY signal into the Fault Register (bit 0 CPU bus cycle, bit 1 if non-CPU bus cycle). The error is generated in one of the following conditions: a.mismatch in the access keys in the MMU page, an access to an execution protected page during instruction cycles, an access to a write protected by the BPU. |

| MEM PAR ER        | Memory Parity<br>Error                   | An active low signal which is sampled by the BUS BUSY signal into bit 2 of the CPU's Fault Register. It signals an error on the Data Bus during a memory cycle. Two detection modes can be selected by programming the control register of the MMU/COMBO: EDAC mode(6 Hamming code parity bits) or single bit parity mode (even or odd parity). The signal is inactive when none of the above modes are selected (default after reset).         |

| EXT ADR ER IN     | External<br>Address Error In             | An active-low input sampled by the BUS BUSY signal into the CPU Fault Register (bit 5 or 8), depending on the cycle(memory or I/O).                                                                                                                                                                                                                                                                                                             |

| EXT ADR ER OUT    | External<br>Address Error<br>Out         | An active low output which signals to the CPU and memory interface logic that an unimplemented memory or illegal I/O access has taken place.                                                                                                                                                                                                                                                                                                    |

| SYSFLT,           | System Fault 0,<br>System Fault 1        | Asychronous, positive edge sensitive inputs that set bit 7 (SYSFLT <sub>0</sub> ) or bits 13 and 15 (SYSFLT1) in the P1750A/AE Fault Register.                                                                                                                                                                                                                                                                                                  |

| EX AD ER/SING ERR | Illegal Address<br>Error/Single<br>Error | An active low output from the PIC indicating an illegal address error when referencing memory or I/O. It becomes an active high input called SINGLE ERROR for handshaking with the P1753 when the PIC is programmed to support EDAC. Default state after reset is high impedance.                                                                                                                                                               |

| WR PROT/PROT FLAG | Write Protected<br>/Protection Flag      | Either an active low output (WR PROT, following STRBD timing) during legal memory write cycles when no protection occurs, or an active high (PROT FLAG) signal indicating a protection error in a write cycle. Either mode can be selected by programming the COMBO control register. Default mode after reset is Write Protected.                                                                                                              |

| ME PA ER/RAMDIS   | Memory Parity<br>Error                   | An active low output indicating a Parity error when reading from memory. It becomes an active high output calles RAM DISABLE for handshaking with the P1753 when the PIC is programmed to support EDAC.                                                                                                                                                                                                                                         |

| тс                | Terminal Count                           | An active high output from the PIC indicating a bus time out or a watchdog trigger.                                                                                                                                                                                                                                                                                                                                                             |

#### STATUS BUS

| Mnemonic | Name          | Description                                                                                                                                                                                                                                                                                                                                                                              |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AK0-AK3  | Access Key    | Active high outputs corresponding to the AK field of the processor status word used to match the Access Lock in the MMU for memory accesses (a mismatch will cause the MMU to pull the MEM PRT ER signal LOW), and also indicate the processor state (PS). Priviledged instructions can be executed with PS=0 only. These signals are tri-state for bus cycles not assigned to this CPU. |

| AS0-AS3  | Address State | Active high outputs corresponding to the AS field of the proces sor status word that selects the page register group in the MMU. In the DMA physical demultiplexed mode, AS(0:1) will receive the 9th and 10th most significant bits of the physical address for use in the BPU function. These signals are tri-state in bus cycles not assigned to this CPU.                            |

#### **INFORMATION BUS**

| Mnemonic                           | Name                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IB <sub>o</sub> -IB <sub>15</sub>  | Information Bus                    | A bi-directional time multiplexed address/data BUS. IB0 is the most significant bit                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EDC <sub>0</sub> -EDC <sub>5</sub> | Error Detection/<br>Correction Bus | An active high bi-directional BUS used for detection of errors on the data BUS ( $IB_0$ - $IB_1$ ) and correction of single errors. When working in parity mode EDC0 is the parity bit. EDC1-EDC5 are undefined in this case.                                                                                                                                                                                                                                                                         |

| A(0:1)/EXT ADR(0:1)<br>A(2:15)     | Address Bus                        | An active high output Bus from the PIC. Contains the address of the current bus cycle as latched by the end of STRBA. In system configurations including the MMU function, the only active lines during memory cycles are A(4:15). In this example, A(2:3) are high impedance (don't care) and A(0:1) turn into inputs called Extended Addresses, EXT AD (0:1). In this situation, these two lines, supplied by the MMU, will be used to operate the programmable ready generation during bus cycles. |

| EXT ADR₀-EXT ADR <sub>7</sub>      | Extended<br>Address Bus            | An bi-directional active high BUS. In CPU cycles, it is an output BUS that is used to select one of 256 pages, 4K words each, expanding the direct addressing space to 1M word. In DMA cycles, indicated by DMA-ACK being active, it is also an output BUS except when programmed for the physical demultiplexed DMA mode. In this example, it becomes an input to receive the eight most significant bits of the DMA physical address for use in the BPU function.                                   |

#### **BUS STROBES AND QUALIFIERS**

| Mnemonic       | Name                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STRBA (note 1) | Address Strobe                     | An active-high output that can be used to externally latch the contents of IB(0:15) into the address latches of the PIC and MMU at the high to low transition of the strobe. The signal is tristate during bus cycles not assigned to this CPU. It is issued by the CPU and input to the MMU and PIC.                                                                                                                                     |

| STRBD (note 2) | Data Strobe                        | An active-low output used to read or write data from the PIC as well as to strobe data in memory and XIO cycles. This signal is tri-state during bus cycles not assigned to this CPU.It is intercon nected in the same manner as STRBA.                                                                                                                                                                                                   |

| MEMW           | Memory Write<br>Strobe             | An active-low output produced in memory write cycles by the PIC.                                                                                                                                                                                                                                                                                                                                                                          |

| MEMR           | Memory Read<br>Strobe              | An active-low output produced by the P1754 in memory read cycles.                                                                                                                                                                                                                                                                                                                                                                         |

| ĪŌW            | I/O Write Strobe                   | An active-low output produced by the P1754 in output write cycles.                                                                                                                                                                                                                                                                                                                                                                        |

| ĪŌR            | I/O Read Strobe                    | An active-low output produced by the P1754 during input read cycles.                                                                                                                                                                                                                                                                                                                                                                      |

| STRB EN        | Strobe Enable                      | An active-low input, enabling the active state of the address outputs of the P1754 and the MEMR, MEMW, IOR and IOW outputs. When a logic "1" ( if enabled by bits EST and EAD of the control register) it will correspondingly tri-state the above signals.                                                                                                                                                                               |

| ĪNTA           | Interrupt<br>Acknowledge<br>Strobe | An active-low output produced during any interrupt sequence corresponding to an output write to address 1000(Hex).                                                                                                                                                                                                                                                                                                                        |

| DMA ACK        | DMA<br>Acknowledge                 | An active-high input from the DMA controller to the P1753 which indicates a DMA cycle. Used to select the DMA table in the BPU memory for protection. For example, this could allow the DMA channel to update the program which could be write protected from the processor. In the physical DMA mode, it will cause the Extended Address Lines (EXT ADR <sub>0-7</sub> ) to become inputs providing BPU protection of the DMA transfers. |

| EX RDY         | External<br>Data Ready             | An active-high output from the MMU that indicates no wait states are requested. It becomes inactive for one clock (inserting one wait state) whenever a memory page different than the current one is accessed (e.g. a cache miss).                                                                                                                                                                                                       |

| EX RDY1        | External<br>Ready Data1            | An active low input to the PIC from the memory interface logic which at a logical "1" overrides the internal RDYD generation and forces it to a logical "0".                                                                                                                                                                                                                                                                              |

Note 1: One internal pulldown resistor is provided at the STRBA input. The nominal value is 40KOhm and the maximum range is 20KOhm to 80KOhm. In designs with TTL devices loading STRBA, an additional external resistor may be required.

Note 2: One internal pullup is provided at the STRBD input. The nominal value is 40KOhms and the maximum range is 20K-80KOhms.

×

#### **COMBO REGISTER MAP**

| 00          | J      |        |         | 18       |         |          |          |                 |       |          |          |        |      |     |     |

|-------------|--------|--------|---------|----------|---------|----------|----------|-----------------|-------|----------|----------|--------|------|-----|-----|

| CONT        | FROL I | REGIST | TER (1F | 50/9F50  | 0)      |          |          |                 |       |          |          |        |      |     |     |

| 0           | 1      | 2      | 3       | 4        | 5       | 6        | 7        | 8               | 9     | 10       | 11       | 12     | 13   | 14  | 15  |

| QR1         | QR2    | QR3    | QR4     | ODD      | EEI     | EED      | EPR      | SPD             | WPT   | EB1      | EB2      | EIO    | GPT  | DMX | DLP |

|             |        |        |         |          |         |          |          |                 |       |          |          |        |      |     |     |

|             |        |        |         | (1F51/9F |         |          |          |                 |       |          |          |        |      |     |     |

| 0           | 1      | 2_     | 3_      | 4        | 5       | 6        | 7        | 8               | 9     | 10       | 11       | 12     | 13   | 14  | 15  |

| WA0         | WA1    | SPI    | RES*    | PEG      | IDL     |          |          |                 | RES   | ERVED    |          |        |      |     |     |

|             |        |        |         |          |         |          |          |                 |       |          |          |        |      |     |     |

|             |        |        |         |          |         | R 1 (1F5 | 5/9F55)  |                 |       |          |          |        |      |     |     |

|             | _1_    |        | 3       | 4        | 5       | 6        |          | 8               | 9     | 10       | 11       | 12     | 13   | 14  | 15  |

|             |        |        | BL      | .1 LO    |         |          |          |                 |       |          | BL1      | HI     |      |     |     |

|             |        |        |         |          |         |          |          |                 |       |          |          |        |      |     |     |

|             |        |        | MEMO    | RY REC   | GISTE   | R 2 (1F5 | 6/9F56   |                 |       |          |          |        |      |     |     |

|             | 1_     | 2      | 3       | 4        | 5       | 6        | 7        | . 8             | 9     | 10       | 11       | 12     | 13   | 14  | 15  |

|             |        |        | Bl      | .2 LO    |         |          |          |                 |       |          | BL2      | HI     |      |     |     |

|             |        |        |         |          |         |          |          |                 |       |          |          |        |      |     |     |

|             |        |        |         | OUTP     |         | MMANE    | ) (1F57  | /9F <b>57</b> ) |       |          |          |        |      |     |     |

| 0_          | _1_    | 2      | 3       | 4        | 5       | 6        | 7        | 8               | 9     | 10       | 11       | 12     | 13   | 14  | 15  |

| X           | Х      | X      | X       | X        | X       | <u> </u> |          | LAST            | SEQUE | NTIAL    | PIO OL   | TPUT   | COMM | AND |     |

|             |        |        |         |          |         |          |          |                 |       |          |          |        |      |     |     |

|             |        |        |         |          |         | MAND (   |          |                 |       |          |          |        |      |     |     |

| 0           | 1      | 2      | 3       | 4        | 5       | 6        | <u> </u> | 8               | 9     | 10       | 11       | 12     | 13   | 14  | 15  |