MAAPGM0064 903261 — Preliminary Information

#### **Features**

- 2 Watt Saturated Output Power Level

- ◆ Variable Drain Voltage (4-10V) Operation

- ♦ MSAG™ Process

- ◆ High Performance Ceramic Bolt Down Package

## **Primary Applications**

- Multiple Band Point-to-Point Radio

- SatCom

- ISM Band

### **Description**

The MAAPGM0064 is a 2-stage 2 W power amplifier with on-chip bias networks in a bolt down ceramic package, allowing easy assembly. This product is fully matched to 50 ohms on both the input and output. It can be used as a power amplifier stage or as a driver stage in high power applications.

Each device is 100% RF tested to ensure performance compliance. The part is fabricated using M/A-COM's GaAs Multifunction Self-Aligned Gate Process.

M/A-COM's MSAG™ process features robust silicon-like manufacturing processes, planar processing of ion implanted transistors and multiple implant capability enabling power, low-noise, switch and digital FETs on a single chip. The use of refractory metals and the absence of platinum in the gate metal formulation prevents hydrogen poisoning when employed in hermetic packaging.

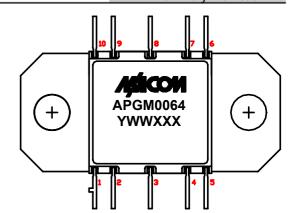

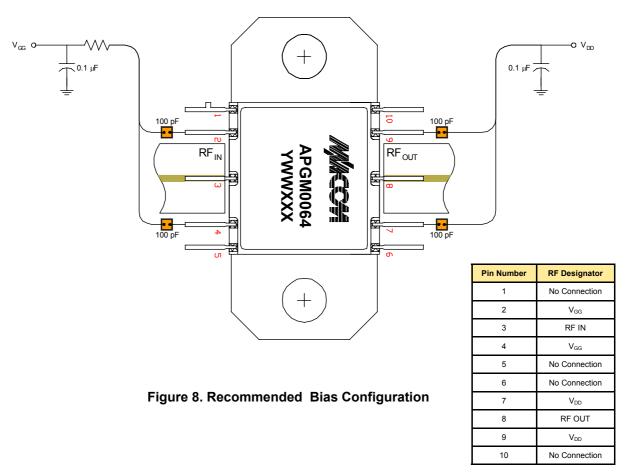

| Pin Number | RF Designator |  |

|------------|---------------|--|

| 1          | No Connection |  |

| 2          | $V_{GG}$      |  |

| 3          | RF IN         |  |

| 4          | $V_{GG}$      |  |

| 5          | No Connection |  |

| 6          | No Connection |  |

| 7          | $V_{DD}$      |  |

| 8          | RF OUT        |  |

| 9          | $V_{DD}$      |  |

| 10         | No Connection |  |

# Maximum Operating Conditions <sup>1</sup>

| Parameter                                 | Symbol            | Absolute Maximum | Units |

|-------------------------------------------|-------------------|------------------|-------|

| Input Power                               | P <sub>IN</sub>   | 23.0             | dBm   |

| Drain Supply Voltage                      | $V_{DD}$          | +12.0            | V     |

| Gate Supply Voltage                       | $V_{\mathrm{GG}}$ | -3.0             | V     |

| Quiescent Drain Current (No RF, 40% Idss) | I <sub>DQ</sub>   | 950              | mA    |

| Quiescent DC Power Dissipated (No RF)     | P <sub>DISS</sub> | 7.9              | W     |

| Junction Temperature                      | TJ                | 180              | °C    |

| Storage Temperature                       | T <sub>STG</sub>  | -55 to +150      | °C    |

1. Operation outside of these ranges may reduce product reliability.

- to make changes to the North America Tel: 800.366.2266 / Fax: 978.366.2266

- Europe Tel: 44.1908.574.200 / Fax: 44.1908.574.300

- Asia/Pacific Tel: 81.44.844.8296 / Fax: 81.44.844.8298

MAAPGM0064 903261 — Preliminary Information

## **Recommended Operating Conditions**

| Characteristic           | Symbol          | Min  | Тур  | Max    | Unit |

|--------------------------|-----------------|------|------|--------|------|

| Drain Supply Voltage     | $V_{DD}$        | 4.0  | 8.0  | 10.0   | V    |

| Gate Supply Voltage      | $V_{GG}$        | -2.4 | -2.0 | -1.3   | V    |

| Input Power              | P <sub>IN</sub> |      | 18.0 | 21.0   | dBm  |

| Junction Temperature     | $T_J$           |      |      | 150    | °C   |

| Thermal Resistance       | $\Theta_{JC}$   |      | 12.4 |        | °C/W |

| Package Base Temperature | T <sub>B</sub>  |      |      | Note 2 | °C   |

<sup>2.</sup> Maximum Package Base Temperature = 150°C —  $\Theta_{JC}^* V_{DD} * I_{DQ}$

#### Electrical Characteristics: $T_B = 40^{\circ}\text{C}^3$ , $Z_0 = 50^{\circ}$ $\Omega$ , $V_{DD} = 8V$ , $I_{DQ} \approx 600^{\circ}$ mA, $P_{in} = 18^{\circ}$ dBm, $R_G \approx 120\Omega$

| Parameter                                                                          | Symbol          | Typical | Units |

|------------------------------------------------------------------------------------|-----------------|---------|-------|

| Bandwidth                                                                          | f               | 6.5-9.5 | GHz   |

| Output Power                                                                       | POUT            | 33      | dBm   |

| Power Added Efficiency                                                             | PAE             | 30      | %     |

| 1-dB Compression Point                                                             | P1dB            | 32      | dBm   |

| Small Signal Gain                                                                  | G               | 17      | dB    |

| Input VSWR                                                                         | VSWR            | 1.8:1   |       |

| Output VSWR                                                                        | VSWR            | 3.0:1   |       |

| Gate Supply Current                                                                | I <sub>GG</sub> | < 5     | mA    |

| Drain Supply Current                                                               | I <sub>DD</sub> | < 1     | mA    |

| Noise Figure                                                                       | NF              | 9.5     | dB    |

| 2 <sup>nd</sup> Harmonic                                                           | 2f              | -20     | dBc   |

| 3 <sup>rd</sup> Harmonic                                                           | 3f              | -45     | dBc   |

| Output Third Order Intercept                                                       | ОТОІ            | 41      | dBm   |

| 3 <sup>rd</sup> Order Intermodulation Distortion,<br>Single Carrier Level = 20 dBm | IM3             | -10     | dBm   |

| 5 <sup>th</sup> Order Intermodulation Distortion,<br>Single Carrier Level = 20 dBm | IM5             | -25     | dBm   |

#### 3. Adjust $V_{\text{GG}}$ between -2.4 and -1.3 V to achieve indicated $I_{\text{DQ}}$ .

## **Operating Instructions**

This device is static sensitive. Please handle with care. To operate the device, follow these steps.

- 1. Apply  $V_{GG} = -1.7 \text{ V}$ ,  $V_{DD} = 0 \text{ V}$ .

- 2. Ramp  $V_{DD}$  to desired voltage, typically 8 V.

- 3. Adjust  $V_{GG}$  to set  $I_{DQ}$ , (approxmately @ -1.7V).

- 4. Set RF input.

<sup>•</sup> Europe Tel: 44.1908.574.200 / Fax: 44.1908.574.300

<sup>•</sup> Asia/Pacific Tel: 81.44.844.8296 / Fax: 81.44.844.8298

MAAPGM0064 903261 — Preliminary Information

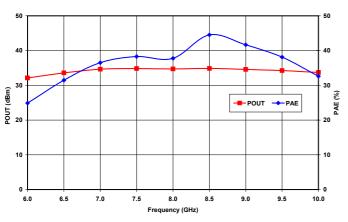

Figure 1. Output Power and Power Added Efficiency vs. Frequency at  $V_{DD}$  = 8V and  $P_{IN}$  = 18 dBm

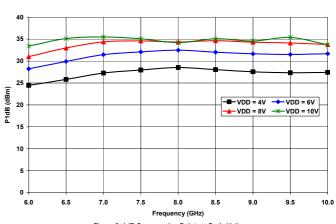

Figure 2. 1dB Compression Point vs. Drain Voltage

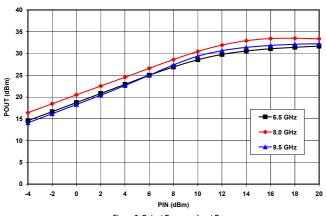

Figure 3. Output Power vs. Input Power at V<sub>DD</sub> = 8V

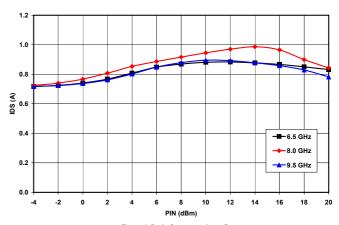

Figure 4. Drain Current vs. Input Power at  $V_{DD}$  = 8V

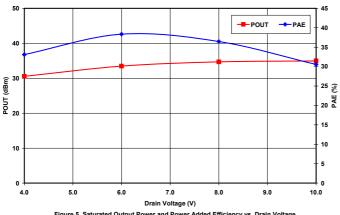

Figure 5. Saturated Output Power and Power Added Efficiency vs. Drain Voltage at  $f_{\text{o}}$  = 8 GHz

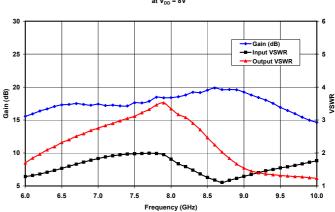

Figure 6. Small Signal Gain and VSWR vs. Frequency at VDD = 8V.

- North America Tel: 800.366.2266 / Fax: 978.366.2266

- Europe Tel: 44.1908.574.200 / Fax: 44.1908.574.300

- Asia/Pacific Tel: 81.44.844.8296 / Fax: 81.44.844.8298

MAAPGM0064 903261 — Preliminary Information

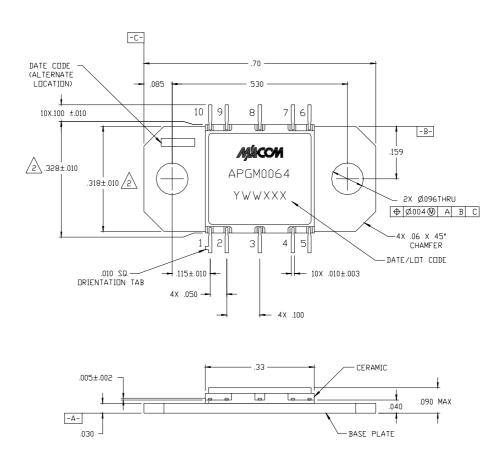

Figure 7. CR-15 Package Dimensions

The CR-15 is a high frequency, low thermal resistance package. The package consists of a cofired ceramic construction with a copper-tungsten base and iron-nickel-cobalt leads. The finish consists of electrolytic gold over nickel plate.

<sup>•</sup> Europe Tel: 44.1908.574.200 / Fax: 44.1908.574.300

<sup>•</sup> Asia/Pacific Tel: 81.44.844.8296 / Fax: 81.44.844.8298

MAAPGM0064 903261 — Preliminary Information

## **Assembly Instructions:**

This flange mount style package provides a robust interface between a highly integrated GaAs MMIC device and a circuit board which may be assembled using conventional surface mount techniques. A thin shim made of a thermally and electrically conductive, ductile material should be used prior to installation of the CR-15 to improve the thermal and electrical performance of the package to housing interface. Refer to **M/A-COM Application Note #M567\*** for more information .

For applications where surface mount components are to be installed after the CR-15 installation, this package will not be damaged when subjected to typical convection or IR oven reflow profiles. Refer to **M/A-COM Application Note #M538\*** for maximum allowable reflow time and temperature. Alternatively, the package leads may be individually soldered. Whether an iron or hot gas soldering equipment is used, care should be taken to insure that the temperature is well controlled and electric static discharge (ESD) safe.

\* Application Notes can be found by going to the Site Search Page on M/A-COM's web page (http://www.macom.com/search/search.jsp) and searching for the required Application Note.

#### **Biasing Notes:**

- ♦ The 100pF bypass capacitors must be placed as close to the V<sub>GG</sub> and V<sub>DD</sub> pins as possible (recommended < 100 mils).</li>

- ♦ A negative bias must be applied to V<sub>GG</sub> before applying a positive bias to V<sub>DD</sub> to prevent damage to the amplifier.

<sup>•</sup> Europe Tel: 44.1908.574.200 / Fax: 44.1908.574.300

Asia/Pacific Tel: 81.44.844.8296 / Fax: 81.44.844.8298