|                         | т            |    |    |             |        |        |        | R        | EVIS | IONS |       |      |      |      |             |       |             |      |      |    |

|-------------------------|--------------|----|----|-------------|--------|--------|--------|----------|------|------|-------|------|------|------|-------------|-------|-------------|------|------|----|

| LTR                     |              |    |    |             | Γ      | ESCR   | IPT1   | ON       |      |      |       |      | ]    | DATE | (YR-M       | O-DA) |             | APPR | OVED | )  |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

| :                       |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             | ,     |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

| REV                     |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

| SHEET                   |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

| REV                     |              |    |    |             |        |        |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

| SHEET                   | 15           | 16 | 17 | 18          | 19     | 20     | 21     | 22       | 23   | 24   |       |      |      |      |             |       |             |      |      |    |

| REV STATU               | JS           |    |    | RE          | v      | ·      |        |          |      |      |       |      |      |      |             |       |             |      |      |    |

| OF SHEETS               | ;            |    |    | SH          | EET    |        | 1      | 2        | 3    | 4    | 5     | 6    | 7    | 8    | 9           | 10    | 11          | 12   | 13   | 14 |

| DMTG N/A                |              |    |    | †           | ARED B | Y      |        |          |      |      |       |      |      |      | l           | l     | l           | L    |      | L  |

| PMIC N/A                |              |    |    | K           |        |        | Ki     | ).<br>ce |      | DI   | EFENS |      |      |      | S SU<br>HIO |       | CENT        | CER  |      |    |

| STANDA                  |              |    |    | CHEC        | KED BY |        | 7      |          |      |      |       |      |      |      | 1110        |       | <del></del> |      |      |    |

| MILI                    | CTAR<br>WING |    |    | APPROVED BY |        |        |        | MIC      | ROC  | IRCU | JIT.  | MEI  | MORY | . D: | IGIT        | 'AL,  | CMC         | os   |      |    |

| Dia                     | T.14         | •  |    |             |        |        |        | 64       | – M  | ACRO | CEL   | L E  | LECT | RIC  | ALLY        |       |             |      |      |    |

| THIS DRAWING            |              |    |    |             |        |        | 4      | Z        | 5    |      |       | MMAE |      |      |             | EVI   | CE,         |      |      |    |

| AND AGENO<br>DEPARTMENT |              |    |    | DRAW        | ING AP | PROVAL | . pate |          |      | MON  | 10TT  | THIC | : 81 | TIC( | ON          |       |             |      |      |    |

|                         |              |    |    |             |        |        |        | ,        |      | SIZ  | E     | CAG  | E CO | DE   |             | 59    | 62-         | 9215 | 8    |    |

| AMSC N/A                |              |    |    | REVIS       | SION L | EVEL   |        |          |      | A    |       | 6    | 726  | 8    |             |       |             |      |      |    |

|                         |              |    |    |             |        |        |        |          |      | SHE  | ET    |      | 1    |      | OF          |       | 24          |      | 1    | ,  |

| DESC FORM 193           |              |    |    |             |        |        |        | 37       |      |      |       |      |      |      |             |       |             |      |      |    |

JUL 91

$\underline{\texttt{DISTRIBUTION}}\ \ \textbf{STATEMENT}\ \ \textbf{A}. \ \ \textbf{Approved}\ \ \text{for public release; distribution is unlimited}.$

5962-E607-92

# 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes B, Q, and M) and space application (device classes S and V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

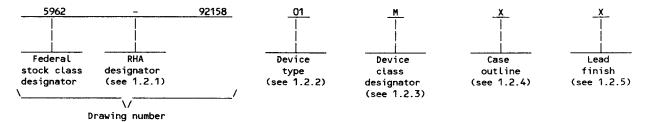

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 RHA designator. Device classes M, B, and S RHA marked devices shall meet the MIL-M-38510 specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number 1/ | Circuit function  | Access time |

|-------------|-------------------|-------------------|-------------|

| 01          |                   | 64-Macrocell EPLD | 40 ns       |

| 02          |                   | 64-Macrocell EPLD | 30 ns       |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

Device class

# Device requirements documentation

M

Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883

B or S

Certification and qualification to MIL-M-38510

Q or V

Certification and qualification to MIL-I-38535

1.2.4 Case outline(s). The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style            |

|----------------|------------------------|------------------|--------------------------|

| X              | AAL-2000 on AAL-1000   | 44               | "I" lead thin carrier 2/ |

1.2.5 <u>Lead finish</u>. The lead finish shall be as specified in MIL-M-38510 for classes M, B, and S or MIL-I-38535 for classes Q and V. Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

- 1/ Generic numbers are listed on the Standardized Military Drawing Source Approval Bulletin at the end of this document and will also be listed in MIL-BUL-103.

- $\underline{2}$ / Lid shall be transparent to permit ultraviolet light erasure.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET 2    |

| 1.3 <u>Absolute maximum ratings</u> . <u>3</u> /                                                                                                                                                                                          |                                                                                             |                                                        |                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------|

| Supply voltage range to ground potential ( $V_{CC}$ )  DC input voltage range                                                                                                                                                             | 2.0 V dc to . 1.5 W 4/ . +260°C . See MIL-STD +175°C65°C to +15!55°C to +12! . 25 erase/wri | +7.0 V dc<br>1835<br>D°C<br>5°C<br>te cycles (minimum) |                     |

| 1.4 Recommended operating conditions.                                                                                                                                                                                                     |                                                                                             |                                                        |                     |

| Supply voltage range (V <sub>CC</sub> )                                                                                                                                                                                                   | 0 V dc<br>2.2 V dc min<br>0.8 V dc max                                                      | imum<br>imum                                           | 1                   |

| 1.5 Logic testing for device classes Q and V.                                                                                                                                                                                             |                                                                                             |                                                        |                     |

| Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012)                                                                                                                                                   | <u>5</u> / percent                                                                          |                                                        |                     |

| 2. APPLICABLE DOCUMENTS                                                                                                                                                                                                                   |                                                                                             |                                                        |                     |

| 2.1 Government specifications, standards, bulletin, and<br>specifications, standards, bulletin, and handbook of the i<br>of Specifications and Standards specified in the solicitat<br>herein.                                            | issue listed in tl                                                                          | nat issue of the Departmer                             | nt of Defense Index |

| SPECIFICATIONS                                                                                                                                                                                                                            |                                                                                             |                                                        |                     |

| MILITARY                                                                                                                                                                                                                                  |                                                                                             |                                                        |                     |

| MIL-M-38510 - Microcircuits, General Specificatio<br>MIL-I-38535 - Integrated Circuits, Manufacturing,                                                                                                                                    |                                                                                             | cation for.                                            |                     |

| STANDARDS                                                                                                                                                                                                                                 |                                                                                             |                                                        |                     |

| MILITARY                                                                                                                                                                                                                                  |                                                                                             |                                                        |                     |

| MIL-STD-480 - Configuration Control-Engineering C<br>MIL-STD-883 - Test Methods and Procedures for Mic<br>MIL-STD-1835 - Microcircuit Case Outlines.                                                                                      |                                                                                             | ns and Waivers.                                        |                     |

| BULLETIN                                                                                                                                                                                                                                  |                                                                                             |                                                        |                     |

| MILITARY                                                                                                                                                                                                                                  |                                                                                             |                                                        |                     |

| MIL-BUL-103 - List of Standardized Military Drawi                                                                                                                                                                                         | ngs (SMD's).                                                                                |                                                        |                     |

| 3/ Stresses above the absolute maximum rating may cause p maximum levels may degrade performance and affect reli 4/ Must withstand the added P <sub>p</sub> due to short circuit test 5/ Values will be added when they become available. | ability.                                                                                    | to the device. Extended c                              | peration at the     |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER                                                                                                                                                                           | SIZE<br>A                                                                                   |                                                        | 5962-92158          |

| DAYTON, OHIO 45444                                                                                                                                                                                                                        |                                                                                             | REVISION LEVEL                                         | SHEET<br>3          |

### HANDBOOK

**MILITARY**

MIL-HDBK-780 - Standardized Military Drawings.

(Copies of the specifications, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Mon-Government publications</u>. The following documents form a part of this document to the extent specified herein. Unless otherwise specified, the issues of the documents which are DoD adopted are those listed in the issue of the DODISS cited in the solicitation. Unless otherwise specified, the issues of documents not listed in the DODISS are the issues of the documents cited in the solicitation.

AMERICAN SOCIETY FOR TESTING AND MATERIALS (ASTM)

ASTM Standard F1192-88 - Standard Guide for the Measurement of Single Event Phenomena from Heavy Ion Irradiation of Semiconductor Devices.

(Applications for copies of ASTM publications should be addressed to the American Society for Testing and Materials, 1916 Race Street, Philadelphia, PA 19103).

ELECTRONICS INDUSTRIES ASSOCIATION (EIA)

JEDEC Standard No. 17 - A Standardized Test Procedure for the Characterization of LATCH-UP in CMOS Integrated Circuits.

(Applications for copies should be addressed to the Electronics Industries Association, 2001 Pennsylvania Street, N.W., Washington, DC 20006.)

(Non-Government standards and other publications are normally available from the organizations that prepare or distribute the documents. These documents also may be available in or through libraries or other informational services.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. This is a full military detail specification and is suitable for qualification of device classes B and S to the requirements of MIL-M-38510. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 <u>Case outline(s)</u>. The case outline(s) shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

- 3.2.3 <u>Truth table</u>. The truth table shall be as specified on figure 2.

- 3.2.3.1 <u>Unprogrammed devices</u>. The truth table for unprogrammed devices for contracts involving no altered item drawing shall be as specified on figure 2. When required in screening (see 4.2 herein) or qualification conformance inspection, groups A, B, or C (see 4.4), the devices shall be programmed by the manufacturer prior to test. A minimum of 50 percent of the total number of cells shall be programmed or at least 25 percent of the total number of cells to any altered item drawing.

- 3.2.3.2 <u>Programmed devices.</u> The truth table for programmed devices shall be as specified by an attached altered item drawing.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>4 |

| T                                            | Sumb a l         | Conditions                                                                                                             | Group A   | Device | 1 1 | mit   | Unit |

|----------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------|-----------|--------|-----|-------|------|

| Test                                         | Symbol           | -55°C ≤ T <sub>C</sub> ≤ +125°C                                                                                        | subgroups | type   |     | m , c |      |

|                                              |                  | $4.5 \text{ V} \leq \text{V}_{CC}^{C} \leq 5.5 \text{ V}$ unless otherwise specified                                   |           |        | Min | Max   |      |

| Output high voltage                          | v <sub>он</sub>  | $V_{CC} = 4.5 \text{ V, } I_{OH} = -4 \text{ mA}$<br>$V_{IH} = 2.2 \text{ V, } V_{IL} = 0.8 \text{ V}$                 | 1,2,3     | All    | 2.4 |       | v    |

| Output low voltage                           | v <sub>oL</sub>  | V <sub>CC</sub> = 4.5 V, I <sub>OL</sub> = 8 mA<br>V <sub>IH</sub> = 2.2 V, V <sub>IL</sub> = 0.8 V                    |           |        |     | 0.45  |      |

| Input high voltage 1/2/                      | v <sub>IH</sub>  |                                                                                                                        |           |        | 2.2 |       |      |

| Input low voltage 1/2/                       | VIL              |                                                                                                                        |           |        |     | 0.8   |      |

| Input leakage current                        | IIX              | V <sub>CC</sub> = 5.5 V,<br>V <sub>IN</sub> = 5.5 V and GND                                                            |           |        | -10 | +10   | μΑ   |

| Output leakage current                       | I <sub>OZ</sub>  | V <sub>CC</sub> = 5.5 V,<br>V <sub>IN</sub> = 5.5 V and GND                                                            |           |        | -40 | +40   |      |

| Output short circuit current 3/4/            | I <sub>SC</sub>  | v <sub>cc</sub> = 5.5 v, v <sub>out</sub> = 0.5 v                                                                      |           |        | -30 | -90   | mA   |

| Power supply current 4/ 5/                   | I <sub>CC1</sub> | V <sub>CC</sub> = 5.5 V, I <sub>OUT</sub> = 0 mA,<br>V <sub>IN</sub> = V <sub>CC</sub> to GND<br>f = f <sub>MAX1</sub> |           |        |     | 275   |      |

| Power supply current<br>(standby) <u>2</u> / | I <sub>CC2</sub> | V <sub>CC</sub> = 5.5 V, I <sub>OUT</sub> = 0 mA,<br>V <sub>IN</sub> = V <sub>CC</sub> to GND,                         |           |        |     | 200   |      |

| Input capacitance 2/                         | CIN              | V <sub>CC</sub> = 5.0 V,<br>T <sub>A</sub> = +25°C, f = 1 MHz,<br>(see 4.4.1e)                                         | 4         |        |     | 10    | рF   |

| Output capacitance <u>2</u> /                | C <sub>OUT</sub> | V <sub>CC</sub> = 5.0 V,<br>T <sub>A</sub> = +25°C, f = 1 MHz,<br>(see 4.4.1e)                                         | 4         |        |     | 10    |      |

| Functional testing                           |                  | See 4.4.1c                                                                                                             | 7,8       | 1      |     |       |      |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>5 |

| Test                                                        | Symbol           | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$                          | Group A<br>subgroups | Device<br>type | -   |     | Unit |

|-------------------------------------------------------------|------------------|----------------------------------------------------------------------------------|----------------------|----------------|-----|-----|------|

|                                                             |                  | -55°C ≤ $T_C$ ≤ +125°C<br>4.5 V ≤ $V_{CC}$ ≤ 5.5 V<br>unless otherwise specified |                      |                | Min | Max |      |

| Dedicated input to combinatorial output delay 7/            | t <sub>PD1</sub> | See figures 3 (circuit A) and 4 6/                                               | 9,10,11              | 01             |     | 40  | ns   |

| · -                                                         |                  |                                                                                  |                      | 02             |     | 30  |      |

| I/O input to combinatorial output delay 8/                  | t <sub>PD2</sub> |                                                                                  |                      | 01             |     | 62  | ]    |

| <u>o</u> ,                                                  |                  |                                                                                  |                      | 02             |     | 44  |      |

| Dedicated input to combinatorial output delay with expander | t <sub>PD3</sub> |                                                                                  |                      | 01             |     | 65  | ]    |

| delay 9/                                                    |                  |                                                                                  |                      | 02             |     | 44  |      |

| I/O input to combinatorial output delay with expander       | t <sub>PD4</sub> |                                                                                  |                      | 01             |     | 87  |      |

| detay <u>2</u> / <u>4</u> / <u>10</u> /                     |                  |                                                                                  |                      | 02             |     | 58  |      |

| Input to output enable delay 4/7/                           | <sup>t</sup> EA  |                                                                                  |                      | 01             |     | 40  |      |

|                                                             | <u></u>          |                                                                                  |                      | 02             |     | 30  |      |

| Input to output disable delay 4/7/                          | t <sub>ER</sub>  | See figures 3 (circuit B) and 4 6/                                               |                      | 01             |     | 40  |      |

|                                                             |                  | <u> </u>                                                                         |                      | 02             |     | 30  |      |

| Synchronous clock input to output delay                     | t <sub>co1</sub> | See figures 3 (circuit A) and 4 6/                                               |                      | 01             |     | 23  |      |

|                                                             |                  |                                                                                  |                      | 02             |     | 16  |      |

| Synchronous clock to local feedback to combinatorial        | t <sub>co2</sub> |                                                                                  |                      | 01             |     | 48  |      |

| output <u>4</u> / <u>11</u> /                               |                  |                                                                                  |                      | 02             |     | 35  |      |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>6 |

| Test                                                  | Symbol          | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$                                          | Group A<br>subgroups | Device<br>type | Lin | Unit |    |

|-------------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------|----------------------|----------------|-----|------|----|

|                                                       |                 | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>unless otherwise specified | i                    |                | Min | Max  |    |

| Dedicated input or feedback setup time to synchronous | t <sub>S1</sub> | See figures 3 (circuit A) and 4 6/                                                               | 9,10,11              | 01             | 28  |      | ns |

| clock input 7/ 12/                                    |                 | and 4 <u>0</u> /                                                                                 |                      | 02             | 20  |      |    |

| I/O input setup time to synchronous clock input       | t <sub>s2</sub> |                                                                                                  |                      | 01             | 45  |      | ]  |

| 7/ 12/                                                |                 |                                                                                                  |                      | 02             | 35  |      |    |

| Input hold time from synchronous clock input 7/       | t <sub>H</sub>  |                                                                                                  |                      | All            | 0   |      |    |

| Synchronous clock input high                          | t <sub>WH</sub> |                                                                                                  |                      | 01             | 15  |      | _  |

| time <u>2</u> /                                       |                 |                                                                                                  |                      | 02             | 10  |      |    |

| Synchronous clock input low time 2/                   | t <sub>WL</sub> |                                                                                                  |                      | 01             | 15  |      |    |

| <u> </u>                                              |                 |                                                                                                  |                      | 02             | 10  |      |    |

| Asynchronous clear width 2/ 4/ 7/                     | t <sub>RW</sub> |                                                                                                  |                      | 01             | 40  |      |    |

| E/ 3/ 1/                                              |                 |                                                                                                  |                      | 02             | 30  |      |    |

| Asynchronous clear recovery time 2/4/7/               | t <sub>RR</sub> |                                                                                                  |                      | 01             | 40  |      |    |

| <u> </u>                                              |                 |                                                                                                  |                      | 02             | 30  |      |    |

| Asynchronous clear to registered                      | t <sub>RO</sub> |                                                                                                  |                      | 01             |     | 40   |    |

| output delay <u>2</u> / <u>7</u> /                    |                 |                                                                                                  |                      | 02             |     | 30   |    |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158 |

|-----------------------------------------------------------------|-----------|----------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>7 |

| Test                                                                                                                                         | Symbol            | -55°C ≤ T <sub>o</sub> ≤ +125°C                                                             | Group A<br>subgroups | Device<br>type | Limit |          | linit |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------|----------------------|----------------|-------|----------|-------|

|                                                                                                                                              |                   | $4.5 \text{ V} \leq \text{V}_{CC}^{\text{L}} \leq 5.5 \text{ V}$ unless otherwise specified |                      |                | Min   | Max      |       |

| Asynchronous preset width 2/ 4/ 7/                                                                                                           | t <sub>PW</sub>   | See figures 3 (circuit A) and 4 6/                                                          | 9,10,11              | 01             | 40    |          | ns    |

| E' Z' L'                                                                                                                                     |                   |                                                                                             |                      | 02             | 30    | <u> </u> | 1     |

| synchronous preset recovery                                                                                                                  | t <sub>PR</sub>   |                                                                                             |                      | 01             | 40    |          |       |

| Cine 2/ 4/ 1/                                                                                                                                |                   |                                                                                             |                      | 02             | 30    | 1        |       |

| synchronous reset to registered output delay 2/7/                                                                                            | t <sub>PO</sub>   |                                                                                             |                      | 01             | i     | 40       |       |

| output detay Z/ I/                                                                                                                           |                   |                                                                                             |                      | 02             | 1     | 30       |       |

| Synchronous clock to local feedback input 4/13/                                                                                              | <sup>t</sup> CF   |                                                                                             |                      | 01             |       | 7        |       |

|                                                                                                                                              |                   | ]                                                                                           |                      | 02             |       | 3        |       |

| xternal synchronous clock<br>period (1/f <sub>MAX3</sub> ) <u>4</u> /                                                                        | tp                | !                                                                                           |                      | 01             | 30    |          | ]     |

| MAX2. —                                                                                                                                      | <u> </u>          | ]                                                                                           |                      | 02             | 20    | !        |       |

| external maximum frequency<br>(1/(t <sub>CO</sub> + t <sub>S1</sub> )) <u>4</u> / <u>14</u> /                                                | f <sub>MAX1</sub> | 1                                                                                           |                      | 01             | 19.6  |          | MHz   |

| ·// · CO · · S1// -/                                                                                                                         | <u> </u>          | ]                                                                                           |                      | 02             | 27    | <u> </u> |       |

| Internal local feedback maximum frequency, lesser of (1/(t <sub>S1</sub> +                                                                   | f <sub>MAX2</sub> | ]                                                                                           |                      | 01             | 28.5  |          |       |

| t <sub>CF</sub> )) or (1/t <sub>CO1</sub> ) 4/ 15/ 31                                                                                        | 1                 | ] '                                                                                         | 1                    | 02             | 43    | 1'       | 1     |

| Data path maximum frequency,<br>least of 1/(t <sub>wl</sub> + t <sub>WH</sub> ),                                                             | f <sub>MAX3</sub> |                                                                                             |                      | 01             | 33    |          |       |

| least of 1/(t <sub>WL</sub> + t <sub>WH</sub> ),<br>1/(t <sub>S1</sub> + t <sub>H</sub> ) or (1/t <sub>CO1</sub> )<br><u>4</u> / <u>16</u> / | 1                 | !                                                                                           | !                    | 02             | 50    |          |       |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-92158 |

|------------------------------------------------------------------------------------|-----------|----------------|------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>8 |

| Test                                                                         | Symbol            | Conditions $-55^{\circ}C \leq T_{C} \leq +125^{\circ}C$ $4.5 \text{ V} \leq V_{CC} \leq 5.5 \text{ V}$ unless otherwise specified | Group A<br>subgroups | Device<br>type | Lin  | nit<br>T | Unii |

|------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------|------|----------|------|

|                                                                              | 1                 | unless otherwise specified                                                                                                        |                      |                | Min  | Max      |      |

| aximum register toggle<br>frequency (1/(t <sub>WL</sub> + t <sub>WH</sub> )) | f <sub>MAX4</sub> | See figures 3 (circuit A) and 4 6/                                                                                                | 9,10,11              | 01             | 33   |          | MHz  |

| 4/ <u>17</u> /                                                               |                   | and 4 <u>0</u> /                                                                                                                  |                      | 02             | 40   | 50       |      |

| output data stable time from synchronous clock input 4/ 18/                  | <sup>t</sup> OH   |                                                                                                                                   |                      | Atl            | 3    |          | ns   |

|                                                                              | Externa           | l asynchronous switching cha                                                                                                      | racteristic          | s              |      |          |      |

| Asynchronous clock input to butput delay 6/                                  | t <sub>ACO1</sub> | See figures 3 (circuit A) and 4 6/                                                                                                | 9,10,11              | 01             |      | 45       | ns   |

|                                                                              |                   | and 4 0/                                                                                                                          |                      | 02             | -    | 30       | ]    |

| synchronous clock input to local feedback to                                 | t <sub>ACO2</sub> |                                                                                                                                   |                      | 01             |      | 64       |      |

| combinatorial output 2/19/                                                   | <u> </u>          |                                                                                                                                   |                      | 02             |      | 46       |      |

| Dedicated input or feedback setup time to asynchronous                       | t <sub>AS1</sub>  |                                                                                                                                   |                      | 01             | 10   |          |      |

| clock input <u>6</u> /                                                       | ļ                 |                                                                                                                                   |                      | 02             | 6    | <u> </u> |      |

| I/O input setup time to asynchronous clock input                             | t <sub>AS2</sub>  |                                                                                                                                   |                      | 01             | 34   |          |      |

| <u>4/ 6</u> /                                                                | <u> </u>          |                                                                                                                                   |                      | 02             | 25   | ļ        | ļ    |

| Input hold time from asynchronous clock input <u>6</u> /                     | <sup>t</sup> AH   |                                                                                                                                   |                      | 01             | 15   |          |      |

|                                                                              |                   |                                                                                                                                   |                      | 02             | 8    |          |      |

| Asynchronous clock input high time <u>2</u> / <u>6</u> /                     | <sup>t</sup> AWH  |                                                                                                                                   |                      | 01             | 17.5 |          |      |

|                                                                              |                   |                                                                                                                                   |                      | 02             | 14   | ļ        |      |

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE |                | 5962-92158 |

|------------------------------------------------------|------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |      | REVISION LEVEL | SHEET 9    |

| Test                                                                                | Symbol             | Conditions $-55^{\circ}C \leq T_{c} \leq +125^{\circ}C$                                          | Group A<br>subgroups | Device<br>type | Limit      |     | Unit |

|-------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------------|----------------------|----------------|------------|-----|------|

|                                                                                     |                    | -55°C ≤ T <sub>C</sub> ≤ +125°C<br>4.5 V ≤ V <sub>CC</sub> ≤ 5.5 V<br>unless otherwise specified | J .                  | ,              | Min        | Max |      |

| Asynchronous clock input low time 2/7/20/                                           | <sup>t</sup> AWL   | See figures 3 (circuit A) and 4 6/                                                               | 9,10,11              | 01             | 17.5       |     | ns   |

| E. 1. 55.                                                                           |                    |                                                                                                  |                      | 02             | 11         |     |      |

| Asynchronous clock to local                                                         | t <sub>ACF</sub>   |                                                                                                  |                      | 01             |            | 26  |      |

| feedback input 4/21/                                                                |                    |                                                                                                  |                      | 02             |            | 18  |      |

| External asynchronous clock                                                         | t <sub>AP</sub>    |                                                                                                  |                      | 01             | <b>3</b> 5 |     |      |

| period (1/f <sub>MAXA4</sub> ) <u>4</u> /                                           |                    |                                                                                                  |                      | 02             | 25         |     |      |

| External maximum frequency in                                                       | f <sub>MAXA1</sub> |                                                                                                  |                      | 01             | 18         |     | MHz  |

| asynchronous mode $1/(t_{ACO1} + t_{AS1})$ 4/ 22/                                   |                    |                                                                                                  |                      | 02             | 27         |     |      |

| Maximum internal asynchronous frequency (1/(t <sub>S1</sub> + t <sub>CF</sub> )) or | f <sub>MAXA2</sub> |                                                                                                  |                      | 01             | 27         |     |      |

| (1/t <sub>co1</sub> ) <u>4</u> / <u>23</u> ) <sup>-</sup>                           |                    |                                                                                                  |                      | 02             | 40         |     |      |

| Data path maximum frequency in asynchronous mode 1/(tul +                           | f <sub>MAXA3</sub> |                                                                                                  |                      | 01             | 22         |     |      |

| asynchronous mode $1/(t_{H} + t_{H})$ , $1/(t_{S1} + t_{H})$ or $(1/t_{CO1})$       |                    |                                                                                                  |                      | 02             | 33         |     |      |

| Maximum asynchronous register                                                       | f <sub>MAXA4</sub> |                                                                                                  |                      | 01             | 28.5       |     |      |

| toggle frequency 1/(t <sub>AWH</sub> +<br>t <sub>AWL)</sub> 4/ <u>25</u> /          |                    |                                                                                                  |                      | 02             | 40         |     |      |

| Output data stable time from asynchronous clock input                               | <sup>t</sup> AOH   |                                                                                                  |                      | All            | 15         |     | ns   |

- 1/ These are absolute values with respect to device ground and all overshoots due to system or tester noise are included.

- 2/ Tested initially and after any design or process changes that affect that parameter, and therefore shall be guaranteed to the limits specified in table I.

- 3/ For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 1 second.

- $\underline{4}$ / May not be tested but shall be guaranteed to the limits specified in table I.

- 5/ Measured with device programmed as a 16-bit counter in each LAB.

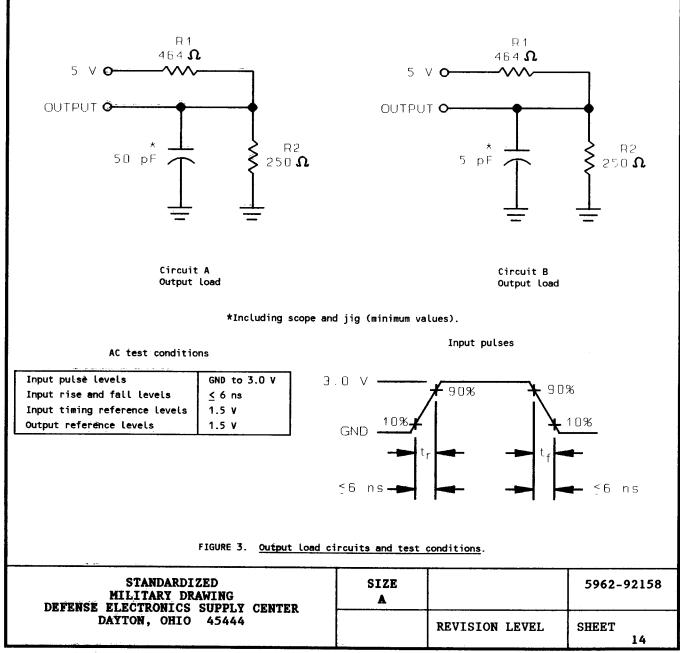

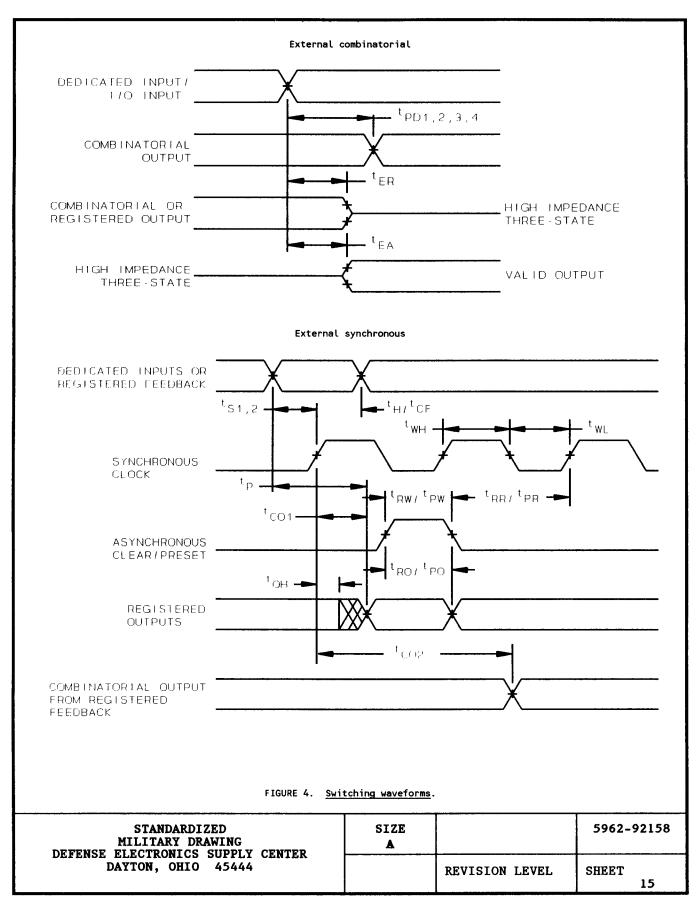

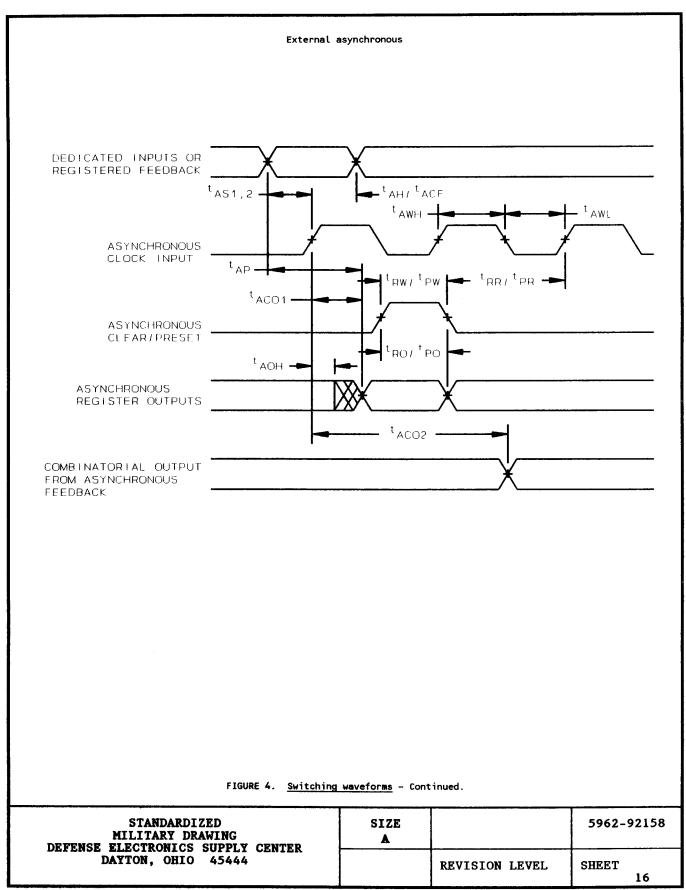

- 6/ AC tests are performed with input rise and fall times of 6 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V, and the output loads on figure 3.

- 7/ This specification is a measure of the delay from input signal applied to a dedicated input to combinatorial output on any output pin. This delay assumes no expander terms are used to form the logic function.

When this note is appled to any parameter specification it indicates that the signal (data, asynchronous clock, asynchronous clear, and/or asynchronous preset) is applied to a dedicated input only and no signal path (either clock or data) employs expander logic.

If an input signal is applied to an I/O pin, an additional delay equal to  $t_{PIA}$  should be added to the comparable delay for a dedicated input. If expanders are used, add the maximum expander delay  $t_{EXP}$  to the overall delay for the comparable delay without expanders.

- 8/ This specification is a measure of the delay from input signal applied to an I/O macrocell pin to any output. This delay assumes no expander terms are used to form the logic function.

- 9/ This specification is a measure of the delay from an input signal applied to a dedicated input to combinatorial output on any output pin. This delay assumes expander terms are used to form the logic function and includes the worst-case expander logic delay for one pass through the expander logic.

| STANDARDIZED  MILITARY DRAWING  DEFENSE ELECTRONICS SUPPLY CENTER  DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-92158  |

|---------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                       |           | REVISION LEVEL | SHEET<br>10 |

# TABLE I. <u>Electrical performance characteristics</u> - Continued.

$\underline{10}$ / This specification is a measure of the delay from an input signal applied to an I/O macrocell pin to any output. This delay assumes expander terms are used to form the logic function and includes the worst-case expander logic delay for one pass through the expander logic.

11/ This specification is a measure of the delay from synchronous register clock to internal feedback of the register output signal to the input of the LAB logic array and then to a combinatorial output. This delay assumes no expanders are used, register is synchronously clocked and all feedback is within the same LAB.

12/ If data is applied to an I/O input for capture by a macrocell register, the I/O pin set-up time minimums

should be observed. These parameters are  $t_{\rm S2}$  for synchronous operation and  $t_{\rm AS2}$  for asynchronous operation. 13/ This specification is a measure of the delay associated with the internal register feedback path. This is the delay from synchronous clock to LAB logic array input. This delay plus the register set-up time, t<sub>S1</sub>, is the minimum internal period for an internal synchronous state machine configuration. This delay is for feedback within the same LAB.

14/ This specification indicates the guaranteed maximum frequency, in synchronous mode, at which a state machine configuration with external feedback can operate. It is assumed that all data inputs and feedback signals are applied to dedicated inputs.

15/ This specification indicates the guaranteed maximum frequency at which a state machine, with internal-only feedback, can operate. If register output states must also control external points, this frequency can still be observed as long as this frequency is less than  $1/t_{CO1}$ . All feedback is assumed to be local, originating within the same LAB.

16/ This frequency indicates the maximum frequency at which the device may operate in data path mode. This delay assumes data input signals are applied to dedicated inputs and no expander logic is used.

17/ This specification indicates the guaranteed maximum frequency, in synchronous mode, at which an individual output or buried register can be cycled.

18/ This parameter indicates the minimum time after a synchronous register clock input that the previous register output data is maintained on the output pin.

19/ This specification is a measure of the delay from an asynchronous register clock input to internal feedback of the register output signal to the input of the LAB logic array and then to a combinatorial output. This delay assumes no expanders are used in the logic of combinatorial output or the asynchronous clock input. The clock signal is applied to a dedicated input pin and all feedback is within a single LAB.

20/ This parameter is measured with a positive-edge triggered clock at the register. For negative edge triggering, the t<sub>AWH</sub> and t<sub>AWL</sub> parameters must be swapped. If a given input is used to clock multiple registers with both positive and negative polarity, t<sub>AWH</sub> should be used for both t<sub>AWH</sub> and t<sub>AWL</sub>.

21/ This specification is a measure of the delay associated with the internal register feedback path for an

asynchronous clock to LAB logic array in put. This delay plus the asynchronous register set-up time,  $t_{AS1}$ , is the minimum internal period for an internal asynchronous clocked state machine configuration. This delay is for feedback within the same LAB, assumes no expander logic in the clock path, and assumes that the clock input signal is applied to a dedicated input pin.

22/ This specification indicates the guaranteed maximum frequency at which an asynchronously clocked state machine configuration with external feedback can operate. It is assumed that all data inputs, clock inputs, and feedback signals are applied to dedicated inputs, and that no expander logic is employed in the clock signal path or data path.

23/ This specification indicates the guaranteed maximum frequency at which an asynchronously clocked state machine with internal-only feedback can operate. This parameter is determined by the lesser of (1/(t<sub>ACF</sub> + 1/t<sub>AS1</sub>)) or (1/(t<sub>AWH</sub> + t<sub>AWL</sub>)). If register output states must also control external points, this frequency can still be observed as long as this frequency is less than 1/t<sub>ACO1</sub>.

24/ This frequency is the maximum frequency at which the device may operate in the asynchronously clocked data

path mode. This specification is determined by the least of  $1/(t_{AWH} + t_{AWL})$ ,  $1/(t_{AS1} + t_{AH})$  or  $1/t_{ACO1}$ . It assumes data and clock input signals are applied to dedicated input pins and no expander logic is used.

25/ This specification indicates the guaranteed maximum frequency at which an individual output or buried register can be cycled in asynchronously clocked mode by a clock signal applied to an external dedicated input pin.

26/ This parameter indicates the minimum time that the previous register output data is maintained on the output after an asynchronous register clock input.

- 3.3 Electrical performance characteristics and postirradiation parameter limits. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 Electrical test requirements. The electrical test requirements shall be the subgroups specified in table IIA. The electrical tests for each subgroup are defined in table I.

5962-92158 **STANDARDIZED** SIZE MILITARY DRAWING A DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL SHEET 11

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes B and S shall be in accordance with MIL-M-38510. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes B and S shall be a "J" or "JAN" as required in MIL-M-38510. The certification mark for device classes Q and V shall be a "QML" as required in MIL-I-38535.

- 3.6 <u>Certificate of compliance</u>. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.3 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.2 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or device classes B and S in MIL-M-38510 or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-480.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device classes M, B, and S</u>. Device classes M, B, and S devices covered by this drawing shall be in microcircuit group number 42 (see MIL-M-38510, appendix E).

- 3.11 <u>Serialization for device class S</u>. All device class S devices shall be serialized in accordance with MIL-M-38510.

- 3.12 <u>Processing EPLDs.</u> All testing requirements and quality assurance provisions herein shall be satisfied by the manufacturer prior to delivery.

- 3.12.1 <u>Frasure of EPLDs.</u> When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.6.

- 3.12.2 <u>Programmability of EPLDs.</u> When specified, devices shall be programmed to the specified pattern using the procedures and characteristics specified in 4.7.

- 3.12.3 <u>Verification of erasure or programmed EPLDs</u>. When specified, devices shall be verified as either programmed to the specified pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

- 3.13 <u>Endurance</u>. A reprogrammability test shall be completed as part of the vendor's reliability monitors, this reprogrammability test shall be done only for initial characterization and after any design or process changes which may affect the reprogrammability of the device. This test shall consist of 25 program/erase cycles on 25 devices with the following conditions:

- (1) All devices selected for testing shall be programmed in accordance with 3.2.3.1 herein.

- (2) Verify pattern (see 3.12.3).

- (3) Erase (see 3.12.1).

- (4) Verify pattern erasure (see 3.12.3)

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>12 |

| Device types  | All             |

|---------------|-----------------|

| Case outlines | X               |

| Terminal      | Terminal symbol |

| number        | ,               |

| 1             | 1/0             |

| 2             | 1/0             |

| 3             | v <sub>cc</sub> |

| 4             | 1/0             |

| 5             | 1/0             |

| 6             | 1/0             |

| 7             | I/O             |

| 8             | 1/0             |

| 9             | INPUT           |

| 10            | GND             |

| 11            | INPUT           |

| 12            | INPUT           |

| 13            | INPUT           |

| 14            | v <sub>cc</sub> |

| 15            | 1/0             |

| 16            | 1/0             |

| 17            | 1/0             |

| 18            | 1/0             |

| 19            | 1/0             |

| 20            | 1/0             |

| 21            | GND             |

| 22            | 1/0             |

| 23            | 1/0             |

| 24            | 1/0             |

| 25            | V <sub>CC</sub> |

| 26            | 1/0             |

| 27            | 1/0             |

| 28            | 1/0             |

| 29            | 1/0             |

| 30<br>31      | I/O<br>INPUT    |

| 32            |                 |

| 33            | GND<br>INPUT    |

| 34            | INPUT/CLK       |

| 35            | INPUT           |

| 36            |                 |

| 37            | V <sub>CC</sub> |

| 38            | 1/0             |

| 39            | 1/0             |

| 40            | 1/0             |

| 41            | 1/0             |

| 42            | 1/0             |

| 43            | GND             |

| 44            | 1/0             |

FIGURE 1. Terminal connections.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE |                | 5962-9215 <b>8</b> |

|------------------------------------------------------|------|----------------|--------------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |      | REVISION LEVEL | SHEET 13           |

| Truth table |        |                |  |  |  |

|-------------|--------|----------------|--|--|--|

| Input       | t pins | Output<br>pins |  |  |  |

| I/CFK       | 1      | 1/0            |  |  |  |

| х           | х      | Z              |  |  |  |

# NOTES:

- 1. X = Don't care.

- 2. Z = High impedance.

FIGURE 2. Truth table (unprogrammed).

### 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein). For device classes B and S, sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 and the device manufacturer's QM plan.

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes B and S, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to qualification and quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-I-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device classes M, B, and S.

- a. Delete the sequence specified as initial (pre-burn-in) electrical parameters through interim (post-burn-in) electrical parameters of method 5004 and substitute lines 1 through 6 of table IIA herein.

- b. For device class M, the burn-in test circuit shall be submitted to DESC-EC for review with the certificate of compliance. For device classes B and S, the burn-in test circuit shall be submitted to the qualifying activity.

- (1) Static burn-in for device class S (method 1015 of MIL-STD-883, test condition A).

- (a) All inputs shall be connected to GND. Outputs may be open or connected to 4.5 V minimum. Resistors R1 are optional on both inputs and outputs, and required on outputs connected to  $V_{CC}$   $\pm 0.5$  V. R1 = 220 $\Omega$  to 47 k $\Omega$ . For static II burn-in, reverse all input connections (i.e.,  $V_{SS}$  to  $V_{CC}$ ).

- (b)  $V_{CC} = 4.5 \text{ V minimum}.$

- (c) Ambient temperature  $(T_A)$  shall be  $+125^{\circ}C$  minimum.

- (d) Test duration for the static test shall be 48 hours minimum. The 48-hour burn-in shall be broken into two sequences of 24 hours each (Static I and Static II) followed by interim electrical measurements.

- (2) Dynamic burn-in for device classes M, B, and S (method 1015 of MIL-STD-883, test condition D) using the circuit submitted (see 4.2.1b herein).

- c. Interim and final electrical parameters shall be as specified in table IIA herein.

- d. A data retention stress test shall be included as part of the screening procedure and shall consist of the following steps: (Steps 1 through 4 may be performed at the wafer level. The maximum storage temperature shall not exceed +200°C for packaged devices or +300°C for unassmbled devices.)

Margin test method. \*Steps 1 through 3 may be performed at wafer level.

- Program a minimum or 95 percent of the total number of cells, including the slowest programming cell (see 3.12.2).

- (2) Bake, unbiased, for 72 hours at  $+140^{\circ}$ C or for 32 hours at  $+150^{\circ}$ C or for 8 hours at  $+200^{\circ}$ C or for 2 hours at  $+300^{\circ}$ C for unassembled devices only.

- (3) Perform electrical test (see 4.2.b) at +25°C including a margin test at Vm = +5.7 V and loose timing (i.e.,  $1 \mu s$ ).

- (4) Erase (see 3.12.1).

- (5) Program a minimum of 50 percent of the total number of cells, including the slowest programming cell (see 3 12 2)

- (6) Perform electrical test (see 4.2.b) at +25°C including a margin test at Vm = +5.7 V and loose timing (i.e., 1  $\mu$ s).

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-92158  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>17 |

DESC FORM 193A

JUL 91

- (7) Perform burn-in (see 4.2.1a).

- (8) Perform electrical test (see 4.2.1b) at +25°C including a margin test at Vm = +5.7 V and loose timing (i.e., 1  $\mu$ s).

- (9) Perform electrical tests at  $T_c = +125$ °C.

- (10) Perform electrical tests at  $T_c = -55$ °C.

- (11) Erase (see 3.12.1). Devices may be submitted for groups A, B, C, and D testing.

- (12) Verify erasure (see 3.12.3).

# 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition, and test temperature or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be submitted to DESC-EC with the certificate of compliance and shall be under the control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535.

- b. Interim and final electrical test parameters shall be as specified in table IIA herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MIL-I-38535 and as detailed in table IIB herein.

- d. Additional requirements beyond MIL-I-38535 for classes Q and V are specified in table IIA herein.

# 4.2.3 Percent Defective Allowable (PDA).

- a. The PDA for class S devices shall be 5 percent for static burn-in and 5 percent for dynamic burn-in, based on the exact number of devices submitted to each separate burn-in.

- b. The PDA for class B devices shall be in accordance with MIL-M-38510 for dynamic burn-in.

- c. Static burn-in I and II failures shall be cumulative for determining PDA.

- d. Those devices whose measured characteristics, after burn-in, exceed the specified delta limits or electrical parameter limits specified in table I, subgroup 1, are defective and shall be removed from the lot. The verified failures divided by the total number of devices in the lot initially submitted to burn-in shall be used to determine the percent defective for the lot and the lot shall be accepted or rejected based on the specified PDA.

- e. The PDA for device classes Q and V shall be in accordance with MIL-I-38535 for dynamic burn-in.

# 4.3 Qualification inspection.

- 4.3.1 <u>Qualification inspection for device classes B and S</u>. Qualification inspection for device classes B and S shall be in accordance with MIL-M-38510. Inspections to be performed shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5). Qualification data for subgroups 7, 8A, and 8B shall be attributes only.

- 4.3.1.1 Qualification extension for device class B and S. When authorized by the qualifying activity, if a manufacturer qualifies one device type which is identical (i.e., same die) to other device types on this specification, the slower device types may be part I qualified, upon the request of the manufacturer, without any further testing. The faster device types may be part I qualified by performing only group A qualification testing.

- 4.3.2 Qualification inspection for device classes Q and V. Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.3.3 <u>Electrostatic Discharge Sensitivity (ESDS) inspection</u>. ESDS testing shall be performed in accordance with MIL-STD-883, method 3015. ESDS testing shall be measured only for initial qualification and after process or design changes which may affect ESDS classification.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                | 5962-92158  |

|-----------------------------------------------------------------|-----------|----------------|-------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL | SHEET<br>18 |

TABLE IIA. <u>Electrical test requirements</u>. <u>1</u>/ <u>2</u>/ <u>3</u>/ <u>4</u>/ <u>5</u>/ <u>6</u>/ <u>7</u>/