|                       |          |                  |     |          |        |               |        | RE | visi | ons      |       |    |      |     |        |             | ,    |         |                                         |             |

|-----------------------|----------|------------------|-----|----------|--------|---------------|--------|----|------|----------|-------|----|------|-----|--------|-------------|------|---------|-----------------------------------------|-------------|

| LTR                   |          |                  |     |          | DI     | ESCRI         | PTIC   | N  |      |          |       |    | D.   | ATE | (YR-MO | -DA)        |      | APPR    | OVED                                    |             |

|                       |          |                  |     |          |        |               |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| REV                   | <u> </u> |                  |     |          |        | <u> </u>      |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| SHEET                 |          |                  |     |          |        |               |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| REV                   |          |                  |     |          |        |               |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| SHEET                 |          |                  |     |          |        |               |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| REV                   |          |                  |     |          |        |               |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| SHEET                 | 15       | 16               | 17  | 18       | 19     | 20            | 21     | 22 | 23   | 24       | 25    | 26 | 27   |     |        |             |      |         |                                         |             |

| REV STAT              | US       |                  |     | RE       | v      |               |        |    |      |          |       |    |      |     |        |             |      |         |                                         |             |

| OF SHEET              | s        |                  |     | SH       | EET    |               | 1      | 2  | 3    | 4        | 5     | 6  | 7    | 8   | 9      | 10          | 11   | 12      | 13                                      | 14          |

| PMIC N/A              |          |                  |     |          | ARED E | SY<br>1. Hess | 3      |    |      | Di       | EFENS |    |      |     |        | PPLY<br>454 |      | TER     |                                         |             |

|                       | ITAI     | RY               | )   |          | KED BY | r<br>1. Hes:  | \$     |    |      |          |       |    |      |     |        |             |      | · · · · |                                         |             |

| THIS DRAWIN           | ALL DE   | VAILA!<br>PARTME | NTS |          | OVED E | BY<br>Poe     | lking  |    |      |          |       |    | -    |     |        | AL,<br>ONOL |      |         |                                         |             |

| AND AGEN<br>DEPARTMEN |          |                  |     |          | ING AF | PROVA         | L DATE |    |      |          |       | 1  |      |     | Τ.     |             |      |         |                                         |             |

| AMSC N/A              |          |                  |     |          | SION L |               |        |    |      | SIZ<br>A | E     | 1  | E CO |     |        | 59          | 962- | 930     | 06                                      |             |

|                       |          |                  |     |          | J. J.  |               |        |    |      |          | EET   | -  | 1    |     | 0      | F           |      | 27      | - W - W - W - W - W - W - W - W - W - W | <del></del> |

| DESC FORM 102         |          |                  |     | <u> </u> |        |               |        |    |      | <u> </u> |       |    |      |     |        |             |      |         |                                         |             |

ESC FORM 193

JUL 91

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E273-93

# 1. SCOPE

- 1.1 <u>Scope</u>. This drawing forms a part of a one part one part number documentation system (see 6.6 herein). Two product assurance classes consisting of military high reliability (device classes B, Q, and M) and space application (device classes S and V), and a choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). Device class M microcircuits represent non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices". When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

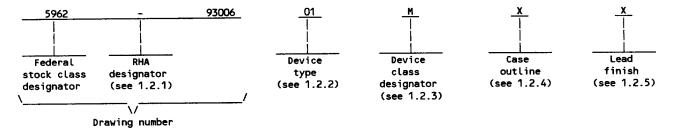

- 1.2 PIN. The PIN shall be as shown in the following example:

- 1.2.1 <u>RHA designator</u>. Device classes M, B, and S RHA marked devices shall meet the MIL-M-38510 specified RHA levels and shall be marked with the appropriate RHA designator. Device classes Q and V RHA marked devices shall meet the MIL-I-38535 specified RHA levels and shall be marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | <u>Generic number</u> | <u>Circuit function</u>  |

|-------------|-----------------------|--------------------------|

| 01          | 320E14                | Digital signal processor |

1.2.3 <u>Device class designator</u>. The device class designator shall be a single letter identifying the product assurance level as follows:

| Device class | Device requirements documentation                                                                                       |

|--------------|-------------------------------------------------------------------------------------------------------------------------|

| м            | Vendor self-certification to the requirements for non-JAN class B microcircuits in accordance with 1.2.1 of MIL-STD-883 |

| B or S       | Certification and qualification to MIL-M-38510                                                                          |

| Q or V       | Certification and qualification to MIL-I-38535                                                                          |

1.2.4 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | Terminals | Package style         |

|----------------|------------------------|-----------|-----------------------|

| x              | CMGA15-P68             | 68        | Pin grid array 1/     |

| Y              | cqcc2-J68              | 68        | J-leaded chip carrier |

1/ This package is inactive for new design.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-93006 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>2 |

| 1.2.5 <u>Lead finish</u> . The lead finish shall be as specified classes Q and V. Finish letter "X" shall not be marked on 1 for use in specifications when lead finishes A, B, and C are preference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | the microcircuit ( | or its packaging. The "X"                                                                                                                                                               | designation is |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1.3 Absolute maximum ratings. 1/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                    |                                                                                                                                                                                         |                |

| Supply voltage range ( $V_{CC}$ ) $2/$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                    | -0.3 V dc to + 7.0 V dc -0.6 V dc to +14.0 V dc -0.3 V dc to +14.0 V dc -0.3 V dc to + 7.0 V dc -0.3 V dc to + 7.0 V dc -0.5 C to +150°C +260°C  36°C/W 50°C/W See MIL-STD-1835 +175°C  | c<br>c         |

| 1.4 Recommended operating conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                    |                                                                                                                                                                                         |                |

| Supply voltage range (V <sub>CC</sub> ) Operating voltage Fast programming Supply voltage range for fast programming 3/(V <sub>PP</sub> ) Supply voltage (V <sub>SS</sub> ) Minimum high level input voltage (V <sub>IH</sub> ) CLKIN, CAPO, CAP1, CMP4/CAP2, CMP5/CAP3, RS IOPO-IOP15 DO-D15, INT, NMI/MC/MP, RXD, TXD, TCLK1/CLK, TCLK2/CLKX Maximum low level input voltage (V <sub>IL</sub> ) CAPO-CAP5 All other inputs Maximum high level output current (I <sub>OH</sub> ) Maximum low level output current (I <sub>OL</sub> ) Case operating temperature range (T <sub>C</sub> )  1.5 <u>Digital logic testing for device classes Q and V</u> .  Fault coverage measurement of manufacturing logic tests (MIL-STD-883, test method 5012) |                    | +4.5 V dc to +5.5 V dc<br>+5.75 V dc to +6.25 V<br>+12.25 V dc to +12.75<br>+0.0 V dc<br>+3.0 V dc<br>+2.4 V dc<br>+2.0 V dc<br>+0.6 V<br>+0.8 V<br>-300 μA<br>+2 mA<br>-55°C to +125°C | dc             |

| 1/ Stresses above the absolute maximum rating may cause maximum levels may degrade performance and affect re 2/ All voltage values are with respect to V <sub>SS</sub> . 3/ V <sub>pp</sub> can be applied only to programming pins designed supply current is I <sub>pp</sub> + I <sub>CC</sub> . 4/ Values will be added when they become available.                                                                                                                                                                                                                                                                                                                                                                                           | liability.         |                                                                                                                                                                                         |                |

| STANDARDIZED<br>MILITARY DRAWING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SIZE<br>A          |                                                                                                                                                                                         | 5962-93006     |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    | REVISION LEVEL                                                                                                                                                                          | SHEET 3        |

# 2. APPLICABLE DOCUMENTS

2.1 Government specifications, standards, bulletin, and handbook. Unless otherwise specified, the following specifications, standards, bulletin, and handbook of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

#### SPECIFICATIONS

MILITARY

MIL-M-38510 - Microcircuits, General Specification for.

MIL-I-38535 - Integrated Circuits, Manufacturing, General Specification for.

**STANDARDS**

MILITARY

MIL-STD-480 - Configuration Control-Engineering Changes, Deviations and Waivers.

MIL-STD-883 - Test Methods and Procedures for Microelectronics.

MIL-STD-1835 - Microcircuit Case Outlines.

BULLETIN

MILITARY

MIL-BUL-103 - List of Standardized Military Drawings (SMD's).

HANDBOOK

MILITARY

MIL-HDBK-780 - Standardized Military Drawings.

(Copies of the specifications, standards, bulletin, and handbook required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

# 3. REQUIREMENTS

- 3.1 Item requirements. The individual item requirements for device class M shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. The individual item requirements for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. For device classes B and S, a full electrical characterization table for each device type shall be included in this SMD. The individual item requirements for device classes Q and V shall be in accordance with MIL-I-38535, the device manufacturer's Quality Management (QM) plan, and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 for device classes M, B, and S and MIL-I-38535 for device classes Q and V and herein.

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.4 herein.

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 1.

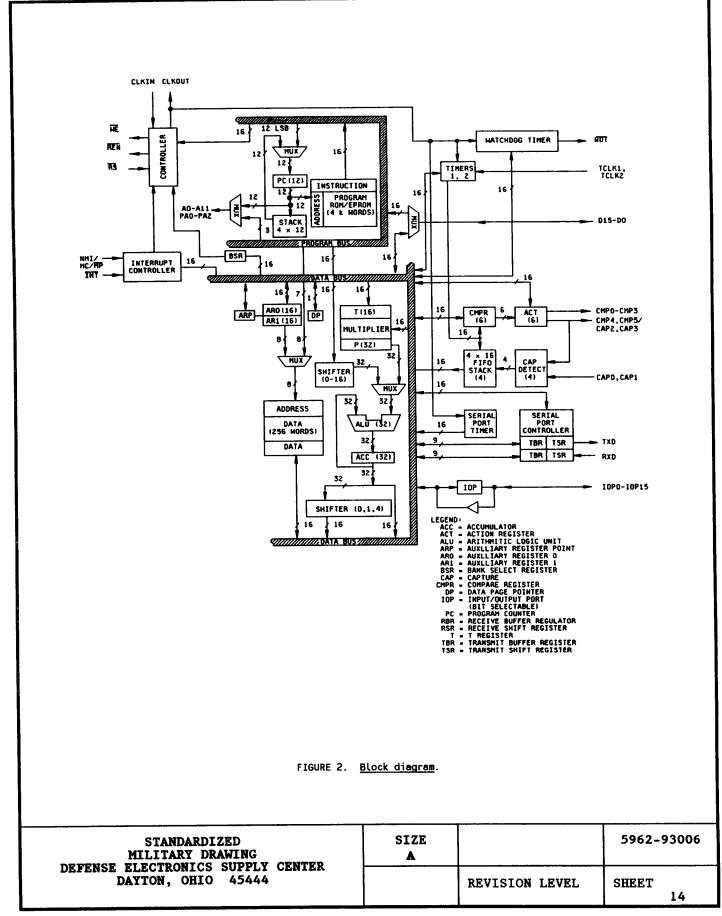

- 3.2.3 Block Diagram. The block diagram shall be as specified on figure 2.

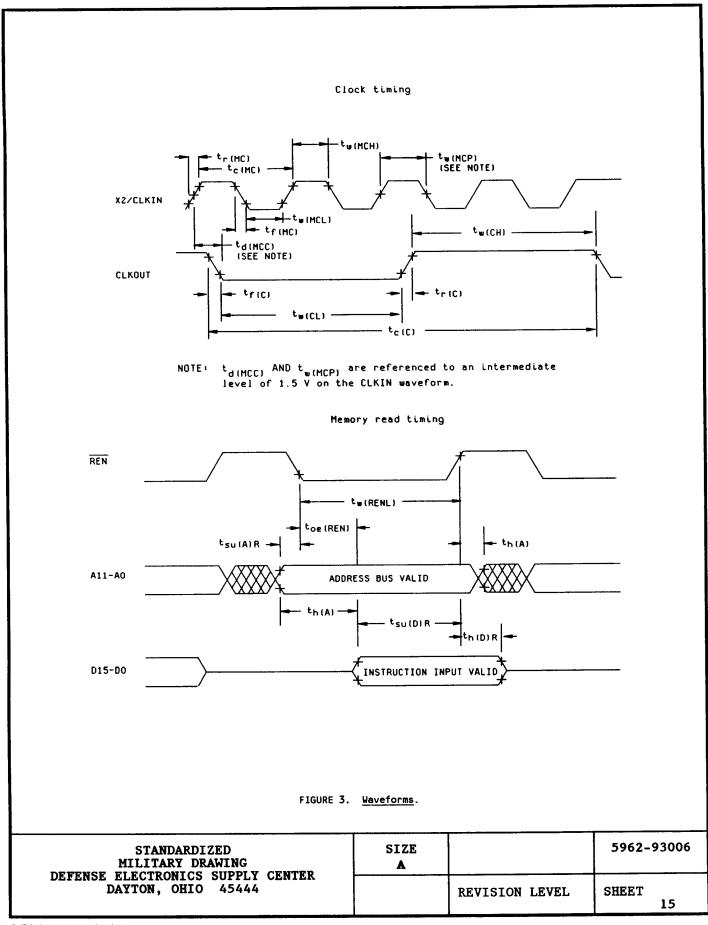

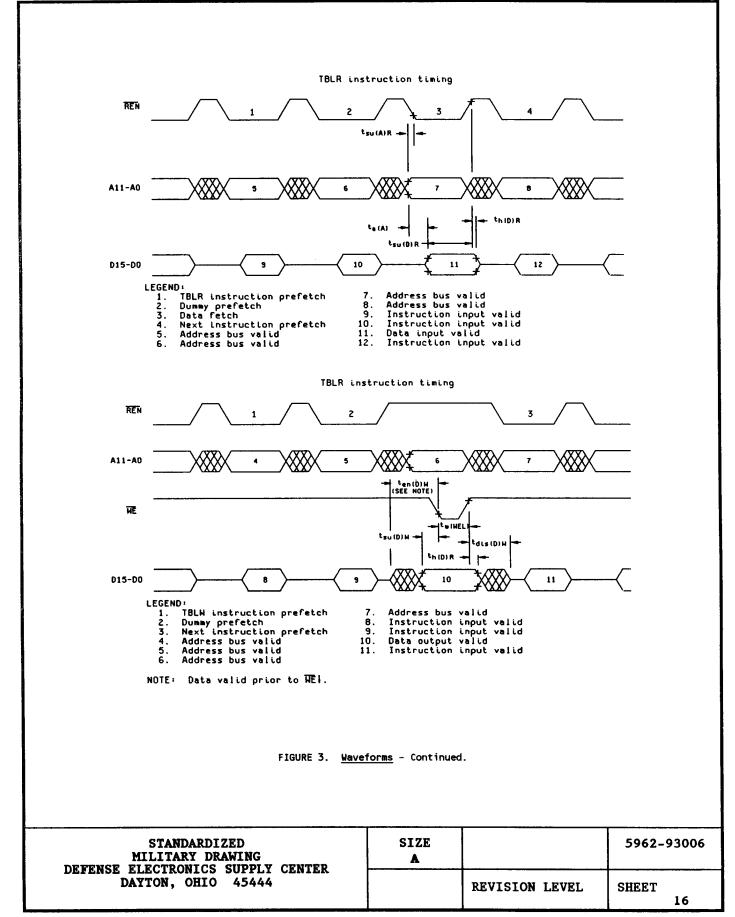

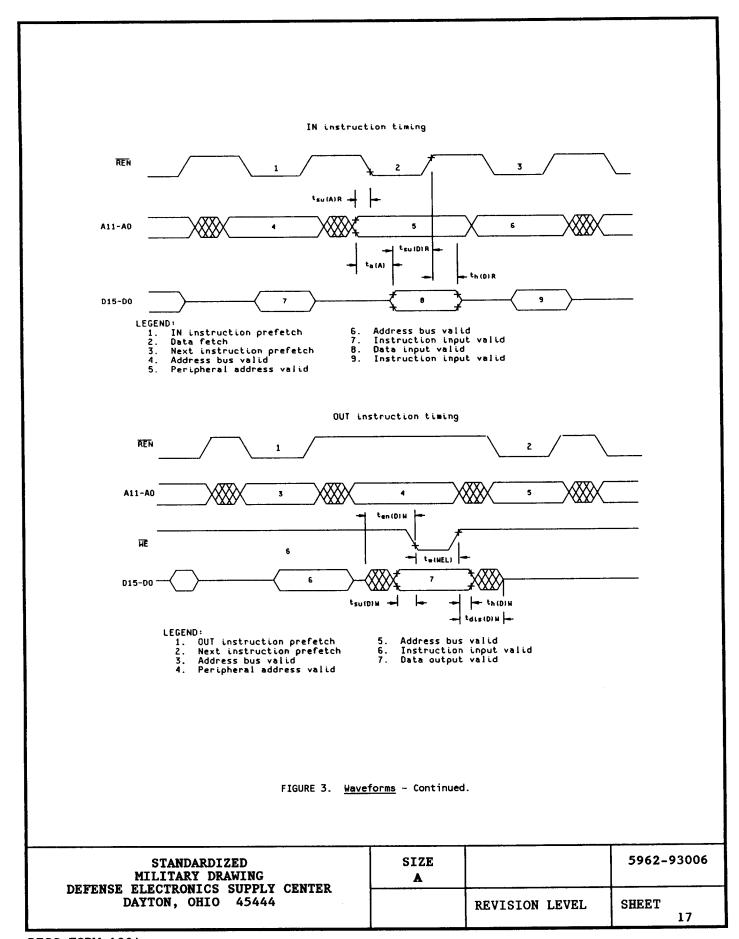

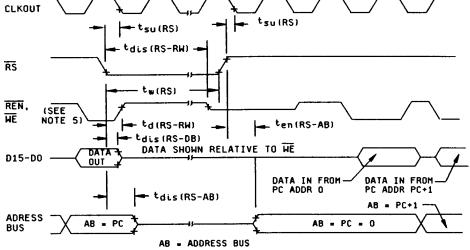

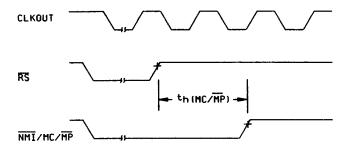

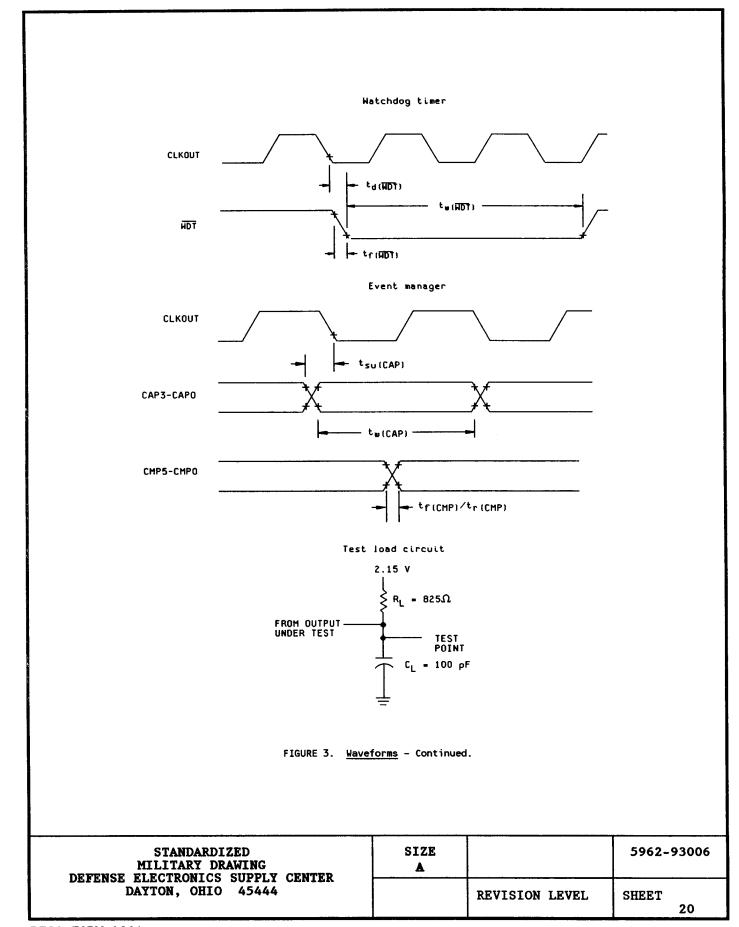

- 3.2.4 Waveforms. The waveforms shall be as specified on figure 3.

- 3.2.5 Radiation exposure circuit. The radiation exposure circuit shall be as specified when available.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                | 5962-93006 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>4 |

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and postirradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 Marking. The part shall be marked with the PIN listed in 1.2 herein. Marking for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein). In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103. Marking for device classes B and S shall be in accordance with MIL-M-38510. Marking for device classes Q and V shall be in accordance with MIL-I-38535.

- 3.5.1 <u>Certification/compliance mark</u>. The compliance mark for device class M shall be a "C" as required in MIL-STD-883 (see 3.1 herein). The certification mark for device classes B and S shall be a "J" or "JAN" as required in MIL-M-38510. The certification mark for device classes Q and V shall be a "QML" as required in MIL-I-38535.

- 3.6 Certificate of compliance. For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.7.3 herein). For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.7.2 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device class M, the requirements of MIL-STD-883 (see 3.1 herein), or for device classes Q and V, the requirements of MIL-I-38535 and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device class M in MIL-STD-883 (see 3.1 herein) or device classes B and S in MIL-M-38510 or for device classes Q and V in MIL-I-38535 shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change for device class M. For device class M, notification to DESC-EC of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change as defined in MIL-STD-480.

- 3.9 <u>Verification and review for device class M</u>. For device class M, DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device classes M, B, and S</u>. Device classes M, B, and S devices covered by this drawing shall be in microcircuit group number 105 (see MIL-M-38510, appendix E).

- 3.11 <u>Serialization for device class S</u>. All device class S devices shall be serialized in accordance with MIL-M-38510.

- 3.12 <u>Processing EPROM's</u>. All testing requirements and quality assurance provisions herein shall be serialized in accordance with MIL-M-38510.

- 3.12.1 <u>Erasure of EPROM's</u>. When specified, devices shall be erased in accordance with the procedures and characteristics specified in 4.5.

- 3.12.2 <u>Programmability of EPROM's</u>. When specified, devices shall be programmed to the specifed pattern using the procedures and characteristics specified in 4.6 and table III.

- 3.12.3 <u>Verification of erasure of programmability of EPROM's</u>. When specified, devices shall be verified as either programmed to the specifed pattern or erased. As a minimum, verification shall consist of performing a functional test (subgroup 7) to verify that all bits are in the proper state. Any bit that does not verify to be in the proper state shall constitute a device failure, and shall be removed from the lot.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. For device class M, sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein). For device classes B and S, sampling and inspection procedures shall be in accordance with MIL-M-38510 and method 5005 of MIL-STD-883, except as modified herein. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-I-38535 and the device manufacturer's QM plan.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZ <b>E</b><br>A |                | 5962-93006 |

|------------------------------------------------------|-------------------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                   | REVISION LEVEL | SHEET<br>5 |

| Test                                                  | Symbol              | Cond<br>–55°C ≤ T                                                                     | itions <u>1</u> /<br>_ ≤ +125°C | Group A subgroups | Device<br>type | Limits             |      | Unit    |

|-------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------|---------------------------------|-------------------|----------------|--------------------|------|---------|

|                                                       |                     | -55°C ≤ T<br>4.5 V ≤ V<br>unless otherw                                               | CC ≤ 5.5 V<br>ise specified     |                   | <br>           | Min                | Max  |         |

| High-level output volt <b>age</b>                     | VOH                 | V <sub>CC</sub> = 4.5 V<br>I <sub>OH</sub> = -300 μA                                  |                                 | 1,2,3             | 01             | 2.4                |      | ٧       |

|                                                       |                     | $V_{CC} = 4.5 \text{ V}$<br>$I_{OH} = 20 \mu\text{A}$                                 | <u>2</u> / <u>3</u> /           |                   |                | ν <sub>cδ.</sub> - | <br> |         |

| Low-level output voltage                              | v <sub>OL</sub>     | V <sub>CC</sub> = 4.5 V<br>I <sub>OL</sub> = 2 mA                                     |                                 | 1,2,3             | 01             | <br>               | 0.6  | ٧       |

| Off-state output current                              | Ioz                 | v <sub>cc</sub> = 5.5 v                                                               | v <sub>0</sub> = 2.4 v          | 1,2,3             | 01             |                    | 20   | μΑ      |

|                                                       |                     |                                                                                       | V <sub>0</sub> = 0.4 V          |                   |                |                    | -20  |         |

| Input current I <sub>I</sub>                          |                     | V <sub>I</sub> = V <sub>SS</sub> to<br>  V <sub>CC</sub><br>  V <sub>CC</sub> = 5.5 V | CLKIN                           | 1,2,3             | 01             |                    | ±50  | μΑ      |

|                                                       |                     | v <sub>cc</sub> = 5.5 v                                                               | All other                       |                   |                | <br> <br>          | ±20  |         |

| Supply current 4/                                     | 1 <sub>CC</sub>     | f = 20.5 MHz                                                                          | v <sub>cc</sub> = 5.5 v         | 1,2,3             | 01             |                    | 90   | mA      |

| V <sub>pp</sub> supply current                        | I <sub>PP1</sub>    | V <sub>PP</sub> = 5.5 V,                                                              | v <sub>cc</sub> = 5.5 v         | 1,2,3             | 01             |                    | 100  | μА      |

| V <sub>pp</sub> supply current (during program pulse) | I <sub>PP2</sub>    | V <sub>PP</sub> = 13 V                                                                |                                 | 1,2,3             | 01             |                    | 50   | mA      |

| Input capacitance                                     | cIN                 | See 4.4.1c                                                                            |                                 | 4                 | 01             |                    | 25   | рF      |

| Output capacitance                                    | C <sub>OUT</sub>    | See 4.4.1c                                                                            |                                 | 4                 | 01             |                    | 25   | pF      |

| Input/output capacitance                              | c <sub>1/0</sub>    | See 4.4.1c                                                                            |                                 | 4                 | 01             |                    | 35   | pF      |

| Functional test                                       |                     | See 4.4.1b                                                                            |                                 | 7, 8              | 01             |                    |      |         |

| See footnotes at end of tab                           | le.                 |                                                                                       |                                 |                   | <u> </u>       |                    |      | L       |

| MILITARY                                              | ARDIZED<br>Y DRAWII | NG                                                                                    | SI                              | ı                 |                |                    | 59   | 62-9300 |

| DEFENSE ELECTRON<br>DAYTON, O                         |                     |                                                                                       |                                 | RE                | WISTON         | LEVEL              | SHE  | PT      |

6

| Test                                                                 | Symbol   Conditions<br>  -55°C $\leq$ T <sub>C</sub> $\leq$ +1 |                                                                                                                                | ns <u>1</u> /   Group A<br>+125°C   subgroups | Device type | Limits         |                                | Unit             |             |  |

|----------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------|----------------|--------------------------------|------------------|-------------|--|

|                                                                      | <br>                                                           | $-55^{\circ}\text{C} \le T_{\text{C}} \le +$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le \frac{1}{2}$<br>unless otherwise s | 5.5 V<br>pecified                             |             |                | Min                            | Max              |             |  |

|                                                                      | •                                                              | External clo                                                                                                                   | ck requirements                               | ;           |                |                                |                  |             |  |

| Input clock frequency                                                | CLKIN                                                          | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9,                                            | ,10,11      | 01             | 6.7                            | <br>  20.5  <br> | MHz         |  |

|                                                                      |                                                                | Clock                                                                                                                          | timing                                        |             |                |                                |                  |             |  |

| CLKOUT cycle time <u>5</u> /                                         | t <sub>c(C)</sub>                                              | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9                                             | ,10,11      | 01             | <br>  195<br>                  | 600              | ns          |  |

| Delay time CLKIN↑ to CLKOUT↓                                         | t <sub>d(MCC)</sub>                                            | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9                                             | ,10,11      | 01             |                                | 60               | ns          |  |

| Master clock cycle time <u>5</u> /                                   | t <sub>c(MC)</sub>                                             | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9                                             | ,10,11      | 01             | <br>  48.75<br>                | 150              | ns          |  |

| Rise time, master clock input 3/                                     | <sup>t</sup> r(MC)                                             | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9                                             | ,10,11      | 01             | <b>1</b>                       | 10               | ns          |  |

| Fall time, master clock input 3/                                     | <sup>t</sup> f(MC)                                             | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        |                                               | ,10,11      | 01             |                                | 10               | ns          |  |

| Pulse duration, master clock                                         | <sup>t</sup> w(MCP)                                            | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9                                             | ,10,11      | 01             | 0.45                           | 0.55             | ns          |  |

| Pulse duration, master clock low 3/                                  | t <sub>w</sub> (MCL)                                           | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        |                                               | ,10,11      | 01             |                                | 82.5             | ns          |  |

| Pulse duration, master clock high <u>3</u> /                         | t <sub>w</sub> (MCH)                                           | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                        | 9                                             | ,10,11      | 01             |                                | 82.5             | ns          |  |

|                                                                      |                                                                | Memory read and                                                                                                                | instruction ti                                | iming       |                |                                |                  |             |  |

| Setup time, add <u>res</u> s bus<br>valid before REN↓                | t <sub>su(A)R</sub>                                            | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                      | 9                                             | ,10,11      | 01             | 0.25                           |                  | ns          |  |

| Setup time, add <u>re</u> ss bus<br>valid before WE↓                 | t <sub>su(A)W</sub>                                            | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                      | Ş                                             | ,10,11      | 01             | 0.50<br> t <sub>c(C)</sub> -45 |                  | ns          |  |

| Hold tim <u>e, address</u> bus valid<br>after REN† or WE† <u>3</u> / | t <sub>h(A)</sub>                                              | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                      | 5                                             | 2,10,11     | 01             | 5                              |                  | ns          |  |

| See footnotes at end of tabl                                         | e.                                                             |                                                                                                                                |                                               |             | <del>, I</del> |                                |                  |             |  |

| STANDAI<br>MILITARY                                                  |                                                                | G                                                                                                                              | SIZE                                          |             |                |                                | 5962             | -9300       |  |

| DEFENSE ELECTRONI<br>DAYTON, OH                                      |                                                                |                                                                                                                                | <u> </u>                                      | RF          | VISION         | I.EVEI.                        | SHEET            | <del></del> |  |

| Test                                                                  | Symbol               | Conditions $\underline{1}$<br>-55°C $\leq$ T <sub>C</sub> $\leq$ +125°                                                                      | / Group A          | Device<br>s type | Limits                         |                               | Unit         |

|-----------------------------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|--------------------------------|-------------------------------|--------------|

| ;                                                                     |                      | $-55^{\circ}\text{C} \le \text{T}_{\text{C}} \le +125^{\circ}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5$<br>unless otherwise spec | V  <br>ified  <br> |                  | <br>  Min                      | Max                           |              |

| nable time, data star <u>ts</u><br>being driven before WE↓ <u>3</u> / | t <sub>en(D)W</sub>  | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,11            | 01               |                                | 0.25<br>t <sub>c(C)</sub>     | ns           |

| etup_time, data valid prior<br>to WE↓                                 | t <sub>su(D)W</sub>  | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,11            | <br>  01<br>     | 0.25<br>t <sub>c(C)</sub> -45  |                               | ns           |

| o <u>ld</u> time, data valid after<br>WET                             | t <sub>h(D)W</sub>   | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,11            | 01               | 0.25<br> t <sub>c(C)</sub> -10 |                               | ns           |

| isable time, data <u>i</u> n high<br>impedance after WE† <u>3</u> /   | tdis(D)W             | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,11            | 01               |                                | 0.25<br>t <sub>c(C)</sub> +25 | ns           |

| ulse duration, WE low                                                 | t <sub>w</sub> (WEL) | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,1             | 1 01             | 0.50<br> t <sub>c(C)</sub> -20 |                               | ns           |

| ulse duration, REN low                                                | tw(RENL)             | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                   | 9,10,1             | 1 01             | 0.75<br>t <sub>c(C)</sub> -20  |                               | ns           |

| Write reco <u>ve</u> ry tim <u>e,</u> time<br>between WE↑ and REN↓    | trec(WE)             | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                   | 9,10,1             | 1 01             | 0.25                           |                               | ns           |

| Read recov <u>ery</u> time, <u>t</u> ime<br>between REN↑ and WE↓      | trec<br>(REN)        | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                   | 9,10,1             | 1 01             | 0.50<br> t <sub>c(C)</sub> -10 |                               | ns           |

| Delay time WET to CLKOUTT                                             | t <sub>d</sub>       |                                                                                                                                             | 9,10,1             | 1 01             | 0.50<br> t <sub>c(C)</sub> -20 |                               | ns           |

| Se <u>tup</u> time, data prior to REN <sup>†</sup>                    | t <sub>su(D)F</sub>  | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,1             | 11 01            | <br>  52<br>                   |                               | ns           |

| Hold time, data after RENT                                            | t <sub>h(D)R</sub>   |                                                                                                                                             | 9,10,              | 11   01          | 0                              |                               | ns           |

| Access time for read cycle<br>data valid after valid<br>address       | t <sub>a(A)</sub>    | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                   | 9,10,              | 11 01            |                                | t <sub>c(C)</sub> -90         | ns           |

| Access <u>time</u> for read cycle<br>from REN↓                        | toe(REN              | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                     | 9,10,              | 11 01            |                                | 0.75<br>t <sub>c(C)</sub> -60 | <br>  ns<br> |

| See footnotes at end of ta                                            | ible.                |                                                                                                                                             |                    |                  |                                |                               |              |

|                                                                       | OARDIZED<br>RY DRAWI |                                                                                                                                             | SIZE               |                  |                                | 5962                          | 2-9300       |

| MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                      |                                                                                                                                             |                    | REVISIO          | N LEVEL                        | SHEET                         | г<br>8       |

| Test                                                                               | Symbol   Condition   -55°C ≤ T <sub>C</sub> ≤ · |                                                                                    | s <u>1</u> / Group<br>125°C subgrou | i i     | Limits              |                               | Unit     |

|------------------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------|---------|---------------------|-------------------------------|----------|

|                                                                                    |                                                 | $-55^{\circ}C \le T_{C} \le +$<br>$4.5 \ V \le V_{CC} \le +$<br>unless otherwise s | 5.5 V  <br>pecified                 |         | <br>  Min           | Max                           |          |

| Disable time, data <u>-in</u> high impedance after REN <u>3</u> /                  | tdis(D)R                                        | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    |                     | 0.25<br>t <sub>c(C)</sub>     | ns       |

|                                                                                    |                                                 | RESET (                                                                            | RS) timing                          |         |                     |                               |          |

| De <u>Lay</u> from RS $\downarrow$ to REN $\uparrow$ and WE $\uparrow$             | t <sub>d</sub>                                  | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    |                     | 0.75<br>t <sub>c(C)</sub> +20 | ns       |

| Delay from RS↓ to REN and WE into high impedance 3/                                | tdis<br>(RS-RW)                                 | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    |                     | 2t <sub>c(C)</sub>            | ns       |

| Disable <u>ti</u> me, data bus<br>after RS↓ <u>3</u> /                             | tdis<br>(RS-DB)                                 | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    |                     | 1.25<br>t <sub>c(C)</sub>     | ns       |

| Disable <u>ti</u> me, address bus<br>after RS↓ <u>3</u> /                          | t <sub>dis</sub>                                | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    |                     | t <sub>c(C)</sub>             | ns       |

| Enable t <u>im</u> e, address bus<br>after RS↑ <u>3</u> /                          | t <sub>en</sub><br>(RS-AB)                      | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    |                     | t <sub>c(C)</sub>             | ns       |

| Setup time, RS before<br>CLKOUT↓ <u>6</u> /                                        | t <sub>su(RS)</sub>                             | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,1                              | 1 01    | 60                  |                               | ns       |

| Pulse duration, RS                                                                 | t <sub>w</sub> (RS)                             | V <sub>CC</sub> = 4.5 V<br>See figure 3                                            | 9,10,                               | 11 01   | 5t <sub>c</sub> (C) |                               | ns       |

|                                                                                    | Mi                                              | crocomputer/micropr                                                                | rocessor mode (NMI/M                | ic/MP)  | I <u></u>           |                               |          |

| Hold time (to put device<br>in mic <u>ro</u> processor mode)<br>after RS high      | t <sub>h</sub>                                  | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                          | 9,10,                               | 11   01 | t <sub>c(C)</sub>   |                               | ns       |

|                                                                                    | J                                               | interrupt (INT)/nonm                                                               | maskable interrupt (                | NMI)    |                     |                               |          |

| Fall time, INT 3/                                                                  | tf(INT)                                         | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                          | 9,10,                               | 11   01 |                     | 15                            | ns       |

| Fall time, NMI 3/                                                                  | t <sub>f(NMI)</sub>                             | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                          | 9,10,                               | 11 01   |                     | 15                            | ns       |

| See footnotes at end of tab                                                        | le.                                             |                                                                                    | <u> </u>                            |         | 1                   |                               | <u>.</u> |

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                                                 |                                                                                    | SIZE                                |         |                     | 590                           | 52-9300  |

|                                                                                    |                                                 |                                                                                    | REVISION                            | I LEVEL | SHE                 | ET                            |          |

| Test                                                                        | Symbol               | Conditions $1/$ $-55^{\circ}C \leq T_{\wedge} \leq +125^{\circ}C$                                                                                        | Group A<br>  subgroups | <br> Device<br>  type | Lim               | its                            | Unit    |  |

|-----------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------------|--------------------------------|---------|--|

| İ                                                                           |                      | $-55^{\circ}\text{C} \le T_{\text{C}} \le +125^{\circ}\text{C}$<br>$4.5 \text{ V} \le \text{V}_{\text{CC}} \le 5.5 \text{ V}$<br>unless otherwise specif | ied                    |                       | Min               | Max                            |         |  |

| ulse duration, INT                                                          | t <sub>w(INT)</sub>  | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                                  | 9,10,11                | 01                    | t <sub>c(C)</sub> |                                | ns      |  |

| ulse duration, NMI                                                          | t <sub>w</sub> (NMI) | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                                  | 9,10,11                | 01                    | t <sub>c(C)</sub> |                                | ns      |  |

| retup time, INT before CLKOUT low 7/                                        | t <sub>su(INT)</sub> | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                                  | 9,10,11                | 01                    | 60                |                                | ns      |  |

| Setup time, NMI before  CLKOUT low 7/                                       | t <sub>su(NMI)</sub> | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                                  | 9,10,11                | 01                    | 60                |                                | ns      |  |

|                                                                             |                      | Bit I/O ti                                                                                                                                               | ming                   |                       |                   |                                |         |  |

| Rise and fall time outputs <u>3</u> /                                       | trfo (IOP)           | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                                  | 9,10,11                | 01                    |                   | 20                             | ns      |  |

| CLKOUT low to data valid outputs                                            | td(IOP)              | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                                                                                  | 9,10,11                | 01                    |                   | 0.75<br> t <sub>c(C)</sub> +80 | ns      |  |

| Rise and fall time inputs 3/                                                | t <sub>t</sub> (IOP) | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                                | 9,10,11                | 01                    |                   | 20                             | ns      |  |

| Setup time, data before<br>CLKOUT time                                      | t <sub>su(IOP)</sub> | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                                | 9,10,11                | 01                    | 40                |                                | ns      |  |

| Input pulse duration                                                        | t <sub>w</sub> (IOP) | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                                | 9,10,1                 | 01                    | t <sub>c(C)</sub> |                                | ns      |  |

|                                                                             |                      | General purpo                                                                                                                                            | se timers              |                       |                   |                                |         |  |

| Rise time, TCLK1, TCLK2 3/                                                  | t <sub>r(TIM)</sub>  | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                                | 9,10,1                 | 1 01                  |                   | 20                             | ns      |  |

| Fall time, TCLK1, TCLK2 3/                                                  | tf(TIM)              | V <sub>CC</sub> = 4.5 V<br>  See figure 3                                                                                                                | 9,10,1                 | 1 01                  |                   | 20                             | ns      |  |

| See footnotes at end of tab                                                 | le.                  | 1                                                                                                                                                        |                        | . 1                   |                   |                                |         |  |

|                                                                             | ARDIZED              | NG                                                                                                                                                       | SIZE                   |                       |                   | 59                             | 62-9300 |  |

| MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                      | PLY CENTER —                                                                                                                                             |                        | REVISIO               | ו וויידו          | SHE                            | ET      |  |

|                                              |                           |                                                                                        | 1                    | 1              | Ī                             | 1   |      |

|----------------------------------------------|---------------------------|----------------------------------------------------------------------------------------|----------------------|----------------|-------------------------------|-----|------|

| Test                                         | Symbol                    | Conditions $1/$ -55°C $\leq T_C \leq +125$ °C                                          | Group A<br>subgroups | Device<br>type | Limits                        |     | Unit |

|                                              |                           | $-55$ °C ≤ $T_C$ ≤ $+125$ °C<br>4.5 V ≤ $V_{CC}$ ≤ 5.5 V<br>unless otherwise specified |                      |                | Min                           | Max |      |

| Pulse duration, TCLK1, TCLK2                 | t <sub>wl(TIM)</sub>      | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | t <sub>c(C)</sub> +20         |     | ns   |

| Pulse duration, TCLK1, TCLK2                 | t <sub>wh(TIM)</sub>      | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | t <sub>c(C)</sub> +20         |     | ns   |

| Input pulse duration                         | t <sub>clk</sub><br>(TIM) | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | 2tc{ç}                        |     | ns   |

|                                              |                           | Watchdog timer timi                                                                    | ngs                  |                |                               |     |      |

| Fall time, WDT <u>3</u> /                    | t <sub>f(WDT)</sub>       | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             |                               | 20  | ns   |

| Delay time, CLKOUT to WDT valid              | <sup>t</sup> d(WDT)       | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | 0.25<br>t <sub>c(C)</sub> +30 |     | ns   |

| Pulse duration, WDT output                   | tw(WDT)                   | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | 7t <sub>c(C)</sub>            |     | ns   |

|                                              |                           | Event manager time                                                                     | er                   |                |                               |     |      |

| Fall time, CMPO-CMP5 <u>3</u> /              | t <sub>f(CMP)</sub>       | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             |                               | 20  | ns   |

| Rise time, CMPO-CMP5 <u>3</u> /              | t <sub>r(CMP)</sub>       | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             |                               | 20  | ns   |

| Pulse duration, CMPO-CMP3                    | tw(CAP)                   | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | t <sub>c(C)</sub> +20         |     | ns   |

| Setup time, capture input before CLKOUT high | t <sub>su(CAP)</sub>      | V <sub>CC</sub> = 4.5 V<br>See figure 3                                                | 9,10,11              | 01             | 20                            |     | ns   |

- $\underline{1}$ / All testing to be performed using worst-case test conditions unless otherwise specified.

- 2/ This voltage specification is included for interface to HCMOS logic. However, note that all of the other timing parameters defined in this drawing are specified for TTL logic levels and will differ for HCMOS logic levels.

- $\underline{\mathbf{3}}/$  Value is derived from characterization data and is guaranteed but not tested.

- $\underline{4}$ /  $I_{CC}$  characteristics are inversely proportional to temperature. Test is performed with outputs open.

- $\frac{5}{c}$  t<sub>c(C)</sub> is the cycle time of CLKOUT, i.e.,  $4t_{c(MC)}$  (4 times CLKIN cycle time if an external oscillator is used).

- $\underline{6}$ /  $\overline{\text{RS}}$  can occur anytime during the clock cycle. Time given is minimum to assure synchronous operation.

- 7/ INT and NMI are synchronous inputs and can occur at any time during the cycle. NMI and INT are edge triggered only.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-93006  |

|---------------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                             |           | REVISION LEVEL | SHEET<br>11 |

Case X

| Name       | Pin        | Name            | Pin | Name            | Pin |

|------------|------------|-----------------|-----|-----------------|-----|

| A11        | A4         | A10             | 84  | A9              | A2  |

| <b>A8</b>  | <b>C1</b>  | A7              | C2  | A6              | D1  |

| <b>A</b> 5 | G1         | Α4              | G2  | А3              | J2  |

| A2/PA2     | K1         | A1/PA1          | L2  | AO/PAO          | K2  |

| D15        | L6         | D14             | К6  | D13             | L8  |

| D12        | K8         | D11             | L10 | D10             | J11 |

| D9         | н10        | D8              | G11 | D7              | D10 |

| D6         | C11        | D5              | c10 | D4              | B11 |

| D3         | A10        | D2              | B10 | D1              | A9  |

| DO         | В9         | INT*            | F1  | NMI*/MC/MP*     | Н1  |

| WE*        | D2         | REN*            | £1  | RS*             | E2  |

| CLKOUT     | F2         | V <sub>CC</sub> | L5  | v <sub>cc</sub> | 85  |

| Vec        | K5         | Vss             | A5  | CLKIN           | J1  |

| RXD        | H11        | TXD             | J10 | TCLK1           | B1  |

| TCLK2      | <b>B</b> 2 | WDT*            | H2  | IOP15           | L3  |

| IOP14      | K3         | IOP13           | L4  | IOP12           | K4  |

| IOP11      | L7         | IOP10           | K7  | IOP9            | L9  |

| 10P8       | К9         | 10P7            | K11 | 10P6            | K10 |

| 10P5       | G10        | IOP4            | F11 | 10P3            | F10 |

| 10P2       | E11        | IOP1            | E10 | 1000            | D11 |

| CMP0       | в3         | CMP1            | A3  | CMP2            | В6  |

| CMP3       | <b>A</b> 6 | CAP0            | В7  | CAP1            | A7  |

| CMP4/CAP2  | 88         | CMP5/CAP3       | A8  |                 |     |

<sup>\*</sup> Indicates active low signals

FIGURE 1. <u>Terminal connections</u>.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-93006  |

|---------------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                             |           | REVISION LEVEL | SHEET<br>12 |

Case Y

| Name            | Pin | Name            | Pin | Name            | Pin |

|-----------------|-----|-----------------|-----|-----------------|-----|

| A11             | 5   | A10             | 6   | A9              | 9   |

| A8              | 12  | A7              | 13  | A6              | 14  |

| A5              | 20  | A4              | 21  | A3              | 25  |

| A2/PA2          | 26  | A1/PA1          | 27  | AO/PAO          | 28  |

| D15             | 35  | D14             | 36  | D13             | 39  |

| D12             | 40  | D11             | 43  | D10             | 46  |

| D9              | 49  | D8              | 50  | D7              | 57  |

| D6              | 58  | D5              | 59  | D4              | 60  |

| D3              | 61  | D2              | 62  | D1              | 63  |

| DO DO           | 64  | INT*            | 18  | NMI*/MC/MP*     | 22  |

| WE*             | 15  | REN*            | 16  | RS*             | 17  |

| CLKOUT          | 19  | V <sub>CC</sub> | 04  | V <sub>CC</sub> | 33  |

| V <sub>SS</sub> | 03  | V <sub>SS</sub> | 34  | CLKIN           | 24  |

| RXD             | 48  | TXD             | 47  | TCLK1           | 10  |

| TCLK2           | 11  | WDT*            | 23  | IOP15           | 29  |

| IOP14           | 30  | IOP13           | 31  | 10P12           | 32  |

| IOP11           | 37  | IOP10           | 38  | IOP9            | 41  |

| 10P8            | 42  | IOP7            | 44  | 10P6            | 45  |

| IOP5            | 51  | IOP4            | 52  | IOP3            | 53  |

| IOP2            | 54  | IOP1            | 55  | IOP0            | 56  |

| CMP0            | 08  | CMP1            | 07  | CMP2            | 02  |

| CMP3            | 01  | CAPO            | 68  | CAP1            | 67  |

| CMP4/CAP2       | 66  | CMP5/CAP3       | 65  |                 |     |

<sup>\*</sup> Indicates active low signals

FIGURE 1. <u>Terminal connections</u> - Continued.

| STANDARDIZED<br>MILITARY DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-93006  |

|---------------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                             |           | REVISION LEVEL | SHEET<br>13 |

Reset timing

NOTES:

- RS forces REN and HE high and then places data bus DO-D15, REN, HE, and address bus AO-A11 in a high-impedance state. AB ouutputs and program counter are synchronously cleared to zero after the next complete clk cycle from RS 1.

- RS must be maintained for a minimum of five clock cycles. Resumption of normal program will commence after one complete CLK cycle from RS1.

- 2. Due to the synchronization action on RS, time to execute the function can vary dependent upon when RS or RS occur in the CLK cycle.

5. Diagram shown is for definition purpose only. WE and REN are mutually exclusive.

# Microcomputer/microprocessor mode timing

FIGURE 3. Waveforms - Continued.

| STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | SIZE<br>A |                | 5962-93006  |

|------------------------------------------------------------------------------------|-----------|----------------|-------------|

|                                                                                    |           | REVISION LEVEL | SHEET<br>18 |

- 4.2 <u>Screening</u>. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. For device classes B and S, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to qualification and quality conformance inspection. For device classes Q and V, screening shall be in accordance with MIL-I-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection.

- 4.2.1 Additional criteria for device classes M, B, and S.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A or D. For device class M, the test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. For device classes B and S, the test circuit shall be submitted to the qualifying activity. For device classes M, B, and S, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- (2)  $T_{\Delta} = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except that interim electrical tests prior to burn in are optional at the discretion of the manufacturer for device class M.

- c. A data retention stress test shall be included as part of the screening procedure and shall consist of the following steps:

- (1) Erase, (see 3.12.1).

- (2) Program all O's, (see 3.12.2).

- (3) Test at +25°C. Measure  $V_{CC}$  max and store this value in the signature row.

- (4) Unbiased bake for 72 hours at  $+165^{\circ}\text{C} \pm 5^{\circ}\text{C}$ .

- (5) Margin test at  $+25^{\circ}$ C. Measure V<sub>CC</sub> max and compare with the value stored in the signature row. Any part with a delta greater than 0.66 V or with V<sub>CC</sub> max less than 6.0 V consitiutes a failure. Also program and verify the r bit.

- (6) Erase, (see 3.12.1).

- (7) Program with random code. Verify this at max  $V_{CC}$ , (see 3.12.2).

- (8) Burn-in (see 4.2.1a).

- (9) Refresh EPROM data. Verify EPROM array at max  $V_{CC}$  and +25°C, (see 3.12.3).

- (10) Test at +125°C and max  $V_{CC}$ . Refresh EPROM data. Verify EPROM array, (see 3.12.3).

- (11) Test at -55°C and max  $V_{CC}$ . Refresh EPROM data. Verify EPROM array, (see 3.12.3).

- (12) Erase, (see 3.12.1).

- (13) Verify erasure at  $+25^{\circ}$ C, (see 3.12.3).

# 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-I-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-I-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- c. Additional screening for device class V beyond the requirements of device class Q shall be as specified in appendix B of MiL-I-38535.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br>A |                | 5962-93006  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>21 |

#### 4.3 Qualification inspection.

- 4.3.1 <u>Qualification inspection for device classes B and S</u>. Qualification inspection for device classes B and S shall be in accordance with MIL-M-38510. Inspections to be performed shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.3.2 Qualification inspection for device classes Q and V. Qualification inspection for device classes Q and V shall be in accordance with MIL-I-38535. Inspections to be performed shall be those specified in MIL-I-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5).

- 4.4 <u>Conformance inspection</u>. Quality conformance inspection for device class M shall be in accordance with MIL-STD-883 (see 3.1 herein) and as specified herein. Quality conformance inspection for device classes B and S shall be in accordance with MIL-M-38510 and as specified herein. Inspections to be performed for device classes M, B, and S shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.5). Technology conformance inspection for classes Q and V shall be in accordance with MIL-I-38535 including groups A, B, C, D, and E inspections and as specified herein except where option 2 of MIL-I-38535 permits alternate in-line control testing.

### 4.4.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the instruction set. For device classes B and S, subgroups 7 and 8 tests shall be sufficient to verify the truth table as approved by the qualifying activity. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device; these tests shall have been fault graded in accordance with MIL-STD-883, test method 5012 (see 1.5 herein).

- c. Subgroup 4 (C<sub>IN</sub>, C<sub>OUT</sub>, C<sub>I/O</sub> measurement) shall be measured only for the inital test and after process or design changes which may affect capacitance. Capacitance shall be measured between the designated terminal and GND at a frequency of 1 MHz. Sample size is five devices with no failures. All input and output terminals shall be tested.

- 4.4.2 <u>Group B inspection.</u> The group B inspection end-point electrical parameters shall be as specified in table II herein. For device class S steady-state life tests, the test circuit shall be submitted to the qualifying activity.

- 4.4.3 <u>Group C inspection</u>. The group C inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.3.1 <u>Additional criteria for device classes M and B</u>. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition A or D. For device class M, the test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. For device class B, the test circuit shall be submitted to the qualifying activity. For device classes M and B, the test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- d. Devices selected for testing shall be programmed with a random 50% pattern. After completion of all testing, the devices shall be erased and verified.