# Low Noise, Matched Dual Monolithic Transistor

**MAT12**

### **Preliminary Technical Data**

Very Low Voltage Noise: 1nV/√Hz max @ 100Hz

Low offset voltage ( $V_{OS}$ ): 50  $\mu$ V max

Excellent Log Conformance:  $r_{BE} = 0.3 \Omega$ Low Offset Voltage Drift: 0.1  $\mu$ V/°C max High Gain Bandwidth Product: 200MHz

**FEATURES**

High Gain (h<sub>FE</sub>):

500 min at  $I_C = 1mA$ 300 min at  $I_C = 1\mu A$

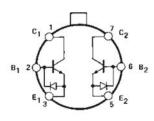

### **PIN CONFIGURATION**

Note: Substrate is connected to case on TO-78 package. Substrate is normally connected to the most negative circuit potential, but can be floated

### **GENERAL DESCRIPTION**

The design of the MAT12 series of NPN dual monolithic transistors is optimized for very low noise, low drift and low  $r_{BE}$ . Exceptional characteristics of the MAT12 include offset voltage of 50  $\mu$ V max and high current gain (hFE) which is maintained over a wide range of collector current. Device performance is specified over the full temperature range as well as at 25°C.

Input protection diodes are provided across the emitter-base junctions to prevent degradation of the device characteristics due to reverse-biased emitter current. The substrate is clamped to the most negative emitter by the parasitic isolation junction created by the protection diodes. This results in complete isolation between the transistors.

The MAT12 is ideal for applications where low noise is a priority. The MAT12 can be used as an input stage to make an amplifier with noise voltage of less than 1.0 nV/ $\sqrt{Hz}$  at 100 Hz. Other applications, such as log/antilog circuits, may use the excellent logging conformity of the MAT12. Typical bulk resistance is only 0.3  $\Omega$  to 0.4  $\Omega$ . The MAT12 electrical characteristics approach those of an ideal transistor when operated over a collector current range of 1µA to 10 mA.

Rev. PrA

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# **SPECIFICATIONS**

### ELECTRICAL CHARACTERISTICS; $V_{CB} = 15V$

$V_{CB}$  = 15 V,  $I_O$  = 10µA,  $T_A$  = 25°C, unless otherwise specified.

### Table 1.

| Parameter                              | Symbol                          | Conditions                                           | Min        | Тур  | Мах | Unit   |

|----------------------------------------|---------------------------------|------------------------------------------------------|------------|------|-----|--------|

| Current Cain                           | <b>L</b>                        | 1 1 m ( ( n e t e 1 )                                | 500        | 605  |     |        |

| Current Gain                           | h <sub>FE</sub>                 | $I_c = 1 \text{mA} \text{ (note 1)}$                 | 500        | 605  |     |        |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C                          | 325        | 500  |     |        |

|                                        |                                 | $I_{c} = 100 \mu A$                                  | 500        | 590  |     |        |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C<br>I <sub>C</sub> = 10μA | 275<br>400 | 550  |     |        |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C                          | 225        | 330  |     |        |

|                                        |                                 | $I_c = 1\mu A$                                       | 300        | 485  |     |        |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C                          | 200        | -65  |     |        |

| Current Gain Match                     | $\Delta h_{\text{FE}}$          | $10\mu A \le I_C \le 1mA$ (note 2)                   |            | 0.5  | 2   | %      |

| Noise Voltage Density                  | еN                              | $I_{c} = 1 \text{ mA}, V_{CB} = 0 \text{ (note 3)}$  |            |      |     |        |

|                                        |                                 | f <sub>0</sub> = 10Hz                                |            | 1.6  | 2   | nV/√Hz |

|                                        |                                 | f <sub>0</sub> = 100Hz                               |            | 0.9  | 1   | nV/√Hz |

|                                        |                                 | f <sub>o</sub> = 1kHz                                |            | 0.85 | 1   | nV/√Hz |

|                                        |                                 | f <sub>o</sub> = 10kHz                               |            | 0.85 | 1   | nV/√Hz |

| Offset Voltage                         | Vos                             | $V_{CB} = 0, 1\mu A \le I_C \le 1mA$                 |            | 10   | 50  | μV     |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C                          |            |      | 70  | uV     |

| Offset Voltage Change vs. $V_{CB}$     | $\Delta V_{OS} / \Delta V_{CB}$ | $0 \le V_{CB} \le V_{MAX}$ (note 4)                  |            | 10   | 25  | μV     |

|                                        |                                 | $1\mu A \le I_C \le 1mA$ (note 5)                    |            |      |     |        |

| Offset Voltage Change vs. $I_C$        | ΔVos/ΔIc                        | $1\mu A \le I_C \le 1mA$ (note 5), $V_{CB}=0$        |            | 5    | 25  | μV     |

| Offset Voltage Drift                   | $\Delta V_{os}/\Delta T$        | -25°C≤T <sub>A</sub> ≤+85°C                          |            | 0.08 | 0.3 | μV/ ∘C |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C, V <sub>os</sub>         |            | 0.03 | 0.3 | μV/ °C |

|                                        |                                 | trimmed to zero                                      |            |      |     | P      |

| Breakdown Voltage                      | BV <sub>CEO</sub>               |                                                      | 40         |      |     | V      |

| Gain-Bandwidth Product                 | fī                              | $I_{C} = 100 \text{mA}, V_{CE} = 10 \text{V}$        |            | 200  |     | MHz    |

| Collector-Base Leakage Current         | Ісво                            | V <sub>CB</sub> =V <sub>MAX</sub>                    |            | 25   | 200 | pА     |

|                                        |                                 | -25°C≤T₄≤+85°C                                       |            | 2    |     | nA     |

| Collector-Collector Leakage Current    | lcc                             | V <sub>CC</sub> =V <sub>MAX</sub> (notes 6,7)        |            | 35   | 200 | рА     |

| ······································ |                                 | -25°C≤T <sub>A</sub> ≤+85°C                          |            | 3    |     | nA     |

| Collector-Emitter Leakage Current      | Ices                            | V <sub>BE</sub> =0 (notes 6,7)                       |            | 35   | 200 | pА     |

|                                        |                                 | -25°C≤T <sub>A</sub> ≤+85°C                          |            | 3    |     | nA     |

# **Preliminary Technical Data**

# **MAT12**

| Input Bias Current                        | IB                   | $I_{C} = 10 \mu A$                              |     | 25    | nA    |

|-------------------------------------------|----------------------|-------------------------------------------------|-----|-------|-------|

|                                           |                      | -25°C≤T <sub>A</sub> ≤+85°C                     |     | 45    | nA    |

| Input Offset Current                      | los                  | lc = 10μΑ                                       |     | 0.6   | nA    |

| input onset current                       | IOS                  | -25°C≤T₄≤+85°C                                  |     | 8     | nA    |

|                                           |                      |                                                 |     |       |       |

| Input Offset Current Drift                | Δlos/ΔT              | Ic=10μA (note 6)                                |     |       |       |

|                                           |                      | -25°C≤T <sub>A</sub> ≤+85°C                     | 40  | 90    | pA/ºC |

|                                           |                      |                                                 |     |       |       |

| Offset Current Change vs. V <sub>CB</sub> | ΔΙος/Δνα             | $0 \leq V_{CR} \leq V_{MAX}$ (note 4)           | 30  | 70    | pA/V  |

|                                           | 2103/2108            |                                                 |     | 70    | p     |

|                                           |                      |                                                 |     |       |       |

| Collector Saturation Voltage              | V <sub>CE(SAT)</sub> | $I_{C} = 1 \text{mA}, I_{B} = 100 \mu \text{A}$ | 0.0 | 5 0.1 | V     |

| Output Capacitance                        | Сов                  | V <sub>CB</sub> =15V, I <sub>E</sub> =0         | 23  |       | pF    |

| Bulk Resistance                           | r <sub>BE</sub>      | 10µA≤Ic≤10mA (note6)                            | 0.3 | 0.5   | Ω     |

| Collector-Collector Capacitance           | Ccc                  | $V_{CC} = 0$                                    | 35  |       | pF    |

|                                           |                      |                                                 |     |       |       |

Notes:

- 1. Current gain is guaranteed with Collector-Base Voltage ( $V_{CB}$ ) swept from 0 to  $V_{MAX}$  at the indicated collector currents.

- 2. Current Gain Match ( $\Delta h_{FE}$ ) defined as:  $\Delta h_{FE} = (100(\Delta I_B)(h_{FE min})/I_C)$

- 3. Noise Voltage Density is guaranteed, but not 100% tested

- 4. This is the maximum change in  $V_{OS}$  as  $V_{CB}$  is swept from 0V to 40V.

- 5. Measured at  $l_{c}{=}10\mu A$  and guaranteed by design over the specified range of  $l_{c}$

- 6. Guaranteed by Design

- 7.  $I_{CC}$  and  $I_{CES}$  are verified by measurement of  $I_{CBO}$

## **ABSOLUTE MAXIMUM RATINGS**

### Table 2.

| 1.010 2.                                       |                 |

|------------------------------------------------|-----------------|

| Parameter                                      | Rating          |

| Collector-Base Voltage (BV <sub>CBO</sub> )    | 40 V            |

| Collector-Emitter Voltage (BV <sub>CEO</sub> ) | 40V             |

| Collector-Collector Voltage (BVcc)             | 40V             |

| Emitter-Emitter Voltage (BV <sub>EE</sub> )    | 40V             |

| Collector Current (Ic)                         | 20 mA           |

| Emitter Current (I <sub>E</sub> )              | 20 mA           |

|                                                |                 |

| Storage Temperature Range H Packages           | –65°C to +150°C |

| Operating Temperature Range                    | –25°C to +85°C  |

| Junction Temperature Range RM, CP Packages     | –65°C to +150°C |

| Lead Temperature (Soldering, 60 sec)           | 300°C           |

|                                                |                 |

<sup>1</sup> Differential input voltage is limited to 5 V or the supply voltage, whichever is less.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type | θ <sub>JA</sub> | ον  | Unit |

|--------------|-----------------|-----|------|

| TO-78 (H)    | TBD             | TBD | °C/W |

|              |                 |     |      |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

©2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. PR09044-0-4/10(PrA)

Rev. PrA | Page 4 of 4