# Am186™ES and Am188™ES User's Manual

© 1997 Advanced Micro Devices, Inc. All rights reserved.

Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.

This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products except as provided in AMD's Terms and Conditions of Sale for such products.

#### **Trademarks**

AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.

Am386 and Am486 are registered trademarks, and Am186, Am188, E86, AMD Facts-On-Demand, and K86 are trademarks of Advanced Micro Devices, Inc.

FusionE86 is a service mark of Advanced Micro Devices, Inc.

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

#### **Customer Service**

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the worldwide staff of AMD field application engineers and factory support staff to answer E86<sup>TM</sup> family hardware and software development questions.

#### Hotline and World Wide Web Support

For answers to technical questions, AMD provides a toll-free number for direct access to our corporate applications hotline. Also available is the AMD World Wide Web home page and FTP site, which provides the latest E86 family product information, including technical information and data on upcoming product releases.

For technical support questions on all E86 products, send E-mail to lpd.support@amd.com.

Corporate Applications Hotline

(800) 222-9323 toll-free for U.S.

44-(0) 1276-803-299 U.K. and Europe hotline

World Wide Web Home Page and FTP Site

To access the AMD home page go to http://www.amd.com.

To download documents and software, ftp to ftp.amd.com and log on as anonymous using your E-mail address as a password. Or via your web browser, go to ftp://ftp.amd.com.

Questions, requests, and input concerning AMD's WWW pages can be sent via E-mail to webmaster@amd.com.

#### **Documentation and Literature**

Free E86 family information such as data books, user's manuals, data sheets, application notes, the FusionE86<sup>SM</sup> Partner Solutions Catalog, and other literature is available with a simple phone call. Internationally, contact your local AMD sales office for complete E86 family literature.

#### Literature Ordering

(800) 222-9323 toll-free for U.S. and Canada

(512) 602-5651 direct dial worldwide

(512) 602-7639 fax

(800) 222-9323 AMD Facts-On-Demand<sup>™</sup> faxback service

toll-free for U.S. and Canada

## TABLE OF CONTENTS

| PURPOSE OF THIS MANUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER'S MANUAL OVERVIEW AMD DOCUMENTATION E86 Family  FEATURES AND PERFORMANCE  1.1 KEY FEATURES AND BENEFITS 1.2 DISTINCTIVE CHARACTERISTICS. 1.3 APPLICATION CONSIDERATIONS. 1.6 1.3.1 Clock Generation 1.3.2 Memory Interface  CHAPTER 2 PROGRAMMING  2.1 REGISTER SET 2.1.1 Processor Status Flags Register 2.2.2 MEMORY ORGANIZATION AND ADDRESS GENERATION 2.3 I/O SPACE 2.4 INSTRUCTION SET 2.5 SEGMENTS 2.6 DATA TYPES 2.7 ADDRESSING MODES 2.7 ADDRESSING MODES 2.7 ADDRESSING MODES 3.1 PIN DESCRIPTIONS 3.1 PIN DESCRIPTIONS 3.1 PIN DESCRIPTIONS 3.1 DISTINCTERIACE UNIT 3.2 BUS OPERATION 3.3 BUS INTERFACE UNIT 3.3.3 BUS INTERFACE UNIT 3.3.4 Pseudo Static RAM (PSRAM) Support 3.4 CLOCK AND POWER MANAGEMENT UNIT 3.25 3.4.1 Phase-Locked Loop (PLL) 3.4.2 Crystal-Driven Clock Source 3.4.3 External Source Clock 3.27 3.4.4 System Clocks 3.27 3.4.4 System Clocks 3.27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AMD DOCUMENTATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| E86 Family   Xiv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CHAPTER 1         FEATURES AND PERFORMANCE           1.1         KEY FEATURES AND BENEFITS         1-1           1.2         DISTINCTIVE CHARACTERISTICS         1-2           1.3         APPLICATION CONSIDERATIONS         1-6           1.3.1         Clock Generation         1-6           1.3.2         Memory Interface         1-6           CHAPTER 2         PROGRAMMING           2.1         REGISTER SET         2-1           2.1.1         Processor Status Flags Register         2-2           2.2         MEMORY ORGANIZATION AND ADDRESS GENERATION         2-3           2.3         I/O SPACE         2-4           2.4         INSTRUCTION SET         2-4           2.5         SEGMENTS         2-6           2.6         DATA TYPES         2-6           2.7         ADDRESSING MODES         2-10           CHAPTER 3           SYSTEM OVERVIEW           3.1         PIN DESCRIPTIONS         3-1           3.1         PIN DESCRIPTIONS         3-1           3.2         BUS OPERATION         3-2           3.3.1         Nonmultiplexed Address Bus         3-2           3.3.2         Static Bus Sizing         3-2<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.1       KEY FEATURES AND BENEFITS       1-1         1.2       DISTINCTIVE CHARACTERISTICS       1-2         1.3       APPLICATION CONSIDERATIONS       1-6         1.3.1       Clock Generation       1-6         1.3.2       Memory Interface       1-6         CHAPTER 2         PROGRAMMING         2.1       REGISTER SET       2-1         2.1.1       Processor Status Flags Register       2-2         2.2       MEMORY ORGANIZATION AND ADDRESS GENERATION       2-3         2.3       I/O SPACE       2-4         2.4       INSTRUCTION SET       2-4         2.5       SEGMENTS       2-6         2.6       DATA TYPES       2-6         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1.1       Pins That Are Used by Emulators       3-1         3.2       BUS OPERATION.       3-2         3.3.1       Nonmultiplexed Address Bus       3-2         3.3.2       Static Bus Sizing       3-2         3.3.3       Byte Write Enables       3-2         3.4.1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1.2       DISTINCTIVE CHARACTERISTICS       1-2         1.3       APPLICATION CONSIDERATIONS       1-6         1.3.1       Clock Generation       1-6         1.3.2       Memory Interface       1-6         CHAPTER 2       PROGRAMMING         2.1       REGISTER SET       2-1         2.1.1       Processor Status Flags Register       2-2         2.2       MEMORY ORGANIZATION AND ADDRESS GENERATION       2-3         2.3       I/O SPACE       2-4         2.4       INSTRUCTION SET       2-4         2.5       SEGMENTS       2-6         2.6       DATA TYPES       2-8         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1.1       Pins That Are Used by Emulators       3-15         3.2       BUS OPERATION       3-26         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-24         3.3.3       Byte Write Enables       3-24         3.4.1       Phase-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.3       APPLICATION CONSIDERATIONS       1-6         1.3.1       Clock Generation       1-6         1.3.2       Memory Interface       1-6         CHAPTER 2       PROGRAMMING         2.1       REGISTER SET       2-1         2.1.1       Processor Status Flags Register       2-2         2.2       MEMORY ORGANIZATION AND ADDRESS GENERATION       2-3         2.3       I/O SPACE       2-4         2.4       INSTRUCTION SET       2-4         2.5       SEGMENTS       2-6         2.6       DATA TYPES       2-6         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1.1       Pins That Are Used by Emulators       3-19         3.2       BUS OPERATION.       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-26         3.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3.1   Clock Generation   1.6     1.3.2   Memory Interface   1.6     CHAPTER 2   PROGRAMMING     2.1   REGISTER SET   2-1     2.1.1   Processor Status Flags Register   2-2     2.2   MEMORY ORGANIZATION AND ADDRESS GENERATION   2-3     2.3   I/O SPACE   2-4     2.4   INSTRUCTION SET   2-4     2.5   SEGMENTS   2-6     2.6   DATA TYPES   2-6     2.7   ADDRESSING MODES   2-10     CHAPTER 3   SYSTEM OVERVIEW     3.1   PIN DESCRIPTIONS   3-1     3.1.1   Pins That Are Used by Emulators   3-19     3.2   BUS OPERATION   3-20     3.3   BUS INTERFACE UNIT   3-25     3.3.1   Nonmultiplexed Address Bus   3-25     3.3.2   Static Bus Sizing   3-25     3.3.3   Byte Write Enables   3-24     3.3.4   Pseudo Static RAM (PSRAM) Support   3-24     3.4.1   Phase-Locked Loop (PLL)   3-25     3.4.2   Crystal-Driven Clock Source   3-25     3.4.3   External Source Clock   3-27     3.4.4   System Clocks   3-27     3.4.5   System Clocks   3-27     3.4.4   System Clocks   3-27     3.4.4   System Clocks   3-27     3.4.5   System Clocks   3-27     3.4.4   System Clocks   3-27     3.4.5   Static Bus Sizing   3-26     3.4.6   Clock   3-27     3.4.7   System Clocks   3-27     3.4.8   System Clocks   3-27     3.4.9   System Clocks   3-27     3.4.10   System Clocks   3-27     3.4.10   System Clocks   3-27     3.4.2   Clock   3-27     3.4.4   System Clocks   3-27     3.4.5   System Clocks   3-27     3.4.6   System Clocks   3-27     3.4.7   System Clocks   3-27     3.4.8   System Clocks   3-27 |

| 1.3.2   Memory Interface   1.6C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CHAPTER 2         PROGRAMMING           2.1         REGISTER SET         2-1           2.1.1         Processor Status Flags Register         2-2           2.2         MEMORY ORGANIZATION AND ADDRESS GENERATION         2-3           2.3         I/O SPACE         2-4           2.4         INSTRUCTION SET         2-4           2.5         SEGMENTS         2-5           2.6         DATA TYPES         2-6           2.7         ADDRESSING MODES         2-10           CHAPTER 3           SYSTEM OVERVIEW           3.1         PIN DESCRIPTIONS         3-1           3.1.1         Pins That Are Used by Emulators         3-1           3.2         BUS OPERATION         3-2           3.3         BUS INTERFACE UNIT         3-2           3.3.1         Nonmultiplexed Address Bus         3-2           3.3.2         Static Bus Sizing         3-2           3.3.3         Byte Write Enables         3-2           3.4         Pseudo Static RAM (PSRAM) Support         3-2           3.4.1         Phase-Locked Loop (PLL)         3-2           3.4.2         Crystal-Driven Clock Source         3-2           3.4.4         S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

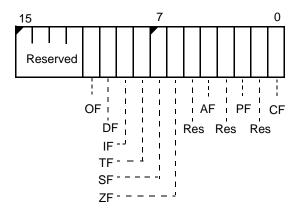

| 2.1       REGISTER SET       2-1         2.1.1       Processor Status Flags Register       2-2         2.2       MEMORY ORGANIZATION AND ADDRESS GENERATION       2-3         2.3       I/O SPACE       2-4         2.4       INSTRUCTION SET       2-4         2.5       SEGMENTS       2-8         2.6       DATA TYPES       2-8         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1.1       PINS That Are Used by Emulators       3-19         3.2       BUS OPERATION       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.4       Pseudo Static RAM (PSRAM) Support       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.1.1 Processor Status Flags Register       2-2         2.2 MEMORY ORGANIZATION AND ADDRESS GENERATION       2-3         2.3 I/O SPACE       2-4         2.4 INSTRUCTION SET       2-4         2.5 SEGMENTS       2-8         2.6 DATA TYPES       2-8         2.7 ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1 PIN DESCRIPTIONS       3-1         3.1.1 Pins That Are Used by Emulators       3-19         3.2 BUS OPERATION       3-20         3.3 BUS INTERFACE UNIT       3-23         3.3.1 Nonmultiplexed Address Bus       3-23         3.3.2 Static Bus Sizing       3-23         3.3.3 Byte Write Enables       3-24         3.4 Pseudo Static RAM (PSRAM) Support       3-24         3.4.1 Phase-Locked Loop (PLL)       3-25         3.4.2 Crystal-Driven Clock Source       3-25         3.4.3 External Source Clock       3-27         3.4.4 System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

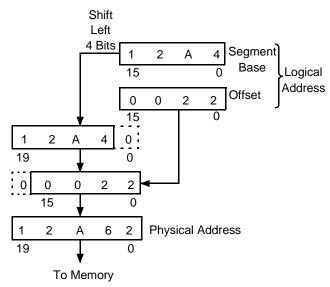

| 2.2       MEMORY ORGANIZATION AND ADDRESS GENERATION       2-3         2.3       I/O SPACE       2-4         2.4       INSTRUCTION SET       2-4         2.5       SEGMENTS       2-8         2.6       DATA TYPES       2-8         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1.1       Pins That Are Used by Emulators       3-19         3.2       BUS OPERATION       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

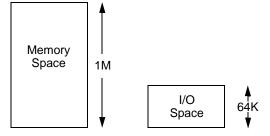

| 2.4       INSTRUCTION SET       2-4         2.5       SEGMENTS       2-8         2.6       DATA TYPES       2-8         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1.1       Pins That Are Used by Emulators       3-19         3.2       BUS OPERATION       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5       SEGMENTS       .2-8         2.6       DATA TYPES       .2-8         2.7       ADDRESSING MODES       .2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       .3-1         3.1.1       Pins That Are Used by Emulators       .3-19         3.2       BUS OPERATION       .3-20         3.3       BUS INTERFACE UNIT       .3-23         3.3.1       Nonmultiplexed Address Bus       .3-23         3.3.2       Static Bus Sizing       .3-23         3.3.3       Byte Write Enables       .3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       .3-24         3.4.1       Phase-Locked Loop (PLL)       .3-25         3.4.1       Phase-Locked Loop (PLL)       .3-25         3.4.2       Crystal-Driven Clock Source       .3-25         3.4.3       External Source Clock       .3-27         3.4.4       System Clocks       .3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

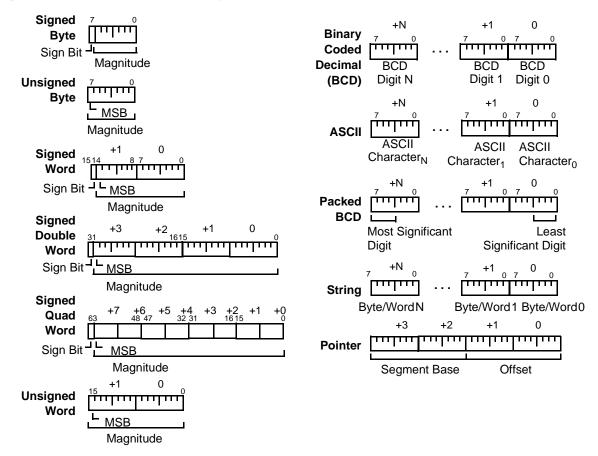

| 2.6       DATA TYPES       2-8         2.7       ADDRESSING MODES       2-10         CHAPTER 3         SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       3-1         3.1       Pins That Are Used by Emulators       3-19         3.2       BUS OPERATION       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-23         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.7 ADDRESSING MODES       2-10         CHAPTER 3       SYSTEM OVERVIEW         3.1 PIN DESCRIPTIONS       3.1 Static Pins That Are Used by Emulators       3.19         3.2 BUS OPERATION       3.20         3.3 BUS INTERFACE UNIT       3.23         3.3.2 Static Bus Sizing       3.23         3.3.3 Byte Write Enables       3.24         3.3.4 Pseudo Static RAM (PSRAM) Support       3.24         3.4.1 Phase-Locked Loop (PLL)       3.25         3.4.2 Crystal-Driven Clock Source       3.25         3.4.3 External Source Clock       3.27         3.4.4 System Clocks       3.27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CHAPTER 3       SYSTEM OVERVIEW         3.1       PIN DESCRIPTIONS       .3-1         3.1.1       Pins That Are Used by Emulators       .3-19         3.2       BUS OPERATION       .3-20         3.3       BUS INTERFACE UNIT       .3-23         3.3.1       Nonmultiplexed Address Bus       .3-23         3.3.2       Static Bus Sizing       .3-23         3.3.3       Byte Write Enables       .3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       .3-24         3.4.1       Phase-Locked Loop (PLL)       .3-25         3.4.1       Phase-Locked Loop (PLL)       .3-25         3.4.2       Crystal-Driven Clock Source       .3-25         3.4.3       External Source Clock       .3-27         3.4.4       System Clocks       .3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.1       PIN DESCRIPTIONS       3-19         3.1.1       Pins That Are Used by Emulators       3-19         3.2       BUS OPERATION.       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3.1.1 Pins That Are Used by Emulators       3-19         3.2 BUS OPERATION.       3-20         3.3 BUS INTERFACE UNIT       3-23         3.3.1 Nonmultiplexed Address Bus       3-23         3.3.2 Static Bus Sizing       3-23         3.3.3 Byte Write Enables       3-24         3.3.4 Pseudo Static RAM (PSRAM) Support       3-24         3.4 CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1 Phase-Locked Loop (PLL)       3-25         3.4.2 Crystal-Driven Clock Source       3-25         3.4.3 External Source Clock       3-27         3.4.4 System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3.2       BUS OPERATION.       3-20         3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3.3       BUS INTERFACE UNIT       3-23         3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3.1       Nonmultiplexed Address Bus       3-23         3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3.2       Static Bus Sizing       3-23         3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3.3.3       Byte Write Enables       3-24         3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3.4       Pseudo Static RAM (PSRAM) Support       3-24         3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

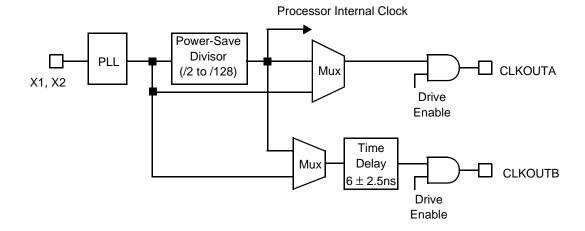

| 3.4       CLOCK AND POWER MANAGEMENT UNIT       3-25         3.4.1       Phase-Locked Loop (PLL)       3-25         3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.4.1 Phase-Locked Loop (PLL)       3-25         3.4.2 Crystal-Driven Clock Source       3-25         3.4.3 External Source Clock       3-27         3.4.4 System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.4.2       Crystal-Driven Clock Source       3-25         3.4.3       External Source Clock       3-27         3.4.4       System Clocks       3-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.3       External Source Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0 4 F Dannar Cana Carantian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.4.5 Power-Save Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CHAPTER 4 PERIPHERAL CONTROL BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.1 OVERVIEW4-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |