# CMOS PARALLEL IN-OUT FIFO MODULE 2K x 9-BIT & 4K x 9-BIT

#### FFATURES:

- First-In, First-Out memory module

- 2K x 9 organization (IDT7M203S)

- 4K x 9 organization (IDT7M204S)

- Low-power consumption

- Asynchronous and simultaneous read and write

- Fully expandable by both word depth and/or bit width

- Assembled with IDT's high-reliability vapor phase solder reflow process

- Single 5V (±10%) power supply

- Master/slave multiprocessing applications

- Bidirectional and rate buffer applications

- · Empty and full warning flags

- High-performance CEMOS™ technology

- Pin compatible with IDT7201 and Mostek MK4501, but with four times word depth (IDT7M203S) or eight times (IDT7M204S)

- Module available with semiconductor components 100% screened to MIL-STD-883, Class B

# PIN CONFIGURATION

#### **PIN NAMES**

| W =         | FL =           | XI =                     | EF =                 |

|-------------|----------------|--------------------------|----------------------|

| WRITE       | FIRST LOAD     | EXPANSION IN             | EMPTY FLAG           |

| R =<br>READ | D =<br>DATA IN | XO =<br>EXPANSION<br>OUT | V <sub>CC</sub> = 5V |

| RS =        | Q =            | FF =                     | GND =                |

| RESET       | DATA OUT       | FULL FLAG                | GROUND               |

#### DESCRIPTION:

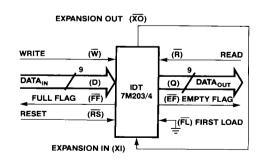

The IDT7M203/204 are FIFO memory modules that utilize a special First-In, First-Out algorithm that loads and empties data on a first-in, first-out basis. The device uses full and empty flags to prevent data overflow and underflow and expansion logic to allow for unlimited expansion capability in both word size and death.

The reads and writes are internally sequential through the use of ring pointers, with no address information required to load and unload data. Data is toggled in and out of the device through the use of the WRITE (W) and READ (R) pins. The device has a read/write cycle time of 65ns (15MHz) for commercial and 70ns (14MHz) for military temperature ranges.

The device utilizes a 9-bit wide data array to allow for control and parity bits at the user's option. This feature is especially useful in data communications applications where it is necessary to use a parity bit for transmission/reception error checking.

The IDT7M203/204 are constructed on a multi-layered ceramic substrate using four IDT7201 (512x9) or four IDT7202 (1Kx9) FIFOs in leadless chip carriers. Extremely high speeds are achieved in this fashion due to the use of IDT7201s and IDT7202s fabricated in IDT's high-performance CEMOS technology.

IDT's military FIFO modules have semiconductor components 100% processed to the test methods of MIL-STD-883, Class B, making them ideally suited to applications demanding the highest level of performance and reliability.

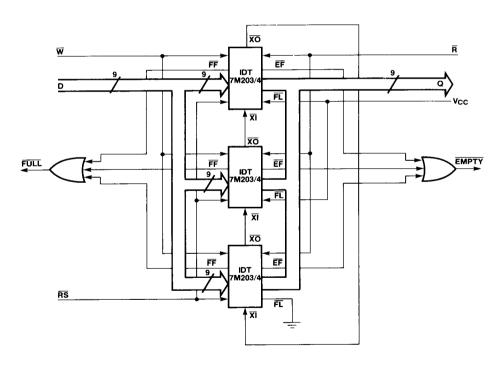

# **FUNCTIONAL BLOCK DIAGRAM**

CEMOS is a trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**JULY 1986**

# 1986 Integrated Device Technology. Inc

13-146

Printed in U.S.A

#### ABSOLUTE MAXIMUM RATING(1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY     | UNIT |

|-------------------|--------------------------------------------|--------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect<br>to GND | -0.5 to +7.0 | -0.5 to +7.0 | v    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to +125  | °C   |

| TBIAS             | Temperature<br>Under Bias                  | -10 to +85   | -65 to +135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to +150  | °C   |

| Pτ                | Power Dissipation                          | 4.0          | 4.0          | w    |

| I <sub>OUT</sub>  | DC Output Current                          | 50           | 50           | mA   |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only and

functional operation of the device at these or any other conditions above those

indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

reliability.

#### RECOMMENDED DC OPERATING CONDITIONS

| SYMBOL              | PARAMETER                                  | MIN. | TYP. | MAX. | UNIT |

|---------------------|--------------------------------------------|------|------|------|------|

| V <sub>CC</sub>     | Military Supply Voltage                    | 4.5  | 5.0  | 5.5  | ٧    |

| V <sub>CC</sub>     | Commercial Supply Voltage                  | 4.5  | 5.0  | 5.5  | V    |

| GND                 | Supply Voltage                             | 0    | 0    | 0    | V    |

| VIH                 | Input High Voltage<br>Commercial           | 2.0  | _    | _    | v    |

| V <sub>IH</sub>     | Input High Voltage<br>Military             | 2.2  | _    | _    | v    |

| V <sub>IL</sub> (1) | Input Low Voltage<br>Commercial & Military | -    | _    | 0.8  | ٧    |

#### NOTE:

1. 1.5V undershoots are allowed for 10ns once per cycle.

# DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%, T_A = -55^{\circ}C \text{ to } +125^{\circ}C \text{ and } 0^{\circ}C \text{ to } +70^{\circ}C)$

| SYMBOL           | PARAMETER                                                       | IDT7M203S<br>IDT7M204S<br>COMMERCIAL |     |      | IDT7M203S<br>IDT7M204S<br>MILITARY |      |      | UNIT | NOTES |

|------------------|-----------------------------------------------------------------|--------------------------------------|-----|------|------------------------------------|------|------|------|-------|

|                  |                                                                 | MIN.                                 | TYP | MAX. | MIN.                               | TYP. | MAX. | 1    |       |

| I <sub>IL</sub>  | Input Leakage Current (Any Input)                               | -5                                   | _   | 5    | -10                                | _    | 10   | μΑ   | 1     |

| IOL              | Output Leakage Current                                          | -10                                  | _   | 10   | -10                                |      | 10   | μА   | 2     |

| V <sub>OH</sub>  | Output Logic "1" Voltage I <sub>H</sub> = -2mA                  | 2.4                                  |     | _    | 2.4                                | _    | _    | V    | _     |

| V <sub>OL</sub>  | Output Logic "0" Voltage I L = 8mA                              | _                                    | _   | 0.4  | _                                  | _    | 0.4  | V    | _     |

| I <sub>CC1</sub> | Average V <sub>CC</sub> Power Supply Current                    | _                                    | 110 | 176  |                                    | 155  | 230  | mA   | 3     |

| I <sub>CC2</sub> | Average Standby Current<br>(R = W = RS = FL = V <sub>IH</sub> ) | _                                    | 20  | 33   | _                                  | 30   | 60   | mA   | 3     |

| I <sub>CC3</sub> | Power Down Current<br>(All Input = V <sub>CC</sub> -0.2V)       | _                                    | _   | 20   | _                                  | _    | 36   | mA   | 3     |

13

#### NOTES:

- 1. Measurements with  $0.4 \le V_{|N} \le V_{CC}$

- $2. \ \overline{R} \geq V_{IH}, \, 0.4 \leq V_{OUT} \leq V_{CC}.$

- I<sub>CC</sub> measurements are made with outputs open.

#### CAPACITANCE (TA = +25°C, f = 1.0MHz)

| SYMBOL          | PARAMETER(1)       | CONDITIONS            | TYP. | UNIT |

|-----------------|--------------------|-----------------------|------|------|

| C <sub>IN</sub> | Input Capacitance  | V <sub>IN</sub> = 0V  | 35   | pF   |

| Cour            | Output Capacitance | V <sub>OUT</sub> = 0V | 40   | pF   |

#### NOTE:

1. This parameter is sampled and not 100% tested.

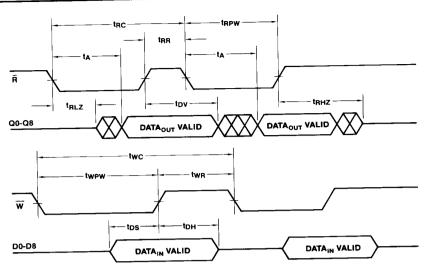

# AC CHARACTERISTICS(1)

$(V_{CC} = 5V \pm 10\%, T_A = -55^{\circ}C \text{ to } +125^{\circ}C \text{ and } 0^{\circ}C \text{ to } +70^{\circ}C)$

|                  |                                               | 7M203/4S40 |              | 7M20 | 3/4\$50 | 7M20 | 3/4S55 | 7M203/4S65 |      | 7M203/4S100 |      | 7M203/4S140    |      | UNIT |

|------------------|-----------------------------------------------|------------|--------------|------|---------|------|--------|------------|------|-------------|------|----------------|------|------|

| SYMBOL           | PARAMETER                                     | COM'L      | ONLY<br>MAX. | MIN. | MAX.    | MIN. | MAX.   | MIN.       | MAX. | MIN.        | MAX. | MIN.           | MAX. |      |

| t <sub>RC</sub>  | Read Cycle Time                               | 50         |              | 65   |         | 70   |        | 85         |      | 125         |      | 165            | 140  | ns   |

| t <sub>A</sub>   | Access Time                                   |            | 40           |      | 50      |      | 55     |            | 65   |             | 100  | -              |      | ns   |

| t <sub>RB</sub>  | Read Recovery Time                            | 10         |              | 15   |         | 15   |        | 20         |      | 25          |      | 25             |      | ns   |

| t <sub>RPW</sub> | Read Pulse Width(2)                           | 40         |              | 50   |         | 55   |        | 65         |      | 100         |      | 140            |      | 115  |

| t <sub>RLZ</sub> | Read Pulse Low to<br>Data Bus at Low Z(3)     | 5          | _            | 10   |         | 10   | _      | 10         |      | 10          |      | 10             |      | ns   |

| t <sub>WLZ</sub> | Write Pulse High to<br>Data Bus at Low Z(3.4) | 10         | _            | 15   | _       | 15   |        | 15         | _    | 20          |      | 20             |      | ns   |

| t <sub>DV</sub>  | Data Valid from<br>Read Pulse High            | 5          | _            | 5    |         | 5    |        | 5          |      | 5           |      | 5              |      | ns   |

| t <sub>RHZ</sub> | Read Pulse High to Data Bus at High Z (3)     | _          | 25           | -    | 30      | _    | 30     | _          | 35   |             | 40   | _              | 50   | ns   |

| t <sub>wc</sub>  | Write Cycle Time                              | 50         |              | 65   |         | 70   |        | 85         |      | 125         |      | 165            |      | ns   |

| t <sub>wpw</sub> | Write Pulse Width(2)                          | 40         |              | 50   |         | 55   |        | 65         |      | 100         |      | 140            |      | ns   |

| twa              | Write Recovery Time                           | 10         |              | 15   |         | 15   |        | 20         |      | 25          |      | 25             |      | ns   |

| t <sub>DS</sub>  | Data Setup Time                               | 20         |              | 25   |         | 30   |        | 40         |      | 50          |      | 50             |      | ns   |

| t <sub>DH</sub>  | Data Hold Time                                | 0          |              | 5    | _       | 10   |        | 10         |      | 10          |      | 10             |      | ns   |

| t <sub>RSC</sub> | Reset Cycle Time                              | 50         |              | 65   |         | 70   |        | 85         |      | 125         |      | 165            |      | ns   |

| t <sub>RS</sub>  | Reset Pulse Width(2)                          | 40         |              | 50   | _       | 55   |        | 65         |      | 100         |      | 140            |      | ns   |

| †RSR             | Reset Recovery Time                           | 10         |              | 15   | _       | 15   |        | 20         |      | 25          |      | 25             |      | ns   |

| t <sub>EFL</sub> | Reset to Empty Flag Low                       | T-         | 45           | T -  | 65      |      | 70     |            | 85   |             | 125  |                | 165  | ns   |

| t <sub>BEF</sub> | Read Low to Empty Flag Low                    | -          | 45           |      | 50      |      | 55     | <u> </u>   | 60   | <del></del> | 95   | <del>  -</del> | 135  | ns   |

| t <sub>REF</sub> | Read High to Full Flag High                   | _          | 45           | T -  | 50      | _    | 55     |            | 60   |             | 95   |                | 135  | ns   |

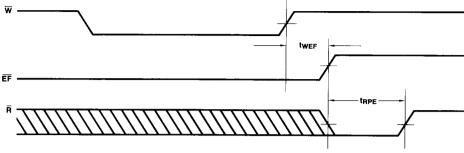

| t <sub>WEF</sub> | Write High to Empty Flag High                 | T -        | 45           | _    | 50      |      | 55     | <u> </u>   | 60   | <u> </u>    | 95_  |                | 135  | ns   |

| twee             | Write Low to Full Flag Low                    |            | 45           | _    | 50      | _    | 55     |            | 60   |             | 95   |                | 135  | ns   |

#### NOTES:

- Timings referenced as in AC Test Conditions.

- 2. Pulse widths less than minimum value are not allowed.

- 3. Values guaranteed by design, not currently tested.

- 4. Only applies to read data flow-through mode.

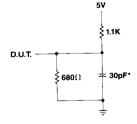

#### AC TEST CONDITIONS

| AC IEST CONDITIONS                                                                                 |                                                    |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Input Pulse Levels Input Rise and Fall Times Input Timing Reference Levels Output Reference Levels | GND to 3.0V<br>5ns<br>1.5V<br>1.5V<br>See Figure 1 |

| Output Load                                                                                        | See Figure 1                                       |

#### NOTE:

Generating  $\overline{R/W}$  Signals — When using these high-speed FIFO devices, it is necessary to have clean inputs on the  $\overline{R}$  and  $\overline{W}$  signals. It is important to not have glitches, spikes or ringing on the  $\overline{R}$ ,  $\overline{W}$  lines (violates the  $V_{lH}$ ,  $V_{lL}$  requirements); although the minimum pulse width low for the  $\overline{R}$  and  $\overline{W}$  are specified in tens of nanosecond, a glitch of 5ns can affect the read or write pointer and cause it to increment.

\*Includes jig and scope capacitances.

Figure 1. Output Load.

#### SIGNAL DESCRIPTIONS:

#### INPUTS: DATA IN (D0-D8)

Data inputs for 9-bit wide data.

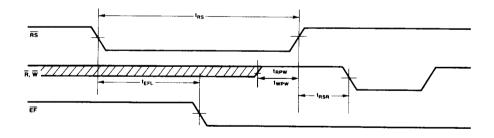

# CONTROLS: RESET (RS)

Reset is accomplished whenever the RESET  $(\overline{RS})$  input is taken to a low state. During reset, both internal read and write pointers are set to the first location. A reset is required after power up before a write operation can take place. Both the READ ENABLE  $(\overline{R})$  and WRITE ENABLE  $(\overline{W})$  inputs must be in the high state during the window shown in Figure 2: i.e.,  $t_{RPW}$  or  $t_{WPW}$  before the rising edge of  $\overline{RS}$ , and  $\overline{W}$  should not change until  $t_{RSR}$  after the rising edge of  $\overline{RS}$ .

#### WRITE ENABLE (W)

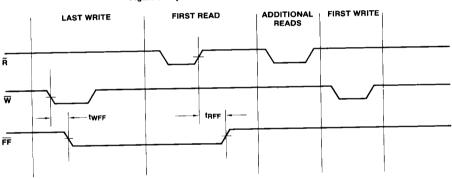

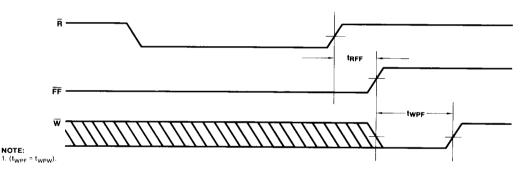

A write cycle is initiated on the falling edge of this input if the FULL FLAG (FF) is not set. Data setup and hold times must be adhered to with respect to the rising edge of the WRITE ENABLE (W). Data is stored in the RAM array sequentially and independently of any ongoing read operation.

To prevent data overflow, the FULL FLAG ( $\overline{FF}$ ) will go low, inhibiting further write operations. Upon the completion of a valid read operation, the FULL FLAG ( $\overline{FF}$ ) will go high after  $t_{RFF}$ , allowing a valid write to begin. When the FIFO is full, the internal write pointer is blocked from  $\overline{W}$ , so external changes in  $\overline{W}$  will not affect the FIFO when it is full.

### **READ ENABLE (R)**

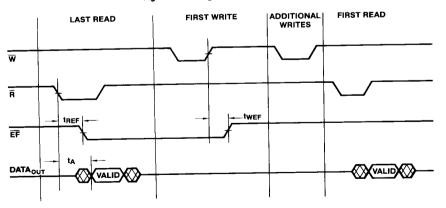

A read cycle is initiated on the falling edge of the READ ENABLE ( $\overline{R}$ ) provided the EMPTY FLAG ( $\overline{EF}$ ) is not set. The data is accessed on a First-In, First-Out basis independent of any ongoing write operations. After READ ENABLE ( $\overline{R}$ ) goes high, the data outputs (Q0 through Q8) will return to a high impedance condition until the next READ operation. When all the data has

been read from the FIFO, the EMPTY FLAG ( $\overline{\text{EF}}$ ) will go low, allowing the "final" read cycle but inhibiting further read operations with the data outputs remaining in a high impedance state. Once a valid write operation has been accomplished, the EMPTY FLAG ( $\overline{\text{EF}}$ ) will go high after  $t_{\text{WEF}}$ , and a valid READ can then begin. When the FIFO is empty, the internal read pointer is blocked from  $\overline{\text{R}}$ ; so external changes in  $\overline{\text{R}}$  will not affect the FIFO when it is empty.

### FIRST LOAD (FL)

This pin is grounded to indicate that it is the first device. In the multiple mode (depth expansion mode) application, this pin on the rest of the devices should connect to  $V_{CC}$  for proper operation.

# **EXPANSION IN (XI)**

EXPANSION IN  $(\overline{XI})$  is connected to EXPANSION OUT  $(\overline{XO})$  of the previous (in depth expansion) or same device for proper application.

# OUTPUTS: FULL FLAG (FF)

The FULL FLAT ( $\overline{FF}$ ) will go low, inhibiting further write operation, when the write pointer is one location from the read pointer, indiciating that the device is full. If the read pointer is not moved after RESET ( $\overline{RS}$ ), the FULL FLAG ( $\overline{FF}$ ) will go low after 2048 writes for the IDT7M203 and 4096 writes for the IDT7M204.

### **EXPANSION OUT (XO)**

EXPANSION OUT  $(\overline{XO})$  is connected to the EXPANSION IN  $(\overline{XI})$  of the same device (single device mode) or the EXPANSION IN  $(\overline{XI})$  of the next device (multiple device, depth expanion mode) for proper operation. This output acts as a signal to the next device by providing a pulse to the next device when the current device reaches the last location of memory.

#### **DATA OUTPUTS (Q0-Q8)**

Data outputs for 9-bit wide data. This output is in a high impedance condition whenever READ  $(\overline{\bf R})$  is in a high state.

13

#### NOTES:

- 1. t<sub>RSC</sub> = t<sub>RS</sub> + t<sub>RSR</sub>.

- 2. W and R = VIH around the rising edge of RS

Figure 2. Reset

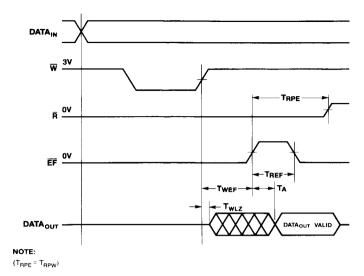

Figure 3. Asynchronous Write and Read Operation

Figure 4. Full Flag From Last Write to First Read

Figure 5. Empty Flag From Last Read to First Write

NOTE: 1. (t<sub>RPE</sub> = t<sub>RPW</sub>)

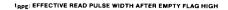

Figure 6. Empty Flag Timing

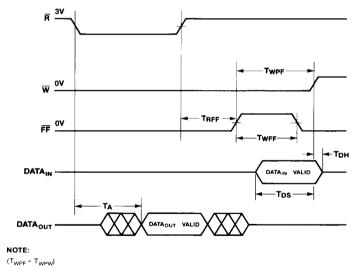

$t_{\mbox{\scriptsize WPF}}$ : EFFECTIVE WRITE PULSE WIDTH AFTER FULL FLAG HIGH

Figure 7. Full Flag Timing

# OPERATING MODES: SINGLE DEVICE MODE

A single IDT7M203/IDT7M204 may be used when the application requirements are for 2048/4096 words or less. The IDT7M203/IDT7M204 is a Single Device Configuration when the EXPANSION IN  $(\overline{\text{XI}})$  control input is connected to the EXPANSION OUT  $(\overline{\text{XO}})$  of the device and the FIRST LOAD  $(\overline{\text{FL}})$  control pin is grounded (see Figure 8).

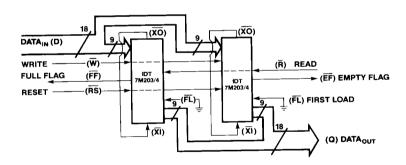

#### WIDTH EXPANSION MODE

Word width may be increased simply by connecting the corresponding input control signals of multiple devices. Status flags (EF, FF) can be detected from any one device. Figure 9 demonstrates an 18-bit word width by using two IDT7M203/IDT7M204s. Any word width can be attained by adding additional IDT7M203/IDT7M204s.

Figure 8. Block Diagram of Single IDT7M203/IDT7M204 FIFO

13

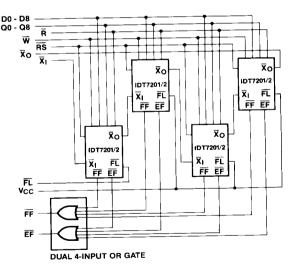

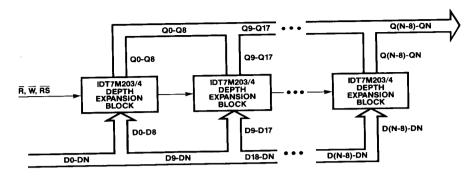

# DEPTH EXPANSION (DAISY CHAIN) MODE

The IDT7M203/IDT7M204 can easily be adapted to applications when the requirements are for greater than 2048/4096 words. Figure 10 demonstrates Depth Expansion using three IDT7M203/IDT7M204s. Any depth can be attained by adding additional IDT7M203/IDT7M204s. The IDT7M203/IDT7M204 operates in the Depth Expansion configuration when the following conditions are met:

- 1. The first device must be designed by grounding the FIRST LOAD (FL) control input.

- 2. All other devices must have FL in the high state.

- 3. The EXPANSION OUT  $(\overline{XO})$  pin of each device must be tied to the EXPANSION IN  $(\overline{XI})$  pin of the next device. See Figure 10.

- External logic is needed to generate a composite FULL FLAG (FF) and EMPTY FLAG (EF). This requires the ORing of all EFs and ORing of all FFs (i.e. all must be set to generate the correct composite FF or EF). See Figure 10.

# COMPOUND EXPANSION MODE

The two expansion techniques described above can be applied together in a straightforward manner to achieve large FIFO arrays. (See Figure 11.)

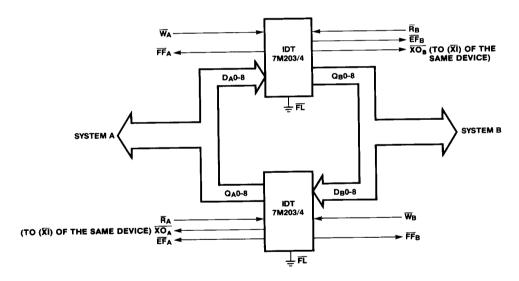

### BIDIRECTIONAL MODE

Applications which require data buffering between two systems (each system capable of READ and WRITE operations) can be achieved by pairing IDT7M203/IDT7M204s as is shown in Figure 12. Care must be taken to assure that the appropriate flag is monitored by each system (i.e.  $\overrightarrow{\mathsf{FF}}$  is monitored on the device where  $\overline{W}$  is used;  $\overline{EF}$  is monitored on the device where  $\overline{R}$  is used). Both Depth Expansion and Width Expansion may be used in this mode.

# **DATA FLOW-THROUGH MODES**

Two types of flow-through modes are permitted with the IDT7M203/IDT7M204: a read flow-through and write flowthrough mode. For the read flow-through mode (Figure 13), the FIFO permits a reading of a single word after writing one word of data into an empty FIFO. The data is enabled on the bus in (twee+  $t_A$ )ns after the rising edge of  $\overline{W}$ , called the first write edge, and it remains on the bus until the  $\overline{\mathbf{R}}$  line is raised from low-to-high, after which the bus would go into a three-state mode after  $t_{RHZ}$ ns. The EF line would have a pulse showing temporary deassertion and then would be asserted. In the interval of time that  $\overline{\mathbf{R}}$  was low, more words can be written to the FIFO (the subsequent writes after the first write edge would deassert the empty flag); however, the same word (written on the first edge), presented to the output bus as the read pointer, would not be incremented when R is low. On toggling R, the other words that were written to the FIFO will appear on the output bus as in the read cycle timings.

In a write flow-through mode (Figure 14), the FIFO permits the writing of a single word of data immediately after reading one word of data from a full FIFO. The R line causes the FF to be deasserted, but the  $\overline{\boldsymbol{W}}$  line being low causes it to be asserted again in anticipation of a new data word. On the rising edge of  $\overline{W}_{\!\scriptscriptstyle k}$ a new word is loaded in the FIFO. The  $\overline{W}$  line must be toggled when FF is not asserted to write new data in the FIFO and increment the write pointer.

Flag detection is accomplished by monitoring the FF and EF signals on either (any) device used in the width expansion configuration. Do not connect any output control signals together.

Figure 9. Block Diagram of 2048x18/4096x18 FIFO Memory Used in Width Expansion Mode

TABLE I — RESET — SINGLE DEVICE CONFIGURATION/WIDTH EXPANSION MODE

|            | INPUT | INTERNA                  | AL STATUS                | OUTPUTS |    |  |

|------------|-------|--------------------------|--------------------------|---------|----|--|

| MODE       | RS    | Read Pointer             | Write Pointer            | EF      | FF |  |

| Reset      | 0     | Location Zero            | Location Zero            | 0       | 1  |  |

| Read/Write | 1     | Increment <sup>(1)</sup> | Increment <sup>(1)</sup> | X       | X  |  |

#### NOTE:

# TABLE II — RESET AND FIRST LOAD TRUTH TABLE — DEPTH EXPANSION/COMPOUND EXPANSION MODE

|                         |    | INPUTS |     | INTERNA       | OUTPUTS       |    |    |

|-------------------------|----|--------|-----|---------------|---------------|----|----|

| MODE                    | RS | FL     | Χī  | Read Pointer  | Write Pointer | EF | FF |

| Reset-First Device      | 0  | 0      | (1) | Location Zero | Location Zero | 0  | 1  |

| Reset all Other Devices | 0  | 1      | (1) | Location Zero | Location Zero | 0  | 1  |

| Read/Write              | 1  | ×      | (1) | Х             | X             | Х  | ×  |

#### NOTES:

RS = Reset Input, FL = First Load, EF = Empty Flag Output, FF = Full Flag Output, XI = Expansion Input.

Figure 10. Block Diagram of 6144x9/12288x9 FIFO Memory (Depth Expansion)

<sup>1.</sup> Pointer will increment if flag is high.

<sup>1.</sup>  $\overline{XI}$  is connected to  $\overline{XO}$  of previous device. See Figure 10.

#### NOTES:

- For depth expansion block see DEPTH EXPANSION Section and Figure 10.

- 2. For flag detection see WIDTH expansion Section and Figure 9.

Figure 11. Compound FIFO Expansion

Figure 12. Bidirectional FIFO Mode

Figure 13. Read Data Flow-Through Mode

Figure 14. Write Data Flow-Through Mode

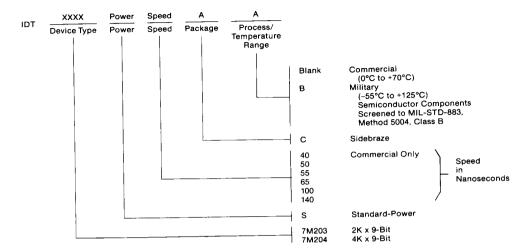

# **ORDERING INFORMATION**