|                                       |                                      |                                                                                                                                                       |                      |           |             |                            |              |          |      |     | RE   | VISIO | ONS  |                                          |                    |              |                           |                   |                          |                      |                    |                           |             |      |                                                  |            |

|---------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|-------------|----------------------------|--------------|----------|------|-----|------|-------|------|------------------------------------------|--------------------|--------------|---------------------------|-------------------|--------------------------|----------------------|--------------------|---------------------------|-------------|------|--------------------------------------------------|------------|

| LTR                                   |                                      | DESCRIPTION                                                                                                                                           |                      |           |             |                            |              |          |      |     |      | DATE  | (YR- | MO-D                                     |                    | •            | PRO                       |                   |                          |                      |                    |                           |             |      |                                                  |            |

| Α                                     | Char                                 | Change V <sub>IH1</sub> , V <sub>IH2</sub> , and t <sub>PHL13</sub> .                                                                                 |                      |           |             |                            |              |          |      |     |      | 1     | 985  | Jar                                      | 1 2                | 1            | M                         | I.                | 14                       | K                    |                    |                           |             |      |                                                  |            |

| В                                     | Char<br>Exte                         | Change end-point electrical test requirements in table II.<br>Extensive changes to table I. Editorial changes throughout.                             |                      |           |             |                            |              |          |      |     |      |       | 986  | Apr                                      | - 14               | 1            | 14                        | .0                | y                        | K                    |                    |                           |             |      |                                                  |            |

| С                                     | Char                                 | Change to military drawing format. Changes to table I. Change to timing diagram. Change to vendor similar part numbers. Editorial changes throughout. |                      |           |             |                            |              |          |      |     |      | 10    | 4.4  | 14 14 14 14 14 14 14 14 14 14 14 14 14 1 | 1                  |              |                           |                   |                          |                      |                    |                           |             |      |                                                  |            |

| D                                     | and<br>swit                          | add<br>tchi                                                                                                                                           | res<br>ng            | s.<br>tes | Add<br>t wa | nam<br>swi<br>vefo<br>GE c | tchi<br>rms. | ng ·     | test | ci  | rcui | ts a  | and  | inp                                      | ut/o               | utp          | numb<br>ut                | er 1              | 989                      | Jar                  |                    |                           | <b></b>     |      | <u>ور</u>                                        | Le Company |

|                                       |                                      |                                                                                                                                                       |                      |           |             |                            |              |          |      |     |      |       |      |                                          |                    |              |                           |                   |                          |                      |                    |                           |             |      |                                                  |            |

| CU                                    | RRE                                  | EN <sup>-</sup>                                                                                                                                       | ТС                   | CA        | GE          | E C                        | OE           | ÞΕ       | 67   | 26  | 8    |       |      | ·                                        |                    |              |                           |                   |                          |                      |                    |                           |             |      | Γ                                                | T -        |

| REV                                   |                                      | N                                                                                                                                                     | ТС                   | CA        | GE          | E C                        | OE           | ÞΕ       | 67   | 26  | 8    |       |      |                                          |                    |              |                           |                   |                          |                      |                    |                           |             |      |                                                  |            |

| REV                                   |                                      |                                                                                                                                                       |                      |           | GE          | E C                        | OE           | ÞΕ       | 67   | 26  | 8    |       |      |                                          |                    |              |                           |                   |                          |                      |                    |                           |             |      |                                                  |            |

| REV<br>SHEET<br>REV                   |                                      | D                                                                                                                                                     | D                    |           | GE          | E C                        | OE           | ÞΕ       | 67   | 26  | 8    |       |      |                                          |                    |              |                           |                   |                          |                      |                    |                           |             |      |                                                  |            |

| REV<br>SHEET<br>REV<br>SHEET          |                                      |                                                                                                                                                       | D<br>23              |           | GE          | E C                        | OE D         |          | 67   | 26  | 8    | D     | D    | D                                        | D                  | D            | D                         | D                 | D                        | D                    | D                  | D                         | D           | D    | D                                                |            |

| REV<br>SHEET<br>REV<br>SHEET          | TATUS                                | D                                                                                                                                                     | D<br>23              |           | GE          | D                          | D            | D        |      | D   | D    | D 7   | -    |                                          | $\vdash$           | _            | Ë                         | _                 |                          | H                    |                    |                           | <del></del> | D 19 | <del>                                     </del> | t          |

| REV SHEET REV SHEET                   | ATUS                                 | D                                                                                                                                                     | D<br>23              | V         | GE          | D 1                        | D<br>2       | D<br>3   | D 4  |     |      | H     | D 8  | D 9                                      | 10                 | 11           | Ë                         | 13<br><b>ELEC</b> | 14                       | 15                   | 16<br>S SU         | 17<br>PPLY                | 18          | 19   | 20                                               | H          |

| REV SHEET REV SHEET OF SHI            | TATUS<br>EETS<br>WA<br>NDA<br>MILI'  | D<br>22<br>ARC                                                                                                                                        | D<br>23<br>RE<br>SHI | v<br>ED   |             | D 1                        | D 2 PARE     | D<br>3   | D 4  | D   | D    | H     | -    | 9                                        | 10<br>MICR<br>SERI | DEFE<br>OCII | 12<br>RCUI<br>INPU<br>HIC | T, DT/OU          | TRO<br>TON,<br>DIGITON   | NIC:<br>OHIO<br>TAL: | 16<br>S SU<br>O 45 | 17<br>PPLY<br>444<br>CHAM | 18 CEN      | 19   | 20                                               | t          |

| REV SHEET REV SHEET OF SHI PMIC N STA | TATUS<br>EETS<br>VA<br>MILI'<br>DRAV | D 22 TAFWIN                                                                                                                                           | D 23 RE SHI          | ED ABL    | E           | D 1 PRE                    | D 2 PARE     | D 3 D BY | D 4  | D 5 | D 6  | H     | -    | 9                                        | 10<br>MICR<br>SERI | DEFE<br>OCII | 12 RCUI INPU              | 13 ELECTORY T, D  | 14<br>TON,<br>DIGITPUTON | 15<br>OHIO<br>TAL    | 16<br>S SU<br>O 45 | PPLY<br>444<br>CHAN       | 18 CEN      | 19   | 20<br>JAL                                        | t          |

\* U.S. GOVERNMENT PRINTING OFFICE: 1987 — 748-129/60912

5962-E1140

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

☆ U. S. GOVERNMENT PRINTING OFFICE: 1988-550-547

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

**MILITARY**

MIL-M-38510

- Microcircuits, General Specification for.

**STANDARD**

**MILITARY**

MIL-STD-883

Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

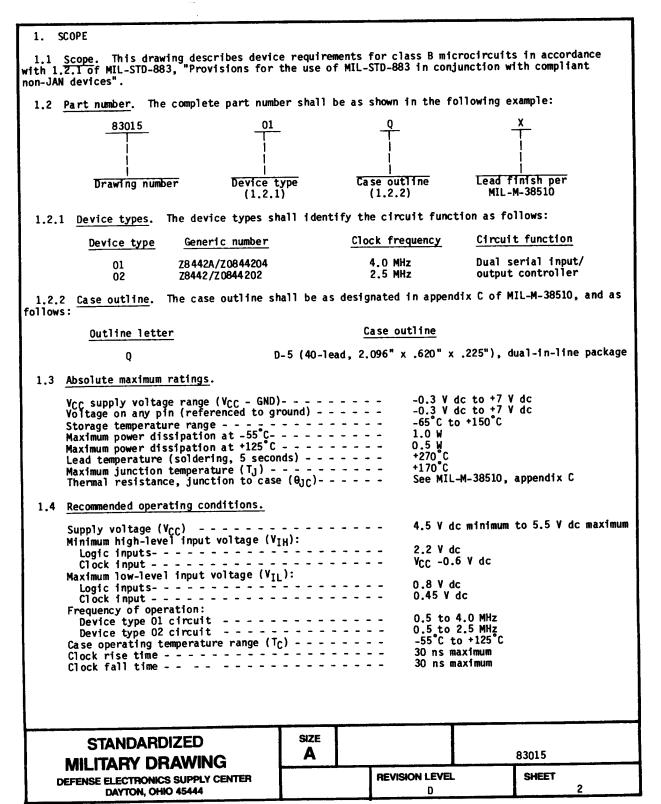

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1.

- 3.2.2 Case outline. The case outline shall be in accordance with 1.2.2 herein.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

| STANDARDIZED MILITARY DRAWING                           | SIZE<br>A |                |   | 83015   |  |

|---------------------------------------------------------|-----------|----------------|---|---------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |           | REVISION LEVEL | - | SHEET 3 |  |

DESC FORM 193A SEP 87

± U. S. GOVERNMENT PRINTING OFFICE: 1988--550-547

| Parameter                                                | Symbol             | Conditions<br>  (T <sub>C</sub> = -55°C to +125°C;           | <br>  Group A<br> subgroups | <br> Reference<br>  number | <u>Lim</u>                 | Unit             |            |

|----------------------------------------------------------|--------------------|--------------------------------------------------------------|-----------------------------|----------------------------|----------------------------|------------------|------------|

|                                                          | ļ<br>!             | V <sub>CC</sub> = 5.0 V ±10%<br>lunless otherwise specified) | 1                           | 1                          | Min                        | i Max            | <u> </u>   |

| Clock input low voltage                                  | V <sub>IL1</sub>   |                                                              | 1, 2, 3                     |                            | - <del>0</del> .3          | 0.45             | ٧          |

| Clock input high voltage                                 | V <sub>IH1</sub>   |                                                              | 1, 2, 3                     |                            | V <sub>CC</sub> -<br>0.6 v | VCC+<br>0.3 V    | ٧          |

| input low voltage                                        | V <sub>IL2</sub>   | <br>                                                         | 1, 2, 3                     |                            | - <del>0</del> .3          | 1                | ٧          |

| input high voltage                                       | V <sub>IH2</sub>   |                                                              | 1, 2, 3                     |                            | 2.2                        | V <sub>C</sub> C | ٧          |

| Output low voltage                                       | V <sub>OL</sub>    | I <sub>OL</sub> = 2.0 mA                                     | 1, 2, 3                     |                            | <br> <br>                  | 1/<br>  0.4      | ٧          |

| Output high voltage                                      | ν <sub>OH</sub>    | <br>  I <sub>OH</sub> = -250 μA                              | 1, 2, 3                     |                            | 1/2.4                      |                  | ٧          |

| Power supply current                                     | 1 <sub>CC</sub>    | <br> Outputs open<br> <br>                                   | 1, 2, 3                     |                            |                            | <br> 182<br>     | mA         |

| Output leakage<br>current low, open<br>drain outputs     | I <sub>LOL</sub>   | V <sub>OUT</sub> = 0.4 V<br>                                 | 1, 2, 3                     |                            | -10                        | +10              | μА         |

| Output leakage<br>current high,<br>open drain<br>outputs | I <sub>LOH</sub>   | V <sub>OUT</sub> = 2.4 V                                     | 1, 2, 3                     | <br>                       | -10                        | +10              | μA         |

| SYNCA pin leakage<br>current low                         | I <sub>IL1</sub>   | V <sub>IN</sub> = 0.4 V                                      | 1, 2, 3                     |                            | -40                        | +10              | μА         |

| SYNCA pin leakage<br>current high                        | I IH1              | V <sub>IN</sub> = 2.4 V                                      | 1, 2, 3                     | <br> <br>                  | -40                        | +10              | μА         |

| Input low current<br>(input and bi-<br>directional)      | I <sub>IL2</sub>   | V <sub>IN</sub> = 0.4 V                                      | 1, 2, 3                     |                            | -10                        | +10              | μ <b>Α</b> |

| Input high current<br>(input and bi-<br>directional)     | I I <sub>IH2</sub> | V <sub>IN</sub> = 2.4 V                                      | 1, 2, 3                     |                            | -10                        | +10              | μ <b>Α</b> |

| ee footnotes at end                                      |                    |                                                              |                             | 1                          |                            |                  |            |

|                                                          | DRAV               |                                                              |                             |                            | 8301                       | 6                |            |

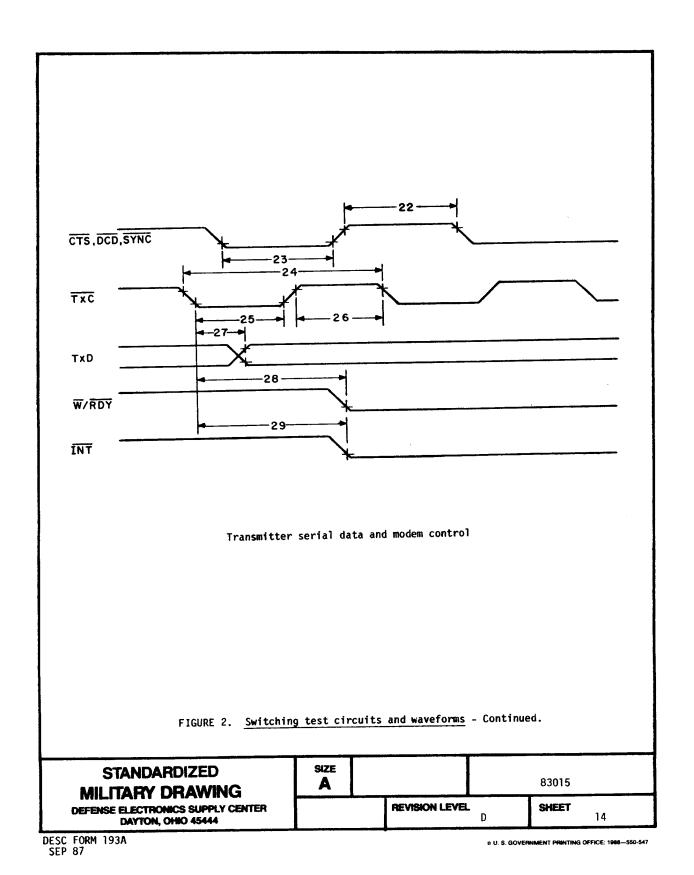

TABLE I. Electrical performance characteristics - Continued. Conditions (T<sub>C</sub> = -55°C to +125°C; V<sub>CC</sub> = 5.0 V ±10% Symbol Unit Group A Reference Limits Parameter number subgroups 2/ Min Max unless otherwise specified) 40  $T_C = +25^{\circ}C$ ; f = 1 MHz4 pF Clock capacitance CCLK see 4.3.1c | Unmeasured pins returned to 5 ground Input capacitance 1CI 15 Output capacitance  $|C_0|$ Functional tests See 4.3.1d 7, 8 4.0 MHz |CL = 100 pF ±10% Device 01 9, 10, 11 Maximum frequency **fMAX** 1/ MHz Device 02 Clock cycle time  $\frac{3}{4}$ 1 250 4000 ns  $C_L = 100 pF \pm 10\%$ Device 01 9, 10, 11 tcyc1 14000 400 Device 02 9, 10, 11 24 400 ns TxC cycle time 1/ tc yc2 400 9, 10, 11 30 ns RxC cycle time 1/ tcyc3 9, 10, 11 3 30 Clock fall time  $\frac{1}{|t_{fC}|}$ ns 4 30 Clock rise time  $\frac{1}{|t_{rC}|}$ 9, 10, 11 ns Clock width high 6/ tpwH1 2000 Device 01|9, 10, 11 2 105 ns Device 02 170 2000 2000 Device 01|9, 10, 11 5 105 ns Clock width low 7/ tpwL1 Device 02 170 12000 Pulse width high 1/tpWH2 (CTS, DCD, SYNC) 200 9, 10, 11 22 ns Pulse width low 1/tpwL2 (CTS, DCD, SYNC) 9, 10, 11 23 200 ns 180 TxC width high 9, 10, 11 26 00 ns 1/|tpwH3 See footnotes at end of table. SIZE **STANDARDIZED** Α 83015 MILITARY DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET DAYTON, OHIO 45444

DESC FORM 193A SEP 87

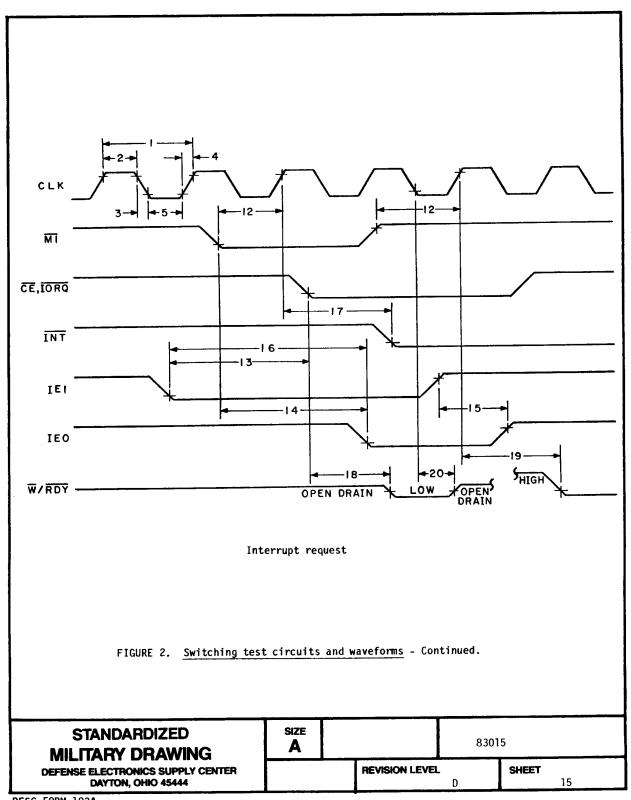

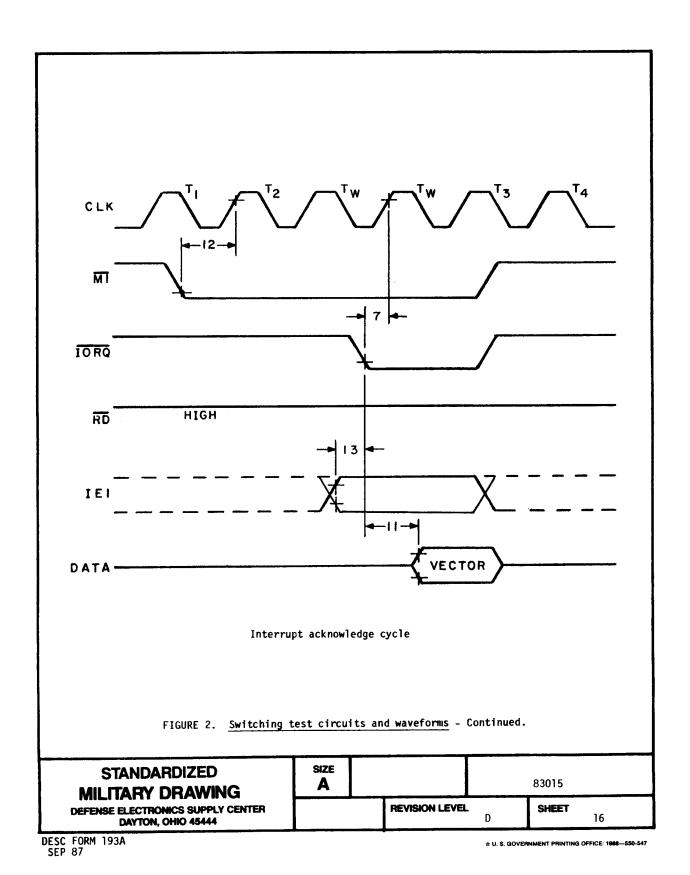

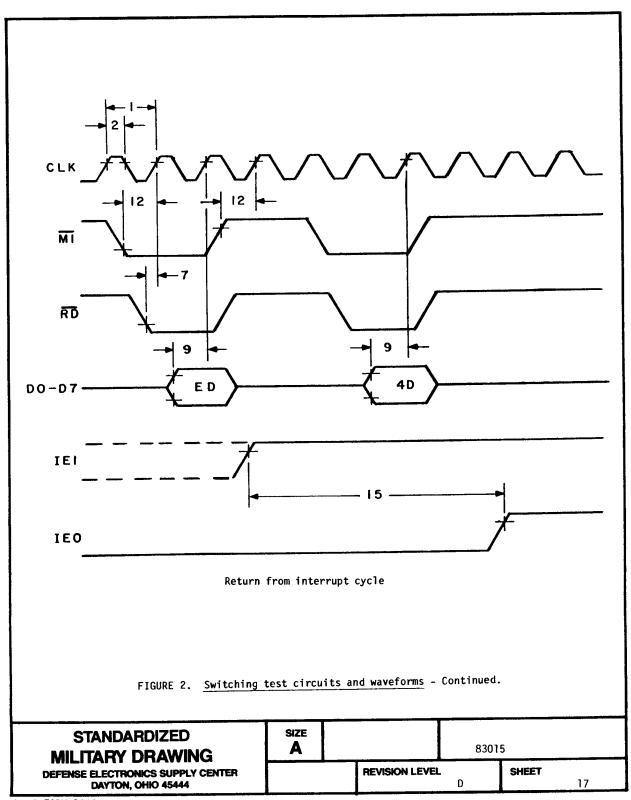

TABLE I. Electrical performance characteristics - Continued. Conditions Limits Unit Group A |Reference Parameter Symbo1 (T<sub>C</sub> = -55°C to +125°C; V<sub>CC</sub> = 5.0 V ±10% number subgroups 2/ Min Max unless otherwise specified) 25 180  $|C_L| = 100 \text{ pF} \pm 10\%$ 9, 10, 11 TxC width low 1/|tpWL3 ns 9, 10, 11 32 180 กร RxC width high 1/ tpWH4 180 9, 10, 11 31 ns RxC width low 1/|tpwL4 145 CE, C/D, B/A to Device 01|9, 10, 11 6 ns tSHL1 clock setup t<sub>SLH1</sub> Device 02 160 7 TORO, RD to clock + |tshl2 115 Device 01|9, 10, 11 ns setup t<sub>SLH2</sub> 240 5/ Device 02 Data in to clock + tshl3 setup (Write or tslH3 9, 10, 11 9 50 ns MI cycle) 9, 10, 11 33 ns RxD to RxC + setup|tSHL4 (x1 mode) 1/ 0 t<sub>SLH4</sub> Device 01|9, 10, 11 12 90 MI to clock+ setup|t<sub>SHL5</sub> ns Device 02 210 IEI to TORO+ setup t<sub>SHL6</sub> (INTA cycle) 1/ t<sub>SLH6</sub> Device 01|9, 10, 11 13 140 ns 200 Device 02  $\begin{array}{c} \text{SYNC to } \overline{\text{RXC}} + \text{setup} \mid \text{t}_{\text{SHL7}} \\ \text{(External SYNC } \underline{1}/\mid \text{t}_{\text{SLH7}} \end{array}$ -100 Device 01 9, 10, 11 38 ns -100 Device 02 modes) 140 9, 10, 11 34 ns RxC + to RxD hold tHHL1 (x1 mode) t<sub>HLH1</sub> 21 0 9, 10, 11 ns Any unspecified tHHL2 hold when setup t<sub>HLH2</sub> specified See footnotes at end of table. SIZE **STANDARDIZED** A 83015 **MILITARY DRAWING** REVISION LEVEL SHEET DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 D 6

DESC FORM 193A SEP 87

Electrical performance characteristics - Continued. TABLE I. Conditions (T<sub>C</sub> = -55°C to +125°C; V<sub>CC</sub> = 5.0 V ±10% Unit **Parameter** Symbo1 Group A Reference Limits number subgroups 2/ Min Max unless otherwise specified)  $|C_L = 100 \text{ pF } \pm 10\%$ 220 Clock + to data out|tpHL1 Device 01|9, 10, 11 8 ns delay tPLH1 240 Device 02 10 110 RD ↑ to data out Device 01|9, 10, 11 ns !tpHZ1 float delay  $\frac{1}{}$ t<sub>PLZ1</sub> 230 Device 021 10RO + to data out |tpHL2 Device 01|9, 10, 11 11 160 ns delay (INTA 340 tPLH2 cycle) Device 02 Device 01 9, 10, 11 27 300 TxC + to TxD delay tpHL3 ns (x1 mode) tPLH3 400 Device 02 MI + to IEO + deTay tpHL4 14 190 Device 01|9, 10, 11 ns (Interrupt before MI) Device 02 300 IEI + to IEO + tPLH4 (After ED decode) Device 01 9, 10, 11 15 100 ns 5/ 1/ Device 02 150 IEI + to IEO + delay tpHL5 Device 01|9, 10, 11 16 100 ns Device 021 150 Clock + to TNT + 9, 10, 11 17 200 ns tPHL6 delay TORO + to CE + to W/RDY delay (Wait Device 01 9, 10, 11 18 210 ns tPHL7 Device 021 300 mode) 120 Clock + to W/RDY + Device 01 9, 10, 11 19 ns tPHL8 delay (Ready 120 Device 02 mode) Clock+ to W/RDY tPLZ2 130 Device 01|9, 10, 11 20 ns float delay (Wait 150 Device 021 mode) See footnotes at end of table. SIZE STANDARDIZED Α 83015 MILITARY DRAWING REVISION LEVEL **DEFENSE ELECTRONICS SUPPLY CENTER** SHEET

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988--550-547

D

DAYTON, OHIO 45444

| Parameter                                                                        | <br> Symbol        | <br>  Conditions                                                                                        | Group A       | Reference | Lin          | Unit |           |

|----------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------|---------------|-----------|--------------|------|-----------|

|                                                                                  |                    | Conditions (T <sub>C</sub> = -55°C to +125°C; V <sub>CC</sub> = 5.0 V ±10% lunless otherwise specified) | subgroups<br> | number    | Min          | Max  | <br> <br> |

| TXC + to W/RDY + delay (Ready mode)                                              | t <sub>PHL9</sub>  | C <sub>L</sub> = 100 pF ±10%                                                                            | 9, 10, 11     | 28        | 5            | 9    | 8/        |

| XC + to INT + 1/<br>delay                                                        | tPHL10             |                                                                                                         | 9, 10, 11     | 29        | 5            | 9    | 8/        |

| (RC + to W/RDY + delay (Ready mode)                                              | tpHL11             | <br>                                                                                                    | 9, 10, 11     | 35        | 10           | 13   | 8/        |

| $\overline{\text{LXC}}$ to $\overline{\text{INT}}$ $\pm$ delay $\underline{1}$ / | t <sub>PHL12</sub> | 1<br>1<br>1<br>1                                                                                        | 9, 10, 11     | 36        | 10           | 13   | 8/        |

| (NC to SYNC setup                                                                | tpHL13             | T<br> <br> -                                                                                            | 9, 10, 11     | 37        | !<br>  4<br> | 7    | 8/        |

- 1/ If not tested, shall be guaranteed to the specified limits.

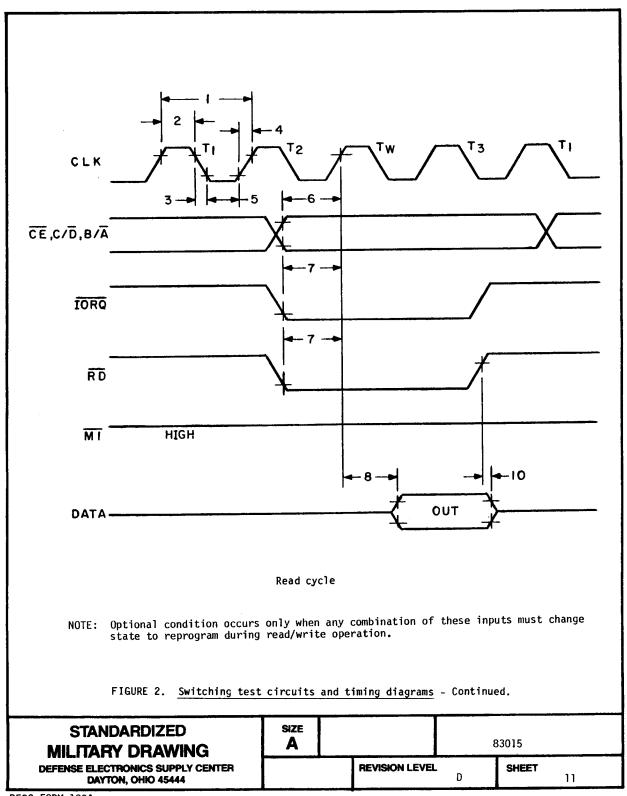

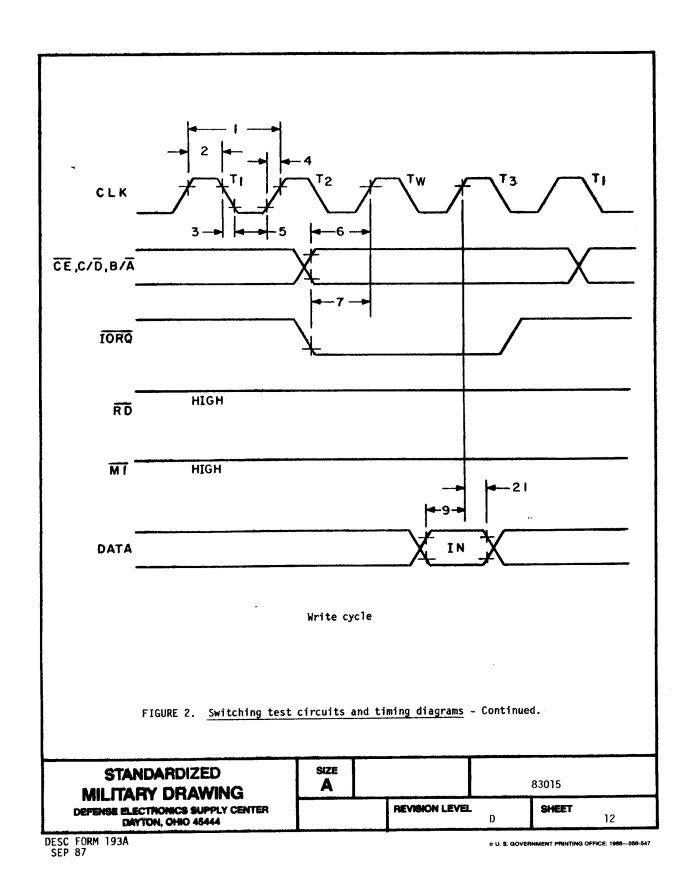

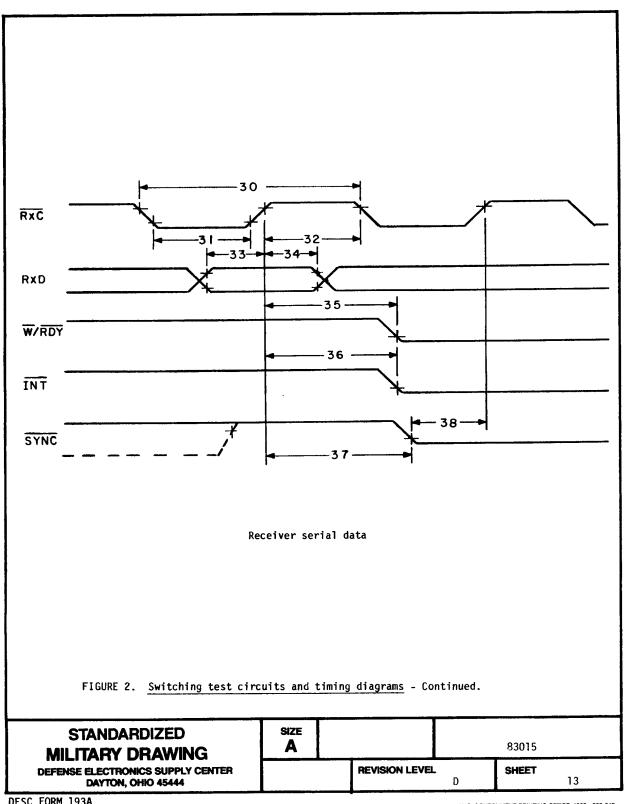

- $\frac{2}{2}$  The reference number refers to the position where the parameters being tested appears on figure 2.

- 3/ In all modes, the system clock rate must be at least five times the maximum data rate.

- 4/ RESET must be active a minimum of one complete clock cycle.

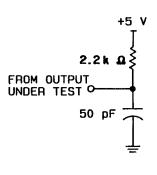

- $\frac{5}{}$  Figure 2 represents the electrical performance characteristics associated with the ac limits shown in table I.

- $\underline{6}$ / tpWH1 = tcYC tpWL1 trC tfC.

- $\frac{7}{}$  tpwL1 = tcYC tpwH1 trC tfC.

- 8/ Clock periods (system clock).

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> | · · · · · |                | <br>83015 |                  |

|------------------------------------------------------|------------------|-----------|----------------|-----------|------------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  |           | REVISION LEVEL | SHEET 8   | المناسبة المارات |

⇔ U. S. GOVERNMENT PRINTING OFFICE: 1988--550-547

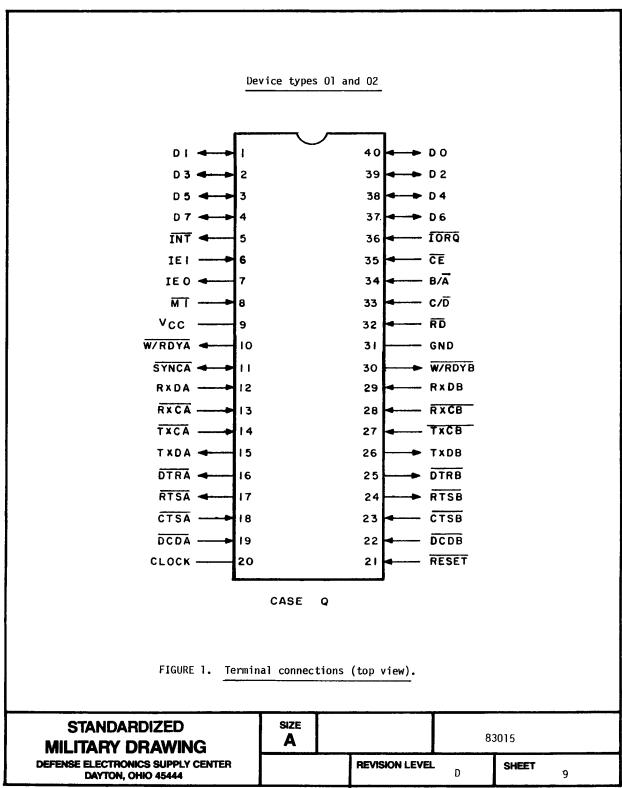

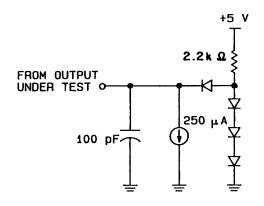

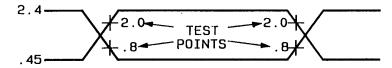

# Switching test circuits

Standard test load

Open drain test load

Switching test input/output waveform

AC testing: Inputs are driven at 2.4 V for logic "1" and 0.45 V for a logic "0". Timing measurements are made at 2.0 V for a logic "1" and 0.8 V for logic "0".

FIGURE 2. Switching test circuits and timing diagrams.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

83015

REVISION LEVEL

D

10

DESC FORM 193A SEP 87

# U. S. GOVERNMENT PRINTING OFFICE: 1988-550-547

Powered by ICminer.com Electronic-Library Service CopyRight 2003

Powered by ICminer.com Electronic-Library Service CopyRight 2003

± U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 Screening. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-SID-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 ( $C_{CLK}$ ,  $C_{I}$ , and  $C_{O}$  measurements) shall be measured only for the initial test and after process or design changes which may affect capacitance. A minimum sample size of 5 devices with zero rejects is required.

- d. Subgroup 7 and 8 functional testing shall include verification of instruction set. These tests form a part of the manufacturers test tape and shall be maintained and available from approved sources of supply.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test, method 1005 of MIL-STD-883 conditions:

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br>A |                       | 83015             |

|------------------------------------------------------|-----------|-----------------------|-------------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | <b>REVISION LEVEL</b> | . <b>SHEET</b> 18 |

☆ U. S. GOVERNMENT PRINTING OFFICE: 1968—550-547

| TABLE | II. | Electrical | test | requirements. |

|-------|-----|------------|------|---------------|

|       |     |            |      |               |

| MIL-STD-883 test requirements                                          | Subgroups<br>(per method  <br>5005, table I) |

|------------------------------------------------------------------------|----------------------------------------------|

| <br> Interim electrical parameters<br>  (method 5004)                  |                                              |

| <br> Final electrical test parameters<br>  (method 5004)               | 1*, 2, 3, 7, 9                               |

| Group A test requirements<br>  (method 5005)                           | 1, 2, 3, 4, 7,<br>8, 9, 10, 11**             |

| Groups C and D end-point<br>  electrical parameters<br>  (method 5005) | 1, 2, 3                                      |

\* PDA applies to subgroup 1.

\*\* Subgroups 10 and 11, if not tested, shall be guaranteed to the specified limits in table I.

# 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

### 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

# STANDARDIZED MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

| SIZE<br>A |                | 83015           |  |

|-----------|----------------|-----------------|--|

|           | REVISION LEVEL | <b>SHEET</b> 19 |  |

DESC FORM 193A SEP 87

6.4 Symbols, definitions, and functional descriptions. The symbols, definitions, and functional description for this device shall be as follows:

# System definitions

## Symbol

### Function

B/Ā (Channel A or B select) Input, high selects channel B. This input defines which channel is accessed during a data transfer between the CPU and the SIO. Address bit  $A_0$  from the CPU is often used for the selection function.

C/D (Control or Data Select) Input, high selects control. This input defines the type of information transfer performed between the CPU and the SIO. A high at this input during a CPU write to the SIO causes the information on the data bus to be interpreted as a command for the channel selected by the B/A. A low at C/D means that the information on the data bus is data. Address bit  $\rm A_1$  is often used for this function.

CE (Chip Enable) Input, active low. A low level at this input enables the SIO to accept command or data input from the CPU during a write cycle, or to transmit data to the CPU during a ready cycle.

CLK (System Clock) Input. The SIO uses the standard System Clock to synchronize internal signals. This is a single-phase clock.

CTSA, CTSB (Clear to Send) Inputs, active low. When programmed as Auto Enables, a low on these inputs enables the respective transmitter. If not programmed as Auto Enables, these inputs may be programmed as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow-rise time signals. The SIO detects pulses on these inputs and interrupts the CPU on both logic level transitions. The Schmitt-trigger buffering does not guarantee a specified noise-level margin.

D<sub>O</sub> - D<sub>7</sub> (System Data Bus) Bidirectional, three-state. The system data bus transfers data and commands between the CPU and the SIO.  $\rm D_{O}$  is the least significant bit.

DCDA, DCDB (Data Carrier Detect) Inputs, active low. These pins function as Receiver Enables if the SIO is programmed for Auto Enables; otherwise they may be used as general-purpose input pins. Both pins are Schmitt-trigger buffered to accommodate slow-rise time signals. The SIO detects pulses on these pins and interrupts the CPU on both logic level transitions. Schmitt-trigger buffering does not guarantee a specific noise-level margin.

DTRA, DTRB (Data Terminal Ready) Outputs, active low. These outputs follow the state programmed into SIO. They can also be programmed as general-purpose outputs.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE A 83015

REVISION LEVEL SHEET 20

DESC FORM 193A SEP 87

IEI

(Interrupt Enable In)

Input, active high. This signal is used with IEO to form a priority daisy chain when there is more than one interrupt-driven device. A high on this line indicates that no other device of high priority is being serviced by a CPU interrupt service routine.

IEO

(Interrupt Enable Out)

Output, active high. IEO is high only if IEI is high and the CPU is not servicing an interrupt from this SIO. Thus, this signal blocks lower priority devices from interrupting while a higher priority device is being serviced by its CPU interrupt service routine.

INT (Interrupt Request) Output, open drain, active low. When the SIO is requesting an interrupt, it pulls  $\overline{\text{INT}}$  low.

TORQ (Input/Output Request) Input from CPU, active low.  $\overline{\mbox{IORQ}}$  is used in conjunction with B/A, C/D, CE and RD to transfer commands and data between the CPU and the SIO. When CE, RD and  $\overline{\mbox{IORQ}}$  are all active, the channel selected by B/A transfers data to the CPU (a read operation). When CE and  $\overline{\mbox{IORQ}}$  are active, but RD is inactive, the channel selected by B/A is written to by the CPU with either data or control information as specified by C/D. As mentioned previously, if  $\overline{\mbox{IORQ}}$  and MI are active simultaneously, the CPU is acknowledging an interrupt and the SIO automatically places its interrupt vector on the CPU data bus if it is the highest priority device requesting an interrupt.

MI (Machine Cycle) Input from CPU, active low. When  $\overline{\text{MI}}$  is active and  $\overline{\text{RD}}$  is also active, the CPU is fetching an instruction from memory; when  $\overline{\text{MI}}$  is active while  $\overline{\text{IORQ}}$  is active, the SIO accepts  $\overline{\text{MI}}$  and  $\overline{\text{IORQ}}$  as an interrupt acknowledge if the SIO is the highest priority device that has interrupted the CPU.

RxCA, RxCB (Receiver Clocks) Inputs. Receive data is sampled on the rising edge of  $\overline{\text{RXC}}$ . The Receiver Clocks may be 1, 16, 32 or 64 times the data rate in asynchronous modes. These clocks may be driven by the CTC Counter Timer Circuit for programmable baud rate generation. Both inputs are Schmitt-trigger buffered (no noise level margin is specified).

RD (Read Cycle Status) Input from CPU, active low. If  $\overline{RD}$  is active, a memory or I/O read operation is in progress.  $\overline{RD}$  is used with B/A,  $\overline{CE}$  and  $\overline{IORQ}$  to transfer data from the SIO to the CPU.

RxDA, RxDB (Receive Data) Inputs, active high. Serial data at TTL levels.

RESET (Reset)

Input, active low. A low RESET disables both receivers and transmitters, forces TxDA and TxDB marking, forces the modem controls high and disables all interrupts. The control registers must be rewritten after the SIO is reset and before data is transmitted or received.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE 83015

REVISION LEVEL SHEET

D 21

DESC FORM 193A SEP 87

★ U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547

RTSA, RTSB (Request to Send) Outputs, active low. When the RTS bit in Write Register 5 is set, the RTS output goes low. When the RTS bit is reset in the asynchronous mode, the output goes high after the transmitter is empty. In synchronous modes, the RTS pin strictly follows the state of the RTS bit. Both pins can be used as general-purpose outputs.

SYNCA (Synchronization) Input/output, active low. This pin can act either as input or output. In the asynchronous receive mode, it is an input similar to CTS and DCD. In this mode, the transitions on this line affect the state of the Sync/Hunt status bits in Read Register O, but have no other function. In the External Sync mode, this line also acts as input. When external synchronization is achieved, SYNC must be driven low on the second rising edge or RxC after that rising edge of RxC on which the last bit of the sync character was received. In other words, after the sync pattern is detected, the external logic must wait for the two full Receive Clock cycles to activate the SYNC input. Once SYNC is forced low, it should be kept low until the CPU informs the external synchronization detect logic that synchronization has been lost or a new message is about to start. Character assembly begins on the rising edge of  $\overline{RxC}$  that immediately precedes the falling edge of  $\overline{SYNC}$  in the External Sync mode. In the internal synchronization mode (Monosync and Bisync), this pin acts as an output that is active during the part of the receive clock ( $\overline{RxC}$ ) cycle in which sync characters are recognized. The sync condition is not latched, so this output is active each time a sync pattern is recognized, regardless of character boundaries.

TxCA, TxCB

(Transmitter Clocks)

TxD changes from the falling edge of TxC. In asynchronous modes, the Transmitter Clocks may be 1, 16, 32 or 64 times the data rate; however, the clock multiplier for the transmitter and the receiver must be the same. The Transmit Clock inputs are Schmitt-trigger buffered for relaxed rise- and fall-time requirements (no noise level margin is specified). Transmitter Clocks may be driven by the CTC Counter Timer Circuit for programmable baud rate generation.

TxDA, TxDB (Transmit Data) Outputs, active high. Serial data at TTL levels.

W/RDYA, W/RDTB (Wait/Ready A, Wait/Ready B) Outputs, open drain, when programmed for Wait function; driven high and low when programmed for Ready function. These dual-purpose outputs may be programmed as Ready lines for a DMA controller or as Wait lines that synchronize the CPU to the SIO data rate. The reset state is open drain.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE 83015

REVISION LEVEL SHEET 22

DESC FORM 193A SEP 87 ± U. S. GOVERNMENT PRINTING OFFICE: 1988--550-541

6.5 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5) has been submitted to DESC-ECS.

| Military drawing part number | Vendor<br>  CAGE<br>  number | Vendor similar part number 1/ | Replacement<br> military specification<br>  part number <u>2</u> / |

|------------------------------|------------------------------|-------------------------------|--------------------------------------------------------------------|

| 8301501QX                    | 56708                        | Z0844204CMB <u>3</u> /        | M38510/48101BQX                                                    |

| 8301502QX                    | 56708                        | Z0844202CMB 4/                | <br>  M38510/48102BQX                                              |

1/ Caution: Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this

drawing. Qualification requirement has been removed from this specification.

(See MIL-STD-1562.)

3/ This part was previously designated as Z8442ACMB. This part was previously designated as Z8442CMB.

**Vendor CAGE** number

56708

Vendor name and address

Zilog, Incorporated 210 Hacienda Avenue Campbell, CA 95008

**STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER** DAYTON, OHIO 45444

SIZE Α

83015

**REVISION LEVEL**

SHEET 23

DESC FORM 193A SEP 87

☆ U. S. GOVERNMENT PRINTING OFFICE: 1988—550-547