To all our customers

# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note : Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

## MITSUBISHI 16-BIT SINGLE-CHIP MICROCOMPUTER 7700 FAMILY / 7751 SERIES

## Preface

.

This manual describes the hardware of the Mitsubishi CMOS 16-bit microcomputers 7751 Group. After reading this manual, the users will be able to understand the functions, so that they can utilize their capabilities fully.

For details concerning the software, refer to the 7751 Series Software Manual. For details concerning the development support tools (assembler, emulation pods), refer to the respective user's manuals.

## **Table of Contents**

| CHAPTER 1. DESCRIPTION   |     |

|--------------------------|-----|

| 1.1 Performance overview |     |

| 1.2 Pin configuration    |     |

| 1.3 Pin description      |     |

| 1.4 Block diagram        | 1-8 |

## CHAPTER 2. CENTRAL PROCESSING UNIT (CPU)

| 2.1 Central processing unit                      | 2-2  |

|--------------------------------------------------|------|

| 2.1.1 Accumulator (Acc)                          | 2-3  |

| 2.1.2 Index register X (X)                       | 2-3  |

| 2.1.3 Index register Y (Y)                       | 2-3  |

| 2.1.4 Stack pointer (S)                          |      |

| 2.1.5 Program counter (PC)                       | 2-5  |

| 2.1.6 Program bank register (PG)                 |      |

| 2.1.7 Data bank register (DT)                    | 2-6  |

| 2.1.8 Direct page register (DPR)                 |      |

| 2.1.9 Processor status register (PS)             | 2-8  |

| 2.2 Bus interface unit                           | 2-10 |

| 2.2.1 Overview                                   | 2-10 |

| 2.2.2 Functions of bus interface unit (BIU)      | 2-12 |

| 2.2.3 Operation of bus interface unit (BIU)      | 2-15 |

| 2.3 Access space                                 |      |

| 2.3.1 Banks                                      | 2-18 |

| 2.3.2 Direct page                                | 2-18 |

| 2.4 Memory assignment                            | 2-19 |

| 2.4.1 Memory assignment in internal area         |      |

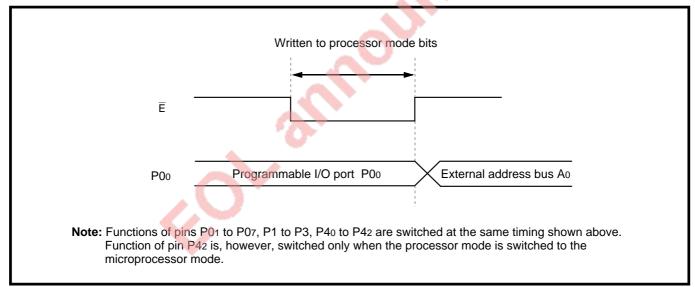

| 2.5 Processor modes                              | 2-22 |

| 2.5.1 Single-chip mode                           | 2-23 |

| 2.5.2 Memory expansion and microprocessor modes  | 2-23 |

| 2.5.3 Setting processor modes                    |      |

| [Precautions when operating in single-chip mode] |      |

## CHAPTER 3. INPUT/OUTPUT PINS

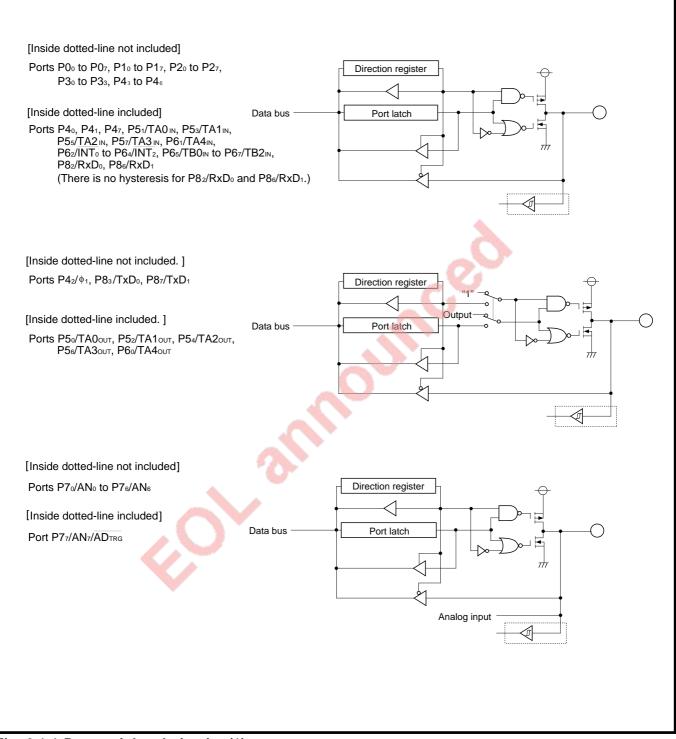

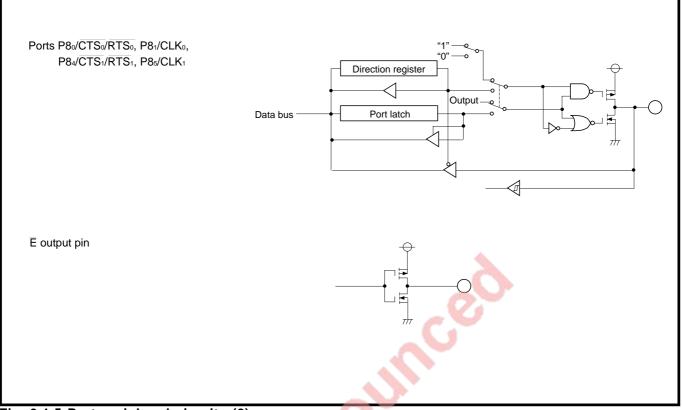

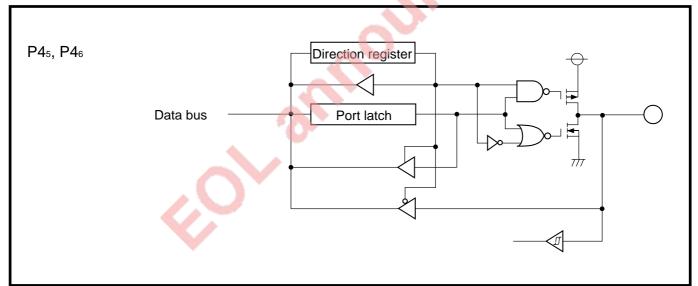

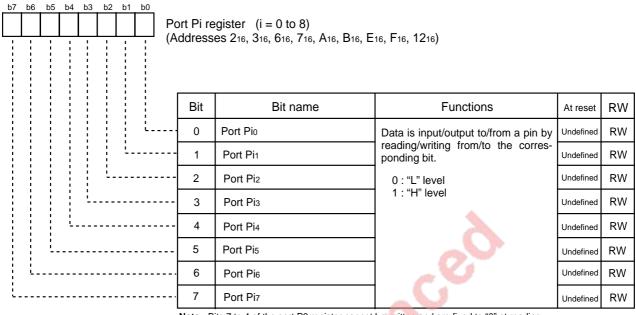

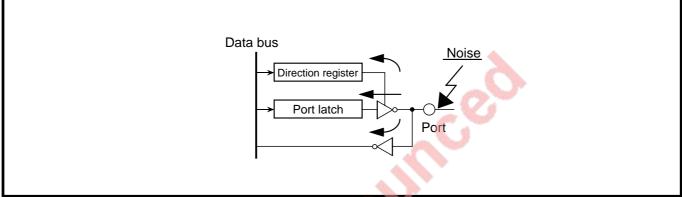

| 3.1 Programmable I/O ports                  |  |

|---------------------------------------------|--|

| 3.1.1 Direction register                    |  |

| 3.1.2 Port register                         |  |

| 3.2 I/O pins of internal peripheral devices |  |

## CHAPTER 4. INTERRUPTS

| 4.1 Overview                                                                             | 4-2  |

|------------------------------------------------------------------------------------------|------|

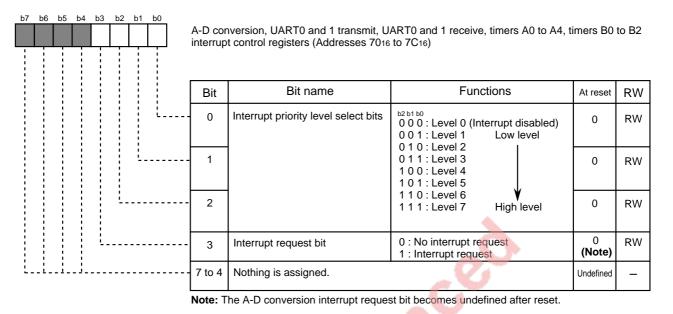

| 4.2 Interrupt sources                                                                    | 4-4  |

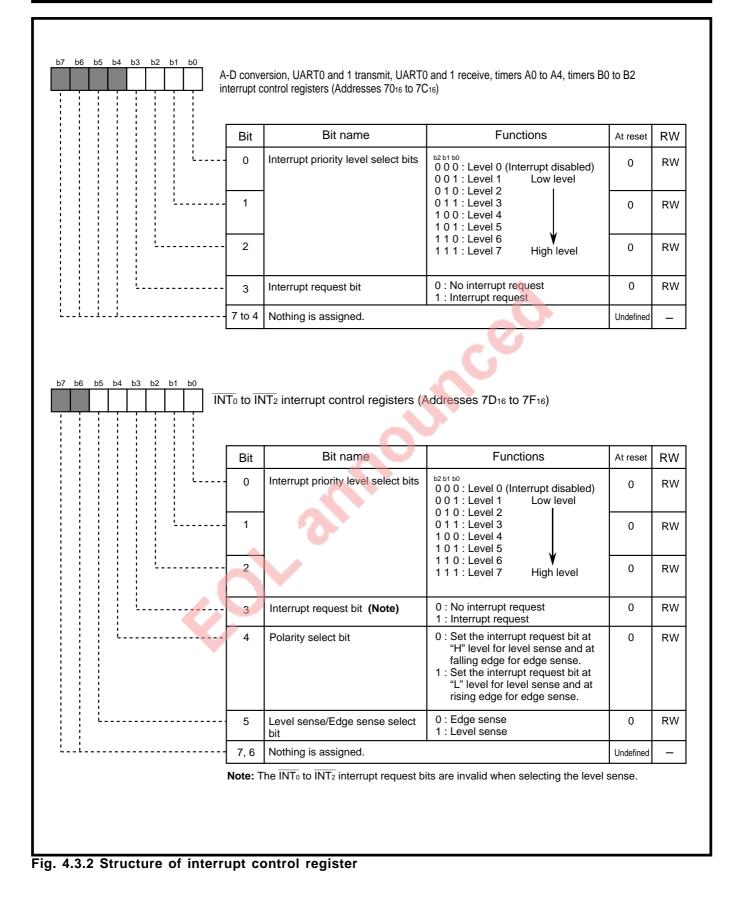

| 4.3 Interrupt control                                                                    |      |

| 4.3.1 Interrupt disable flag (I)                                                         | 4-8  |

| 4.3.2 Interrupt request bit                                                              | 4-8  |

| 4.3.3 Interrupt priority level select bits and processor interrupt priority level (IPL). |      |

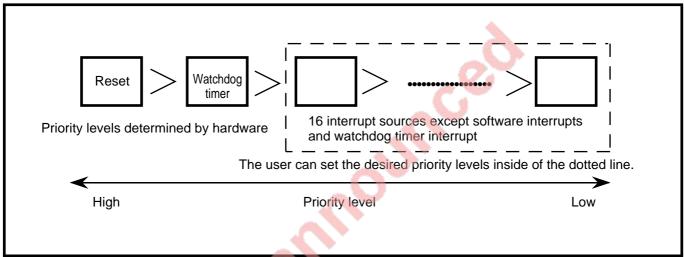

| 4.4 Interrupt priority level                                                             | 4-10 |

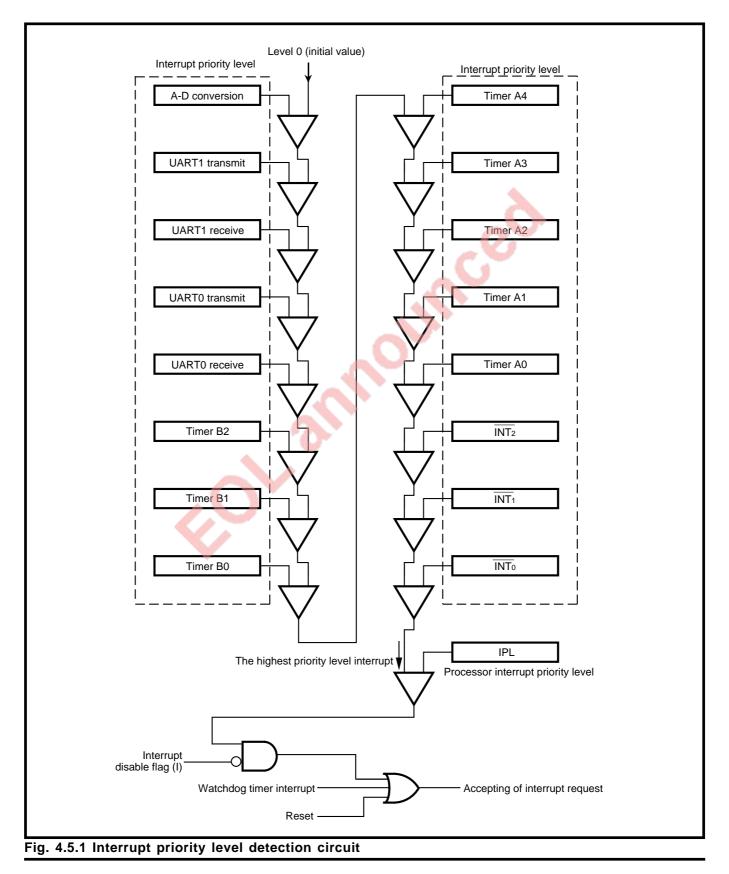

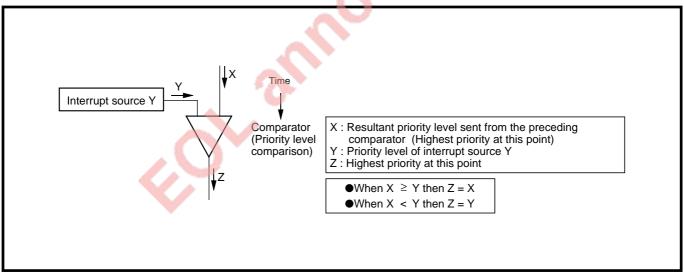

| 4.5 Interrupt priority level detection circuit                                           | 4-11 |

| 4.6 Interrupt priority level detection time                                              | 4-13 |

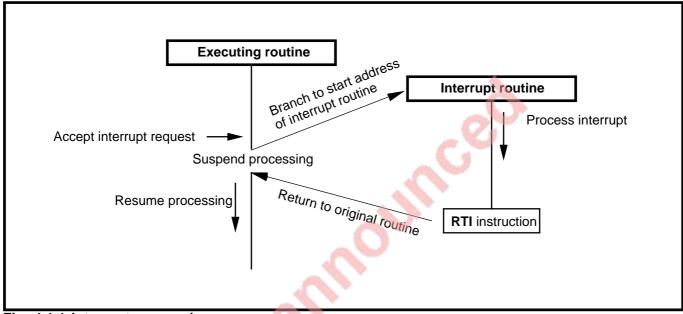

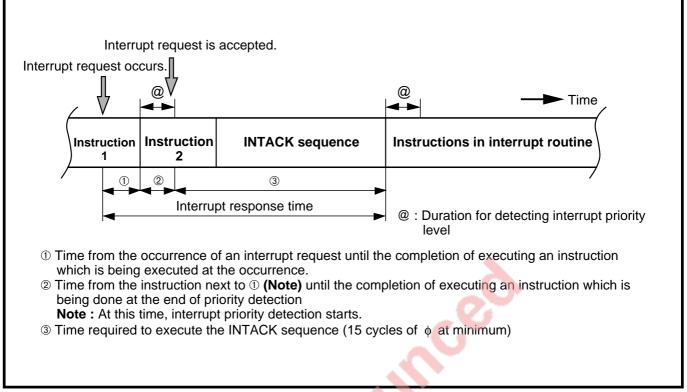

| 4.7 Sequence from acceptance of interrupt request to execution of interrupt routine      | 4-14 |

| 4.7.1 Change in IPL at acceptance of interrupt request                                   | 4-16 |

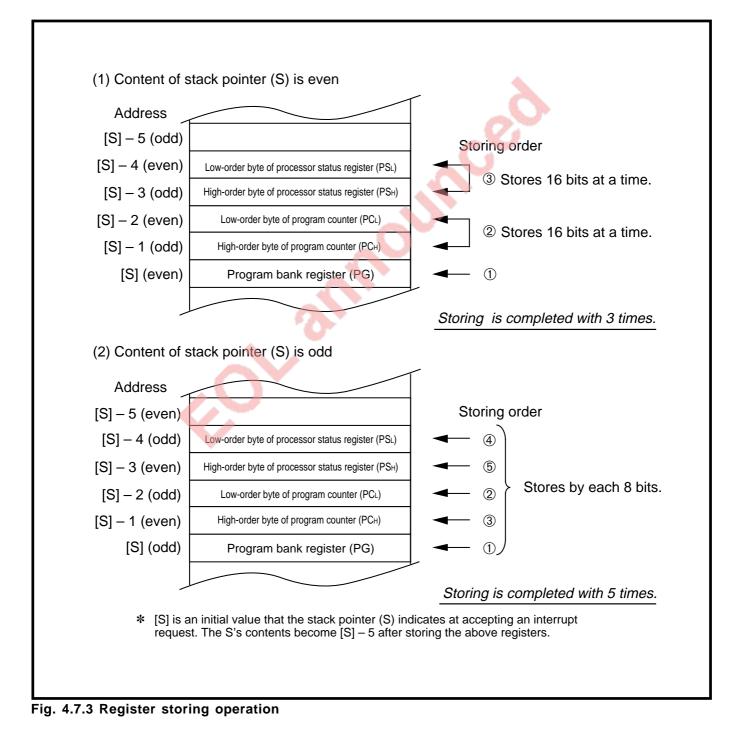

| 4.7.2 Storing registers                                                                  | 4-17 |

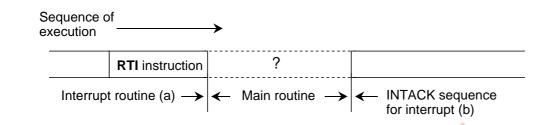

| 4.8 Return from interrupt routine                                                        |      |

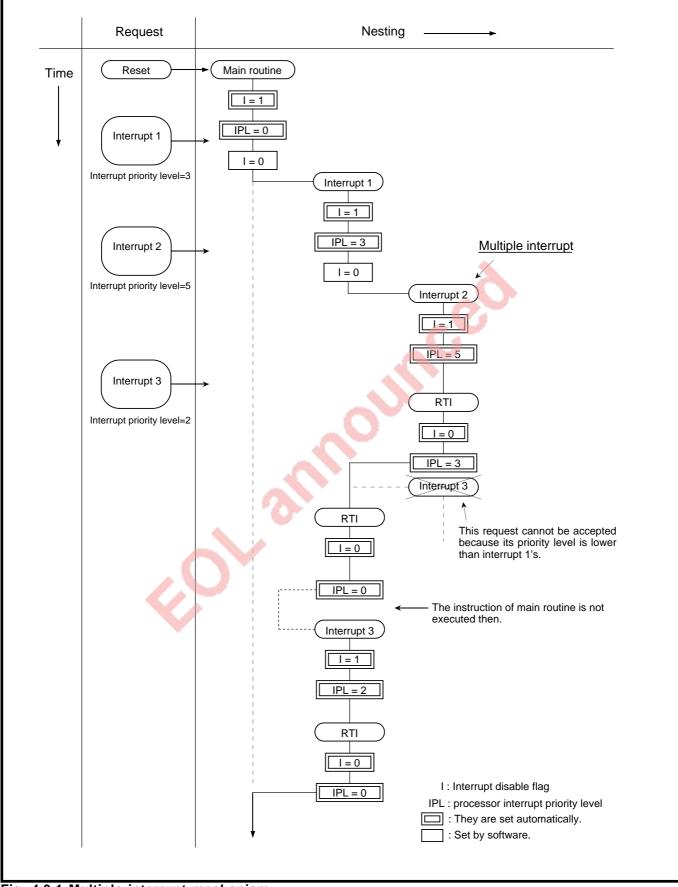

| 4.9 Multiple interrupts                                                                  | 4-18 |

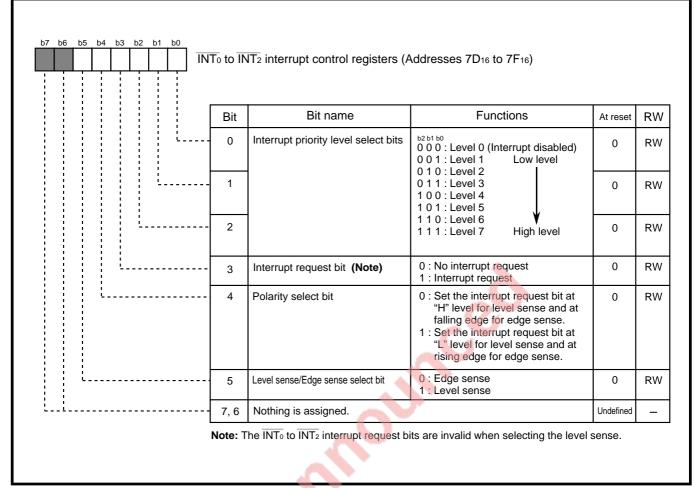

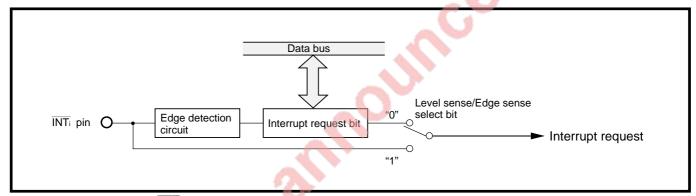

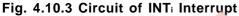

| 4.10 External interrupts (INT: interrupt)                                                | 4-20 |

| 4.10.1 Function of INT interrupt request bit                                             | 4-23 |

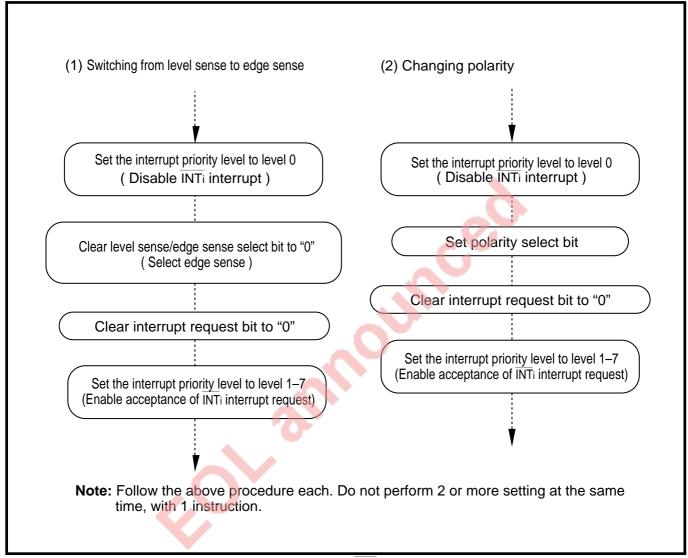

| 4.10.2 Switch of occurrence factor of INT interrupt request                              | 4-25 |

|                                                                                          |      |

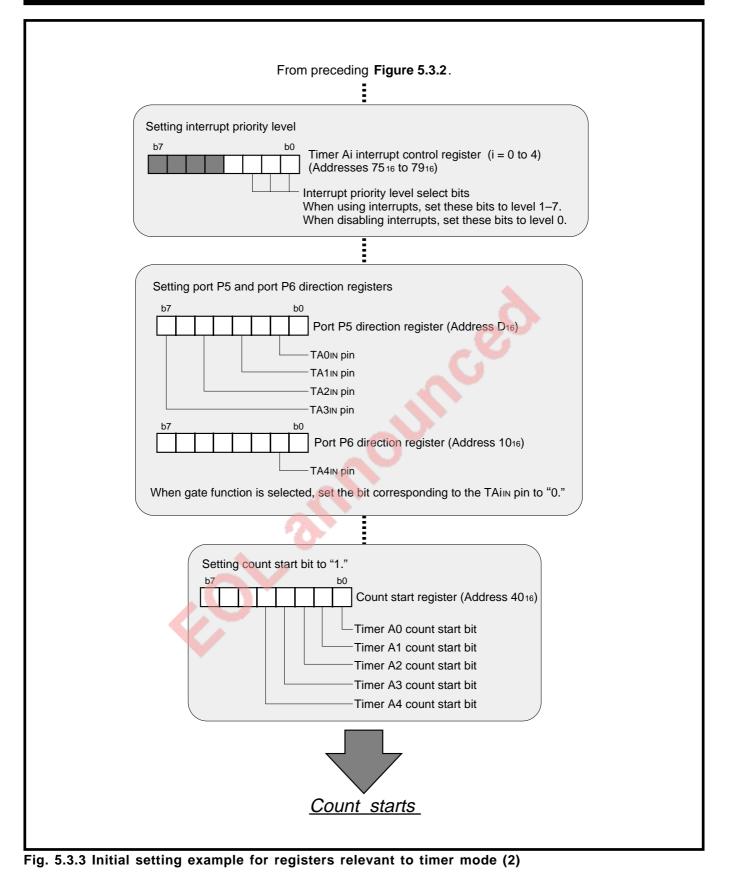

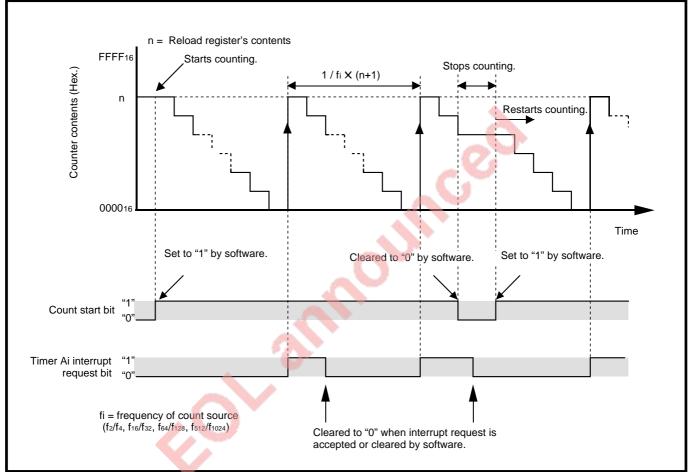

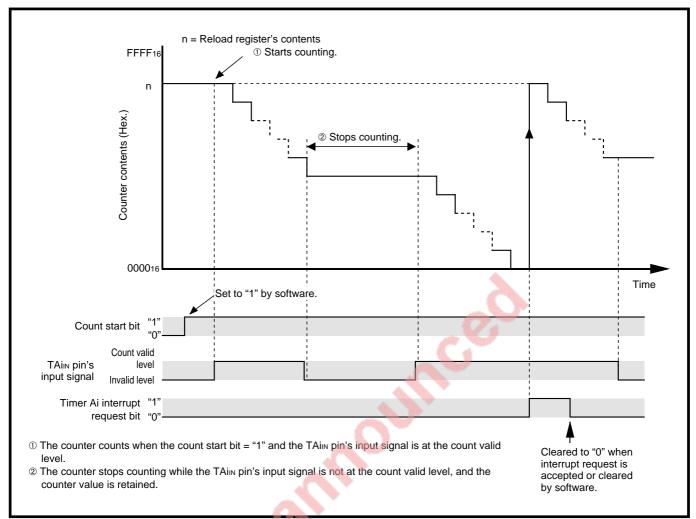

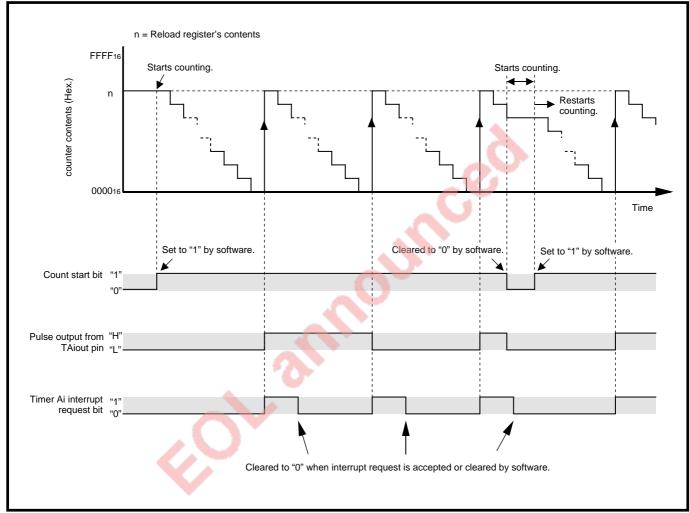

## CHAPTER 5. TIMER A

| 5.1 Overview                              |                   |

|-------------------------------------------|-------------------|

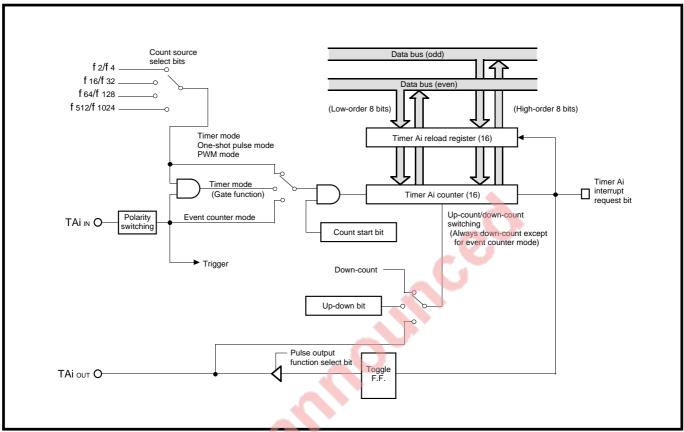

| 5.2 Block description                     |                   |

| 5.2.1 Counter and reload register (time   | r Ai register)5-4 |

| 5.2.2 Count start register                | 5-5               |

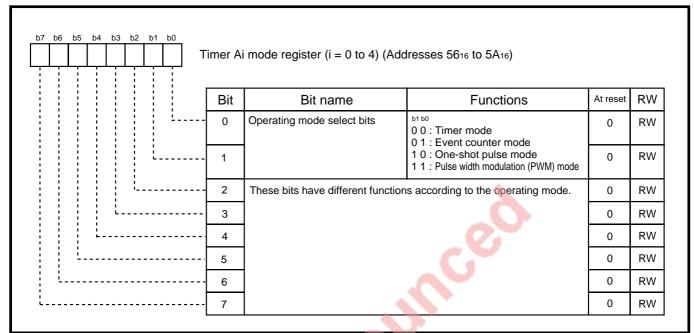

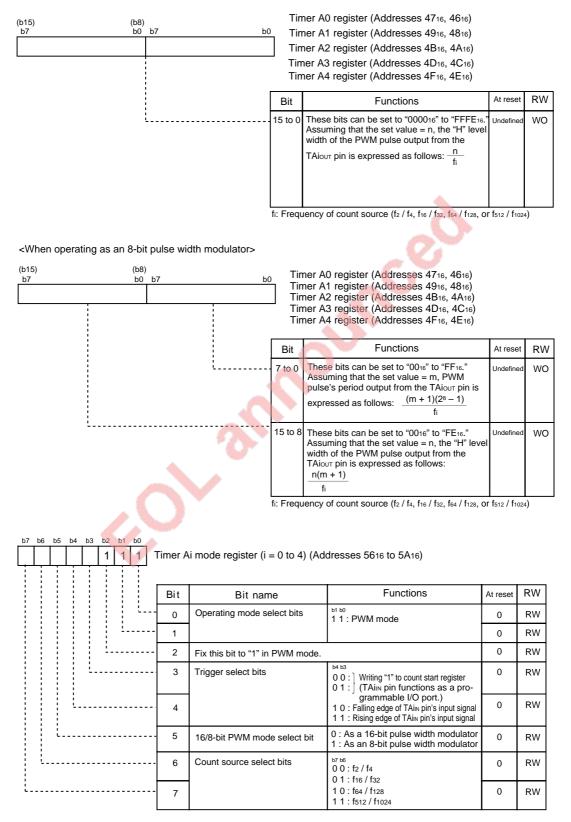

| 5.2.3 Timer Ai mode register              |                   |

| 5.2.4 Timer Ai interrupt control register |                   |

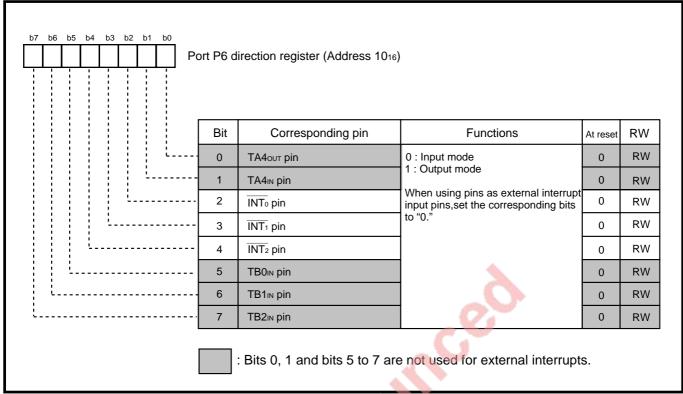

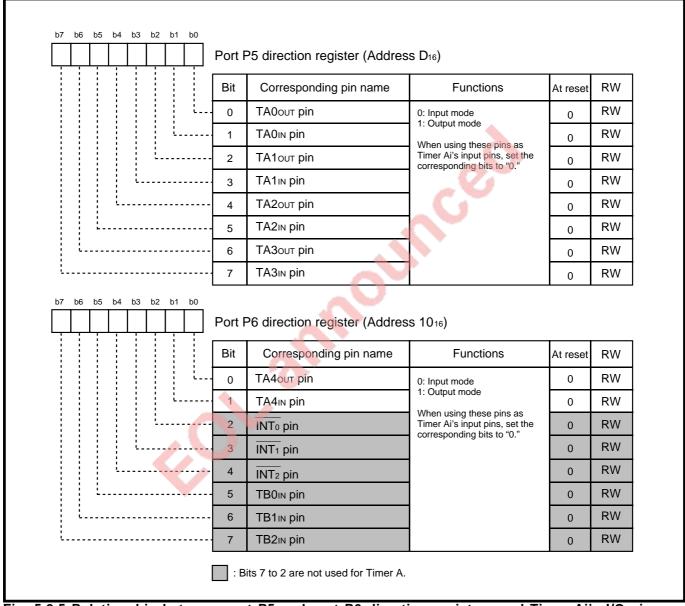

| 5.2.5 Port P5 and port P6 direction reg   | jisters           |

|                                           |                   |

| J J J J J J J J J J J J J J J J J J J     |                   |

|                                           |                   |

|                                           |                   |

| 5.3.4 Select function                     |                   |

|                                           |                   |

|                                           |                   |

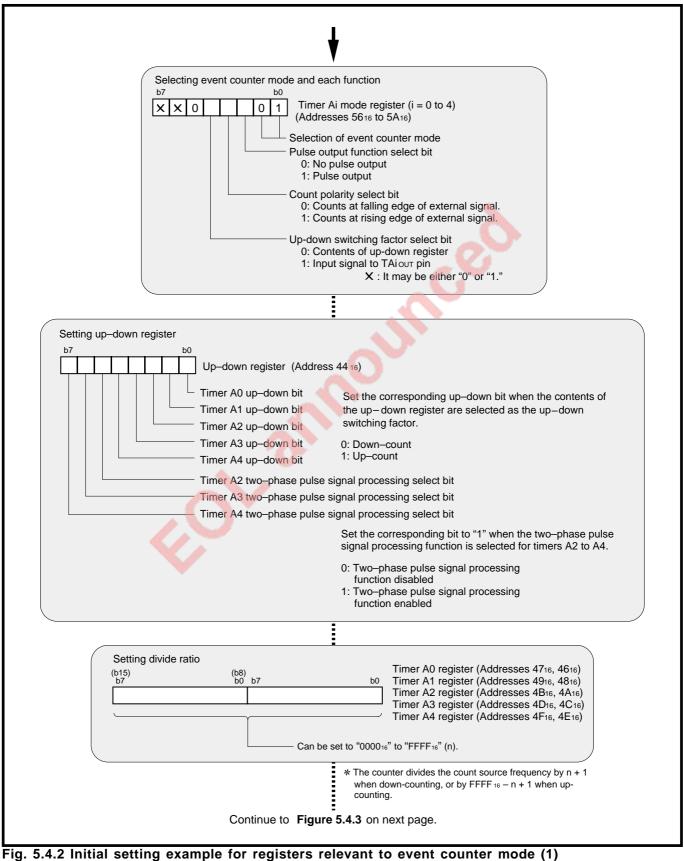

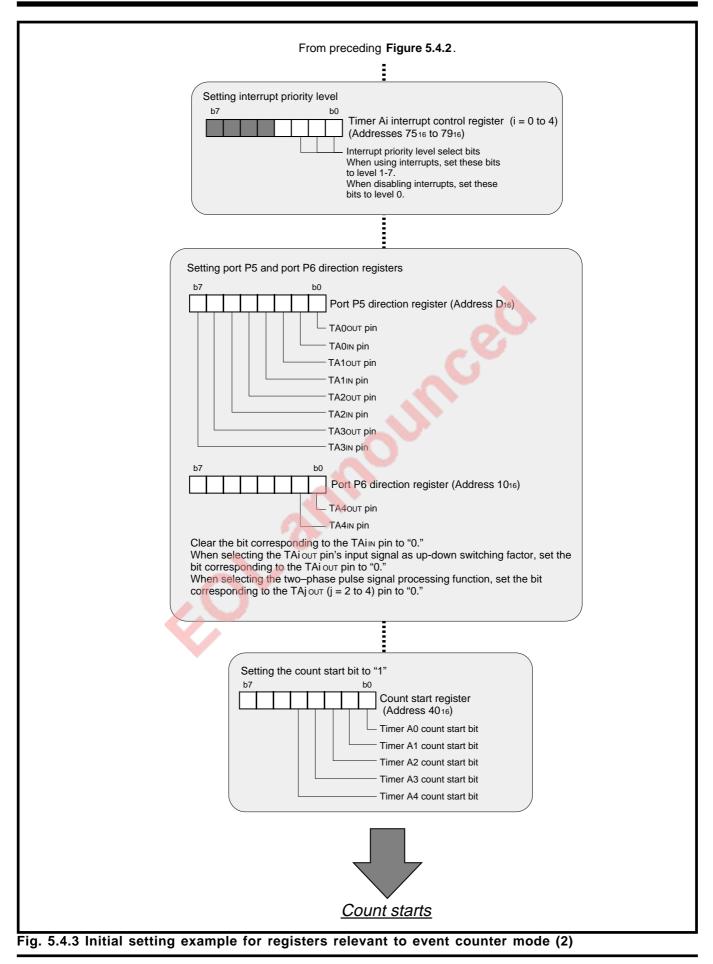

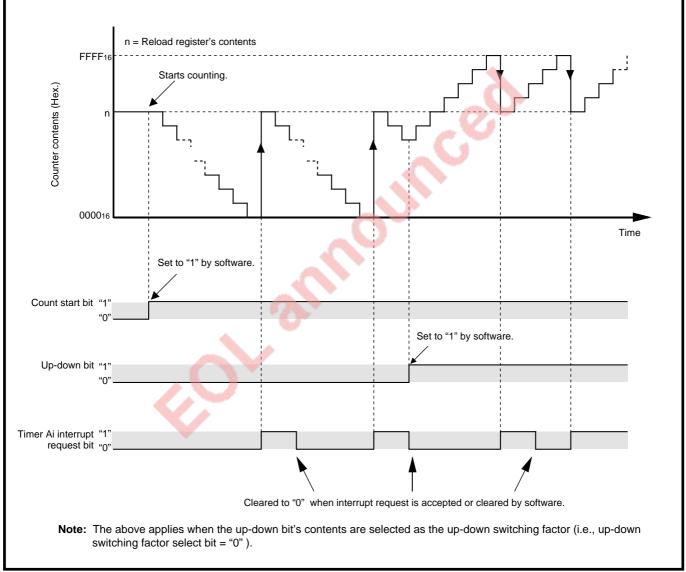

| 5.4.2 Operation in event counter mode     |                   |

|                                           |                   |

|                                           |                   |

|                                           |                   |

|                                           |                   |

|                                           |                   |

|                                           | e 5-36            |

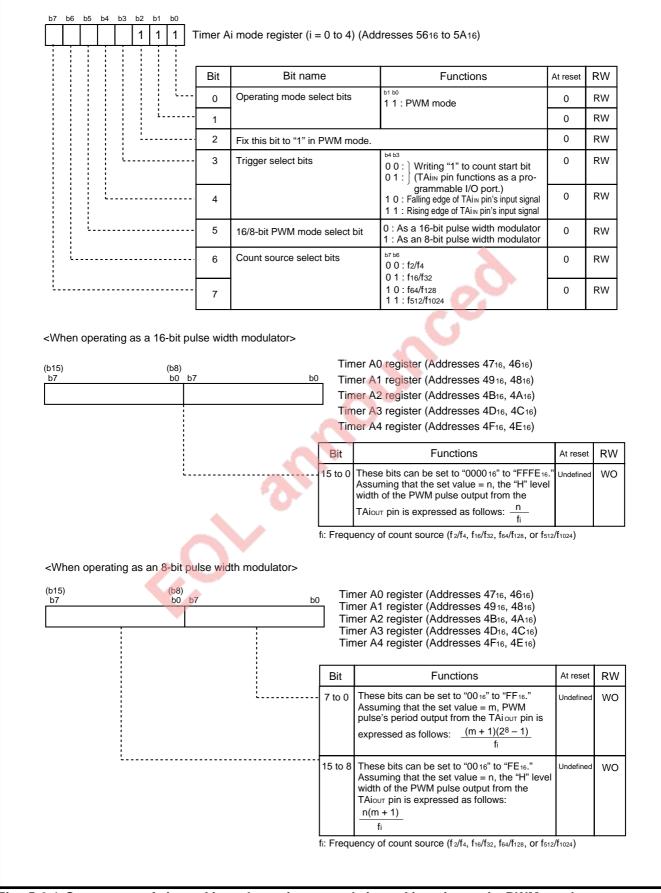

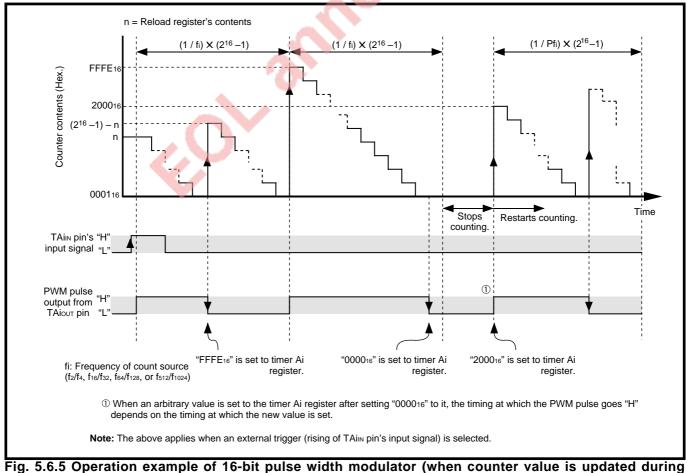

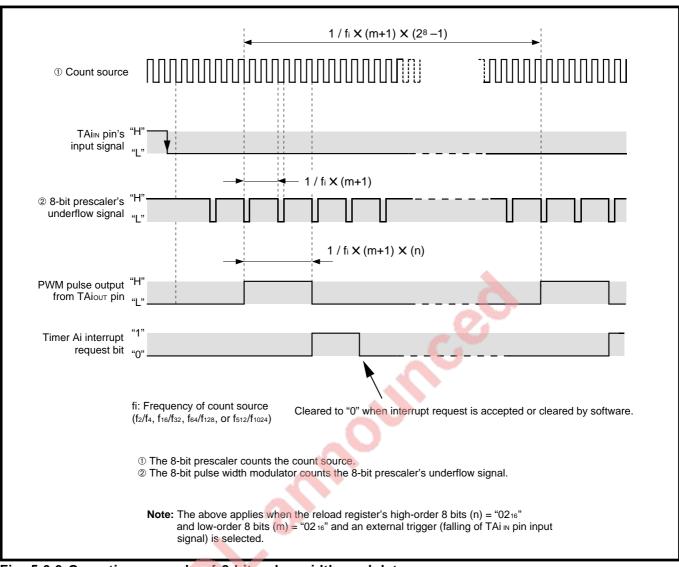

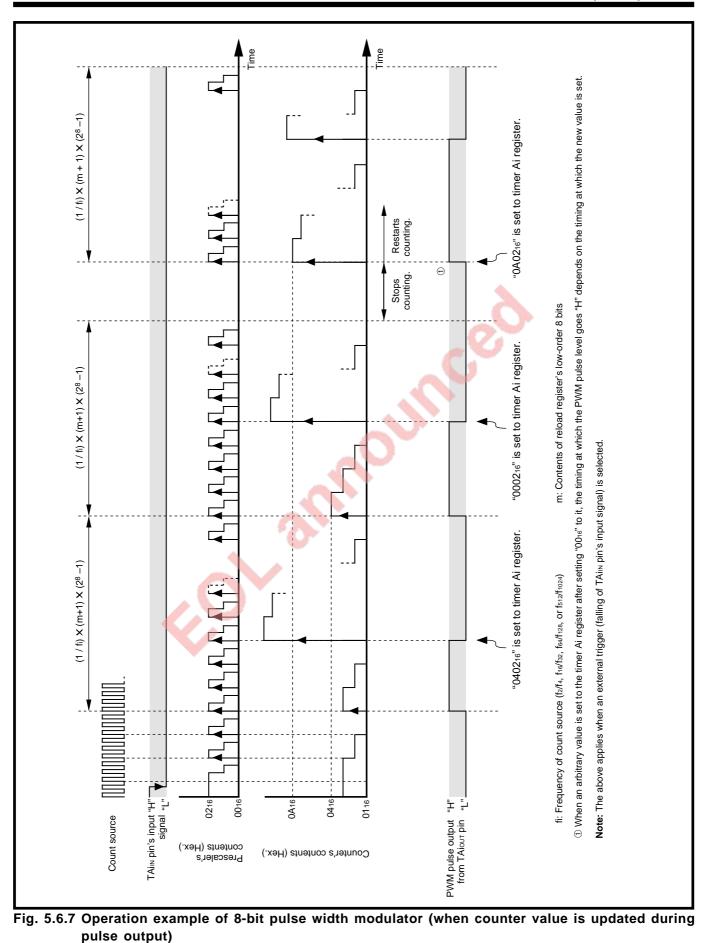

| 5.6 Pulse width modulation (PWM) mode     | ə 5-39            |

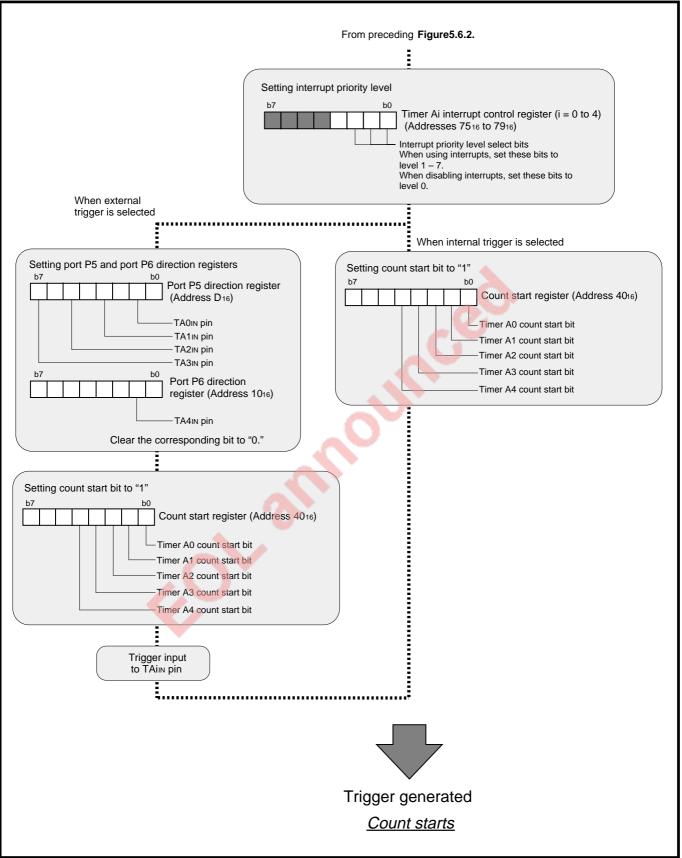

| 5.6.1 Setting for PWM mode                |                   |

|                                           |                   |

|                                           |                   |

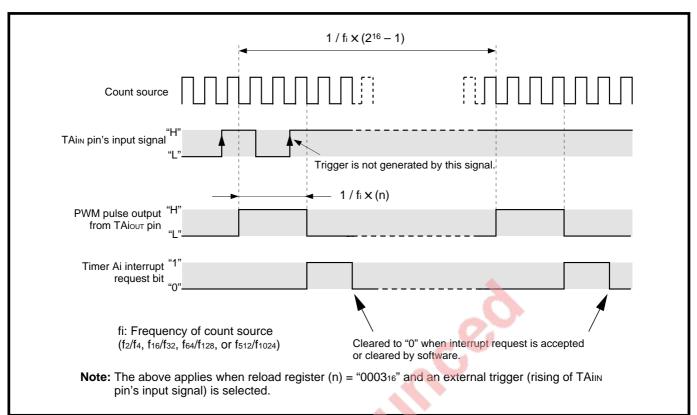

| 5.6.4 Operation in PWM mode               |                   |

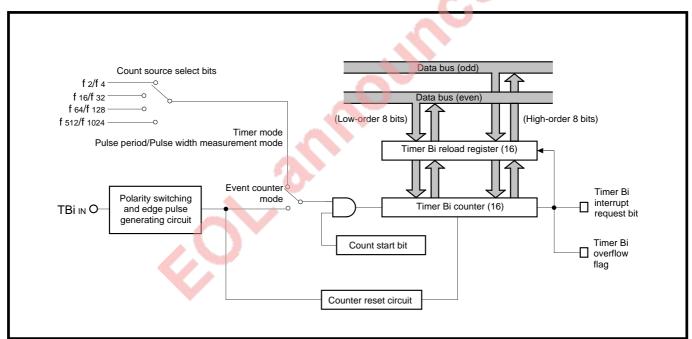

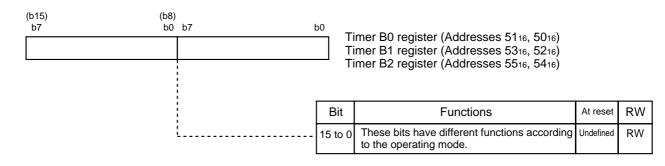

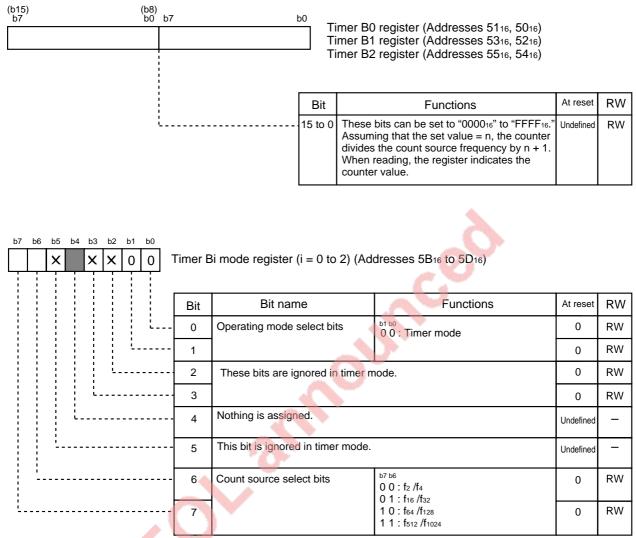

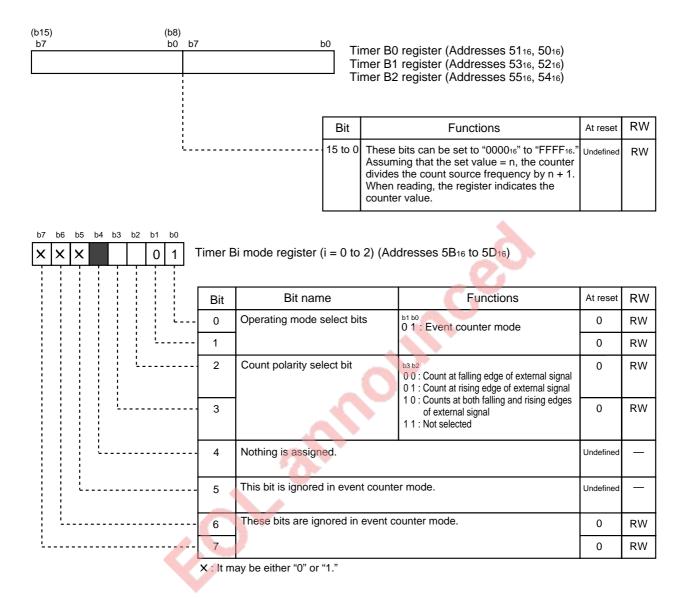

### CHAPTER 6. TIMER B

| 6.1 Overview                                                 | 6-2  |

|--------------------------------------------------------------|------|

| 6.2 Block description                                        | 6-2  |

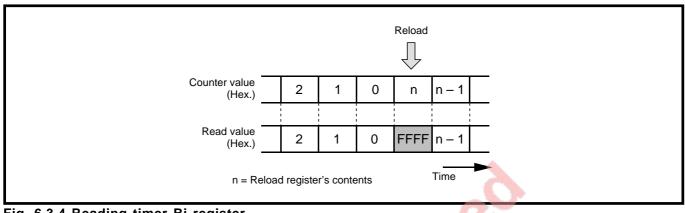

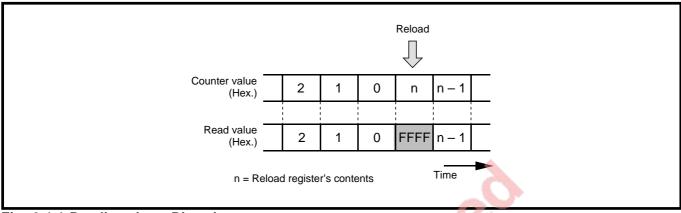

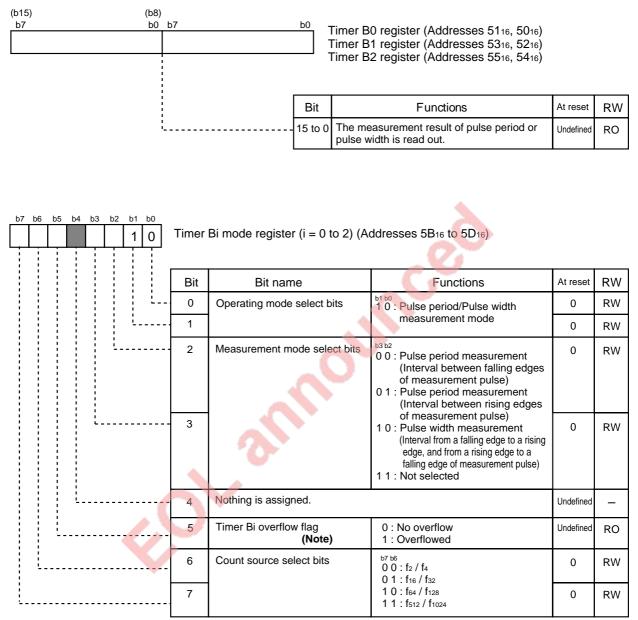

| 6.2.1 Counter and reload register (timer Bi register)        | 6-3  |

| 6.2.2 Count start register                                   | 6-4  |

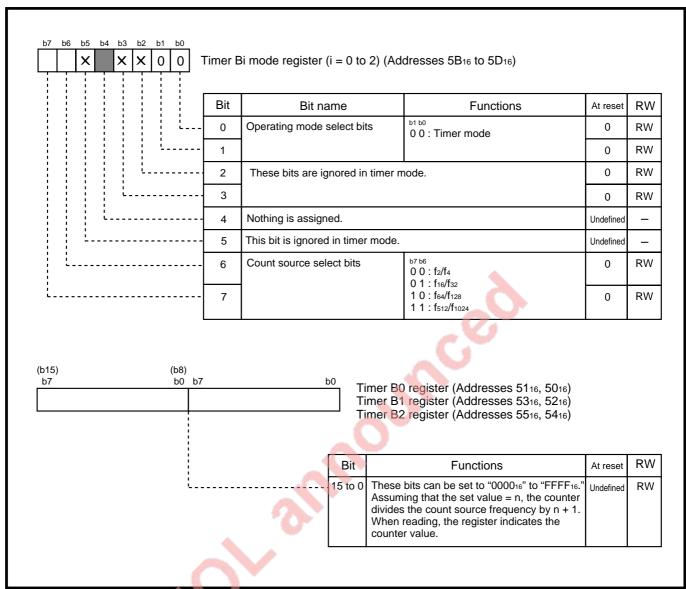

| 6.2.3 Timer Bi mode register                                 | 6-5  |

| 6.2.4 Timer Bi interrupt control register                    | 6-6  |

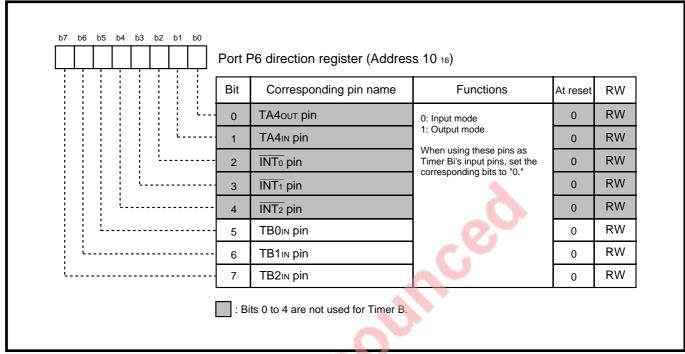

| 6.2.5 Port P6 direction register                             | 6-7  |

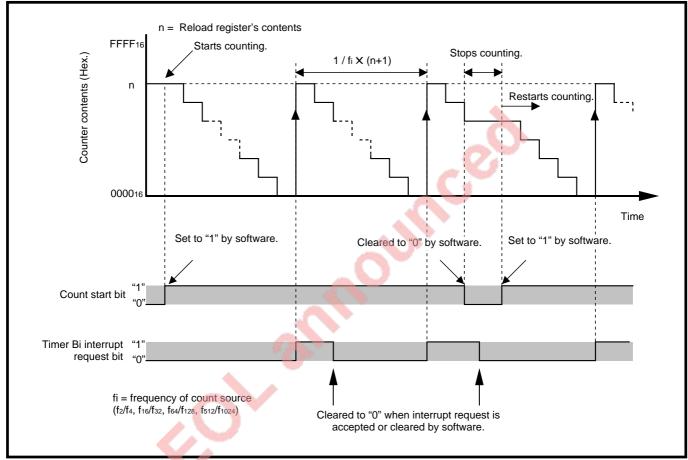

| 6.3 Timer mode                                               | 6-8  |

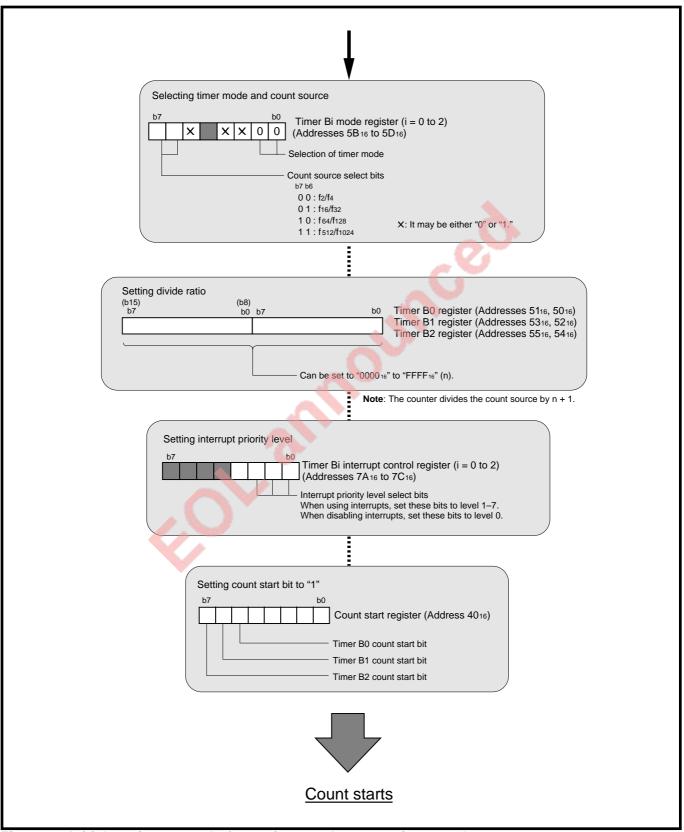

| 6.3.1 Setting for timer mode                                 | 6-10 |

| 6.3.2 Count source                                           | 6-11 |

| 6.3.3 Operation in timer mode                                | 6-12 |

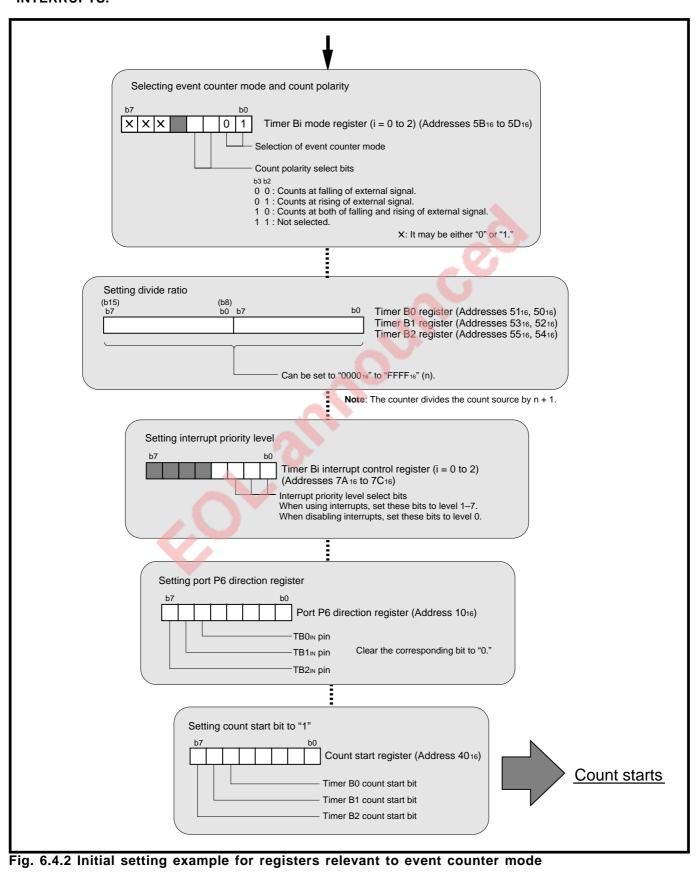

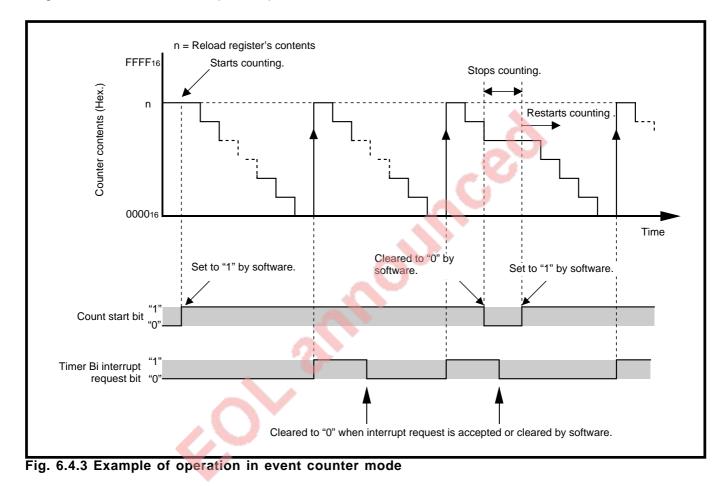

| 6.4 Event counter mode                                       | 6-14 |

| 6.4.1 Setting for event counter mode                         | 6-16 |

| 6.4.2 Operation in event counter mode                        |      |

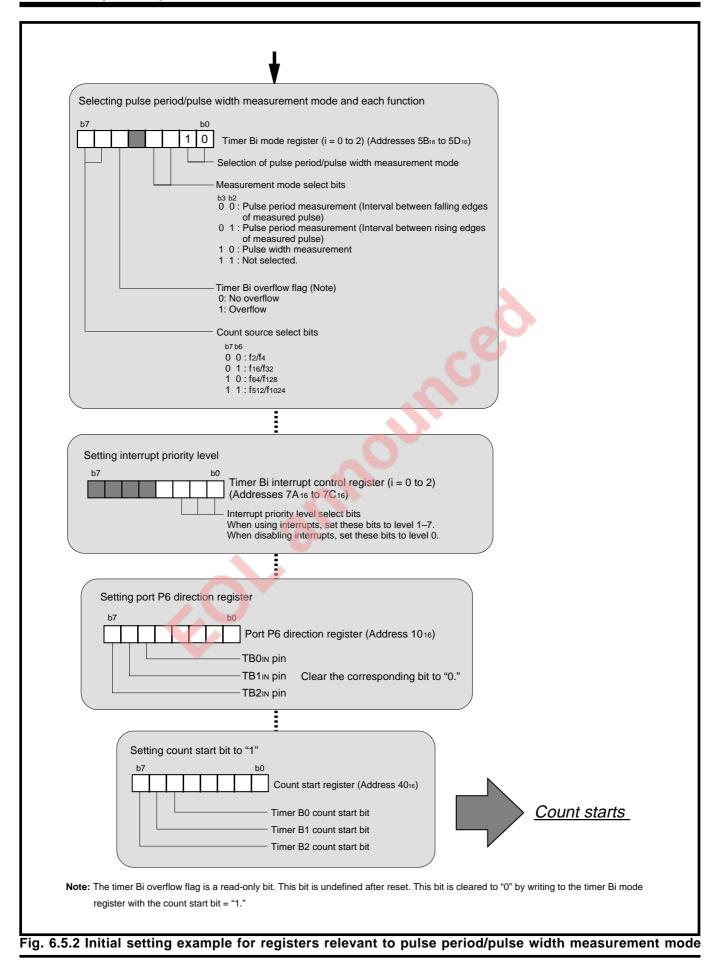

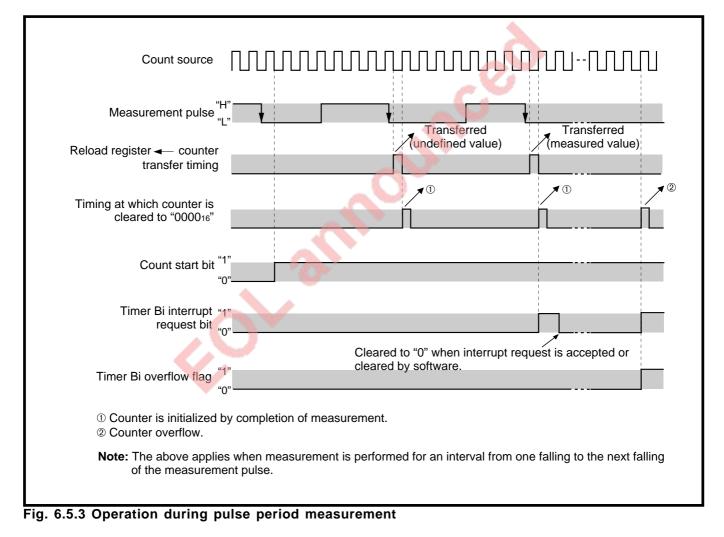

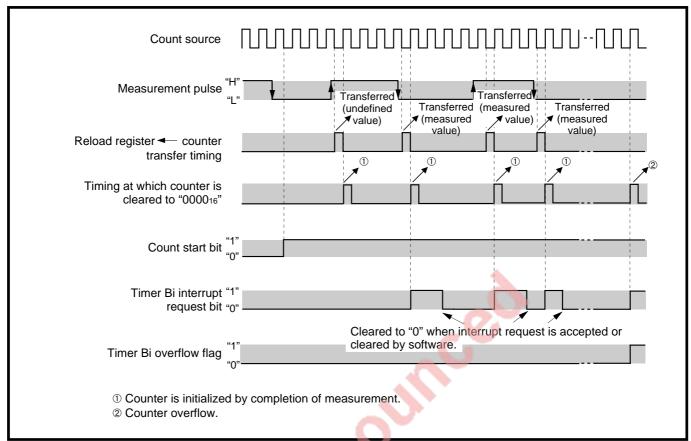

| 6.5 Pulse period/pulse width measurement mode                | 6-19 |

| 6.5.1 Setting for pulse period/pulse width measurement mode  | 6-21 |

| 6.5.2 Count source                                           | 6-23 |

| 6.5.3 Operation in pulse period/pulse width measurement mode | 6-24 |

|                                                              |      |

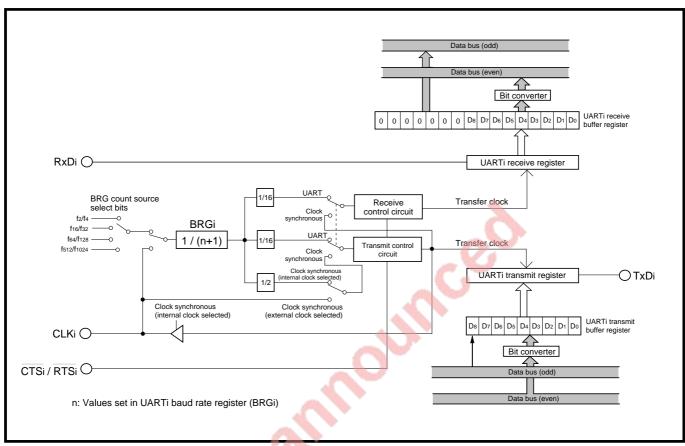

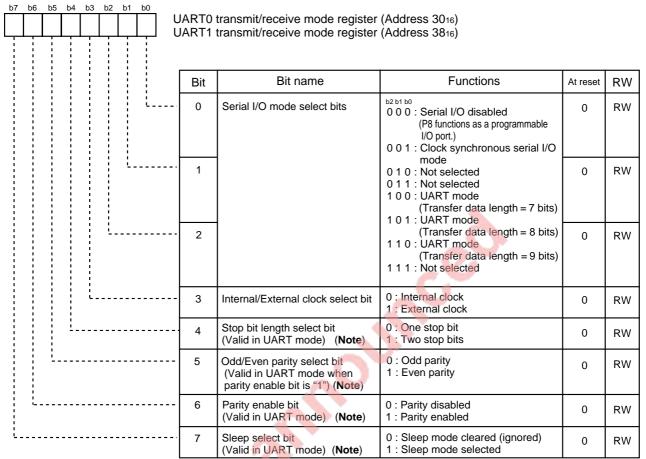

## CHAPTER 7. SERIAL I/O

| 7.1 Overview                                                                         |        |

|--------------------------------------------------------------------------------------|--------|

| 7.2 Block description                                                                | 7-3    |

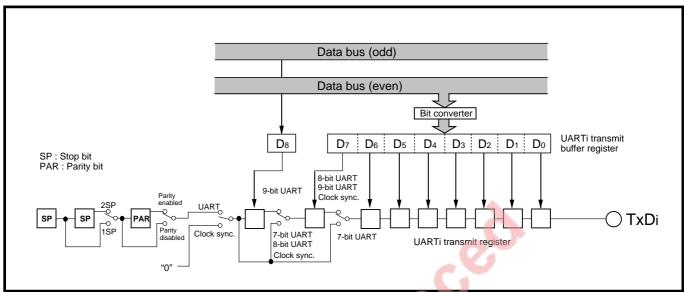

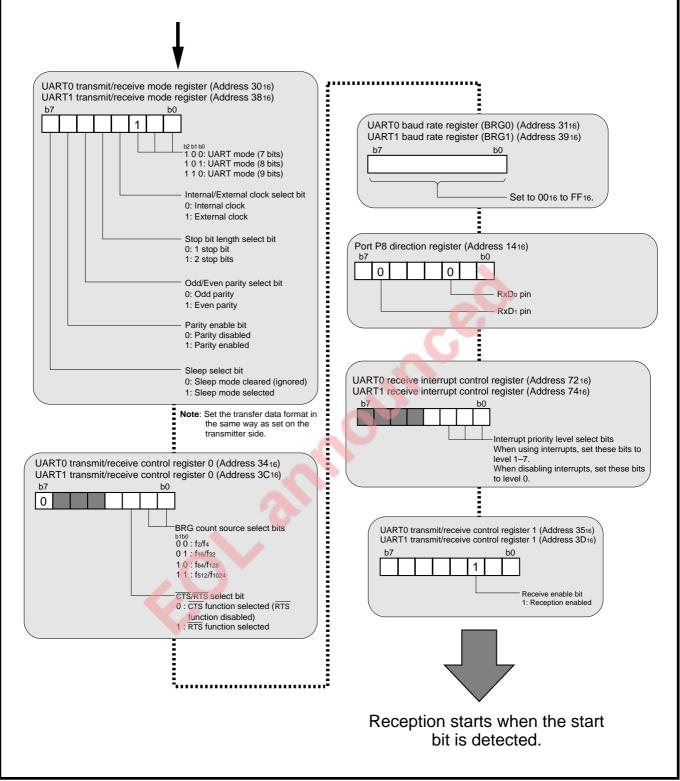

| 7.2.1 UARTi transmit/receive mode register                                           | 7-4    |

| 7.2.2 UARTi transmit/receive control register 0                                      | 7-6    |

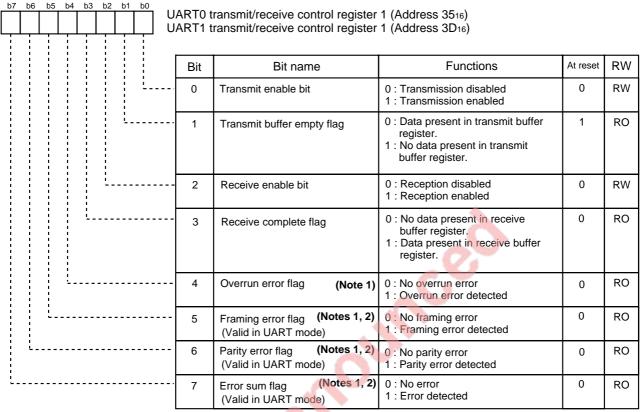

| 7.2.3 UARTi transmit/receive control register 1                                      |        |

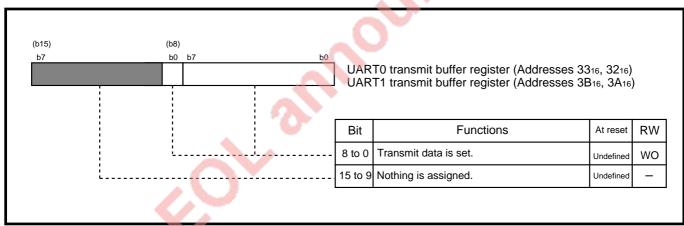

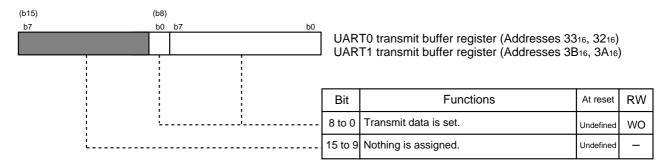

| 7.2.4 UARTi transmit register and UARTi transmit buffer register                     |        |

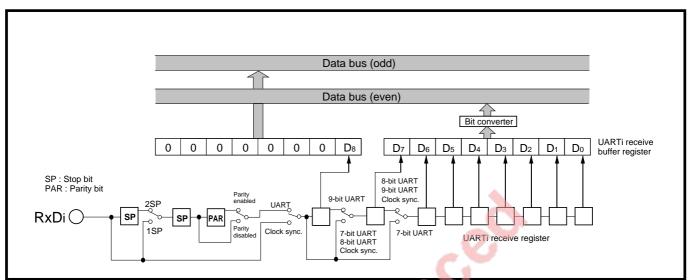

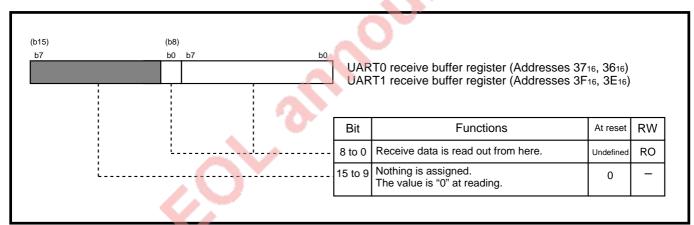

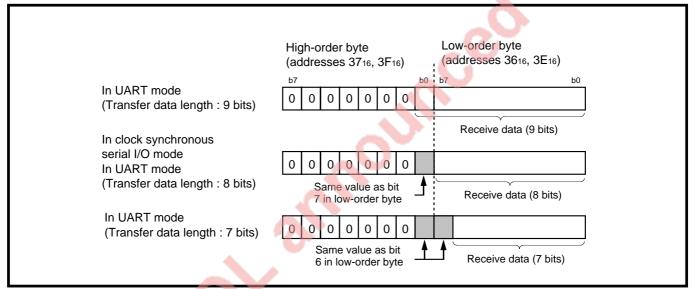

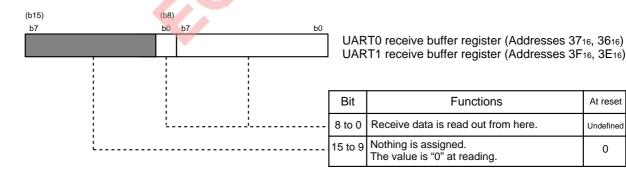

| 7.2.5 UARTi receive register and UARTi receive buffer register                       |        |

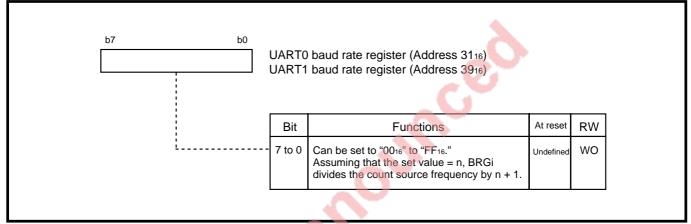

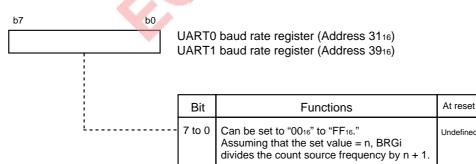

| 7.2.6 UARTi baud rate register (BRGi)                                                | . 7-13 |

| 7.2.7 UARTi transmit interrupt control and UARTi receive interrupt control registers |        |

| 7.2.8 Port P8 direction register                                                     |        |

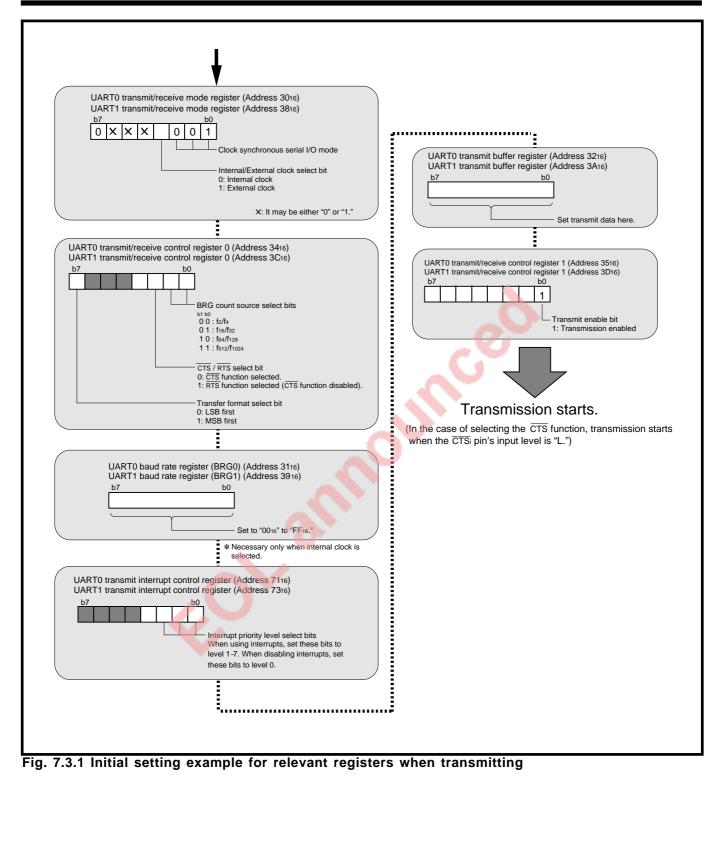

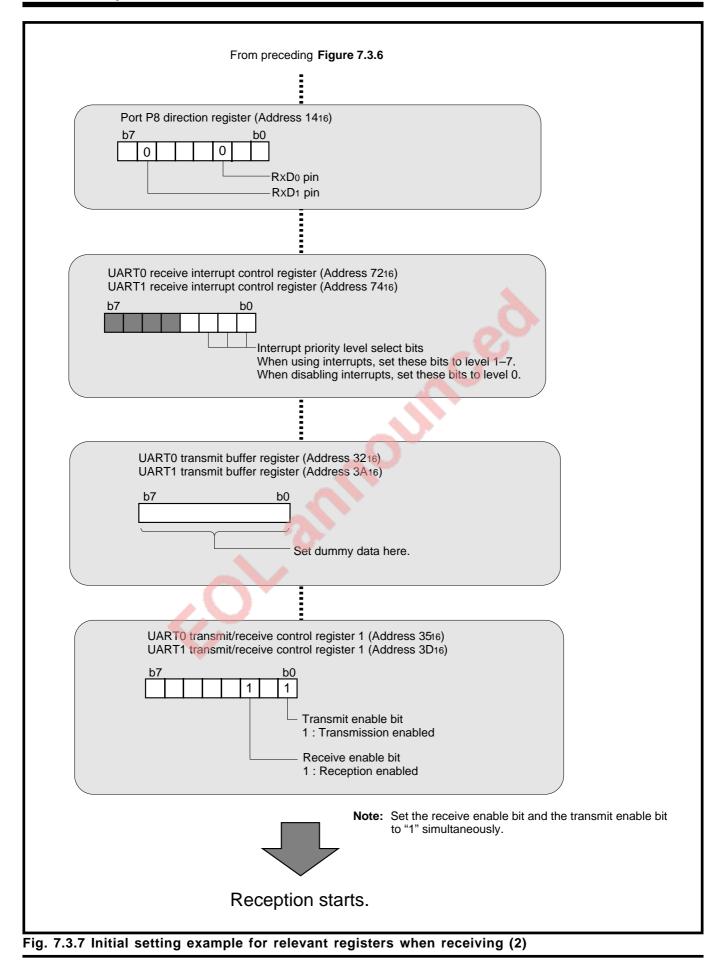

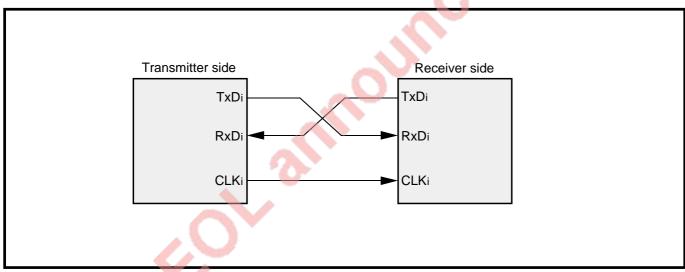

| 7.3 Clock synchronous serial I/O mode                                                |        |

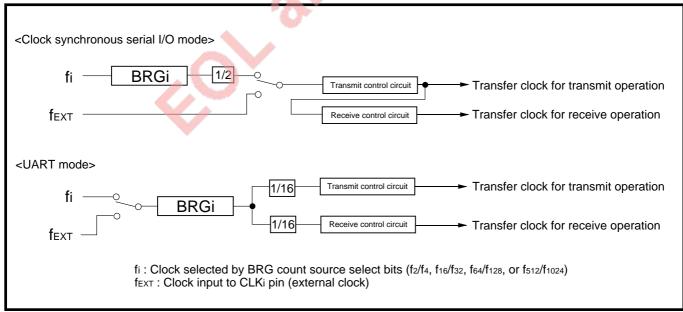

| 7.3.1 Transfer clock (synchronizing clock)                                           |        |

| 7.3.2 Transfer data format                                                           |        |

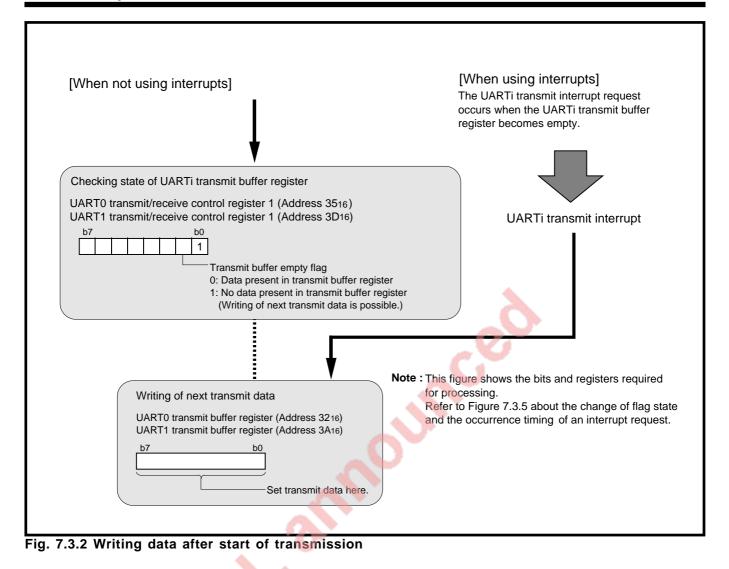

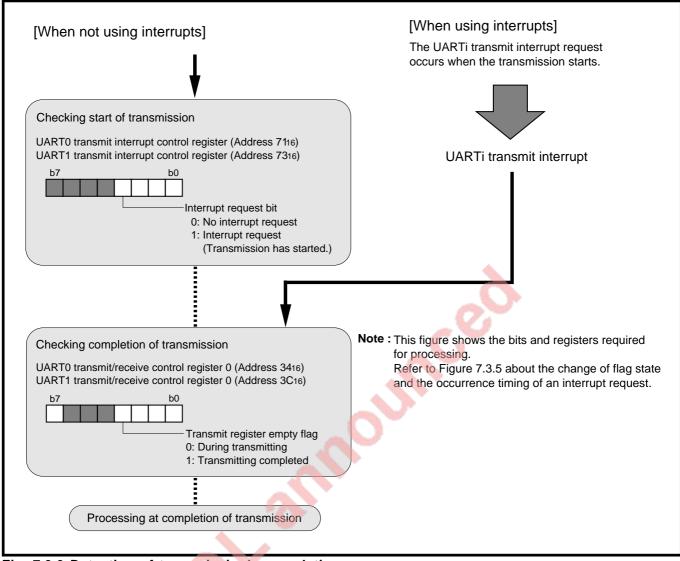

| 7.3.3 Method of transmission                                                         |        |

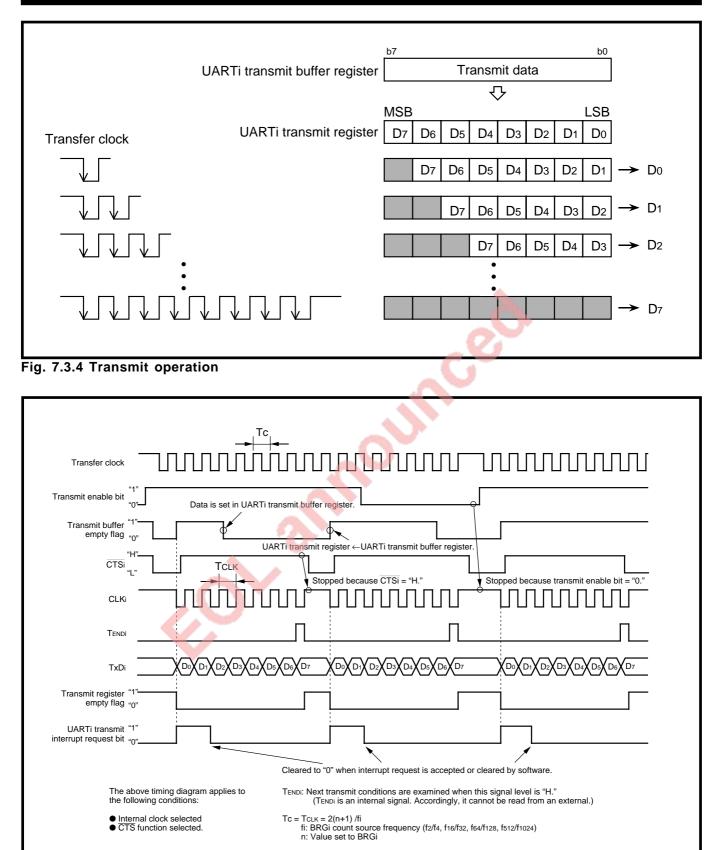

| 7.3.4 Transmit operation                                                             |        |

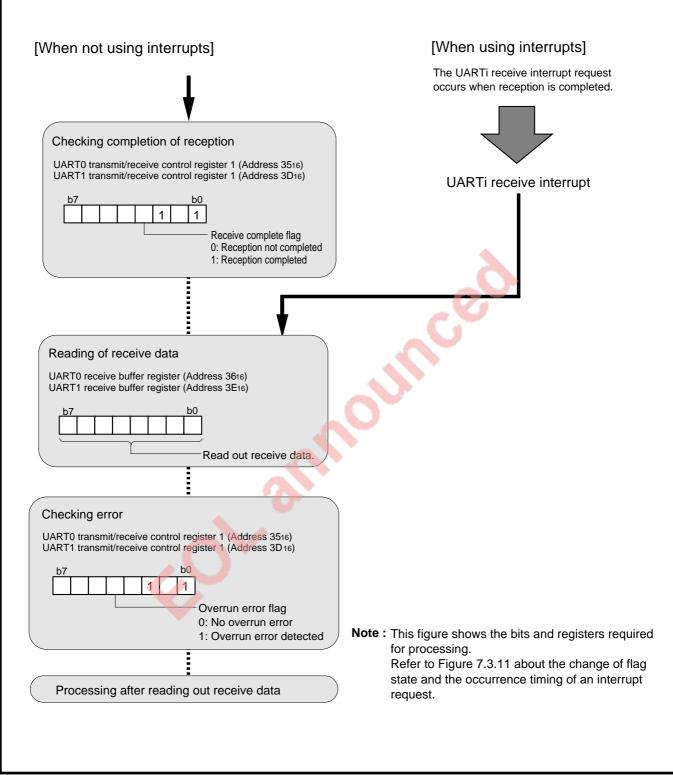

| 7.3.5 Method of reception                                                            |        |

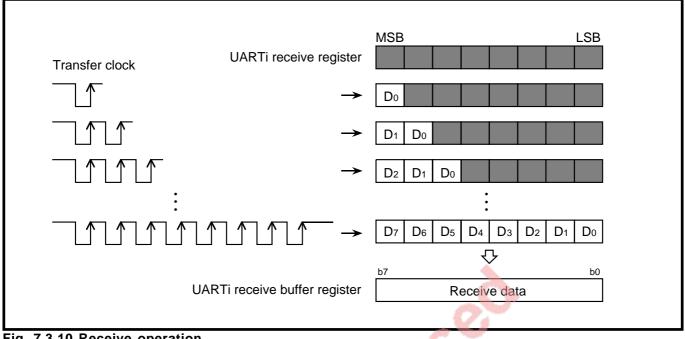

| 7.3.6 Receive operation                                                              |        |

| 7.3.7 Process on detecting overrun error                                             |        |

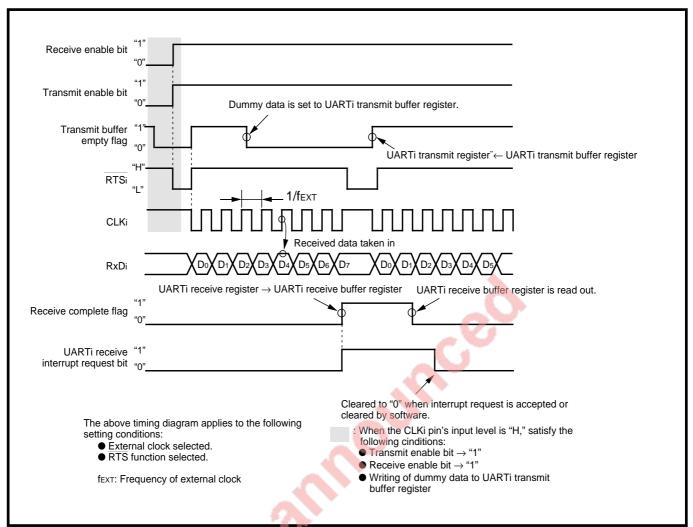

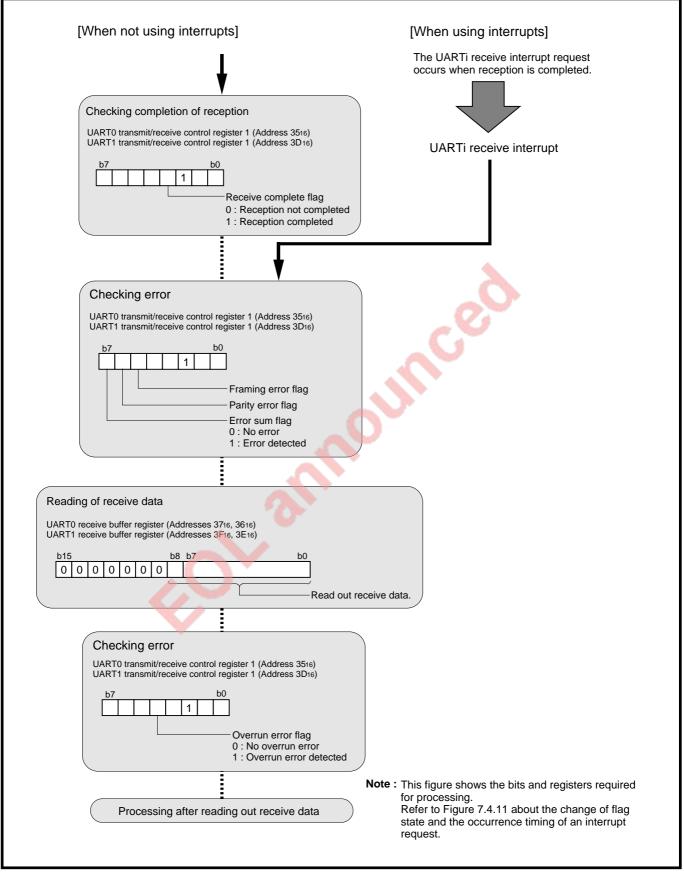

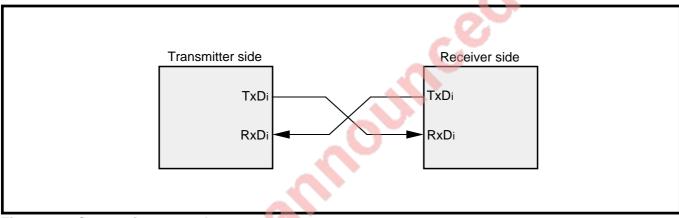

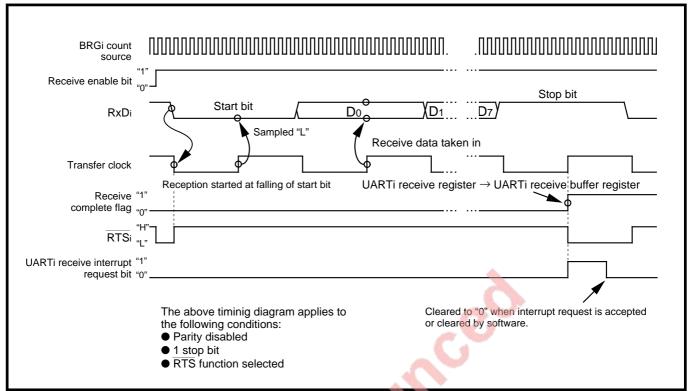

| 7.4 Clock asynchronous serial I/O (UART) mode                                        |        |

| 7.4.1 Transfer rate (frequency of transfer clock)                                    |        |

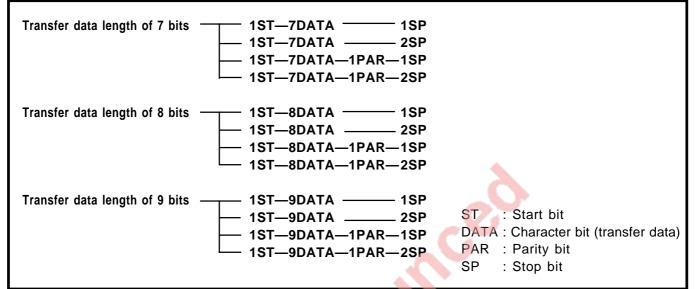

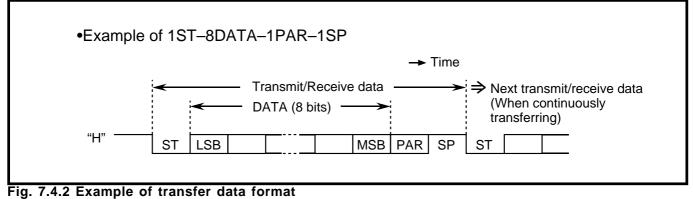

| 7.4.2 Transfer data format                                                           |        |

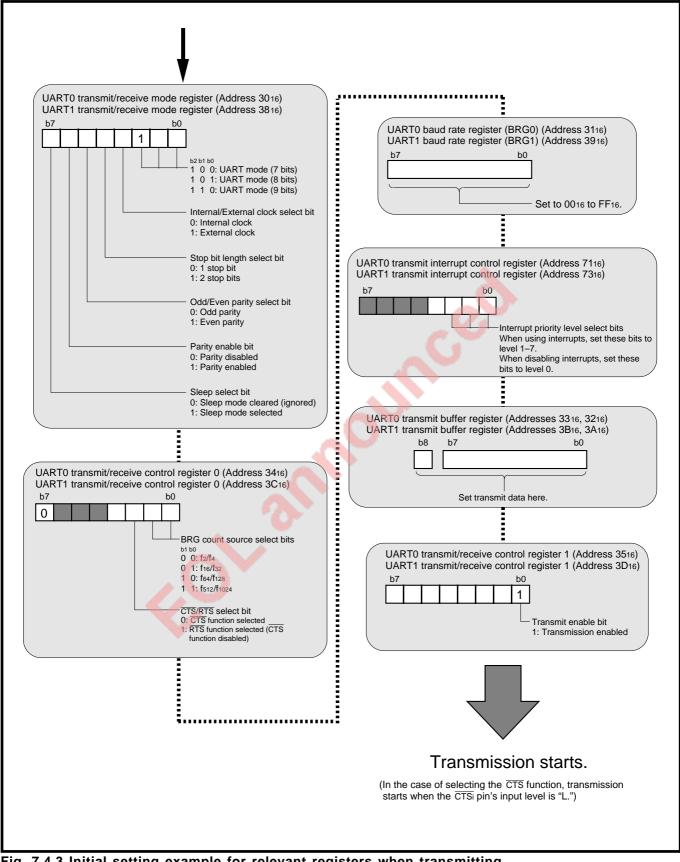

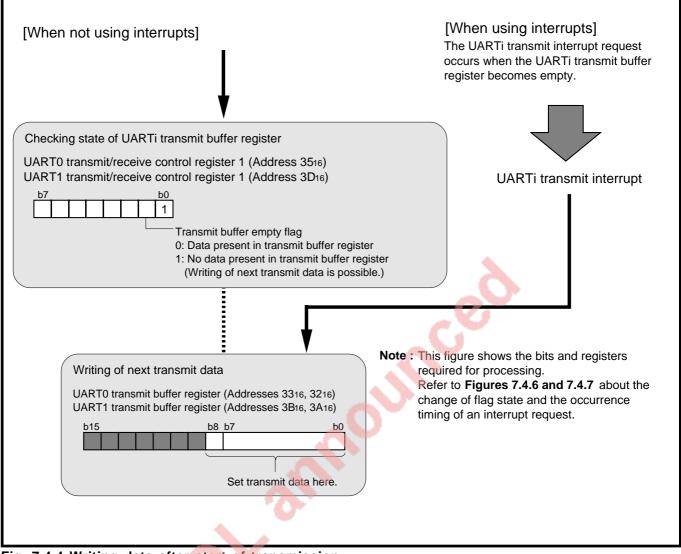

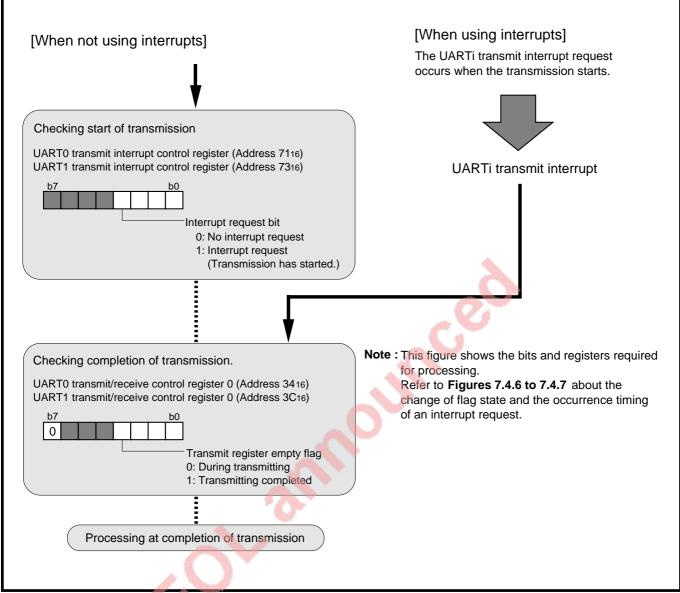

| 7.4.3 Method of transmission                                                         | -      |

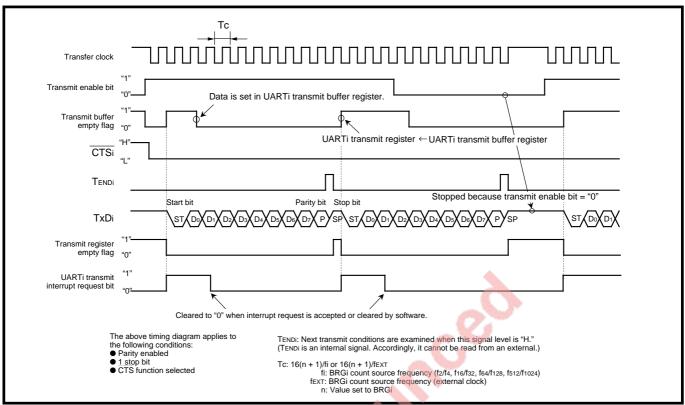

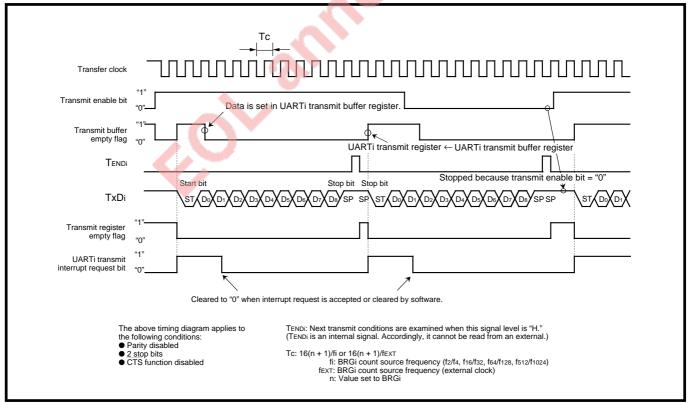

| 7.4.4 Transmit operation                                                             |        |

| 7.4.5 Method of reception                                                            |        |

| 7.4.6 Receive operation                                                              |        |

| 7.4.7 Process on detecting error                                                     |        |

| 7.4.8 Sleep mode                                                                     | . 7-52 |

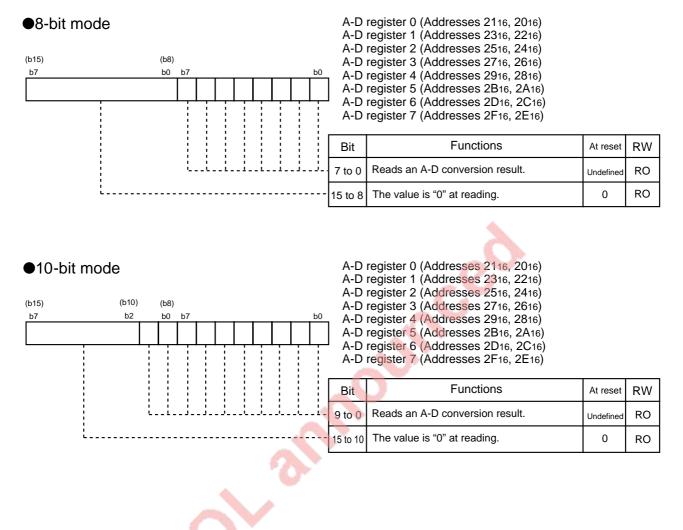

#### CHAPTER 8. A-D CONVERTER

| 8.1 Overview                                                           | 8-2  |

|------------------------------------------------------------------------|------|

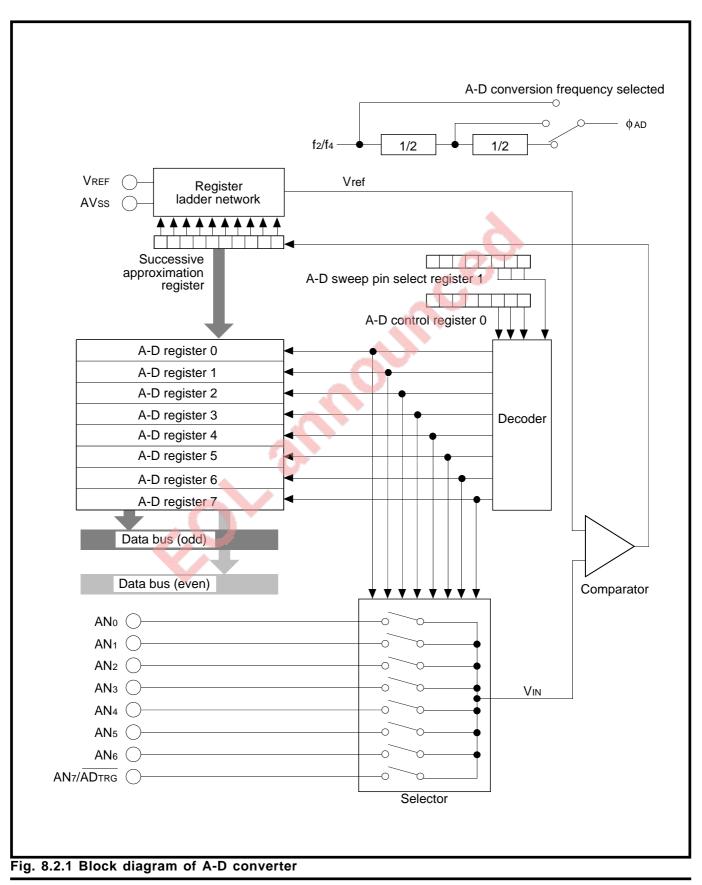

| 8.2 Block description                                                  | 8-3  |

| 8.2.1 A-D control register 0                                           | 8-4  |

| 8.2.2 A-D control register 1                                           | 8-6  |

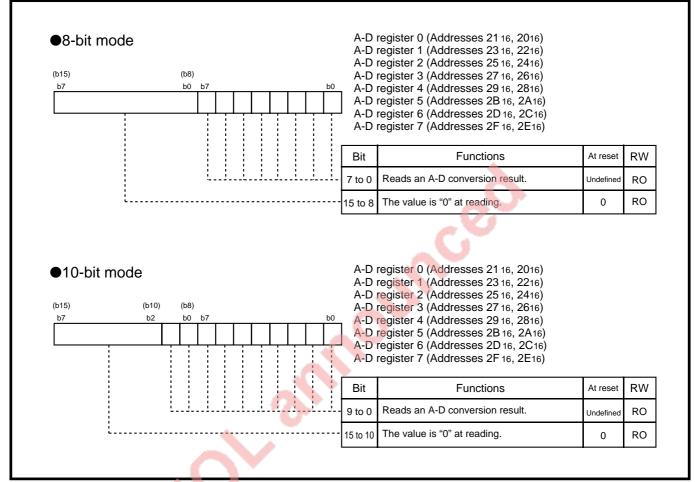

| 8.2.3 A-D register i (i = 0 to 7)                                      | 8-7  |

| 8.2.4 A-D conversion interrupt control register                        | 8-8  |

| 8.2.5 Port P7 direction register                                       | 8-9  |

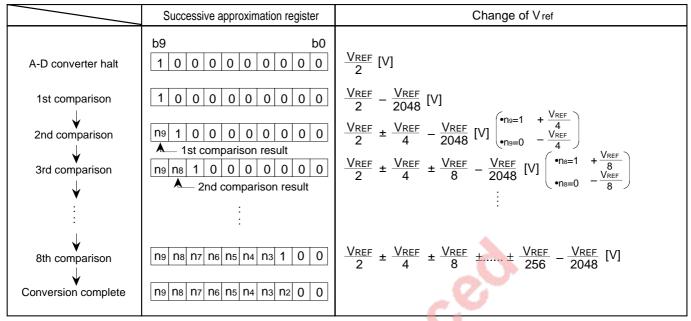

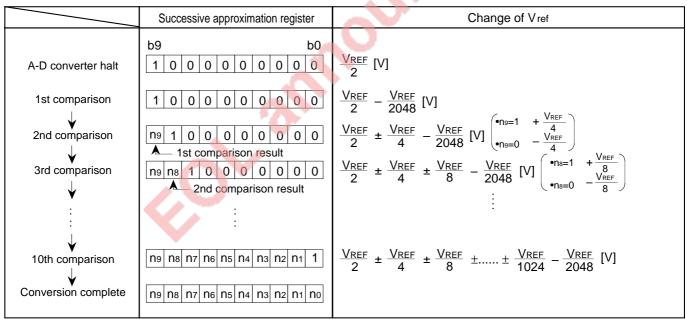

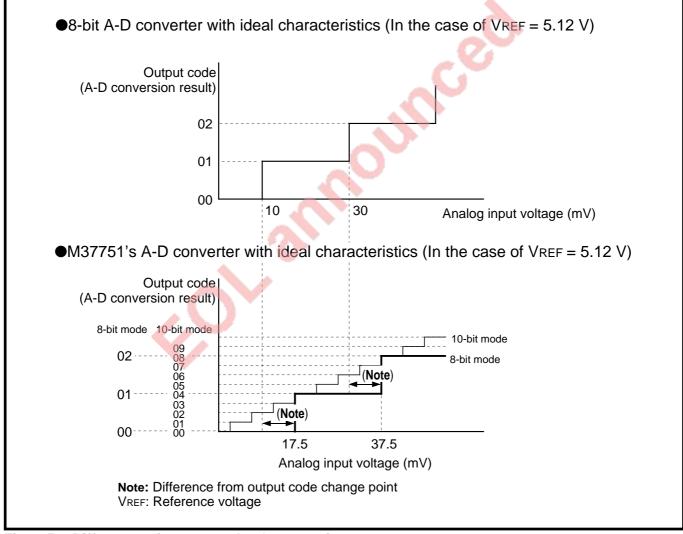

| 8.3 A-D conversion method (successive approximation conversion method) | 8-10 |

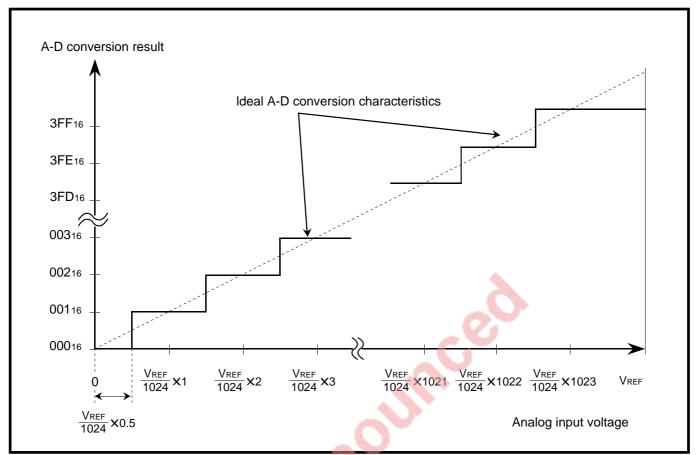

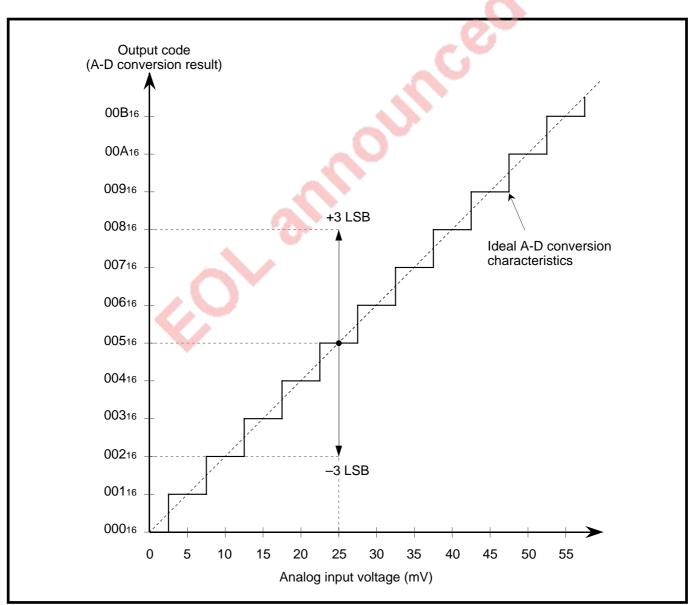

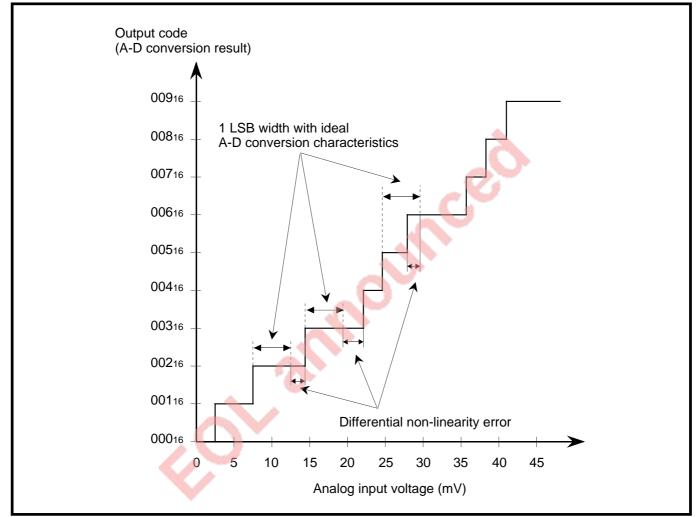

| 8.4 Absolute accuracy and differential non-linearity error             | 8-13 |

| 8.4.1 Absolute accuracy                                                | 8-13 |

| 8.4.2 Differential non-linearity error                                 | 8-14 |

| 8.5 Comparison voltage in 8-bit mode                                   | 8-15 |

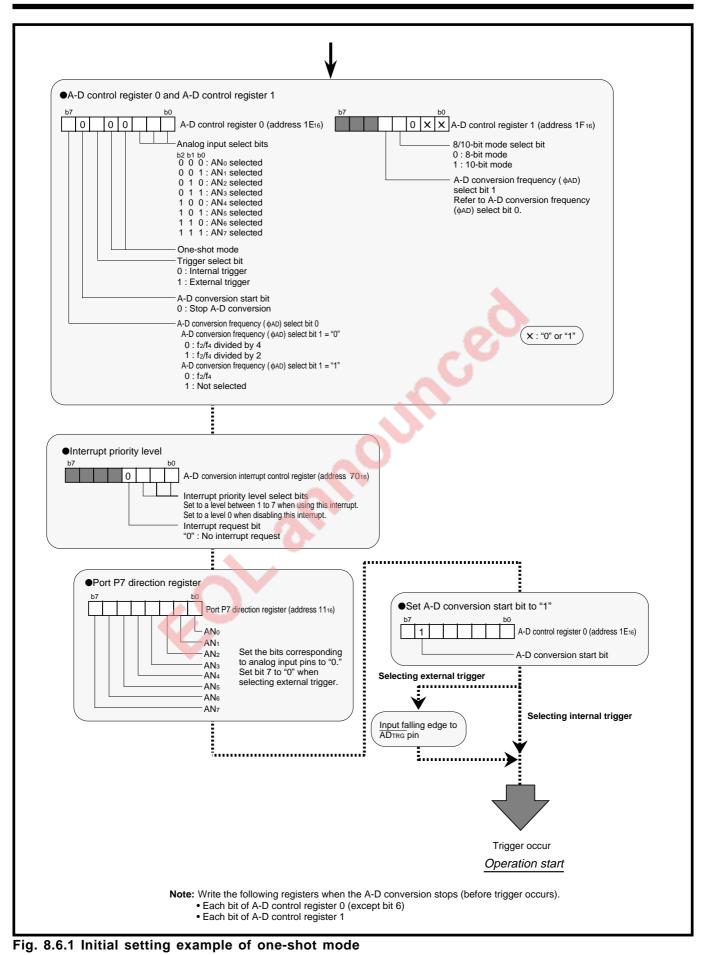

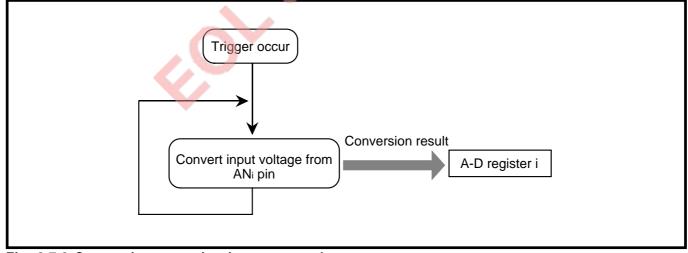

| 8.6 One-shot mode                                                      | 8-16 |

| 8.6.1 Settings for one-shot mode                                       |      |

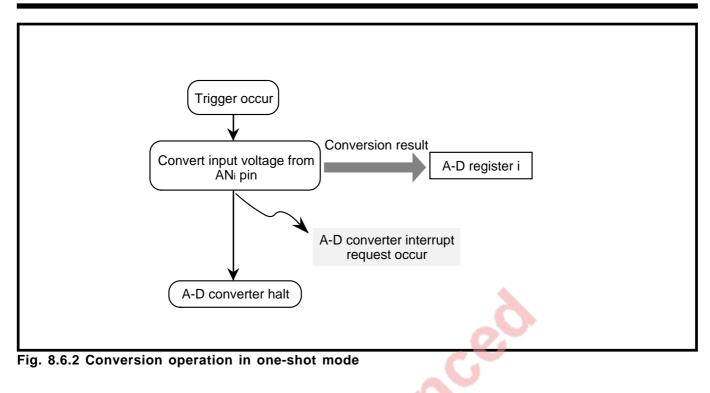

| 8.6.2 One-shot mode operation description                              | 8-18 |

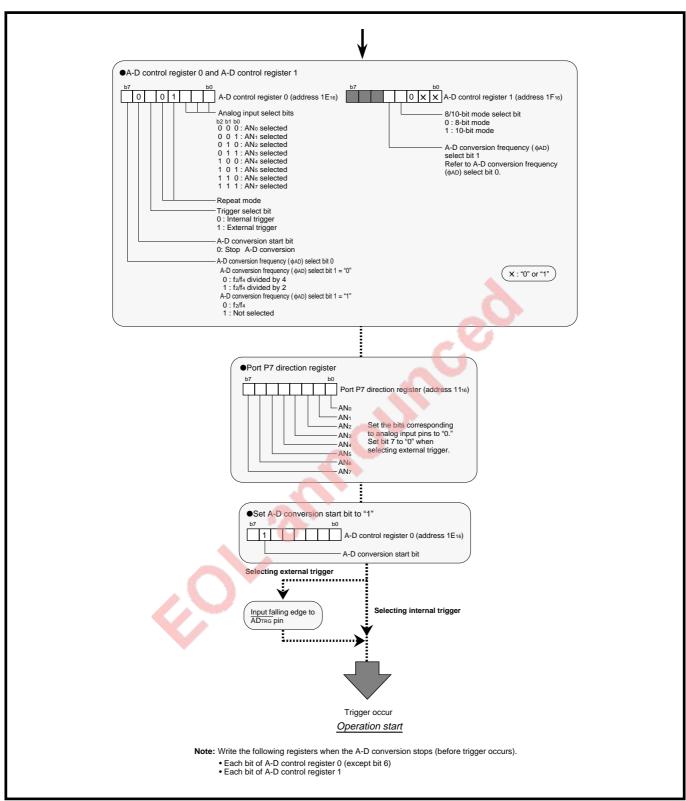

| 8.7 Repeat mode                                                        |      |

| 8.7.1 Settings for repeat mode                                         |      |

| 8.7.2 Repeat mode operation description                                | 8-22 |

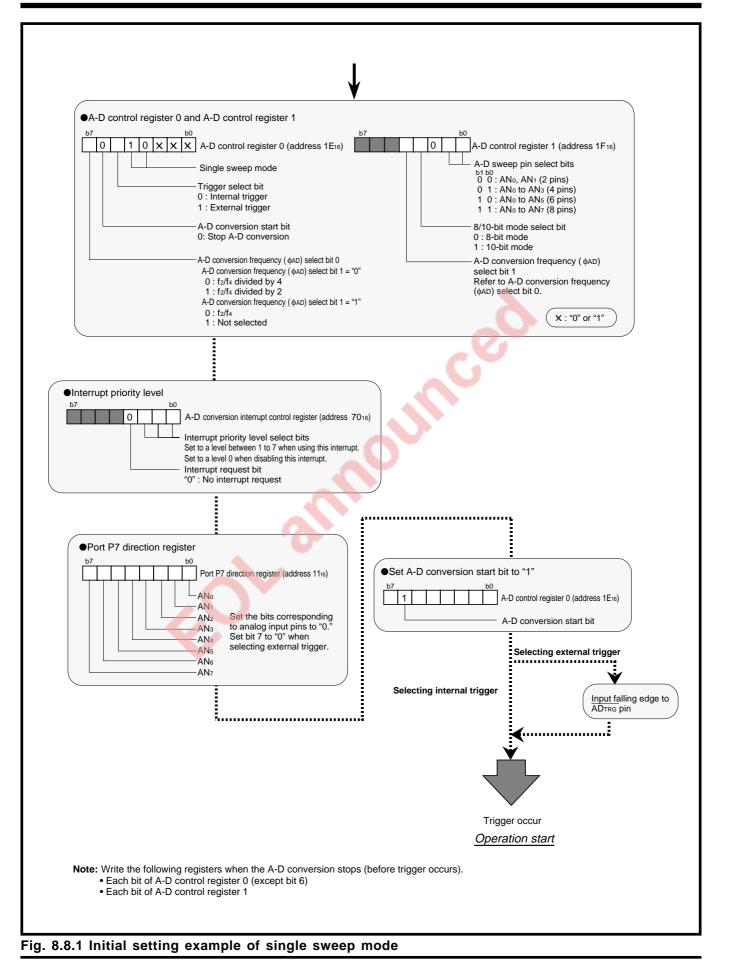

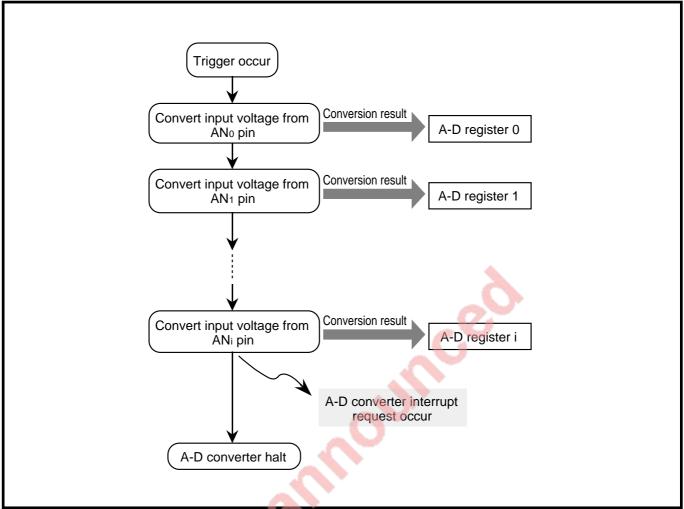

| 8.8 Single sweep mode                                                  |      |

| 8.8.1 Settings for single sweep mode                                   | 8-23 |

| 8.8.2 Single sweep mode operation description                          |      |

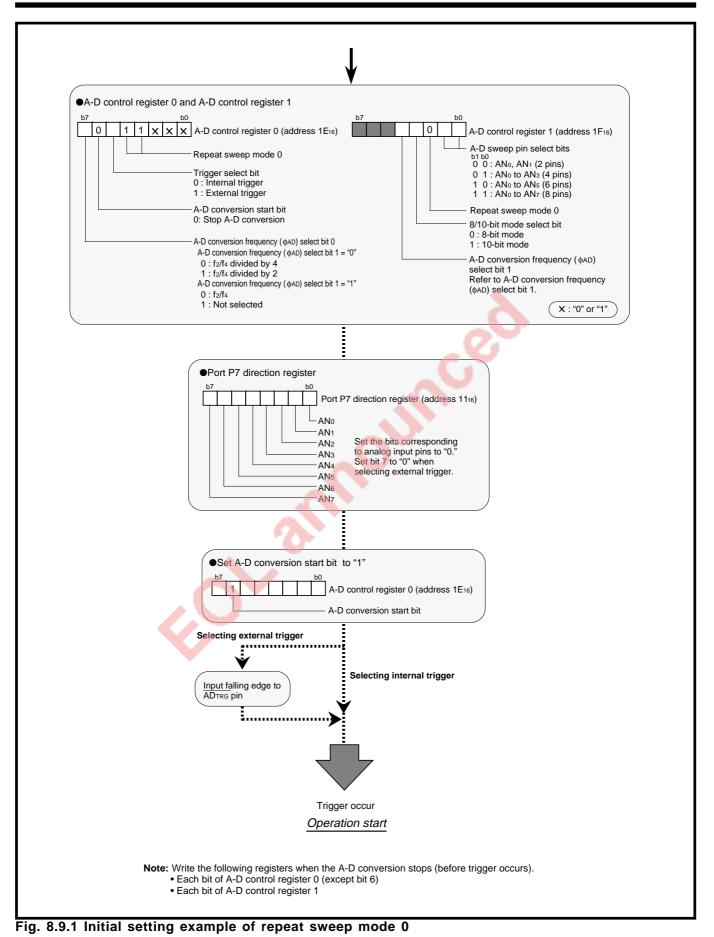

| 8.9 Repeat sweep mode 0                                                |      |

| 8.9.1 Settings for repeat sweep mode 0                                 |      |

| 8.9.2 Repeat sweep mode 0 operation description                        |      |

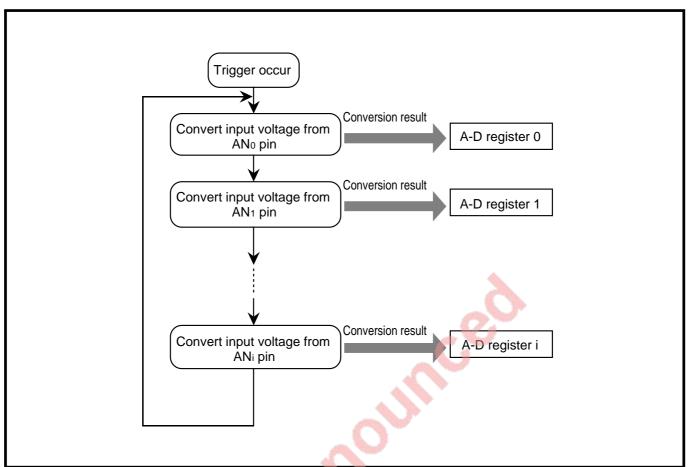

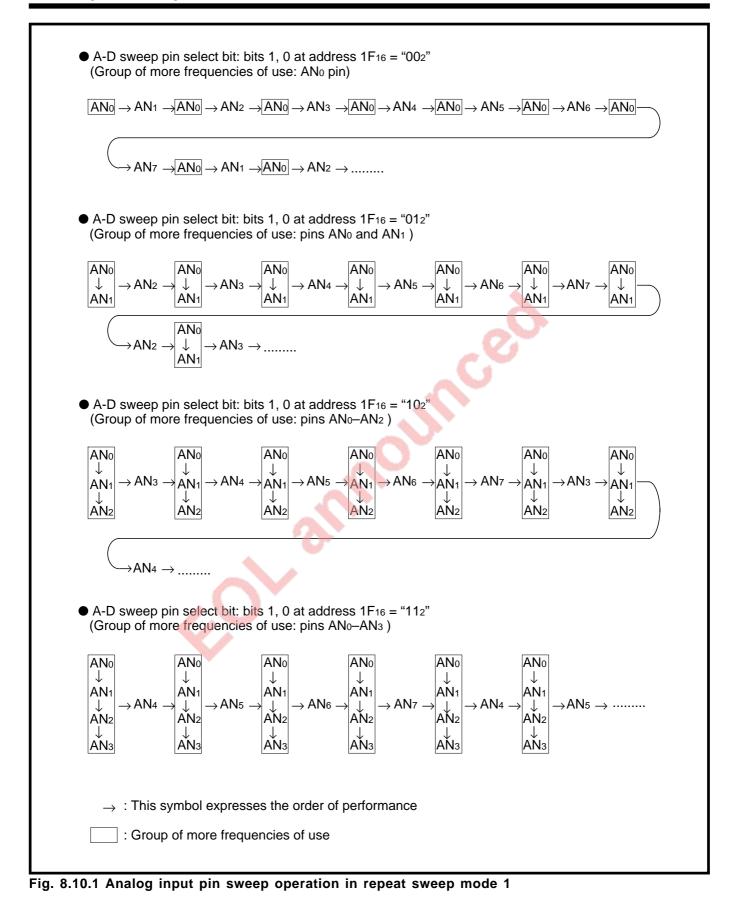

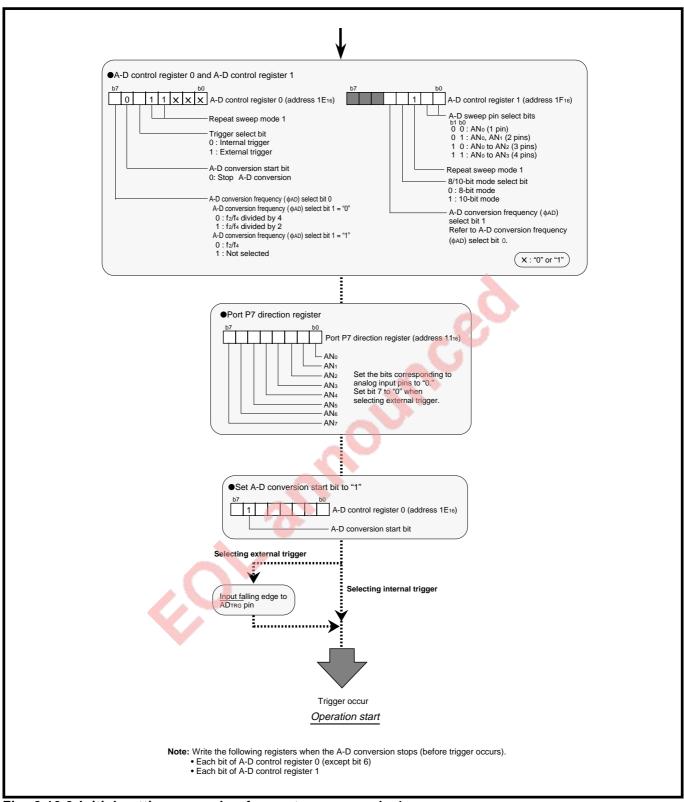

| 8.10 Repeat sweep mode 1                                               | 8-31 |

| 8.10.1 Settings for repeat sweep mode 1                                | 8-31 |

| 8.10.2 Repeat sweep mode 1 operation description                       | 8-34 |

## CHAPTER 9. WATCHDOG TIMER

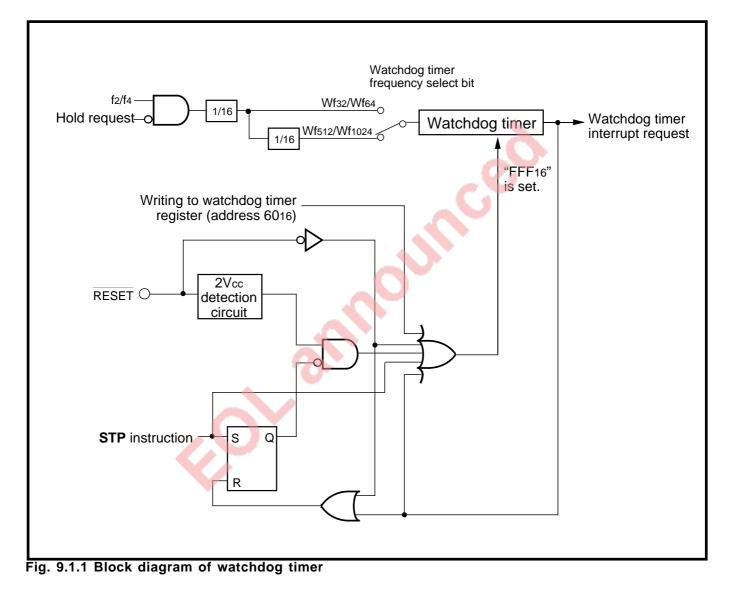

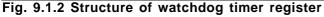

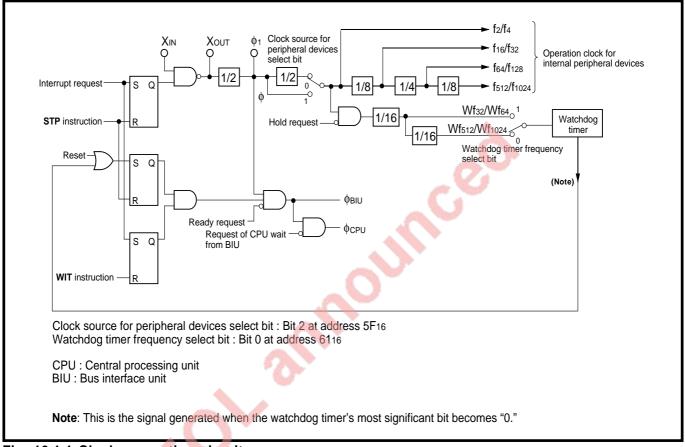

| 9.1 Block description                          | 9-2 |

|------------------------------------------------|-----|

| 9.1.1 Watchdog timer                           |     |

| 9.1.2 Watchdog timer frequency select register |     |

| 9.2 Operation description                      |     |

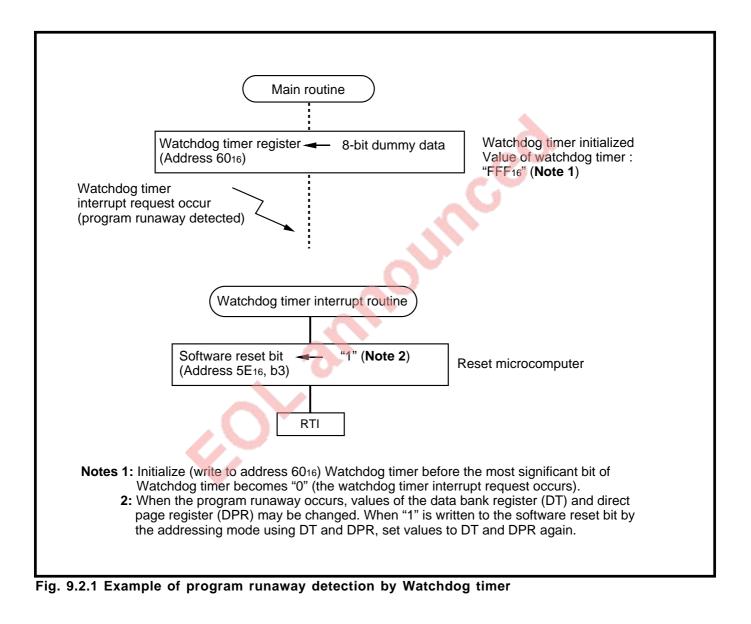

| 9.2.1 Basic operation                          | 9-5 |

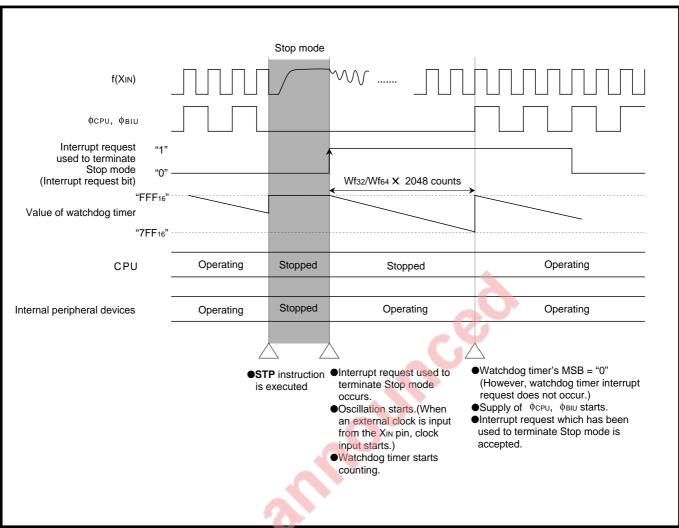

| 9.2.2 Operation in Stop mode                   | 9-7 |

| 9.2.3 Operation in Hold state                  | 9-7 |

| 9.3 Precautions when using watchdog timer      | 9-8 |

## CHAPTER 10. STOP MODE

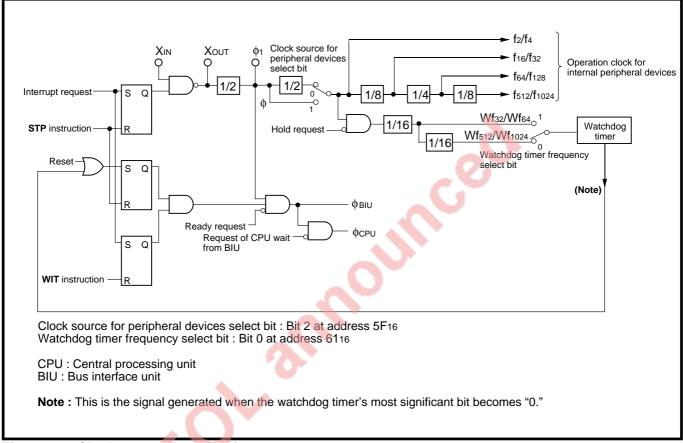

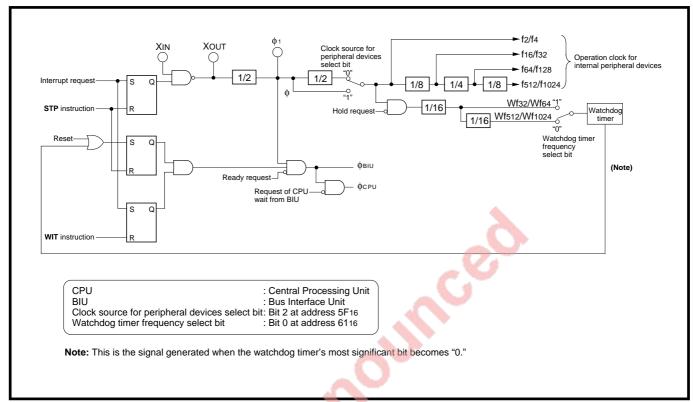

| 10.1 Clock generating circuit                      | 10-2 |

|----------------------------------------------------|------|

| 10.2 Operation description                         |      |

| 10.2.1 Termination by interrupt request occurrence |      |

| 10.2.2 Termination by hardware reset               |      |

| 10.3 Precautions for Stop mode                     | 10-6 |

#### CHAPTER 11. WAIT MODE

| 11.1 Clock generating circuit                      | . 11-2 |

|----------------------------------------------------|--------|

| 11.2 Operation description                         |        |

| 11.2.1 Termination by interrupt request occurrence |        |

| 11.2.2 Termination by hardware reset               |        |

| 11.3 Precautions for Wait mode                     |        |

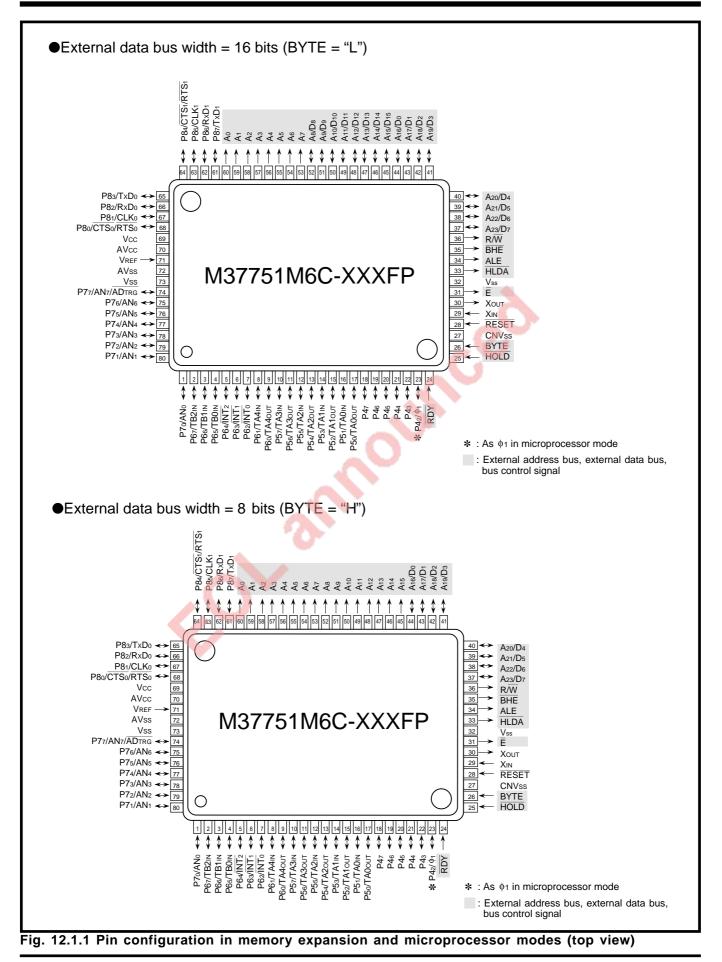

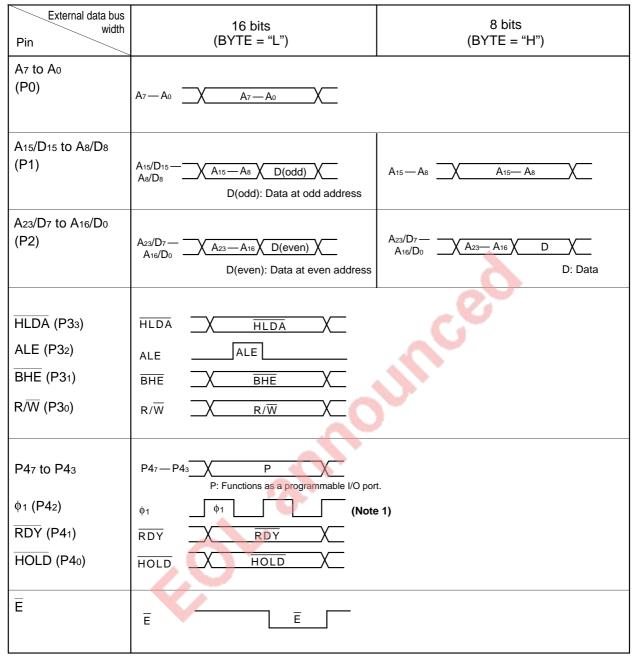

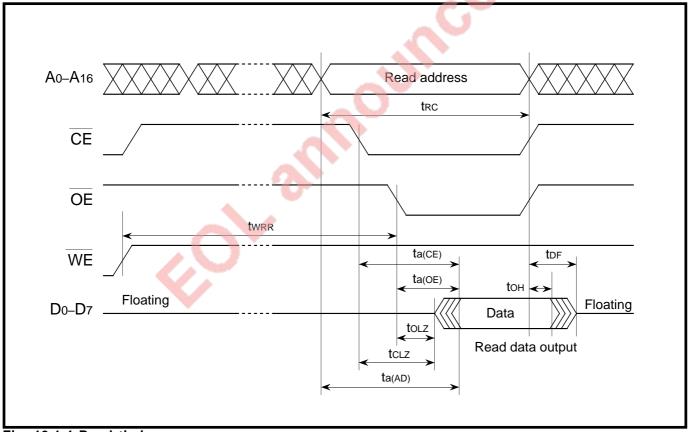

## CHAPTER 12. CONNECTION WITH EXTERNAL DEVICES

| 12.1 Signals required for accessing external devices |       |

|------------------------------------------------------|-------|

| 12.1.1 Descriptions of signals                       |       |

| 12.1.2 Operation of bus interface unit (BIU)         |       |

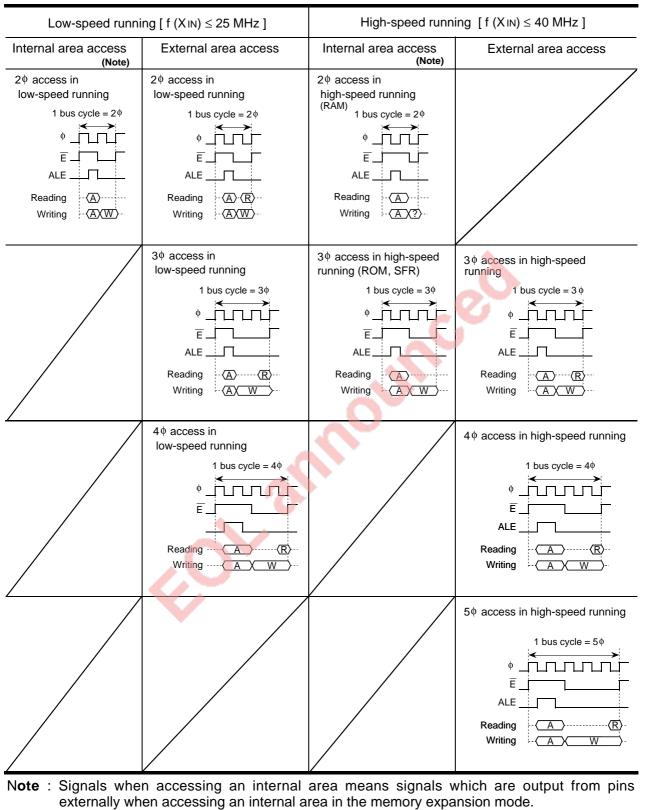

| 12.2 Bus cycle                                       | 12-11 |

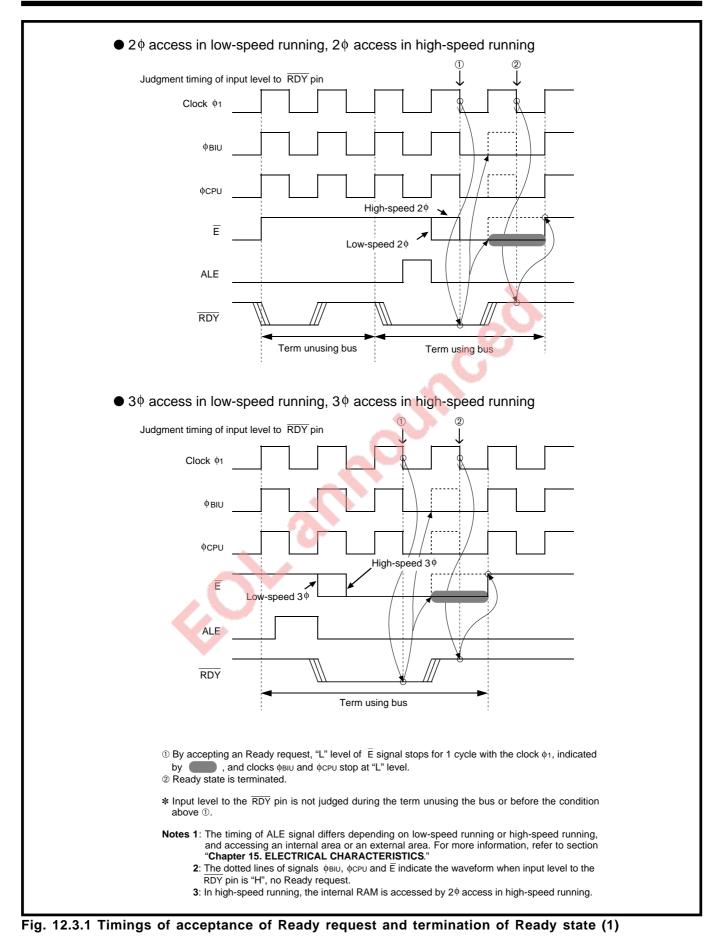

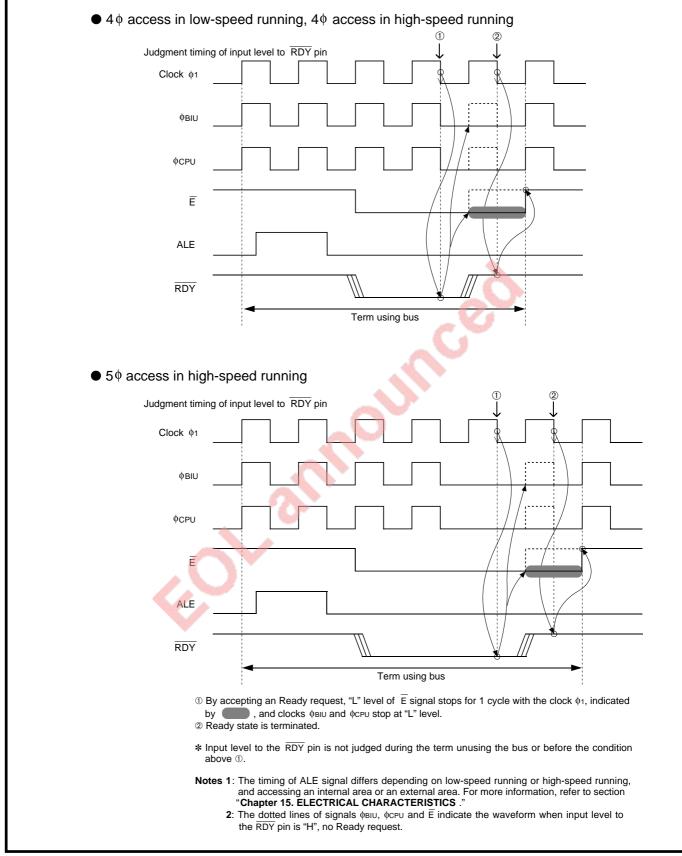

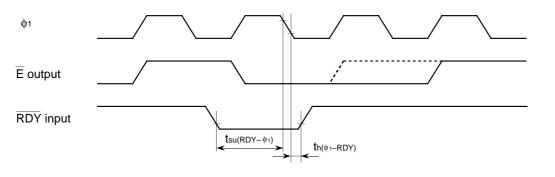

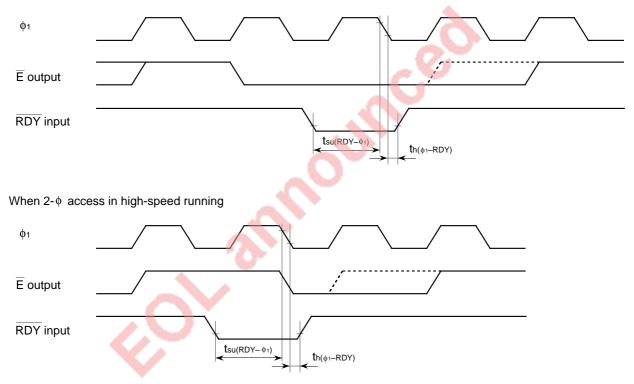

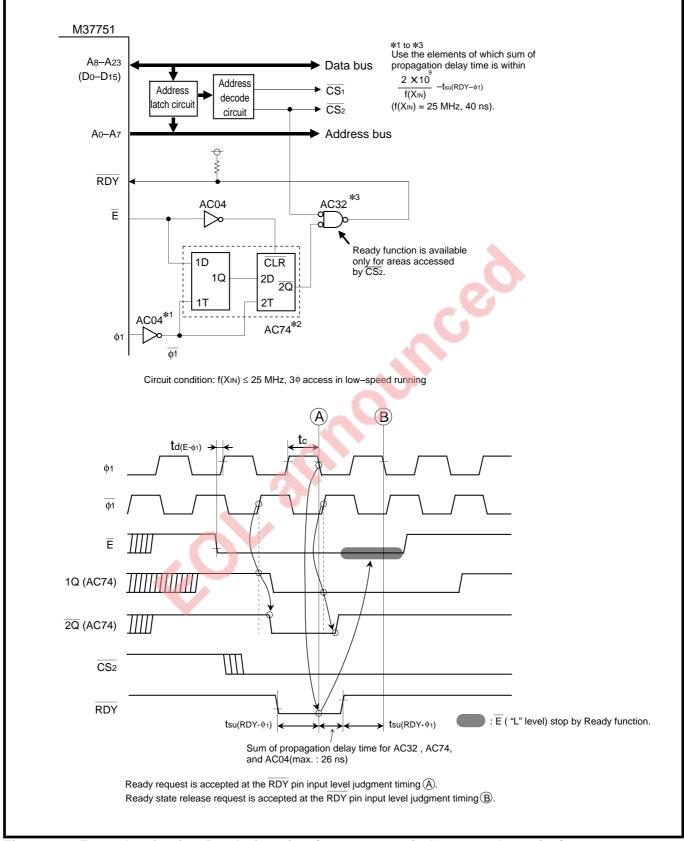

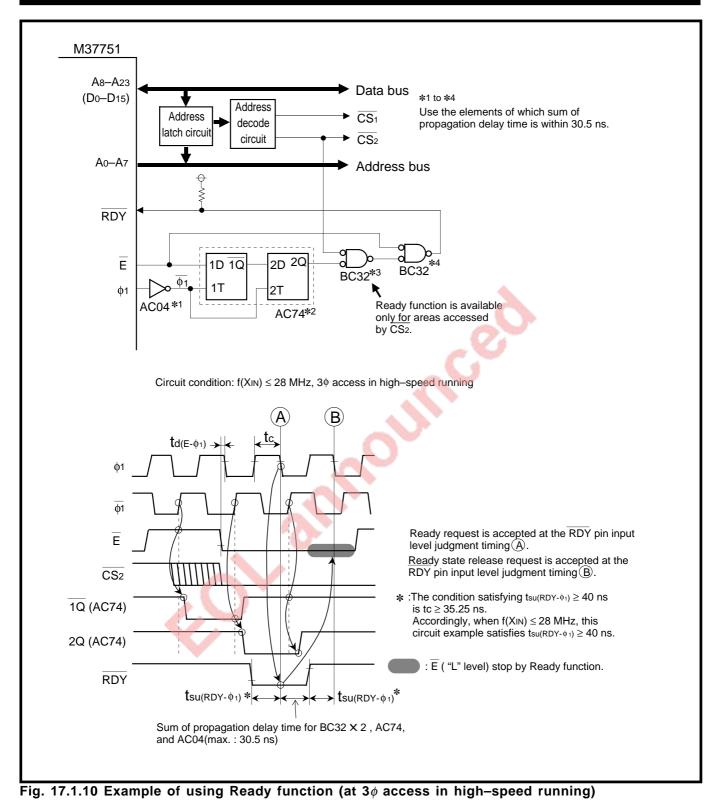

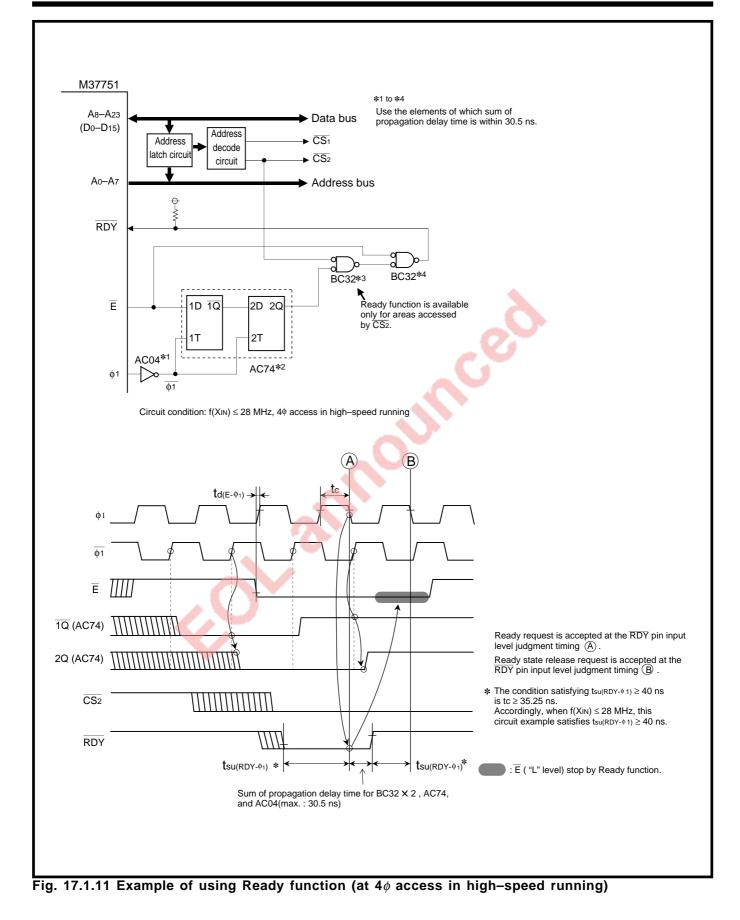

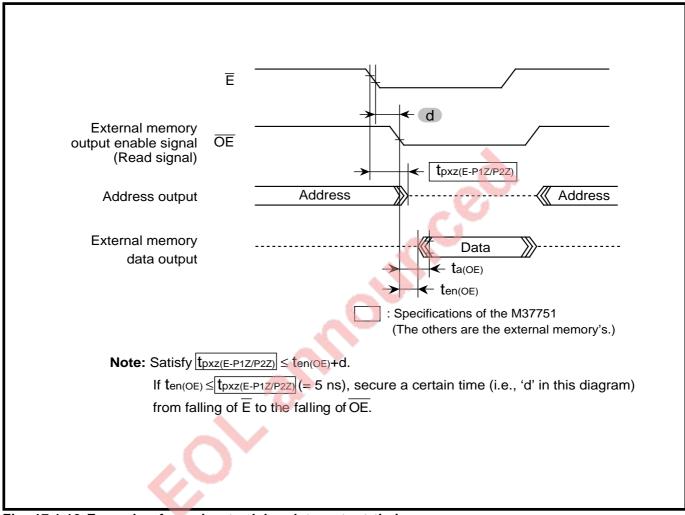

| 12.3 Ready function                                  |       |

| 12.3.1 Operation description                         | 12-15 |

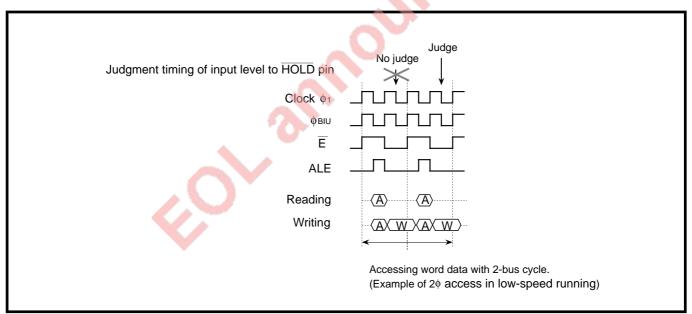

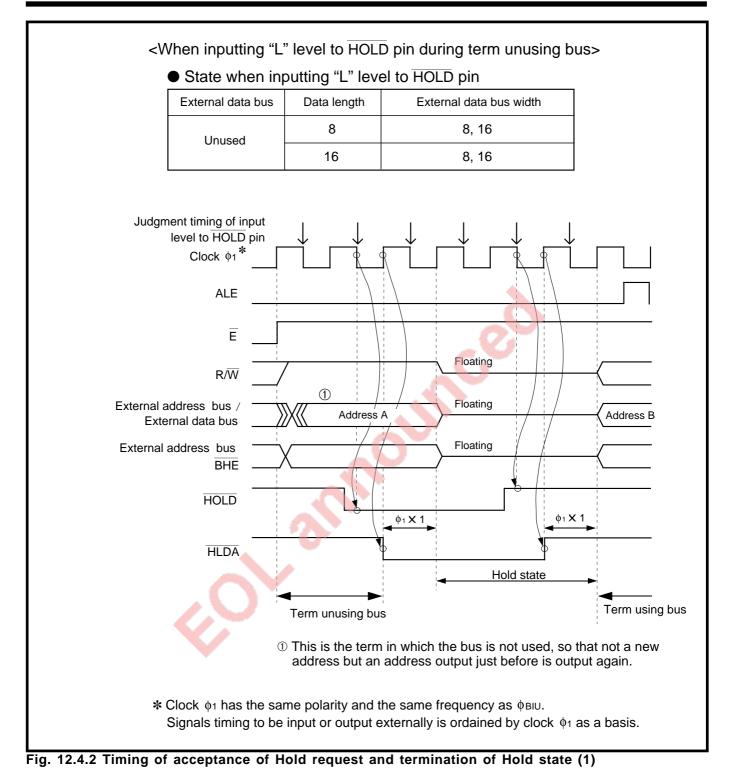

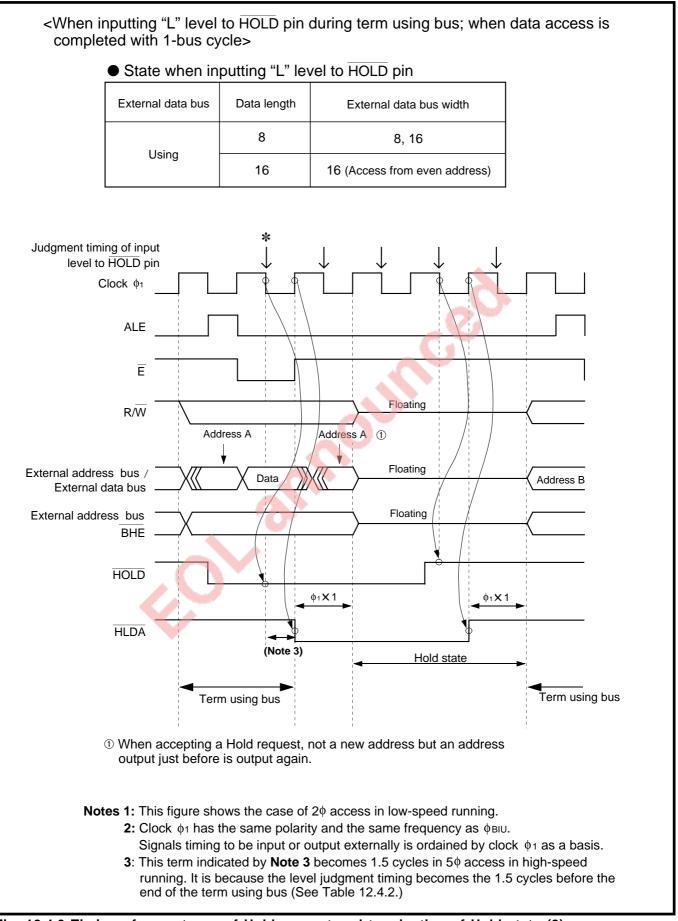

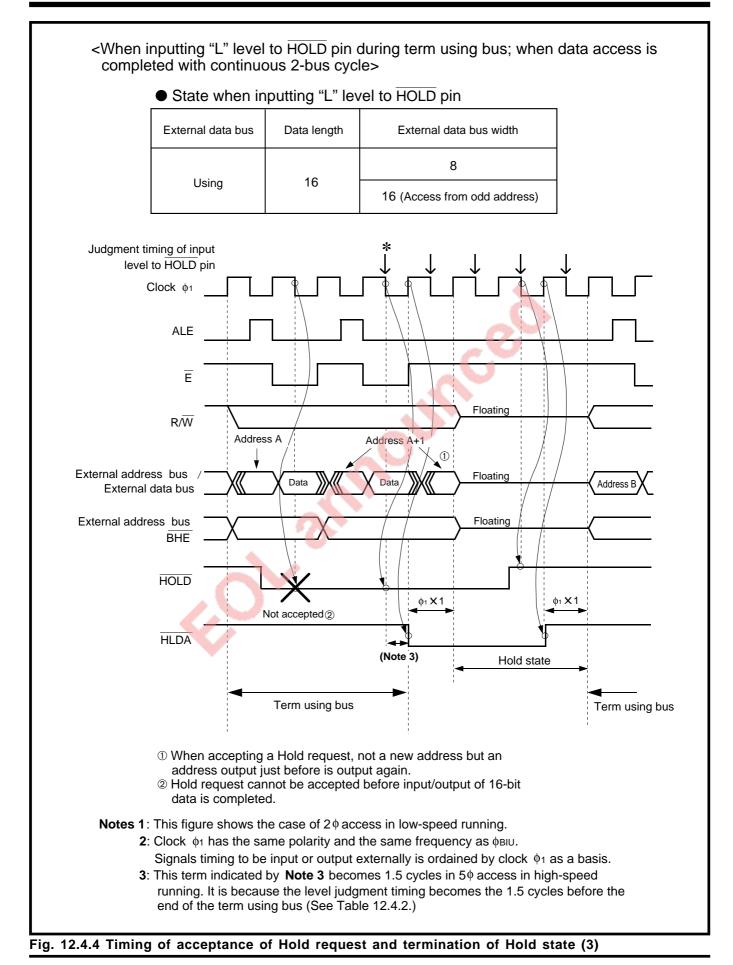

| 12.4 Hold function                                   | 12-18 |

| 12.4.1 Operation description                         | 12-19 |

|                                                      |       |

### CHAPTER 13. RESET

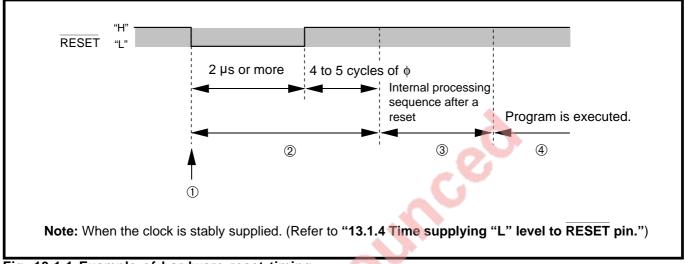

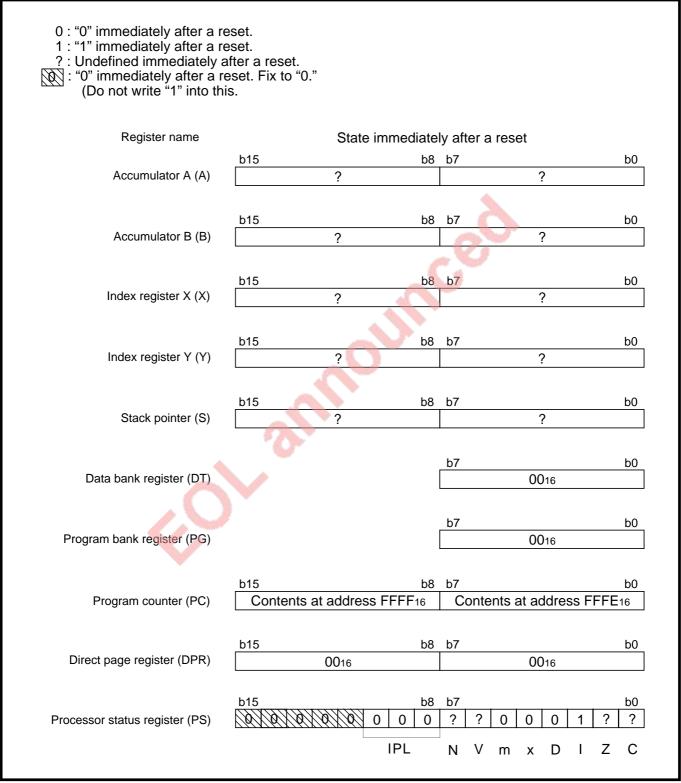

| 13.1 Hardware reset                                  | 13-2 |

|------------------------------------------------------|------|

| 13.1.1 Pin state                                     |      |

| 13.1.2 State of CPU, SFR area, and internal RAM area |      |

| 13.1.3 Internal processing sequence after reset      |      |

| 13.1.4 Time supplying "L" level to RESET pin         |      |

| 13.2 Software reset                                  |      |

## CHAPTER 14. CLOCK GENERATING CIRCUIT

-

| 14.1 Oscillation circuit example                       |      |

|--------------------------------------------------------|------|

| 14.1.1 Connection example using resonator/oscillator   |      |

| 14.1.2 Input example of externally generated clock     |      |

| 14.2 Clock                                             | 14-3 |

| 14.2.1 Clock generated in clock generating circuit     |      |

| 14.2.2 Operation clock for internal peripheral devices |      |

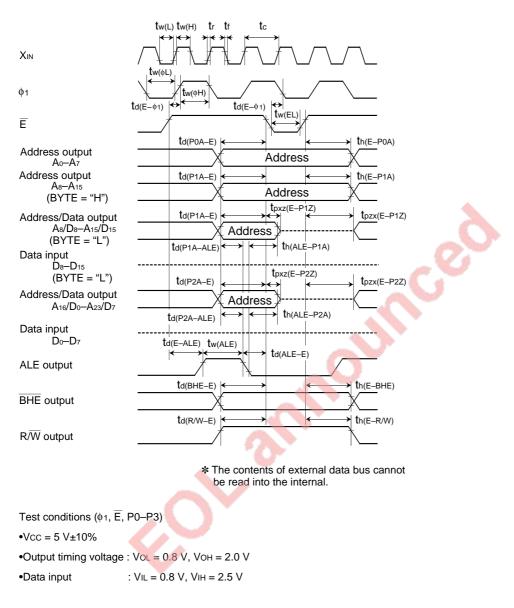

### CHAPTER 15. ELECTRICAL CHARACTERISTICS

| 15.1 Absolute maximum ratings 15-2                                                               |

|--------------------------------------------------------------------------------------------------|

| 15.2 Recommended operating conditions15-3                                                        |

| 15.3 Electrical characteristics 15-4                                                             |

| 15.4 A-D converter characteristics 15-5                                                          |

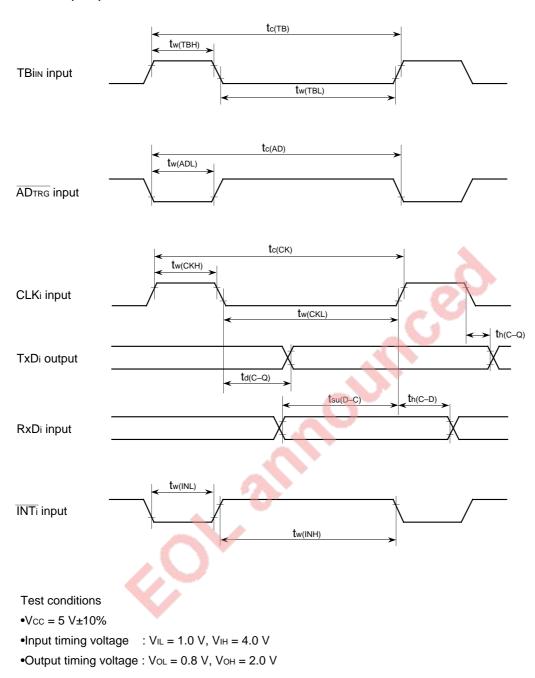

| 15.5 Internal peripheral devices 15-6                                                            |

| 15.6 Ready and Hold 15-13                                                                        |

| 15.7 Single-chip mode 15-16                                                                      |

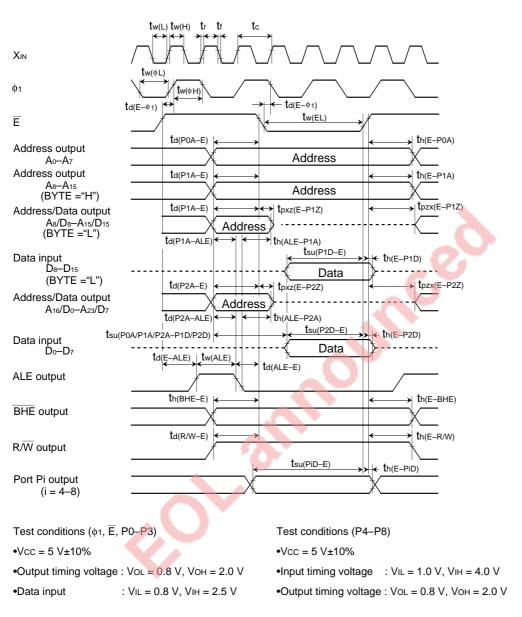

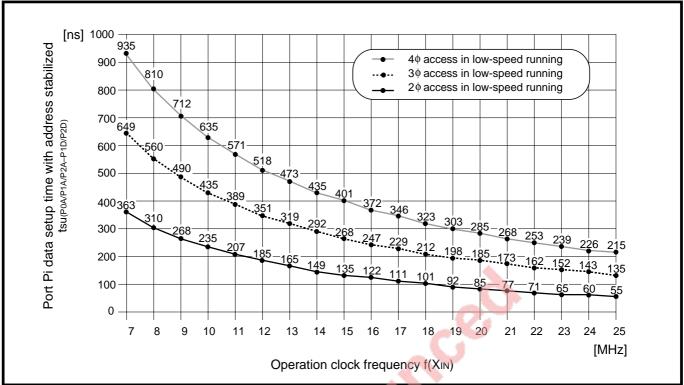

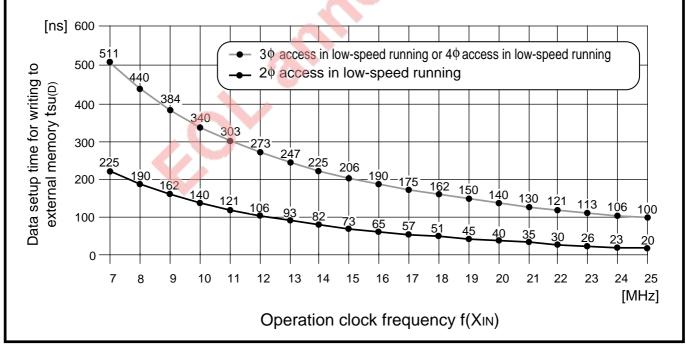

| 15.8 Memory expansion mode and microprocessor mode : When 2- $\phi$ access in                    |

| low-speed running15-18                                                                           |

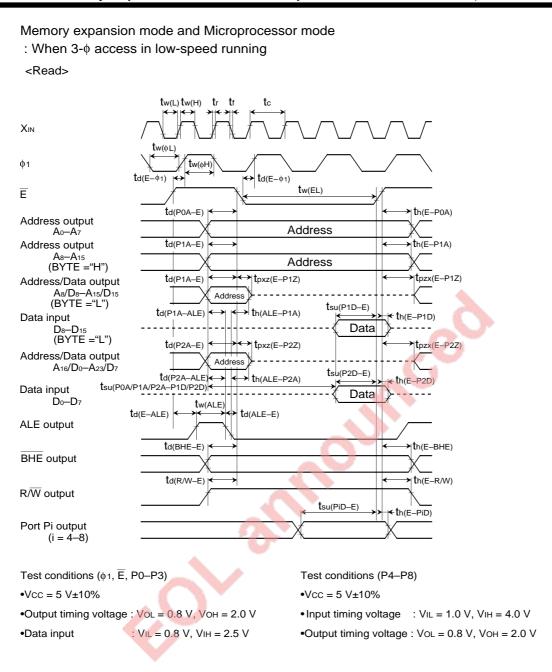

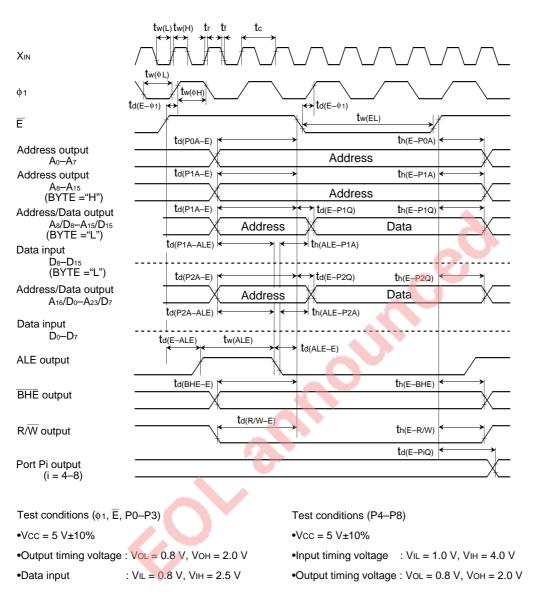

| 15.9 Memory expansion mode and microprocessor mode : When 3- $\phi$ access in                    |

| low-speed running15-23                                                                           |

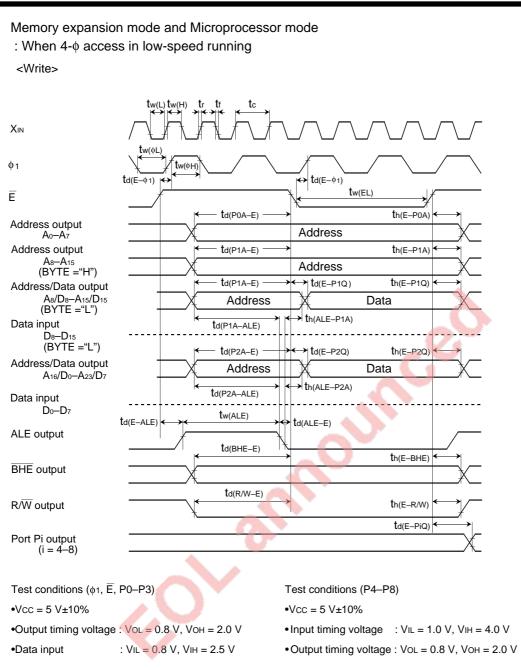

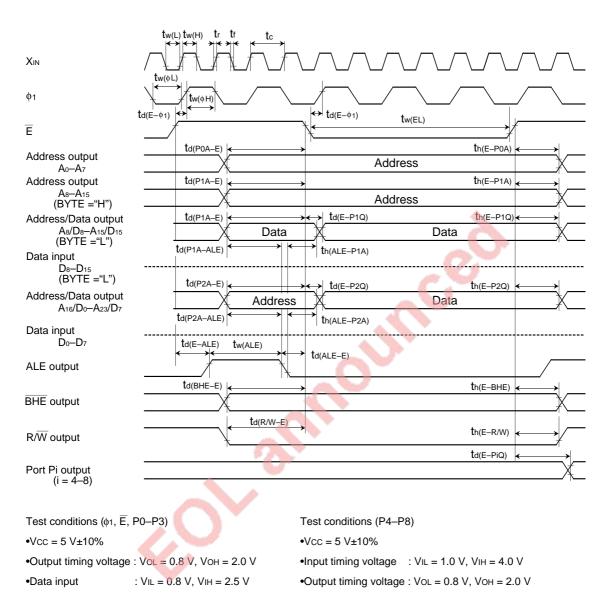

| 15.10 Memory expansion mode and microprocessor mode : When $4-\phi$ access in low-speed running  |

|                                                                                                  |

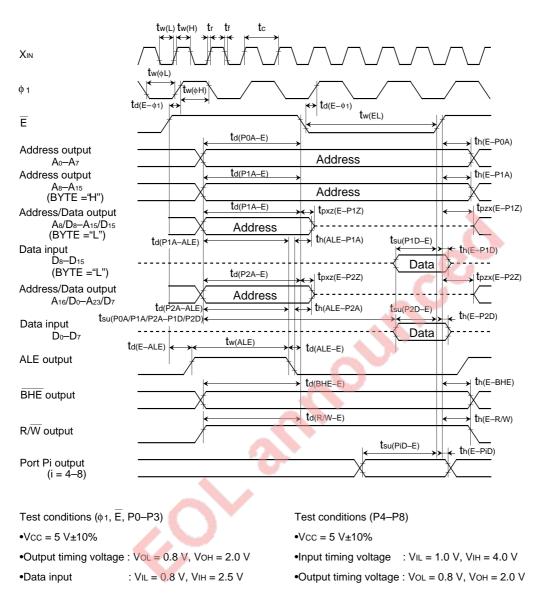

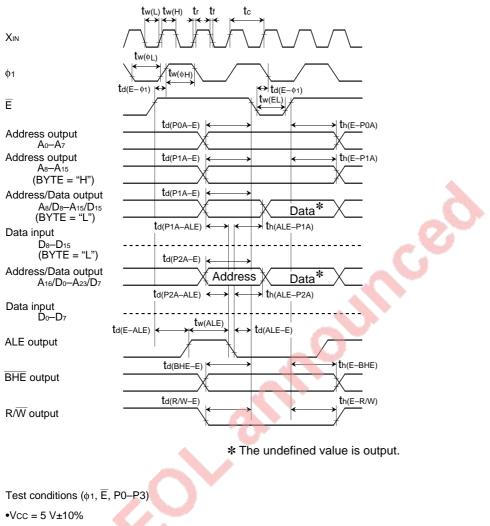

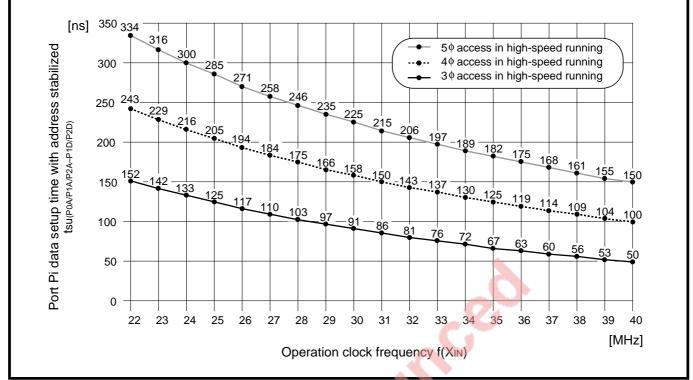

| 15.11 Memory expansion mode and microprocessor mode . When $3-\phi$ access in high-speed running |

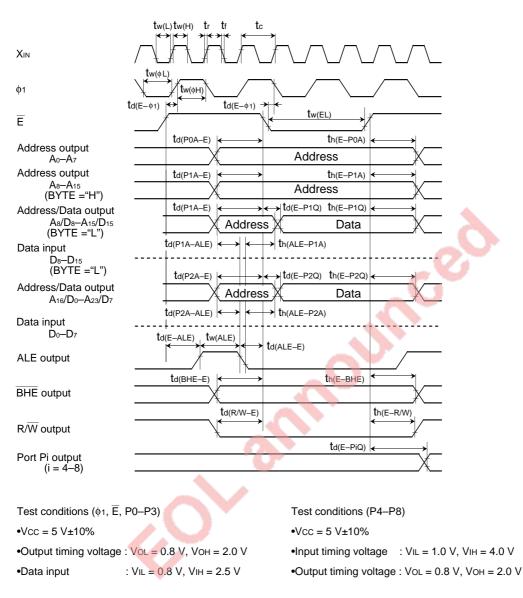

| 15.12 Memory expansion mode and microprocessor mode : When 4- $\phi$ access in                   |

| high-speed running                                                                               |

| 15.13 Memory expansion mode and microprocessor mode : When 5- $\phi$ access in                   |

| high-speed running 15-43                                                                         |

| 15.14 Memory expansion mode and microprocessor mode : When 2- $\phi$ access in                   |

| high-speed running (Internal RAM access)                                                         |

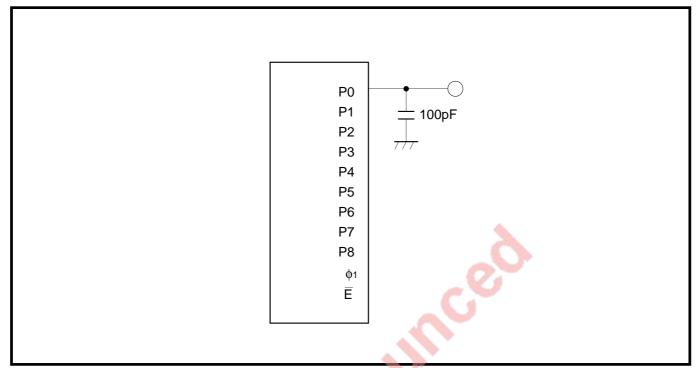

| 15.15 Testing circuit for ports P0 to P8, $\phi_1$ , and E                                       |

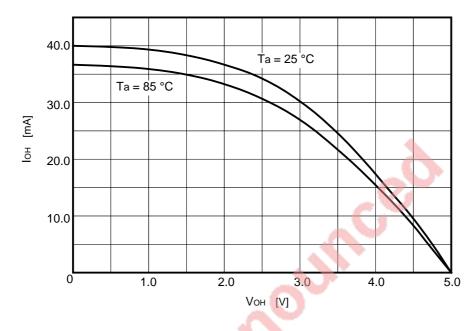

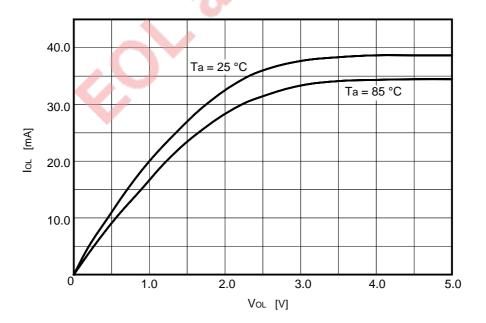

### CHAPTER 16. STANDARD CHARACTERISTICS

| 16.1 Standard characteristics                                       | 16-2 |

|---------------------------------------------------------------------|------|

| 16.1.1 Programmable I/O port (CMOS output) standard characteristics | -    |

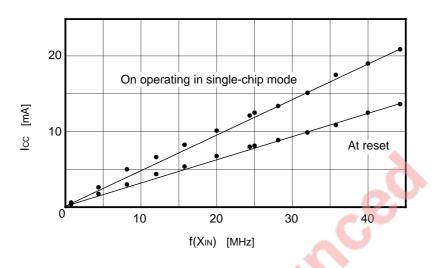

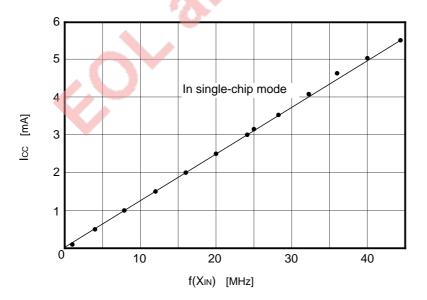

| 16.1.2 Icc-f(XIN) standard characteristics                          |      |

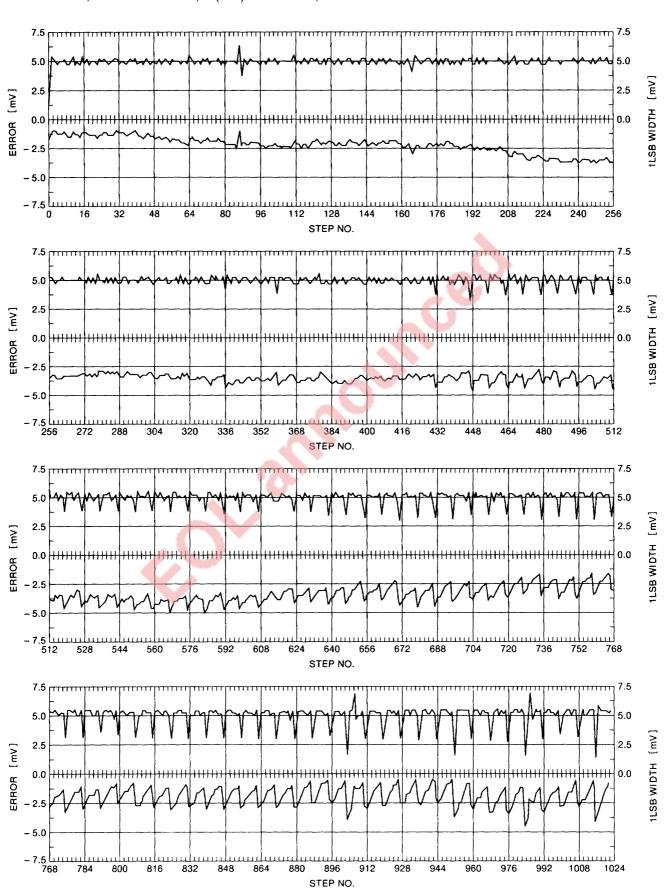

| 16.1.3 A-D converter standard characteristics                       | 16-4 |

## CHAPTER 17. APPLICATIONS

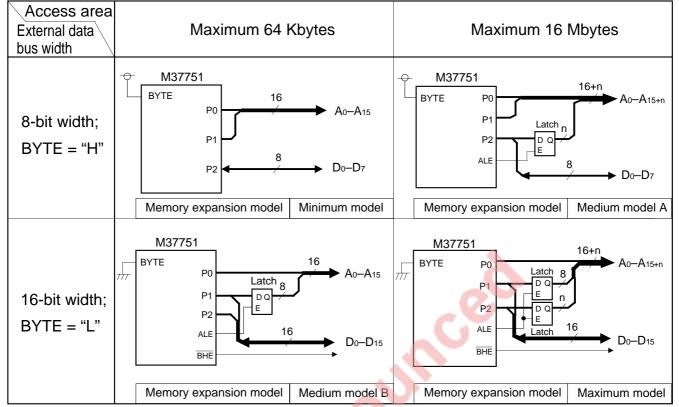

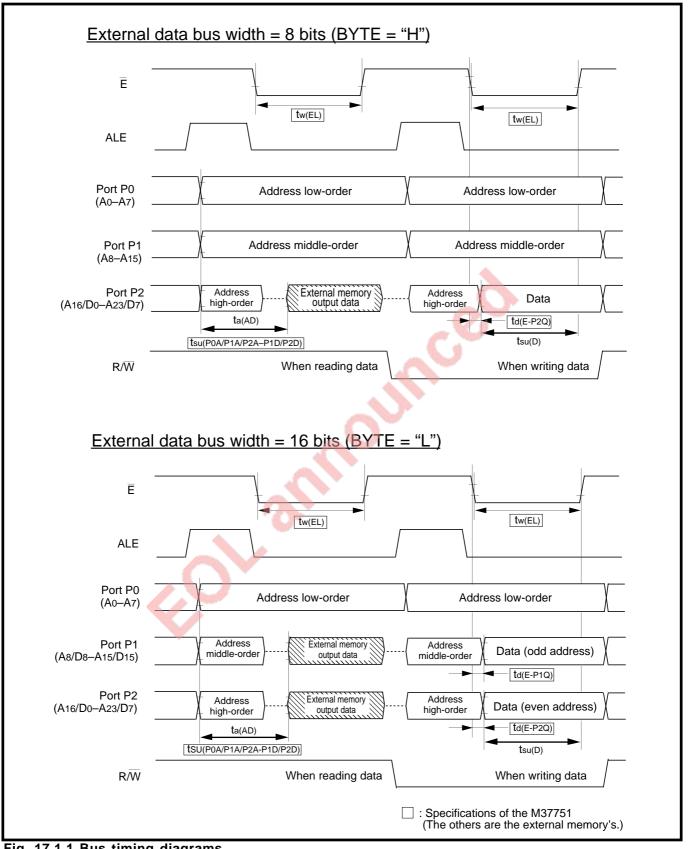

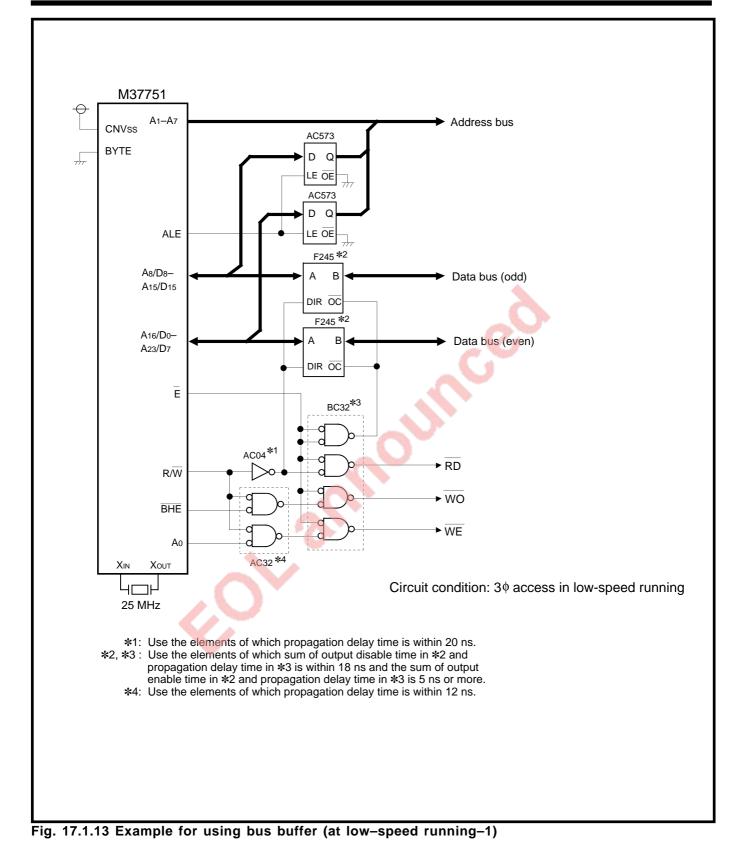

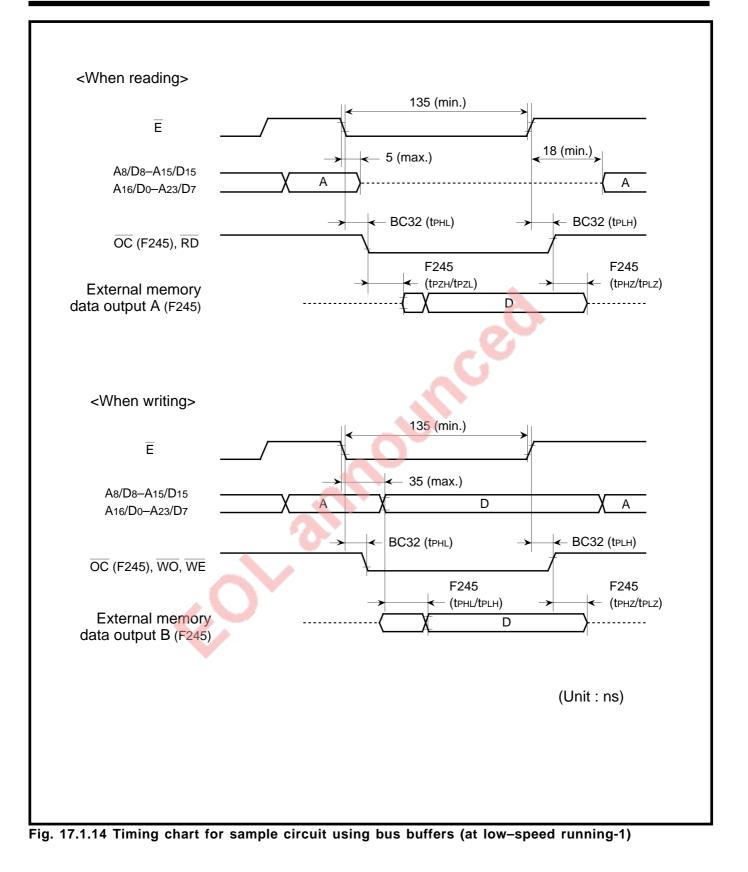

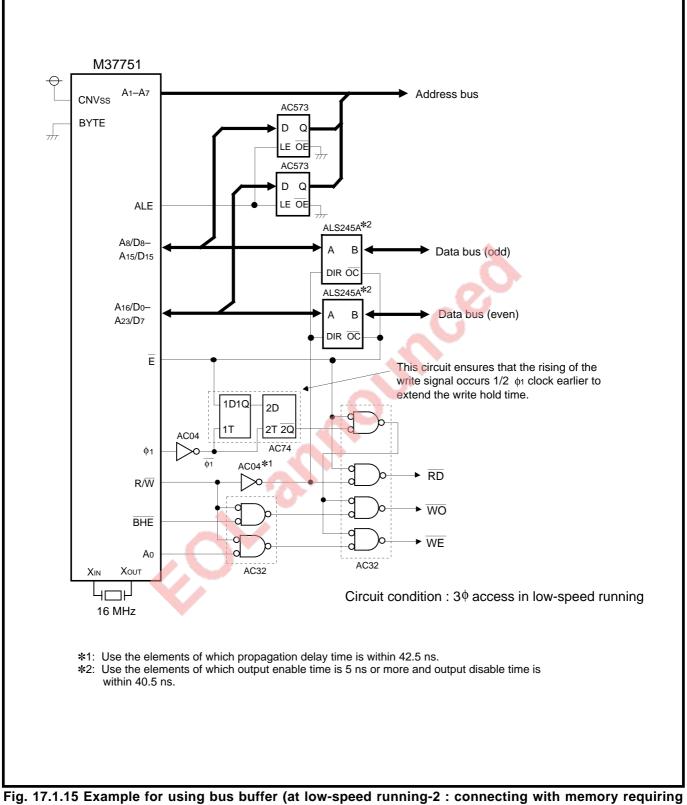

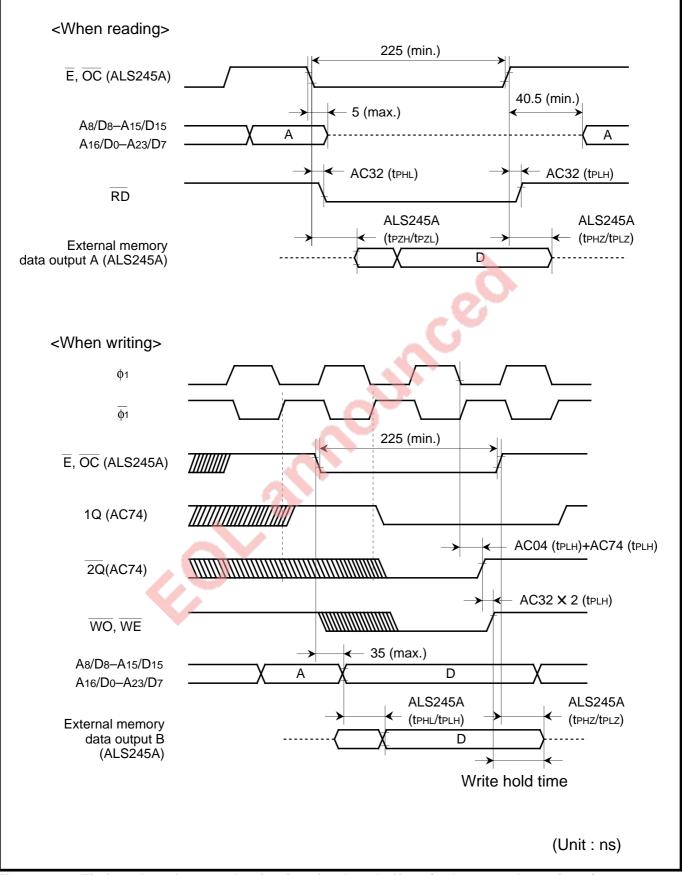

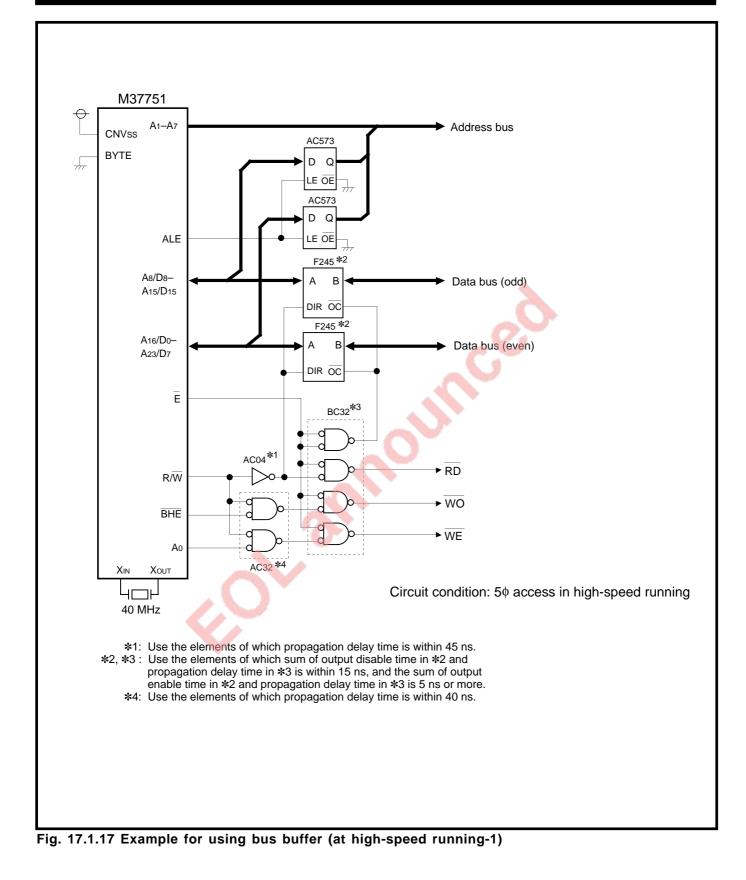

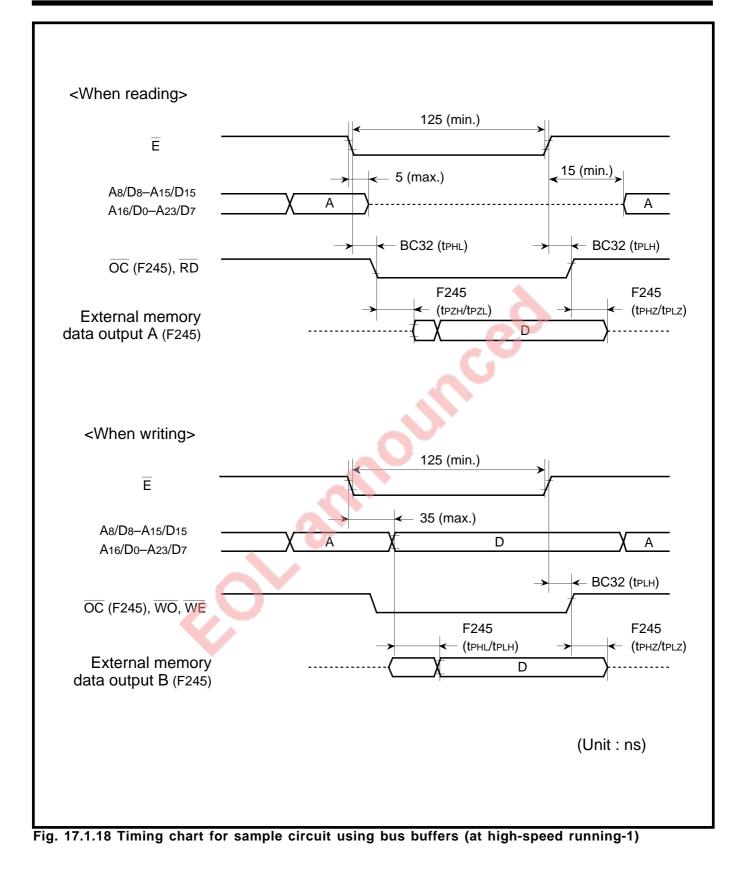

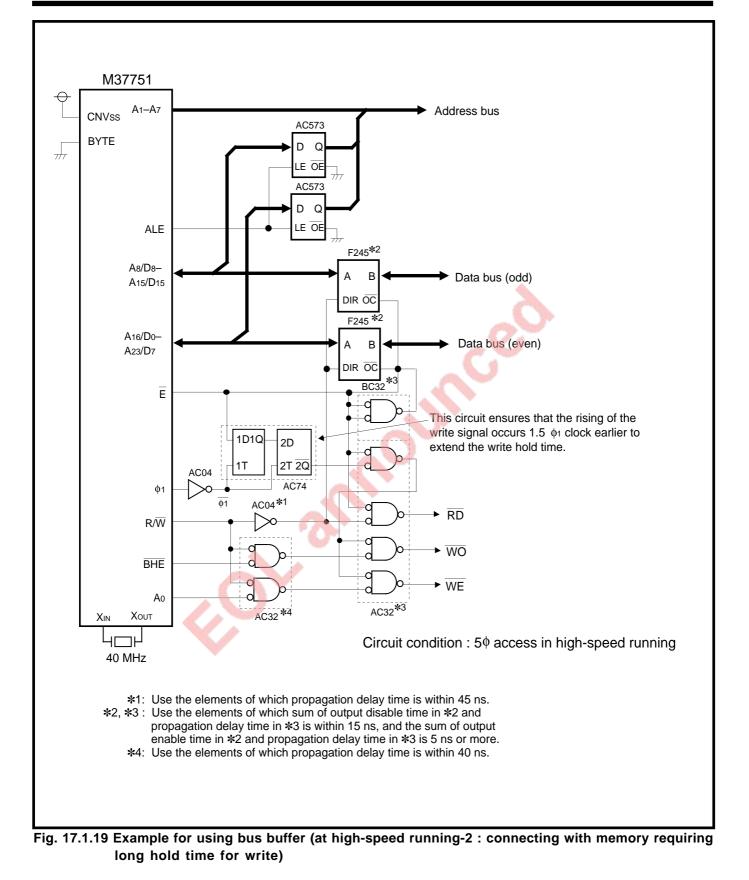

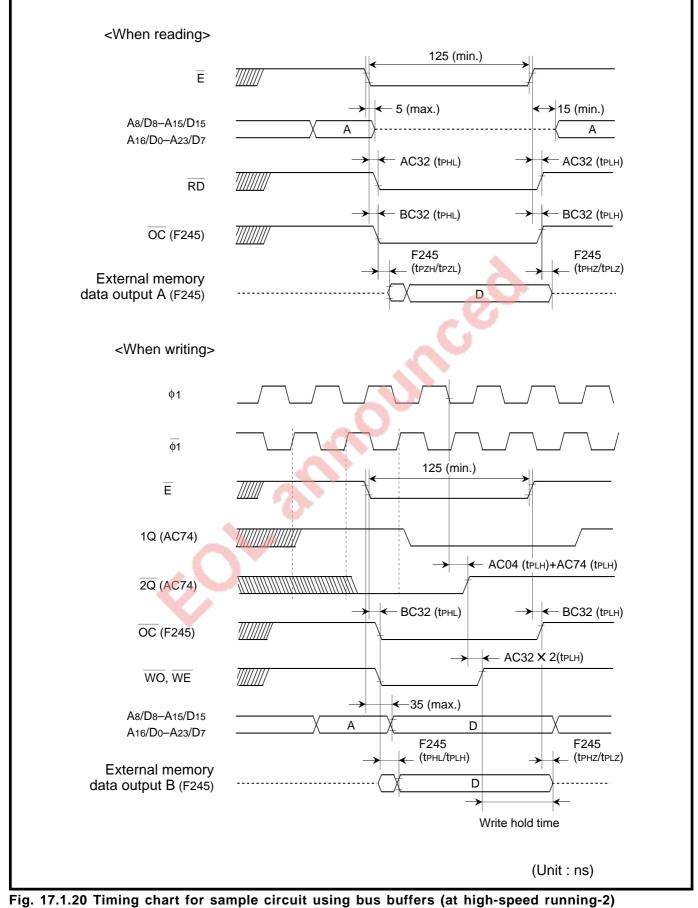

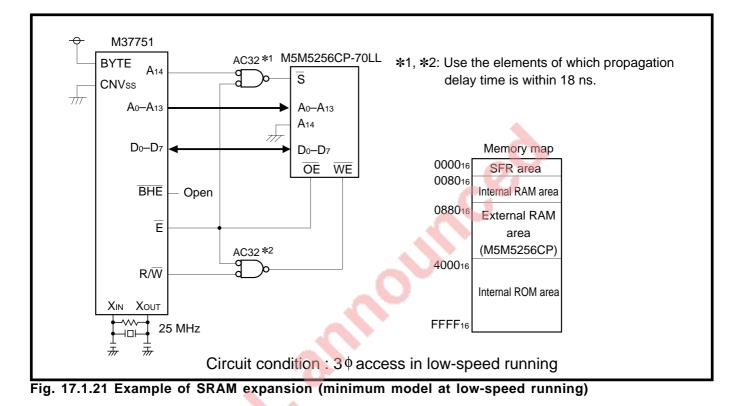

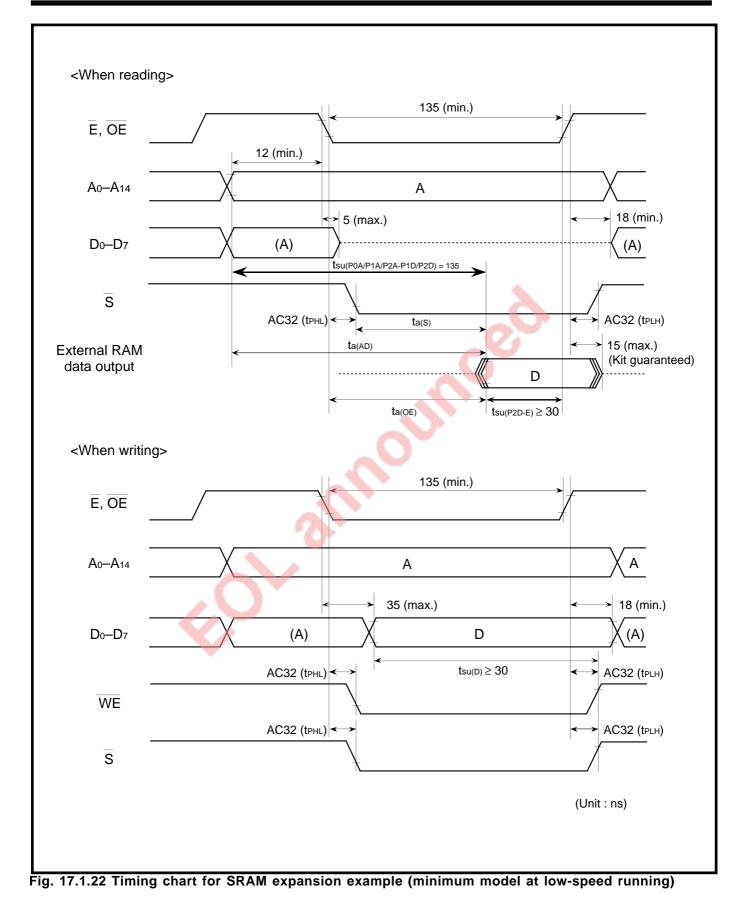

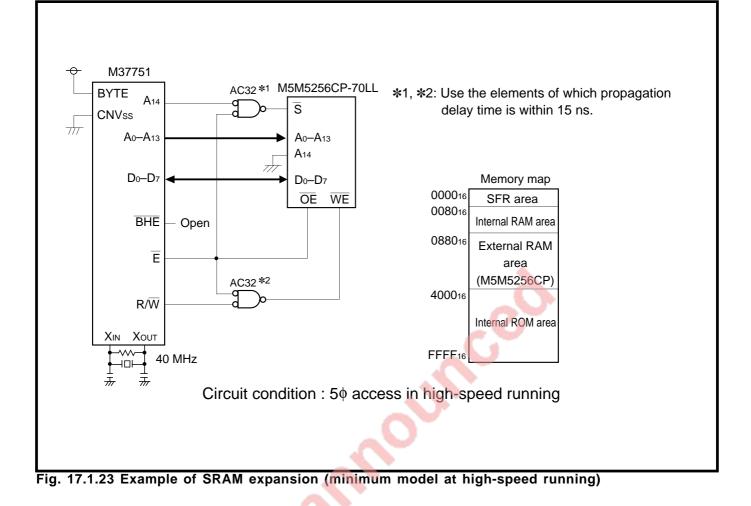

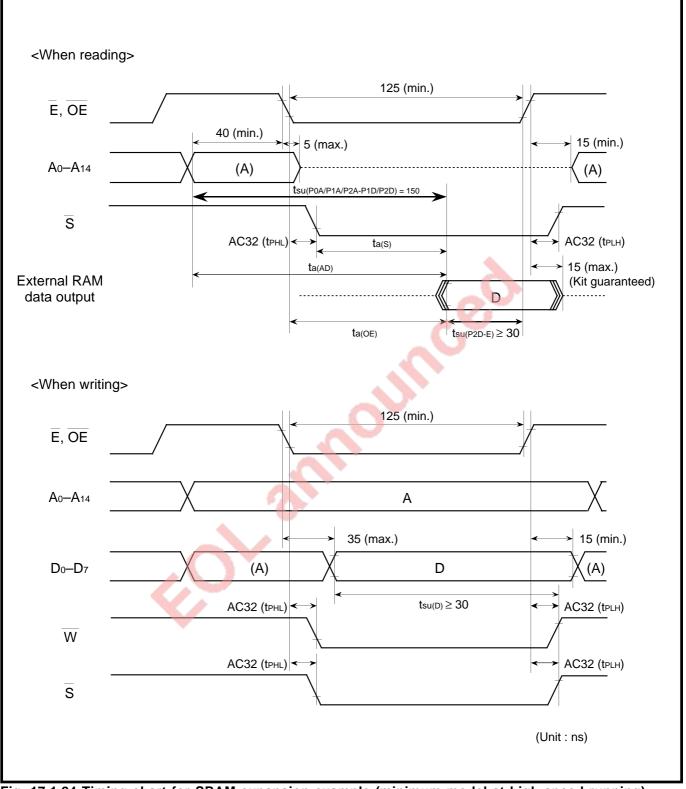

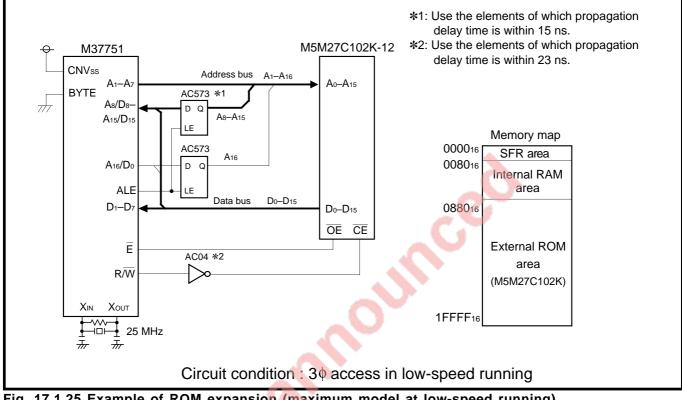

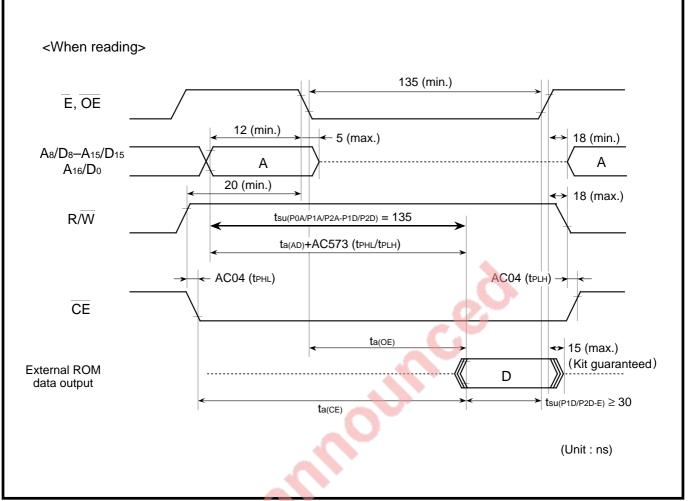

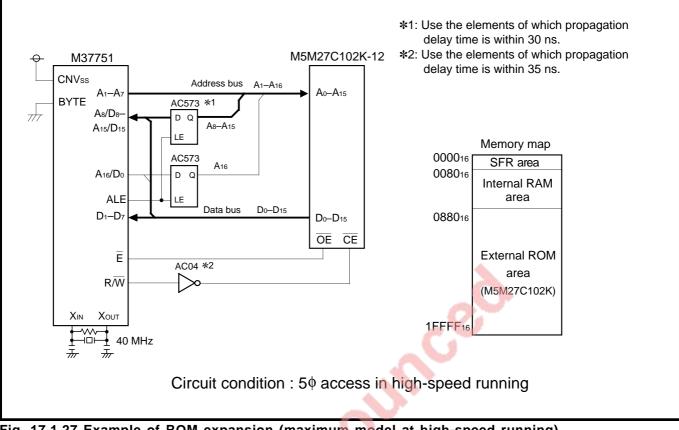

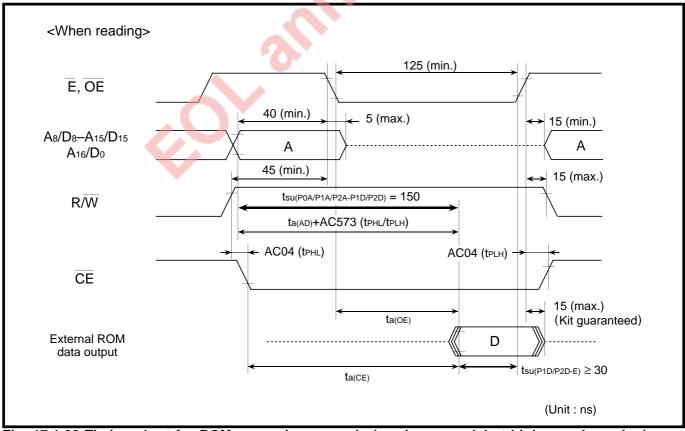

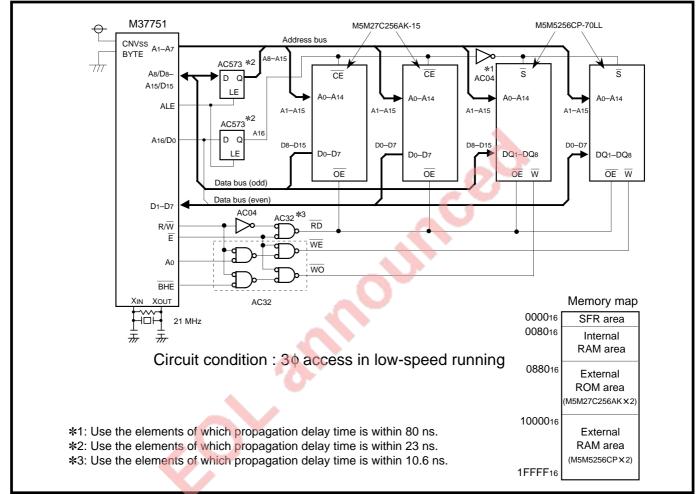

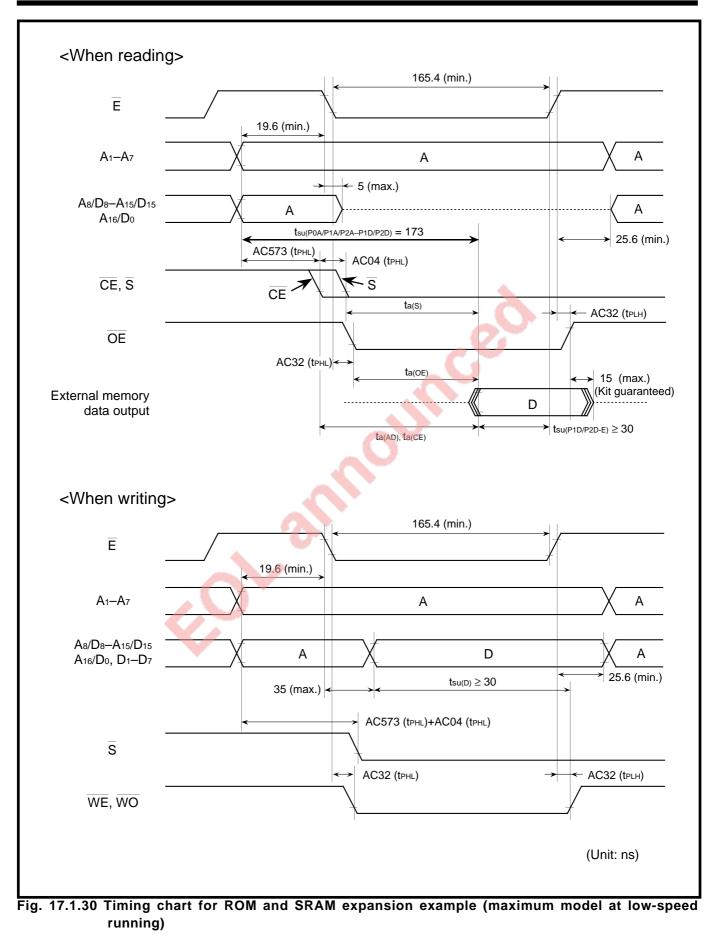

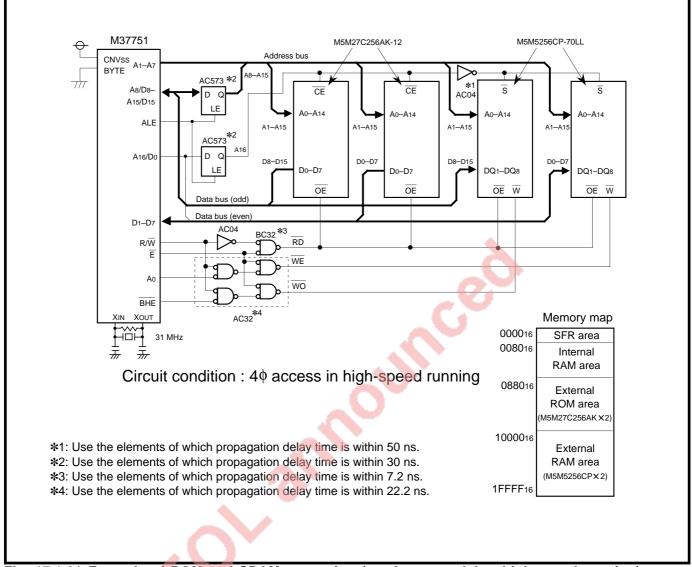

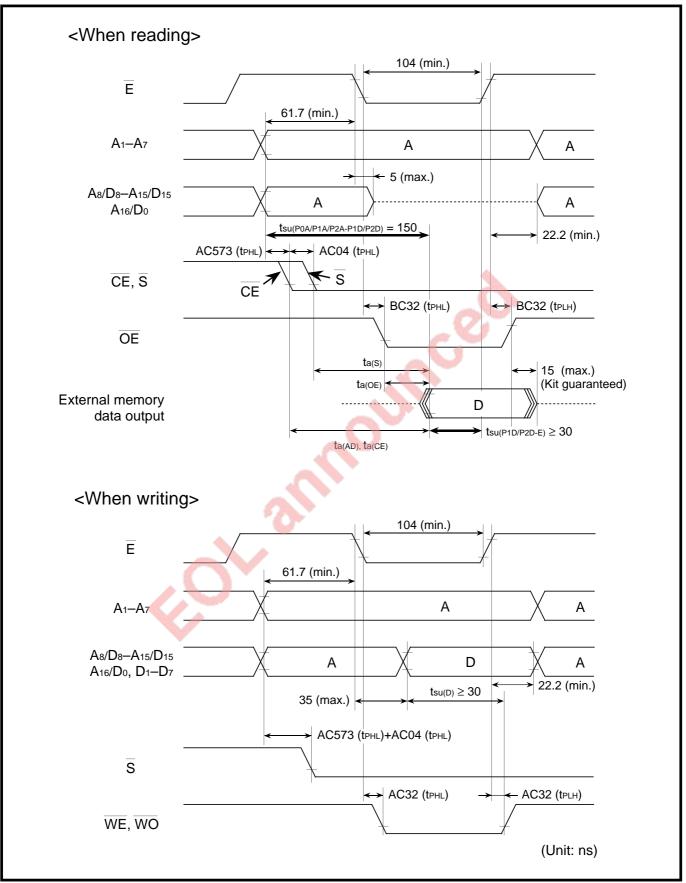

| 17.1 Memory expansion              | 17-2  |

|------------------------------------|-------|

| 17.1.1 Memory expansion model      |       |

| 17.1.2 How to calculate timing     |       |

| 17.1.3 Points in memory expansion  |       |

| 17.1.4 Example of memory expansion |       |

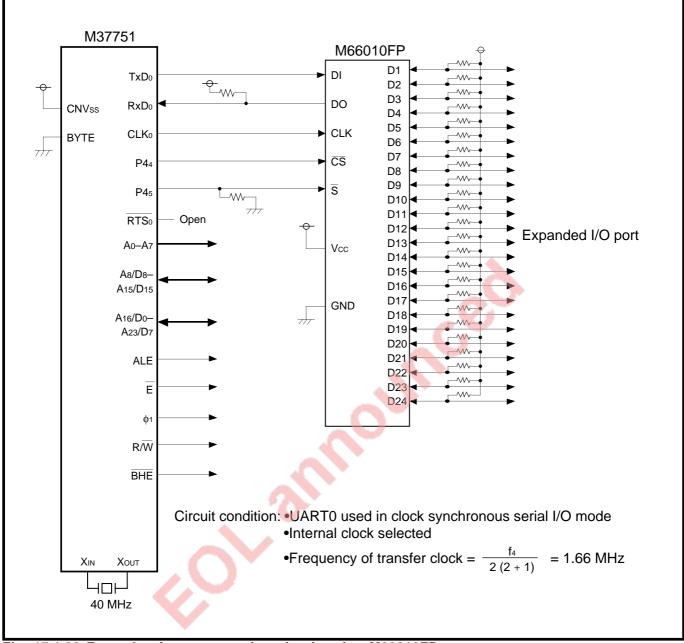

| 17.1.5 Example of I/O expansion    | 17-37 |

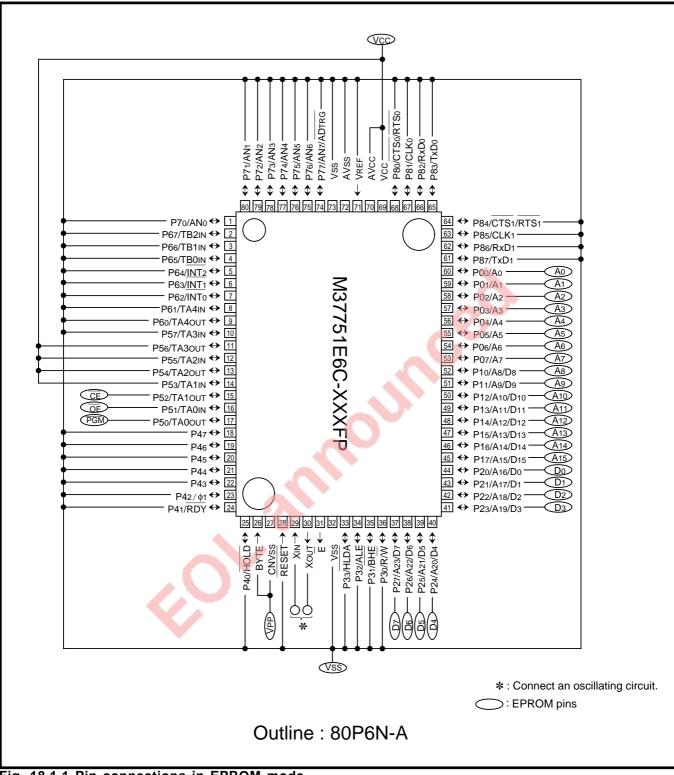

#### CHAPTER 18. PROM VERSION

| 18.1 EPROM mode                                            |  |

|------------------------------------------------------------|--|

| 18.1.1 Pin description                                     |  |

| 18.1.2 Programming/reading to/from built-in PROM           |  |

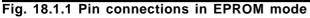

| 18.1.3 Programming algorithm of built-in PROM              |  |

| 18.1.4 Electrical characteristics of programming algorithm |  |

| 18.2 Usage precaution                                      |  |

| 18.2.1 Precautions on all PROM versions                    |  |

| 18.2.2 Precautions on one time PROM version                |  |

| 18.2.3 Precautions on EPROM version                        |  |

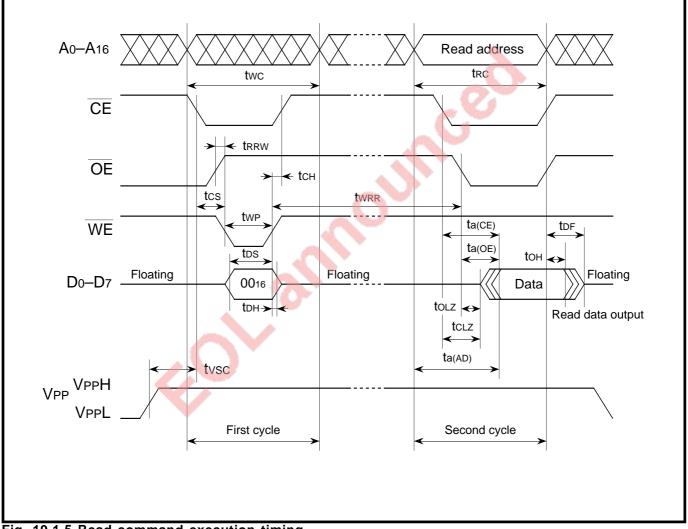

### CHAPTER 19. FLASH MEMORY VERSION

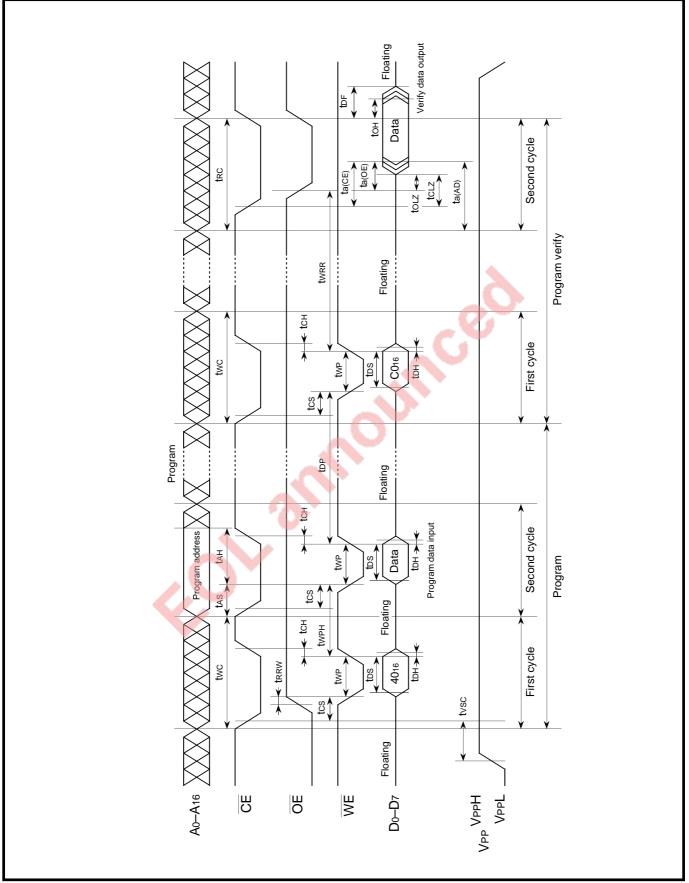

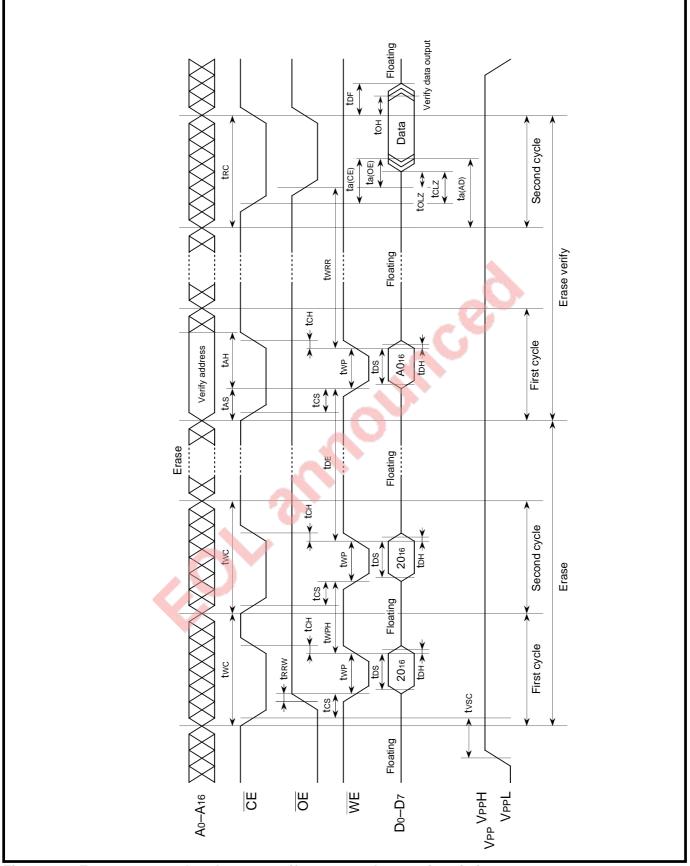

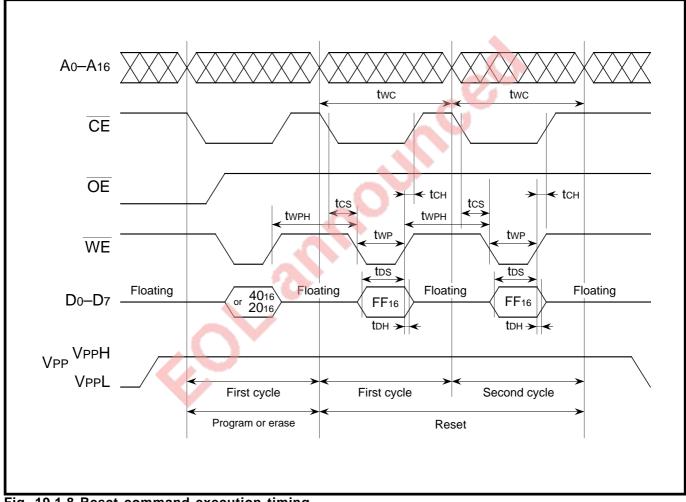

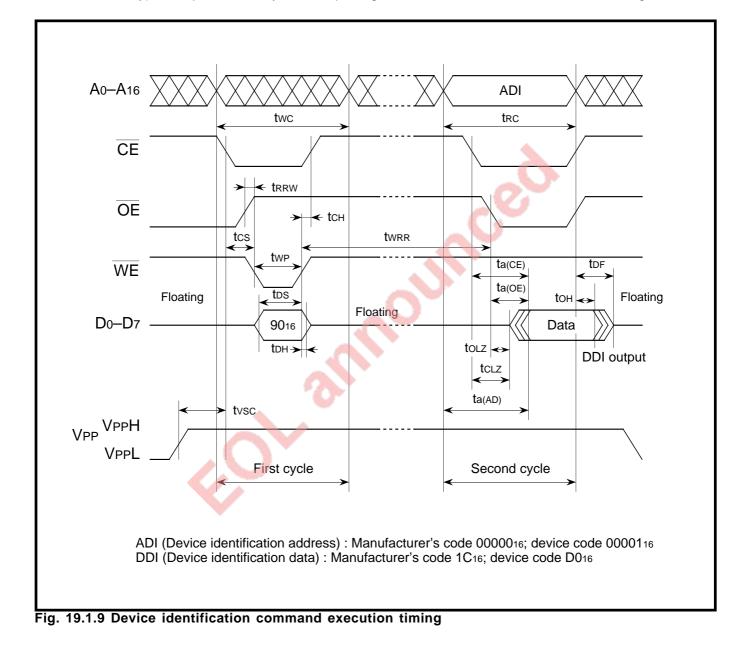

| 19.1 Parallel input/output mode                   |  |

|---------------------------------------------------|--|

| 19.1.1 Pin description                            |  |

| 19.1.2 Access to built-in flash memory            |  |

| 19.1.3 Read-only mode                             |  |

| 19.1.4 Read/write (software command control) mode |  |

| 19.1.5 Electrical characteristics                 |  |

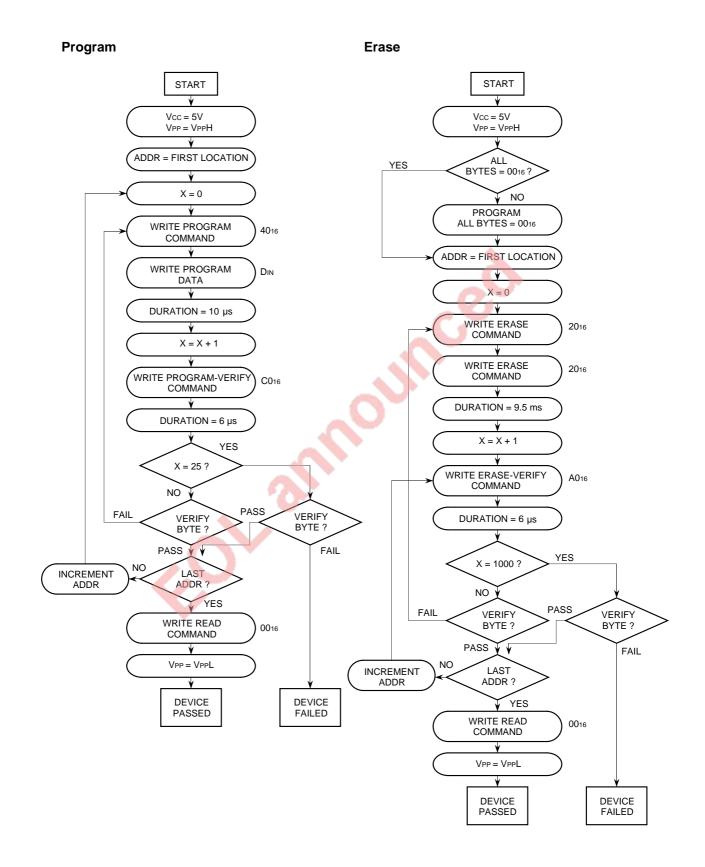

| 19.1.6 Program/erase algorithm flow chart         |  |

| 19.2 Serial input/output mode                     |  |

| 19.2.1 Pin description                            |  |

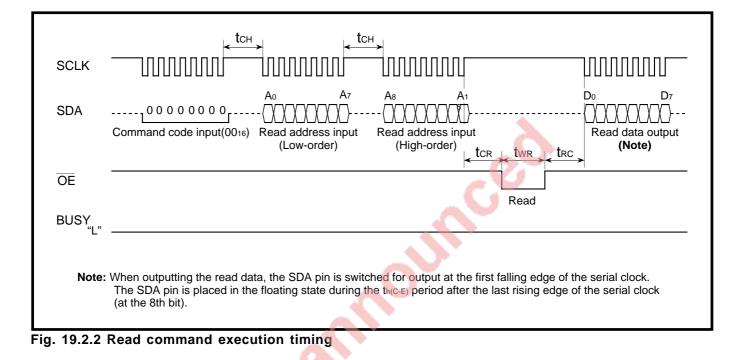

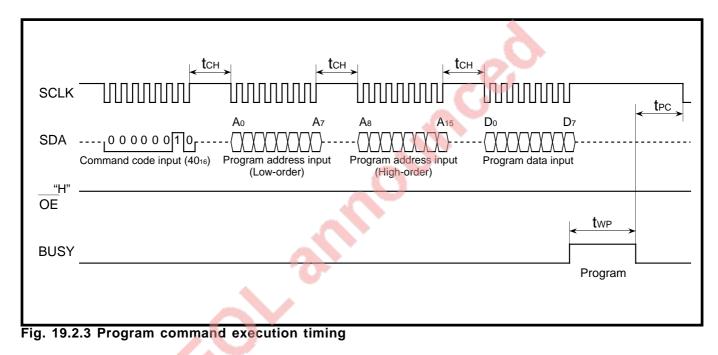

| 19.2.2 Access to built-in flash memory            |  |

| 19.2.3 Electrical characteristics                 |  |

| 19.2.4 Program algorithm flow chart               |  |

### APPENDIX

| Appendix 1. Memory assignment                      | 20-2  |

|----------------------------------------------------|-------|

| Appendix 2. Memory assignment in SFR area          | 20-5  |

| Appendix 3. Control registers                      | 20-9  |

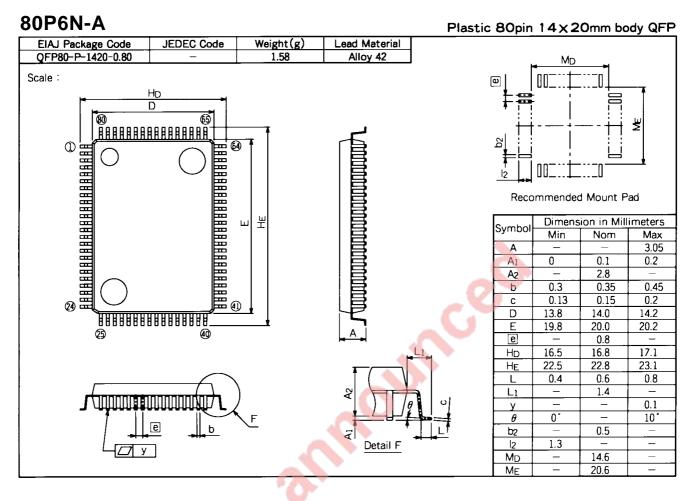

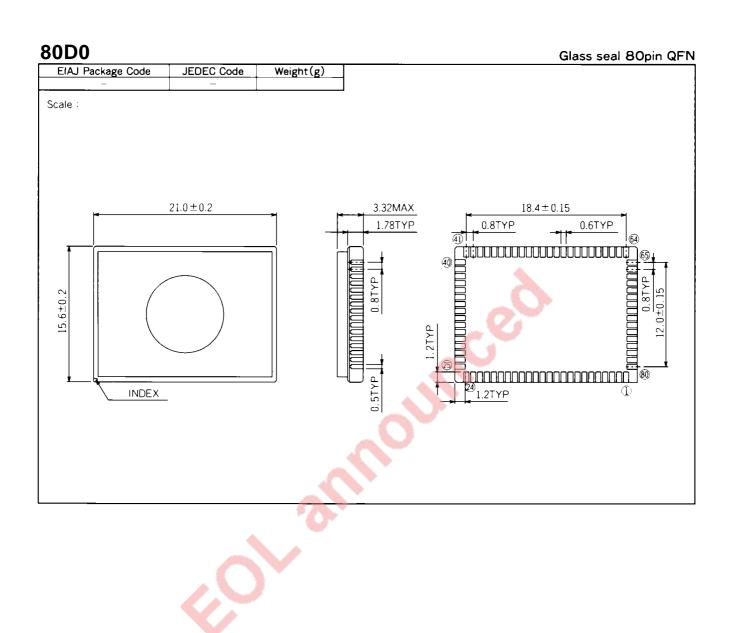

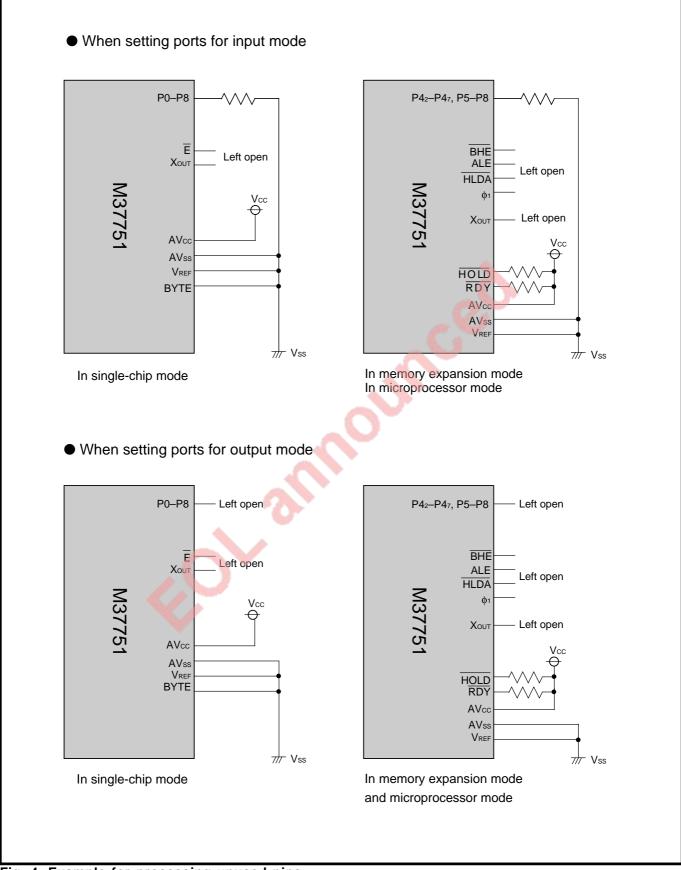

| Appendix 4. Package outlines                       | 20-32 |

| Appendix 5. Example for processing unused pins     |       |

| Appendix 6. Hexadecimal instruction code table     |       |

| Appendix 7. Machine instructions                   | 20-40 |

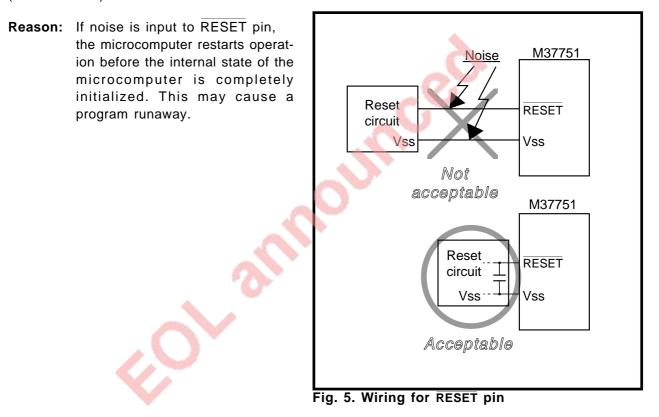

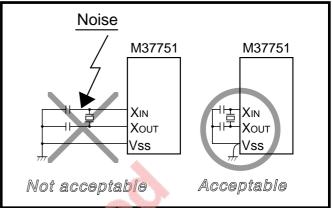

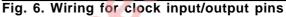

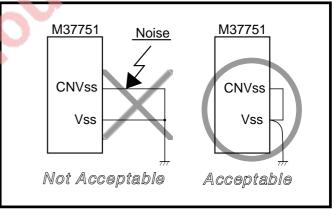

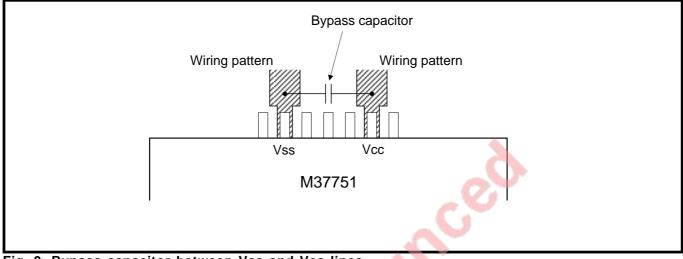

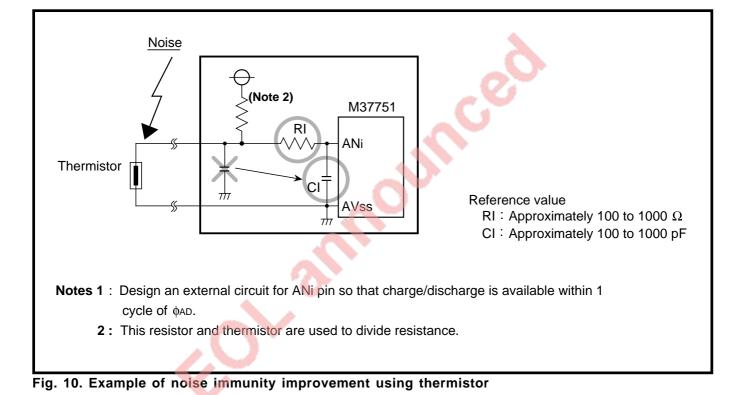

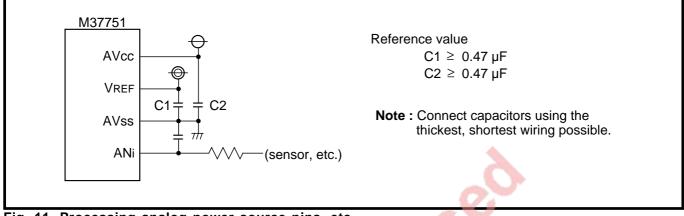

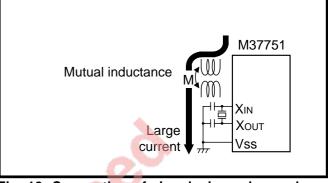

| Appendix 8. Examples of noise immunity improvement |       |

| Appendix 9. Q & A                                  | 20-71 |

|                                                    |       |

## MEMORANDUM

# CHAPTER 1 DESCRIPTION

- 1.1 Performance overview 1.2 Pin configuration

- 1.3 Pin description

- 1.4 Block diagram

The 16-bit single-chip microcomputers 7751 Group is suitable for office, business, and industrial equipment controllers that require high-speed processing of large amounts of data.

These microcomputers develop with the M37751M6C-XXXFP as the base chip. This manual describes the functions about the M37751M6C-XXXFP unless there is a specific difference and refers to the M37751M6C-XXXFP as "M37751."

- Notes 1: About details concerning each microcomputer's development status of the 7751 Group, inquire of "CONTACT ADDRESSES FOR FURTHER INFORMATION" described last.

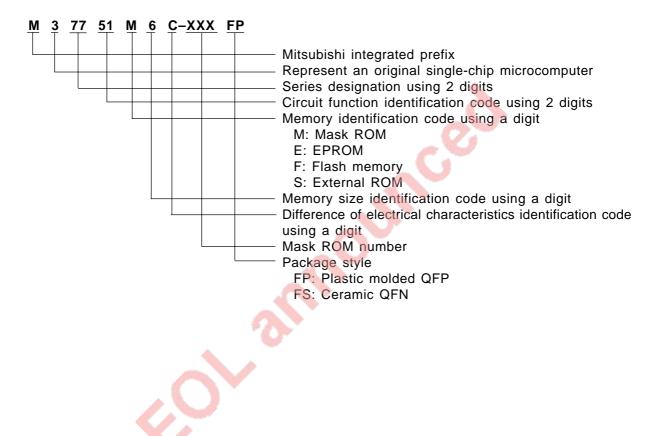

- 2: How the 7751 Group's type name see is described below.

**1.1 Performance overview**

### **1.1 Performance overview**

Table 1.1.1 shows the performance overview of the M37751.

#### Table 1.1.1 M37751 performance overview

| Parameters                                    |                                | Functions                                                         |

|-----------------------------------------------|--------------------------------|-------------------------------------------------------------------|

| Number of basic instructions                  |                                | 109                                                               |

| Instruction execution time                    |                                | 100 ns (the minimum instruction at $f(X_{IN}) = 40 \text{ MHz}$ ) |

| Operating clock frequency f(X <sub>IN</sub> ) |                                | 40 MHz (maximum at high-speed running)                            |

| Memory size                                   | ROM                            | 49152 bytes                                                       |

|                                               | RAM                            | 2048 bytes                                                        |

| Programmable Input/Output                     | P0-P2, P4-P8                   | 8 bits X 8                                                        |

| ports                                         | P3                             | 4 bits X 1                                                        |

| Multifunction timers                          | TA0–TA4                        | 16 bits X 5                                                       |

|                                               | TB0–TB2                        | 16 bits X 3                                                       |

| Serial I/O                                    | UART0, UART1                   | (UART or clock synchronous serial I/O) X 2                        |

| A-D converter                                 |                                | 10-bit successive approximation method $\times$ 1 (8 channels)    |

| Watchdog timer                                |                                | 12 bits X 1                                                       |

| Interrupts                                    |                                | 3 external, 16 internal (priority levels 0 to 7 can               |

|                                               |                                | be set for each interrupt with software)                          |

| Clock generating circuit                      |                                | Built-in (externally connected to a ceramic                       |

|                                               |                                | resonator or a quartz-crystal oscillator)                         |

| Supply voltage                                |                                | 5 V ±10 %                                                         |

| Power dissipation                             |                                | 125 mW (at f(X <sub>IN</sub> ) = 40 MHz frequency, typ.)          |

| Port Input/Output                             | Input/Output withstand voltage | 5 V                                                               |

| characteristics                               | Output current                 | 5 mA                                                              |

| Memory expansion                              | * <b>O</b> *                   | Maximum 16 Mbytes                                                 |

| Operating temperature range                   |                                | –20°C to 85°C                                                     |

| Device structure                              |                                | CMOS high-performance silicon gate process                        |

| Package                                       |                                | 80-pin plastic molded QFP                                         |

Note: All of the 7751 Group microcomputers are the same except for the package type, memory type, memory size, and electric characteristics.

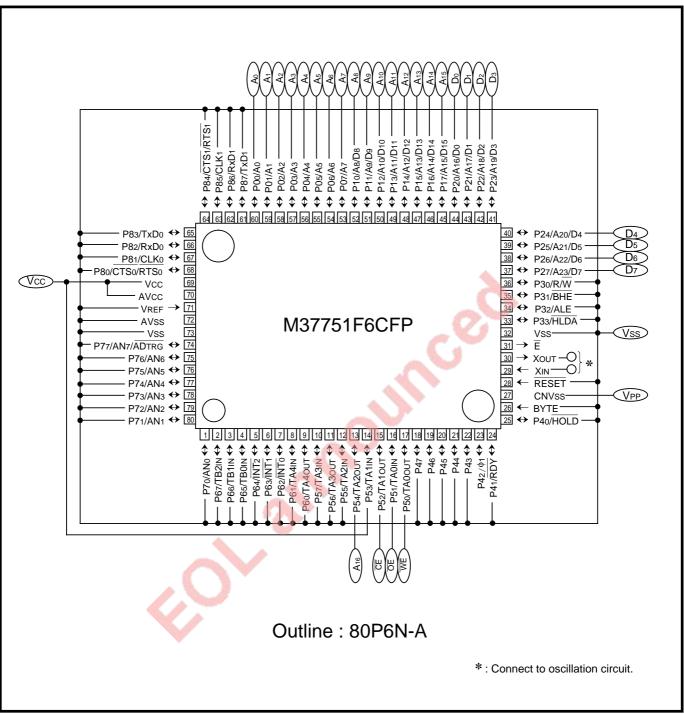

## 1.2 Pin configuration

## **1.2 Pin configuration**

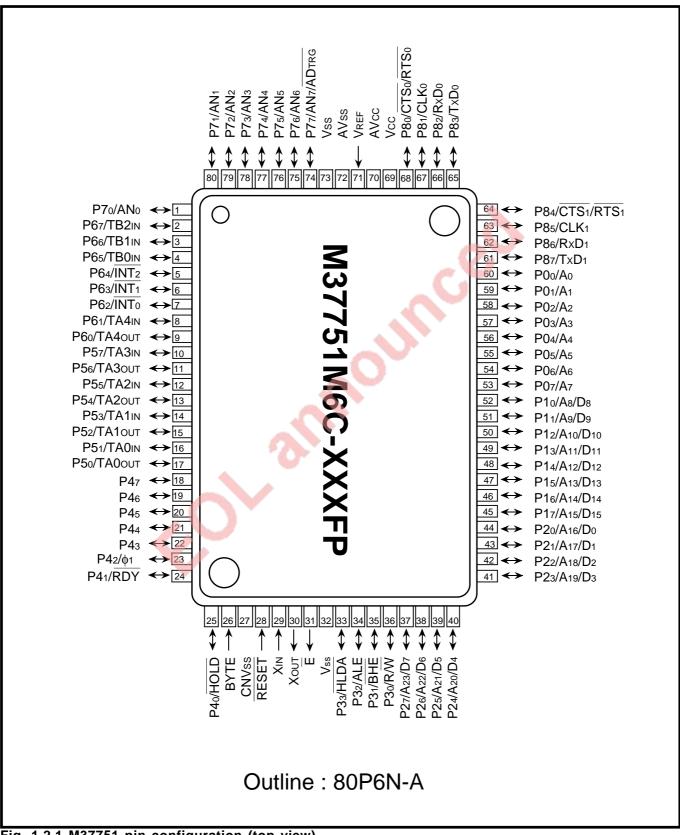

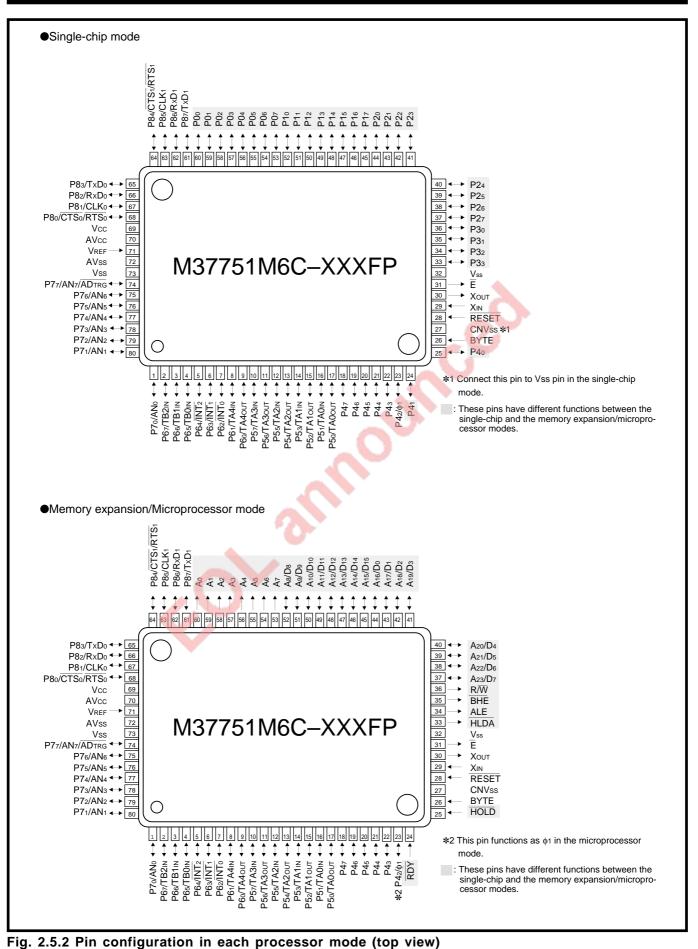

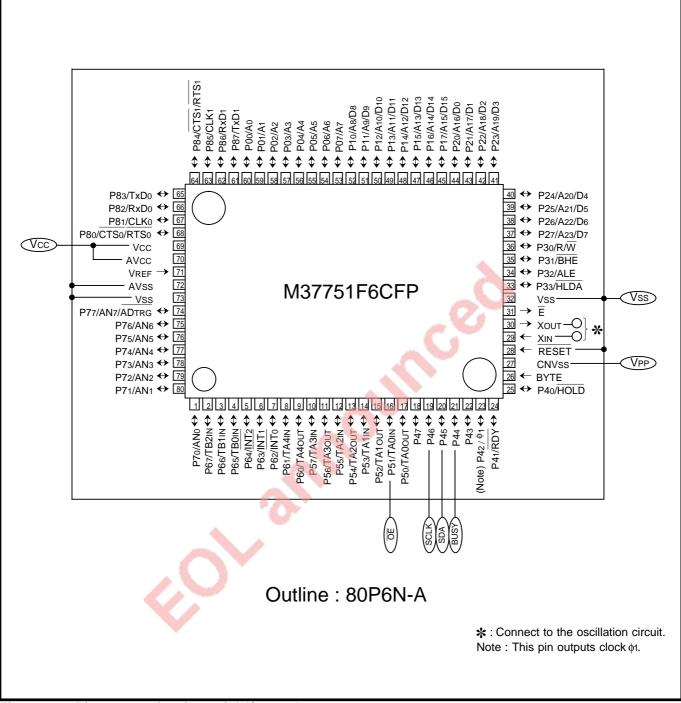

Figure 1.2.1 shows the M37751 pin configuration.

Fig. 1.2.1 M37751 pin configuration (top view)

1.3 Pin description

## **1.3 Pin description**

Tables 1.3.1 to 1.3.3 list the pin description.

| Pin      | Name                    | Input/Output | Functions                                                    |

|----------|-------------------------|--------------|--------------------------------------------------------------|

| Vcc, Vss | Power supply            |              | Supply 5 V ±10 % to Vcc pin and 0 V to Vss pin.              |

| CNVss    | CNVss                   | Input        | This pin controls the processor mode.                        |

|          |                         |              | [Single-chip mode] [Memory expansion mode]                   |

|          |                         |              | Connect to Vss pin.                                          |

|          |                         |              | [Microprocessor mode]                                        |

|          |                         |              | Connect to Vcc pin.                                          |

| RESET    | Reset input             | Input        | The microcomputer is reset when supplying "L" level          |

|          |                         |              | to this pin.                                                 |

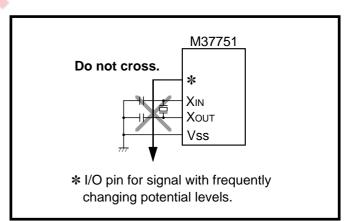

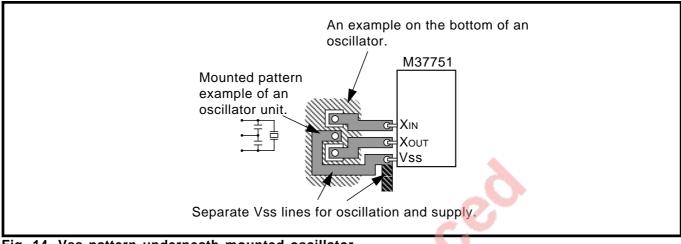

| Xin      | Clock input             | Input        | These are I/O pins of the internal clock generating          |

|          |                         |              | circuit. Connect a ceramic resonator or quartz-crystal       |

| Xout     | Clock output            | Output       | oscillator between XIN and XOUT pins. When using an          |

|          |                         |              | external clock, the clock source should be input to XIN      |

|          |                         |              | pin and Xour pin should be left open.                        |

| Ē        | Enable output           | Output       | This pin outputs E signal.                                   |

|          |                         |              | Data/instruction code read or data write is performed        |

|          |                         |              | when output from this pin is "L" level.                      |

| BYTE     | External data bus width | Input        | [Memory expansion mode] [Microprocessor mode]                |

|          | selection input         |              | Input level to this pin determines whether the external      |

|          |                         |              | data bus has a 16-bit width or 8-bit width. The width        |

|          |                         |              | is 16 bits when the level is "L", and 8 bits when the        |

|          |                         | - O-         | level is "H."                                                |

| AVcc     | Analog supply input     |              | The power supply pin for the A-D converter. Externally       |

|          |                         |              | connect AVcc to Vcc pin.                                     |

| AVss     |                         |              | The power supply pin for the A-D converter. Externally       |

|          |                         |              | connect AVss to Vss pin.                                     |

| Vref     | Reference voltage input | Input        | This is a reference voltage input pin for the A-D converter. |

#### Table 1.3.1 Pin description (1)

## 1.3 Pin description

### Table 1.3.2 Pin description (2)

| Pin                              | Name        | Input/Output | Functions                                                                         |

|----------------------------------|-------------|--------------|-----------------------------------------------------------------------------------|

| P00-P07                          | I/O port P0 | I/O          | [Single-chip mode]                                                                |

|                                  |             |              | Port P0 is an 8-bit CMOS I/O port. This port has an                               |

|                                  |             |              | I/O direction register and each pin can be programmed                             |

|                                  |             |              | for input or output.                                                              |

| A0-A7                            | _           | Output       | [Memory expansion mode] [Microprocessor mode]                                     |

|                                  |             |              | Low-order 8 bits $(A_0 - A_7)$ of the address are output.                         |

| P10-P17                          | I/O port P1 | I/O          | [Single-chip mode]                                                                |

|                                  |             |              | Port P1 is an 8-bit I/O port with the same function as                            |

|                                  |             |              | P0.                                                                               |

| A <sub>8</sub> /D <sub>8</sub> - | _           |              | [Memory expansion mode] [Microprocessor mode]                                     |

| A15/D15                          |             |              | •External bus width = 8 bits (When the BYTE pin is                                |

| 1 110, 2 10                      |             |              | "H" level)                                                                        |

|                                  |             |              | Middle-order 8 bits (A <sub>8</sub> -A <sub>15</sub> ) of the address are output. |

|                                  |             |              | •External bus width = 16 bits (When the BYTE pin is                               |

|                                  |             |              | "L" level)                                                                        |

|                                  |             |              | Data ( $D_8$ to $D_{15}$ ) input/output and output of the middle-                 |

|                                  |             |              | order 8 bits $(A_8-A_{15})$ of the address are performed                          |

|                                  |             |              | with the time sharing system.                                                     |

| P20-P27                          | I/O port P2 | I/O          | [Single-chip mode]                                                                |

|                                  |             | 1/0          | Port P2 is an 8-bit I/O port with the same function as P0.                        |

| A16/D0-                          | _           |              | [Memory expansion mode] [Microprocessor mode]                                     |

| A16/D0-<br>A23/D7                |             |              | Data ( $D_0$ to $D_7$ ) input/output and output of the high-                      |

| A23/D7                           |             |              | order 8 bits $(A_{16}-A_{23})$ of the address are performed                       |

|                                  |             |              | with the time sharing system.                                                     |

| <br>                             |             | 1/0          | [Single-chip mode]                                                                |

| P3₀–P3₃                          | I/O port P3 | I/O          |                                                                                   |

|                                  |             |              | Port P3 is a 4-bit I/O port with the same function as P0.                         |

| R/W,                             |             | Output       | [Memory expansion mode] [Microprocessor mode]                                     |

| BHE,                             |             |              | P3 <sub>0</sub> –P3 <sub>3</sub> respectively output R/W, BHE, ALE, and HLDA      |

| ALE,                             |             |              | signals.                                                                          |

| HLDA                             |             |              |                                                                                   |

|                                  |             |              | The Read/Write signal indicates the data bus state.                               |

|                                  |             |              | The state is read while this signal is "H" level, and                             |

|                                  |             |              | write while this is "L" level.                                                    |

|                                  |             |              | ●BHE                                                                              |

|                                  |             |              | "L" level is output when an odd-numbered address is                               |

|                                  |             |              | accessed.                                                                         |

|                                  |             |              | ●ALE                                                                              |

|                                  |             |              | This is used to obtain only the address from address                              |

|                                  |             |              | and data multiplex signals.                                                       |

|                                  |             |              | •HLDA                                                                             |

|                                  |             |              | This is the signal to externally indicate the state when                          |

|                                  |             |              | the microcomputer is in Hold state.                                               |

|                                  |             |              | "L" level is output during Hold state.                                            |

## 1.3 Pin description

| Pin       | Name        | Input/Output | Functions                                                                           |

|-----------|-------------|--------------|-------------------------------------------------------------------------------------|

| P40-P47   | I/O port P4 | I/O          | [Single-chip mode]                                                                  |

|           |             |              | Port P4 is an 8-bit I/O port with the same function as                              |

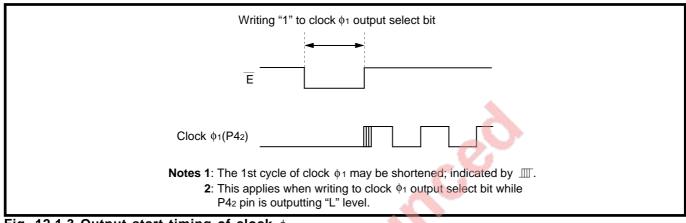

|           |             |              | P0. P4 <sub>2</sub> can be programmed as the clock $\phi_1$ output pin.             |

| HOLD,     |             | Input        | [Memory expansion mode]                                                             |

| RDY,      |             | Input        | $P4_0$ functions as the $\overline{HOLD}$ input pin, $P4_1$ as the $\overline{RDY}$ |

| P42-P47   |             | I/O          | input pin. The microcomputer is in Hold state while "L"                             |

|           |             |              | level is input to the HOLD pin.                                                     |

|           |             |              | The microcomputer is in Ready state while "L" level is                              |

|           |             |              | input to the RDY pin.                                                               |

|           |             |              | $P4_2$ - $P4_7$ function as I/O ports with the same functions                       |

|           |             |              | as P0.                                                                              |

|           |             |              | P4 <sub>2</sub> can be programmed for the clock $\phi_1$ output pin.                |

| HOLD,     |             | Input        | [Microprocessor mode]                                                               |

| RDY,      |             | Input        | $P4_0$ functions as the HOLD input pin, $P4_1$ as the RDY                           |

| $\phi_1,$ |             | Output       | input pin. P4 <sub>2</sub> always functions as the clock $\phi_1$ output            |

| P43-P47   |             | I/O          | pin.                                                                                |

|           |             |              | P4 <sub>3</sub> –P4 <sub>7</sub> function as I/O ports with the same functions      |

|           |             |              | as P0.                                                                              |

| P50-P57   | I/O port P5 | I/O          | Port P5 is an 8-bit I/O port with the same function as                              |

|           |             |              | P0. These pins can be programmed as I/O pins for                                    |

|           |             |              | Timers A0–A3.                                                                       |

| P60-P67   | I/O port P6 | I/O          | Port P6 is an 8-bit I/O port with the same function as                              |

|           |             |              | P0. These pins can be programmed as I/O pins for                                    |

|           |             | ·O·          | Timer A4, input pins for external interrupt and input                               |

|           |             |              | pins for Timers B0-B2.                                                              |

| P70–P77   | I/O port P7 | 1/0          | Port P7 is an 8-bit I/O port with the same function as                              |

|           |             |              | P0. These pins can be programmed as input pins for                                  |

|           |             |              | A-D converter.                                                                      |

| P80-P87   | I/O port P8 | I/O          | Port P8 is an 8-bit I/O port with the same function as                              |

|           |             |              | P0. These pins can be programmed as I/O pins for                                    |

|           |             |              | serial I/O.                                                                         |

#### Table 1.3.3 Pin description (3)

## 1.4 Block diagram

## 1.4 Block diagram

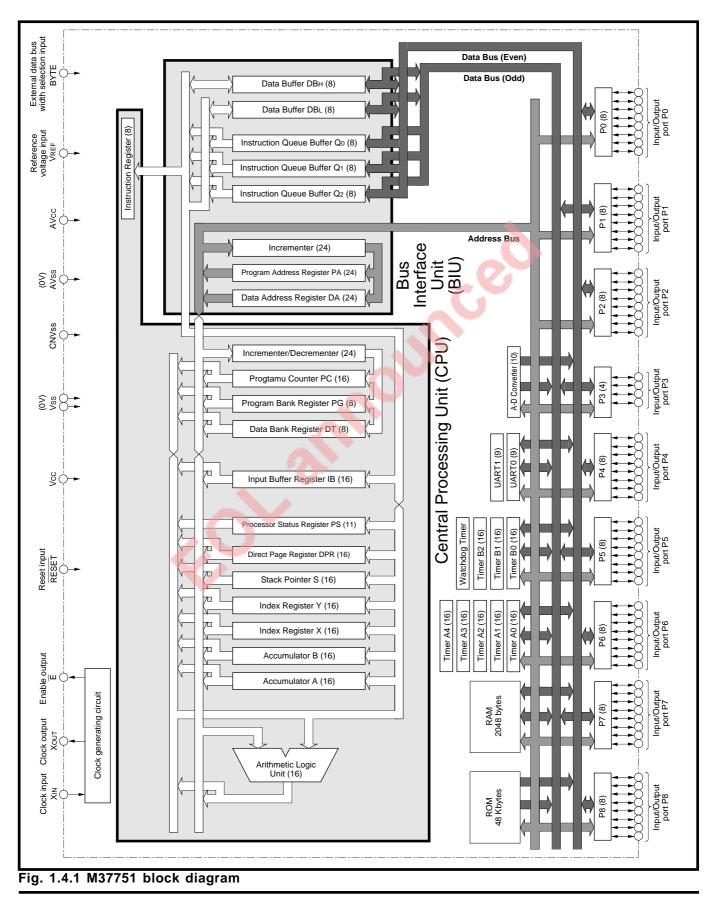

Figure 1.4.1 shows the M37751 block diagram.

# CHAPTER 2 CENTRAL PROCESSING UNIT (CPU)

- 2.1 Central processing unit

- 2.2 Bus interface unit

- 2.3 Access space

- 2.4 Memory assignment

- 2.5 Processor modes

### 2.1 Central processing unit

## 2.1 Central processing unit

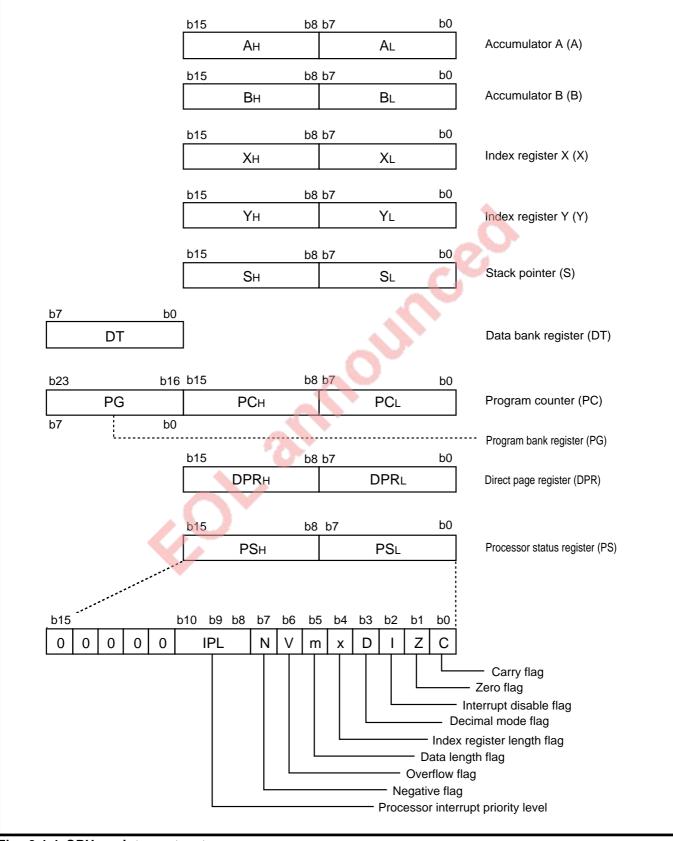

The CPU (Central Processing Unit) has the ten registers as shown in Figure 2.1.1.

Fig. 2.1.1 CPU registers structure

#### 2.1.1 Accumulator (Acc)

Accumulators A and B are available.

#### (1) Accumulator A (A)

Accumulator A is the main register of the microcomputer. The transaction of data such as calculation, data transfer, and input/output are performed mainly through accumulator A. It consists of 16 bits, and the low-order 8 bits can also be used separately. The data length flag (m) determines whether the register is used as a 16-bit register or as an 8-bit register. Flag m is a part of the processor status register which is described later. When an 8-bit register is selected, only the low-order 8 bits of accumulator A are used and the contents of the high-order 8 bits is unchanged.

#### (2) Accumulator B (B)

Accumulator B is a 16-bit register with the same function as accumulator A. Accumulator B can be used instead of accumulator A. The use of accumulator B, however except for some instructions, requires more instruction bytes and execution cycles than that of accumulator A. Accumulator B is also controlled by the data length flag (m) just as in accumulator A.

#### 2.1.2 Index register X (X)

Index register X consists of 16 bits and the low-order 8 bits can also be used separately. The index register length flag (x) determines whether the register is used as a 16-bit register or as an 8-bit register. Flag x is a part of the processor status register which is described later. When an 8-bit register is selected, only the low-order 8 bits of index register X are used and the contents of the high-order 8 bits is unchanged. In an addressing mode in which index register X is used as an index register, the address obtained by adding the contents of this register to the operand's contents is accessed.

In the **MVP** or **MVN** instruction, a block transfer instruction, the contents of index register X indicate the low-order 16 bits of the source address. The third byte of the instruction is the high-order 8 bits of the source address.

In the **RMPA** instruction, a Repeat MultiPly and Accumulate instruction, the contents of index register X indicate the low-order 16 bits of address in which multiplicands are stored.

Note: Refer to "7751 Series Software Manual" for addressing modes.

#### 2.1.3 Index register Y (Y)

Index register Y is a 16-bit register with the same function as index register X. Just as in index register X, the index register length flag (x) determines whether this register is used as a 16-bit register or as an 8-bit register.

In the **MVP** or **MVN** instruction, a block transfer instruction, the contents of index register Y indicate the low-order 16 bits of the destination address. The second byte of the instruction is the high-order 8 bits of the destination address.

In the **RMPA** instruction, a Repeat MultiPly and Accumulate instruction, the contents of index register Y indicate the low-order 16 bits of address in which multipliers are stored.

#### 2.1 Central processing unit

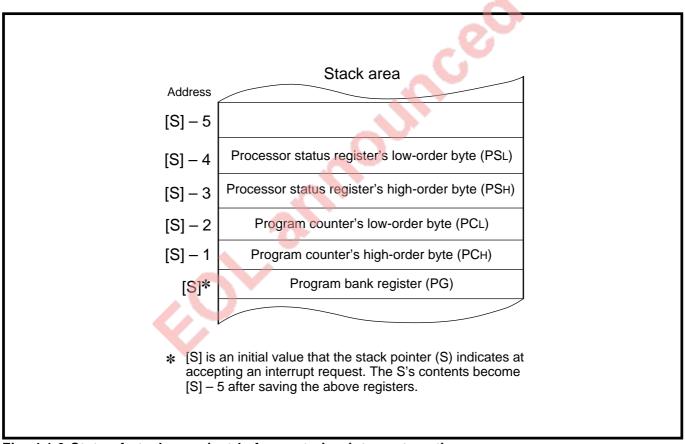

#### 2.1.4 Stack pointer (S)

The stack pointer (S) is a 16-bit register. It is used for a subroutine call or an interrupt. It is also used when addressing modes using the stack are executed. The contents of S indicate an address (stack area) for storing registers during subroutine calls and interrupts. Bank 016 is specified for the stack area. (Refer to "2.1.6 Program bank register (PG).")

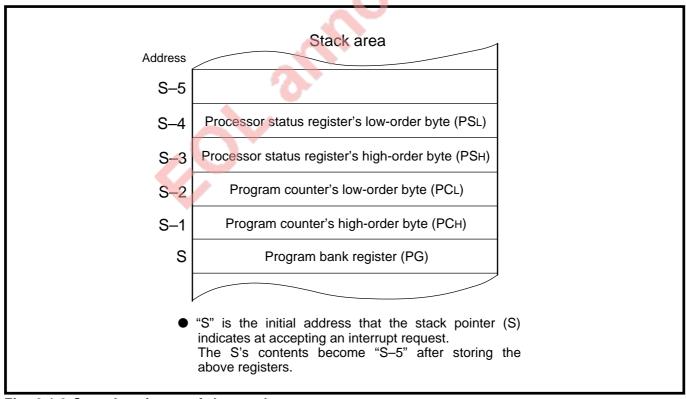

When an interrupt request is accepted, the microcomputer stores the contents of the program bank register (PG) at the address indicated by the contents of S and decrements the contents of S by 1. Then the contents of the program counter (PC) and the processor status register (PS) are stored. The contents of S after accepting an interrupt request is equal to the contents of S decremented by 5 before the accepting of the interrupt request. (Refer to Figure 2.1.2.)

When completing the process in the interrupt routine and returning to the original routine, the contents of registers stored in the stack area are restored into the original registers in the reverse sequence ( $PS \rightarrow PC \rightarrow PG$ ) by executing the **RTI** instruction. The contents of S is returned to the state before accepting an interrupt request.

The same operation is performed during a subroutine call, however, the contents of PS is not automatically stored. (The contents of PG may not be stored. This depends on the addressing mode.)

The user should store registers other than those described above with software when the user needs them during interrupts or subroutine calls.

Additionally, initialize S at the beginning of the program because its contents are undefined at reset. The stack area changes when subroutines are nested or when multiple interrupt requests are accepted. Therefore, make sure of the subroutine's nesting depth not to destroy the necessary data.

#### Note: Refer to "7751 Series Software Manual" for addressing modes.

Fig. 2.1.2 Stored registers of the stack area

#### 2.1 Central processing unit

#### 2.1.5 Program counter (PC)

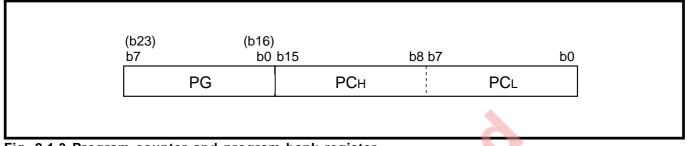

The program counter is a 16-bit counter that indicates the low-order 16 bits of the address (24 bits) at which an instruction to be executed next (in other words, an instruction to be read out from an instruction queue buffer next) is stored. The contents of the high-order program counter (PC<sub>H</sub>) become "FF<sub>16</sub>," and the low-order program counter (PC<sub>L</sub>) becomes "FE<sub>16</sub>" at reset. The contents of the program counter becomes the contents of the reset's vector address (addresses FFFE<sub>16</sub>, FFFF<sub>16</sub>) immediately after reset. Figure 2.1.3 shows the program counter and the program bank register.

Fig. 2.1.3 Program counter and program bank register

#### 2.1.6 Program bank register (PG)

The program bank register is an 8-bit register. This register indicates the high-order 8 bits (bank) of the address (24 bits) at which an instruction to be executed next (in other words, an instruction to be read out from an instruction queue buffer next) is stored. These 8 bits are called bank.

When a carry occurs after adding the contents of the program counter or adding the offset value to the contents of the program counter in the branch instruction and others, the contents of the program bank register is automatically incremented by 1. When a borrow occurs after subtracting the contents of the program counter, the contents of the program bank register is automatically decremented by 1. Accordingly, there is no need to consider bank boundaries in programming, usually.

In the single-chip mode, make sure to prevent the program bank register from being set to the value other than "0016" by executing the branch instructions and others. It is because the access space of the single-chip mode is the internal area within the bank  $0_{16}$ .

This register is cleared to "0016" at reset.

#### 2.1 Central processing unit

#### 2.1.7 Data bank register (DT)

The data bank register is an 8-bit register. In the following addressing modes using the data bank register, the contents of this register is used as the high-order 8 bits (bank) of a 24-bit address to be accessed. Use the **LDT** instruction to set a value to this register.

In the single-chip mode, make sure to fix this register to " $00_{16}$ ". It is because the access space of the single-chip mode is the internal area within the bank  $0_{16}$ . This register is cleared to " $00_{16}$ " at reset.

•Addressing modes using data bank register

- •Direct indirect

- •Direct indexed X indirect

- •Direct indirect indexed Y

- Absolute

- •Absolute bit

- •Absolute indexed X

- •Absolute indexed Y

- •Absolute bit relative

- •Stack pointer relative indirect indexed Y

- •Multiplied accumulation

#### 2.1.8 Direct page register (DPR)

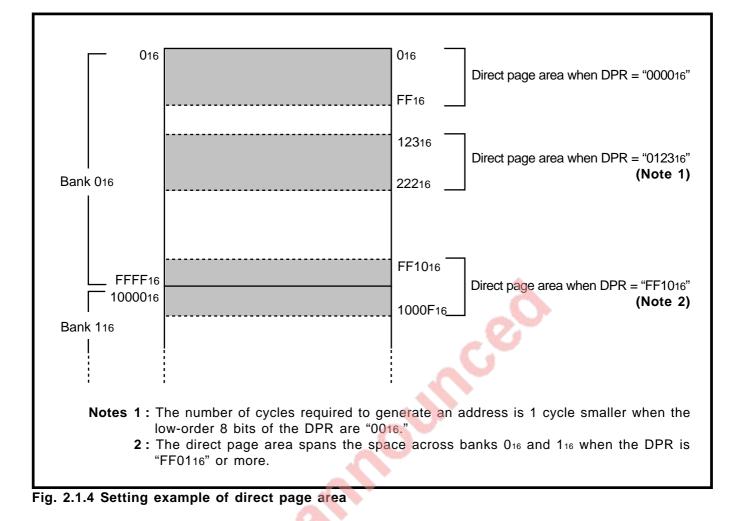

The direct page register is a 16-bit register. The contents of this register indicate the direct page area which is allocated in bank  $0_{16}$  or in the space across banks  $0_{16}$  and  $1_{16}$ . The following addressing modes use the direct page register.

The contents of the direct page register indicate the base address (the lowest address) of the direct page area. The space which extends to 256 bytes above that address is specified as a direct page.

The direct page register can contain a value from "0000<sub>16</sub>" to "FFFF<sub>16</sub>." When it contains a value equal to or more than "FF01<sub>16</sub>," the direct page area spans the space across banks 0<sub>16</sub> and 1<sub>16</sub>.

When the contents of low-order 8 bits of the direct page register is "00<sub>16</sub>," the number of cycles required to generate an address is 1 cycle smaller than the number when its contents are not "00<sub>16</sub>." Accordingly, the access efficiency can be enhanced in this case.

This register is cleared to "000016" at reset.

Figure 2.1.4 shows a setting example of the direct page area.

- •Addressing modes using direct page register

- Direct

- Direct bit

- •Direct indexed X

- •Direct indexed Y

- Direct indirect

- •Direct indexed X indirect

- •Direct indirect indexed Y

- Direct indirect long

- •Direct indirect long indexed Y

- Direct bit relative

2.1 Central processing unit

## 2.1 Central processing unit

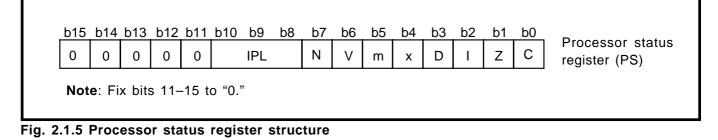

#### 2.1.9 Processor status register (PS)

The processor status register is an 11-bit register.

Figure 2.1.5 shows the structure of the processor status register.

#### (1) Bit 0: Carry flag (C)

It retains a carry or a borrow generated in the arithmetic and logic unit (ALU) during an arithmetic operation. This flag is also affected by shift and rotate instructions. When the **BCC** or **BCS** instruction is executed, this flag's contents determine whether the program causes a branch or not. Use the **SEC** or **SEP** instruction to set this flag to "1," and use the **CLC** or **CLP** instruction to clear it to "0."

#### (2) Bit 1: Zero flag (Z)

It is set to "1" when a result of an arithmetic operation or data transfer is "0," and cleared to "0" when otherwise. When the **BNE** or **BEQ** instruction is executed, this flag's contents determine whether the program causes a branch or not.

Use the SEP instruction to set this flag to "1," and use the CLP instruction to clear it to "0."

Note: This flag is invalid in the decimal mode addition (the ADC instruction).

#### (3) Bit 2: Interrupt disable flag (I)

It disables all maskable interrupts (interrupts other than watchdog timer, the **BRK** instruction, and zero division). Interrupts are disabled when this flag is "1." When an interrupt request is accepted, this flag is automatically set to "1" to avoid multiple interrupts. Use the **SEI** or **SEP** instruction to set this flag to "1," and use the **CLI** or **CLP** instruction to clear it to "0." This flag is set to "1" at reset.

#### (4) Bit 3: Decimal mode flag (D)

It determines whether addition and subtraction are performed in binary or decimal. Binary arithmetic is performed when this flag is "0." When it is "1," decimal arithmetic is performed with each word treated as two or four digits decimal (determined by the data length flag). Decimal adjust is automatically performed. Decimal operation is possible only with the **ADC** and **SBC** instructions. Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0." This flag is cleared to "0" at reset.

#### (5) Bit 4: Index register length flag (x)

It determines whether each of index register X and index register Y is used as a 16-bit register or an 8-bit register. That register is used as a 16-bit register when this flag is "0," and as an 8-bit register when it is "1." Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0." This flag is cleared to "0" at reset.

Note: When transferring data between registers which are different in bit length, the data is transferred with the length of the destination register, but except for the TXA, TYA, TXB, TYB, and TXS instructions. Refer to "7751 Series Software Manual" for details.

#### (6) Bit 5: Data length flag (m)

It determines whether to use a data as a 16-bit unit or as an 8-bit unit. A data is treated as a 16-bit unit when this flag is "0," and as an 8-bit unit when it is "1."

Use the **SEM** or **SEP** instruction to set this flag to "1," and use the **CLM** or **CLP** instruction to clear it to "0." This flag is cleared to "0" at reset.

Note: When transferring data between registers which are different in bit length, the data is transferred with the length of the destination register, but except for the TXA, TYA, TXB, TYB, and TXS instructions. Refer to "7751 Series Software Manual" for details.

#### (7) Bit 6: Overflow flag (V)

It is used when adding or subtracting with a word regarded as signed binary. When the data length flag (m) is "0," the overflow flag is set to "1" when the result of addition or subtraction exceeds the range between -32768 and +32767, and cleared to "0" in all other cases. When the data length flag (m) is "1," the overflow flag is set to "1" when the result of addition or subtraction exceeds the range between -128 and +127, and cleared to "0" in all other cases.

The overflow flag is also set to "1" when a result of division exceeds the register length to be stored in the **DIV** or **DIVS** instruction, a division instruction with unsigned or signed; and when a result of addition exceeds the range between -2147483648 and +2147483647 in the **RMPA** instruction, a Repeat MultiPly and Accumulate instruction.

When the **BVC** or **BVS** instruction is executed, this flag's contents determine whether the program causes a branch or not.

Use the SEP instruction to set this flag to "1," and use the CLV or CLP instruction to clear it to "0."

Note: This flag is invalid in the decimal mode.

#### (8) Bit 7: Negative flag (N)

It is set to "1" when a result of arithmetic operation or data transfer is negative. (Bit 15 of the result is "1" when the data length flag (m) is "0," or bit 7 of the result is "1" when the data length flag (m) is "1.") It is cleared to "0" in all other cases. When the **BPL** or **BMI** instruction is executed, this flag determines whether the program causes a branch or not. Use the **SEP** instruction to set this flag to "1," and use the **CLP** instruction to clear it to "0."

Note: This flag is invalid in the decimal mode.

#### (9) Bits 10 to 8: Processor interrupt priority level (IPL)

These three bits can determine the processor interrupt priority level to one of levels 0 to 7. The interrupt is enabled when <u>the interrupt priority level</u> of a required interrupt, which is set in each interrupt control register, is higher than IPL. When an interrupt request is accepted, IPL is stored in the stack area, and IPL is replaced by the interrupt priority level of the accepted interrupt request. There are no instruction to directly set or clear the bits of IPL. IPL can be changed by storing the new IPL into the stack area and updating the processor status register with the **PUL** or **PLP** instruction. The contents of IPL is cleared to "000<sub>2</sub>" at reset.

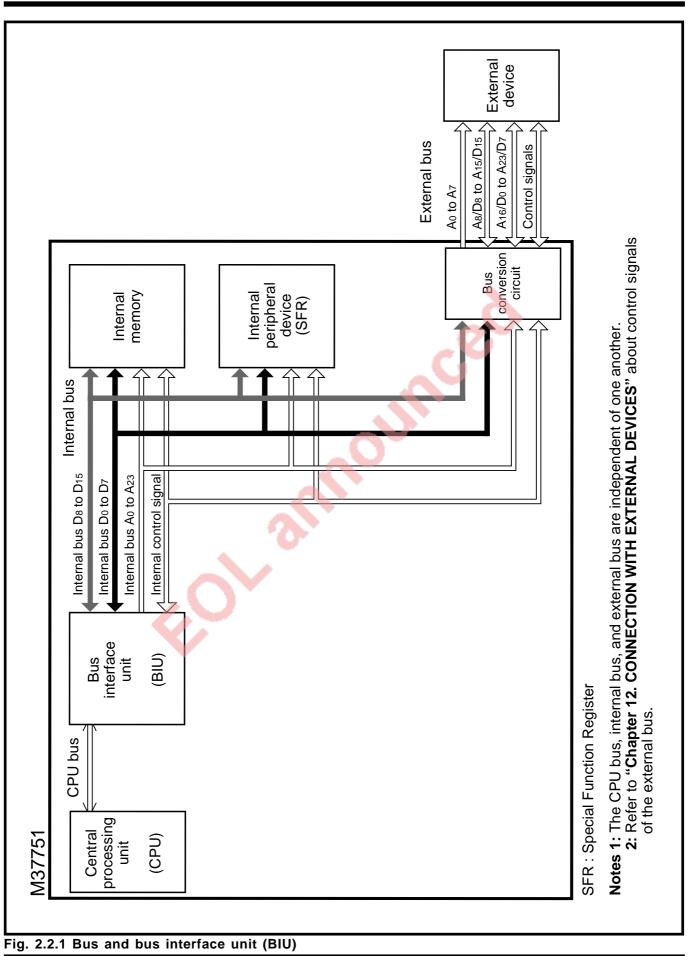

### 2.2 Bus interface unit

### 2.2 Bus interface unit

A bus interface unit (BIU) is built-in between the central processing unit (CPU) and memory•I/O devices. BIU's function and operation are described below.

When externally connecting devices, refer to "Chapter 12. CONNECTION WITH EXTERNAL DEVICES."

#### 2.2.1 Overview

Transfer operation between the CPU and memory•I/O devices is always performed via the BIU. Figure 2.2.1 shows the bus and bus interface unit (BIU).

① The BIU reads an instruction from the memory before the CPU executes it.

3

- <sup>(2)</sup> When the CPU reads data from the memory•I/O device, the CPU first specifies the address from which data is read to the BIU. The BIU reads data from the specified address and passes it to the CPU.

- ③ When the CPU writes data to the memory•I/O device, the CPU first specifies the address to which data is written to the BIU and write data. The BIU writes the data to the specified address.

- ④ To perform the above operations ① to ③, the BIU inputs and outputs the control signals, and control the bus.

7751 Group User's Manual

2.2 Bus interface unit

## 2.2 Bus interface unit

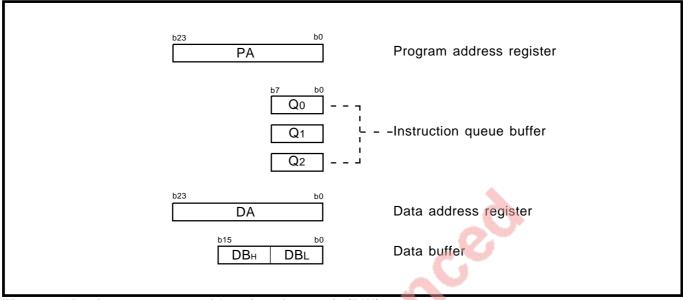

#### 2.2.2 Functions of bus interface unit (BIU)

The bus interface unit (BIU) consists of four registers shown in Figure 2.2.2. Table 2.2.1 lists the functions of each register.

Fig. 2.2.2 Register structure of bus interface unit (BIU)

| Table 2.2.1 Functions of each register |

|----------------------------------------|

|----------------------------------------|

| Name                     | Functions                                                                      |

|--------------------------|--------------------------------------------------------------------------------|

| Program address register | Indicates the storage address for the instruction which is next taken into the |

|                          | instruction queue buffer.                                                      |

| Instruction queue buffer | Temporarily stores the instruction which has been taken in.                    |

| Data address register    | Indicates the address for the data which is next read from or written to.      |

| Data buffer              | Temporarily stores the data which is read from the memory-I/O device by the    |

|                          | BIU or which is written to the memory•I/O device by the CPU.                   |

#### 2.2 Bus interface unit

The CPU and the bus send or receive data via BIU because each operates based on different clocks (Note). The BIU allows the CPU to operate at high speed without waiting for access to the memory • I/O devices that require a long access time.

The BIU's functions are described bellow.

**Note:** The CPU operates based on  $\phi$ CPU. The period of  $\phi$ CPU is normally the same as that of  $\phi$ . The internal bus operates based on the  $\overline{E}$  signal. The period of the  $\overline{E}$  signal is twice that of  $\phi$  at a minimum.

#### (1) Reading out instruction (Instruction prefetch)

When the CPU does not require to read or write data, that is, when the bus is not in use, the BIU reads instructions from the memory and stores them in the instruction queue buffer. This is called instruction prefetch.

The CPU reads instructions from the instruction queue buffer and executes them, so that the CPU can operate at high speed without waiting for access to the memory which requires a long access time.

When the instruction queue buffer becomes empty or contains only 1 byte of an instruction, the BIU performs instruction prefetch. The instruction queue buffer can store instructions up to 3 bytes.

The contents of the instruction queue buffer is initialized when a branch or jump instruction is executed, and the BIU reads a new instruction from the destination address.

When instructions in the instruction queue buffer are insufficient for the CPU's needs, the BIU extends the pulse duration of clock  $\phi_{CPU}$  in order to keep the CPU waiting until the BIU fetches the required number of instructions or more.

#### (2) Reading data from memory•I/O device

The CPU specifies the storage address of data to be read to the BIU's data address register, and requires data. The CPU waits until data is ready in the BIU.

The BIU outputs the address received from the CPU onto the address bus, reads contents at the specified address, and takes it into the data buffer.

The CPU continues processing, using data in the data buffer.

However, if the BIU uses the bus for instruction prefetch when the CPU requires to read data, the BIU keeps the CPU waiting.

#### (3) Writing data to memory-I/O device

The CPU specifies the address of data to be written to the BIU's data address register. Then, the CPU writes data into the data buffer. The BIU outputs the address received from the CPU onto the address bus and writes data in the data buffer into the specified address.

The CPU advances to the next processing without waiting for completion of BIU's write operation. However, if the BIU uses the bus for instruction prefetch when the CPU requires to write data, the BIU keeps the CPU waiting.

### 2.2 Bus interface unit

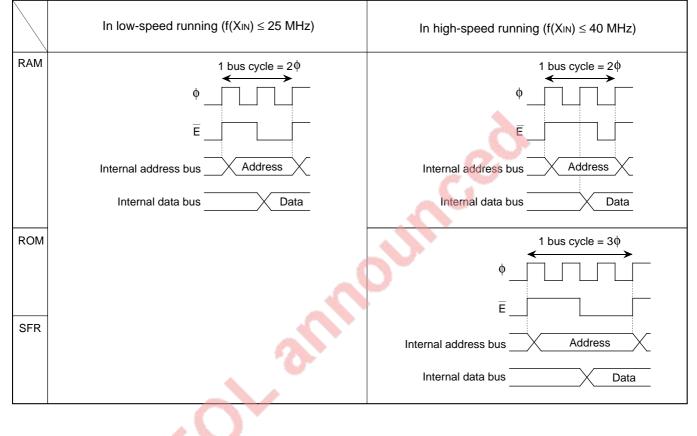

#### (4) Bus control

To perform the above operations (1) to (3), the BIU inputs and outputs the control signals, and controls the address bus and the data bus. The cycle in which the BIU controls the bus and accesses the memory•I/O device is called the bus cycle. Table 2.2.2 shows the bus cycle at accessing the internal area.

Refer to "Chapter 12. CONNECTION WITH EXTERNAL DEVICES" about the bus cycle at accessing the external devices.

#### 2.2 Bus interface unit

#### 2.2.3 Operation of bus interface unit (BIU)

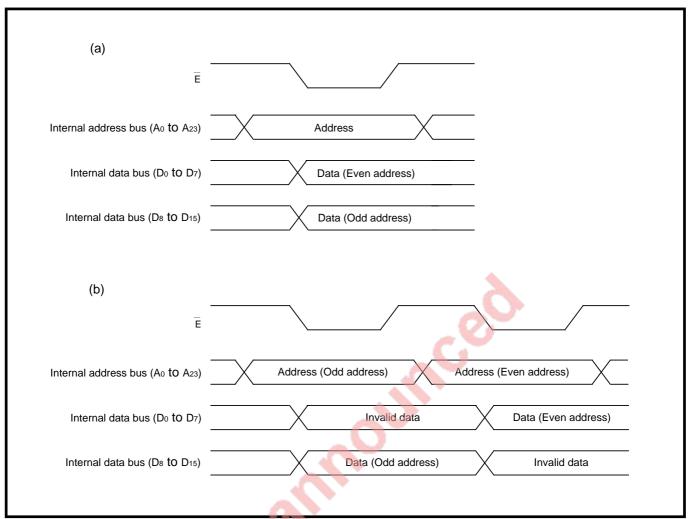

Figure 2.2.3 shows the basic operating waveforms of the bus interface unit (BIU).

About signals which are input/output externally when accessing external devices, refer to "Chapter 12. CONNECTION WITH EXTERNAL DEVICES."

#### (1) When fetching instructions into the instruction queue buffer

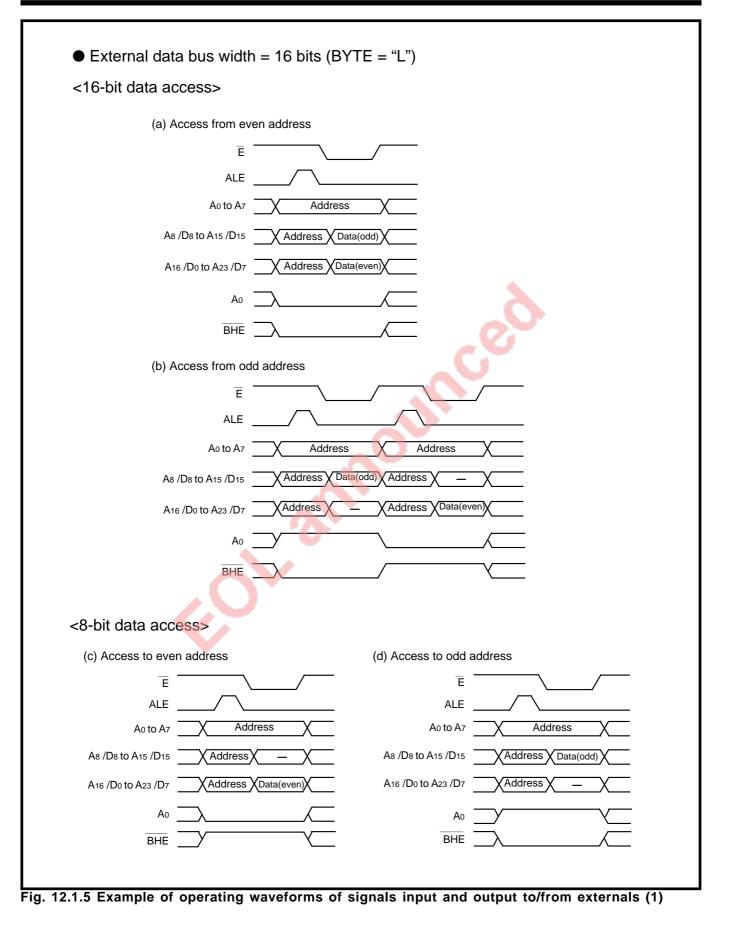

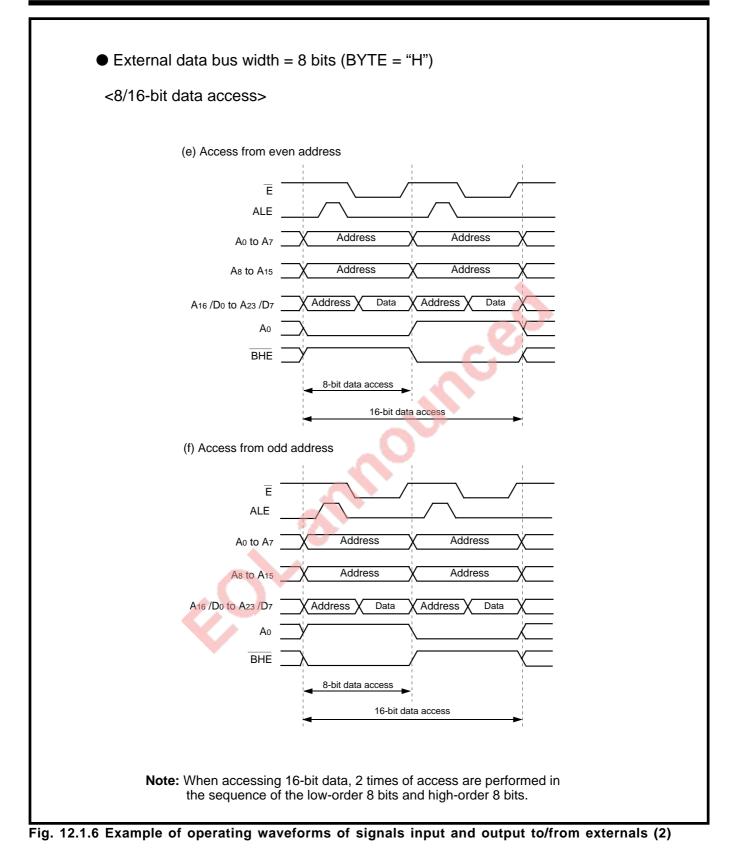

① When the instruction which is next fetched is located at an even address, the BIU fetches 2 bytes at a time with the timing of waveform (a).

However, when accessing an external device which is connected with the 8-bit external data bus width (BYTE = "H"), only 1 byte is fetched.

② When the instruction which is next fetched is located at an odd address, the BIU fetches only 1 byte with the timing of waveform (a). The contents at the even address are not taken.

#### (2) When reading or writing data to and from the memory•I/O device

- ① When accessing a 16-bit data which begins at an even address, waveform (a) is applied. The 16 bits of data are accessed at a time.

- ② When accessing a 16-bit data which begins at an odd address, waveform (b) is applied. The 16 bits of data are accessed separately in 2 operations, 8 bits at a time. Invalid data is not fetched into the data buffer.

- <sup>③</sup> When accessing an 8-bit data at an even address, waveform (a) is applied. The data at the odd address is not fetched into the data buffer.

- ④ When accessing an 8-bit data at an odd address, waveform (a) is applied. The data at the even address is not fetched into the data buffer.

For instructions that are affected by the data length flag (m) and the index register length flag (x), operation ① or ② is applied when flag m or x = "0"; operation ③ or ④ is applied when flag m or x = "1."

### 2.2 Bus interface unit

Fig. 2.2.3 Basic operating waveforms of bus interface unit (BIU)

2.3 Access space

### 2.3 Access space

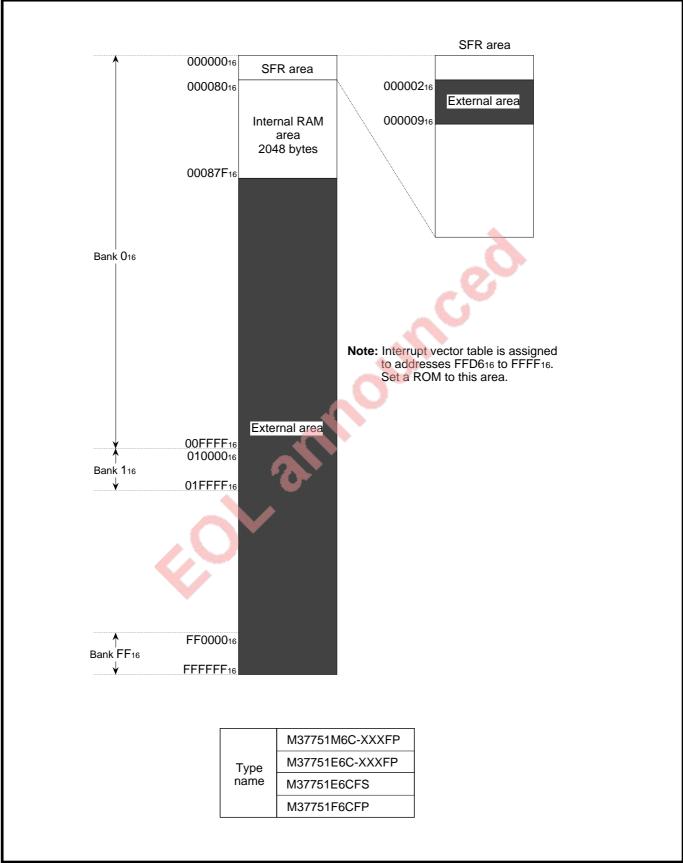

Figure 2.3.1 shows the M37751's access space.

By combination of the program counter (PC), which is 16 bits of structure, and the program bank register (PG), a 16-Mbyte space from addresses  $0_{16}$  to FFFFF<sub>16</sub> can be accessed. For details about access of an external area, refer to "Chapter 12. CONNECTION WITH EXTERNAL DEVICES."

The memory and I/O devices are allocated in the same access space. Accordingly, it is possible to perform transfer and arithmetic operations using the same instructions without discrimination of the memory from I/O devices.

Fig. 2.3.1 M37751's access space

## 2.3 Access space

### 2.3.1 Banks

The access space is divided in units of 64 Kbytes. This unit is called "bank." The high-order 8 bits of address (24 bits) indicate a bank, which is specified by the program bank register (PG) or data bank register (DT). Each bank can be accessed efficiently by using an addressing mode that uses the data bank register (DT).

If the program counter (PC) overflows at a bank boundary, the contents of the program bank register (PG) is incremented by 1. If a borrow occurs in the program counter (PC) as a result of subtraction, the contents of the program bank register (PG) is decremented by 1. Normally, accordingly, the user can program without concern for bank boundaries.

SFR (Special Function Register), internal RAM, and internal ROM are assigned in bank 016. For details, refer to section **"2.4 Memory assignment."**

### 2.3.2 Direct page

A 256-byte space specified by the direct page register (DPR) is called "direct page." A direct page is specified by setting the base address (the lowest address) of the area to be specified as a direct page into the direct page register (DPR).

By using a direct page addressing mode, a direct page can be accessed with less instruction cycles than otherwise.

Note: Refer also to section "2.1 Central processing unit."

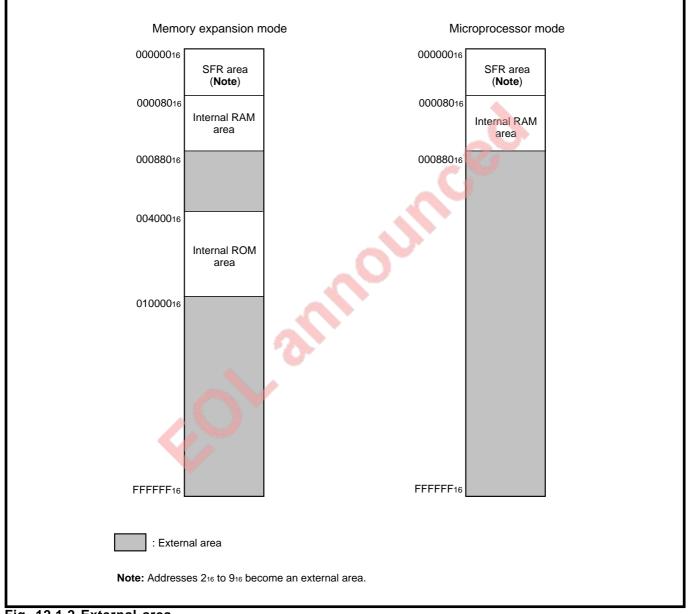

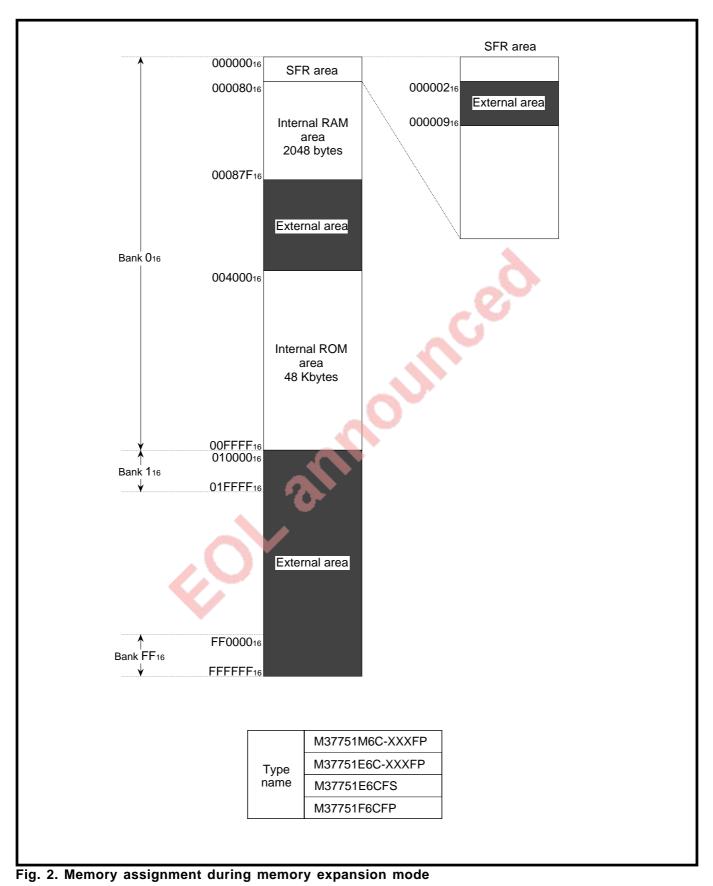

## 2.4 Memory assignment

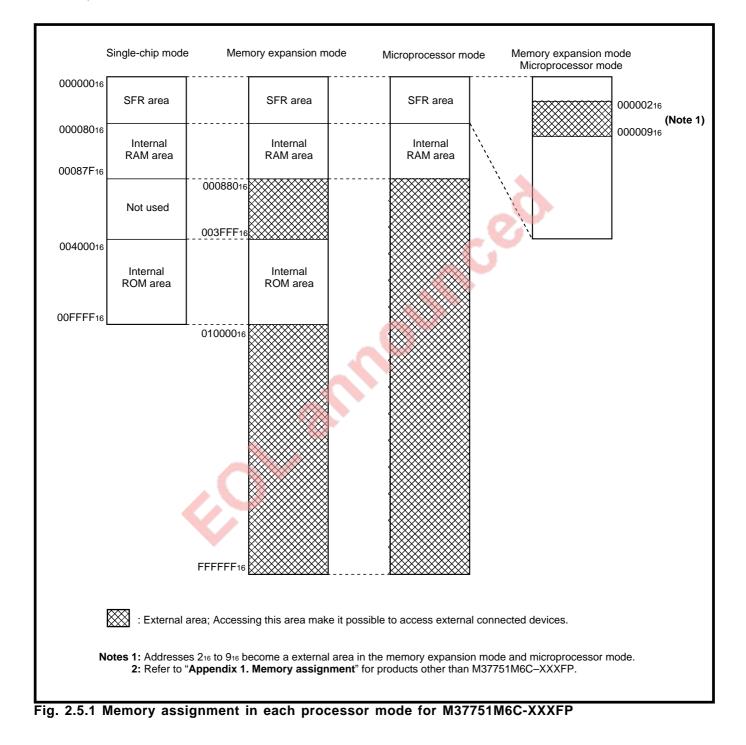

This section describes the internal area's memory assignment. For more information about the external area, refer also to section "2.5 Processor modes."

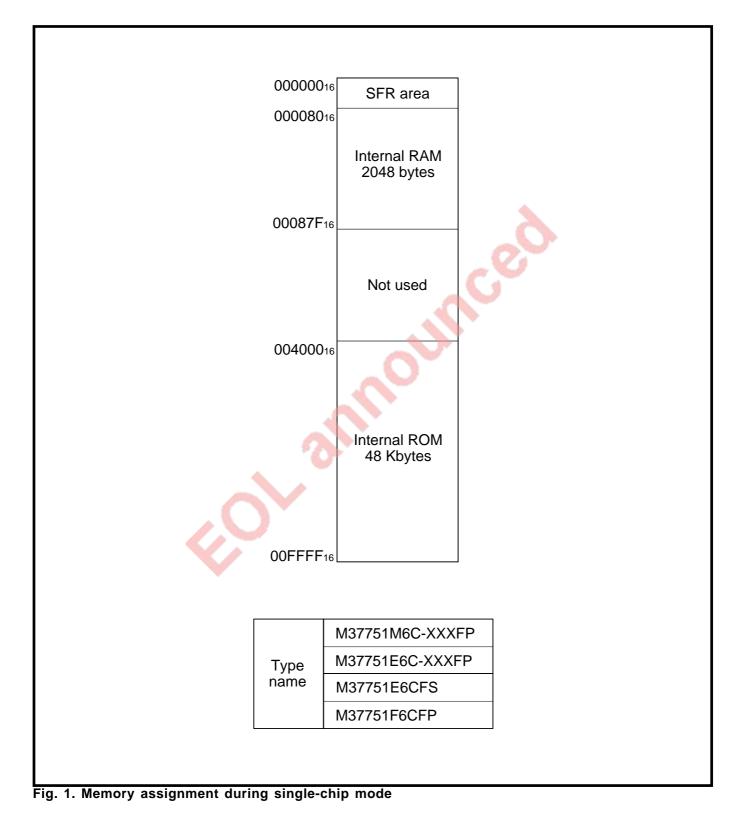

### 2.4.1 Memory assignment in internal area

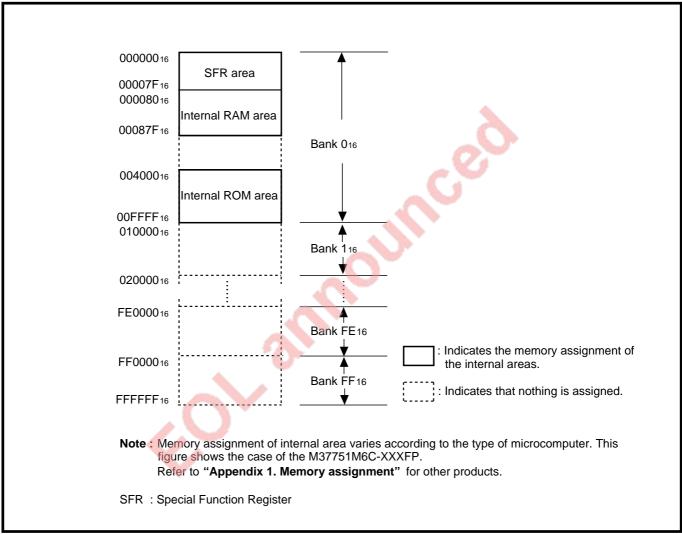

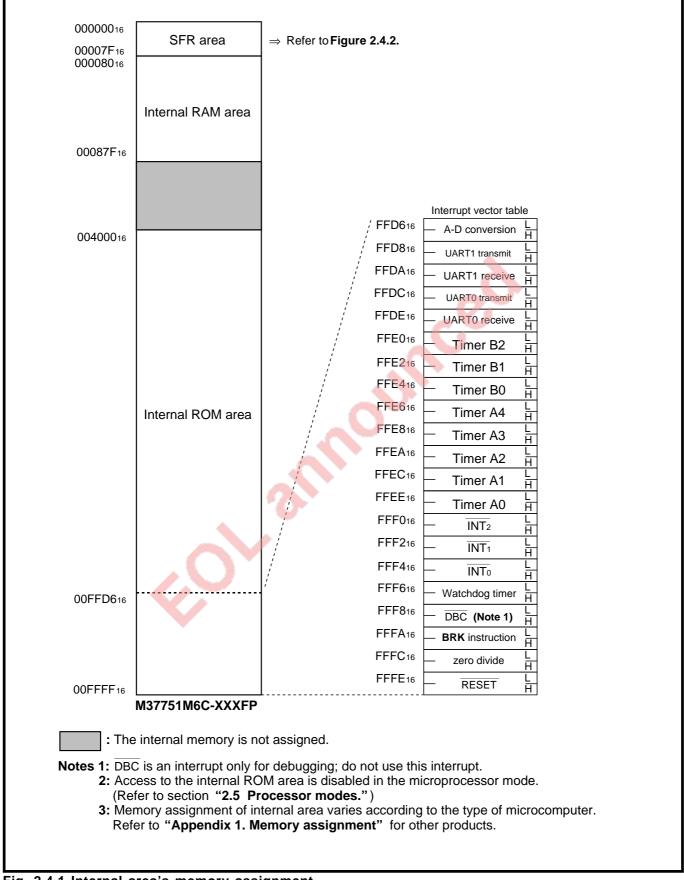

SFR (Special Function Register), internal RAM, and internal ROM are assigned in the internal area. Figure 2.4.1 shows the internal area's memory assignment.

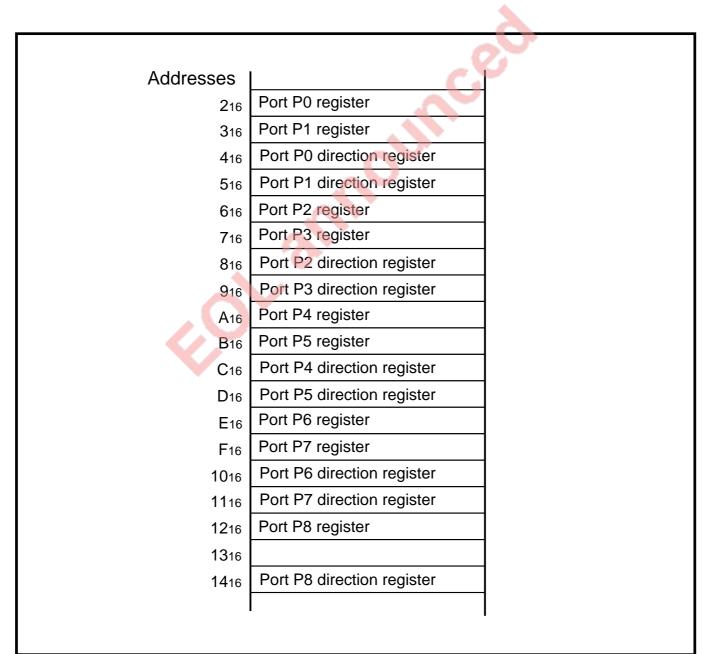

#### (1) SFR area

The registers for setting internal peripheral devices are assigned at addresses 0<sub>16</sub> to 7F<sub>16</sub>. This area is called SFR (Special Function Register). Figure 2.4.2 shows the SFR area's memory assignment. For each register in the SFR area, refer to each functional description in this manual.

For the state of the SFR area immediately after a reset, refer to section "13.1.2 State of CPU, SFR area, and internal RAM area."

### (2) Internal RAM area

The M37751M6C-XXXFP (See **Note**) assigns the 2048-byte static RAM at addresses 80<sub>16</sub> to 87F<sub>16</sub>. The internal RAM area is used as a stack area, as well as an area to store data. Accordingly, note that set the nesting depth of a subroutine and multiple interrupts' level not to destroy the necessary data.

### (3) Internal ROM area

The M37751M6C-XXXFP (See **Note**) assigns the 48-Kbyte mask RAM at addresses 4000<sub>16</sub> to FFFF<sub>16</sub>. Its addresses FFD6<sub>16</sub> to FFFF<sub>16</sub> are the vector addresses, which are called the interrupt vector table, for reset and interrupts. In the microprocessor mode where use of the internal ROM area is inhibited, assign a ROM at addresses FFD6<sub>16</sub> to FFFF<sub>16</sub>.

Note : Refer to "Appendix 1. Memory assignment" for other products.

## 2.4 Memory assignment

Fig. 2.4.1 Internal area's memory assignment

2.4 Memory assignment

| Addres       | SS                                        |

|--------------|-------------------------------------------|

| 016          |                                           |

| 116          |                                           |

| 216          | Port P0 register                          |

| 316          | Port P1 register                          |

| 416          | Port P0 direction register                |

| 516          | Port P1 direction register                |

| 616          | Port P2 register                          |

| 716          | Port P3 register                          |

| 816          | Port P2 direction register                |

| 916          | Port P3 direction register                |

| A16          | Port P4 register                          |

| B16          | Port P5 register                          |

| C16          | Port P4 direction register                |

| D16          | Port P5 direction register                |

| E16          | Port P6 register                          |

| F16          | Port P7 register                          |

| 1016         | Port P6 direction register                |

| 1116         | Port P7 direction register                |

| 1216         | Port P8 register                          |

| 1316         | Port PS direction register                |

| 1416<br>1516 | Port P8 direction register                |

| 1516<br>1616 |                                           |

| 1616<br>1716 |                                           |

| 1716         |                                           |

| 1916         |                                           |

| 1A16         |                                           |

| 1B16         |                                           |

| 1C16         |                                           |

| 1D16         |                                           |

| 1E16         | A-D control register 0                    |

| 1F16         | A-D control register 1                    |

| 2016         |                                           |

| 2116         | A-D register 0                            |

| 2216         | A-D register 1                            |

| 2316         |                                           |

| 2416         | A-D register 2                            |

| 2516         |                                           |

| 2616         | A-D register 3                            |

| 2716         |                                           |

| 2816         | A-D register 4                            |

| 2916         |                                           |

| 2A16         | A-D register 5                            |

| 2B16         |                                           |

| 2C16<br>2D16 | A-D register 6                            |

| 2D16<br>2E16 |                                           |

| 2E16<br>2F16 | A-D register 7                            |

| 3016         | UART0 transmit/receive mode register      |

| 3116         | UARTO baud rate register (BRG0)           |

| 3216         |                                           |

| 3316         | UART0 transmit buffer register            |

| 3416         | UART0 transmit/receive control register 0 |

| 3516         | UART0 transmit/receive control register 1 |

| 3616         |                                           |

| 3716         | UART0 receive buffer register             |

| 3816         | UART1 transmit/receive mode register      |

| 3916         | UART1 baud rate register (BRG1)           |

| 3A16         | UART1 transmit buffer register            |

| 3B16         | -                                         |

| 3C16         | UART1 transmit/receive control register 0 |

| 3D16         | UART1 transmit/receive control register 1 |

| 3E16         | UART1 receive buffer register             |

| 3F16         |                                           |

|              |                                           |

| Addres        | S                                                                       |

|---------------|-------------------------------------------------------------------------|

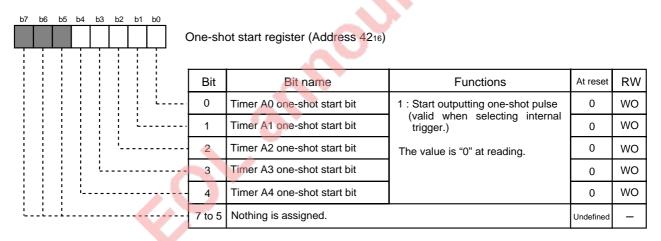

| 4016          | Count start register                                                    |

| 4116          |                                                                         |

| 4216<br>4316  | One-shot start register                                                 |

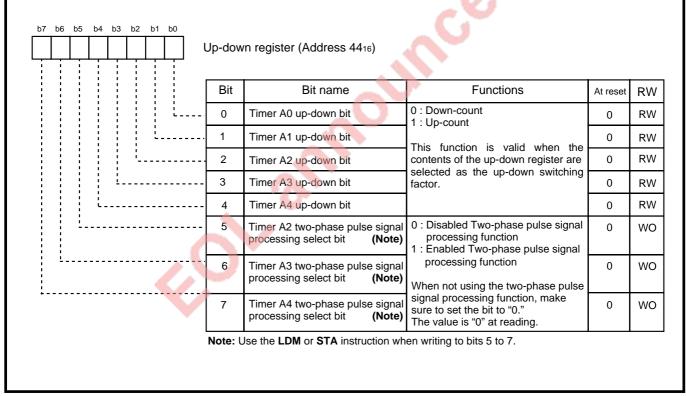

| 4316          | Up-down register                                                        |

| 4516          |                                                                         |

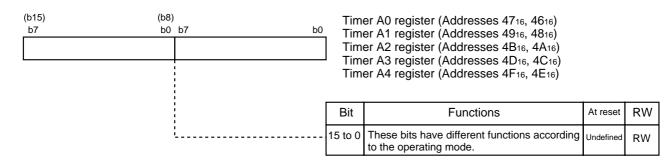

| 4616          | Timer A0 register                                                       |

| 4716          |                                                                         |

| 4816<br>4916  | Timer A1 register                                                       |

| 4916<br>4A16  |                                                                         |

| 4B16          | Timer A2 register                                                       |

| 4C16          | Timer A3 register                                                       |

| 4D16          |                                                                         |

| 4E16<br>4F16  | Timer A4 register                                                       |

| 4F 16<br>5016 |                                                                         |

| 5116          | Timer B0 register                                                       |

| 5216          | Timer B1 register                                                       |

| 5316          |                                                                         |

| 5416          | Timer B2 register                                                       |

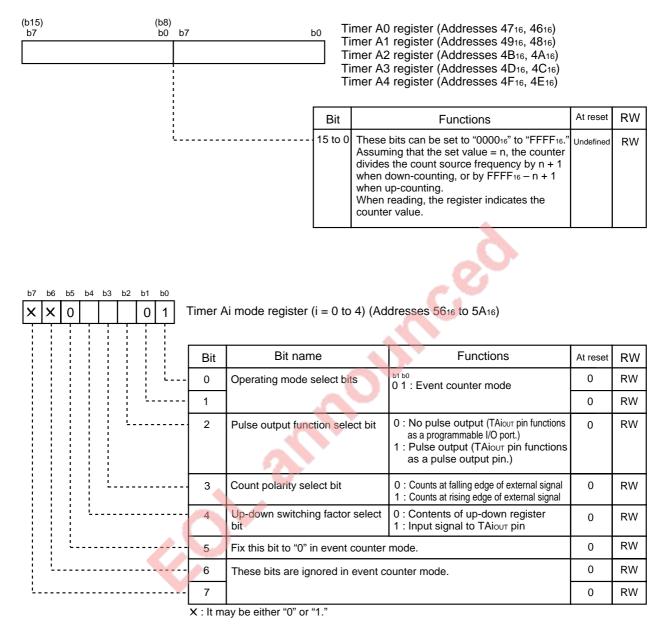

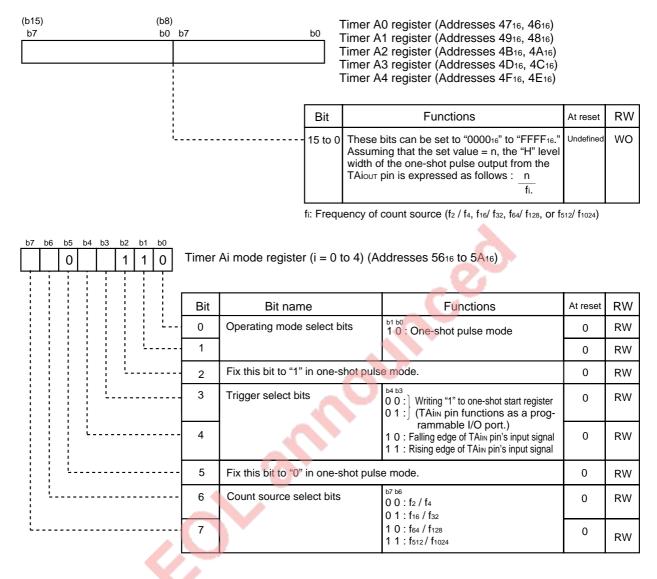

| 5516<br>5616  | Timer A0 mode register                                                  |

| 5016<br>5716  | Timer A1 mode register                                                  |

| 5816          | Timer A2 mode register                                                  |

| 5916          | Timer A3 mode register                                                  |

| 5A16          | Timer A4 mode register                                                  |

| 5B16          | Timer B0 mode register                                                  |

| 5C16          | Timer B1 mode register                                                  |

| 5D16          | Timer B2 mode register                                                  |

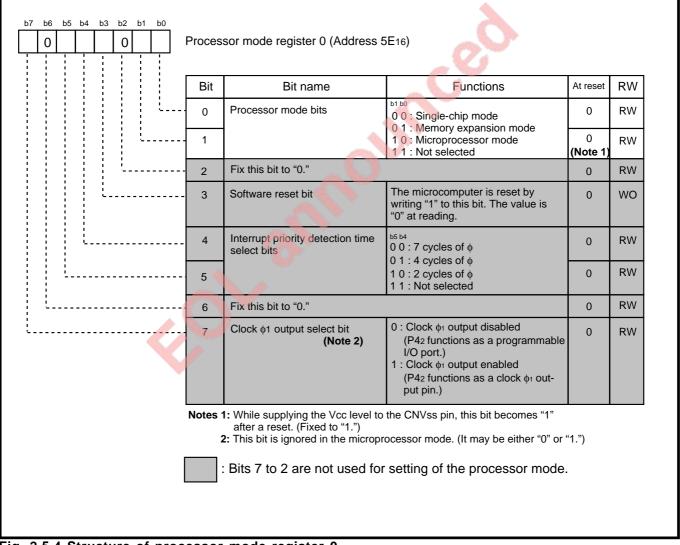

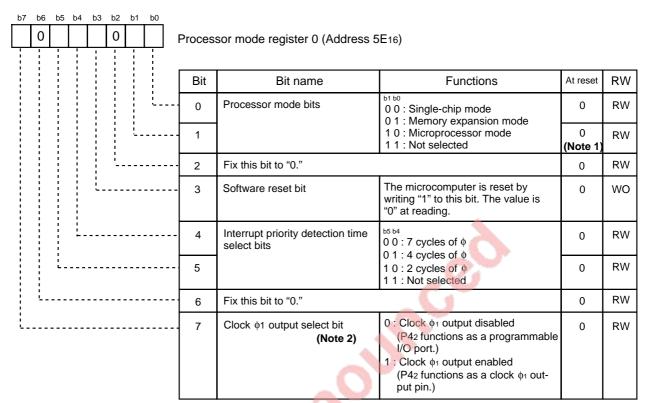

| 5E16          | Processor mode register 0                                               |

| 5F16          | Processor mode register 1                                               |

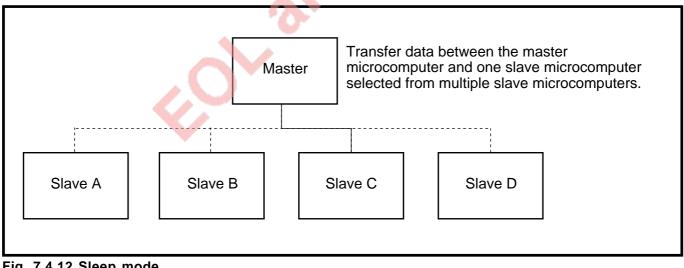

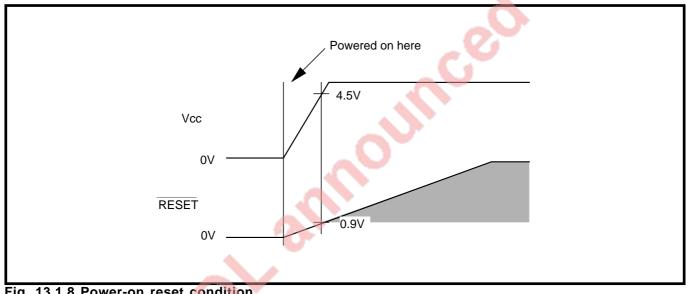

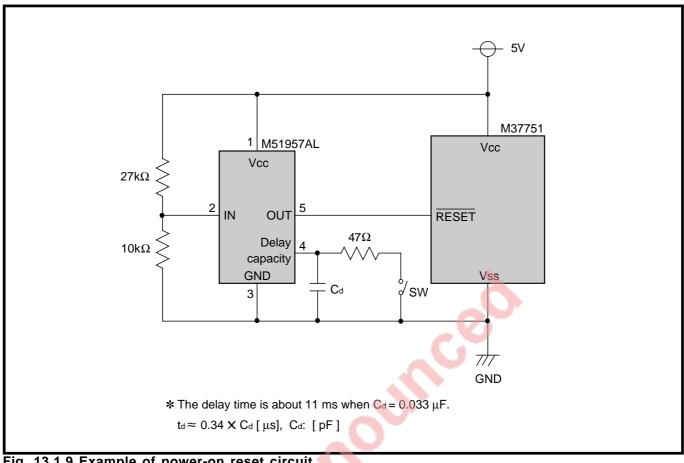

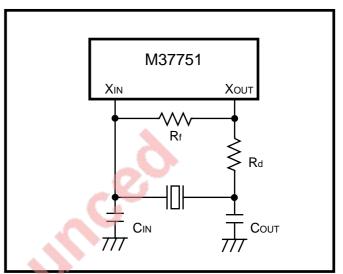

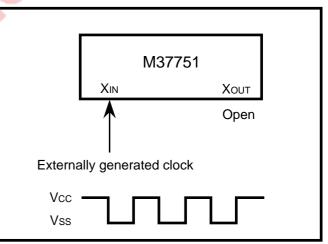

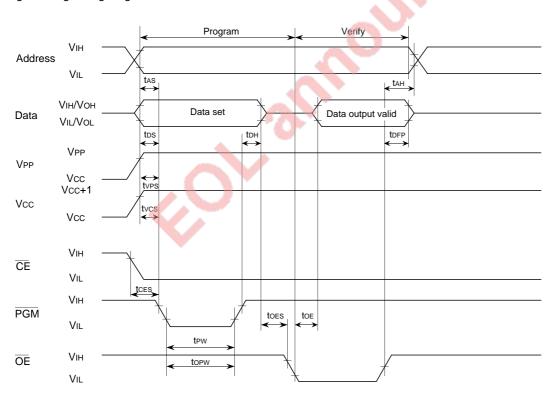

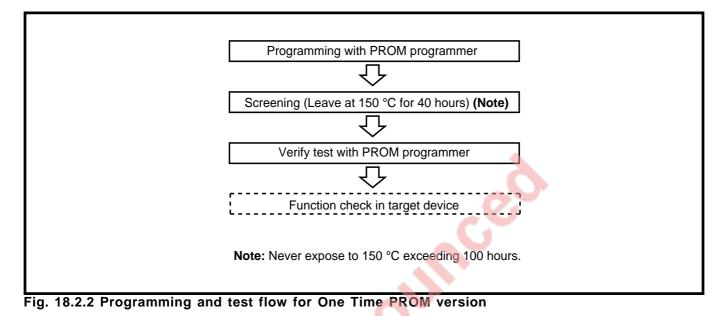

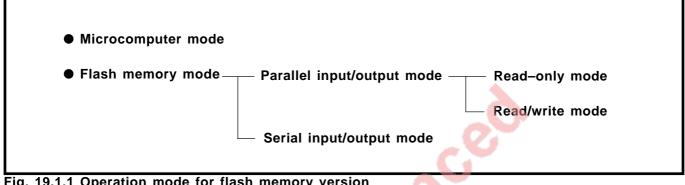

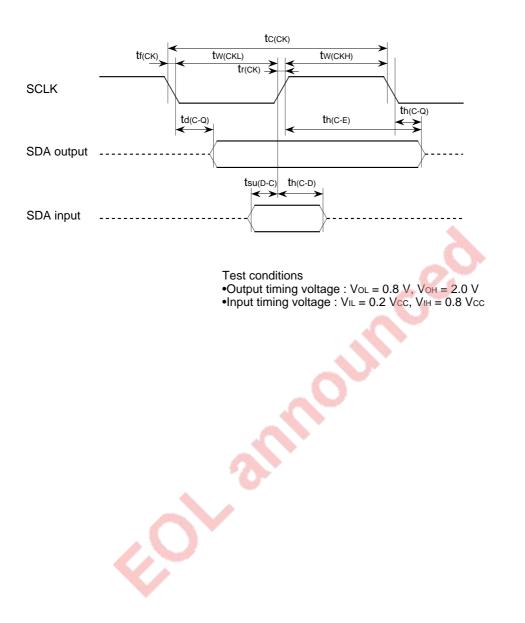

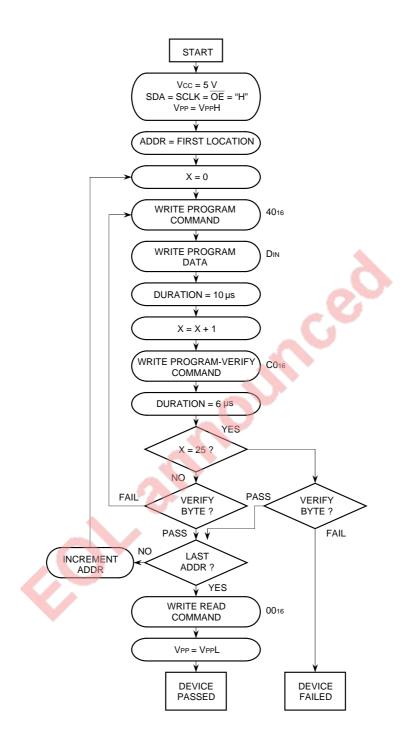

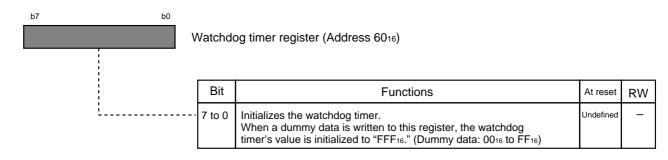

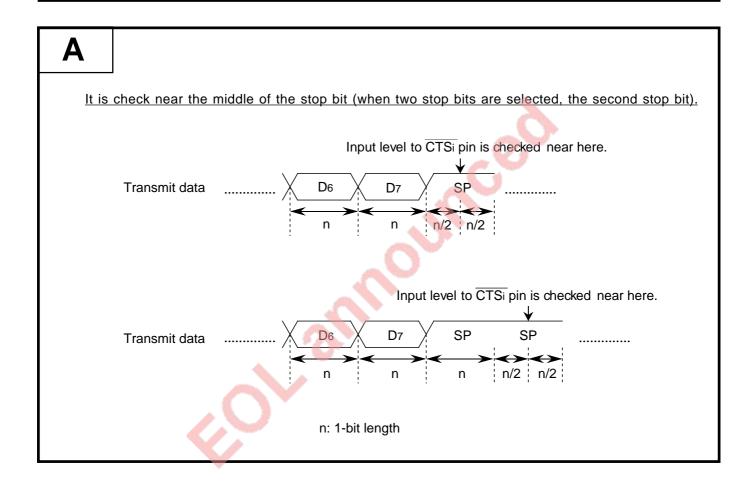

| 6016          | Watchdog timer register                                                 |