# PRELIMINARY PRODUCT INFORMATION

# mos integrated circuit $\mu PD78P054Y$

## 8-BIT SINGLE-CHIP MICROCOMPUTER

#### **DESCRIPTION**

The  $\mu$ PD78P054Y is a product in which the on-chip mask ROM of the  $\mu$ PD78054Y is replaced by one-time PROM which can be written to once only, or by EPROM which can be programmed, erased, and reprogrammed.

As program write by user is possible, the  $\mu$ PD78P054Y is best suited for evaluation, short-run and multiple-device production, and early rise upon system development.

Functions are described in detail in the following User's Manual, which should be read when carrying out design work.

$\mu$ PD78054Y Series User's Manual (Preliminary): In preparation

#### **FEATURES**

- Pin compatible with mask ROM products (except the VPP pin)

- Internal PROM: 32K bytes\*

- Internal high-speed RAM: 1024 bytes\*

- Buffer RAM : 32 bytes

- Operable in the same range of supply voltage as mask ROM products (2.0 to 6.0 V)

- Internal PROM and internal high-speed RAM capacities can be changed by memory size switching register.

#### **Differs from Mask ROM Products in Following Points -**

- The same memory mapping as mask ROM products is enabled by setting the memory size switching register.

- Pins P60 to P63 do not incorporate a pull-up resistor.

#### **ORDERING INFORMATION**

| Ordering Code    | Package                                       | On-Chip ROM   |

|------------------|-----------------------------------------------|---------------|

| μPD78P054YGC-3B9 | 80-pin plastic QFP (□14 mm)                   | One-Time PROM |

| μPD78P054YGK-BE9 | 80-pin plastic TQFP (□12 mm)                  | One-Time PROM |

| μPD78P054YKK-T   | 80-pin ceramic WQFN (LCC with window)(□14 mm) | EPROM         |

In this document, "PROM" is used in parts common to one-time PROM products and EPROM products.

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

Document No. IP-3205B (0. D. No. IP-8719B) Date Published February 1994 P Printed in Japan The mark \* shows major revised points.

**■** 6427525 0082362 308 **■**

© NEC Corporation 1993

#### **QUALITY GRADE**

Standard

Please refer to "Quality grade on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

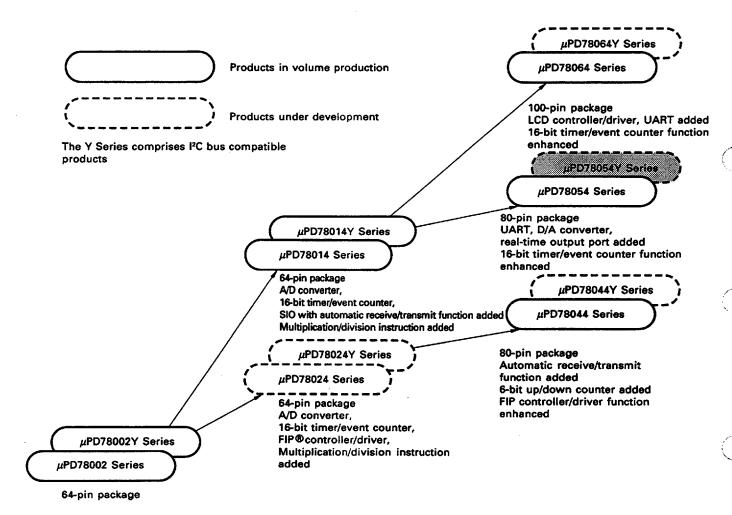

#### 78K/O SERIES DEVELOPMENT

# **FUNCTION DESCRIPTION**

|                    | ltem                               | Function                                                                                                                                                                                                |  |

|--------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Internal mem       | ory                                | PROM: 32K bytes* RAM Internal high-speed RAM: 1024 bytes* Buffer RAM: 32 bytes                                                                                                                          |  |

| Memory space       | e e                                | 64K bytes                                                                                                                                                                                               |  |

| General regis      | ter                                | 8 bits × 32 registers (8 bits × 8 registers × 4 banks)                                                                                                                                                  |  |

|                    |                                    | Instruction execution time variable function is built in.                                                                                                                                               |  |

| Instruction cycles | When main system clock is selected | 0.4μs/0.8 μs/1.6 μs/3.2 μs/6.4 μs/12.8 μs (when operating at 5.0 MHz)                                                                                                                                   |  |

|                    | When subsystem clock is selected   | 122 $\mu$ s (when operating at 32.768 kHz)                                                                                                                                                              |  |

| Instruction se     | rt                                 | <ul> <li>16-bit operation</li> <li>Multiplication/division (8 bits × 8 bits, 16 bits + 8 bits)</li> <li>Bit manipulation (set, reset, test, boolean operation)</li> <li>BCD correction, etc.</li> </ul> |  |

| I/O ports          |                                    | Total : 69  CMOS input : 2  CMOS input/output : 63  N-ch open-drain input/output : 4                                                                                                                    |  |

| A/D converter      | r                                  | 8-bit resolution × 8 ch                                                                                                                                                                                 |  |

| D/A converter      | •                                  | • 8-bit resolution × 2 ch                                                                                                                                                                               |  |

| Serial interface   |                                    | 3-wire/2-wire/l²C bus mode selectable : 1 ch     3-wire mode (with on-chip max. 32-byte auto transmitting/receiving function) : 1 ch     3-wire/UART mode selectable : 1 ch                             |  |

| Timer              |                                    | 16-bit timer/event counter : 1 ch     8-bit timer/event counter : 2 ch     Watch timer : 1 ch     Watchdog timer : 1 ch                                                                                 |  |

| Timer output       |                                    | 3 pins (14-bit PWM output enable: 1 pin)                                                                                                                                                                |  |

| Clock output       |                                    | 19.5 kHz, 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz, 2.5 MHz, and 5.0 MHz (when operating at main system clock 5.0 MHz) 32.768 kHz (when operating at subsystem clock 32.768 kHz)         |  |

| Buzzer output      |                                    | 1.2 kHz, 2.4 kHz, 4.9 kHz and 9.8 kHz<br>(when operating at main system clock 5.0 MHz)                                                                                                                  |  |

| Maskable interrupt |                                    | Internal : 13, External : 7                                                                                                                                                                             |  |

| Vectored interrupt | Non-maskable<br>interrupt          | Internal : 1                                                                                                                                                                                            |  |

| Software interrupt |                                    | Internal : 1                                                                                                                                                                                            |  |

| Test input         |                                    | Internal : 1, External : 1                                                                                                                                                                              |  |

| Operating vol      | tage range                         | V <sub>DD</sub> = 2.0 to 6.0 V                                                                                                                                                                          |  |

| Package            |                                    | 80-pin plastic QFP (□14 mm)     80-pin plastic TQFP (□12 mm)     80-pin ceramic WQFN (LCC with window) (□14 mm)                                                                                         |  |

<sup>\*</sup> Internal PROM/internal high-speed RAM capacity can be changed by the memory size switching register.

**■ 6427525 0082364 180 ■**

\_

3

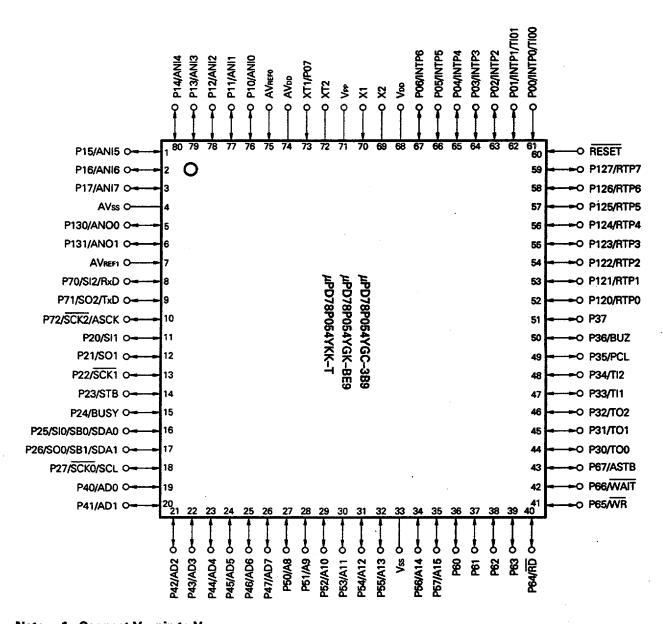

#### PIN CONFIGURATION (Top View)

#### (1) Normal operating mode

80-pin plastic QFP (□14 mm) 80-pin plastic TQFP (□12 mm) 80-pin ceramic WQFN (LCC with window)(□14 mm)

Note 1. Connect VPP pin to Vss.

- 2. Connect AVpp pin to Vpp.

- 3. Connect AVss pin to Vss.

**6427525 0082365 017**

| P00 to P07   | : | Port 0  |

|--------------|---|---------|

| P10 to P17   | : | Port 1  |

| P20 to P27   | : | Port 2  |

| P30 to P37   | : | Port 3  |

| P40 to P47   | : | Port 4  |

| P50 to P57   | : | Port 5  |

| P60 to P67   | : | Port 6  |

| P70 to P72   | : | Port 7  |

| P120 to P127 | : | Port 12 |

| P130, P131   | : | Port 13 |

RTP0 to RTP7 : Real-Time Output Port

INTP0 to INTP6 : Interrupt From Peripherals

TI00, TI01 : Timer Input

Ti1,Ti2 : Timer Input TO0 to TO2 : Timer Output SBO, SB1 : Serial Bus SIO to SI2 : Serial Input SO0 to SO2 : Serial Output SCK0 to SCK2 : Serial Clock SCL : Serial Clock SDA0, SDA1 : Serial Data

RxD : Receive Data

TxD : Transmit Data

ASCK : Asynchronous Serial Clock

PCL : Programmable Clock

BUZ : Buzzer Clock

STB : Strobe

BUSY : Busy

AD0 to AD7 : Address/ Data Bus

A8 to A15 : Address Bus

RD : Read Strobe

WR : Write Strobe

WAIT : Wait

ASTB : Address Strobe

X1, X2 : Crystal (Main System Clock)

XT1, XT2 : Crystal (Subsystem Clock)

RESET : Reset

ANI0 to ANI7 : Analog Input

ANO0, ANO1 : Analog Output

AVDD : Analog Power Supply

AVss : Analog Ground

AVREF0,1 : Analog Reference Voltage

VDD : Power Supply

VPP : Programming Power Supply

Vss : Ground

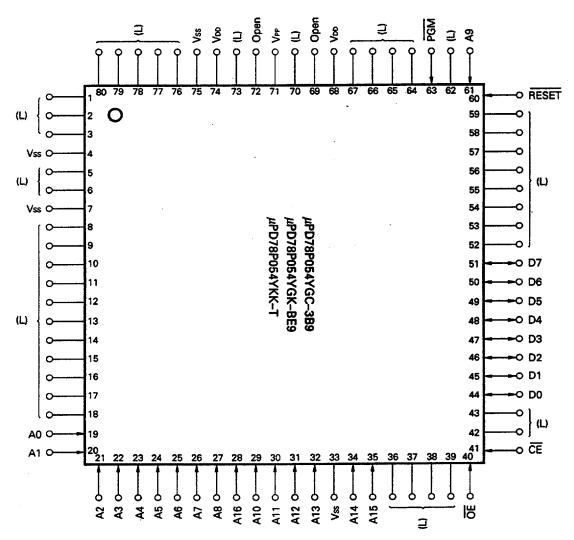

#### (2) PROM programming mode

80-pin plastic QFP (□14 mm), 80-pin plastic TQFP (□12 mm) 80-pin ceramic WQFN (LCC with window)(□14 mm)

Note 1. (L) : Individually connect to Vss via a pull-down resistor.

Vss : Connect to GND.

RESET : Set to low level.

Open : No connection

A0 to A16 : Address Bus RESET : Reset

D0 to D7 : Data Bus Vpp : Power Supply

CE : Chip Enable VPP : Programming Power Supply

OE : Output Enable Vss : Ground

PGM : Program

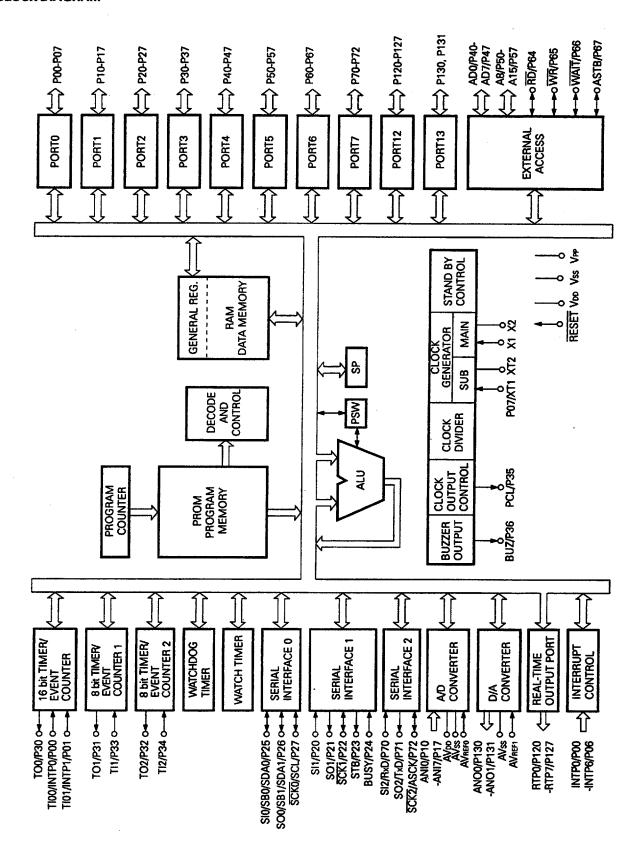

#### **BLOCK DIAGRAM**

**=** 6427525 0082368 826 **=**

# **CONTENTS**

|   | 7. | DIFFERENCES BETWEEN µPD/8P054Y AND MASK NOW PRODUCTS                    | J  |

|---|----|-------------------------------------------------------------------------|----|

|   | 2. | PIN FUNCTION TABLE                                                      | 10 |

|   |    | 2.1 PINS IN NORMAL OPERATING MODE                                       | 10 |

|   |    | 2.2 PINS IN PROM PROGRAMMING MODE                                       | 14 |

|   |    | 2.3 PIN INPUT/OUTPUT CIRCUITS AND RECOMMENDED CONNECTION OF UNUSED PINS | 15 |

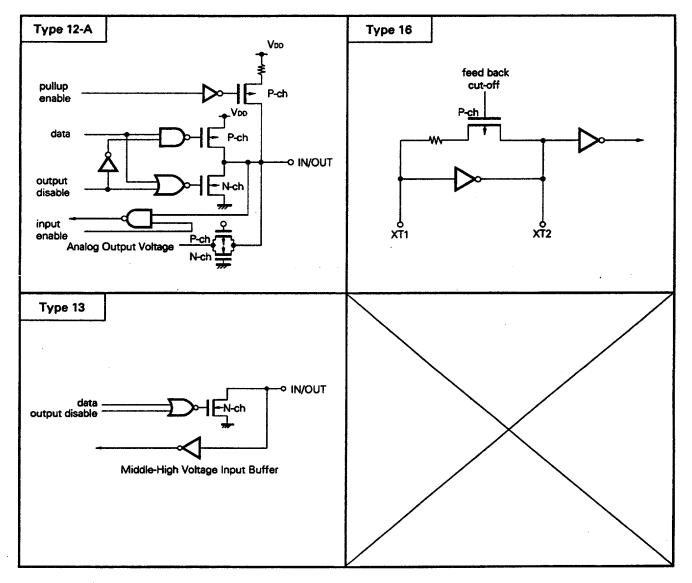

|   | 3. | MEMORY SIZE SWITCHING REGISTER (IMS)                                    | 19 |

|   | 4. | PROM PROGRAMMING                                                        |    |

|   |    | 4.1 OPERATING MODES                                                     | 20 |

|   |    | 4.2 PROM WRITE PROCEDURE                                                | 22 |

|   |    | 4.3 PROM READ PROCEDURE                                                 | 26 |

|   | 5. | ERASURE METHOD (μPD78P054YKK-T ONLY)                                    | 27 |

|   | 6. | ERASURE WINDOW SEAL (μPD78P054YKK-T ONLY)                               | 27 |

|   | 7. | ONE-TIME PROM PRODUCTS SCREENING                                        | 27 |

|   | 8. | PACKAGE INFORMATION                                                     | 28 |

|   | AP | PENDIX A. DEVELOPMENT TOOLS                                             | 31 |

| _ | AE | DENDIV D. DELATED DOCLIMENTS                                            | 34 |

#### 1. DIFFERENCES BETWEEN $\mu$ PD78P054Y AND MASK ROM PRODUCTS

The  $\mu$ PD78P054Y is a single-chip microcomputer with an on-chip one-time writable PROM or with an on-chip EPROM which has program write, erasure and rewrite capability.

It is possible to make all the functions except for PROM specification, and mask option of P60 to P63 pins, to the same as those of mask ROM products by setting the memory size switching register.

Differences between the  $\mu$ PD78P054Y and mask ROM products are shown in Table 1-1.

Table 1-1 Differences between μPD78P054Y and Mask ROM Products

| ltem                           | μPD78P054Y                           | Mask ROM Products                                   |

|--------------------------------|--------------------------------------|-----------------------------------------------------|

| IC pin                         | No                                   | Yes                                                 |

| Ver pin                        | Yes                                  | No                                                  |

| Mask option of P60 to P63 pins | Pull-up resistor is not incorporated | Pull-up resistor can be incorporated by mask option |

Note For the  $\mu$ PD78P054Y, the internal PROM/internal high-speed RAM capacities can be set by the memory size switching register.

The internal PROM becomes to 32K bytes and the internal high-speed RAM becomes 1K bytes by the RESET input.

# 2. PIN FUNCTION TABLE

# 2.1 PINS IN NORMAL OPERATING MODE

#### (1) Port pins (1/2)

| Pin Name   | input/Output |                                                 | Function                                                 | After Reset | Dual-Function Pin |

|------------|--------------|-------------------------------------------------|----------------------------------------------------------|-------------|-------------------|

| P00        | Input        |                                                 | Input only                                               | Input       | INTPO/TIOO        |

| P01        |              |                                                 |                                                          | Input       | INTP1/Ti01        |

| P02        |              |                                                 | Input/output is specifiable                              |             | INTP2             |

| P03        | Input/output | Port 0 8-bit_input/output                       | bit-wise. When used as the input port, it is possible to |             | INTP3             |

| P04        |              | port                                            | connect a pull-up resistor by software.                  |             | INTP4             |

| P05        |              |                                                 |                                                          |             | INTP5             |

| P06        |              |                                                 |                                                          |             | INTP6             |

| P07*1      | Input        |                                                 | input only                                               | Input       | XT1               |

| P10 to P17 | Input/output | Input/output is specifi<br>When used as the in  |                                                          |             |                   |

| P20        |              |                                                 |                                                          |             | SI1               |

| P21        |              |                                                 |                                                          | Input       | S01               |

| P22        |              |                                                 |                                                          |             | SCK1              |

| P23        | 1            | Port 2<br>8-bit input/output por                |                                                          |             | STB               |

| P24        | Input/output |                                                 |                                                          |             | BUSY              |

| P25        |              | connect a pull-up res                           |                                                          |             | SI0/SB0/SDA0      |

| P26        |              |                                                 |                                                          |             | SO0/SB1/SDA1      |

| P27        |              |                                                 |                                                          | ,           | SCK0/SCL          |

| P30        |              |                                                 |                                                          |             | TOO               |

| P31        | 1            |                                                 |                                                          |             | TO1               |

| P32        | 1            |                                                 |                                                          |             | TO2               |

| P33        | 1            | Port 3 8-bit input/output por                   | t                                                        |             | TI1               |

| P34        | Input/output | Input/output is specifi<br>When used as the inp | out port, it is possible to                              | Input       | TI2               |

| P35        |              | connect a pull-up res                           | istor by software.                                       |             | PCL               |

| P36        | 1            |                                                 |                                                          | BUZ         |                   |

| P37        | 1            |                                                 |                                                          |             |                   |

<sup>\* 1.</sup> When P07/XT1 pins are used as the input ports, set the processor clock control register bit 6 (FRC) to 1 (Be sure not to use the feedback resistor of the subsystem clock oscillation circuit.)

<sup>2.</sup> When P10/ANI0 to P17/ANI7 pins are used as the analog inputs for A/D converter, a pull-up resistor becomes automatically unused.

# (1) Port pins (2/2)

| Pin Name     | Input/Output | Funct                                                                                                                                                | tion                                                                                   | After Reset  | Dual-Function Pin |

|--------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------|-------------------|

| P40 to P47   | Input/output | Port 4 8-bit input/output port Input/output is specifiable a When used as the input po connect a pull-up resistor t Test flag (KRIF) is set to 1 t   | Input                                                                                  | AD0 to AD7   |                   |

| P50 to P57   | Input/output | Port 5 8-bit input/output port It is possible to directly driv Input/output is specifiable I When used as the input po- connect a pull-up resistor b | Input                                                                                  | A8 to A15    |                   |

| P60          |              |                                                                                                                                                      |                                                                                        |              |                   |

| P61          |              |                                                                                                                                                      | N-ch open-drain input/output port.                                                     | Immund       | .—                |

| P62          |              |                                                                                                                                                      | It is possible to directly drive LED.                                                  | Input        |                   |

| P63          | Input/output | Port 6<br>8-bit input/output port                                                                                                                    |                                                                                        |              |                   |

| P64          | mpayoutput   | Input/output is specifiable bit-wise.                                                                                                                | When used as the input port, it is possible to connect a pull-up resistor by software. | Input        | RD                |

| P65          |              |                                                                                                                                                      |                                                                                        |              | WR                |

| P66          |              |                                                                                                                                                      |                                                                                        |              | WAIT              |

| P67          |              |                                                                                                                                                      |                                                                                        |              | ASTB              |

| P70          |              | Port 7 3-bit input/output port                                                                                                                       |                                                                                        |              | SI2/RxD           |

| P71          | Input/output | Input/output is specifiable to When used as the input por                                                                                            |                                                                                        | Input        | SO2/TxD           |

| P72          |              | connect a pull-up resistor b                                                                                                                         |                                                                                        |              | SCK2/ASCK         |

| P120 to P127 | input/output | Port 12<br>8-bit input/output port<br>Input/output is specifiable b<br>When used as the input por<br>connect a pull-up resistor b                    | Input                                                                                  | RTP0 to RTP7 |                   |

| P130, P131   | Input/output | Port 13 2-bit input/output port Input/output is specifiable b When used as the input por connect a pull-up resistor b                                | Input                                                                                  | ANO0, ANO1   |                   |

# (2) Non-port pins (1/2)

| Pin Name | Input/Output | Function                                                                                        | After Reset  | Dual-Function Pin                                |       |

|----------|--------------|-------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------|-------|

| INTP0    |              |                                                                                                 |              | P00/T100                                         |       |

| INTP1    |              |                                                                                                 |              | P01/T101                                         |       |

| iNTP2    | 1            |                                                                                                 |              | P02                                              |       |

| iNTP3    | Input        | External interruption inputs, with specifiable valid edges (rising edge, falling edge, and both | Input        | P03                                              |       |

| INTP4    | 1            | rising and falling edges) .                                                                     |              | P04                                              |       |

| INTP5    | 1            |                                                                                                 |              | P05                                              |       |

| INTP6    | 1            |                                                                                                 |              | P06                                              |       |

| SIO      |              |                                                                                                 |              | P25/SB0/SDA0                                     |       |

| SI1      | Input        | Serial data input of the serial interface                                                       | Input        | P20                                              |       |

| S12      | 1            |                                                                                                 |              | P70/RxD                                          |       |

| S00      |              |                                                                                                 |              | P26/SB1/SDA1                                     |       |

| SO1      | Output       | Output Serial data output of the serial interface                                               | Input        | P21                                              |       |

| SO2      |              |                                                                                                 |              | P71/TxD                                          |       |

| SB0      |              | ·                                                                                               |              | P25/SI0/SDA0                                     |       |

| SB1      | Input/output |                                                                                                 |              | P26/SO0/SDA1                                     |       |

| SDA0     |              | Input/output                                                                                    | Input/output | Serial data input/output of the serial interface | Input |

| SDA1     |              |                                                                                                 |              | P26/SO0/SB1                                      |       |

| SCK0     |              |                                                                                                 |              | P27/SCL                                          |       |

| SCK1     | 1            |                                                                                                 |              | P22                                              |       |

| SCK2     | Input/output | Serial clock input/output of the serial interface                                               | Input        | P72/ASCK                                         |       |

| SCL      | 1            |                                                                                                 |              | P27/SCK0                                         |       |

| STB      | Output       | Automatic transmitting/receiving strobe output of the serial interface                          | Input        | P23                                              |       |

| BUSY     | Input        | Automatic transmitting/receiving busy input of the serial interface                             | Input        | P24                                              |       |

| RxD      | Input        | Serial data input for asynchronous serial interface                                             | Input        | P70/S12                                          |       |

| TxD      | Output       | Serial data output for asynchronous serial interface                                            | Input        | P71/SO2                                          |       |

| ASCK     | Input        | Serial clock input for asynchronous serial interface                                            | Input        | P72/SCK2                                         |       |

| T100     |              | External count clock input to 16-bit timer (TM0)                                                |              | P00/INTP0                                        |       |

| TIO1     | 1 .          | Capture trigger signal input to capture register (CR00)                                         | <b>1</b>     | P01/INTP1                                        |       |

| Ti1      | Input        | External count clock input to 8-bit timer (TM1)                                                 | Input        | , P33                                            |       |

| Ti2      | 1            | External count clock input to 8-bit timer (TM2)                                                 |              | P34                                              |       |

# (2) Non-port pins (2/2)

| Pin Name     | Input/Output | Function                                                                                                                | After Reset | Dual-Function Pin |

|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------|-------------|-------------------|

| ТО0          | Outmut       | 16-bit timer output (dual-function as 14-bit PWM output) Output                                                         |             | P30               |

| TO1          | Output       | O his simon autous                                                                                                      | Input       | P31               |

| TO2          |              | 8-bit timer output                                                                                                      |             | P32               |

| PCL          | Output       | Clock output (for trimming main system clock and subsystem clock)                                                       | Input       | P35               |

| BUZ          | Output       | Buzzer output                                                                                                           | Input       | P36               |

| RTP0 to RTP7 | Output       | Real-time output port which outputs data in synchronization with trigger.                                               | Input       | P120 to P127      |

| AD0 to AD7   | Input/output | Low-order address/data bus when expanding memory to the outside.                                                        | Input       | P40 to P47        |

| A8 to A15    | Output       | High-order address bus when expanding memory to the outside.                                                            | Input       | P50 to P57        |

| RD           | Outnut       | Strobe signal output for the external memory read operation                                                             | Input       | P64               |

| WR           | Output       | Strobe signal output for the external memory write operation                                                            | Input       | P65               |

| WAIT         | Input        | Wait insertion when accessing external memory                                                                           | Input       | P66               |

| ASTB         | Output       | Strobe output to externally latches address information which is output to ports 4 and 5 for accessing external memory. | Input       | P67               |

| ANI0 to ANI7 | Input        | Analog input of A/D converter                                                                                           | Input       | P10 to P17        |

| ANO0, ANO1   | Output       | Analog output of D/A converter                                                                                          | Input       | P130, P131        |

| AVREF0       | Input        | Reference voltage input of A/D converter                                                                                |             | -                 |

| AVREF1       | Input        | Reference voltage input of D/A converter                                                                                |             |                   |

| AVDD         |              | Analog power supply of A/D converter, connected to V <sub>00</sub>                                                      |             |                   |

| AVss         |              | Ground potential of A/D converter, connected to Vss                                                                     |             |                   |

| RESET        | Input        | System reset input                                                                                                      |             |                   |

| X1           | Input        |                                                                                                                         |             |                   |

| X2           |              | Main system clock oscillation crystal connection                                                                        |             |                   |

| XT1          | Input        |                                                                                                                         | Input       | P07               |

| XT2          |              | Subsystem clock oscillation crystal connection                                                                          |             |                   |

| Voo          |              | Positive power supply                                                                                                   |             |                   |

| Vpp          |              | High-voltage applied during program write/<br>verification. Normally, connected to Vss in normal<br>operating mode      |             |                   |

| Vss          |              | Ground potential                                                                                                        |             | -                 |

■ 6427525 0082374 02T **■**

#### 2.2 PINS IN PROM PROGRAMMING MODE

| Pin Name  | Input/Output | Function                                                                                                                                                                       |  |  |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RESET     | Input        | PROM programming mode setting When +5 V or +12.5 V is applied to the Vm pin and a low level signal is applied to the RESET pin, this chip is set in the PROM programming mode. |  |  |

| VPP       | Input        | PROM programming mode setting and high-voltage applied during program write/<br>verification                                                                                   |  |  |

| A0 to A16 | Input        | Address bus                                                                                                                                                                    |  |  |

| D0 to D7  | input/output | Data bus                                                                                                                                                                       |  |  |

| CE        | input        | PROM enable input/program pulse input                                                                                                                                          |  |  |

| ŌĒ        | Input        | Read strobe input to PROM                                                                                                                                                      |  |  |

| PGM       | Input        | Program/program inhibit input in PROM programing mode.                                                                                                                         |  |  |

| Voo       |              | Positive power supply                                                                                                                                                          |  |  |

| Vss       |              | Ground potential                                                                                                                                                               |  |  |

# 2.3 PIN INPUT/OUTPUT CIRCUITS AND RECOMMEDED CONNECTION OF UNUSED PINS

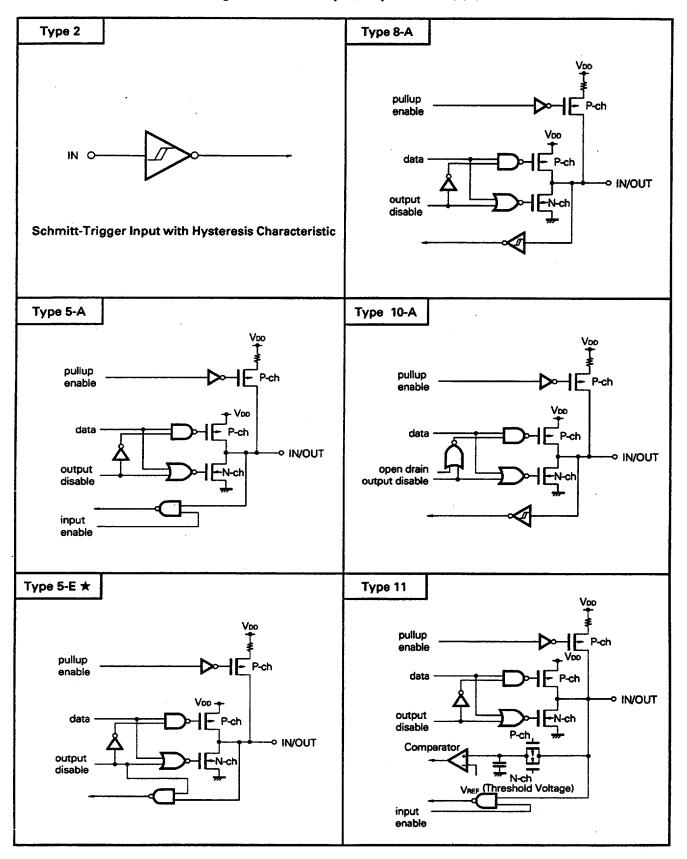

Types of input/output circuits of the pins and recommeded connection of unused pins are shown in Table 2-1. For the configuration of each type of input/output circuit, see Fig. 2-1.

Table 2-1 Type of Input/Output Circuit of Each Pin (1/2)

| Pin Name             | Input/Output<br>Circuit Type | input/Output  | Recommended Connecting Method when Unused           |

|----------------------|------------------------------|---------------|-----------------------------------------------------|

| P00/INTP0/Ti00       | 2                            | Input         | Connect to Vss.                                     |

| P01/INTP1/Ti01       |                              |               |                                                     |

| P02/INTP2            |                              |               |                                                     |

| P03/INTP3            |                              |               | Input : Connect to Vss.                             |

| P04/INTP4            | 8-A                          | input/output  | Output: Leave open.                                 |

| P05/INTP5            | 1                            |               |                                                     |

| P06/INTP6            |                              |               |                                                     |

| P07/XT1              | 16                           | Input         | Connect to Vss.                                     |

| P10/ANI0 to P17/ANI7 | 11                           | Input/output  | Input : Connect to Vpp or Vss. Output : Leave open. |

| P20/SI1              | 8-A                          |               |                                                     |

| P21/SO1              | 5-A                          |               |                                                     |

| P22/SCK1             | 8-A                          |               |                                                     |

| P23/STB              | 5-A                          |               | Input : Connect to Vpp or Vss.                      |

| P24/BUSY             | 8-A                          | Input/output  | Output: Leave open.                                 |

| P25/SI0/SB0/SDA0     |                              |               |                                                     |

| P26/SO0/SB1/SDA1     | 10-A                         |               |                                                     |

| P27/SCK0/SCL         |                              |               |                                                     |

| P30/TO0              |                              |               |                                                     |

| P31/TO1              | 5-A                          |               |                                                     |

| P32/TO2              |                              |               |                                                     |

| P33/TI1              | 0.4                          | Innuate verve | Input : Connect to Voc or Vss.                      |

| P34/TI2              | 8-A                          | Input/output  | Output : Leave open.                                |

| P35/PCL              |                              |               |                                                     |

| P36/BUZ              | 5-A                          |               |                                                     |

| P37                  |                              |               |                                                     |

| P40/AD0 to P47/AD7   | 5-E                          | Input/output  | Input : Connect to Vss.<br>Output : Leave open.     |

■ 6427525 0082376 9T2 ■

Table 2-1 Type of Input/Output Circuit of Each Pin (2/2)

| Pin Name               | Input/Output<br>Circuit Type          | Input/Output | Recommended Connecting<br>Method when Unused        |  |

|------------------------|---------------------------------------|--------------|-----------------------------------------------------|--|

| P50/A8 to P57/A15      | 5-A                                   |              |                                                     |  |

| P60 to P63             | 13                                    |              |                                                     |  |

| P64/RD                 |                                       |              | Input : Connect to Vop or Vss.                      |  |

| P65/WR                 |                                       | Input/output | Output : Leave open.                                |  |

| P66/WAIT               | 5-A                                   |              |                                                     |  |

| P67/ASTB               |                                       |              |                                                     |  |

| P70/Si2/RxD            | 8-A                                   |              |                                                     |  |

| P71/SO2/TxD            | 5-A                                   |              | Input : Connect to Vpp or Vss. Output : Leave open. |  |

| P72/SCK2/ASCK          | 8-A                                   |              |                                                     |  |

| P120/RTP0 to P127/RTP7 | 5-A                                   | Input/output | Input : Connect to Voo or Vss. Output : Leave open. |  |

| P130/ANO0, P131/ANO1   | 12-A                                  | input/output | Input : Connect to Vop or Vss. Output : Leave open. |  |

| RESET                  | 2                                     | Input        |                                                     |  |

| XT2                    | 16                                    |              | Leave open                                          |  |

| AV <sub>REF0</sub>     | · · · · · · · · · · · · · · · · · · · |              | Connect to Vss                                      |  |

| AVREF1                 |                                       |              | Constant                                            |  |

| AVoo                   |                                       | *******      | Connect to Voo                                      |  |

| AVss                   |                                       |              |                                                     |  |

| VPP                    |                                       |              | Connect to Vss                                      |  |

\*

Fig. 2-1 List of Pin Input/Output Circuits (1/2)

**=** 6427525 0082378 775 **=**

Fig. 2-1 List of Pin Input/Output Circuits (2/2)

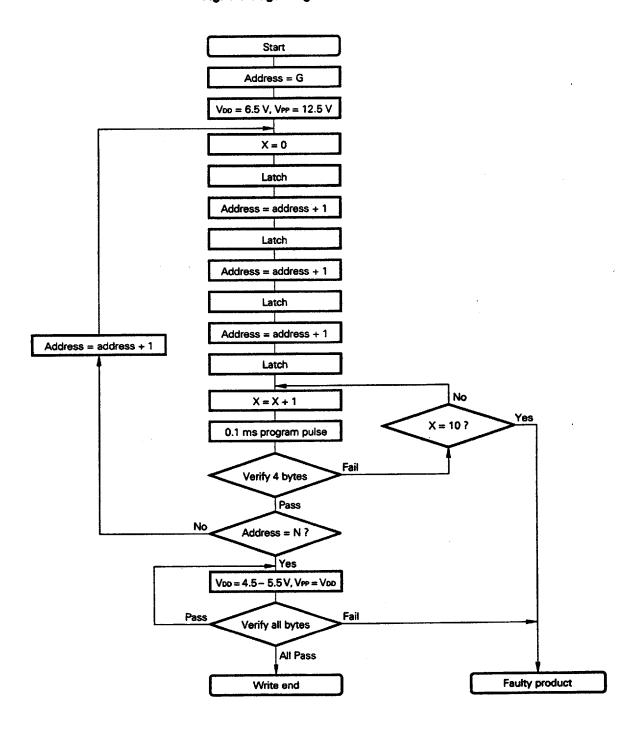

#### 3. MEMORY SIZE SWITCHING REGISTER (IMS)

This is a register to disable use of part of internal memories by software. By setting this memory size switching register (IMS), it is possible to get the same memory mapping as that of mask ROM product having different internal memories (ROM, RAM).

The IMS is set up by the 8-bit memory manipulation instruction. C8H will result by the RESET input.

Fig. 3-1 Memory Size Switching Register Format

Table 3-1 shows the setting values of IMS which makes the memory mapping the same as that of the various mask ROM products.

**Table 3-1 Memory Size Switching Register Setting Examples**

| Target Mask ROM Product | IMS Setting Value |

|-------------------------|-------------------|

| μPD78052Y               | 44H .             |

| μPD78053Y               | С6Н               |

| μPD78054Y               | СВН               |

#### 4. PROM PROGRAMMING

The  $\mu$ PD78P054Y has an on-chip 32K-byte PROM as a program memory. For programming, set the PROM programming mode by the Ver and  $\overline{RESET}$  pins. For connecting unused pins, refer to "Pin Configuration (2) PROM programming mode."

#### 4.1 OPERATING MODES

When +5 V or +12.5 V is applied to the VPP pin and a low level signal is applied to the RESET pin, the PROM programming mode is set. This mode will become the operating mode as shown in Table 4-1 when the CE, OE and PGM pins are set as shown.

Further, when the read mode is set, it is possible to read the contents of the PROM.

**Table 4-1 Operating Modes of PROM Programming**

| Pin Operating Mode | RESET | Ver     | Voo    | Œ | ŌĒ  | PGM | D0 to D7       |

|--------------------|-------|---------|--------|---|-----|-----|----------------|

| Page data latch    |       | +12.5 V | +6.5 V | н | L   | н   | Data input     |

| Page write         |       |         |        | H | н   | L   | High-impedance |

| Byte write         | L     |         |        | L | н   | L   | Data input     |

| Program verify     |       |         |        | L | L   | н   | Data output    |

|                    |       |         |        | × | н   | н   | Wigh impedance |

| Program inhibit    |       |         |        | × | L   | Ł   | High-impedance |

| Read               |       | +5 V    | +5 V   | Ĺ | L   | н   | Data output    |

| Output disable     |       |         |        | L | . н | ×   | High-impedance |

| Standby            |       |         |        | н | ×   | ×   | High-impedance |

Remarks x: Lor H

#### (1) Read mode

Read mode is set if  $\overline{CE} = L$ ,  $\overline{OE} = L$  are set.

#### (2) Output disable mode

Data output becomes high-impedance, and is in the output disable mode, if  $\overline{OE} = H$  is set.

Therefore, it allows data to be read from any device by controlling the  $\overline{OE}$  pin, if multiple  $\mu$ PD78P054Ys are connected to the data bus.

#### (3) Standby mode

Standby mode is set if  $\overline{CE} = H$  is set.

In this mode, data outputs become high-impedance irrespective of the OE status.

#### (4) Page data latch mode

Page data latch mode is set if  $\overline{CE} = H$ ,  $\overline{PGM} = H$ ,  $\overline{OE} = L$  are set at the beginning of page write mode. In this mode, 1 page 4-byte data is latched in an internal address/data latch circuit.

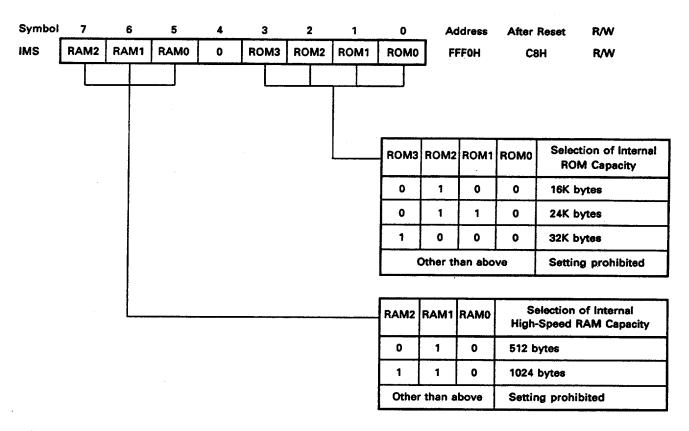

#### (5) Page write mode

After 1 page 4 bytes of addresses and data are latched in the page data latch mode, a page write is executed by applying a 0.1 ms program pulse (active low) to the  $\overline{PGM}$  pin with  $\overline{CE} = H$ . Then, program verification can be performed, if  $\overline{CE} = L$ ,  $\overline{OE} = L$  are set.

If programming is not performed by a one-time program pulse, X ( $X \le 10$ ) write and verification operations should be executed repeatedly.

#### (6) Byte write mode

Byte write is executed when a 0.1 ms program pulse (active low) is applied to the  $\overline{PGM}$  pin with  $\overline{CE} = L$ ,  $\overline{OE} = H$ . Then, program verification can be performed if  $\overline{OE} = L$  is set.

If programming is not performed by a one-time program pulse, X ( $X \le 10$ ) write and verification operations should be executed repeatedly.

#### (7) Program verify mode

Program verify mode is set if  $\overline{CE} = L$ ,  $\overline{PGM} = H$ ,  $\overline{OE} = L$  are set.

In this mode, check if a write operation is performed correctly, after the write.

#### (8) Program inhibit mode

Program inhibit mode is used when the  $\overline{OE}$  pin, VPP pin and D0 to D7 pins of multiple  $\mu$ PD78P054Ys are connected in parallel and a write is performed to one of those devices.

When a write operation is performed, the page write mode or byte write mode described above is used. At this time, a write is not performed to a device which has the PGM pin driven high.

#### 4.2 PROM WRITE PROCEDURE

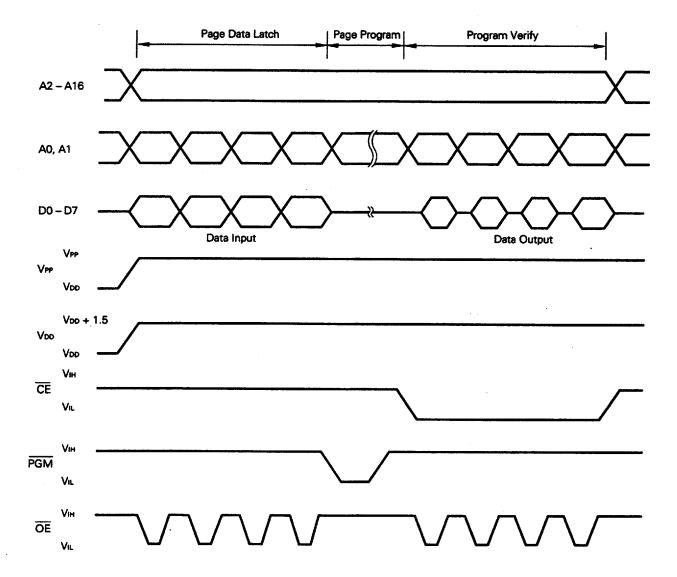

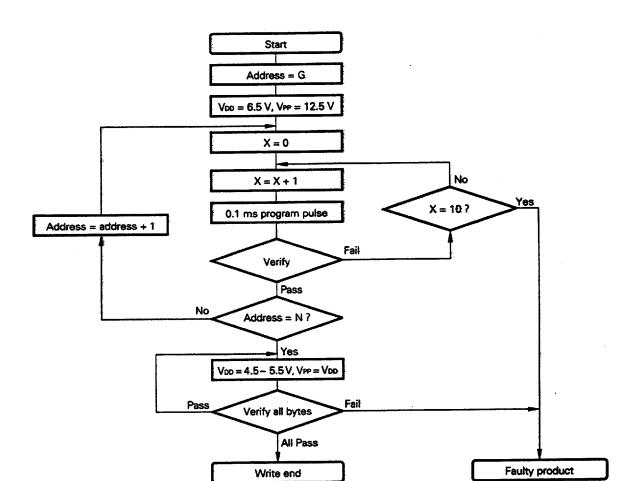

Fig. 4-1 Page Program Mode Flowchart

Remarks 1. G = Start address

2. N = Program last address

Fig. 4-2 Page Program Mode Timing

Fig. 4-3 Byte Program Mode Flow Chart

- Remarks 1. G = Start address

- 2. N = Program last address

Program Program Verify A0 - A16 D0 - D7 Data Input **Data Output** VPP Voo  $V_{DD} + 1.5$ Voo VDD CE VIL **PGM** VIL Vін ŌĒ VIL

Fig. 4-4 Byte Program Mode Timing

Note

- 1. Vpp should be applied before Ver and cut after Ver.

- 2. VPP must not exceed +13.5 V including overshoot.

- 3. Reliability may be adversely affected if removal/reinsertion is performed while +12.5 V is being applied to V<sub>PP</sub>.

#### 4.3 PROM READ PROCEDURE

The contents of PROM are readable to the external data bus (D0 to D7) according to the read procedure shown below.

- (1) Fix the RESET pin at low level, supply +5 V to the VPP pin, and connect all other unused pins as shown in "Pin Configuration (2) PROM programming mode".

- (2) Supply +5 V to the Voo and Vrr pins.

- (3) Input address of read data into the A0 to A16 pins.

- (4) Read mode

- (5) Output data to D0 to D7 pins.

The timings of the above steps (2) to (5) are shown in Fig. 4-5.

Fig. 4-5 PROM Read Timings

#### 5. ERASURE METHOD (μPD78P054YKK-T ONLY)

The  $\mu$ PD78P054YKK-T is capable of erasing (FFH) the contents of data written in a program memory and rewriting.

When erasing the contents of data, irradiate light having a wavelength of less than about 400 nm to the erasing window. Normally, irradiate ultraviolet rays of 254 nm wavelength. Volume of irradiation required to completely erase the contents of data is as follows:

- UV intensity × erasing time : 15 W·s/cm² or more

- Erasing time: 15 to 20 min. (When a UV lamp of 12,000 μW/cm² is used. However, a longer time may be needed because of deterioration in performance of the UV lamp, contamination of the erasing window, etc.)

When erasing the contents of data, set up the UV lamp within 2.5 cm from the erasing window. Further, if a filter is provided for a UV lamp, irradiate the ultraviolet rays after removing the filter.

#### 6. ERASURE WINDOW SEAL (μPD78P054YKK-T ONLY)

To protect from miserasure by rays other than that of the lamp for erasing EPROM contents, or to protect internal circuit other than EPROM from misoperating by rays, stick a protection seal on the erasure window when EPROM contents erasure is not performed.

#### 7. ONE-TIME PROM PRODUCTS SCREENING

The one-time PROM product ( $\mu$ PD78P054YGC-3B9,  $\mu$ PD78P054YGK-BE9) can not be tested completely by NEC before it is shipped, because of its structure. It is recommended to perform screening to verify PROM after writing necessary data and performing high-temperature storage under the condition below.

| Storage Temperature | Storage time |

|---------------------|--------------|

| 125 °C              | 24 hours     |

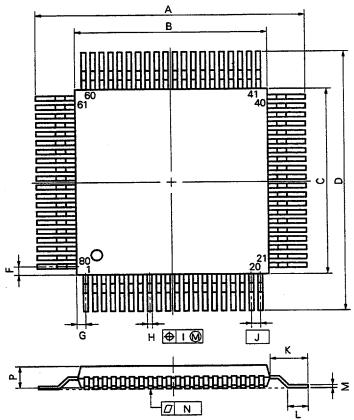

# 8. PACKAGE INFORMATION

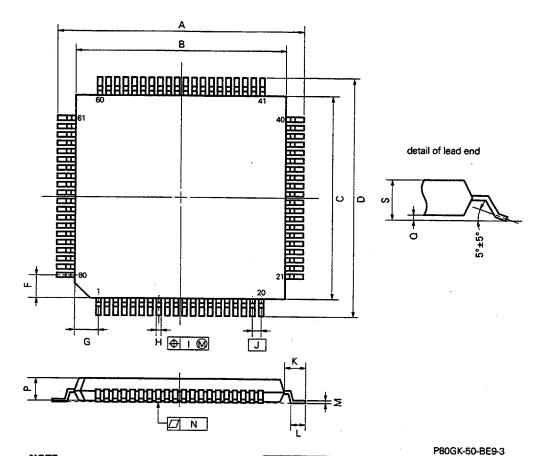

# 80 PIN PLASTIC QFP (□14)

detail of lead end

## NOTE

Each lead centerline is located within 0.13 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| 580  | GU | ,-bt | ⊱3 | ೮೪ | ٠. |

|------|----|------|----|----|----|

| <br> | _  |      |    | _  |    |

| MILLIMETERS | INCHES                                                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------|

| 17.2±0.4    | 0.677±0.016                                                                                                                     |

| 14.0±0.2    | 0.551+0.009                                                                                                                     |

| 14.0±0.2    | 0.551+0.009                                                                                                                     |

| 17.2±0.4    | 0.677±0.016                                                                                                                     |

| 0.8         | 0.031                                                                                                                           |

| 0.8         | 0.031                                                                                                                           |

| 0.30±0.10   | · 0.012 <sup>+0.004</sup>                                                                                                       |

| 0.13        | 0.005                                                                                                                           |

| 0.65 (T.P.) | 0.026 (T.P.)                                                                                                                    |

| 1.6±0.2     | 0.063±0.008                                                                                                                     |

| 0.8±0.2     | 0.031+0.009                                                                                                                     |

| 0.15+0.10   | 0.006+0.004                                                                                                                     |

| 0.10        | 0.004                                                                                                                           |

| 2.7         | 0.106                                                                                                                           |

| 0.1±0.1     | 0.004±0.004                                                                                                                     |

| 3.0 MAX.    | 0.119 MAX.                                                                                                                      |

|             | 17.2±0.4  14.0±0.2  14.0±0.2  17.2±0.4  0.8  0.8  0.30±0.10  0.13  0.65 (T.P.)  1.6±0.2  0.8±0.2  0.15±0.05  0.10  2.7  0.1±0.1 |

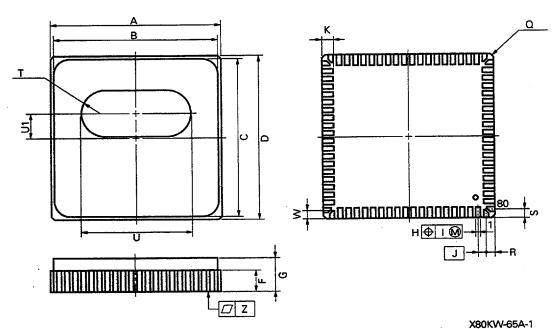

# 80 PIN PLASTIC TQFP (FINE PITCH) (□12)

#### NOTE

Each lead centerline is located within 0.10 mm (0.004 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS | INCHES       |

|------|-------------|--------------|

| Α    | 14.0±0.4    | 0.551±0.016  |

| В    | 12.0±0.2    | 0.472+0.009  |

| С    | 12.0±0.2    | 0.472+0.009  |

| D    | 14.0±0.4    | 0.551±0.016  |

| F    | 1.25        | 0.049        |

| G    | 1.25        | 0.049        |

| Ξ    | 0.20±0.10   | 0.008±0.004  |

| 1    | 0.10        | 0.004        |

| J    | 0.5 (T.P.)  | 0.020 (T.P.) |

| K    | 1.0±0.2     | 0.039+0.009  |

| L    | 0.5±0.2     | 0.020+0.008  |

| М    | 0.125+0.10  | 0.005±0.004  |

| N    | 0.10        | 0.004        |

| Р    | 1.05        | 0.041        |

| Q    | 0.05±0.05   | 0.002±0.002  |

| s    | 1.27 MAX.   | 0.05 MAX.    |

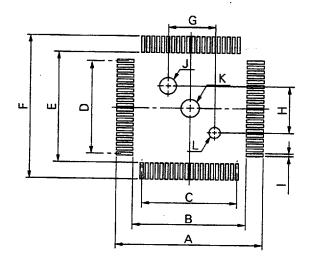

# **★ 80 PIN CERAMIC WQFN**

#### NOTE

Each lead centerline is located within 0.06 mm (0.003 inch) of its true position (T.P.) at maximum material condition.

|      |             | VOOLA A COL  |

|------|-------------|--------------|

| ITEM | MILLIMETERS | INCHES       |

| Α    | 14.0±0.2    | 0.551±0.008  |

| В    | 13.6        | 0.535        |

| С    | 13.6        | 0.535        |

| D    | 14.0±0.2    | 0.551±0.008  |

| F    | 1.84        | 0.072        |

| Ģ    | 3.6 MAX.    | 0.142 MAX.   |

| Н    | 0.45±0.10   | 0.018+0.004  |

| 1    | 0.06        | 0.003        |

| J    | 0.65 (T.P.) | 0.024 (T.P.) |

| К    | 1.0±0.15    | 0.039-0.007  |

| a    | C 0.3       | C 0.012      |

| R    | 0.825       | 0.032        |

| S    | 0.825       | 0.032        |

| Т    | R 2.0       | R 0.079      |

| U    | 9.0         | 0.354        |

| U1   | 2.1         | 0.083        |

| W    | 0.75±0.15   | 0.030+0.006  |

| Z.   | 0.10        | 0.004        |

|      |             |              |

# **APPENDIX A. DEVELOPMENT TOOLS**

To support development of systems which use the  $\mu$ PD78P054Y, the following development tools are available.

#### **Language Processing Software**

| RA78K/0 *1,2 | 78K/0 series common assembler package              |

|--------------|----------------------------------------------------|

| CC78K/0 *1,2 | 78K/0 series common C compiler package             |

| CC78K/0 *1,2 | 78K/0 series common C compiler library source file |

# **PROM Write Tools**

| PG-1500               | PROM Programmer                                 |

|-----------------------|-------------------------------------------------|

| PA-78P054GC           |                                                 |

| PA-78P054GK           | PG-1500 Programmer adapter connected to PG-1500 |

| PA-78P054KK-T         |                                                 |

| PG-1500 Controller *1 | PG-1500 control program                         |

#### **Debugging Tools**

| IE-78000-R    | 78K/0 series common in-circuit emulator                                       |

|---------------|-------------------------------------------------------------------------------|

| IE-78000-R-BK | 78/0 series common break board                                                |

| IE-78064-R-EM | μPD78064 series common emulation board                                        |

| EP-7230GC-R   | μPD78234 series common emulation probe                                        |

| EV-78054GK-R  | μPD78054 series common emulation probe                                        |

| EV-9200GC-80  | Socket to be mounted on user system board created for the 80-pin plastic QFP  |

| EV-9500GK-80  | Adapter to be mounted on user system board created for the 80-pin plastic QFP |

| SD78K/0 *1    | IE-78000-R screen debugger                                                    |

| DF78054 *1,3  | μPD78054 series common device file                                            |

#### **Real-Time OS**

| RX78K/0 *1,2 | 78K/0 series common real-time OS |

|--------------|----------------------------------|

#### Fuzzy Inference Development Support System

| FE9000 *1        | Fuzzy knowledge data creation tool |

|------------------|------------------------------------|

| FT9080 <b>*1</b> | Translator                         |

| FI78K0 *1        | Fuzzy inference module .           |

| FD78K0 *1,3      | Fuzzy inference debugger           |

- \* 1. PC-9800 series (MS-DOSTM) based, IBM PC/ATTM (PC DOSTM) based

- 2. HP9000 series 300™ (HP-UX™) based, SPARCstation™ (Sun OS™) based, EWS-4800 series™ (EWS-UX/V™) based

- 3. Under development

**6**427525 0082392 045 **=**

# ★ External View of Conversion Socket (EV-9200GC-80) and Recommended Board Mounting Pattern

No.1 pin index

Fig. A-1 EV-9200GC-80 (Reference) (Unit: mm)

EV-9200GC-80-G0

| ITEM | MILLIMETERS | INCHES         |  |

|------|-------------|----------------|--|

| Α    | 18.0        | 0.709          |  |

| В    | 14.4        | 0.567          |  |

| С    | 14.4        | 0.567          |  |

| D    | 18.0        | 0.709          |  |

| E    | 4-C 2.0     | 4-C 0.079      |  |

| F    | 0.8         | 0.031          |  |

| G    | 6.0         | 0.236          |  |

| Н    | 16.0        | 0.63           |  |

| ı    | 18.7        | 0.736          |  |

| C.   | 6.0         | 0.236          |  |

| Κ    | 16.0        | 0.63           |  |

| L    | 18.7        | 0.736          |  |

| М    | 8.2         | 0.323          |  |

| 0    | 8.0         | 0.315          |  |

| N    | 2.5         | 0.098          |  |

| Р    | 2.0         | 0.079          |  |

| a    | 0.35        | 0.014          |  |

| R    | ø2.3        | ø0.091         |  |

| S    | ø1.5        | <b>ø</b> 0.059 |  |

■ 6427525 0082393 T81 ■

Fig. A-2 EV-9200GC-80 Recommended Board Mounting Pattern (Reference) (Unit: mm)

EV-9200GC-80-P0

| ITEM | MILLIMETERS               | INCHES                                                           |

|------|---------------------------|------------------------------------------------------------------|

| Α    | 19.7                      | 0.776                                                            |

| В    | 15.0                      | 0.591                                                            |

| С    | 0.65±0.02 × 19=12.35±0.05 | $0.026^{+0.001}_{-0.002} \times 0.748 = 0.486^{+0.003}_{-0.002}$ |

| D    | 0.65±0.02 × 19=12.35±0.05 | $0.026^{+0.001}_{-0.002} \times 0.748 = 0.486^{+0.003}_{-0.002}$ |

| E    | 15.0                      | 0.591                                                            |

| F    | 19.7                      | 0.776                                                            |

| G    | 6.0±0.05                  | 0.236+0.003                                                      |

| Н    | 6.0±0.05                  | 0.236+0.003                                                      |

| ı    | 0.35±0.02                 | 0.014+0.001                                                      |

| J    | \$\phi_2.36±0.03          | Ø0.093 <sup>+0.001</sup>                                         |

| κ    | <b>ø</b> 2.3              | φ0.091                                                           |

| L    | Ø1.57±0.03                | Ø 0.062+0.001                                                    |

Caution Dimensions of mount pad for EV-9200 and that for target device (QFP) may be different in some parts. For the recommended mount pad dimensions for QFP, refer to **SEMICONDUCTOR DEVICE MOUNTING TECHNOLOGY** MANUAL" (IEI-1207).

# \* APPENDIX B. RELATED DOCUMENTS

# **Device Related Documents**

| Document Name                                                | Document No.   |

|--------------------------------------------------------------|----------------|

| User's Manual                                                | In preparation |

| 78K/0 Series Instruction Application Table                   |                |

| 78K/0 Series Instruction Set                                 |                |

| μPD78054Y Series Special Function Register Application Table |                |

# Development Tools Related Documents (User's Manual)

| Documer                                        | nt Name             | Document No. |

|------------------------------------------------|---------------------|--------------|

| Darrie A. L. A. Landers Bankson                | Operation Volume    |              |

| RA78K Series Assembler Package                 | Language Volume     |              |

| RA78K Series Structured Assembler Preprocessor |                     |              |

| CC78K Series C Compiler                        | Instruction Volume  |              |

|                                                | Language Volume     |              |

| CC78K Series Library Source File               |                     |              |

| PG-1500 PROM Programmer                        |                     |              |

| IE-78000-R                                     |                     |              |

| 1E-78000-R-BK                                  |                     |              |

| IE-78064-R-EM                                  |                     |              |

| SD78K/0 Screen Debugger                        | Introductory Volume |              |

| 2010MA Sciedii penaRRai                        | Reference Volume    |              |

# **Built-In Software Related Documents (User's Manual)**

| Document Name                                                                    |                     | Document No. |

|----------------------------------------------------------------------------------|---------------------|--------------|

|                                                                                  | Introduction Volume |              |

| TOKIN 0 . 1 . P 1 T                                                              | Installation Volume |              |

| 78K/0 Series Real-Time OS                                                        | Debugging Volume    |              |

|                                                                                  | Technical Volume    |              |

| Fuzzy Knowledge Data Creation Tool                                               |                     |              |

| 78K/0, 78K/II, 87AD Series Fuzzy Inference Development Support System Translator |                     | ·            |

| 78K/0 Series Fuzzy Inference Development Support System Fuzzy Inference Module   |                     |              |

| 78K/0 Series Fuzzy Inference Development Support System Fuzzy Inference Debugger |                     |              |

Note The contents of the above related documents are subject to change withoug notice. The latest document should be used for design, etc.

#### **Other Documents**

| Document Name                                                   | Document No. |

|-----------------------------------------------------------------|--------------|

| Package Manual                                                  |              |

| Surface Mount Technology Manual                                 |              |

| Quality Grade on NEC Semiconductor Devices                      |              |

| NEC Semiconductor Devices                                       |              |

| Electrostatic Discharge (ESD) Test                              |              |

| Semiconductor Devices Quality Guarantee Guide                   |              |

| Microcomputer Related Products Guide Others Manufactures Volume |              |

Note The contents of the above related documents are subject to change withoug notice. The latest document should be used for design, etc.