#### **Document Title**

#### 256K x8 bit Low Power and Low Voltage Full CMOS Static RAM

#### **Revision History**

| Revision No. | History       |                                                                                                                                                                                  | <b>Draft Date</b> | Remark |

|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------|

| 0.0          | Initial Draft |                                                                                                                                                                                  | June 7, 2007      |        |

| 0.1          | 0.1 Revision  | Remove BYTE option information                                                                                                                                                   | June 15, 2007     |        |

| 0.2          | 0.2 Revision  | Remove $\overline{\text{UB}}$ , $\overline{\text{LB}}$ information                                                                                                               | June 21, 2007     |        |

| 0.3          | 0.3 Revision  | Revised VOH(2.2v to 2.4v),tOH(15ns to 10ns),<br>tOE-55(30ns to 25ns), tWP-55(45ns to 40ns),<br>tWP-70(55ns to 50ns), tWHZ-70(25ns to 20ns),<br>ICC(2mA to 3mA), ICC1(2mA to 3mA) | July 2, 2007      |        |

| 0.4          | 0.4 Revision  | $V_{\mbox{\scriptsize IH}}$ level change from 2.0V to 2.2V                                                                                                                       | Aug. 16, 2007     |        |

#### **Emerging Memory & Logic Solutions Inc.**

4F Korea Construction Financial Cooperative B/D, 301-1 Yeon-Dong, Jeju-Si, Jeju-Do, Rep.of Korea Zip Code : 690-719 Tel : +82-64-740-1712 Fax : +82-64-740-1749~1750 / Homepage : www.emlsi.com

The attached data sheets are provided by EMLSI reserve the right to change the specifications and products. EMLSI will answer to your questions about device. If you have any questions, please contact the EMLSI office.

#### 256K x8 Bit Low Power and Low Voltage CMOS Static RAM

#### **FEATURES**

- Process Technology: 0.15μm Full CMOS

Organization :256K x8Power Supply Voltage

=> EM620FV8B : 2.7~3.6V

- Low Data Retention Voltage: 1.5V

- Three state output and TTL Compatible

- Packaged product designed for 45/55/70ns

#### **GENERAL PHYSICAL SPECIFICATIONS**

- Backside die surface of polished bare silicon

- Typical Die Thickness = 725um +/-15um

- Typical top-level metallization :

=> Metal (Ti/AlCu/TiN/ARC SiON/SiO2) : 5.2K Angstroms

- Topside Passivation:

=> Passivation (HDP/pNIT/PIQ) : 5.4K Angstroms

- Wafer diameter: 8 inch

#### **OPTIONS**

- C1/W1 : DC Probed Die/Wafer @ Hot Temp- C2/W2 : DC/AC Probed Die/Wafer @ Hot Temp

#### **PAD DESCRIPTIONS**

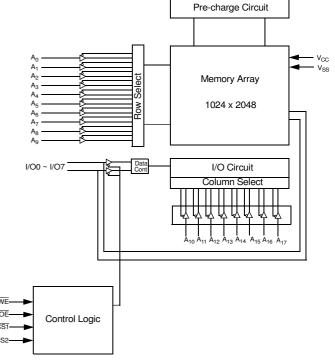

| Name      | Function            | Name | Function      |

|-----------|---------------------|------|---------------|

| CS1,CS2   | Chip select inputs  | Vcc  | Power Supply  |

| ŌE        | Output Enable input | Vss  | Ground        |

| WE        | Write Enable input  | NC   | No Connection |

| A0~A17    | Address Inputs      |      |               |

| I/O0~I/O7 | Data Inputs/Outputs |      |               |

#### **BONDING INSTRUCTIONS**

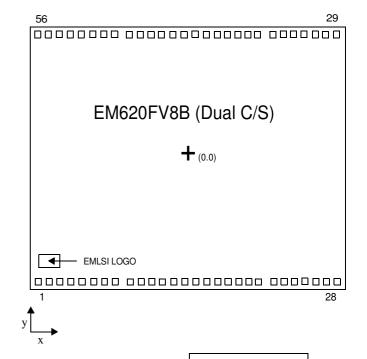

The 2M full CMOS SRAM die has total 56pads. Refer to the bond pad location and identification table for X, Y coordinates. EMLSI recommends using a bond wire on back side of die onto Vss bond pad for improved noise immunity.

#### **FUNCTIONAL SPECIFICATIONS**

There are 3 classifications for EMLSI die and wafers products, which are C1 and C2 for die and W1 and W2 for wafer, respectively. Each die and wafer support dedicated characteristics and probe the electrical parameters within their specifications. Followings are brief information for die and wafer classifications. Please refer to packaged specifications for more information but these parameters are not guaranteed at bare die and wafer.

#### - C1 LEVEL DIE OR W1 LEVEL WAFER

The DC parameters are measured by specification for C1 level die or W1 level wafer. The DC parameters measured at 70°C temperature, which called 'Hot DC Sorting' Other parameters are not guaranteed and warranted including device reliability. Please refer to qualification report for device reliability and package level datasheets for electrical parameters.

#### - C2 LEVEL DIE OR W2 LEVEL WAFER

The DC parameters and selected AC parameters are measured with for C2 level die or W2 level wafer. The DC characteristics of C2 die and W2 wafer is tested based on DC specifications of C1 level die and W1 level wafer. The DC and specified AC parameters are tested at 70°C temperature, which called 'Hot DC & Selective AC Sorting'. Other parameters are not guaranteed and warranted including device reliability. Please refer to qualification report for device reliability and package level datasheets for electrical parameters.

C2 level die and W2 level wafer probe following AC parameter.

- tRC, tAA, tCO

- tWC, tCW

#### **PACKAGING**

Individual device will be packed in anti-static trays.

- Chip Trays : A 2-inch square waffle style carrier for die with separate compartments for each die. Commonly referred to as a waffle pack, each tray has a cavity size selected for the device that allows for easy loading and unloading and prevents rotation. The tray itself is made of conductive material to reduce the danger of damage to the die from electrostatic discharge. The chip carriers will be labeled with the following information :

- EMLSI wafer lot number

- EMLSI part number

- Quantity

- Jar Packing: Jar packing is made by EMLSI and used by many customers that we deliver the requested die as wafer. The pack is consisted of clean paper to wrap the wafer, high cushioned sponge between wafers and hardly fragile plastic box with sponge. Each pack has typically 24 wafers and then several packs are put into larger box depending on amounts of wafers.

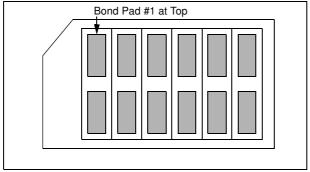

Die orientation in chip carriers

#### STORAGE AND HANDLING

EMLSI recommends the die stored in a controlled environment with filtered nitrogen. The carrier must be opened at ESD safe environment when inspection and assembly.

#### **ABSOLUTE MAXIMUM RATINGS \***

| Parameter                             | Symbol                             | Minimum      | Unit |

|---------------------------------------|------------------------------------|--------------|------|

| Voltage on Any Pin Relative to Vss    | V <sub>IN</sub> , V <sub>OUT</sub> | -0.2 to 4.0V | V    |

| Voltage on Vcc supply relative to Vss | V <sub>CC</sub>                    | -0.2 to 4.0V | V    |

| Power Dissipation                     | P <sub>D</sub>                     | 1.0          | W    |

| Operating Temperature                 | T <sub>A</sub>                     | -40 to 85    | °C   |

<sup>\*</sup> Stresses greater than those listed above "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be restricted to recommended operating condition. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **FUNCTIONAL DESCRIPTION**

| CS1 | CS2 | OE | WE | I/O <sub>0-7</sub> | Mode            | Power    |

|-----|-----|----|----|--------------------|-----------------|----------|

| Н   | Х   | Х  | Х  | High-Z             | Deselected      | Stand by |

| Х   | L   | Х  | Х  | High-Z             | Deselected      | Stand by |

| Х   | Х   | Х  | Х  | High-Z             | Deselected      | Stand by |

| L   | Н   | Н  | Н  | High-Z             | Output Disabled | Active   |

| L   | Н   | Н  | Н  | High-Z             | Output Disabled | Active   |

| L   | Н   | L  | Н  | Data Out           | Read            | Active   |

| L   | Н   | Х  | L  | Data In            | Write           | Active   |

Note: X means don't care. (Must be low or high state)

### **RECOMMENDED DC OPERATING CONDITIONS 1)**

| Parameter          | Symbol          | Min                | Тур | Max                 | Unit |

|--------------------|-----------------|--------------------|-----|---------------------|------|

| Supply voltage     | V <sub>CC</sub> | 2.7                | 3.3 | 3.6                 | V    |

| Ground             | V <sub>SS</sub> | 0                  | 0   | 0                   | V    |

| Input high voltage | V <sub>IH</sub> | 2.2                | -   | $V_{CC} + 0.2^{2)}$ | V    |

| Input low voltage  | V <sub>IL</sub> | -0.2 <sup>3)</sup> | -   | 0.6                 | V    |

- 1. TA= -40 to 85°C, otherwise specified

- 2. Overshoot: Vcc +2.0 V in case of pulse width ≤ 20ns

- 3. Undershoot: -2.0 V in case of pulse width ≤ 20ns

- 4. Overshoot and undershoot are sampled, not 100% tested.

# **CAPACITANCE**<sup>1)</sup> (f =1MHz, $T_A$ =25°C)

| Item                    | Symbol          | Test Condition      | Min | Max | Unit |

|-------------------------|-----------------|---------------------|-----|-----|------|

| Input capacitance       | C <sub>IN</sub> | V <sub>IN</sub> =0V | -   | 8   | pF   |

| Input/Ouput capacitance | C <sub>IO</sub> | V <sub>IO</sub> =0V | -   | 10  | pF   |

<sup>1.</sup> Capacitance is sampled, not 100% tested.

#### DC AND OPERATING CHARACTERISTICS

| Parameter                 | Symbol           | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                      | Min | Тур             | Max | Unit |

|---------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|------|

| Input leakage current     | I <sub>LI</sub>  | V <sub>IN</sub> =V <sub>SS</sub> to V <sub>CC</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      | -1  | -               | 1   | uA   |

| Output leakage current    | I <sub>LO</sub>  | $\overline{\text{CS1}} = \text{V}_{\text{IH}} \text{ or } \text{CS2} = \text{V}_{\text{IL}} \text{ or } \overline{\text{OE}} = \text{V}_{\text{IH}} \text{ or } \overline{\text{WE}} = \text{V}_{\text{IL}}$ $\text{V}_{\text{IO}} = \text{V}_{\text{SS}} \text{ to V}_{\text{CC}}$                                                                                                                                                                                                                                                                                             |                                                                                                                      | -1  | -               | 1   | uA   |

| Operating power supply    | I <sub>CC</sub>  | $I_{IO}$ =0mA, $\overline{CS1}$ = $V_{IL}$ , $CS2$ = $\overline{WE}$ = $V_{IH}$ , $V_{IN}$ = $V_{IH}$ or $V_{IL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                      | -   | -               | 3   | mA   |

|                           | I <sub>CC1</sub> | $\label{eq:cycle_time}  \begin{split} & \frac{\text{Cycle time} = 1 \mu \text{s}, \ 100\% \ \text{duty}, \ I_{IO} = 0 \text{mA}, \\ & \frac{\text{CS1}}{\leq} 0.2 \text{V}, \ \text{CS2} \\ & \frac{\text{C}}{\text{C}} \cdot 0.2 \text{V}, \\ & \text{V}_{IN} \\ \leq 0.2 \text{V or V}_{IN} \\ \geq \text{V}_{CC} \cdot 0.2 \text{V} \end{split}$                                                                                                                                                                                                                             |                                                                                                                      | -   | -               | 3   | mA   |

| Average operating current | I <sub>CC2</sub> | Cycle time = Min, I <sub>IO</sub> =0mA, 100% duty,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 45ns                                                                                                                 | -   | -               | 35  | mA   |

|                           |                  | CS1=V <sub>IL</sub> , CS2=V <sub>IH</sub> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 55ns                                                                                                                 | -   | -               | 30  |      |

|                           |                  | V <sub>IN</sub> =V <sub>IL</sub> or V <sub>IH</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                      | -   | -               | 25  |      |

| Output low voltage        | V <sub>OL</sub>  | I <sub>OL</sub> = 2.1mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      | -   | -               | 0.4 | ٧    |

| Output high voltage       | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                      | 2.4 | -               | -   | ٧    |

| Standby Current (TTL)     | I <sub>SB</sub>  | CS1=V <sub>IH</sub> , CS2=V <sub>IL</sub> , Other inputs=V <sub>IH</sub> or V <sub>IL</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                      | -   | -               | 0.3 | mA   |

| Standby Current (CMOS)    | I <sub>SB1</sub> | $\label{eq:controlled} \hline \overline{\text{CS1}}{}_{\geq}\text{V}_{\text{CC}}\text{-}0.2\text{V}, \text{CS2}{}_{\geq}\text{V}_{\text{CC}}\text{-}0.2\text{V}~(\overline{\text{CS}}~\text{controlled})} \\ \text{or } 0\text{V}{}_{\leq}\text{CS2}{}_{\leq}0.2\text{V}~(\text{CS2}~\text{controlled}), \\ \text{Other inputs} = 0{}^{\sim}\text{V}_{\text{CC}} \\ \text{(Typ. condition}: \text{V}_{\text{CC}}\text{=}3.3\text{V}~@25^{\text{o}}\text{C})} \\ \text{(Max. condition}: \text{V}_{\text{CC}}\text{=}3.6\text{V}~@85^{\text{o}}\text{C})} \\ \hline \end{array}$ | $V_{\le}$ CS2 $\le$ 0.2V (CS2 controlled),<br>er inputs = $0 \sim V_{CC}$ LF<br>. condition : $V_{CC}$ =3.3V @ 25°C) |     | 1 <sup>1)</sup> | 10  | uA   |

#### **NOTES**

1. Typical values are measured at Vcc=3.3V,  $T_A$ =25°C and not 100% tested.

#### **AC OPERATING CONDITIONS**

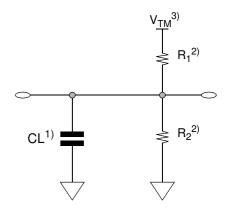

Test Conditions (Test Load and Test Input/Output Reference)

Input Pulse Level: 0.4 to 2.2V Input Rise and Fall Time: 5ns

Input and Output reference Voltage : 1.5V Output Load (See right) :  $CL^{1)} = 100pF + 1 TTL$

$CL^{1)} = 30pF + 1 TTL$ (only 45ns part)

1. Including scope and Jig capacitance 2.  $R_1$ =3070 ohm,  $R_2$ =3150 ohm

3.  $V_{TM} = 2.8V$

# **READ CYCLE** ( $V_{cc} = 2.7V$ to 3.6V, Gnd = 0V, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )

| Dougeneston                     | Cymphol                             | 45  | 45ns |     | 55ns |     | Ons | l locit |  |

|---------------------------------|-------------------------------------|-----|------|-----|------|-----|-----|---------|--|

| Parameter                       | Symbol                              | Min | Max  | Min | Max  | Min | Max | Unit    |  |

| Read cycle time                 | t <sub>RC</sub>                     | 45  | -    | 55  | -    | 70  | -   | ns      |  |

| Address access time             | t <sub>AA</sub>                     | -   | 45   | -   | 55   | -   | 70  | ns      |  |

| Chip select to output           | t <sub>CO1</sub> , t <sub>CO2</sub> | -   | 45   | -   | 55   | -   | 70  | ns      |  |

| Output enable to valid output   | t <sub>OE</sub>                     | -   | 25   | -   | 25   | -   | 35  | ns      |  |

| Chip select to low-Z output     | t <sub>LZ1</sub> , t <sub>LZ2</sub> | 10  | -    | 10  | -    | 10  | -   | ns      |  |

| Output enable to low-Z output   | t <sub>OLZ</sub>                    | 5   | -    | 5   | -    | 5   | -   | ns      |  |

| Chip disable to high-Z output   | t <sub>HZ1</sub> , t <sub>HZ2</sub> | 0   | 20   | 0   | 20   | 0   | 25  | ns      |  |

| Output disable to high-Z output | t <sub>OHZ</sub>                    | 0   | 15   | 0   | 20   | 0   | 25  | ns      |  |

| Output hold from address change | t <sub>OH</sub>                     | 10  | -    | 10  | -    | 10  | -   | ns      |  |

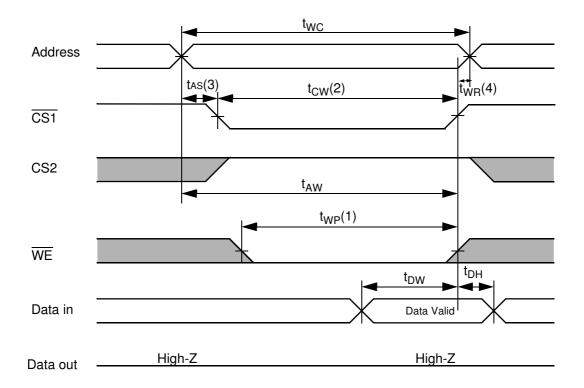

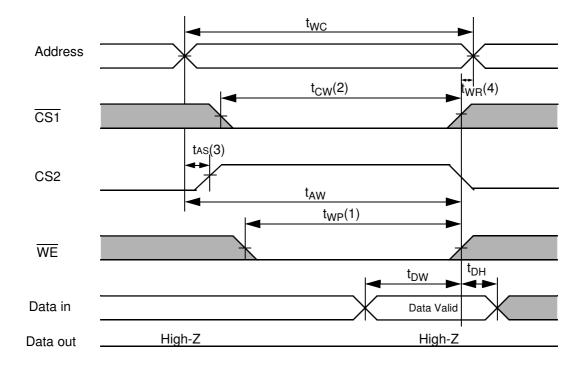

# **WRITE CYCLE** ( $V_{cc} = 2.7V$ to 3.6V, Gnd = 0V, $T_A = -40^{\circ}C$ to $+85^{\circ}C$ )

| Parameter                     | Symbol                              | 45  | 45ns |     | 55ns |     | )ns | Unit |  |

|-------------------------------|-------------------------------------|-----|------|-----|------|-----|-----|------|--|

| Parameter                     | Syllibol                            | Min | Max  | Min | Max  | Min | Max | Onit |  |

| Write cycle time              | t <sub>WC</sub>                     | 45  | -    | 55  | -    | 70  | -   | ns   |  |

| Chip select to end of write   | t <sub>CW1</sub> , t <sub>CW2</sub> | 45  | -    | 45  | -    | 60  | -   | ns   |  |

| Address setup time            | t <sub>AS</sub>                     | 0   | -    | 0   | -    | 0   | -   | ns   |  |

| Address valid to end of write | t <sub>AW</sub>                     | 45  | -    | 45  | -    | 60  | -   | ns   |  |

| Write pulse width             | t <sub>WP</sub>                     | 35  | -    | 40  | -    | 50  | -   | ns   |  |

| Write recovery time           | t <sub>WR</sub>                     | 0   | -    | 0   | -    | 0   | -   | ns   |  |

| Write to ouput high-Z         | t <sub>WHZ</sub>                    | 0   | 15   | 0   | 20   | 0   | 20  | ns   |  |

| Data to write time overlap    | t <sub>DW</sub>                     | 25  |      | 25  |      | 30  |     | ns   |  |

| Data hold from write time     | t <sub>DH</sub>                     | 0   | -    | 0   | -    | 0   | -   | ns   |  |

| End write to output low-Z     | t <sub>OW</sub>                     | 5   | -    | 5   | -    | 5   | -   | ns   |  |

#### **TIMING DIAGRAMS**

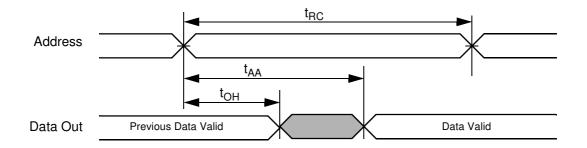

# TIMING WAVEFORM OF READ CYCLE(1) (Address Controlled, $\overline{\text{CS1}} = \overline{\text{OE}} = \text{V}_{\text{IL}}, \text{CS2} = \overline{\text{WE}} = \text{V}_{\text{IH}})$

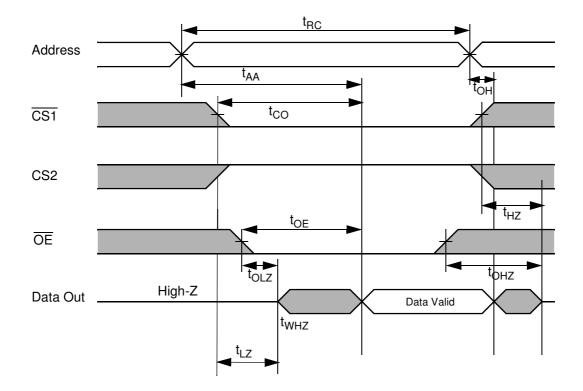

# TIMING WAVEFORM OF READ CYCLE(2) ( $\overline{\text{WE}} = \text{V}_{\text{IH}}$ )

### NOTES (READ CYCLE)

- 1.  $t_{HZ}$  and  $t_{OHZ}$  are defined as the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- 2. At any given temperature and voltage condition, t<sub>HZ</sub>(Max.) is less than t<sub>LZ</sub>(Min.) both for a given device and from device to device interconnection.

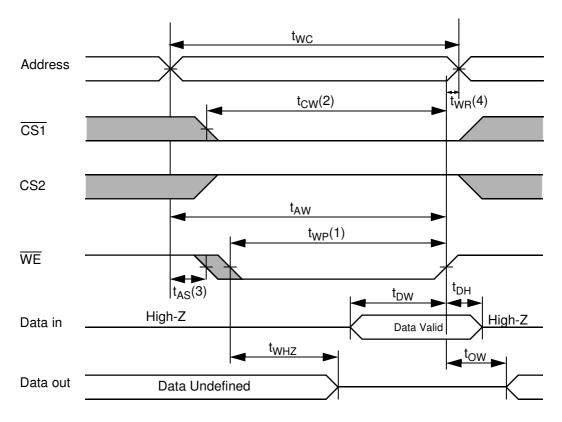

# TIMING WAVEFORM OF WRITE CYCLE(1) (WE CONTROLLED)

# TIMING WAVEFORM OF WRITE CYCLE(2) (CS1 CONTROLLED)

#### TIMING WAVEFORM OF WRITE CYCLE(3) (CS2 CONTROLLED)

#### NOTES (WRITE CYCLE)

- 1. A write occurs during the overlap(t<sub>WP</sub>) of low  $\overline{CS1}$ , a high CS2 and low  $\overline{WE}$ . A write begins at the latest transition among  $\overline{CS1}$  goes low, CS2 goes high and  $\overline{WE}$  goes low. A write ends at the earliest transition when  $\overline{CS1}$  goes high, CS2 goes high and  $\overline{WE}$  goes high. The t<sub>WP</sub> is measured from the beginning of write to the end of write.

- 2.  $t_{CW}$  is measured from the  $\overline{CS1}$  going low to end of write.

- 3.  $t_{\mbox{\scriptsize AS}}$  is measured from the address valid to the beginning of write.

- 4. t<sub>WR</sub> is measured from the end or write to the address change. t<sub>WR</sub> applied in case a write ends as  $\overline{\text{CS1}}$  or  $\overline{\text{WE}}$  going high.

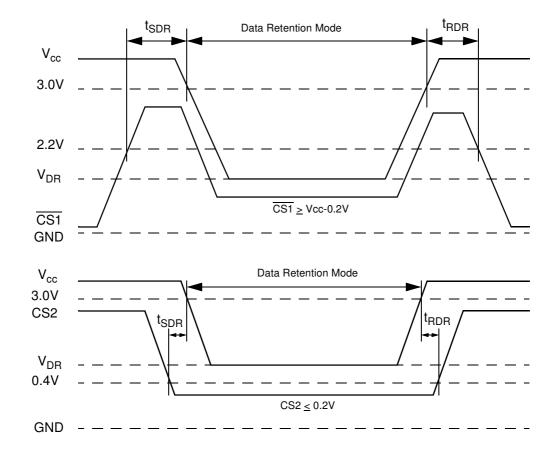

#### **DATA RETENTION CHARACTERISTICS**

| Parameter                            | Symbol                 | Test Condition                                                                          | Min             | Typ <sup>2)</sup> | Max | Unit |

|--------------------------------------|------------------------|-----------------------------------------------------------------------------------------|-----------------|-------------------|-----|------|

| V <sub>CC</sub> for Data Retention   | <b>V</b> <sub>DR</sub> | I <sub>SB1</sub> Test Condition<br>(Chip Disabled) <sup>1)</sup>                        | 1.5             | -                 | 3.6 | V    |

| Data Retention Current               | I <sub>DR</sub>        | V <sub>CC</sub> =1.5V, I <sub>SB1</sub> Test Condition<br>(Chip Disabled) <sup>1)</sup> | -               | 0.5               | -   | μА   |

| Chip Deselect to Data Retention Time | t <sub>SDR</sub>       | See data retention wave form                                                            | 0               | -                 | -   | ns   |

| Operation Recovery Time              | t <sub>RDR</sub>       | See data retention wave form                                                            | t <sub>RC</sub> | -                 | -   | 113  |

#### NOTES

- 1. See the  $I_{SB1}$  measurement condition of data sheet page 5.

- 2. Typical value is measured at  $T_A=25^{\circ}C$  and not 100% tested.

### **DATA RETENTION WAVE FORM**

10

www.DataSheet4U.com

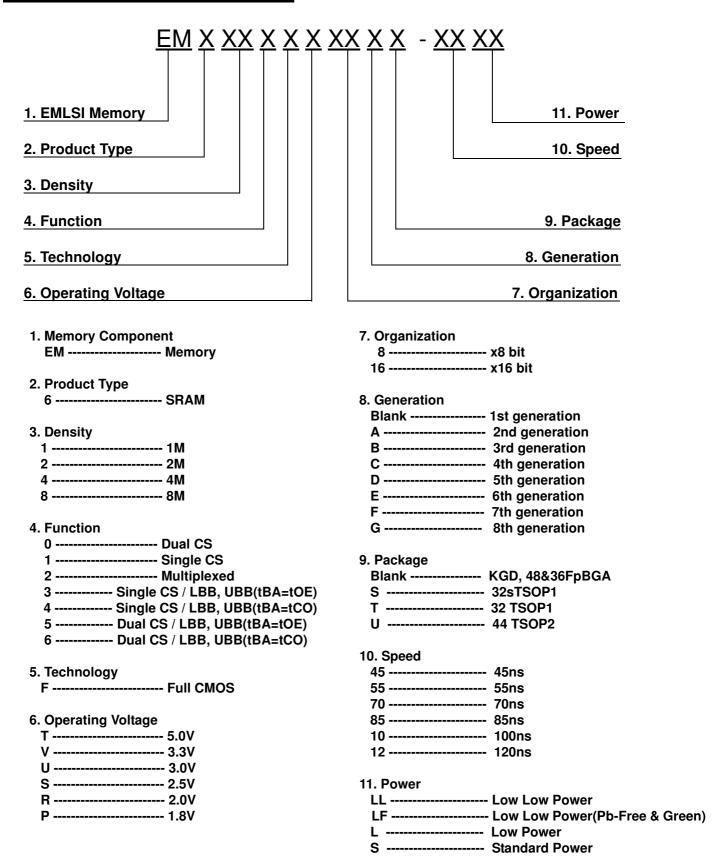

### **SRAM PART CODING SYSTEM**