# •₩YUNDAI

# **HY5216257 Series**

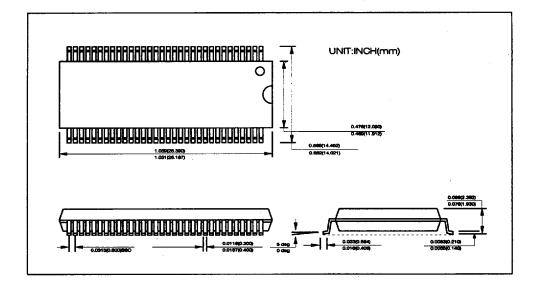

256K × 16-bit Video RAM with 2WE

#### Introduction

#### Overview

The 4megabit Video RAM is an application specific memory device designed for graphics applications. It comprises a 256k x16 DRAM memory array interfaced to a 256 x16 Serial Access Memory (SAM), or register. A half row of data, 256 columns x 16 bits, can be transferred from the DRAM array into the register in a single RAS cycle. Subsequently, the data can be read serially, 16bits(one address) at a time, starting from any arbitrary address location within the register. Once the data is transferred into the register from the DRAM array, the DRAM is free to be read or written through its random port. Concurrently and asynchronously, data can be accessed from the SAM port.

#### Features

- 8 x 8 (x2) Block Write allows as many as 128 bits of data to be written in every CAS cycle.

- Persistent and nonpersistent Write Per Bit operations allow individual write control to each DRAM I/O.

- Separate high and low byte write enable signals to facilitate byte write operations.

- Normal Fast Page mode with Extended Data Out delivers 33 MHz read/write performance on DRAM port.

- Pipelined page mode delivers 50 MHz peak read or write performance on DRAM port.

- Split serial register architecture allows one half of the register to be loaded from DRAM while the

other half is read out of the SAM port.

- Binary stop detection in the SAM allows jumps to a new starting location while data is being accessed, facilitating the design of "tile mapped" displays and displays of any arbitrary pixel resolution.

- Selective Flash Write for large area fills (available at customer request).

- . Compatible with JEDEC standards.

| VCC   1                 | 64 SC                  |            |                                      | cross<br>reference |

|-------------------------|------------------------|------------|--------------------------------------|--------------------|

| 777G E 2<br>∨8S E 3     | 63 D SE<br>62 D VSS    | Pin        | Description                          | Telefel ICe        |

| SGO El 4                | 61 0 8015              |            |                                      |                    |

| 000 0 5                 | eo D DQ15              | A0-A8      | Address Inputs                       |                    |

| 801 0 6                 | 59 E SQ14              | DQ0-DQ15   | DRAM I/O, Write Mask                 | W0/100-W15/101     |

| DQ1 D 7                 | 58 E DQ14              | RAS<br>CAS | Row Address Strobe                   |                    |

| voc 🗖 a                 | 57 D VCC               | WEL.WEU    | Column Address Strobe                |                    |

| 802 E 9                 | 56 E SQ13              |            | DRAM Byte Write Enables              |                    |

| DC22 🗖 10               | 55 D DQ13              | TRG        | DRAM Output Enable /                 | DT/OE,TR/OE        |

| SQ3 🗖 11                | 54 D SQ12              |            | Transfer select                      | 1                  |

| DQ3 [] 12               | 53 D DQ12              | DSF        | Special Function Select              | DSF1               |

| V8S 🗖 13                | 52 D VSS               | DSF2       | Enables pipelined page mode          | l                  |

| SQ4 C 14                | 51 2 5011              | QSF        | Special Function Output              | l                  |

| DOM 1 15<br>SOS 1 16    | 50 DQ11                |            | (high/low serial bank active flag)   | l                  |

| 006 1 17                | 49 D SQ10<br>48 D DQ10 |            | ( ingertions don't be in doubt inag) |                    |

| VCC 118                 | 47 B VCC               |            |                                      |                    |

| SQ6 D 19                | 48 D SQ6               | sc         | Serial Clock                         |                    |

| DOS 20                  | 45 E DQ9               |            |                                      |                    |

| SQ7 E 21                | 44 E SQ8               | SQ0-SQ15   | Serial Data Output                   |                    |

| DQ7 C 22                | 43 D DQ8               | SE         | Serial Output Enable                 | i                  |

| V8S [ 23                | 42 🗖 VSS               |            | i                                    | )                  |

| WEL C 24                | 41 DSF                 | VCC        | Supply Voltage, 5 volts              | i                  |

| <u>WE</u> D <u>I</u> 26 | 40 D DSF2              | VSS        | Ground                               | 1                  |

| FAS C 26                | 39 D CAS               |            | 1                                    | 1                  |

| A8 C 27<br>A7 C 28      | 38 D C6F               |            | ı                                    | l                  |

| A7 🖸 26<br>A6 🖸 29      | 37 D AO                |            |                                      | 1                  |

| A5   30                 | 36 D A1<br>36 D A2     |            |                                      | 1                  |

| A   31                  | 34 1 43                |            |                                      | !                  |

| V00 E 32                | 33 5 788               |            |                                      |                    |

Figure 1. Pin Diagram and Nomenclature

**=** 4675088 0005098 690 |

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any responsibility for use of circuits described. No patent licences are implied.

1089

| RAS<br>Access<br>Time | RAS<br>Cycle<br>Time | Page Mode<br>Cycle Time | Pipelined Page<br>Mode Cycle<br>Time | Serial Data<br>Cycle Time | Icc, DRAM Port<br>Read/Write | icc,Serial<br>Port |

|-----------------------|----------------------|-------------------------|--------------------------------------|---------------------------|------------------------------|--------------------|

| 60 ns                 | 101 ns               | 30 ns                   | 20 ns                                | 18 ns                     | 140 mA                       | 40 mA              |

Table 1. Major performance parameters

#### **Definition of Terms and Conventions**

RAM, or DRAM: The circuitry comprising the random access memory

SAM: The circuitry comprising the serial access memory.

IOi, DQi, Planei: The individual I/Os comprising the 16 bit DRAM port. DQi may also be used to refer to the specific package pin corresponding to I/Oi(Planei).

Low byte refers to data stored in or accessed from DQ0-DQ7. High byte refers to data stored in or accessed from DQ8-DQ15.

Write Mask, or Write Mask Register: A register comprising 16 bits, each bit controlling a write operation to one of the 16 planes. In write per bit mode, write mask bit i enables or disables a write operation to IOi (planei). The write mask is thus a *control* register.

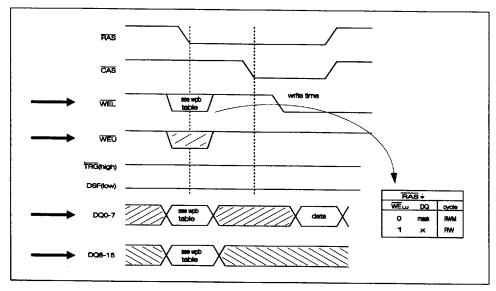

Write Time: The latter of CAS going low and either WEL going low, if the low byte is to be written, or WEU going low, if the high byte is to be written. This is consistent with conventional DRAM timing except that individual write controls are available for the low and high bytes.

Signal(RAS): The state of signal when RAS goes low.

Signal(CAS): The state of signal when CAS goes low.

Signal(write): The state of signal at write time.

Address Mask, Column Mask, or Column Address Mask: The mask formed by DQ0(write)-DQ7(write) for the lower byte and DQ8(CAS)-DQ15(CAS) for the upper byte which replaces the column address bits A0-A2 during Block Write operations. The address mask contains only address information.

A signal is said to be asserted when it is in its active state, regardless if the signal is active high or active low. A signal is said to be negated if it is in its inactive state, regardless if the signal is active high or active low.

Tap, or Starting Location: The position within the SAM at which the SAM will begin access after a transfter cycle or bank switch.

Quad Row: One quarter of a row of DRAM, ordered as follows:

| Column Addresses | Quad Row |

|------------------|----------|

| 0-127            | 0        |

| 128-255          | 1        |

| 256-383          | 2        |

| 384-511          | 3        |

Half Row: One half of a row of DRAM, ordered as follows:

| Column Addresses | Half Row |

|------------------|----------|

| 0-255            | low      |

| 255-511          | high:    |

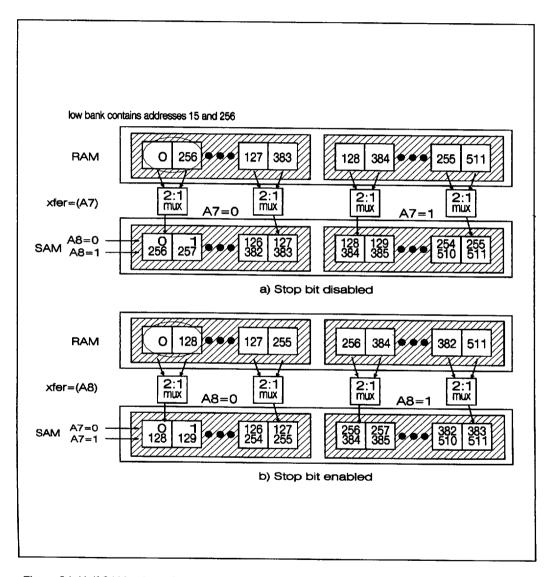

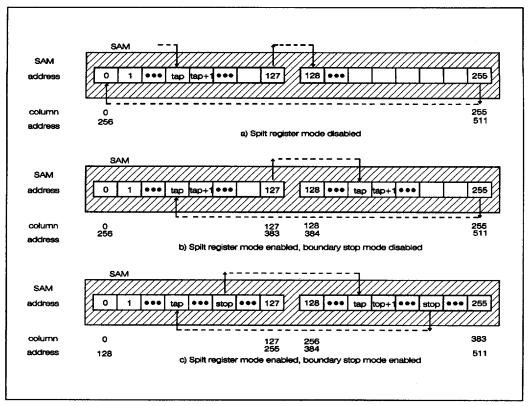

SAM Bank, or Bank: One half of the SAM register, designated as either the low or the high bank. Mapping to column addresses will depend on whether or not binary stop bit mode is enabled.

Word: The sixteen bits of data, DQ0-DQ15 correponding to a single memory address.

| · •  | ■ 4675088 | 0005099 | 527 |                |

|------|-----------|---------|-----|----------------|

| 1090 |           |         |     | 1VC02-00-MAY05 |

#### **Architecture**

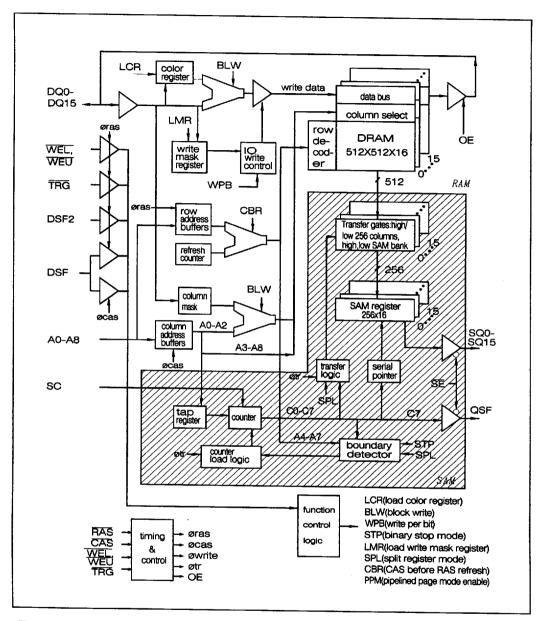

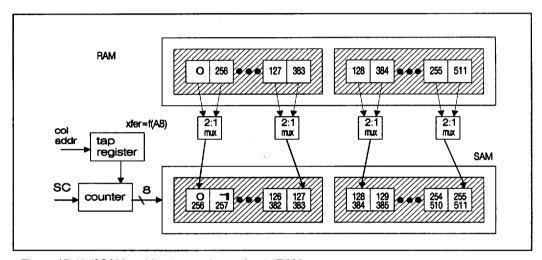

Figure 3 shows the top level block diagram of the 4 megabit Video RAM. The shaded area provides a conceptual boundary of the SAM and the supporting circuitry required to transfer data from the RAM to the SAM. The area outside of the shaded region corresponds to the RAM. The signals in boldface are external, or package pin signals.

#### Pin Description(per mode)

A0-A8(address); Address, Input

RAM Operations: Eighteen address bits of information are required to decode one of 256K memory addresses. The address is divided into a 9-bit row address and a 9-bit column address. The row address is presented on A0-A8 on the falling edge of RAS and the column address is presented on A0-A8 on the falling edge of RAS.

Transfer Operations: In a normal transfer operation, the address of the row to be transferred to the SAM is presented on A0-A8 at the falling edge of RAS. The column address within the row at which serial data will begin access from is presented on A0-A8 on the falling edge of CAS. Column address A8 designates either the lower 256 columns (0-255) of the row or the upper 256 columns (256-511) of the row to be transferred to the 256 bit positions in the SAM. A8=0 selects the lower 256 columns and A8=1 selects the upper 256 columns. Column addresses A0-A7 determine which of the 256 possible start, or tap locations the SAM will begin reading from.

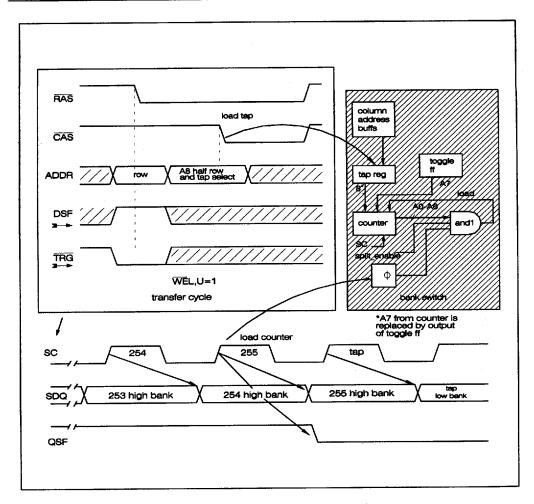

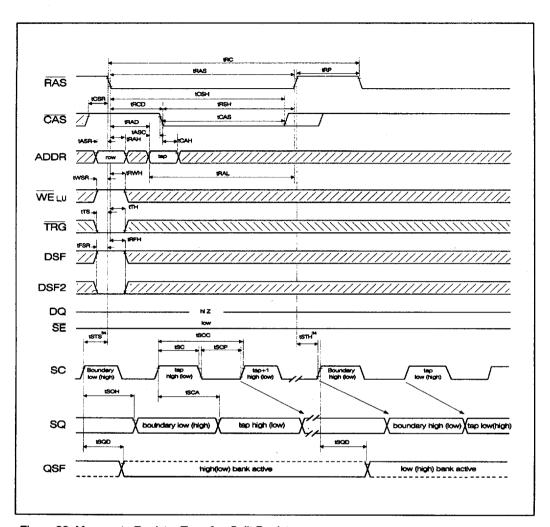

In split register mode the SAM is further divided into two banks, a low bank comprising register locations 0-127 and a high bank comprising register locations 128-255. Each bank holds one *quad row* of data. During split register transfer operations. A7 is ignored on the falling edge of CAS. An internal toggle flip flop arrangement remembers which segment is active and which segment is to be reloaded.

When enabling the stop bit mode of serial operation via a CBR refresh with stop bit enable (CBRS) cycle, A4-A7 contain the stop bit information at the falling edge of RAS. Strictly speaking, A7 is not used. However to maintain compatibility with 512 word SAM devices it is recommended that A7 be supplied and set to a logic low level during all CBRS cycles.

## DQ0-DQ15(RAM data); Data, IO; Address (block write), input

RAM Operations: During normal DRAM operations, DQ0-DQ15 provide the datapath into and out of RAM. During read cycles, data from the selected memory address is delivered to DQ0-DQ15 after the RAS, CAS, and output enable (TRG) access times have been satisfied. During write cycles, DQ0-DQ15 provide the data to be written to RAM.

DQ0-DQ15 will go to low impedance during all read, late write, and read-modify-write cycles when the following events and conditions occur.

- 1. TRG is brought low after RAS goes low

- 2. CAS goes low while RAS is low and WEL, WEU are high

DQ0-DQ15 will return to high impedance when any of the following events occur.

- 1. TRG goes high

- 2. RAS and CAS both go high (end of active cycle)

- 3. Either WEL or WEU goes low during any active read, write, or hidden refresh cycle.

TRG provides unlatched output impedance control of DQ0-DQ15. If TRG goes high and then low during an active read cycle, DQ0-DQ15 will go to high impedance and then back to low impedance. If RAS and CAS both go high, DQ0-DQ15 will go to high impedance and remain in high impedance until the next RAS activated read, late write, or read-modify write cycle. If WEL or WEU go low during any active cycle, then DQ0-DQ15 will go to high impedance and remain in high impedance until either of the following conditions occur.

**4675088 0005100 079**

- a. WEL, WEU return high and CAS is then brought low (eg. a page mode write-read sequence)

- b. The RAS cycle ends and another read, late write, or read-modify write cycle is performed

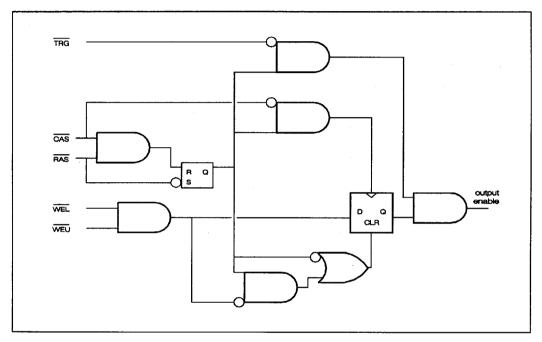

Figure 2 below shows a simplified logic diagram for the output enable control circuitry during read, write, and hidden refresh cycles. DQ0-DQ15 remain in high impedance during CAS before RAS auto refresh cycles.

Figure 2. Simplified logic of output enable control for read and write cycles

Transfer Operations: DQ0-DQ15 are not used during RAM to SAM transfer operations. They remain in high impedance for the entire transfer cycle.

Figure 3. Top Level Functional Block Diagram

## RAS(Row Address Strobe); Control, Input

RAS initiates all RAM and transfer cycles. On the falling edge of RAS, a memory or transfer cycle is initiated, a row address is latched on A0-A8, and the states of CAS, TRG, WEU, WEL, DSF, and DSF2 are latched to determine the type of cycle to be executed. RAS going high terminates the active portion of the memory cycle, except that any data read on DQ0-DQ15 will remain active untill CAS goes high or TRG goes high. This allows hidden refresh cycles to be supported.

## CAS(Column Address Strobe): Control, Input

CAS is a control input which functions as a column address strobe and cloumn select.

RAM operations: CAS going low latches the column address presented on A0-A8 and enables the column circuitry. CAS going low also latches the state of DSF to enable/disable block write operation or to enable/disable a "load color register" cycle. See Table 2 for details. The 4 megabit Video RAM supports Extended Data Output Page Mode operation, which means that data remains valid after CAS goes high. This allows the address for the next page mode cycle to be set up while data from the current cycle is latched by the accessing device.

Transfer Operations: During transfer operations, CAS going low latches A0-A8 to select which columns of the selected row in RAM are to be transferred to the SAM and also to select the starting location at which the SAM will begin accessing from.

## TRG (Transfer / RAM output enable): Control, Input

The TRG signal is latched on the falling input of RAS to select either a RAM or a transfer operation.

RAM operations: TRG functions as an output enable for DQ0-DQ15.

Transfer operations: On normal transfer cycles, TRG controls the physical transfer of data from the RAM to SAM and the reloading of the serial counter to the new tap address. During split register transfer cycle, holding TRG low when RAS falls enables a transfer from RAM to the inactive bank of the SAM. The timing of the physical transfer of data is controlled internally and is completed within the transfer cycle. Also during split register mode operation, the reloading of the serial counter, and therefore the readout of the SAM from the new tap location in the inactive bank, is deferred until after the most significant address (binary stop mode enabled) or a specified boundary address (binary stop mode enabled) is read out from the active bank of the SAM.

## WEL, WEU (Byte Write Enable, write per bit select): Control, Input

RAM Operations: WEU, WEU are latched on the falling edge of RAS to enable or disable write per bit operation. If either WEU or WEU is held low on the falling edge of RAS, write per bit mode will be enabled for all 16 DQs. If write per bit mode is disabled, then the write to the sixteen DQs is controlled exclusively by WEU(for DQ0-DQ7) and WEU (for DQ8-DQ15). If write per bit mode is enabled, then the write to any DQ is enabled by setting its correponding write mask bit to 1 using either persistent or non persistent write per bit mode. Subsequently, the actual write to that DQ is performed by asserting that DQ's correponding byte write enable, WEU or WEU, during write time. WEU, and WEU can also be used to control the output impedance of DQi, All DQ's will go to the high impedance state whenever WEU or WEU is asserted(low).

Serial Operations: WEU, WEU are not used during actual serial operation, however they are used to invoke the boundary stop mode of serial operation. This is accomplished by performing a special CAS before RAS(CBRS) cycle with either WEU or WEU held low on the falling edge of RAS. See Table 2 for details.

Transfer Operations: not used

## DSF (Special Function Select); Control, Input

Random Operations: Enables persistent write per bit mode and loads the write mask register. Allows persistent write per bit mode to be sustained during CBR cycles. Enables block mode write operation and the loading of

the on chip color register used during block write operations. Enables selective flash write operation using the contents of the color register. (Flash write is available as a special part number at customer request.) See Table 2 for details.

Transfer Operations: Selects between split register and non split register transfer and serial operation.

## DSF2(Special Function Select): Control, Input

Random Operations: Enables / disables pipelined page mode operation.

Transfer Operations: Not used.

SC(serial clock): Clock, Input

RAM Operations: not used

Transfer Operations: Not used per SE, but there are important timing parameters which must be met to synchronize SC to the transfer operation. In normal transfers (split register mode disabled). SC must be synchronized with respect to TRG1 to be sure that the last bit of the old register contents and the first bit of the new register contents are read properly. During split register transfers, the transfer cycle must be completed sufficiently in advance of the last bit being read out of the SAM from the active portion of the register. See Timing Diagrams for details.

## SQ0-SQ15(Serial Data); Output

RAM Operations: not used

Transfer Operations: Not used.

Serial Operations: SQ0-SQ15 are the output data terminals for the SAM. Data from the SAM is normally accessed serially, module 256, from each SC↑ starting from the tap location selected during the the previous transfer cycle. In split register mode, however, the SAM will skip to the tap address in the inactive bank whenever a "boundary crossing" occurs in the active bank and a transfer to the inactive bank has occured before the boundary in the active bank is reached.

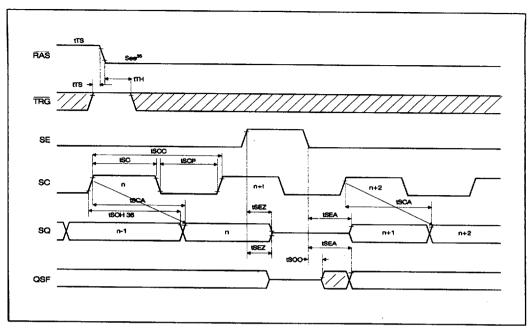

## SE(Serial Output and QSF Enable); Control, Input

Serial Operations: Enables or disables serial data output at SQ0-SQ15 and the bank active output QSF. Important: SE is only a serial output enable, not a general serial mode enable. Thus, if SE is negated, the counter is not prevented from advancing if the serial clock (SC) continues to toggle. The serial register and supporting circuits are static, so no refresh operations are required to sustain information in the SAM.

## QSF (Special Function Output, Active Register Flag); Control, Output

Serial Operations: This signal outputs a 0 if the lower bank of the register is being accessed, a 1 if the higher bank of the register is being accessed, and is in the high impedance state if SE is negated.

## **Description of Functional Units**

The block diagram shown in Figure 3 should be referenced for discussions of the major functional blocks.

#### Write Mask Register

The write mask register is a 16 bit register used to control the internal write enables to each IO, or plane in RAM. The write mask register can be loaded from the DQ inputs on a per write cycle basis, known as "nonpersistent" mode, or can be loaded during a special "Load write Mask Register" (LMR) cycle with timing and control similar to a conventional DRAM write cycle. Once a Load Write Mask cycle is executed, the Video RAM goes into "persistent" mode, and will use the contents of the write mask on every write per bit write cycle thereafter until persistent mode is disabled. While in persistent mode, the contents of the write mask cannot be altered, except

4675088 0005104 714 🖿 -

by another Load write Mask Register cycle. The Video RAM can be returned to nonpersistent mode by performing a special CAS before RAS(CBRR) cycle "with option reset." See Table 2 for details.

## **Byte Write Input Buffers**

To facilitate byte write operations, the 4Mb Video RAM features separate WE pins, denoted WEL and WEU (dual WE version)or separate CAS pins, denoted CASL and CASU,(dual CAS version) to individually control write operations to DQ0-DQ7 and DQ8-DQ15 respectively. Timing for each is similar to conventional DRAM operation.

The byte write enable signals can be combined with write per bit operation. For example, if write per bit mode is enabled, a particular IO is written if and only if both its byte write enable signal and its correposating bit in the write mask register are asserted.

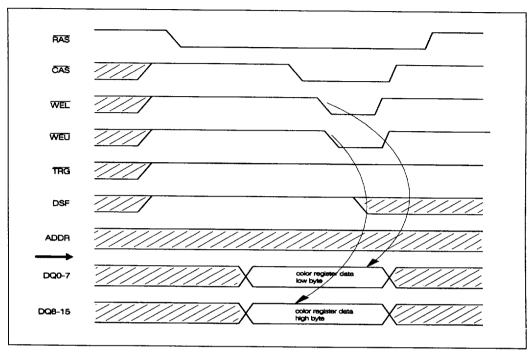

#### **Color Register**

The color register is a 16 bit register used as an alternate data source during block write operations. The register is loaded from the DQi inputs during "Load Color Register" (LCR) cycles and used as data during block write cycles. Once loaded, it cannot be altered except by another LCR cycle or by removing power from the device.

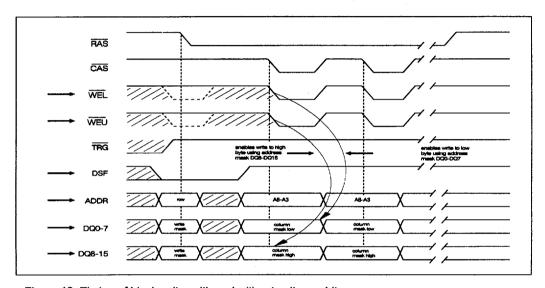

#### Column Address Mask

During block write cycles, the column mask is used to select any arbitrary subset of eight contiguous column locations in RAM chosen by A3-A8 to be written using the contents of the color register. The column mask is loaded from the DQ inputs at write time during block write cycles. Separate 8-bit masks are loaded on DQ0-7 and DQ8-15, meaning that the subset of columns written to memory can be different for the high and low bytes. If block write mode is enabled, the column mask can be changed during each page mode write cycle, allowing the column mask to be controlled dynamically during page mode operation as A3-A8 is changed.

## **Special Function Logic**

The special function logic is a control block that takes as input CAS(RAS), TRG(RAS), WEU(RAS), WEU(RAS), DSF(RAS), and DSF(CAS) and gives as output the control signals necessary to execute the various special function cycles. The modes can be deduced from the signals output from the special function logic in Figure 3.

#### Serial Access Memory(SAM)

Although the SAM is accessed serially according to the corresponding column addresses in RAM, it is implemented internally as a RAM with a counter supplying the address. The counter is incremented by each positive edge of the serial clock, SC.

#### Transfer Logic

Controls the logic and timing for the various operating modes of transfer operation, including real time data transfer, split register transfer, early and late load, and binary stop mode enabled and disabled.

#### Transfer Gates

The transfer gates are MOSFETS connected between each pair of bit lines and a register bit inside the SAM. While in split register mode the register can be loaded one bank at a time. The upper bank can be loaded while the lower bank is read out through the SAM port and vice versa.

#### Counter

The counter is presettable from the tap register. During normal transfers (split register mode disabled), it is loaded from the tap register while the transfer logic completes the physical transfer of data from RAM to SAM. In split register mode, the loading of the counter is deferred until the last bit is read out of the active bank.

1096 4675088 0005105 650 ■ 1VC02-00-MAY95

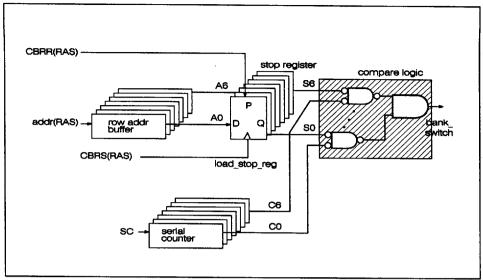

#### **MSB** Detector

During split register mode, the MSB detector reads the outputs of the counter and issues a bank switch signal when the most significant address is read from either the high or low bank in the SAM. The MSB detector essentially detects all 1's from the seven least significant bits of the counter. When the binary stop bit mode is enabled, only some of these bits are compared for 1's, depending upon which stop bits are enabled. Enabling the stop bits is done by performing a CBRS cycle(See Table 2 for detailed logic assignments).

#### **Timing**

In general, there are three types of operations which can be occuring in the Video RAM: DRAM access, serial access, and transfer cycles. When not transferring data from RAM to SAM, the timing block can be thought of as two independent sub blocks, one controlling DRAM read, write, and refresh operations and the other controlling the advancing of the counter and the serial read path in the SAM. During transfer cycles, the two timing blocks must be synchronized, especially during real time register load cycles.

## **Summary of Special Functions**

The special functions of the 4Mb Video RAM, are invoked by decoding the states of the control pins, including DSF and DSF2, on the falling edges of RAS and CAS. The DQ pins will assume various functions, providing information other than just normal RAM data, depending on the particular cycle invoked. For example, the DQ pins serve as a write mask on write per bit cycles and as a multiple (column) address mask on block write cycles.

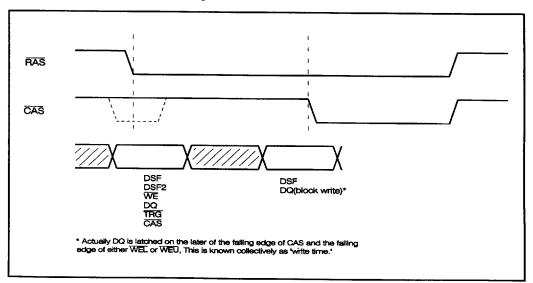

Figure 4 below illustrates the general timing by which the control inputs are latched and the cycle types that they select. See the timing parameters and diagrams for details.

Figure 4. Special Function Control Scheme

Table 2 shows the JEDEC approved truth table describing how the various DRAM and transfer cycles are invoked. The mne codes are used throughout this document to refer to the particular cycles defined in the table.

| Function, or Cycle Type                                             | RAS↓<br>signal(RAS) |     |              |     |       |               | CAS↓<br>signal(CAS) |     | CAS↓ & (WEL↓  T WEU↓)1 | mne<br>code      |      |

|---------------------------------------------------------------------|---------------------|-----|--------------|-----|-------|---------------|---------------------|-----|------------------------|------------------|------|

|                                                                     | CAS                 | TRG | WEL,<br>WEU2 | DSF | DSF2  | Ad-<br>dress  | DQi3                | DSF | Ad-<br>dress           | DQi              |      |

| CBR, reset to nonpersistent & disable stop bit mode                 | 0                   | ×   | 1            | 0   | 0     | x             | x                   | x   | x                      | x                | CBRR |

| CBR, Enable, set Stop bit                                           | 0                   | ×   | 0            | 1   | 0     | stop<br>A4-A7 | x                   | ×   | ×                      | x                | CBRS |

| CBR,No reset to nonper-<br>sistent or disable of stop bit           | 0                   | ×   | 1            | 1   | 0     | x             | ×                   | x   | x                      | x                | CBRN |

| Read Transfer                                                       | 1                   | 0   | 1            | 0   | 0     | row           | x                   | x   | tap                    | x                | RT   |

| Split Register Read Transfer                                        | 1                   | 0   | 1            | 1   | 0     | row           | х                   | х   | tap                    | x                | SRT  |

| DRAM write per bit,<br>nonpersistent, use new mask                  | 1                   | 1   | 0            | 0   | note4 | row           | Write-<br>mask      | 0   | col-<br>umn            | data             | RWM  |

| DRAM bolck write with write per bit, nonpersistent, use new mask    | 1                   | 1   | 0            | 0   | note4 | row           | write-<br>mask      | 1   | block<br>addr<br>A3-A8 | col addr<br>mask | BWM  |

| DRAM write per bit,<br>persistent, use old mask                     | 1                   | 1   | 0            | 0   | note4 | row           | x                   | 0   | col-<br>umn            | data             | RWM  |

| DRAM block write with write<br>per bit, persistent, use old<br>mask | 1                   | 1   | 0            | 0   | note4 | row           | x                   | 1   | block<br>addr<br>A3-A8 | col addr<br>mask | BWM  |

| Masked Flash Write,<br>nonpersistent, use new mask                  | 1                   | 1   | 0            | 1   | 0     | row           | write-<br>mask      | x   | x                      | ×                | FWT⁵ |

| Masked Flash Write, per-<br>sistent, use old mask                   | 1                   | 1   | 0            | 1   | 0     | row           | x                   | x   | x                      | x                | FWT⁵ |

| DRAM write, no write per bit, no mask                               | 1                   | 1   | 1            | 0   | note4 | row           | ×                   | 0   | col-<br>umn            | data             | RW   |

| DRAM block write, no write per bit, no mask                         | 1                   | 1   | 1            | 0   | note4 | row           | x                   | 1   | block<br>addr<br>A3-A8 | col addr<br>mask | BW   |

| Load Write Mask Register                                            | 1                   | 1   | 1            | 1   | 0     | x             | x                   | 0   | x                      | write<br>mask    | LMR  |

| Load Color Register                                                 | 1                   | 1   | 1            | 1   | 0     | x             | x                   | 1   | ×                      | color<br>data    | LCR  |

## **Table 2. Special Function Truth Table**

1098

4675088 0005107 423 1VC02-00-MAY95

Notes;

1 The signals on all DQ pins are strobed in on the later of the falling edge of CAS and the falling edge of either WEL and WEU, However, the low (high)byte is not enabled for write operation unless WEL (WEU) is asserted.

<sup>&</sup>lt;sup>2</sup> The 0's in this column denote that WEL=0 or WEU=0. The 1's in this column denote that WEL=1 and WEU=1.

<sup>&</sup>lt;sup>3</sup> DQi refers to DQ0 - DQ15 collectively.

<sup>&</sup>lt;sup>4</sup> Available in extended data out page mode (DSF2 low when RAS↓) and pipelined page mode with extended data out (DSF2 high when RAS↓).

<sup>&</sup>lt;sup>5</sup> Available by special part number at customer request.

## Parametric specifications

## **Absolute Maximum Ratings**

| SYMBOL    | PARAMETER                                 | RATING      | UNIT |  |

|-----------|-------------------------------------------|-------------|------|--|

| TA        | Operating Temperature (Ambient)           | 0 to 70     |      |  |

| TSTG      | Storage Temperature(Plastic)              | -65 to 150  | °C   |  |

| VIN, VOUT | Voltage on Vcc Supply Pin Relative to Vss | -1.0 to 7.0 | V    |  |

| Iso       | Short Circuit Output Current              | 50          | mA   |  |

| PD        | Power Dissipation                         | 1.1         | W    |  |

NOTE: Stresses greater than those listed above may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended Operating Conditions**

| SYMBOL | PARAMETER          | MIN. | TYP. | MAX. | UNIT |

|--------|--------------------|------|------|------|------|

| Vcc    | Supply Voltage     | 4.5  | 5.0  | 5.5  | V ´  |

| Vss    | Supply Voltage     | _    | 0    | _    | V    |

| ViH    | Input High Voltage | 2.4  | _    | 6.5  | V    |

| VIL    | Input Low Voltage  | -1.0 | _    | 0.8  | V    |

## Capacitance

(TA=25°C, Vcc=5V+10%, f=1MHz)

| SYMBOL | PARAMETER                                              | MAX. | UNIT |

|--------|--------------------------------------------------------|------|------|

| Cic    | Input Capacitance(RAS,CAS, WEL,u,TRG, SC,SE, DSF,DSF2) | 7    | pf   |

| CIA    | Input Capacitance(A0 - A8)                             | 5    | pf   |

| Ci/o   | Input/Output Capacitance(DQ)                           | 7    | pf   |

| Co     | Output Capacitance (SQ, QSF)                           | 7    | pf   |

## **DC Characteristics**

(TA=0°C to 70°C, VCC=5V+10%, VSS=0V, unless otherwise noted.)

| SYMBOL | PARAMETER              | TEST CONDITIONS                                      | MIN. | MAX. | UNIT |  |

|--------|------------------------|------------------------------------------------------|------|------|------|--|

| lu     | Input Leakage Current  | 0V ≤ VIN ≤ 5.5V<br>All other pins not under test=Vss | -10  | 10   | μА   |  |

| ILO    | Output Leakage Current | 0V < Vout < 5.5V<br>SQ, DQ pins disabled             | -10  | 10   | μА   |  |

| Vol    | Output Low Voltage     | IOL=2mA                                              | -    | 0.4  | V    |  |

| VoH    | Output High Voltage    | IOH=-1mA                                             | 2.4  | _    | V    |  |

## **ICC Characteristics**

(TA= 0°C TO 70°C, VCC=5V+10%, VSS=0V, unless otherwise noted.)

|        | PARAMETER               |                                          |         | HY52 | 16257 |      | NOTE |

|--------|-------------------------|------------------------------------------|---------|------|-------|------|------|

| SYMBOL |                         | TEST CONDITIONS                          | SAM     | -60  | -70   | UNIT |      |

|        |                         |                                          |         | MAX. | MAX.  |      |      |

| lcc1   | Operating Current       | RAS & CAS Cycling,                       | Standby | 140  | 115   | mA   | 11   |

| ICC1A  | -Read/Write/LMR/LCR     | tRC= tRC (min.)                          | Active  | 185  | 135   | mA   | 2    |

| ICC2   | Standby Current         | RAS & CAS=VIH,                           | Standby | 5    | 5     | mA   | 1    |

| ICC2A  | -TTL input Levels       | Other Pins Vss                           | Active  | 45   | 40    | mA   | 2    |

| ICC3   | RAS Only Refresh        | RAS Cycling, CAS=VIH,                    | Standby | 140  | 115   | mA   | 11   |

| ICC3A  | Current                 | trc=trc (min.)                           | Active  | 185  | 150   | mA   | 2    |

| ICC4   | Fast Page Current       | RAS=VIL, CAS Cycling,                    | Standby | 110  | 85    | mA   | 1    |

| ICC4A  | rast rage Current       | tPC=tPC (min.)                           | Active  | 140  | 115   | mA   | 2    |

| ICC5   | CAS Before RAS          | RAS &VIL, CAS Cycling,<br>tRC=tRC (min.) | Standby | 140  | 115   | mA   | 1    |

| ICC5A  | Auto Refresh Current    |                                          | Active  | 185  | 155   | mA   | 2    |

| ICC6   | Data Transfer Current   | RAS & CAS Cycling,                       | Standby | 140  | 115   | mA   | 1    |

| ICC6A  | Data Transfer Current   | trc=trc(min.)                            | Active  | 185  | 155   | mA   | 2    |

| ICC7   | Flash Write Current     | RAS & CAS Cycling,                       | Standby | 140  | 115   | mA   | 1    |

| ICC7A  | Flash Wike Cullent      | trc=trc(min.)                            | Active  | 170  | 142   | mΑ   | 2    |

| ICC8   | Page Block Write        | RAS=VIL, CAS Cycling,                    | Standby | 140  | 115   | mA   | 1    |

| ICC8A  | Current                 | tPC=tPC(min.)                            | Active  | 185  | 130   | mA   | 2    |

| ICC9   | Pipelined Page Current  | RAS=VIL, CAS Cycling,                    | Standby | 140  | 115   | mA   | 1    |

| ICC9A  | ripelliled rage Current | tPCP=tPCP (min.)                         | Active  | 185  | 150   | mA   | 2    |

| ICC10  | Pipelined Page          | RAS=VIL, CAS Cycling,                    | Standby | 140  | 115   | mA   | 1    |

| ICC10A | Block Write Current     | tPCP=tPCP (min.)                         | Active  | 185  | 150   | mA   | 2    |

## Notes:

- 1. SAM Standby: SE at VIH and SC stable at either VIH OR VIL

- 2. SAM Active: SE at VIL and tScc=tScc(min)

- 3. An initial pause of 200µs is required after power-up followed by 8 refresh cycles, 8 transfer cycles and 8 pulses or more of SC clock before proper device operation is achieved. In case of using internal refresh counter, a minimum of 8 CAS-Before-RAS initialization cycles are required (Within the power-up and pause time, all control and address signals should be fixed high or low, or should be turned on in compliance with Vcc.)

4675088 0005110 T18 **=**

## **AC Characteristics**

|    |        | PARAMETER                                                      |      | HY521    | E    |        |      |      |

|----|--------|----------------------------------------------------------------|------|----------|------|--------|------|------|

| #  | SYMBOL |                                                                |      | -60      |      | -70    | UNIT | NOTE |

|    |        |                                                                | MIN. | MAX.     | MIN. | MAX.   |      |      |

| 1  | taa    | Acess time from column address                                 |      | 30       | -    | 35     | ns   | 5    |

| 2  | tasc   | Cojumn address setup time                                      | 0    | _        | 0    | -      | ns   |      |

| 3  | tasd   | Column address to first SC high after TRG high (Read Transfer) | 25   | -        | 25   | -      | ns   | 12   |

| 4  | tasr   | ROW address setup time                                         | 0    |          | 0    | -      | ns   |      |

| 5  | tath   | TRG hold time from column address (real time data transfer)    | 18   | -        | 18   | -      | ns   |      |

| 6  | tawd   | Column address to WE low delay time (RMW cycles)               | 50   | -        | 60   | -      | ns   | 6    |

| 7  | tCAC   | Access time from CAS low (Extended Data Out mode)              | -    | 17       | -    | 20     | ns   | 3,5  |

| 8  | tCAC2  | Access time, 1st bit from CAS low (pipelined page mode)        | -    | 18       | -    | 22     | ns   |      |

| 9  | tCAH   | Column address hold time                                       | 10   | <b>-</b> | 10   | -      | ns   |      |

| 10 | tCAL   | Column address to CAS high delay time (Extended Data Out)      | 25   | -        | 35   | •      | ns   |      |

| 11 | tCAS   | CAS low pulse width                                            | 10   | 10,000   | 10   | 10,000 | ns   |      |

| 12 | tCASP  | CAS low pulse width (piplined page mode)                       | 7    | 10,000   | 10   | 10,000 | ns   |      |

| 13 | tCFH   | DSF hold time from CAS low                                     | 10   | -        | 10   | -      | ns   |      |

| 14 | tchr   | CAS hold time from RAS low (CBR cycles)                        | 10   | -        | 10   | -      | ns   |      |

| 15 | ICLZ   | Output enable delay from CAS low                               | 3    | -        | 3    | -      | ns   | 3    |

| 16 | tсон   | DQ output form CAS low                                         | 4    | -        | 5    |        | ns   |      |

| 17 | tCP    | CAS precharge time                                             | 10   | _        | 10   | -      | ns   |      |

| 18 | tCPP   | CAS precharge time (pipelined page mode)                       | 7    | -        | 10   | -      | ns   |      |

| 19 | tCPA   | Access time from previous CAS high (page mode)                 | _    | - 35     | -    | 40     | ns   | 5    |

| 20 | tcqD   | CAS low QSF propagation delay time (early load)                | -    | 30       | -    | 30     | ns   | 11   |

| 21 | tcsp   | CAS low to first SC high after TRG high (Read Transfer)        | 20   | -        | 20   | -      | ns   | 12   |

| 22 | tcsH   | CAS low hold time from RAS low                                 | 53   |          | 60   | -      | ns   |      |

## AC Characteristics(continued))

|    |        | PARAMETER                                                    |      | HY5216 | UNIT |      |    |      |

|----|--------|--------------------------------------------------------------|------|--------|------|------|----|------|

| #  | SYMBOL |                                                              | -60  |        |      | -70  |    | NOTE |

|    |        |                                                              | MIN. | MAX.   | MIN. | MAX. |    |      |

| 23 | tcsr   | CAS setup time before /RAS low                               | 0    | _      | 0    | -    | ns | 13   |

| 24 | tстн   | TRG hold time from CAS low (Real Time Data Transfer          | 15   | -      | 15   | -    | ns |      |

| 25 | tcwp   | CAS low to WE low delay time (RMW cycles)                    | 37   | -      | 45   | -    | ns | 6    |

| 26 | tCWL   | Write low to CAS high delay (lead) time                      | 15   | -      | 15   | _    | ns |      |

| 27 | tCWLP  | Write low to CAS high delay (lead) time, pipelined page mode | 7    | -      | 10   | -    | ns |      |

| 28 | tDH    | Data hold time                                               | 12   | _      | 15   | -    | ns |      |

| 29 | tos    | Data setup time                                              | 0    | -      | 0    | -    | กร |      |

| 30 | tozc   | Data bus tristate to CAS low delay time                      | 0    | -      | 0    | -    | ns | 10   |

| 31 | tozo   | Data bus tristate (no input data) to TRG low delay time      | 0    | -      | 0    | -    | ns | 10   |

| 32 | trsc   | DSF setup time before CAS low                                | 0    | _      | 0    |      | ns |      |

| 33 | tFSR   | DSF setup time before RAS low                                | 0    | -      | 0    | -    | ns |      |

| 34 | tmH    | Write mask hold time RAS low                                 | 10   |        | 10   | -    | ns |      |

| 35 | tms    | Write mask setup time before RAS low                         | 0    | -      | 0    | _    | ns |      |

| 36 | tOEA   | Access time from TRG low                                     |      | 15     | -    | 20   | ns | 5    |

| 37 | tOED   | TRG high to data applied on data bus delay time              | 10   | -      | 15   | -    | ns |      |

| 38 | toen   | TRG high time after WE low (to maintain tristate)            | 10   | -      | 10   |      | ns |      |

| 39 | tOELZ  | Output enable from TRG low                                   | 3    | _      | 3    | -    | ns |      |

| 40 | toez   | Output disable from TRG high                                 | 3    | 15     | 3    | 20   | ns | 6    |

| 41 | torc   | Output disable from CAS high                                 | 3    | 15     | 3    | 20   | ns |      |

| 42 | tofr   | Output disable from RAS high                                 | 3    | 15     | 3    | 20   | ns |      |

| 43 | tPC    | Read or write page mode cycle time.                          | 30   |        | 30   | _    | ns |      |

| 44 | tPCP   | Read or write page mode cycle time (pipelined page mode)     | 20   | -      | 25   | _    | ns |      |

| 45 | tPRWC  | Read-modify-write page mode delay time                       | 75   | -      | 80   | -    |    |      |

| 46 | trac   | Access time from RAS low                                     | -    | 60     | -    | 70   |    |      |

## AC Characteristics(continued)

| #  | SYMBOL |                                                         |     | HY5216257GE |      |         |      |      |

|----|--------|---------------------------------------------------------|-----|-------------|------|---------|------|------|

|    |        | PARAMETER                                               | -60 |             | -70  |         | UNIT | NOTE |

|    |        |                                                         |     | MAX.        | MIN. | MAX.    |      |      |

| 47 | trad   | RAS low to column address delay time                    | 15  | 30          | 15   | 35      | ns   | 3    |

| 48 | trah   | Row address hold time                                   | 10  | -           | 10   | -       | ns   |      |

| 49 | tRAL   | Column address to RAS high lead time                    | 30  | -           | 35   | - :     | ns   |      |

| 50 | tRAS   | RAS pulse width                                         | 60  | 10,000      | 70   | 10,000  | ns   |      |

| 51 | trasp  | RAS pulse width<br>(page or pipelined page mode)        | 60  | 100,000     | 70   | 100,000 | ns   |      |

| 52 | tRC    | Read or write cycle time                                | 100 | -           | 120  | -       | ns   |      |

| 53 | tRCD   | RAS low to CAS low delay time                           | 20  | 43          | 20   | 50      | ns   | 7    |

| 54 | trch   | Read command hold time after CAS high                   | 0   | _           | 0    | -       | ns   | 8    |

| 55 | tRCS   | Read command setup time                                 | 0   | -           | 0    | -       | ns   |      |

| 56 | tREF   | Refresh period                                          | -   | 8           |      | 8       | ms   |      |

| 57 | tRFH   | DSF hold time from RAS low                              | 10  | -           | 10   | -       | ns   |      |

| 58 | tROH   | RAS low hold time from TRG low                          | 15  | _           | 15   | -       | ns   |      |

| 59 | tRP    | RAS precharge time                                      | 35  | -           | 45   | -       | ns   |      |

| 60 | tRPC   | RAS high(precharge)to CAS low delay time                | 0   | -           | 0    | -       | ns   | 14   |

| 61 | tRQD   | RAS low to QSF delay time (early load)                  |     | 60          | -    | 70      | ns   | 11   |

| 62 | trrh   | Read command hold time after RAS high                   | 0   | -           | 0    | -       | ns   | 8    |

| 63 | trsd   | RAS low to first SC high after TRG high (Read Transfer) | 60  | •           | 70   | •       | ns   | 12   |

| 64 | trsh   | RAS low hold time from CAS low                          | 15  | -           | 20   | -       | ns   |      |

| 65 | trth   | TRG hold time from RAS low (real time data transfer)    | 45  | -           | 55   | -       | ņs   |      |

| 66 | trwc   | Read-modify-write cycle time                            | 140 | -           | 165  | •       | ns   |      |

| 67 | tRWD   | RAS low to write WE low delay time<br>(RMW cycles)      | 80  | -           | 95   | -       | ns   | 6    |

| 68 | tRWH   | WE hold time from RAS low                               | 10  | -           | 10   | -       | ns   |      |

| 69 | trwl   | WE low to RAS high delay (lead) time                    | 15  |             | 15   | -       | ns   |      |

| 70 | tsc    | SC high pulse width                                     | 5   | -           | 8    | -       | ns   |      |

| 71 | tSCA   | SQ access time from SC high                             | -   | 15          | -    | 20      | ns   | 11   |

## AC Characteristics(continued)

| #  | SYMBOL | PARAMETER                                                                        |       | HY521 | UNIT  | NOTE |     |    |

|----|--------|----------------------------------------------------------------------------------|-------|-------|-------|------|-----|----|

|    |        |                                                                                  | -60   |       |       |      | -70 |    |

|    |        |                                                                                  | MIN.  | MAX.  | MIN.  | MAX. |     |    |

| 72 | tscc   | SC serial cycle time                                                             | 18    | _     | 22    | -    | ns  |    |

| 73 | tscp   | SC slow pulse width                                                              | 5     | -     | 8     |      | ns  |    |

| 74 | tSEA   | Access time of SQ and QSF from /SE low                                           | -     | 12    | -     | 15   | ns  | 11 |

| 75 | tsez   | Serial output buffer turn off delay from SE high                                 | 3     | 10    | 3     | 15   | ns  |    |

| 76 | tson   | Serial output hold time from SC high                                             | 4     | _     | 5     |      | ns  |    |

| 77 | tsoo   | Serial output turn on delay from SE low                                          | 3     | _     | -     | -    | ns  |    |

| 78 | tsop   | SC high to QSF delay time                                                        | -     | 20    |       | 25   | ns  | 11 |

| 79 | tsrs   | SC high to RAS low<br>(CBRS, CBRR cycles only)                                   | 10    | -     | 10    | -    | ns  |    |

| 80 | tsтн   | Split transfer hold time (RAS high to SC high of active bank boundary location)  | 15    | -     | 20    | •    | ns  |    |

| 81 | tsts   | Split transfer set up time (SC high of active bank boundary location to RAS low) | 15    | •     | 20    | -    | ns  |    |

| 82 | tтн    | TRG hold time from RAS low                                                       | 10    |       | 10    | -    | ns  |    |

| 83 | tr     | Transition time, rise and fall                                                   | 3     | 50    | 3     | 50   | ns  | 1  |

| 84 | tτΡ    | TRG high pulse width                                                             | 15    | -     | 20    | _    | ns  |    |

| 85 | tTQD   | TRG high to QSF delay time                                                       | -     | 25    | -     | 25   | กร  | 11 |

| 86 | ttrp   | TRG high to RAS low precharge time (late load data transfer)                     | tRP+5 | -     | tRP+5 | •    | ns  |    |

| 87 | trs    | TRG setup time before RAS low                                                    | 0     | -     | 0     |      | ns  |    |

| 88 | ttsd   | TRG high to first SC high delay time (Read transfer)                             | 20    | -     | 25    | -    | ns  | 12 |

| 89 | tTSL   | Last SC high to TRG high delay (lead) time (Read Transfer)                       | 5     | -     | 5     | -    | ns  | 12 |

| 90 | ttrrh  | TRG high to RAS high delay time                                                  | -10   | -     | -10   | ~    | ns  |    |

| 91 | twch   | Write command setup time                                                         | 10    | -     | 15    | -    | ns  |    |

| 92 | twez   | Output disable time from WE low (while CAS is high)                              | 3     | 15    | 3     | 20   | ns  |    |

| 93 | twcs   | Write command setup time                                                         | 0     | _     | 0     |      | ns  | 9  |

| 94 | tWP    | Write command pulse width                                                        | 10    | -     | 10    | -    | ns  |    |

| 95 | twsR   | WE setup time before RAS low                                                     | 0     |       | 0     |      | ns  |    |

#### Notes:

- 1. AC measurements assume tT=3ns.

- 2. VIH(min.) and VIL(max.) are reference levels for measuring timing of input signals. Also, transition times are measured between VIH and VIL.

- Operation within the tRAD(max.), tRCD(max.) limit ensures that tRAC(max.) can be met. The tRAD(max.)

limit is specified as a reference point only. If tRAD is greater than the specified tRAD(max.) limit, then access time is controlled by tAA.

- 4. If tASC > tAA tCAC -tT and tRAD > tRAD(max.), the access time is controlled by the column address.

- 5. Measured with a load equivalent to 1 TTL loads plus 50pF and output reference level is VoH/VoL = 2V/0.8V.

- toez define the time at which the output achieves the open circuit condition and is not referenced to output voltages levels.

- 7. trcD(min.) = trah(min.)+2tr+tasc(min.)

- 8. Either tRCH or tRRH must be satisfied for a read cycle.

- 9. twcs indicates early write operation, and not an operational limit point of the device. If twcs ≥ twcs(min.), the cycle is an early is an early write cycle and data out pin will remain open circuit(high impedance) through the entire cycle.

- 10. Operation is generated whichever timing requirement tozc or tozo is met.

- 11. Measured with a load equivalent to 1 TTL load plus 30pF serial data out reference level is VoH/VoL = 2V/0.8V.

- 12. Except split register transfers.

- 13. tcsR replaces both tcsR and tcRP quoted in specifications of other VRAM manufacturers.

- 14. Needed to avoid invoking a hidden refresh cycle.

## Operation (Cycle Description, Timing Overview)

#### **RAM Port**

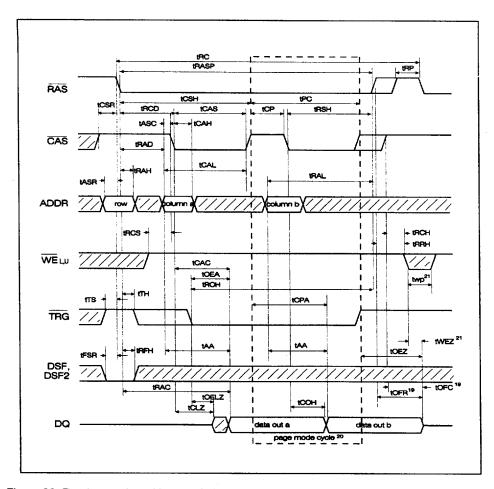

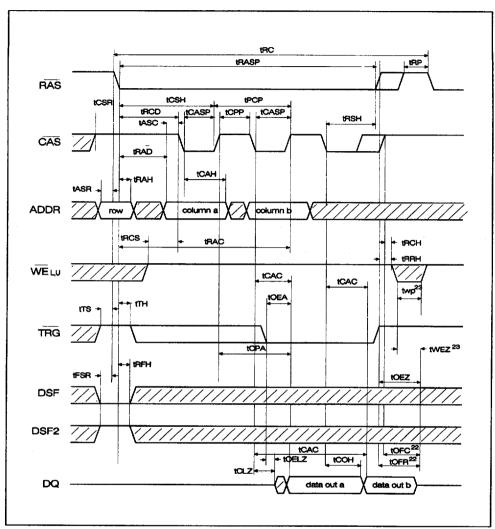

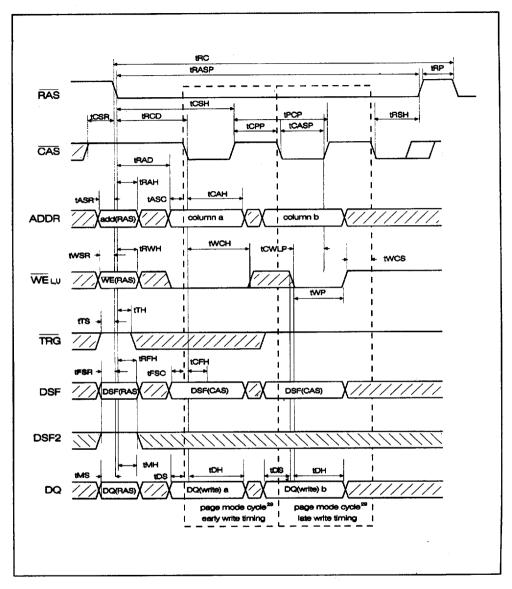

#### Read, Write, RMW with EDO mode

Read, write, and rdad-modify-write cycles are executed similarly to normal DRAM operations and are described by the detailed timing diagrams. However it is instructive to define here the mechanism of extended data output page mode.

Extended data output page mode differs from traditional fast page mode in that once RAS and CAS are brought low and RAS remains low, CAS has no tristate control over the random outputs (DQ pins). When CAS goes high, data corresponding to the previous CAS low remains valid on DQi. During page mode, this allows the accessing device more time to latch the data while CAS goes back high to set up the next page mode access.

WEL and WEU provide tristate control over the DQ pins and latch the data presented on the DQ pins and control the write operation. Whenever WEU is asserted, the all sixteen DRAM output bufffers will go to tristate.

## Read, Write, with pipelined page mode

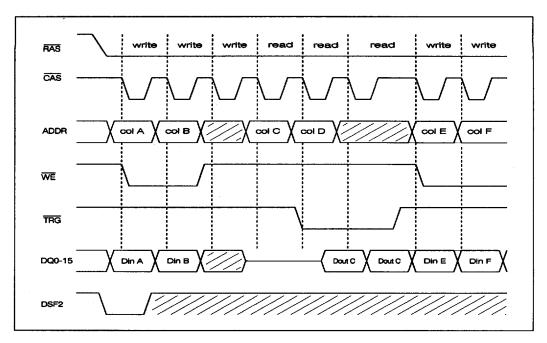

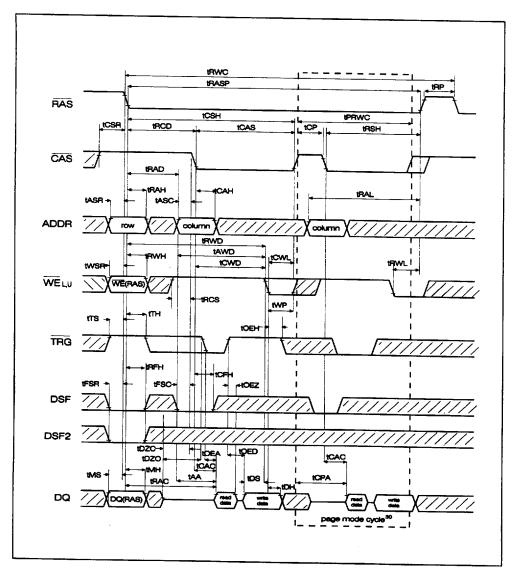

Pipelined page mode is selected using the DSF2 control input. In this mode, a pipeline register is activated in the page mode read data path. This substantially accelerates the peak data rate at the DRAM outputs while introducing one additional page mode cycle of latency before the first address is read out. Thus, to read out n column addresses, a total of n+1 CAS cycles must be performed. Pipelined page mode is ideal for performing long, high speed bursts of reads or bursts of writes within a page. During write operations, data is actually written during the page mode cycle in which it and its corresponding column address are latched, so no additional clock cycles are necessary to complete the last write operation. However to maintain compatibility with other implementations of pipelined page mode, it is recommended that one additional page mode cycle be performed at the end of each burst of pipelined page mode write operations. Pipelined page mode read cycles can be intermixed with pipelined page mode write cycles during the same RAS low period, however each burst of in reads, consuming n+1 CAS cycles, must be completed before initiating a burst write sequence. Likewise, when pipelined page mode reads follow a burst of in pipelined page mode writes, n+1 CAS cycles are recommended to complete the write operations. Following the n+1 CAS cycle, pipelined page mode read operation can begin and the first data read out will occur on the second CAS cycle following the n+1 CAS cycle which completed the write operation. Figure 5 illustrates intermixed read and write cycles during pipelined page mode operation. Pipelined page mode is available for all DRAM read and write operation, including byte write, block write, and write per bit cycles. For details, see the timing diagrams.

#### Refresh

#### Refresh Requirements

The 4Mb Video RAM contains 512 row addresses which must be refreshed within each eight millisecond interval. On the 4Mb Video RAM, certain CAS before RAS cycles (CBRR and CBRS) are also used to enable or disable useful special functions as indicated in Table 2 and described below.

#### **RAS Only Refresh**

RAS only Refresh is performed as in conventional DRAMs, by supplying the address of the row to be refreshed on the falling edge of RAS. Generally, CAS, WEL, WEU, and TRG are negated throughout the RAS only refresh cycle. There are no specific timing constraints beyond normal DRAM refresh cycles.

|                | 4675088 | 0002116 | 436 |  |      |

|----------------|---------|---------|-----|--|------|

| 1VC02-00-MAY95 |         |         |     |  | 1107 |

Figure 5. Write-Read-Write burst sequence in Pipelined Page Mode

#### Hidden Refresh

This cycle is performed identically to conventional DRAMs. Prior to a hidden refresh cycle, RAS, CAS, and TRG are asserted, causing data to appear at the DQ outputs. Subsequently, RAS is negated while both CAS and TRG remain asserted RAS is again asserted and the row addressed by the internal CBR counter is refreshed. The hidden refresh cycle allows a useful refresh operation to be performed while data is waiting to be latched by the accessing device.

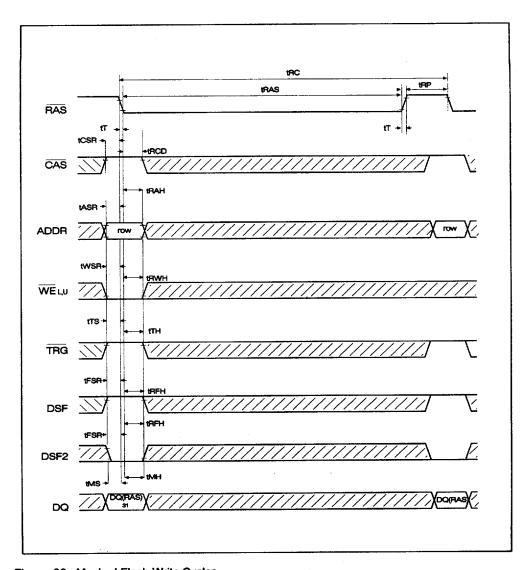

#### CBR Refresh, Normal Mode with Option Reset.(CBRR)

The 4Mb Video RAM has an internal 9-bit row address counter which is incremented on every CBR refresh cycle. During CBRS cycles, DSF(RAS) is low, so that two functions are accomplished. First, the row addressed by the CBR counter is refreshed. Second, the Video RAM unconditionally disables persistent write per bit and serial binary stop bit modes of operation. Persistent write per bit mode can be re-enabled by performing a Load Write Mask (LMR) cycle. Stop bit mode can be re-enabled by performing a stop mode enable CBR cycle(CBRS). Typically, a system will use either persistent or non persistent write per bit mode exclusively. Likewise, a system will typically use or not use stop bit mode all of the time. During power up, a CBRR cycle can be executed to clear both persistent mode and stop bit enable mode. From there, each mode can be selected individually by executing the LMR and CBRS cycles according to Table 2.

## CBR Refresh; Persistent, Stop Bit Modes Not Reset..(CBRN)

Same as CBRR, except that DSF(RAS)=1, preventing persistent mode and stop bit mode from being reset. This CBRN cycle cannot be used to change the Video RAM from nonpersistent mode to persistent mode. That is accomplished by performing Load Write Mask Register(LMR) cycles.

## CBR Refresh, Set Binary Stop for Split Register.(CBRS)

The CBRS cycle performs a CBR refresh and enables stop bit mode to be used in serial split register operation. The stop bits are supplied on the A4-A7 pins on the falling edge of  $\overline{RAS}$ .

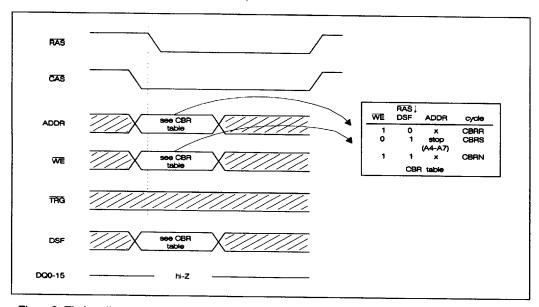

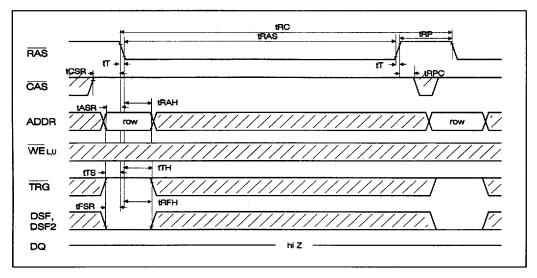

Figure6. Timing diagram of CBR cycles

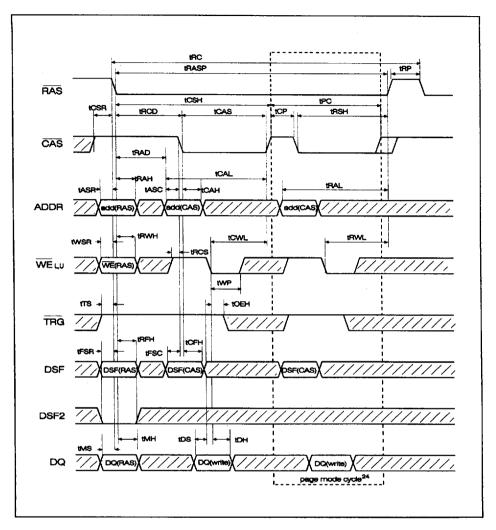

#### Write Per Bit

Write per bit mode allows the write of data to each of the sixteen RAM DQs to be controlled individually. A 16 bit write mask is supplied to the video RAM on its DQ lines at the falling edge of RAS. The mask is latched and stored on chip and is used to select which DQs will be written during write per bit cycles and which will not. If the mask bit for DQi is a 1. DQi will be written at write time during write per bit cycles. If the mask bit for DQi is a 0. DQi will not be written at write time during write per bit cycles.

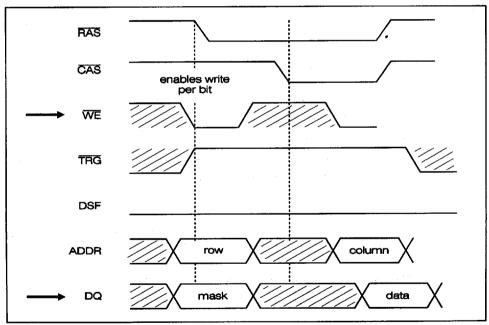

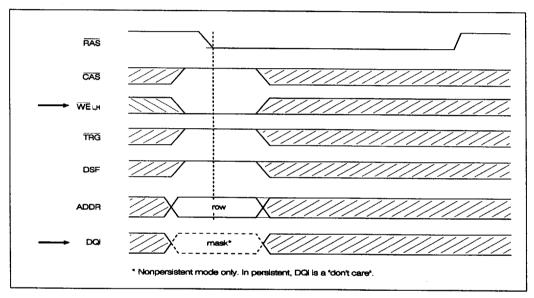

#### Nonpersistent Write Per Bit

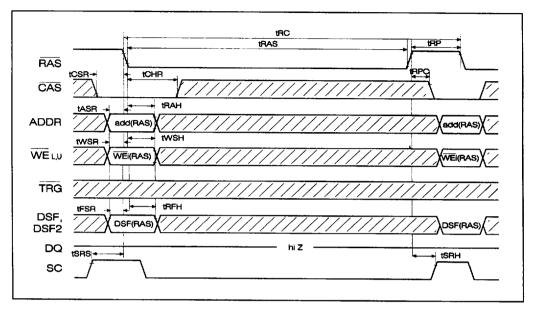

In nonpersistent write per bit mode, write per bit mode is selected by asserting either WEL or WEU on the falling edge of RAS. Also at the falling edge of RAS, the state of the DQ pins are latched and stored in the Video RAMS internal write mask register. At write time during the same cycle, the write mask is used as described in Section to enable write operation only to those DQs whose corresponding write mask bits are set to 1. Figure 7 illustrates the general timing and control of the nonpersistent write per bit write cycle. During page mode operation, the write mask is not changed. The same DQs are enabled on every page mode write cycle. The advantage of the nonpersistent write per bit mode is that the write mask can be loaded on every write per bit RAS cycle, providing maximum flexibility. The disadvantages are twofold. First, the timing is somewhat unlike conventional DRAMs, since the DQ lines must be driven with write control information as RAS is asserted. Second, and related to the first, the DQ lines cannot be "trimultiplexed" with the address lines, since the write mask would collide with the row address.

Figure 7. Nonpersistent (new mask) write per bit general timing

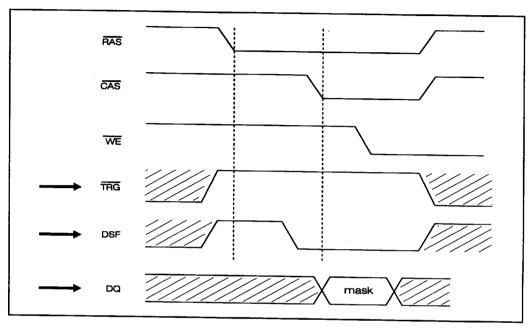

#### Persistent Write Per Bit

Often, the Video RAM user maintains the same write mask for many cycles. The persistent write per bit operation exploits this and resolves the two chief problems with nonpersistent write per bit operation. The general scheme is to split the write per bit function into two separate cycle types. The first cycle type (LMR) is used to load the write mask, using conventional DRAM timing and control. This enters the 4Mb Video RAM into the "persistent" mode.

Subsequent write per bit cycles are performed similar to nonpersistent mode, except that the write mask is not reloaded from the DQ lines when RAS falls. The write mask maintains the value it was written to during the previous write mask load (LMR) cycle. To change the write mask, another LMR cycle must be performed. Figure 8 illustrates the basic timing and control for the LMR cycle. Note that the write mask is written using conventional DRAM timing, except there is no required address. The destination of the write operation is the write mask register, not an address in RAM. The disadvantage of persistent write per bit mode is that an additional memory cycle is required each time the write mask is changed.

Figure 8. Persistent mode write per bit mask load (LMR) cycle.

Figure 9 shows a write per bit cycle being performed in persistent mode. Note that the state of the DQ lines is a don't care when RAS is asserted. There is no conflict between the row address and write mask, so the address and DQ lines can be tied together.

Persistent write per bit mode can be reset to nonpersistent mode by executing a CBRR.

Figure 9. Persistent mode write per bit, write cycles

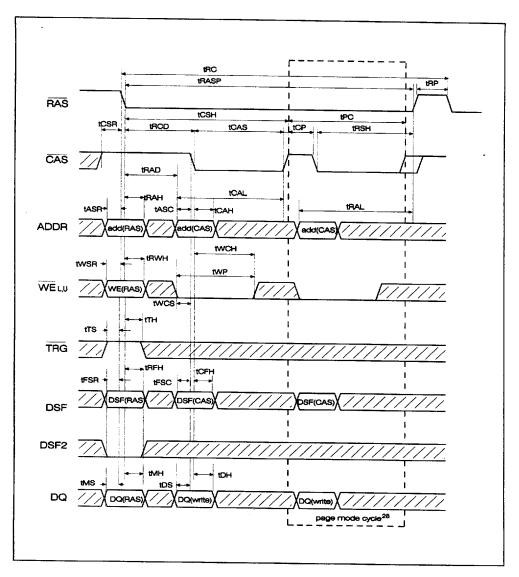

#### **Byte Write**

To facilitate byte operations, the 4Mb Video RAM is equipped with two write enable signals. WEL serves as the write enable for the lower byte. DQ0-DQ7, WEU serves as the write enable for the upper byte, DQ8-DQ15. Timing is similar to that of traditional single WE DRAM devices, with the following note worthy expections.

In the case where WEU and WEU are skewed, that is asserted or negated at different times, the write interval is defined by the assertion of the earlier of the two signals and the negation of the later of the two signals. In late write cycles, data setup time and data hold time are referenced from the earlier of WEL↓ or WEU↓. Also, if an early write cycle is invoked by asserting either WEL or WEU before CAS is asserted, then early write operation is invoked for both the high and low byte, with data setup time referenced to CAS for both bytes.

Byte write can be combined with write per bit. During write per bit operations, a DQ plane is written if and only if its corresponding write mask bit and byte write enables are asserted.

To invoke write per bit operation for both the high and low bytes, either WEL or WEU can be held low on the falling edge of RAS (See Table 2 and accompanying footnotes). If in non persistent mode, invoking write per bit will cause a new mask for both the high and the low bytes to be loaded from the DQ pins on the falling edge of RAS. At write time, a write to each of the 16 bits will occur if and only if its corresponding write mask register bit is set and its corresponding byte write signal (WEL or WEU) is asserted. Figure 10 shows an example of byte write with and without write per bit invoked.

■ 4675088 0005121 AT3 ■ 1112 1VC02-00-MAY95

The dotted lines refer to write per bit operation. In this example, WEL alone controls the invokation of write per bit, although WEU could have been used either alone or with WEL. Although write per bit is invoked according to the accompanying write per bit table, WEU is not asserted at write time and therefore no bits in the high byte will be written.

Figure 10. Example, byte write to low byte

#### **Block Write**

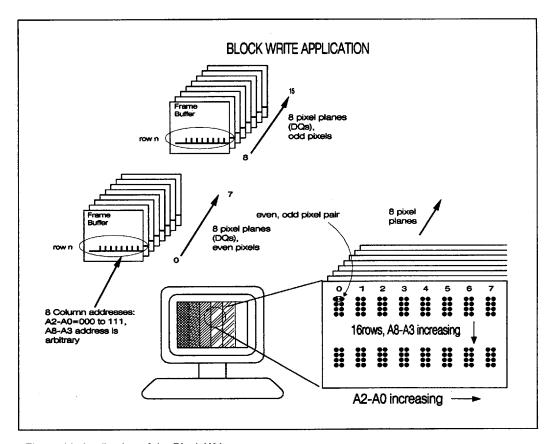

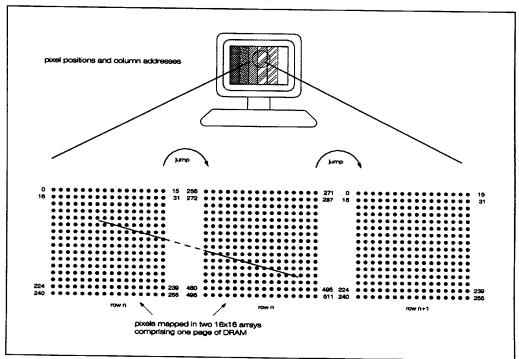

Block Write allows any subset of eight column location in RAM, chosen by A3-A8, to be written in a single write cycle using the contents of an on chip color register. The one-of-eight column select function normally performed by cloumn addresses A2-A0 is replaced by an "n of eight" (n=1 through 8) column select using DQ0-7 for the low byte and DQ8-15 for the high byte as an address mask. The Block Write thus gains write access to 16x8=128 bits of information. The application example in Figure 11 shows the 16 DQs of the 4Mb Video RAM split into two(8 bit per pixel)sets. So each 16 bit "word" represents an even and odd pixel pair.

The eight column addresses \*2 pixels per address = 16 pixels are mapped to 16 contiguous horizontal pixel locations on the display. By using an address mapping scheme known as "tiling," it is possible to combine such groups of pixels into multiple rows, creating a rectangular grid of pixels all mapped to a single page of the DRAM as shown. The graphics controller can mainpulate the pixels in the grid very quickly by operating in page mode. Each page mode cycle accesses on horizontal group of 16 pixels, that group consisting of 8 pixel pairs. Using Block Write, a write operation can be performed to any subset of the 8 pixel pairs using the contents of the color register. Block write is fully compatible with byte write and write per bit operation.

> 4675088 0005122 73T 📟 1113

The individual pixels in each pixel pair can be write controlled (written or not written) by either byte write operation(using WEL and WEÜ) or by using write per bit mode. Thus, by combining block write with either bype write or write per bit, any subset of the 16 pixels accessed on each page mode cycle can be written. With a little imagination, we can see how patterns(eg characters, line segments) within localized rectangular arrays of pixels can be quickly manipulated.

Figure 11. Application of the Block Write

#### **Load Color Register**

To perform block write cycles, the data to be written to the multiple column locations must first be loaded into the on chip color register using a Load Color Register(LCR) cycle. The timing and control is similar to a normal DRAM write cycle. The important differences are the values of DSF(RAS), DSF(CAS) and the fact that the address information supplied to the chip is ignored. Figure 12 illustrates the Load Color Register cycle using late write timing. The Color Register can also be loaded using early write timing. Also byte write is supported, allowing individual write control of each byte in the color register. The arrows in Figure 12 are intended to show that the writes of the high and low bytes are controlled by WEL and WEU respectively.

**4675088 0005123 676 🖿 \_**

Figure 12. Timing of the Load Color Register Cycle, late write timing

#### **Block Write Cycles**

One the desired data is loaded into the color register, the block write cycles can be performed. Figure 13 shows a sequence of page mode block write cycles. Block write can be combined with write per bit, as denoted by the dotted lines. Either WEL(RAS)=0 or WEU(RAS)=0 is sufficient to enable write per bit mode to both the low and the high byte. In this case, nonpersistent mode write per bit is being used, however persistent mode write per bit operation can also be used with block write. Consequently, block write can selectively write any DQ and any combination of eight contiguous column locations(selected by column address A8-A3) in a single CAS cycle. AS many as 8 ×16=128 bits of data can be written per CAS cycle in full page mode or pipelined page mode.

In each CAS cycle, the state of DSF is latched on the falling edge of CAS. DSF(CAS)=1 enables block write operation while DSF(CAS)=0 disables block write operation. DQ0-DQ7 is latched at write time, defined as the later of CAS falling and either WEL or WEU falling. DQ0-DQ7 are used as an eight bit address mask for the lower byte only, providing individual write control to the block of eight column addresses defined by A3(CAS)-A8(CAS). The eight least significant DQ pins replace the address inputs A0-A2. For example, if DQ0(write time)=1, then column A2-A0=000b, lower byte will be written with the data stored in the lower byte of the color register. If DQ0(write)=0, then column A2-A0=000b, lower byte will not be written with the data stored in the lower byte of the color register. Thus:

1VC02-00-MAY95 4675088 0005124 502 ■ \_\_\_\_\_\_ 1115

#### for i=0-7

DQi(write)=1 enables write to address A2-A0=i, low byte. DQi(write)=0 disables the write to A2-A0=i, low byte.

Likewise, DQ8(write)-DA15(write) are used as an eight bit address mask for the upper byte only, providing individual write control to the block of eight column addresses defined by A3(CAS)-A8(CAS).

#### for i=8-15

DQi(write)=1 enables write to address A2-A0=i, high byte. DQi(write)=0 disables the write to A2-A0=i, low byte.

Figure 13. Timing of block write, with and without write per bit.

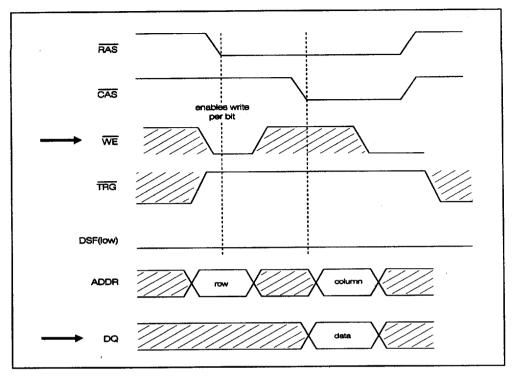

## Flash Write(non standard feature, available at customer request)

Flash Write allows all 512 columns of an addressed row to be written in a single minimum RAS cycle time using the contents of the on chip color register. Flash Write is unconditionally masked with respect to each DQ in RAM using the contents of the Write Mask Register either in persistent or in non persistent mode. If the Write Mask bit for DQi is set to "1", then during the Flash Write cycle all columns in the addressed row for DQi will be written using the contents of bit "i" in the color register. A simplified timing diagram of the Flash Write cycle is shown in Figure 14. Flash Write is invoked by holding CAS, TRG, and DSF high and either WEL or WEU low during the falling edge of RAS. If the device is operating in nonpersistent mode, the write mask must be supplied on the DQ pins during the falling edge of RAS. If the device is operating in persistent mode, the write mask must be previously loaded using a Load Mask Register(LMR) cycle as described. The color register is loaded using a Load Color Register (LCR) cycle as described.

Figure 14. Masked Flash Write general timing

#### Transfer Operation, RAM to SAM

Periodically, data will need to be transferred from a specified row in RAM to the SAM in order to provide data to the video display system. This is referred to as a transfer, a transfer read, or memory-to-register transfer operation. These terms will be used interchangeably in this specification unless otherwise noted.

## **Discussion of Address Mapping**

#### Half SAM architecture

To facilitate discussion of the SAM serial architecture, the reader should review the definition of terms and conventions.

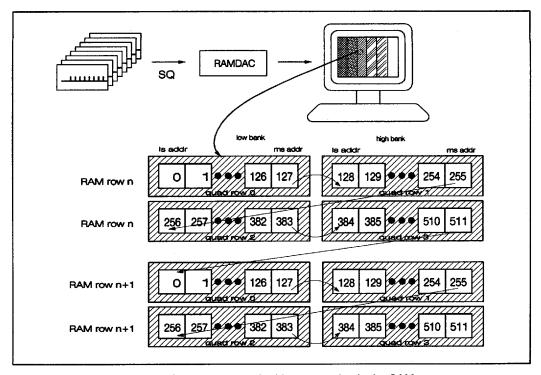

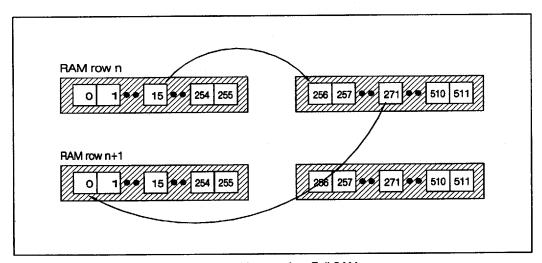

During normal transfer cycles in which address A8=0 on the falling edge of CAS, data from column addresses 0-255 are loaded from the selected row in RAM to the SAM. During normal transfer cycles in which address A8=1 on the falling edge of CAS, data from column addresses 256-511 are loaded from the selected row in RAM to the SAM. The selection of the upper or lower 256 columns is shown in Figure 15.

Figure 15 also illustrates the internal mapping in RAM required for the half SAM architecture. The columns in RAM are interleaved with respect to A8, creating a sequence of:

n. n+256 for n=0 to 255

From an internal chip design standpoint, we will see that this internal mapping is modified when the Video RAM is operated in binary stop bit mode. To support binary stop bit mode, an internal(transparent to user) column address bit swap between column addresses. A8 and A7 is invoked. The effect of this swap is to reverse the physical positions of quad rows 2 and 3 in both RAM and SAM. This address swap is required to maintain socket compatibility with full SAM devices.

Figure 15. Half SAM architecture and mapping to RAM

## Overview of transfer operations

There are five distinct types of transfer operations:

- 1. normal transfer

- 2. read time transfer and real time transfer with late load

- 3. early transfer(or early load)

- 4. split register transfer, for use in split register serial operation

- 5. split register transfer, for use in split register serial operation, with binary stop bit mode enabled

#### **Normal Load**

1118

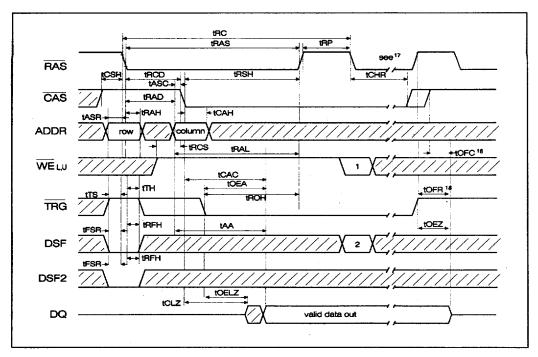

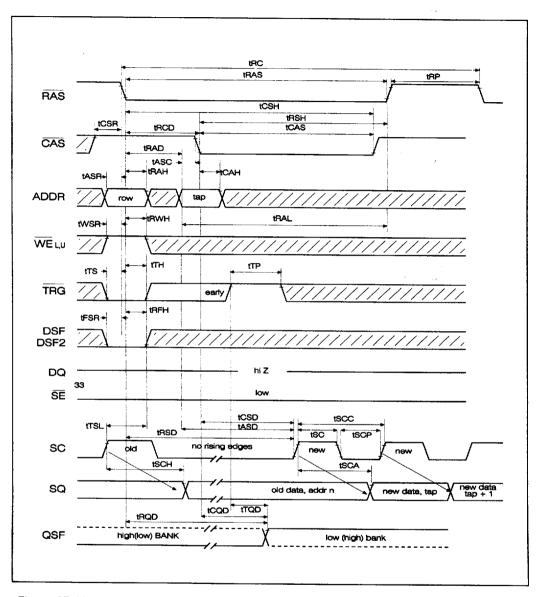

Figure 16 illustates the sequence of operations for a normal transfer read. To transfer data to the register from DRAM, the DRAM begins to access the required row of data similar to the way it would in a normal read cycle. On the falling edge of CAS, A8 is latched and determines whether the lower 256 column will be loaded into the SAM(A8=0) or the upper 256 columns will be loaded into the SAM(A8=1).

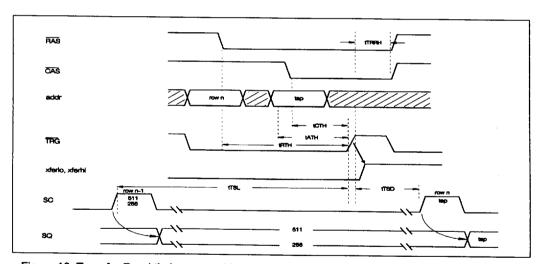

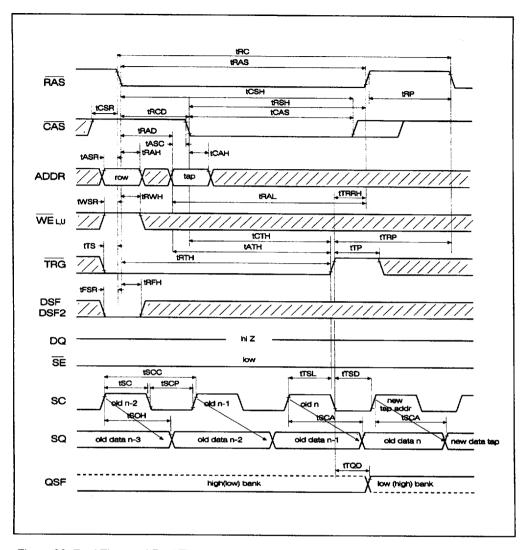

Also on the falling edge of CAS, the starting location, or tap, is loaded into an on chip tap register from column address pins A0-A7. Subsequently, when TRG goes high, the data are transferred to the serial register and the serial counter is reloaded from the tap address register. The data at the serial output does not change until the first positive edge of the serial clock after TRG goes high.

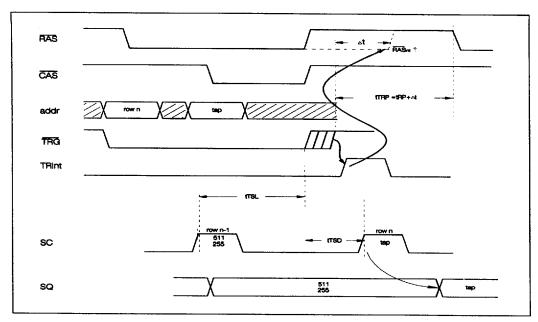

There are historically six key timing parameters that must be met during transfer cycles, all relating to the physical transfer of information to the SAM and the clocking of the SAM register directly before and after the physical transfer. These are shown in Figure 16 and are discussed below.

trsi, or last SCT of old register contents to TRG 1, guarantees the last bit will appear out of the SAM from the old register contents before the transfer and will remain until the next SCT.

trso, or TRG ↑ to first SC↑ of new register contents after transfer, guarantees that the transfer is completed in sufficient time to guarantee the serial data access time for the first access after the transfer.

tктн, or RAS↓ to TRG↑, guarantees that the data from the half row to be transferred is safely latched on the bit lines before transfer begins.

tcm, or CAS ↓ to TRG↑, guarantees that the tap address is safely latched so the access of the first address after transfer is not delayed.

taπ, or column address valid to TRG↑, also guarantees that the tap address is safely latched so the access of the first address after transfer is not delayed.

trring, or TRG ↑ to RAS↓, guarantees that the transfer will be completed before the end of the RAS low time.

Figure 16. Transfer Read timing, normal load

Note that the physical transfer of data from RAM to SAM must be performed between two serial clock positive edges. Under normal load conditions, this time interval, defined mostly by trsule trso is generally large and poses no significant synchronization problems. For some applications, however, this time interval will become very narrow, and synchronization problems will occur. To circumvent these problems, this Video RAM supports both real time load and split register load.

\_\_\_\_\_ 4675088 0005128 158 **\_\_\_**\_\_

In addition to the problem of synchronizing the serial clock to the transfer operation, the parameters tath, toth, ath, and trash have historically caused syncronization problems by placing significant timing constraints on TRG1, particularly when the RAS low time is near the minimum spec value. To relax the timing constraints in this regard, this Video RAM supports early load and late load transfer cycles.

#### Real time transfer

Real time transfer, or real time load, is a simple extension of normal load. It is intended to allow continuous serial data streams while the transfer is occuring, but places most of the burden of synchronization on the user. Basically, the real time load is a normal load in which the serial clock, SC, continues to clock data during the transfer cycle both before and after TRG↑. In other words, the parameters tTSL and tTSD are taken to their specification limits, as shown in Figure 17.

Figure 17. Transfer Read timing, real time load

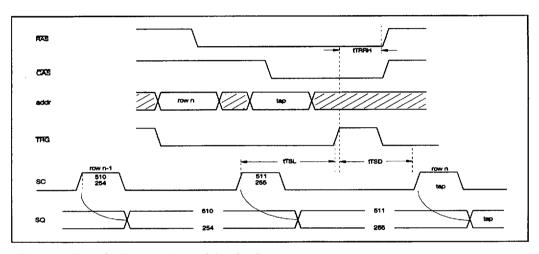

## Real Time Transfer with Late Load

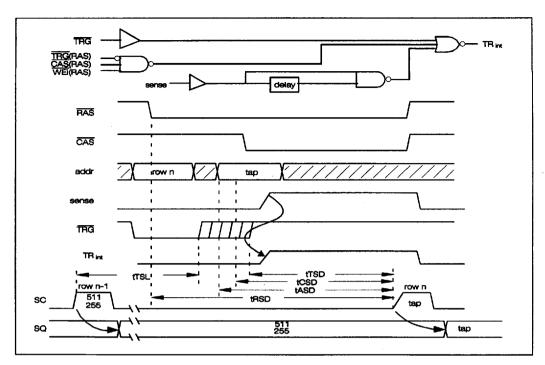

In the Real:time transfer with late load, the trans parameter is eliminated, allowing TRG to go high before, coincident with, or after RAS goes high. Internally, RAS is prevented from going high, since the data from the RAM must remain on the bit lines until after TRG↑ and the transfer has completed. Since the precharge cycle cannot begin until the internal RAS signal has been negated, parameter trap or TRG↑ to RAS↓ is imposed on the user and is set equal to the RAS precharge time plus any additional time necessary to complete the transfer before the row and sense clocks can be reset. Figure 18 shows the timing and a simplified logic implementation of the late load, including important internal signals. See the Real Time and Late Load timing diagram, Figure 38, for more datails.

Figure 18. Real time transfer, late load timing and control.

## **Early Register Load**