SHARP

# REFERENCE

| SPEC No. | MS   | <del>-</del> J | 0 9 8 | 0 | 7 |  |

|----------|------|----------------|-------|---|---|--|

| ISSUE:   | Sep. | 16.            | 1997  |   |   |  |

| To; |   |

|-----|---|

|     | _ |

| Engineering Dept. 2  Memory IC Engineering Center  Tenri Integrated Circuits Group                                                                                                                                                                                                                                                                                                        |                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Product Type                                                                                                                                                                                                                                                                                                                                                                              | ·<br>:                                                                                                         |

| Product Type                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                |

| LH52V1000CJS-70L  Model No.  ( LHSC105S )  *This specifications contains 11 pages including the cover and appendix. If you have any objections, please contact us before issuing purchasing of ustomers acceptance  DATE:  PRSENTED  BY:  T. KUZUMOTO Dept. General Manager  REVIEWED BY:  PREPARED BY:  Engineering Dept. 2 Memory IC Engineering Center Tenri Integrated Circuits Group | FICATIONS                                                                                                      |

| LH52V1000CJS-70L  Model No.  ( LHSC105S )  *This specifications contains 11 pages including the cover and appendix. If you have any objections, please contact us before issuing purchasing of ustomers acceptance  DATE:  PRSENTED  BY:  T. KUZUMOTO Dept. General Manager  REVIEWED BY:  PREPARED BY:  Engineering Dept. 2 Memory IC Engineering Center Tenri Integrated Circuits Group |                                                                                                                |

| Model No.  #This specifications contains 11 pages including the cover and appendix.  If you have any objections, please contact us before issuing purchasing of ustomers acceptance  PRSENTED  BY:  T. KUZUMOTO Dept. General Manager  REVIEWED BY:  PREPARED BY:  Engineering Dept. 2  Memory IC Engineering Center Tenri Integrated Circuits Group                                      | 1M SRAM                                                                                                        |

| *This specifications contains 11 pages including the cover and appendix.  If you have any objections, please contact us before issuing purchasing of USTOMERS ACCEPTANCE  DATE:  PRSENTED  BY:  T. KUZUMOTO Dept. General Manager  REVIEWED BY:  PREPARED BY:  Engineering Dept. 2  Memory IC Engineering Center Tenri Integrated Circuits Group                                          | 1000CJS-70LL                                                                                                   |

| *This specifications contains 11 pages including the cover and appendix.  If you have any objections, please contact us before issuing purchasing of the cover and appendix.  USTOMERS ACCEPTANCE  PRSENTED  BY:  T. KUZUMOTO Dept. General Manager  REVIEWED BY:  PREPARED BY:  T. Takes  Engineering Dept. 2  Memory IC Engineering Center Tenri Integrated Circuits Group              | LHSC105S )                                                                                                     |

| If you have any objections, please contact us before issuing purchasing of USTOMERS ACCEPTANCE  DATE:  PRSENTED  BY:  T. KUZUMOTO  Dept. General Manager   REVIEWED BY:  PREPARED BY:  Engineering Dept. 2  Memory IC Engineering Center  Tenri Integrated Circuits Group                                                                                                                 |                                                                                                                |

| BY:  T. KUZUMOTO Dept. General Manager  REVIEWED BY:  PREPARED BY:  Lake  Engineering Dept. 2  Memory IC Engineering Center Tenri Integrated Circuits Group                                                                                                                                                                                                                               |                                                                                                                |

| T. KUZUMOTO Dept. General Manager  REVIEWED BY: PREPARED BY:  T. Taken  Engineering Dept. 2  Memory IC Engineering Center Tenri Integrated Circuits Group                                                                                                                                                                                                                                 | PRSENTED                                                                                                       |

| Dept. General Manager  REVIEWED BY: PREPARED BY:  Thiblushi T. Taked  Engineering Dept. 2  Memory IC Engineering Center  Tenri Integrated Circuits Group                                                                                                                                                                                                                                  | BY: Kunggots.                                                                                                  |

| Engineering Dept. 2  Memory IC Engineering Center  Tenri Integrated Circuits Group                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| Engineering Dept. 2  Memory IC Engineering Center  Tenri Integrated Circuits Group                                                                                                                                                                                                                                                                                                        |                                                                                                                |

| Memory IC Engineering Center Tenri Integrated Circuits Group                                                                                                                                                                                                                                                                                                                              | Dept. General Manager                                                                                          |

| Memory IC Engineering Center Tenri Integrated Circuits Group                                                                                                                                                                                                                                                                                                                              | Dept. General Manager  REVIEWED BY: PREPARED BY:                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                           | Dept. General Manager  REVIEWED BY: PREPARED BY:  T. Takela                                                    |

| SHARP CORPORATION                                                                                                                                                                                                                                                                                                                                                                         | Dept. General Manager  REVIEWED BY: PREPARED BY:  T. Takeda  Engineering Dept. 2  Memory IC Engineering Center |

|                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                |

- Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.

- When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.

- (1) The products covered herein are designed and manufactured for the following application areas. When using the products covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph (3).

- · Office electronics

- · Instrumentation and measuring equipment

- · Machine tools

- · Audiovisual equipment

- · Home appliances

- · Communication equipment other than for trunk lines

- (2) Those contemplating using the products covered herein for the following equipment which demands high reliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-sale operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.

- · Control and safety devices for airplanes, trains, automobiles, and other transportation equipment

- · Mainframe computers

- · Traffic control systems

- · Gas leak detectors and automatic cutoff devices

- · Rescue and security equipment

- · Other safety devices and safety equipment, etc.

- (3) Do not use the products covered herein for the following equipment which demands extremely high performance in terms of functionality, reliability, or accuracy.

- · Aerospace equipment

- · Communications equipment for trunk lines

- · Control equipment for the nuclear power industry

- · Medical equipment related to life support, etc.

- (4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a sales representative of the company.

- Please direct all queries regarding the products covered herein to a sales representative of the company.

**SHARP**

#### Contents

| 1.  | Description · · · · · · · · · · · · · · · · · · · | 2   |

|-----|---------------------------------------------------|-----|

| 2.  | Pin Configuration                                 | 2   |

| 3.  | Truth Table                                       | 3   |

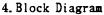

| 4.  | Block Diagram                                     | . 3 |

| 5.  | Absolute Maximum Ratings                          | 4   |

| 6.  | Recommended DC Operating Conditions               | 4   |

| 7.  | DC Electrical Characteristics                     | 4   |

| 8.  | AC Electrical Characteristics                     | 5   |

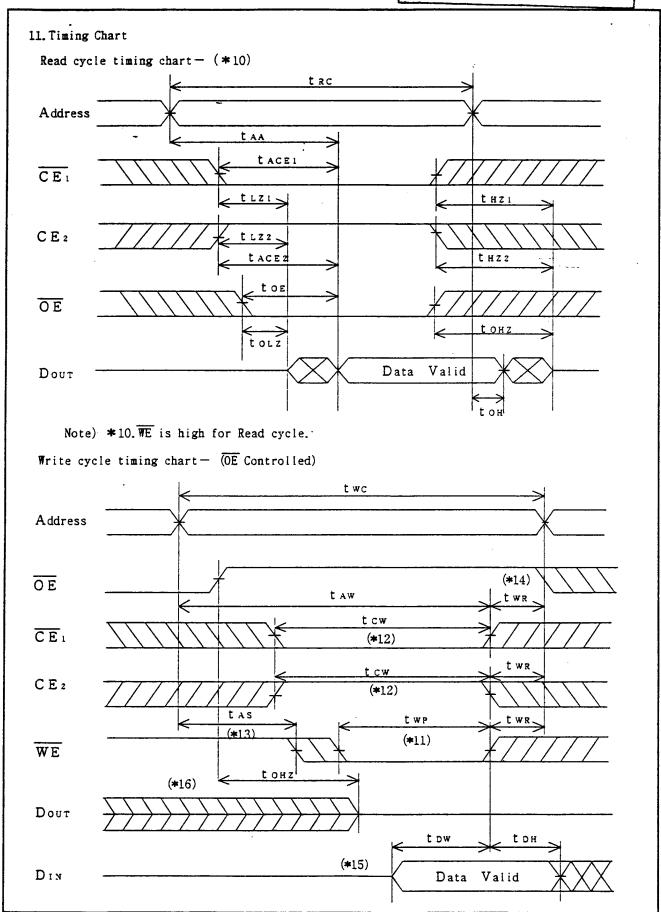

| 9.  | Data Retention Characteristics                    | 6   |

| 10. | Pin Capacitance                                   | 6   |

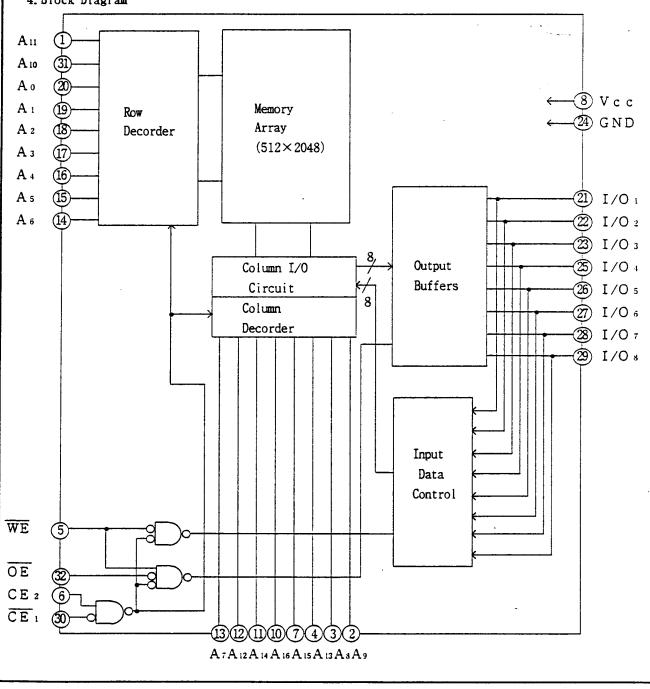

| 11. | Timing Chart                                      | 7   |

```

1. Description

The LH52V1000CJS-70LL is a static RAM organized as 131, 072\times8 bit

with provides low-power standby mode.

It is fabricated using silicon-gate CMOS process technology.

Features

70 ns (Max.)

OAccess Time

40 mA (Max.)

Operating current

5 mA (Max. trc. twc=1 \mus)

OStandby current

50 \muA (Max. Ta=85°C)

OData retention current

1.0 \mu A (Max. Vccbr = 3 V, Ta = 25°C)

OSingle power supply

2.7 V to 3.6 V

Operating temperature

-25°C to +85°C

OFully static operation

OThree-state output

ONot designed or rated as radiation hardened

TSOP ( TSOP32-P-0813) plastic package

○ 3 2 pin

ON-type bulk silicon

2. Pin Configuration

OE

10

32

A 11

31

2

A 10

A 9

30

CEı

3

A 8

29

I/O 8

4

А 13

WE

5

28

I/O 7

27

I/O 6

6

CE 2 =

26

7

I/O 5

A 15

25

I/O+

Vcc □

8

9

24

GND

NC

23

I/O 3

10

A 16

22

I/O 2

11

A 14

21

I/O 1

12

A 12

20

Αo

13

A 7

19

A_1

14

A 6

15

18

A 2

A 5

(Top View)

17

Аз

16

A٠

Function

Pin Name

Address inputs

Ao to Ais

CEL

Chip enable 1

Chip enable 2

CE2

WE

Write enable

Output enable

ΟE

```

I/Oito I/Os

Vcc

GND NC

Data

Ground

Power supply

Non connection

inputs/outputs

#### 3. Truth Table

| CE: | CE2 | WE | ŌĒ | Mode           | I /O 1 to I /O s | Supply current |

|-----|-----|----|----|----------------|------------------|----------------|

| H   | *   | *  | *  | Standby        | High impedance   | Standby (Ism)  |

| *   | L   | *  | *  | Standby        | High impedance   | Standby (Ism)  |

| L   | H - | L  | *  | Write :        | Data input       | Active (Ice)   |

| L   | Н   | Н  | L  | Read           | Data output      | Active (Ice)   |

| L   | Н   | H  | Н  | Output disable | High impedance   | Active (Icc)   |

(\*=Don't Care, L=Low, H=High)

#### 5. Absolute Maximum Ratings

| Parameter             | Symbol | Ratings            | Unit |

|-----------------------|--------|--------------------|------|

| Supply voltage (*1)   | Vcc    | -0.3 to $+4.6$     | V    |

| Input voltage (*1)    | или    | -0.3(*2)to Vcc+0.3 | V    |

| Operating temperature | Topr   | -25 to +85         | τ    |

| Storage temperature   | Tstg   | -65 to +150        | 2    |

Note) \*1. The maximum applicable voltage on any pin with respect to GND.

\*2. Undershoot of -3.0V is allowed width of pluse bellow 50ns.

#### 6. Recommended DC Operating Conditions

(Ta = -25% to +85%)

| Parameter      | Symbol | Min.      | Typ.        | Max.    | Unit |

|----------------|--------|-----------|-------------|---------|------|

| Supply voltage | Vcc    | 2.7       | 3.0         | 3.6     | V    |

| Input voltage  | VIH    | 2.2       |             | Vcc+0.3 | V    |

|                | VIL    | -0.3 (*3) | <del></del> | 0.8     | V    |

Note) \*3. Undershoot of -3.0V is allowed width of pluse below 50ns.

#### 7. DC Electrical Characteristics

(Ta = -25 °C to + 85 °C , Vcc = 2.7 V to 3.6 V)

| Parameter     | Symbol | Conditions                              |                  | Min. | Typ. (*4) | Max. | Unit |

|---------------|--------|-----------------------------------------|------------------|------|-----------|------|------|

| Input leakage | Itt    | Vix=OV to Vcc                           |                  |      |           |      |      |

| current       |        |                                         |                  | -1.0 |           | 1.0  | μА   |

| Output        | Ito    | CE1=ViH or CE2=ViL or                   |                  |      | -         |      |      |

| leakage       |        | OE=VIH OF WE=VIL                        | OE=VIH OF WE=VIL |      |           | 1.0  | μA   |

| current       |        | V <sub>1/0</sub> =0V to V <sub>CC</sub> |                  |      |           |      |      |

| Operating     | I cc   | CE1=VIL, VIN=VIL or VIH                 | tcycLE           |      |           |      |      |

| supply        |        | CE2=V1H, I1/0=OmA                       | =Min             |      |           | 4 0  | m A  |

| current       | Icci   | CE1=0. 2V, Vin=0. 2V or Vcc - 0. 2V     | tcycle           | :    |           |      |      |

|               |        | CE2=Vcc - 0. 2V. I1/0=0mA               | =1.0 μ S         |      |           | 5    | mΑ   |

| Standby       | Isa    | CE1.CE2≥Vcc -0.2V or                    |                  |      |           |      |      |

| current       |        | CE2≦0. 2V                               |                  |      | 0.7       | 5 0  | μA   |

|               | Issi   | CE1=VIH OF CE2=VIL                      |                  |      |           | 3    | mΑ   |

| Output        | Vol    | IoL= 2.0 mA                             |                  |      |           | 0.4  | V    |

| voltage       | Vон    | Гон= — 1. О пдА                         |                  | 2.4  |           |      | V    |

Note) ★4. Typical values at Vcc=3.0V, Ta=25°C.

#### 8. AC Electrical Characteristics

# AC Test Conditions

| Input pulse level                  | 0.6 V to 2.2           | V    |

|------------------------------------|------------------------|------|

| Input rise and fall time           | 5                      | пs   |

| Input and Output timing Ref. level | 1.5                    | V    |

| Output load                        | 1 T T L + C t(3 0 p F) | (*5) |

Note) \*5. Including scope and jig capacitance.

# Read cycle

(Ta = -25 °C to + 85 °C , Vcc = 2.7 V to 3.6 V)

| Parameter                            | Symbol  | Min. | Max. | Unit |            |

|--------------------------------------|---------|------|------|------|------------|

| Read cycle time                      | trc     | 7 0  |      | ns   |            |

| Address access time                  | t aa    |      | 7 0  | ns   | 7          |

| CE1 access time                      | t ACE 1 |      | 7 0  | ns   | 7          |

| CE2 access time                      | t ACE 2 |      | 7 0  | ns   | 7          |

| Output enable to output valid        | toe     |      | 3 5  | ns   |            |

| Output hold from address change      | tон     | 1 0  |      | ns   | 7          |

| CE: Low to output active             | tızı    | 1 0  |      | ns   | <b>*</b> 6 |

| CE2 High to output active            | t L Z 2 | 1 0  |      | ns   | * 6        |

| OE Low to output active              | . touz  | 5    |      | ns   | * 6        |

| CE: High to output in High impedance | t H Z 1 | 0    | 3 0  | ns   | * 6        |

| CE2 Low to output in High impedance  | t HZ2   | 0    | 3 0  | ns   | <b>*</b> 6 |

| OE High to output in High impedance  | tонz    | 0    | 3 0  | ns   | * 6        |

# Write cycle

$(Ta = -2.5 \, \text{°C} \text{ to } + 8.5 \, \text{°C}, Vcc = 2.7 \, \text{°V} \text{ to } 3.6 \, \text{V})$

| Parameter                           | Symbol | Min. | Max.     | Unit |     |

|-------------------------------------|--------|------|----------|------|-----|

| Write cycle time                    | t wc   | 7 0  |          | ns   |     |

| Chip enable to end of write         | tcw    | 6 0  |          | ns   |     |

| Address valid to end of write       | taw    | 6 0  |          | ns   | 7   |

| Address setup time                  | tas    | 0    |          | ns   | 7   |

| Write pluse width                   | twp    | 5 0  |          | ns   |     |

| Write recovery time                 | twr    | 0    |          | ns   | _   |

| Input data setup time               | tow    | 3 0  | *        | ns   | 7   |

| Input data hold time                | tон    | 0    | <u> </u> | ns   |     |

| WE High to output active            | tow    | 5    | ,        | ns   | * 6 |

| WE Low to output in High impedance  | twz    | 0    | 3 0      | ns   | * ( |

| OE High to output in High impedance | tonz   | 0    | 3 0      | ns   | * ( |

Note) \*6. Active output to High impedance and High impedance to output active tests specified for a ±200mV transition from steady state levels into the test load.

#### 9. Data Retention Characteristics

(Ta = -25°C to +85°C)

| Paramenter     | Symbol. | Conditions       |             | Min. | Typ. (*8) | Max. | Unit |

|----------------|---------|------------------|-------------|------|-----------|------|------|

| Data Retention | Vccdr   | C E 2 ≤ 0.2 V or |             |      |           |      |      |

| supply voltage |         | CE1≥ Vccor-0.2   | V (*7)      | 2.0  |           | 3.6  | V    |

| Data Retention | Iccor   | Vccor=3 V        | T a = 2 5 ℃ |      | 0.7       | 1.0  | μΑ   |

| supply current |         | C E 2 ≤ 0.2 or   |             |      |           |      |      |

|                |         | CE1≥ VccdR-0.2   | V (*7)      |      |           | 4 0  | μΑ   |

| Chip enable    | tcor    |                  |             |      |           |      |      |

| setup time     |         |                  |             | 0    |           |      | m s  |

| Chip enable    | tr      |                  |             | -    |           |      |      |

| hold time      |         |                  |             | 5    |           |      | m s  |

Note)  $*7. CE_2 \ge V_{CCDR} - 0.2 V$  or  $CE_2 \le 0.2 V$

**★8.** Typical values at Ta=25°C

# 10. Pin Capacitance

$(T_a=25 \, \text{C}, f=1 \, \text{MHz})$

| Parameter         | Symbol | Conditions      | Min. | Typ. | Max. | Unit |   |

|-------------------|--------|-----------------|------|------|------|------|---|

| Input capacitance | CIN    | V 0 = K 1 V     |      |      | 1 0  | p F  | * |

| I/O capacitance   | C1/0   | $V_{I/O} = 0 V$ |      |      | 1 0  | pF   | * |

Note) \*9. This parameter is sampled and not production tested.

Note) \* 11. A write occurs during the overlap of a low CE1, a high CE2 and a low WE. A write begins at the latest transition among CE: going low, CE: going high and WE going low.

> A write ends at the earliest transition among CE1 going high, CE2 going low and WE going high. two is measured from the beginning of write to the end of write.

- \* 12. to is measured from the later of CE1 going low or CE2 going high to the end of write.

- \* 13. tas is measured from the address valid to the beginning of write.

- \* 14. two is measured from the end of write to the address change, two applies in case a write ends at CE1 or WE going high, two applies in case a write ends at CE2 going low.

- \* 15. During this period, I/O pins are in the output state, therefore the input signals of opposite phase to the outputs must not be applied.

- \* 16. If  $\overline{\text{CE}_1}$  goes low simultaneously with  $\overline{\text{WE}}$  going low or after  $\overline{\text{WE}}$  going low, the outputs remain in high impedance state.

- \* 17. If  $\overline{\text{CE}_1}$  goes high simultaneously with  $\overline{\text{WE}}$  going high or before  $\overline{\text{WE}}$  going high, the outputs remain in high impedance state.

Data Retention timing chart - (CE: Controlled) Data Retention mode Vcc tcor 2.2 V -Vccdr " CE1≥VccDR-0.2V CEı

Data Retention timing chart— (CE2 Controlled)

Note) \*18. To control the data retention mode at CE1, fix the input level of CE2 between Vccm and Vccm - 0.2V or OV and 0.2V during the data retention mode.