# PC87560UBD — PCI System I/O 1.0 General Description

The PC87560 is a highly integrated IC which incorporates PCI Interface, Bus Mastering Fast IDE Controller, Universal Serial Bus (USB) Host Controller, commonly-used I/O peripherals, and power management functions. When used in conjunction with the PC87550, the PC87560 provides all the peripheral and power management functions for efficient design of notebook computers and docking stations.

The PCI Interface provides up to 33 MHz PCI Bus frequency. Address re-mapping via PCI configuration registers is provided to support Plug and Play-capable systems.

The IDE Controller provides two channels with programmable access timing per channel/drive and a maximum sustained data transfer rate of 16 MBytes/sec. A multi-tasking DMA engine assures channel concurrency.

Peripheral functions include one Floppy Disk Controller (FDC), one parallel port (IEEE 1284), and two standard serial ports (one with Universal Infrared (UIR) capability). The FDC supports tri-mode floppy drives, Perpendicular Recording, and enhanced Tape Drive Register (TDR) operation. An external floppy disk may be multiplexed on the parallel port. The parallel port supports all standard operational modes. Both standard serial ports (16550 UARTs) support MIDI baud rates. The second serial port may be configured as a UIR serial port in IrDA1.0 SIR, IrDA1.1 MIR and FIR, Sharp-IR, or Remote TV compatible modes. Each peripheral function can be individually disabled.

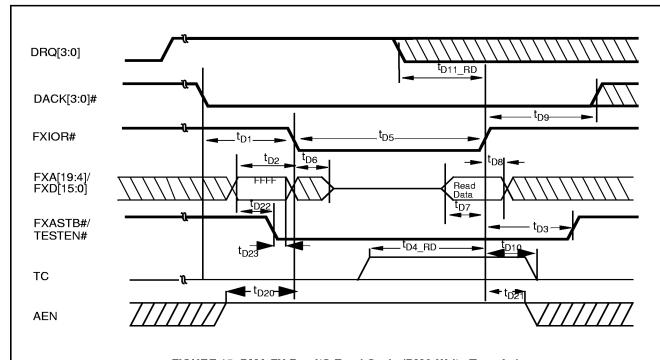

System Interface functions include two 8237 DMA Controllers, two 8259 Interrupt Controllers, an 8254-compatible System Timer, CPU reset control, and numeric coprocessor error support. The DMA Controllers support seven channels (Master/Slave modes), DMA channel routing for Plug and Play compatibility, and ISA-compatible timing. The Interrupt Controllers support PCI native interrupts and interrupt routing. Edge— and level—triggering are individually programmable for each interrupt line. A PCIway Serial Interrupt interface (Master or Slave mode) is supported for docking.

Interfaces to ROM/FLASH ROM, a Real Time Clock (RTC), and Keyboard Controller (KBC) are provided. The PC87560 enables I/O subsystem expansion via a 16-bit Fast Expansion Bus (FX Bus) and provides Fast GateA20 and I/O peripheral design flexibility.

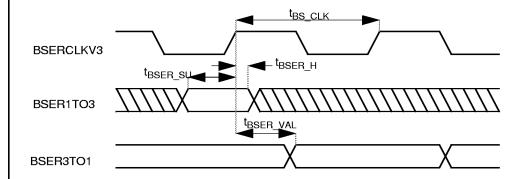

Advanced Configuration and Power Interface (ACPI) 1.0 compliance offers complete power management when combined with peripheral port access monitors, back powering protection, a system event register, and a full set of shadow registers. An on-chip Burst Serial Interface (BSER) communicates power management activity when used in conjuction with the PC87550 Host Bridge.

The USB OHCI Host Controller is a PCI Master device with two root hub ports. An optimized List—Queue Manager enables transfer scheduling and management. Dynamic rescheduling of data transfers and real—time device attaching/detaching are supported. Legacy keyboard and mouse support is also included.

$\mathsf{TRI}\text{-}\mathsf{STATE}^{\textcircled{\tiny{\textbf{0}}}} \text{ is a registered trademark of National Semiconductor Corporation}.$

#### 2.0 Features

#### · PCI Bus Interface

- PCI 2.1 and PCI Mobile Design Guide 1.0 compliant

- 32-bit PCI Bus with up to 33 MHz PCI Bus frequency

#### Fast Bus Master IDE Controller

- Access timing programmable per channel/drive

- 16 MBytes/sec maximum data transfer rate

- -2 IDE channels (primary and secondary)

- SFF 8038i and SFF8022i compliant

#### I/O Peripherals

- Floppy Disk Controller: Software compatible with the PC8477, the NEC μPD765A and the N82077; Perpendicular Recording drive support; Support for enhanced Tape Drive Register (TDR); Tri-mode floppy and FM Mode support

- IEEE 1284 compatible Parallel Port: Compatible, Nibble, Byte, ECP, EPP 1.7, and EPP1.9 mode support; Floppy Interface multiplexed on this port

- Two Standard Serial Ports (16550 UARTs): MIDI baud rate supported on both ports; Second port configurable as serial port or UIR port

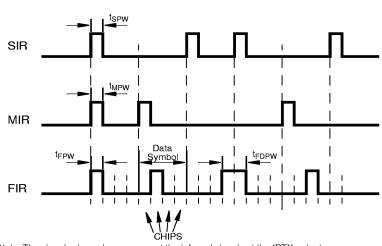

- Universal Infrared (UIR) Port: IrDA 1.0 SIR, IrDA 1.1 MIR and FIR, Sharp-IR and Consumer Remote compatible; Programmable pulse width of 1.6 μs or 3/16 bit time

#### System Interface

- Two DMA Controllers: Seven 8237 compatible channels; distributed DMA Master and Slave modes; 2 Double-Word Buffers for PCI Bus transfers; Support for preemption and rearbitration for each PCI Bus transfer cycle

- FX Bus (Non-Bus Master ISA Bus): Programmable timing for ISA compatible peripherals; 2 Programmable I/O range Chip Selects; 1 Programmable Memory Range; 1 programmable, fragmented I/O window with Chip select for Sound Blaster compatibility; 4 Channel DMA and 3 channel Interrupt support

- Interfaces to External Devices: Up to 256 KBytes of ROM/ FLASH ROM (with special 1 MB ROM space for PowerPC platforms); 8051 and PC87570 style keyboard controllers with Fast GateA20, Fast reset and remappable Chip Select; DS1287 style Real-Time Clock; X86 CPU interface support

- Two 8259 Interrupt Controllers: Native PCI internal request support; edge—or level—trigger individually programmable on a per channel basis

- 8254 Compatible System Timer: with 3 timer channels

- Numeric Coprocessor Error Support (Port F0)

#### Power Management

- Advanced Configuration and Power Interface (ACPI) 1.0 specification compliant

- Slave Mode: Power management control in the NorthBridge

- Peripheral port access monitors (FDC, Serial 1&2, IDE 1&2, USB, and Parallel ports)

- Shadow registers and one System event register

- Back powering protection from printer, FDC and IDE interfaces

#### · Universal Serial Bus (USB) Host Controller

- USB 1.0 and OpenHCI 1.0a compliant

- Two Root Hub Ports with integrated transceivers

- Full-speed (12 Mbps) and Low-speed device transfer protocols

- Legacy keyboard and mouse support

#### General

- Mixed 3.3/5 Volt operation

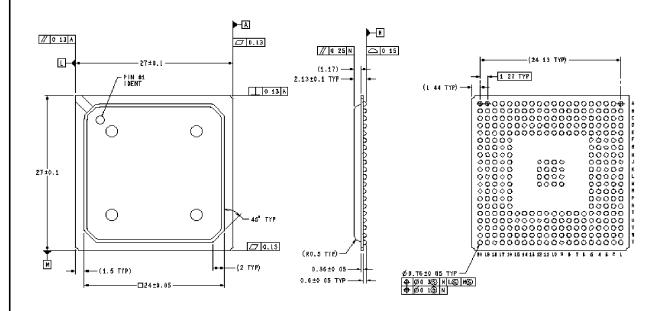

- 316-pin BGA package

Copyright <sup>©</sup> 1997 National Semiconductor Corporation. All rights reserved.

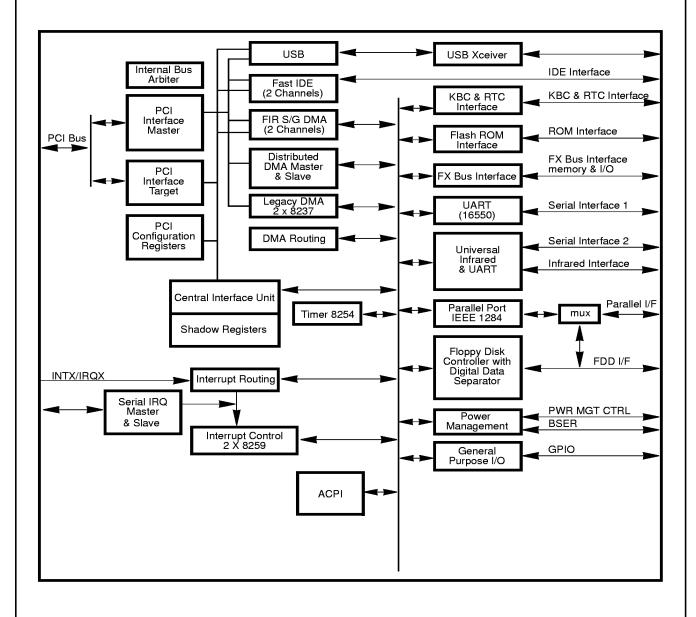

# 3.0 Block Diagram

# **Table of Contents** 1.0 General Description ....... 1 4.0 Pin Descriptions ...... 4

# 4.0 Pin Descriptions

This section describes the signals available in the PC87560 device and associates each signal with a pin in the 316-pin BGA package. A package drawing is also provided.

The nomenclature for the values used in the "Voltage" column in the following tables is shown in Table I.

**TABLE I. Nomenclature for Voltage Values**

| Voltage Value | Impact on the Associated Signal/Pin(s)                                                                                                                                                                                |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3/5V          | When the chip is powered by 3V (VDD=3.3V), the I/O is 3.3V. When the chip is powered by 5V (VDD=5V), the I/O is 5V.                                                                                                   |

| 3/5VT         | When the chip is powered by 3V (VCC=3.3V), the I/O is 3.3V with 5V tolerant inputs. When the chip is powered by 5V (VCC=5V), the I/O is 5V.                                                                           |

| 3/5V_PM       | This signal is supported by the ACPI logic and powered by the VDD_PM input.  When the ACPI logic is powered by 3V (VDD_PM=3.3V), the I/O is 3.3V.  When the ACPI logic is powered by 5V (VDD_PM=5V), the I/O is 5V.   |

| Open Drain    | This output signal or set of output signals are always Open Drain signals capable of directly driving associated CPU signals. These outputs must have an external pull-up resistor to the appropriate supply voltage. |

#### **4.1 PCI INTERFACE**

**TABLE II. PCI Interface**

| Symbol(s)     | Pin(s)                                                                                                                                                                             | Туре | Voltage | Function                                                                                                                                                                                                                          |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bus Interface |                                                                                                                                                                                    |      |         |                                                                                                                                                                                                                                   |

| AD[31:0]      | C14, D14,<br>A15, B15,<br>C15, D15,<br>A16, B16,<br>C16, D16,<br>A17, B17,<br>C17, A18,<br>B18, D17,<br>A19, C18,<br>C19, C20,<br>D18, D19,<br>D20, E17,<br>E18, E19,<br>E20, F17, | I/O  | 3/5V    | Address and Data. The Address and Data signals are multiplexed. The direction of these pins is defined as follows:  Phase Target Bus Master Address Phase Input Output Read Data Phase Output Input Write Data Phase Input Output |

| C/BE[3:0]     | F18, F19,<br>F20, G17<br>G18, G19,                                                                                                                                                 | I/O  | 3/5V    | Command or Byte Enable.                                                                                                                                                                                                           |

|               | G20, H17                                                                                                                                                                           |      |         | Signals are multiplexed bus command or byte enables.                                                                                                                                                                              |

| DEVSEL#       | D11                                                                                                                                                                                | I/O  | 3/5V    | Device Select.  When driven active low, this signal indicates the driving device has decoded its address as the target of the current access.                                                                                     |

| FRAME#        | B11                                                                                                                                                                                | I/O  | 3/5V    | Frame. Cycle Frame is driven by the initiator to indicate the beginning and duration of an access.                                                                                                                                |

| IDSEL         | B14                                                                                                                                                                                | I    | 3/5V    | Initialization Device Select. Used as a chip select during configuration read and write transactions.                                                                                                                             |

| IRDY#         | B12                                                                                                                                                                                | I/O  | 3/5V    | Initiator Ready. Indicates that the initiator is ready to complete the current data phase of the transaction.                                                                                                                     |

|                               |                      | T    | ABLE II. P | CI Interface (Continued)                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|----------------------|------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol(s)                     | Pin(s)               | Туре | Voltage    | Function                                                                                                                                                                                                                                                                                                                                       |

| LOCK#                         | A11                  | ı    | 3/5V       | Lock. Indicates an atomic operation that may require multiple transactions to complete.                                                                                                                                                                                                                                                        |

| PAR                           | D12                  | I/O  | 3/5V       | Parity. Parity is even across AD[31:0] and C/BE[3:0]. PAR directionality follows the AD[31:0] directionality.                                                                                                                                                                                                                                  |

| PCICLK                        | A14                  | I    | 3/5V       | PCI Clock. The PCI clock input can be any frequency from 0-33MHz.                                                                                                                                                                                                                                                                              |

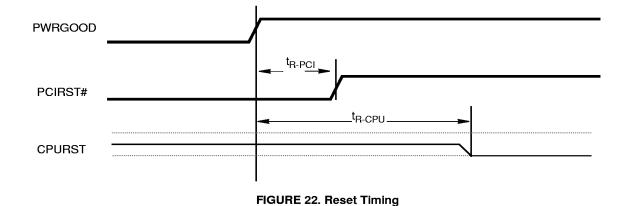

| PCIRST#                       | D13                  | 0    | 3/5V       | PCI Reset. PCIRST# is used to reset PCI Bus devices and is asserted following RESET_IN#. PCIRST# will be de-asserted a minimum of 1ms after RESET_IN# is de-asserted.                                                                                                                                                                          |

| PERR#                         | A13                  | I/O  | 3/5V       | Parity Error. Used for reporting data parity errors during all PCI transactions except a Special Cycle. PERR# is an output when AD[31:0] and PAR are inputs and is an input when AD[31:0] and PAR are outputs.                                                                                                                                 |

| SERR#                         | A12                  | I/O  | 3/5V       | System Error. Used for reporting address parity errors, data parity errors on the Special Cycle command, or any other system error where the result will be catastrophic. When reporting address parity errors, SERR# is an output. As an input to the PC87560, any PCI device can pulse the SERR# to indicate a catastrophic error condition. |

| STOP#                         | C11                  | I/O  | 3/5V       | Stop. Indicates that the current target is requesting the initiator to stop the current transaction.                                                                                                                                                                                                                                           |

| TRDY#                         | C12                  | I/O  | 3/5V       | Target Ready. Indicates that the target of the current data phase of the transaction is ready to be completed.                                                                                                                                                                                                                                 |

| Bus Arbiter                   |                      |      |            |                                                                                                                                                                                                                                                                                                                                                |

| SIOGNT#                       | C13                  | ı    | 3/5V       | System I/O Grant. This signal is asserted from the host controller allowing the PC87560 to become the PCI Bus Master.                                                                                                                                                                                                                          |

| SIOREQ#                       | B13                  | 0    | 3/5V       | System I/O Request. This signal is asserted to request the host controller to allow the PC87560 to become PCI Bus Master.                                                                                                                                                                                                                      |

| Interrupts                    | •                    | •    |            |                                                                                                                                                                                                                                                                                                                                                |

| INTA#, INTB#,<br>INTC#, INTD# | A9, D10,<br>C10, B10 | ı    | 3/5V       | Interrupt Request A, B, C, and D. These four active–low, shareable interrupt requests may be used by PCI devices to make an interrupt request.                                                                                                                                                                                                 |

# 4.2 FAST BUS MASTER IDE CONTROLLER INTERFACE

# **TABLE III. Fast Bus Master IDE Controller Interface**

| Symbol(s)             | Pin(s)      | Туре | Voltage | Function                                                                                                                                                                                                   |

|-----------------------|-------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CH1_CS1#,<br>CH1_CS3# | U9,<br>V9   | 0    | 3/5V    | Channel 1 Chip Select 1 and 3.  CH1_CS1# is the chip select signal to select the Channel 1 Command Block Registers. CH1_CS3# is the chip select signal to select the Control Block Registers of Channel 1. |

| CH2_CS1#,<br>CH2_CS3# | V10,<br>W10 | 0    | 3/5V    | Channel 2 Chip Select 1 and 3.  CH2_CS1# is the chip select signal to select the Channel 2 Command Block Registers. CH2_CS3# is the chip select signal to select the Control Block Registers of Channel 2. |

| TABLE III. Fast Bus Master IDE Controller Interface (Continued) |                                                                                                     |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol(s)                                                       | Pin(s)                                                                                              | Туре | Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

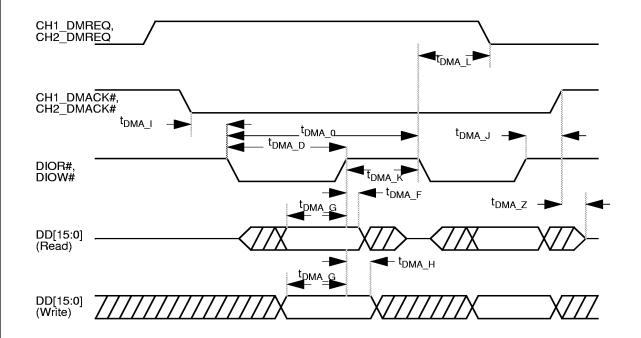

| CH1_DMREQ                                                       | Y9                                                                                                  | ı    | 3/5VT   | Channel 1 DMA Request. This signal is used when the IDE device is configured to use the pseudo DMA handshake mode or when using the internal IDE DMA controller. When asserted, this signals the PC87560 that the selected drive on Channel 1 is ready to transfer data.                                                                                                                                               |  |  |  |  |

| CH2_DMREQ                                                       | Y11                                                                                                 | I    | 3/5VT   | Channel 2 DMA Request. This signal is used when the IDE device is configured to use the pseudo DMA handshake mode or when using the internal IDE DMA controller. When asserted, this signals the PC87560 that the selected drive on Channel 2 is ready to transfer data.                                                                                                                                               |  |  |  |  |

| CH1_DMACK#                                                      | U10                                                                                                 | 0    | 3/5V    | Channel 1 DMA Acknowledge. This signal is used when the PC87560's IDE Controller is configured to use the pseudo DMA handshake mode or when using the internal IDE DMA controller. This signal indicates to the selected drive on Channel 1 that data has either been accepted, or that data is available.                                                                                                             |  |  |  |  |

| CH2_DMACK#                                                      | W11                                                                                                 | 0    | 3/5V    | Channel 2 DMA Acknowledge. This signal is used when the PC87560's IDE Controller is configured to use the pseudo DMA handshake mode or when using the internal IDE DMA controller. This signal indicates to the selected drive on Channel 2 that data has either been accepted, or that data is available.                                                                                                             |  |  |  |  |

| CH1_INT,<br>CH2_INT                                             | W9,<br>Y10                                                                                          | I    | 3/5VT   | Channel 1 and Channel 2 Drive Interrupts.  These signals are used to interrupt the host system. CH1_INT is asserted when the IDE drive(s) on Channel 1 have a pending interrupt. CH2_INT is asserted when the IDE drive(s) on Channel 2 have a pending interrupt.                                                                                                                                                      |  |  |  |  |

| DA[2:0]                                                         | W16, V16,<br>U16                                                                                    | 0    | 3/5V    | Drive Address.  When accessing the IDE drive, these pins are the address bits 2-0 used to access a register or data port in the drive.                                                                                                                                                                                                                                                                                 |  |  |  |  |

| DD[15:0]                                                        | W12, V12,<br>U12, Y13,<br>W13, V13,<br>U13, Y14,<br>W14, V14,<br>U14, Y15,<br>W15, V15,<br>U15, Y16 | I/O  | 3/5VT   | Drive Data Bus. When accessing the IDE drive, this is an 8- or 16-bit bi-direction data bus between the PC87560 chip and the drive. The lower 8 bits are also used for non-data 8-bit transfers (such as registers and ECC bytes).                                                                                                                                                                                     |  |  |  |  |

| DIORDY                                                          | V11                                                                                                 | I    | 3/5VT   | Drive I/O Channel Ready. When accessing the IDE drive, this signal is negated (low) to extend a Programmable I/O (PIO) disk transfer cycle of any register access (read or write) when the drive is not ready to respond to a data transfer request. When an IDE drive no longer desires to extend the cycle, DIORDY will be placed in TRI-STATE® by the IDE drive(s) and pulled high by an external pull-up resistor. |  |  |  |  |

| DIOR#                                                           | U11                                                                                                 | 0    | 3/5V    | Drive I/O Read. This is the read strobe signal for both channels. When active low, DIOR# enables data from a register or the data port of the drive onto the IDE Drive data bus.                                                                                                                                                                                                                                       |  |  |  |  |

|           | TABLE III. Fast Bus Master IDE Controller Interface (Continued) |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|-----------|-----------------------------------------------------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol(s) | Pin(s)                                                          | Туре | Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| DIOW#     | Y12                                                             | 0    | 3/5V    | Drive I/O Write. This is the write strobe signal for both channels. The rising edge of DIOW# clocks data from the IDE Drive data bus into the register or the data port of the IDE drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| DRST#     | Y8                                                              | O    | 3/5V    | Drive Reset. This signal from the IDE Controller is asserted active (low) during power up or under software control. DRST# will remain active low as long as the PCI Reset signal (PCIRST#) is asserted low or as long as the drive reset bit in the IDE Controller is set to one.  NOTE: This signal will be driven active low for a maximum of 2 msec. following the rising edge of RESET_IN#. It is the system designer's responsibility to guarantee that no accesses are made if the IDE drive devices use this signal as reset and the PC87560's PCIRST# is not used as the PCI Bus reset. In such a case, the PC87560 cannot guarantee that a PCI Bus Cycle will not occur while DRST# remains active (low). If the PC87560's PCIRST# (pin D13) is used as the PCI Bus reset, no PCI Bus access will occur until DRST# is de-asserted (high). |  |  |  |  |

#### 4.3 I/O PERIPHERALS

The following tables identify the signals and pins associated with particular peripheral functions. These functions include the Floppy Disk Controller, Parallel Port/Floppy Interface, Serial Interface Ports 1 and 2, and the Universal Infrared Interface.

# 4.3.1 Floppy Disk Controller (FDC)

**TABLE IV. FDC Controller Interface**

| Symbol(s)  | Pin(s) | Туре | Voltage | Function                                                                                                                                                                        |

|------------|--------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DENSL[1:0] | D2, D3 | 0    | 3/5V    | Density Select 0 and 1. Indicates high or low density FDC data rate is selected.                                                                                                |

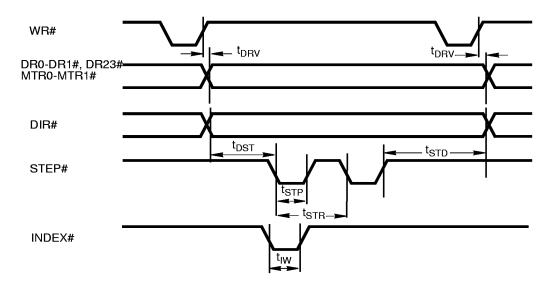

| DIR#       | E1     | 0    | 3/5V    | <b>Direction.</b> This signal determines the direction of movement of the selected floppy disk drive head during a seek operation.                                              |

| DSKCHG#    | N3     | ı    | 3/5VT   | Disk Change. This input signal indicates if floppy disk drive door is open.                                                                                                     |

| DS[1:0]#   | E3, E2 | 0    | 3/5V    | Drive Select 0 and 1.  These active—low signals are used to decode Drive Select outputs which control four floppy disk drives.                                                  |

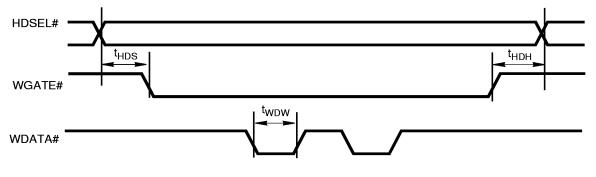

| HDSEL#     | F1     | 0    | 3/5V    | Head Select. This signal detainees which side of the FDD is accessed. Active low selects side 1, inactive high selects side 0.                                                  |

| INDEX#     | G2     | ı    | 3/5VT   | Index. This input signal indicates the beginning of an FDD track.                                                                                                               |

| MSEN[1:0]  | G3, G4 | I    | 3/5VT   | Media Sense 0 and 1. These input pins act as media sensors. Each pin has a $40$ kΩ internal pull-up resistor.                                                                   |

| MTR[1:0]#  | D1, E4 | 0    | 3/5V    | Motor Select 0 and 1. These active low signals are the motor enable lines for floppy disk drives 0 and 1. They are encoded with information to control four Floppy Disk Drives. |

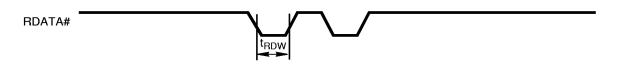

| RDATA#     | N2     | I    | 3/5VT   | Read Data. This input signal is the raw read from the floppy disk drive.                                                                                                        |

|           | TABLE IV. FDC Controller Interface (Continued) |      |         |                                                                                                                                                                           |  |  |  |

|-----------|------------------------------------------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol(s) | Pin(s)                                         | Туре | Voltage | Function                                                                                                                                                                  |  |  |  |

| STEP#     | F4                                             | 0    | 3/5V    | Step. This signal issues pulses to the floppy disk drive at a programmable rate to move the head during a seek operation.                                                 |  |  |  |

| TRK0#     | M4                                             | I    | 3/5VT   | Track 0.  This signal indicates to the controller that the head of the selected floppy disk drive is at track zero.                                                       |  |  |  |

| WDATA#    | F3                                             | 0    | 3/5V    | Write Data. This is the write precompensated data that is written to selected FDD. Precompensation is selectable.                                                         |  |  |  |

| WGATE#    | F2                                             | 0    | 3/5V    | Write Gate. This output signal enables the write circuitry of the selected floppy disk drive. WGATE# is designed to prevent writing to the disk when the power is cycled. |  |  |  |

| WP#       | N1                                             | I    | 3/5VT   | Write Protect. This input indicates that the disk in the selected floppy disk drive is write protected.                                                                   |  |  |  |

# 4.3.2 Parallel Port/Floppy Interface

TABLE V. Parallel Port/Floppy Interface

| Symbol(s)                  | Pin(s) | Туре | Voltage | Function                                                                                                                                                                                  |

|----------------------------|--------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK#/DS1#                  | Т3     | I/O  | 3/5VT   | Acknowledge or Drive Select 1. Signal indicates Acknowledge in Parallel Port mode or Drive Select 1 in Floppy mode.                                                                       |

| AFD#/<br>DSTRB#/<br>DENSL0 | V3     | 0    | 3/5V    | Automatic Feed XT, DataStrobe#, or Density Select 0. Signal indicates Automatic Feed XT in compatibility Parallel Port mode, DataStrobe# in ECP mode, or Density Select 0 In Floppy mode. |

| BUSY#/<br>WAIT#/<br>MTR1#  | T4     | I/O  | 3/5VT   | Busy, Wait, or Motor Select 1. Signal indicates Busy in compatibility Parallel Port mode, Wait in ECP mode, or Motor Select 1 in Floppy mode.                                             |

| ERR#/<br>HDSEL#            | V2     | I/O  | 3/5VT   | Error or Head Select. Signal indicates Error in Parallel Port mode or Head Select in Floppy mode.                                                                                         |

| INIT#/DIR#                 | V1     | 0    | 3/5V    | Initialize or Direction. Signal indicates Initialize in Parallel Port mode or Direction in Floppy mode.                                                                                   |

| PD0/INDEX#                 | P3     | I/O  | 3/5VT   | Data 0 or Index#. Signal indicates Data 0 in Parallel Port mode or Index in Floppy mode.                                                                                                  |

| PD1/TRK0#                  | P4     | I/O  | 3/5VT   | Data 1 or Track 0. Signal indicates Data 1 in Parallel Port mode or Track 0 in Floppy mode.                                                                                               |

| PD2/WP#                    | R1     | I/O  | 3/5VT   | Data 2 or Write Protect. Signal indicates Data 2 in Parallel Port mode or Write Protect in Floppy mode.                                                                                   |

| PD3/RDATA#                 | R2     | I/O  | 3/5VT   | Data 3 or Read Data. Signal indicates Data 3 in Parallel Port mode or Read Data in Floppy mode.                                                                                           |

| PD4/<br>DSKCHG#            | R3     | I/O  | 3/5VT   | Data 4 or Disk Change. Signal indicates Data 4 in Parallel Port mode or Disk Change in Floppy mode.                                                                                       |

| TABLE V. Parallel Port/Floppy Interface (Continued) |        |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|-----------------------------------------------------|--------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol(s)                                           | Pin(s) | Туре | Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| PD5/MSEN0                                           | R4     | I/O  | 3/5VT   | Data 5 or Media Sense 0. Signal indicates Data 5 in Parallel Port mode or Media Sense 0 in Floppy mode.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| PD6/DENSL1                                          | T2     | I/O  | 3/5VT   | Data 6 or Density Select 1. Signal indicates Data 6 in Parallel Port mode or Density Select 1 in Floppy mode.                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| PD7/MSEN1                                           | T1     | I/O  | 3/5VT   | Data 7 or Media Sense 1. Signal indicates Data 7 in Parallel Port mode or Media Sense 1 in Floppy mode.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| PE/WDATA#                                           | U1     | I/O  | 3/5VT   | Paper End or Write Data. Signal indicates Paper End in Parallel Port mode or Write Data in Floppy mode.                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| PNF                                                 | N4     | I    | 3/5VT   | Printer Not Floppy (PNF). This input is disabled when the PNF Select bit (Bit 0 of the Function 1 System I/O Configuration Register at configuration offset 5Ch) is a zero. When this input is a zero and the PNF Select bit is a one, the FDC signals are multiplexed onto the Parallel Port/Floppy pins. When this input is a one and the PNF Select bit is a one, the Parallel Port signals are multiplexed onto the Parallel Port/Floppy pins. |  |  |  |

| SLCT/<br>WGATE#                                     | U2     | I/O  | 3/5VT   | Select or Write Gate. Signal indicates Select in Parallel Port mode or Write Gate in Floppy mode.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| SLIN#/<br>ASTB#/<br>STEP#                           | U3     | 0    | 3/5V    | Select Input, Strobe, or Step. Signal indicates Select Input in compatibility Parallel Port mode, Strobe in ECP mode, or Step in Floppy mode.                                                                                                                                                                                                                                                                                                      |  |  |  |

| STB#/WRITE#                                         | P2     | 0    | 3/5V    | Data Strobe or Write Strobe. Signal provides Data Strobe in compatibility Parallel Port mode or Write Strobe in ECP mode.                                                                                                                                                                                                                                                                                                                          |  |  |  |

# 4.3.3 Serial Interface (Ports 1 and 2)

# **TABLE VI. Serial Interface**

| Symbol(s) | Pin(s) | Туре | Voltage | Function                                                                             |

|-----------|--------|------|---------|--------------------------------------------------------------------------------------|

| CTS[1:0]# | U8, Y4 | I    | 3/5VT   | Clear To Send. Indicates Clear to Send for Serial Ports 1 and 2.                     |

| DCD[1:0]# | Y6, U4 | ı    | 3/5VT   | Data Carrier Detect. Indicates Data Carrier Detect for Serial Ports 1 and 2.         |

| DSR[1:0]# | U7, W3 | ı    | 3/5VT   | Data Set Ready. Data Set Ready for Serial Ports 1 and 2.                             |

| DTR[1:0]# | V8, U5 | 0    | 3/5V    | Data Terminal Ready. Indicates Data Terminal Ready for Serial Ports 1 and 2.         |

| RTS[1:0]# | W7, V4 | 0    | 3/5V    | Request To Send. Indicates RequesT to Send for Serial Ports 1 and 2.                 |

| RI[1:0]#  | W8, V5 | I    | 3/5VT   | Ring Indicator. Indicates that either Serial Port 1 or 2 is receiving a ring signal. |

| SIN[1:0]  | V7, Y3 | I    | 3/5VT   | Serial Data Input. Indicates Serial Data Input for Serial Ports 1 and 2.             |

| SOUT[1:0] | Y7, W4 | 0    | 3/5V    | Serial Data Output. Indicates Serial Data Output for Serial Ports 1 and 2.           |

# 4.3.4 Universal Infrared (UIR) Interface (Serial Port 2)

# TABLE VII. Universal Infrared (UIR) Interface

| Symbol(s)              | Pin(s)    | Туре | Voltage | Function                                                                                                                                    |

|------------------------|-----------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ID[0]/IRSEL0/<br>IRRX2 | U6        | I/O  | 3/5VT   | ID0, Infrared Select 0, or Infrared Receive Data 2. Indicates ID0 for Plug and Play support, Infrared Select 0, or Infrared Receive Data 2. |

| ID[2:1]/<br>IRSEL[2:1] | W6,<br>V6 | I/O  | 3/5VT   | ID[2:1] or Infrared Select 2-1. Indicates ID[2:1] for Plug and Play support or Infrared Select 2-1.                                         |

| IRRX                   | Y5        | I    | 3/5VT   | Infrared Receive Data. Signal indicates Infrared Receive Data.                                                                              |

| IRTX                   | W5        | 0    | 3/5V    | Infrared Transmit Data. Indicates Infrared Transmit Data.                                                                                   |

# 4.4 CPU INTERFACE

# **TABLE VIII. CPU Interface**

| Symbol(s) | Pin(s) | Туре | Voltage       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------|--------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

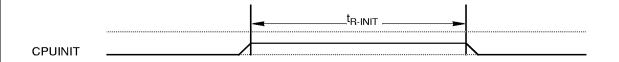

| CPUINIT   | D6     | 0    | Open<br>Drain | CPU Initialization. This signal with a pull-up resistor can be used to drive the CPU's INIT pin during power-up (RESET_IN# active) or when the PC87560 detects a shutdown special cycle on the PCI Bus. CPUINIT will also be active if a soft reset is initiated via Port 92, or a snooped Fast Reset (if Fast Reset is enabled) or KBRST# is asserted (if Fast Reset is disabled).                                                                                   |

| CPUINT    | C5     | 0    | Open<br>Drain | CPU Interrupt. This signal with a pull-up resistor can be used to drive the CPU INT pin.                                                                                                                                                                                                                                                                                                                                                                              |

| CPURST    | A5     | 0    | Open<br>Drain | CPU Reset. This signal with a pull-up resistor can be used to drive the CPU Reset signal of the CPU. The PC87560 releases CPURST during power-up (RESET_IN# active). CPURST is driven inactive (low) a minimum of 2ms after RESET_IN# is driven inactive to allow the CPU's clock and VCC time to stabilize. CPURST is driven inactive low synchronously to the rising edge of PCICLK.                                                                                |

| FERR#     | C6     | I    | 3/5V          | Numeric Coprocessor Error. This signal is the Numeric Coprocessor Error input from the CPU.                                                                                                                                                                                                                                                                                                                                                                           |

| FGA20     | B5     | 0    | Open<br>Drain | Fast Gate A20. This signal with a pull-up resistor can be used to drive the CPU A20M# pin. If the USB Legacy Keyboard Support function is enabled, it will be the source for this output. Otherwise, if the Fast GateA20 strapping option is enabled, this would be the source of this signal. If both the USB Legacy Keyboard Support function and the Fast Gate A20 strapping option are disabled, then the Keyboard GateA20 input (KBGA20) will drive this signal. |

| IGNNE#    | B6     | 0    | Open<br>Drain | Ignore Numeric Error. This signal with a pull-up resistor may be used to drive the CPU IGNNE# pin.                                                                                                                                                                                                                                                                                                                                                                    |

| NMI       | A6     | 0    | Open<br>Drain | Non Maskable Interrupt. This signal with a pull-up resistor may be used to drive the CPU's NMI signal. This signal will go active (high) when a PCI System Error occurs.                                                                                                                                                                                                                                                                                              |

| TABLE VIII. CPU Interface (Continued) |        |      |          |                                                                                                                                                                                                                                                                                                             |  |  |

|---------------------------------------|--------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Symbol(s)                             | Pin(s) | Туре | Voltage  | Function                                                                                                                                                                                                                                                                                                    |  |  |

| PM_PWRGOOD                            | H4     | I    | 3/5VT_PM | Power Management Power Good. When PM_PWRGOOD is asserted (high), it indicates that the VDD_PM power is on and valid. When PM_PWRGOOD is deasserted (low), it will reset all PC87560 functions that are powered by VDD_PM.                                                                                   |  |  |

| RESET_IN#                             | H2     | I    | 3/5VT_PM | Reset Input. When de-asserted (high), RESET_IN# is an indication to the PC87560 that power and PCICLK have been stable for at least 1ms. When RESET_IN# is asserted (low), the PC87560 resets all functions powered by VDD and asserts CPURST, CPUINIT and PCIRST#. RESET_IN# can be driven asynchronously. |  |  |

# 4.5 FX BUS (FXB) INTERFACE

# TABLE IX. FXB Interface

| Symbol(s)          | Pin(s) | Туре | Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|--------|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUDIOCS#           | P19    | 0    | 3/5V    | Audio Chip Select. This active-low output Chip Select provides support for a compatible, fragmented Sound Blaster I/O map.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BHE#               | M18    | 0    | 3/5V    | Byte High Enable. This FX Bus signal is asserted low to indicate that high (odd) data byte is being transferred. Only 16-bit devices use this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DACK0#/<br>DOCKEN# | J18    | I/O  | 3/5VT   | DMA Acknowledge 0 or Dock Enable. During normal operation, this pin will act as the active-low DMA Acknowledge output signal associated with the DRQ[0] input. During a power-up reset, this pin will become an input strapping option and is sampled on the rising edge of RESET_IN#. This I/O signal has a weak pull-down resistor; thus, it will default low unless an external pull-up resistor is used. If this pin is sampled low, the PC87560 will indicate that it is in a Docking Station (Its Function 1 Device ID will be 000Eh). If this pin is sampled high, then the PC87560 will indicate that it is in a Notebook Mother- board (Its Function 1 Device ID will be 0011h). |

| DACK1#/<br>FENCFG  | J19    | I/O  | 3/5VT   | DMA Acknowledge 1 or Function Enable Configuration.  During normal operation, this pin will act as the active-low DMA Acknowledge output signal associated with the DRQ[1] input.  During a power-up reset, this pin will become an input strapping option and is sampled on the rising edge of RESET_IN#. This I/O signal has a weak pull-down resistor; thus, it will default low unless an external pull-up resistor is used. If this pin is sampled low, all of the PC87560 functions are disabled. If this pin is sampled high, then the PC87560 functions will operate normally as defined.                                                                                         |

| DACK2#/<br>FGA20EN | J20    | I/O  | 3/5VT   | DMA Acknowledge 2 or Fast Gate A20 Enable.  During normal operation, this pin will act as the active-low DMA Acknowledge output signal associated with the DRQ[2] input.  During a power-up reset, this pin will become an input strapping option and is sampled on the rising edge of RESET_IN#. This I/O signal has a weak pull-down resistor; thus, it will default low unless an external pull-up resistor is used. If this pin is sampled low, the Fast GateA20 and the Fast Keyboard Reset logic will be disabled. If this pin is sampled high, the Fast GateA20 and the Fast Keyboard Reset logic will be enabled.                                                                 |

| TABLE IX. FXB Interface (Continued) |                                                                                                     |      |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol(s)                           | Pin(s)                                                                                              | Туре | Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| DACK3#/<br>SIRQMST                  | K17                                                                                                 | I/O  | 3/5VT   | DMA Acknowledge 3 or Serial Interrupt Request Master.  During normal operation, this pin will act as the active-low DMA Acknowledge output signal associated with the DRQ[3] input.  During a power-up reset, this pin will become an input strapping option and is sampled on the rising edge of RESET_IN#. This I/O signal has a weak pull-down resistor; thus, it will default low unless an external pull-up resistor is used. If this pin is sampled low, the Serial Interrupt interface logic will be operate as a Slave. If this pin is sampled high, the Serial Interrupt interface logic will operate as the Master.                                                                                                                                              |  |  |  |

| DRQ[3:0]                            | L20, K20,<br>K19, K18                                                                               | -    | 3/5VT   | DMA Requests 3-0. These DMA request pins may be steered to any of the internal PC87560 8237 DMA Controllers' request inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| FXA[20]/<br>POWERPC                 | Y17                                                                                                 | 0    | 3/5V    | FX Address 20 or PowerPC ROM Chip Select Range Enable. During normal operation, this signal drives out the most significant address bit on the FX Bus. During a reset (when RESET_IN# is low), this pin provides an input strapping option. By default, this I/O has a weak pull-down resistor that is enabled whenever RESET_IN# is active low unless a $10 \text{K}\Omega$ is applied. The rising edge of RESET_IN# samples this pin. If it is sampled low, the PowerPC ROM Chip Select memory range (FFF00000-FFFFFFFh) will not be decoded by the PC87560 to generate an active ROMCS# signal and an associated FX Bus cycle. If this pin is sampled high, the PowerPC ROM chip select memory range will be decoded along with the appropriate associated FX Bus cycle |  |  |  |

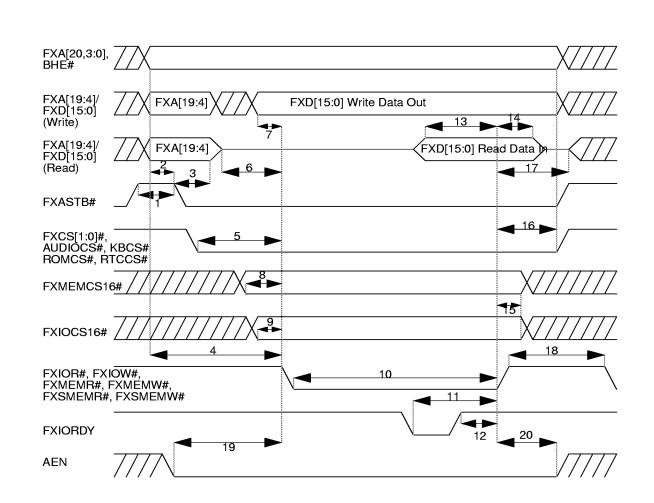

| FXA[19:4]/<br>FXD[15:0]             | W17, V17,<br>Y18, W18,<br>V18, W20,<br>U17, V19,<br>V20, U18,<br>U19, U20,<br>T17, T18,<br>T19, T20 | 1/0  | 3/5VT   | FX Address 19-4 or FX Data Bus 15-0. This is the multiplexed FX address/data bus. During FX Bus address phases, the appropriate address will be driven onto these pins by the PC87560. During FX Bus data phases, the PC87560 will drive out the appropriate data during write cycles and will put these signals in TRI-STATE during read cycles, thus acting as inputs.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| FXA[3]/<br>IDE_3v_EN#               | R17                                                                                                 | I/O  | 3/5VT   | FX Address 3 or IDE Interface 3 Volt Drive Strength Enable. During normal operation, this signal is an output for address bit 3 on the FX Bus. During a power—up reset (when RESET_IN# is low), this pin is an input strapping option. This I/O has a weak pull—down resistor that is enabled whenever RESET_IN# is active low causing the pin to default to a low signal state unless an external pull—up resistor is applied. If sampled low, the IDE Interface drivers are optimized for a 3V system. If sampled high, the IDE Interface drivers are optimized for a 5V system.  NOTE: This strapping option must be configured for the correct system voltage to ensure that the IDE Interface signals adhere to the ATA specification.                                |  |  |  |

| FXA[2:0]                            | R18, R19,<br>R20                                                                                    | I/O  | 3/5VT   | FX Address 2-0. These three signals are the least significant address bits on the FX Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| FXASTB#                             | P20                                                                                                 | 0    | 3/5V    | FX Address Strobe.  During the FX Bus address phase, the falling edge of FXASTB# is used to latch the address FXA[19:4] off the multiplexed FXA[19:4]/FXD[15:0] pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| Cumbal(a)  | Din(a)           | Tuna | Valtage | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|------------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol(s)  | Pin(s)           | Туре | Voltage | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| FXCS[1:0]# | P17, P18         | 0    | 3/5V    | FX Chip Select 0 and 1.  These active—low signals are programmable I/O address range chip selects to select external devices on the FX bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FXIOCS16#  | N20              | ı    | 3/5VT   | FX I/O Chip Select 16 Bit. This input signal is driven active (low) by 16-bit I/O devices wher they are being addressed and this signal will be used by the PC87560's FX Bus Controller to appropriately steer data for I/O cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| FXIRQ[2:0] | H20, H19,<br>H18 | I    | 3/5VT   | FX Bus Interrupt Request 2-0. These are general purpose interrupts that are internally routed (configurable) to the interrupt lines of the 8259s.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| FXIORDY    | N19              | I/O  | 3/5VT   | FX I/O Ready. When accessing the FX Bus, this signal may be negated (low) b the device being accessed to extend the FX Bus transfer cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| FXIOR#     | N17              | 0    | 3/5VT   | <b>FX I/O Read.</b> This is the FX Bus I/O read strobe. The pulse width of this signal is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| FXIOW#     | N18              | 0    | 3/5VT   | FX I/O Write. This is the FX Bus I/O write strobe. The pulse width of this signal is programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| FXMEMCS16# | M17              | I    | 3/5VT   | FX Memory Chip Select 16 Bit. This input signal is driven active (low) by 16-bit memory devices when they are being addressed and this signal will be used by the PC87560's FX Bus Controller to appropriately steer data for memory cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| FXMEMR#    | M19              | 0    | 3/5V    | FX Memory Read. This is the FX Bus Memory read strobe. This signal will strobe active for every memory read cycle on the FX Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

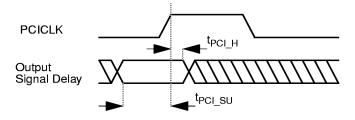

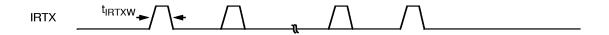

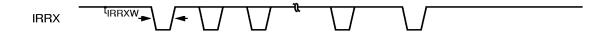

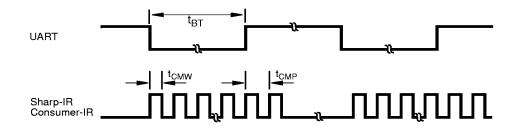

| FXMEMW#    | M20              | 0    | 3/5V    | FX Memory Write. This is the FX Bus Memory write strobe. This signal will strobe active for every memory write cycle on the FX Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |