# μPD72002 Serial Communications Controller: Single-Channel, Advanced Multiprotocol, CMOS

June 1991

## Description

The  $\mu$ PD72002 Serial Communications Controller is an advanced multiprotocol serial controller (AMPSC). The high-performance  $\mu$ PD72002 is a software-compatible, single-channel version of NEC's powerful  $\mu$ PD72001 AMPSC. Both the  $\mu$ PD72002 and the  $\mu$ PD72001 have a superset of the functions of the 8530 SCC.

The  $\mu$ PD72002 AMPSC contains a single full-duplex serial channel that can be configured to transmit and receive data in either asynchronous protocol or one of two synchronous protocols.

- Character-oriented protocol (COP), such as binary synchronous control (Bisync) and Monosync.

- Bit-oriented protocol (BOP), such as high-level data link control (HDLC) and synchronous data link control (SDLC).

The  $\mu$ PD72002 AMPSC, like its forerunner the  $\mu$ PD72001, provides vectored and non-vectored interrupt operation. Vectored operation allows multiple AMPSCs (both  $\mu$ PD72001s and  $\mu$ PD72002s) to be connected in an interrupt daisy chain configuration.

Separate direct memory access (DMA) request and acknowledge lines, available for both transmitter and receiver, provide a direct interface to the  $\mu$ PD71071 and 8237 DMA controllers, allowing for high-speed operation. The AMPSC is easily interfaced to most microprocessors with a minimum of additional logic.

Features that make the  $\mu$ PD72001 the right choice for today's advanced communications requirements are also present in the  $\mu$ PD72002. An on-chip digital phase-locked loop (DPLL) and two baud rate generator (BRG)/timers are available, one BRG for the transmitter and one for the receiver. The BRGs provide the flexibility of operation with asymmetrical data rates on the serial channel.

A crystal oscillator and a low-power standby mode of operation are also included. The standby mode reduces power consumption dramatically, preserving all register values while disabling the transmitter and receiver. The  $\mu$ PD72002's features simplify design requirements and make it an excellent choice for applications that require only one serial communications channel.

#### **Features**

- Single-channel version of μPD72001

- □ Software compatible with µPD72001

- Functional superset of industry standard 8530

- CMOS technology

- □ Multiprotocol

- Asynchronous

- Synchronous

- Character-oriented (Bisync and Monosync)

- Bit-oriented (SDLC/HDLC)

- One full-duplex channel

- Versatile host-system interface

- -Software polling

- Interrupt

- -- DMA

- Direct interface to μPD71071 and 8237 DMA controllers

- Interface to a majority of microprocessors (V-Series, 8080, 8085, 80x86/80x88, and others)

- □ Dc to 2.2-Mb/s data rate

- Modem control signals

- NRZ, NRZI, and FM encoding/decoding, Manchester decoding

- Digital phase-locked loop

- Two baud rate generator/timers (receive and transmit)

- Crystal oscillator

- SDLC loop mode

- Mark idle detection

- Short-frame detection

- Single + 5-volt power supply

- Standby mode for reduced power consumption

- 11-MHz, 12-MHz, or 12.5-MHz system and input data clocks

- Available in DIP, PLCC, and QFP packages

50178-1

6427525 0087041 497 **=**

#### **Ordering Information**

| Part Number | Package            | Max Clock Speed |  |  |

|-------------|--------------------|-----------------|--|--|

| μPD72002C   | 40-pin plastic DIP | 12.5 MHz        |  |  |

| μPD72002GB  | 44-pin plastic QFP | •               |  |  |

| μPD72002L   | 44-pin PLCC        | •               |  |  |

#### Pin Configurations

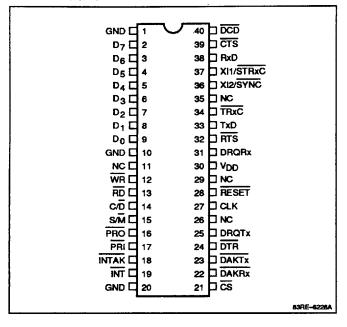

#### 40-Pin Plastic DIP

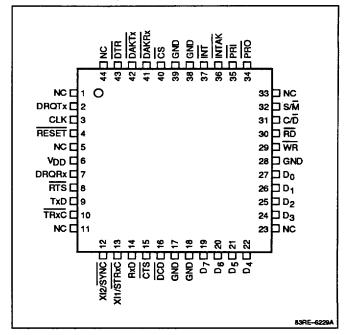

#### 44-Pin Plastic QFP

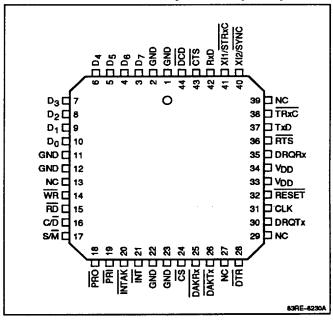

## 44-Pin Plastic Leaded Chip Carrier (PLCC)

#### Pin Identification

| Symbol                         | 1/0 | Signal Function                                                  |

|--------------------------------|-----|------------------------------------------------------------------|

| C/D                            | In  | Control/data select from host computer                           |

| CLK                            | ln  | System clock from host computer                                  |

| CS                             | In  | Chip select                                                      |

| CTS                            | ln  | Clear-to-send                                                    |

| D <sub>0</sub> -D <sub>7</sub> | 1/0 | System data bus                                                  |

| DAKRX                          | In  | Receive DMA acknowledge                                          |

| DAKTX                          | ln  | Transmit DMA acknowledge                                         |

| DCD                            | ln  | Data carrier detect                                              |

| DRQRx                          | Out | Receive DMA request                                              |

| DRQTx                          | Out | Transmit DMA request                                             |

| DTR                            | Out | Data terminal ready                                              |

| INT                            | Out | Interrupt request to host computer                               |

| INTAK                          | In  | Interrupt acknowledge from host computer                         |

| PAI                            | ln  | Priority interrupt daisy chain control                           |

| PRO                            | Out | Priority interrupt daisy chain control                           |

| RD                             | ln  | Read control from host computer                                  |

| RESET                          | in  | System reset from host computer                                  |

| RTS                            | Out | Request-to-send                                                  |

| RxD                            | In  | Receive data                                                     |

| S/M                            | In  | Secondary or main register select                                |

| TRxC                           | 1/0 | Transmit-receive clock                                           |

| TxD                            | Out | Transmit data                                                    |

| WA                             | ln  | Write control from host computer                                 |

| XI1/STRxC                      | ln  | External crystal connection or transmit-<br>receive clock source |

| XI2/SYNC                       | I/O | External crystal connection or synchronization signal            |

| NC                             |     | No connection                                                    |

| GND                            |     | System ground                                                    |

| V <sub>DD</sub>                |     | +5 V (typical)                                                   |

#### **PIN FUNCTIONS**

#### **CPU** Interface

$C/\overline{D}$  (Control/Data Select). The input to this pin selects the type of data on the data bus during a write or read access. A low input selects data; a high input selects a control or status register.

**CLK (System Clock).** This input supplies the clock for the internal operation of the device. It is separate from the data clocks. The system clock input must be more than five times the serial data transfer rate.

**CS** (Chip Select). An active-low input signal at this pin selects the AMPSC for a read or write operation.

**D<sub>0</sub>-D<sub>7</sub> (Data Bus).** These pins constitute a three-state, 8-bit, bidirectional data bus. The bus is connected to the host processor's data bus to transfer control words, status information, and send/receive data.

**INT** (Interrupt). The interrupt request output signal at this pin goes low if an interrupt source occurs within the AMPSC. The output is an open-drain transistor and requires a pull-up resistor.

INTAK (Interrupt Acknowledge). An active-low input signal at this pin is used in response to an interrupt request. In the vectored mode (CR2M bit D7 = 1), it causes the interrupt vector to be placed on the data bus. The output vector mode determines the number of cycles of INTAK toggling required for each interrupt acknowledge cycle (see CR2M bits D3-D5). In the nonvectored mode (D7 = 0), this pin must be pulled high. If unused, this pin must be pulled high also.

PRI (Priority Input). The PRI signal controls interrupt request generation and interrupt vector output. This pin is the input for the interrupt priority daisy chain that determines how interrupts from multiple devices are resolved. A high level prevents the AMPSC from presenting an interrupt vector during the INTAK sequence. A low level allows the vector to be presented. If unused, this pin must be tied low.

PRO (Priority Output). This is an output to the interrupt priority daisy chain. It controls interrupt requests from lower-priority devices. It indicates the existence of a higher-priority interrupt, either within the AMPSC or, if no internal interrupt exists, the condition of the PRI input.

$\overline{RD}$  (Read). The active-low  $\overline{RD}$  input signal in conjunction with  $\overline{CS}$  causes status or receive (Rx) data to be read out of the AMPSC. The data is presented on pins  $D_0$ - $D_7$ . The values are dependent on the state of the  $S/\overline{M}$  and  $C/\overline{D}$  inputs and the internal state of the device.

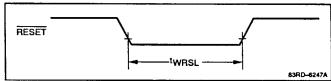

RESET (Reset). Applying a low signal continuously for two or more clock cycles (t<sub>CYK</sub>) to this pin resets the AMPSC (system reset) and places it in standby mode. A system reset disables the transmitter, receiver, interrupt, and DMA functions and sets the TxD and general-purpose output pins to high. It also resets all bits of the control registers.

S/M (Secondary/Main Select). The input to this pin selects either the main or secondary registers during a read or write operation. A low selects the main registers; a high selects the secondary registers.

$\overline{WR}$  (Write). The active-low  $\overline{WR}$  input signal in conjunction with  $\overline{CS}$  causes control words or transmit (Tx) data to be written into the AMPSC. The data written is input on D<sub>0</sub>-D<sub>7</sub>. The destination of the data is determined by the state of the S/ $\overline{M}$  and C/ $\overline{D}$  pins and the value of the internal register pointer.

#### **Channel Interface**

DAKRx (Receive DMA Acknowledge). This active-low input is a DMA acknowledge from the DMA controller. The pin is set low by the DMA controller in response to a receive DMA request from the AMPSC to indicate that DMA service has been granted to the AMPSC. This signal replaces the  $\overline{CS}$  signal for DMA transfers

DAKTx (Transmit DMA Acknowledge). This active-low input is a DMA acknowledge from the DMA controller. The pin is set low by the DMA controller in response to a transmit DMA request from the AMPSC to indicate that DMA service has been granted to the AMPSC. This signal replaces the  $\overline{CS}$  signal for DMA transfers.

DRQRx (Receive DMA Request). This active-high output is a DMA request to the DMA controller. The pin is set to high when the receiver enters the Rx Character Available state. It is reset when received data is read out of the channel.

DRQTx (Transmit DMA Request). This active-high output is a DMA request to the DMA controller. The pin is set to high when the Tx buffer is emptied. The conditions under which this occurs depend on the status of control register CR1 bit D2.

RxD (Receive Data). Receive data enters the AMPSC on this pin.

STRxC (Clock Source). This pin is the transmit or receive clock source input. It can be routed internally to the transmitter, receiver, the BRGs, or the DPLL. An alternative function as an external crystal connection point (XI1) is selected by CR15 bit D7.

TRxC (Transmit/Receive Clock). If bit D2 of CR15 is 0, this pin is a transmit or receive clock input. Also, it is an input if bits D5 and D6 or D3 and D4 of CR15 are set 1 and 0, respectively, overriding the state of bit D2.

If none of the conditions above are true, the pin functions as an output for either the crystal oscillator, the BRG, the DPLL, or the transmit clock. The clock source is selected by bits D0 and D1 of CR15.

TxD (Transmit Data). Transmit data exits the AMPSC on this pin.

XI1, XI2 (Crystal Connections). This pin pair may be connected to an external crystal that controls the internal oscillator.

#### **Modem Control**

CTS (Clear to Send). This is a general-purpose input usable, as an example, for modem control. A status change on CTS affects E/S bit latch operation. If E/S INT is enabled (CR1 bit D0 set to 1), an E/S interrupt occurs. If the Auto Enable mode is selected (CR3 bit D5 set to 1), CTS can be used with the Tx Enable bit (CR5 bit D3) to control transmitter operation.

DCD (Data Carrier Detect). This is a general-purpose input usable, as an example, for modem control. A status change on DCD affects E/S bit latch operation. If E/S INT is enabled (CR1 bit D0 set to 1), an E/S interrupt occurs. If the Auto Enable mode is selected (CR3 bit D5 set to 1), DCD can be used with the Rx Enable bit (CR3 bit D0) to control receiver operation.

**DTR** (Data Terminal Ready). This is a general-purpose active-low output controlled by CR5 bit D7.

RTS (Request to Send). This is a general-purpose output usable, as an example, for modem control. Pin status is set by CR5 bit D1 and Auto Enable bit status (CR3 bit D5).

SYNC (Sync Input or Output). In accordance with the settings of CR4 bits D7-D2, and with CR15 bit D7 = 0, the three functions of this pin are as follows.

- (1) Asynchronous mode: general-purpose input that functions like DCD and CTS.

- (2) External sync mode: active-low input indicates to the AMPSC that synchronization has occurred.

- (3) Internal sync mode: active low output indicates when synchronization is detected by the AMPSC.

An alternative function as an external crystal connection point (XI2) is selected by CR15 bit D7.

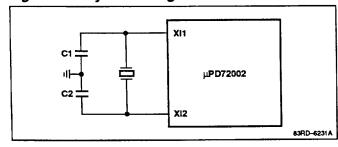

#### OSCILLATOR CRYSTAL

The crystal used with the  $\mu$ PD72002 internal crystal oscillator should be parallel resonant, fundamental mode, with an AT cut. For frequency stability, two capacitors can be added from the pins of the crystal to ground (figure 1). The value of the capacitors can be calculated by the following formula.

$$C_L = \frac{C1 \times C2}{C1 + C2} + C_S$$

■ 6427525 0087044 1T6 **■**

$C_L$  is the load capacitance of the crystal and  $C_S$  is all stray capacitance in parallel with the crystal. The  $C_S$  value should include the input capacitance ( $C_{IO}$  and  $C_{IN}$ ) of the  $\mu$ PD72002 and any wiring or socket capacitance.

Figure 1. Crystal Configuration Circuit

#### **ELECTRICAL SPECIFICATIONS**

## **Absolute Maximum Ratings**

$T_A = +25^{\circ}C$

| Power supply voltage, V <sub>DD</sub>   | -0.5 to +7.0 V                  |

|-----------------------------------------|---------------------------------|

| Input voltage, V <sub>I</sub>           | -0.5 to V <sub>DD</sub> + 0.5 V |

| Output voltage, V <sub>O</sub>          | -0.5 to V <sub>DD</sub> + 0.5 V |

| Operating temperature, T <sub>OPT</sub> | -10 to +70°C                    |

| Storage temperature, T <sub>STG</sub>   | -65 to +150°C                   |

#### Capacitance

$T_A = +25^{\circ}C; V_{DD} = 0 V; f_C = 1 MHz$

| Parameter         | Symbol | Тур | Max | Unit | Conditions              |  |  |

|-------------------|--------|-----|-----|------|-------------------------|--|--|

| Input capacitance | CIN    | PiN |     | pF   | Unmeasured              |  |  |

| I/O capacitance   | СЮ     |     | 20  | рF   | pins returned<br>to 0 V |  |  |

#### **DC Characteristics**

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5 \text{ V } \pm 10\%$

| Parameter                      | Symbol           | Min                 | Тур | Max                   | Unit | Conditions                                         |

|--------------------------------|------------------|---------------------|-----|-----------------------|------|----------------------------------------------------|

| Input low voltage              | V <sub>IL</sub>  | -0.5                |     | + 0.8                 | V    | All pins except CLK                                |

|                                | VILC             | -0.5                |     | + 0.6                 | ٧    | CLK pins                                           |

| Input high voltage             | V <sub>IH</sub>  | + 2.2               |     | V <sub>DD</sub> + 0.5 | ٧    | All pins except CLK                                |

|                                | V <sub>IHC</sub> | + 3.3               |     | V <sub>DD</sub> + 0.5 | ٧    | CLK pin                                            |

| Output low voltage             | V <sub>OL</sub>  |                     |     | + 0.45                | ٧    | I <sub>OL</sub> = 2.0 mA                           |

| Output high voltage            | V <sub>ОН</sub>  | 0.7 V <sub>DD</sub> |     |                       | ٧    | l <sub>OH</sub> = -400 μA                          |

| Output leakage current, high   | I <sub>LOH</sub> |                     |     | + 10                  | μΑ   | V <sub>OUT</sub> = V <sub>DD</sub>                 |

| Output leakage current, low    | <sup>1</sup> LOL |                     |     | -10                   | μΑ   | V <sub>OUT</sub> = 0 V                             |

| Input leakage current, high    | ILIH             |                     |     | + 10                  | μΑ   | $V_{IN} = V_{DD}$                                  |

| Input leakage current, low     | LIL              |                     |     | -10                   | μΑ   | V <sub>IN</sub> = 0 V                              |

| V <sub>DD</sub> supply current | l <sub>DD</sub>  |                     | 20  | 40                    | mA   | All outputs at high level; t <sub>CY</sub> = 90 ns |

| Standby current                | IDDI             |                     | 1   | 20                    | μΑ   | fRxC = fTxC = fCLK= DC                             |

|                                |                  |                     |     | 1                     | mA   | Standby mode                                       |

# μPD72002

## **AC Characteristics**

$T_A = -10 \text{ to } +70^{\circ}\text{C}; V_{DD} = +5.0 \text{ V } \pm 10\%$

|                                         |                     | 11       | MHz      | 12 and 12.5                   | MHz       |                  |              |

|-----------------------------------------|---------------------|----------|----------|-------------------------------|-----------|------------------|--------------|

| Parameter                               | Symbol              | Min      | Max      | Min                           | Max       | Unit             | Conditions   |

| Clock                                   |                     |          |          |                               |           |                  |              |

| Clock cycle (Note 1)                    | <sup>t</sup> CYK    | 90       | 2000     | 83 (12 MHz)<br>80 (12.5 MHz)  | 2000      | ns               |              |

| Clock high-level width                  | ¹wĸн                | 40       | 1000     | 35                            | 1000      | ns               |              |

| Clock low-level width                   | twkL                | 40       | 1000     | 35                            | 1000      | ns               |              |

| Clock rise time, 1.5 to 3.0 V           | t <sub>KR</sub>     |          | 10       |                               | 10        | ns               |              |

| Clock fall time, 3.0 to 1.5 V           | t <sub>KF</sub>     |          | 10       |                               | 10        | ns               |              |

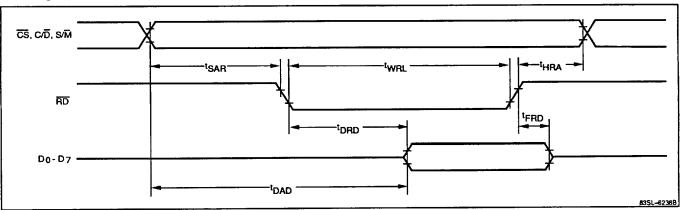

| Read Cycle                              |                     |          |          |                               |           |                  |              |

| Address setup time to RD ↓              | tsar                | 0        |          | 0                             |           | ns               |              |

| Address hold time from RD †             | t <sub>HRA</sub>    | 0        |          | 0                             |           | ns               |              |

| RD pulse width                          | *WRL                | 120      |          | 105                           |           | ns               |              |

| Data output delay time from address     | t <sub>DAD</sub>    |          | 100      |                               | 100       | ns               |              |

| Data output delay time from RD ↓        | <sup>t</sup> DRD    |          | 100      |                               | 95        | ns               |              |

| Data float delay time from RD f         | t <sub>FRD</sub>    | 10       | 40       | 10                            | 40        | ns               |              |

| Write Cycle                             |                     |          |          |                               |           |                  | - <u>-</u>   |

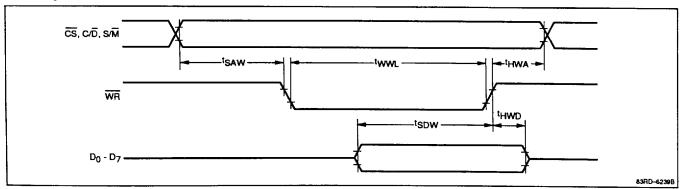

| Address setup time to WR ↓              | t <sub>SAW</sub>    | 0        |          | 0                             |           | ns               |              |

| Address hold time from WR †             | tHWA                | 0        |          | 0                             |           | ns               |              |

| WR pulse width                          | twwL                | 120      |          | 85                            |           | ns               |              |

| Data setup time to WR †                 | tsow                | 100      |          | 75                            |           | ns               |              |

| Data hold time from ₩R ↑                | tHWD                | 0        |          | 0                             |           | ns               |              |

| Read/Write Cycle                        |                     |          |          |                               |           |                  |              |

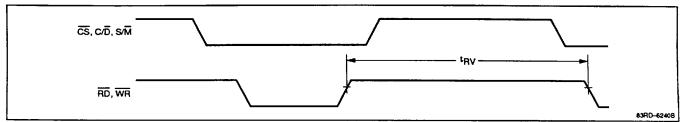

| RD/WR recovery time (Note 2)            | t <sub>RV</sub>     | 140      |          | 125                           |           | ns               |              |

| Transmit or Receive Cycle               |                     |          |          |                               |           |                  |              |

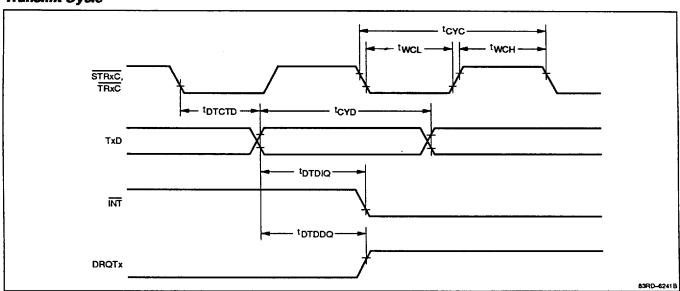

| Transmit/receive data cycle             | tcyp                | 5        |          | 5                             |           | t <sub>CYK</sub> |              |

| STRxC, TRxC input clock cycle           | tcyc                | 90       |          | 83 (12 MHz),<br>80 (12.5 MHz) |           | ns               |              |

| STRxC, TRxC input clock pulse           |                     |          |          | 0.5                           |           | -                |              |

| High-level width Low-level width        | twc⊦<br>twc⊦        | 40<br>40 |          | 35<br>40                      |           | ns<br>ns         |              |

| Transmit Cycle                          |                     |          |          |                               |           |                  |              |

| TxD delay time from STRxC ↓, TRxC ↓     |                     |          |          |                               |           |                  |              |

| x1 mode                                 | <sup>†</sup> DTCTD1 |          | 100      |                               | 90<br>150 | ns<br>ns         |              |

| x16, x32, x64 mode                      | †DTCTD2             |          | 300      |                               | 6         |                  | Tx INT mode  |

| INT delay time from TxD                 | <sup>†</sup> DTDIQ  | 4        | <u> </u> | 4                             | 6         | tovr             | Tx DMA mod   |

| DRQTx delay time from TxD               | †DTDDQ              | 4        | 6        | 4                             | - 0       | <sup>‡</sup> CYK | IX DIAM IIIO |

| Receive Cycle                           |                     |          |          |                               |           |                  |              |

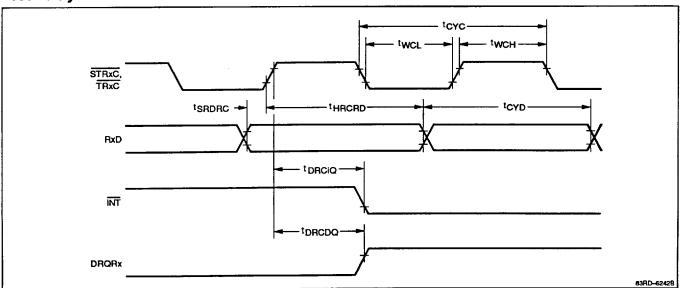

| RxD setup time to STRxC t, TRxC t       | †SRDRC              | 0        |          | 0                             |           | ns               |              |

| RxD hold time from STRxC t, TRxC t      | <sup>t</sup> HRCRD  | 120      |          | 90                            |           | ns               | D. MIT       |

| INT delay time from RxC 1 (Note 3)      | †DRCIQ              | 7        | 11       | 7                             | 11        | t <sub>CYK</sub> | Rx INT mod   |

| DRQRx delay time from RxC f<br>(Note 3) | <sup>t</sup> DRCDQ  | 7        | 11       | 7                             | 11        | <sup>‡</sup> СҮК | Rx DMA mo    |

# AC Characteristics (cont)

|                                                             |                     | 11 MHz |      | 12 and 12.5                   | ИНz  |                  |                              |

|-------------------------------------------------------------|---------------------|--------|------|-------------------------------|------|------------------|------------------------------|

| Parameter                                                   | Symbol              | Min    | Max  | Min                           | Max  | Unit             | Conditions                   |

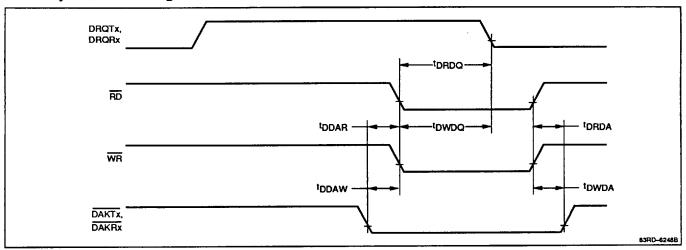

| DMA Request/Acknowledge Cont                                | rol                 |        |      |                               |      | ·                |                              |

| DRQRx ↓ request delay time from RD ↓                        | t <sub>DRDQ</sub>   |        | 120  |                               | 100  | ns               |                              |

| DRQTx ↓ request delay time from WR ↓                        | tDWDQ               |        | 120  |                               | 100  | ns               |                              |

| DAKRx setup time to RD ↓                                    | t <sub>DDAR</sub>   | 0      |      | 0                             |      | ns               |                              |

| DAKTx setup time to WR ↓                                    | <sup>t</sup> DDAW   | 0      |      | 0                             |      | ns               |                              |

| DAKRx hold time from RD f                                   | <sup>t</sup> DRDA   | 0      |      | 0                             |      | ns               |                              |

| DAKTx hold time from WR †                                   | t <sub>DWDA</sub>   | 0      |      | 0                             |      | ns               |                              |

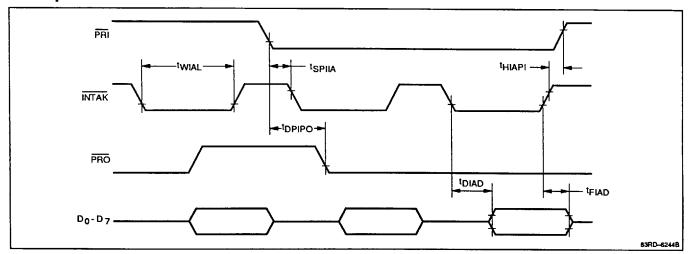

| Interrupt Control                                           |                     |        |      |                               |      |                  |                              |

| INTAK low-level width                                       | †WIAL               | 120    |      | 75                            |      | ns               |                              |

| PRO delay time from PRI                                     | <sup>t</sup> DPIPO  |        | 50   |                               | 30   | ns               |                              |

| PRI setup time to INTAK ↓                                   | t <sub>SPIIA</sub>  | 0      |      | 0                             |      | ns               | When vector                  |

| PRI hold time from INTAK †                                  | <sup>t</sup> HIAPI  | 20     |      | 10                            | -    | ns               | output is selected           |

| Data output delay time from INTAK ↓                         | <sup>t</sup> DIAD   |        | 120  |                               | 80   | ns               |                              |

| Data float delay time from INTAK †                          | t <sub>FIAD</sub>   | 10     | 40   | 10                            | 40   | ns               | ,                            |

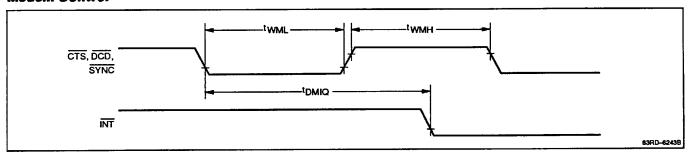

| Modem Control                                               |                     |        |      | <del>,</del>                  |      | -                |                              |

| CTS, DCD, SYNC pulse<br>High-level width<br>Low-level width | twmH<br>twmL        | 2 2    |      | 2 2                           |      | t <sub>CYK</sub> |                              |

| INT delay time from CTS, DCD, SYNC                          | t <sub>DMIQ</sub>   |        | 2    |                               | 2    | †CYK             |                              |

| Sync Control                                                |                     |        |      |                               |      |                  | <u> </u>                     |

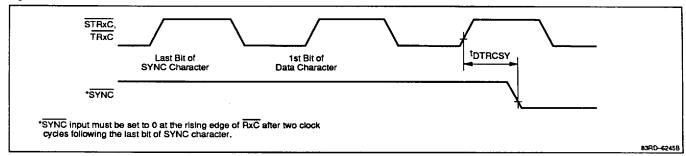

| SYNC delay time from STRxC t,                               | <sup>t</sup> DTRCSY | 0      | 2    | 0                             | 2    | <sup>t</sup> CYK | COP external synchronization |

| Crystal Oscillator                                          |                     |        |      |                               |      |                  |                              |

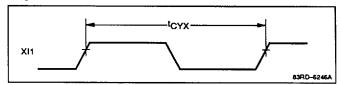

| XI1 input cycle time                                        | <sup>t</sup> CYX    | 90     | 2000 | 83 (12 MHz),<br>80 (12.5 MHz) | 2000 | ns               |                              |

| Reset                                                       |                     |        |      |                               |      |                  |                              |

| RESET pulse width                                           | twrsl               | 2      |      | 2                             |      | <sup>t</sup> CYK |                              |

#### Notes:

<sup>(1)</sup> In all modes, the system clock frequency must be more than five times the maximum data rate.

<sup>(2)</sup> For all operations except Tx/Rx data transfer.

<sup>(3)</sup>  $\overline{RxC} = \overline{STRxC}$  or  $\overline{TRxC}$ .

# µPD72002

# **Timing Waveforms**

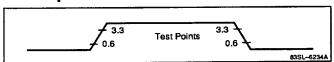

# **Clock Input Test Points**

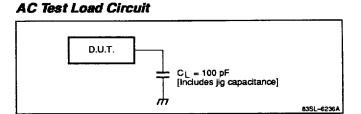

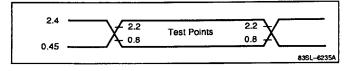

#### I/O Waveform Test Points

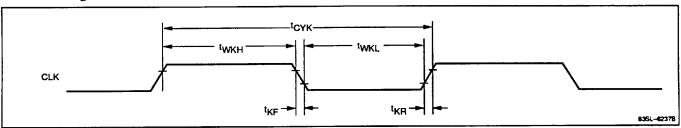

# **Clock Timing**

## Read Cycle

## Write Cycle

# Read/Write Cycle (for all operations except Tx/Rx data transfer)

# Transmit Cycle

# Receive Cycle

## DMA Request/Acknowledge Control

## **Modem Control**

■ 6427525 0087050 4TT **■**

### Interrupt Control

# Sync Control

## Crystal Oscillator

# Reset

# µPD72002

#### **FUNCTIONAL OPERATION**

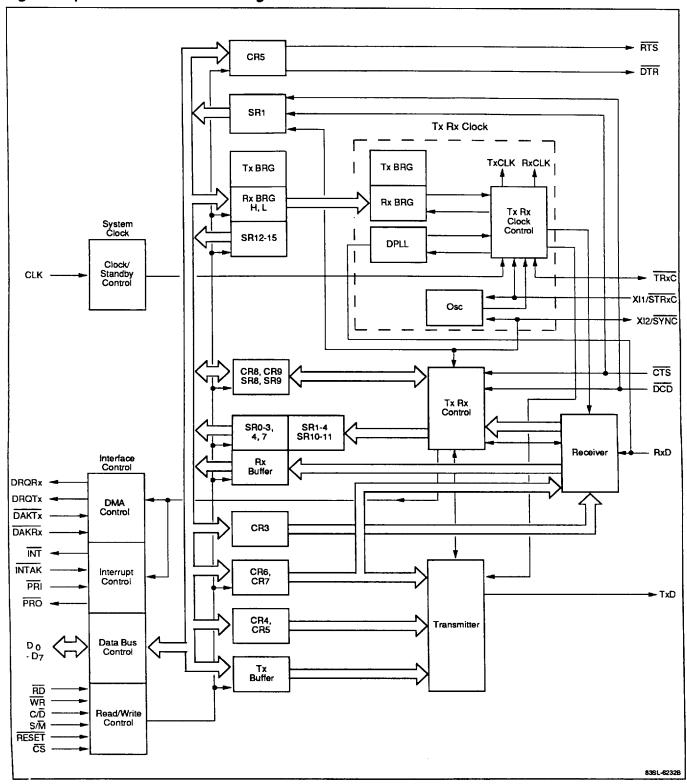

Refer to the  $\mu$ PD72002 AMPSC block diagram (figure 2) for an overview of the four major functional blocks of logic listed below.

- System clock control

- Interface control

- Transmitter

- Receiver

## **System Clock Control**

The system clock control logic receives and manages the system clock (CLK), which operates the internal circuitry of the  $\mu$ PD72002. The system clock and internal circuitry must be operating for the transmitters and receivers of the  $\mu$ PD72002 to function. In standby mode, the system clock is blocked by the clock control circuitry and the transmitters and receivers cannot operate. In clocked operation, the system clock can be used as the source for the data clock required by the transmitters and receivers.

The internal registers of the  $\mu$ PD72002 are static in nature and do not require the system clock to retain their contents.

#### Interface Control

The interface control logic contains the signals used to control the transfer of data and status information between the host CPU and the AMPSC. This logic block has four types of interface lines. The read/write and control lines (RD, WR, C/D, S/M, CS) select the data to be transferred and the direction of transfer.

The reset line (RESET), which is part of this group, resets the internal state of the  $\mu$ PD72002 when held active. The interrupt control line (INT) sends a signal to the host CPU when the AMPSC requires attention. The interrupt acknowledge line (INTAK) signals the  $\mu$ PD72002 when the host CPU is ready to service its request for attention. The interrupt priority lines (PRI, PRO) are used to form the interrupt priority daisy chain, which arbitrates the interrupt service priority.

The DMA control lines (DRQRx, DRQTx,  $\overline{DAKRx}$ ,  $\overline{DAKTx}$ ) inform the DMA controller when a data transfer is ready and when DMA service has been granted to the AMPSC. The data bus buffer provides temporary storage of the data (D<sub>0</sub>-D<sub>7</sub>) being transferred from the internal registers of the  $\mu$ PD72002 to the host CPU.

#### Transmitter

The transmitter accepts parallel byte data and sends it out serially. The data is sent out at a rate determined by the transmit data clock (TxCLK). The source of this clock is determined by the clock control multiplexer. Bytes are loaded into the transmit buffer. When the transmit shift register is empty, the contents of the transmit buffer are loaded into the transmit shift register.

The transmitter is also responsible for the transmit CRC calculation and the sending of flags and SYNC characters. The transmitter can be made to send breaks and aborts using commands from the host CPU.

The internal loopback feature connects the transmitter to the receiver and disconnects the receiver from the RxD pin. The echo loop feature connects the receiver to the TxD pin and disconnects the transmitter.

The baud rate generators (BRGs) divide down the selected clock source to produce data clocks that can be used for the transmitter and receiver. The clock multiplexer selects the clock sources for them. By selecting the correct value for the BRG count, the BRG can be used as a timer with a wide dynamic range. The clock source for the timer can be selected from the system clock, the data clock, an external source, or a crystal.

#### Receiver

The receiver in the AMPSC accepts serial data into the receive shift register, which in turn assembles this serial data into parallel characters (byte). The assembled byte is transferred into the receive buffer (FIFO), which can contain up to three bytes. The receive status of each byte is transferred along with it through the receive buffer. In this way, the status reported by the  $\mu$ PD72002 is always current for the byte that is about to be removed from the FIFO.

The receive shift register also checks for flags and SYNC characters in the synchronous modes. Flags are automatically removed from the data stream, while SYNC characters have the option of being retained. This is determined by a CPU command.

The receiver in synchronous modes calculates the received CRC and checks it against the CRC received with the data. A difference is reported to the host processor.

The digital phase-locked loop (DPLL) is used to separate the data from the clocking information in the NRZI, FM, and Manchester-encoded bit streams. It locks in on the received data and provides an accurate and stable clock for the receiver.

Figure 2. µPD72002 AMPSC Block Diagram

13

### Standby Mode

The  $\mu$ PD72002 enters the standby mode after a hardware reset or by issuing the standby command (CR13 bit D0). In standby mode, the system and data clocks are blocked internally by the clock multiplexer. This shuts down the AMPSC and reduces power consumption greatly. System power requirements can be further reduced by externally stopping the input clock transitions.

In standby mode, the  $\mu$ PD72002 retains all register values, but no internal functions operate and read operations of the AMPSC will not transfer any data. The transmitter and receiver remain disabled once standby mode is released, even if they were enabled when the AMPSC was placed in standby mode.

To release the standby mode, a write cycle must be performed to CR0. To resume normal operation without affecting the internal state of the device, a 0 can be written to CR0.

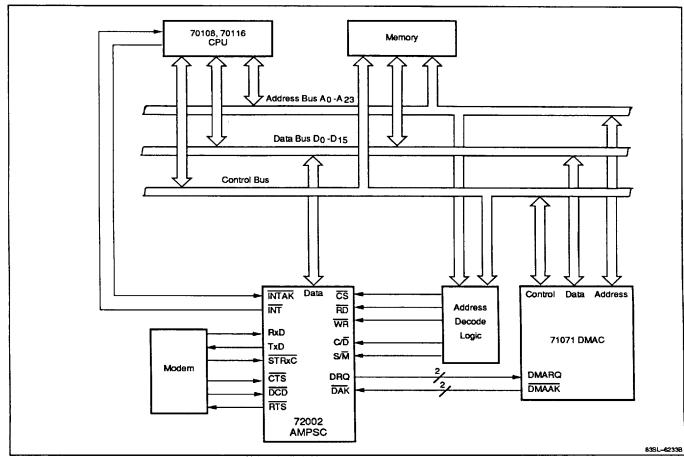

#### SYSTEM CONFIGURATION

In the system configuration example (figure 3), the  $\mu$ PD72002 is used as a high-speed interface to a modern. It controls the modern interface and serial data flow. The AMPSC is used with a direct memory access controller (DMAC) such as  $\mu$ PD71071 to speed data transfer and reduce host CPU overhead.

The  $\mu$ PD72002 directly interfaces the host CPU without requiring an interrupt controller, such as the  $\mu$ PD71059. Extra hardware is not required since the AMPSC can generate its own interrupt vectors.

The interface between the  $\mu$ PD72002 and the host CPU is not very complex. It requires only address decoding logic for I/O operations. The  $\mu$ PD72002 provides a direct DMA interface to the  $\mu$ PD71071 DMA controller by providing both DMA request and DMA acknowledge lines. The only additional signals required during DMA operation are  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ ;  $\overline{\text{CS}}$  is not used during DMA data transfer.

The AMPSC's flexible interface simplifies connection to a variety of host processors.

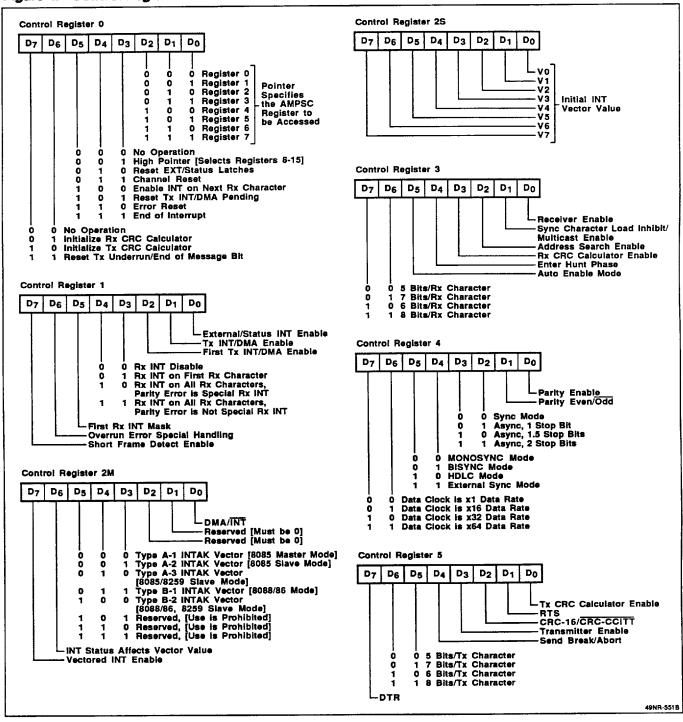

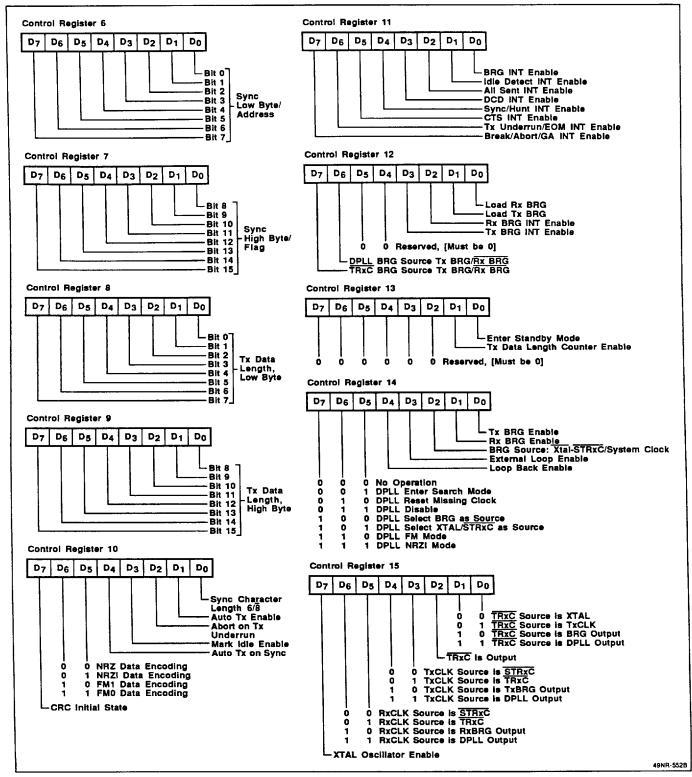

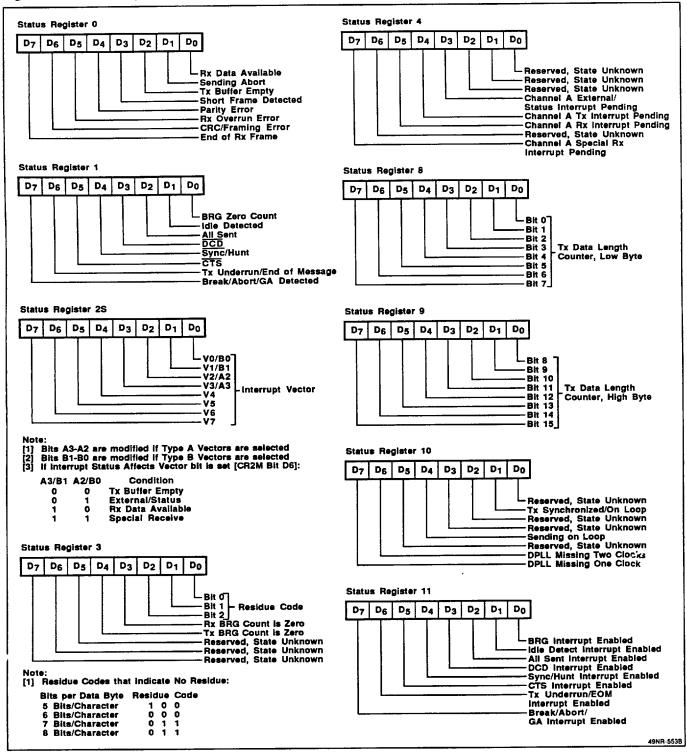

#### **PROGRAMMING**

Software programming the AMPSC utilizes separate data and command/status paths. The data path uses an 8-bit register. The command/status path has a set of 8-bit registers structured for efficient and complete control with a minimum of interaction from the host processor.

The internal registers (table 1) are divided into control registers (CRs) and status registers (SRs).

To maintain compatibility with  $\mu$ PD72001:

- (1) Registers CR2A and CR2B of the 72001 are replaced in the 72002 by CR2M (main) and CR2S (secondary).

- (2) Register SR2B of the 72001 is replaced in the 72002 by SR2S.

The control and status registers for a given register bank are all accessed through the same I/O address. The different registers are selected by the register pointer in CR0 (bits D0-D2). The register pointer is reset to 0 after each register operation. For example,to write to CR2, a 2 is initially written to the control address (C/ $\overline{D}$  pin set high). After this the value to be written into CR2 is also written to the control address.

To read from SR2, a 2 is written to the control address, and then a read cycle at the control address reads the value in SR2. A 0 is not required to be written before CR0 and SR0 are accessed. Control registers (figure 4) set up the device operation mode or control device operations. The host processor writes control words into these registers.

Status registers (figure 5) hold device status information. The host processor can sense the AMPSC device status by reading these registers.

Frequently used information is retained in control register CR0 and status register SR0. This information can be sent or received by writing or reading a single byte. In normal operation, CR0 is initially loaded with a command to reset the AMPSC. Next, CR2M is loaded to set the interface mode. This is followed by the remaining registers, beginning with CR4 to set the protocol type.

Figure 3. System Configuration Example

Figure 4. Control Register Bit Functions

Figure 4. Control Register Bit Functions (cont)

Figure 5. Status Register Bit Functions

Figure 5. Status Register Bit Functions (cont)

Table 1. AMPSC Internal Registers

| Control Registers | CROM, CROS |                                                                |

|-------------------|------------|----------------------------------------------------------------|

|                   | CR1        |                                                                |

|                   | CR2M       |                                                                |

|                   | CR2S       | Initial value of an interrupt vector                           |

|                   | CR3        |                                                                |

|                   | CR4        |                                                                |

|                   | CR5        | THE                                                            |

|                   | CR6        |                                                                |

|                   | CR7        |                                                                |

|                   | CR8, CR9   | Used as a pair                                                 |

|                   | CR10       |                                                                |

|                   | CR11       |                                                                |

| ,                 | CR12       | Tx/Rx BRG registers are loaded by setting bits 0 and 1 of CR12 |

|                   | CR13       | ·                                                              |

|                   | CR14       |                                                                |

|                   | CR15       |                                                                |

| Status Registers | SRO           |                                          |

|------------------|---------------|------------------------------------------|

|                  | SR1           |                                          |

|                  | SR2M          | No register                              |

|                  | SR2S          | Value of interrupt vector                |

|                  | SR3           |                                          |

|                  | SR4           |                                          |

|                  | SR5, SR6, SR7 | No registers                             |

|                  | SR8           |                                          |

|                  | SR9           |                                          |

|                  | SR10          |                                          |

|                  | SR11          | - NA |

|                  | SR12, SR13    | Used as a pair                           |

|                  | SR14, SR15    | Used as a pair                           |

#### **CONTROL REGISTER CRO**

#### CRC Control (D7-D6)

These bits are valid when the COP or BOP mode is selected. They are not used in the asynchronous mode.

No Operation (00). This command has no effect.

Initialize Rx CRC Calculator (01). This command initializes the receive (Rx) CRC calculator. The command should be issued before data reception starts. However, before this command is issued, the initial value of the Rx CRC calculator must be set by the value of CR10 bit D7.

This command is not required in the BOP mode, since the CRC calculator is automatically initialized upon receipt of a flag according to the value of CR10 bit D7.

Initialize Tx CRC Calculator (10). This command initializes the transmit (Tx) CRC calculator. It should be issued before data transmission is started. However, before the command is issued, the initial value of the Tx CRC calculator must be set by the value of CR10 bit D7.

In the BOP mode, if CR10 bit D7 is set to 1, the Tx CRC calculator is automatically initialized to 1 when a flag is loaded into the transmit shift register within the AMPSC.

Reset Tx Underrun/EOM Bit (11). This command resets SR1 bit D6 (transmit underrun/end-of-message bit) from 1 to 0. If data is not loaded into the transmit buffer before the transmit shift register begins transmitting its last bit, the AMPSC enters the Tx Underrun/EOM state. At this point, the AMPSC checks to see if a CRC or SYNC/Flag is to be sent—which depends on the value of SR1 bit D6 and the operating mode. Therefore, SR1 bit D6 must be reset before transmission of the last byte starts to enable transmission of the CRC. At the occurrence of a Tx Underrun, the CRC or the SYNC character/flag is sent when SR1 bit D6 is a 0 or 1, respectively. SR1 bit D6 is set when the CRC byte is written to the Tx shift register by the AMPSC.

In the BOP mode, bit D6 of SR1 is automatically set to 0 when the first data byte of a frame is written into the AMPSC.

## Command (D5-D3)

These bits control the state of the device.

No Operation (000). This command has no effect.

High Pointer (001). This command is used in conjunction with CR0 bits D2-D0 (register pointer) to access status registers 8 through 15. For example, to access SR11, bits D5-D0 of CR0 are set to 001011.

Reset E/S Bit Latches (010). The Reset External Status Bit Latch command is issued when an E/S bit (any bit of SR1) latch operation has occurred. It opens the E/S latches and prepares for the latching of a new E/S bit status change. If the E/S interrupt is enabled, an E/S interrupt will occur and the latches will latch when an E/S bit's status changes. Not all state transitions will cause latching and an interrupt to occur. See the description of SR1 for details. New status will not be available in SR1 until this command is issued.

Channel Reset (011). This command resets the serial channel. It performs a function similar to the RESET pin. Executing the channel reset command halts channel operation. After a channel reset, three system clock periods (t<sub>CY</sub>) should elapse before any further commands or data are sent to the channel.

Enable Next Rx Character Interrupt (100). This command is valid only when the First Rx Character mode (CR1 bits D4-D3 = 01) is selected. It is issued at the end of a message to request an additional Rx interrupt for the first received byte of the next message. The additional Rx interrupt occurs when the next data byte is received after the command is issued.

This command has no effect when the First Rx INT mask is on (CR1 bit D5 = 1), even if the First Rx INT mode is selected.

Reset Tx Interrupt/DMA Pending (101). This command is used to clear a pending Tx interrupt request or Tx DMA request while the Tx buffer is empty (SR0 bit D2 = 1). It is typically used to clear a Tx interrupt or Tx DMA request caused by the Tx buffer empty state that occurs after the last byte is written into the AMPSC.

Error Reset (110). This command is used to reset the pertinent bits (SR0 bits D7-D3) if a Special Rx Condition has occurred. If it occurs when the First Rx INT mode is selected, any data that is subsequently received is not transferred to the last stage of the AMPSC internal Rx buffer, but will remain in the first and second stages until this command is issued.

End of Interrupt (111). This command is used so that the AMPSC can recognize the end of interrupt service processing. It should be issued when interrupt service for the AMPSC is completed. Command execution resets the internal interrupt service latch and reenables lower priority interrupt requests. This command is required when the start of interrupt service has been indicated by either conducting an INTAK cycle, or by reading SR2S.

**■** 6427525 0087060 349 **■**

#### Register Pointer (D2-D0)

These bits specify which AMPSC register number is to be accessed. The bits are reset to 000 when system reset is executed or when the AMPSC is accessed after a register pointer value is specified. For registers numbered 8 and above, the High Pointer command (D5-D3 = 001) is used in conjunction with the register pointer to access them.

#### **CONTROL REGISTER CR1**

## **Short Frame Detect (D7)**

Valid only in BOP mode, this bit detects short HDLC frames (frames shorter than 32 bits).

Short Frame Detect Disabled (0). Short frame detection is disabled.

**Short Frame Detect Enabled (1).** Short frame detection is enabled. If a short frame is received, SR0 bit D3 (Short Frame Detect) is set to 1, and a Special Rx Condition interrupt is generated.

## Overrun Error (D6)

This bit selects the timing of overrun error detection.

Normal Mode (0). In this mode, a Special Rx Condition interrupt indicating Rx Overrun Error occurs when the received data that caused the error is transferred to the last stage of the Rx FIFO.

**Special Mode (1).** In this mode, a Special Rx Condition interrupt indicating Rx Overrun Error occurs immediately when the AMPSC detects the overrun error. The received data that caused the overrun error may not be the byte at the last stage of the Rx FIFO.

# Receive Interrupt on First Character Mask (D5)

This bit is enabled only if the First Rx INT mode (CR1 bits D4-D3 = 01) is selected. It is used to mask Rx interrupts caused by received data. Setting this bit to 1 causes all first receive interrupts to be masked. It does not mask Special Rx Condition interrupts. It is used in data transfers when no interrupt service is desired or required, such as DMA only data transfer.

#### Receive Interrupt Mode (D4-D3)

These bits set the Rx INT mode. They specify the way received data is managed.

**Disable Mode (00).** This mode is used to accept received data using status polling, or to disable the receive interrupt request.

First Rx Character Mode (01). In this mode, which is typically used with DMA data transfer, an Rx interrupt occurs only when the first byte is received. This interrupt occurs when the receiver is enabled after initialization or after the Enable Next Received Character interrupt command is issued.

All Receive-1 Mode (10). This mode causes a receive interrupt to be generated for each byte received. In this mode, a parity error causes a Special Rx Condition interrupt.

All Receive-2 Mode (11). This mode is the same as All Receive-1 mode, except that a parity error does not cause a Special Rx Condition interrupt.

# First Transmit Interrupt/DMA Enable (D2)

This bit determines whether a transmit interrupt or DMA request is generated immediately after the transmitter is enabled. It is valid when Tx INT/DMA is enabled (CR1 bit D1 = 1).

A transmit interrupt or DMA request is issued if bit D2 is 1 when the transmitter is enabled, but not if it is 0. Regardless of the state of bit D2, an interrupt or DMA request is generated when the Tx buffer makes the full-to-empty transition.

### Transmit Interrupt/DMA Enable (D1)

This bit enables the transmit interrupt or DMA request. Each time a Tx Buffer Empty condition exists and provided bit D1 is set, an interrupt or DMA request is generated.

# External/Status Interrupt Enable (D0)

If bit D0 is set, a change in state of the external/status bits causes an interrupt to occur. The current state of the external/status bits is latched. The latches must be reset with the Reset External/Status Bit Latches command (CR0 bits D5-D3) before subsequent interrupts can occur.

#### **CONTROL REGISTER CR2M**

## **Vectored Interrupt Enable (D7)**

This bit determines the handling of the interrupt vector. If the bit is set, the interrupt vector is placed on the data bus during the INTAK cycle by the AMPSC. If the bit is reset, the vector is not placed on the bus; it can be read by the host processor from status register SR2S. In this mode, the INT signal is released after the host processor reads SR2S or clears the interrupt condition.

**■** 6427525 0087061 285 **■**

# Interrupt Status Affects Vector (D6)

This bit determines if the value of an interrupt vector is modified according to the source of the interrupt. If the bit is set, the vector is modified as specified by bits D5-D3. If the bit is reset, the vector is not modified and the cause of the interrupt must be determined by reading SR0 and SR1.

#### Interrupt Vector Mode (D5-D3)

These bits determine the interrupt vector operation and select which bits of an interrupt vector are to be changed when the Interrupt Status Affects Vector bit is set (CR2M bit D6 = 1). For details of how the vector is modified, refer to the description of register SR2S. Table 4 shows the vector operation determined by bits D5-D3.

#### Interrupt/DMA Mode (D0)

This bit selects the data transfer mode: interrupt (D0 = 0) or DMA (D0 = 1). The E/S, Rx, and Special Rx Condition interrupts can be enabled in both modes. The Tx interrupts are disabled in DMA mode.

# **CONTROL REGISTER CR2S**

Bits D7-D0 of CR2S set the initial value of an interrupt vector.

#### **CONTROL REGISTER CR3**

# Receive Character Bit Length (D7-D6)

These bits determine the number of bits per character in the received data.

| Bits D7-D6 | Bits per Character |

|------------|--------------------|

| 00         | 5                  |

| 01         | 7                  |

| 10         | 6                  |

| 11         | 8                  |

In COP mode, the number of bits in the SYNC character must be equal to the bit length of the received character. Parity is enabled or disabled accordingly (CR4 bit D0) depending on the selection of the received character bit length to match the SYNC character bit length.

#### Auto Enable Mode (D5)

Bit D5 enables and disables the auto enable mode. In this mode, the  $\overline{CTS}$  and  $\overline{DCD}$  pins control operation of the transmitter and receiver, respectively. If the input pin is high, the transmitter or receiver is disabled. In asynchronous mode with bit D5 = 1, the  $\overline{RTS}$  pin outputs the

current transmitter status. The pin remains low during transmission and returns high only after all characters have been sent.

The auto enable mode is enabled by setting bit D5 to 1 and disabled by resetting bit D5 to 0. With bit D5 = 0, CTS, DCD, and RTS function as normal inputs and outputs.

In auto enable mode, any status change on the  $\overline{\text{CTS}}$  or  $\overline{\text{DCD}}$  pins is latched and an external/status interrupt is generated.

## Enter Hunt Phase (D4)

Valid in COP or BOP mode, bit D4 set to 1 forces the AMPSC to enter the hunt phase. In the hunt phase, the AMPSC searches the received data stream for either a SYNC character or Flag before it begins loading data into the Rx FIFO. When synchronization is established, bit D4 is set to 0 automatically.

#### Receive CRC Calculator Enable (D3)

Valid only in COP or BOP mode, bit D3 determines whether a CRC calculation is to be performed on the received data. In COP mode, the CRC is calculated 8 bit times after a byte is transferred into the receive FIFO. If bit D3 is reset before this time, the byte will not be included in the CRC calculation. D3 must be set again after the next byte is received to resume the CRC calculation.

#### Address Search Mode Enable (D2)

Valid only in BOP mode, bit D2 determines whether the address field value of a received frame is to be compared with the value set in CR6. If the bit is set to 1, Address Search is enabled and the AMPSC checks the first byte of the frame. If the byte matches CR6 or the global address (FFH), the frame is received. If the byte does not match, the AMPSC enters the Hunt mode again, and the byte and the rest of the frame are blocked and not received. If Multicast mode is enabled (CR3 bit D1), only the 4 most significant bits (CR6 bits D7-D4) of the address byte are compared.

# Sync Character Load Inhibit/Multicast Enable (D1)

Valid only in COP or BOP mode, bit D1 has a different meaning in each mode. In COP mode, setting bit D1 to 1 enables the Sync Character Load Inhibit function. This prevents any byte that matches the value in CR6 from being loaded into the Rx FIFO and from being included in the CRC calculation.

■ 6427525 0087062 **111** ■

In COP mode, this bit is used in conjunction with the Enter Hunt Phase bit (CR3 bit D4) to begin receive operation by the AMPSC. Once synchronization has been established, SYNC characters included in the received data stream are not transferred into the Rx buffer and are not included in the CRC calculation. However, if the Rx FIFO is full and the SYNC character causes an overrun, this function is invalidated. The SYNC character will be transferred into the first stage of the Rx FIFO, but no overrun error is reported by the AMPSC.

In BOP mode, bit D1 enables the Multicast function. In this mode, which is a modified form of the address search mode, only the most significant 4 bits of the received address are compared with the identical bits of CR6. Frame acceptance will function in the same way as in the address search mode.

If Multicast mode is enabled, no Abort detection is performed unless the address that matches the value in CR6 is detected. Once address detection is performed, Abort detection is subsequently performed unconditionally.

## Receiver Enable (D0)

This bit enables and disables the receiver. Setting bit D0 enables the receiver; resetting it disables the receiver. If the Auto Enable mode is selected (CR3 bit D5 = 1), the signal applied to the  $\overline{DCD}$  pin controls receiver operation.

Table 4. Interrupt Vector Operation Throughout INTAK Sequence

| CR2N         | CR2M |    |      |      |             |            | D  | ata Bus S  | Status (INTA | K response | of AMPS | C) |    |

|--------------|------|----|------|------|-------------|------------|----|------------|--------------|------------|---------|----|----|

| D5           | D4   | D3 | Mode | PRI  | INTAK Cycle | D7         | D6 | D5         | D4           | D3         | D2      | D1 | Do |

| <del>-</del> | 0    | 0  | A1   | Low  | 1st         | 1          | 1  | 0          | 0            | 1          | 1       | 0  | 1  |

| _            |      |    |      | Low  | 2nd         | <b>V</b> 7 | V6 | V5         | V4           | MЗ         | M2      | V1 | VO |

|              |      |    |      | Low  | 3rd         | 0          | 0  | 0          | 0            | 0          | 0       | 0  | 0  |

|              |      |    |      | X    | 1st         | 1          | 1  | 0          | 0            | 1          | 1       | 0  | 1  |

|              |      |    |      | High | 2nd         |            |    |            | High Im      | pedance    |         |    |    |

|              |      |    |      | High | 3rd         |            |    |            | High Im      | pedance    |         |    |    |

| 0            | 0    | 1  | A2   | Low  | 1st         |            |    |            | High Im      | pedance    |         |    |    |

|              |      |    |      | Low  | 2nd         | <b>V7</b>  | V6 | V5         | V4           | M3         | M2      | V1 | Vo |

|              |      |    |      | Low  | 3rd         | 0          | 0  | 0          | 0            | 0          | 0       | 0  | 0  |

|              |      |    |      | ×    | 1st         |            |    |            | High In      | npedance   |         |    |    |

|              |      |    |      | High | 2nd         |            |    |            | High In      | npedance   |         |    |    |

|              |      |    |      | High | 3rd         |            |    |            | High In      | npedance   |         |    |    |

| 0            | 1    | 0  | АЗ   | ×    | 1st         |            |    |            | High Im      | pedance    |         |    |    |

| •            | •    | _  |      | Low  | 2nd         | <b>V7</b>  | V6 | <b>V</b> 5 | V4           | МЗ         | M2      | V1 | Vo |

|              |      |    |      | Low  | 3rd         | 0          | 0  | 0          | 0            | 0 _        | 0       | 0  | 0  |

|              |      |    |      | x    | 1st         |            |    |            | High In      | npedance   |         |    |    |

|              |      |    |      | High | 2nd         |            |    |            | High Ir      | npedance   |         |    |    |

|              |      |    |      | High | 3rd         |            |    |            | High ir      | npedance   |         |    |    |

| 0            | 1    | 1  | B1   | Low  | 1st         |            |    |            | High In      | npedance   |         |    |    |

| •            |      |    |      | Low  | 2nd         | <b>V7</b>  | V6 | V5         | V4           | V3         | V2      | M1 | M  |

|              |      |    |      | x    | 1st         |            |    |            | High Ir      | npedance   |         |    |    |

|              |      |    |      | High | 2nd         |            |    |            | High it      | mpedance   |         |    |    |

| 1            | 0    | 0  | B2   | X    | 1st         |            |    |            | High Ir      | npedance   |         |    |    |

|              |      |    |      | Low  | 2nd         | V7         | V6 | V5         | V4           | V3         | V2      | M1 | М  |

|              |      |    |      | x    | 1st         |            |    |            |              | mpedance   |         |    |    |

|              |      |    |      | High | 2nd         |            |    |            | High I       | mpedance   |         |    |    |

#### Notes:

- (1) X = Don't care

- (2) When the Interrupt Status Affects Vector (Bit D6 of CR2M) is set, the M data bits are modified to indicate the interrupt source.

- (3) Modes A3 and B2 ignore the state of PRI. They are slave modes for use with an interrupt controller such as the μPD71059.

#### **CONTROL REGISTER CR4**

#### Clock Rate (D7-D6)

Bits D7 and D6 select the clock rate divisor. They are ignored in the internal synchronous modes. In the external synchronous mode, only the x1 and x16 selections are valid.

In asynchronous mode, the following values apply.

| Bits D7-D6 | Divisor   |

|------------|-----------|

| 00         | <u>x1</u> |

| 01         | x16       |

| 10         | x32       |

| 11         | x64       |

The divisor value is the factor by which the supplied data clock is greater than the data rate for the transmitter and receiver. The data clock source is selected by the clock multiplexer. It can be set to any of the BRG, DPLL, or external clock sources. The divisor determines the number of times that the received data is sampled per bit time by the receiver. Also, it determines the composition of the transmitter output.

## Protocol Mode (D5-D4)

Bits D5-D4 select the synchronous protocol, which is used when the synchronous mode is selected with bits D3-D2.

| Bits D5-D4 | <u>Mode</u>                          |

|------------|--------------------------------------|

| 00         | Monosync, character synchronous      |

| 01         | Bisync, character synchronous        |

| 11         | External sync, character synchronous |

| 10         | HDLC, bit synchronous                |

## Tx Stop Bits/Sync Mode (D3-D2)

Bits D3-D2 select the number of stop bits sent after each byte in asynchronous mode, or they select the synchronous mode.

| Bits D3-D2 | Mode                      |  |  |  |  |  |

|------------|---------------------------|--|--|--|--|--|

| 00         | Sync mode                 |  |  |  |  |  |

| 01         | Async mode, 1 stop bit    |  |  |  |  |  |

| 10         | Async mode, 1.5 stop bits |  |  |  |  |  |

| 11         | Async mode, 2 stop bits   |  |  |  |  |  |

#### Parity Select (D1)

Valid in asynchronous and COP modes, bit D1 selects the parity type: 0 = odd and 1 = even. It is used only when the Parity Enable bit D0 of CR4 is set to 1.

## Parity Enable (D0)

Bit D0 enables the parity bit calculation on transmitted data and parity checking on received data. Setting bit D0 enables parity; resetting bit D0 disables parity. If the length of the received character is 7 bits or less, the parity bit can be read in the received data byte. If parity is disabled, no parity bit is transmitted and none is expected on receipt.

#### **CONTROL REGISTER CR5**

# DTR Control (D7)

This bit controls the  $\overline{DTR}$  pin status: 0 = high and 1 = low.

# Transmit Character Bit Length (D6-D5)

These bits specify the bit count per character in transmitted data.

| Bits D6-D5 | Bits/Character |

|------------|----------------|

| 00         | 5 or fewer     |

| 01         | 7              |

| 10         | 6              |

| 11         | 8              |

If the bit count per character is 6 or 7, only the low-order bits of the byte are valid and the most significant bit(s) are ignored. If the count is 5 bits or lower when writing into the transmit data register, refer to the data format in table 5.

Table 5. Parallel Data Format for 1 to 5 Bits per Character

| Bits | D7 | D6 | D5 | D4 | D3 | D2 | D1 | Do |  |

|------|----|----|----|----|----|----|----|----|--|

| 1    | 1  | 1  | 1  | 1  | 0  | 0  | 0  | DO |  |

| 2    | 1  | 1  | 1  | 0  | 0  | 0  | D1 | D0 |  |

| 3    | 1  | 1  | 0  | 0  | 0  | D2 | D1 | D0 |  |

| 4    | 1  | 0  | 0  | 0  | DЗ | D2 | D1 | D0 |  |

| 5    | 0  | 0  | 0  | D4 | DЗ | D2 | D1 | D0 |  |

Dn = Valid data bit

## Send Break/Abort (D4)

Bit D4 controls the break or abort transmission according to the selected mode. In asynchronous mode, bit D4 controls sending the break signal (TxD set to spacing (0) condition). Setting bit D4 to 1 begins sending the break signal; resetting it to 0 returns the transmitter to normal operation.

In BOP mode, setting bit D4 to 1 causes eight 1-bits (Abort sequence) to be sent. Depending on the preceding serial data, a total of up to 13 1-bits can be transmitted by the AMPSC when this command is issued. When the abort is transmitted, the data in the Tx buffer is invalidated. After completion of the message, bit D4 is reset automatically and the transmitter returns to the idle state.

#### Transmitter Enable (D3)

Disable. Setting bit D3 to 0 disables the transmitter. If the transmitter is currently sending a character, the AMPSC waits until the character is completed before setting TxD to the marking (1) state. If bit D3 is reset during transmission of a CRC character, a SYNC character or Flag is sent in place of the CRC character.

If D3 is reset in the COP or BOP mode, the Tx Underrun/ EOM bit (SR1 bit D6) is set.

If the AMPSC is in the SDLC Loop mode (refer to CR10) or the Echo Loop Test mode (refer to CR14), the TxD pin is connected to RxD and is not set to marking.

**Enable.** Setting bit D3 to 1 enables the transmitter to start transmission. If the Auto Enable mode is selected (CR3 bit D5 = 1), the signal applied to the CTS pin controls transmitter operation.

#### CRC Polynomial (D2)

This bit selects the polynomial used for CRC calculation. It is valid only in COP or BOP mode. Only the CCITT polynomial is used in BOP mode. Bit D7 of CR10 sets the initial value of the CRC calculator.

D2 = 0 (CRC-CCITT): The generating polynomial expression is  $X^{16} + X^{12} + X^5 + 1$ .

D2 = 1 (CRC-16): The generating polynomial expression is  $X^{16} + X^{15} + X^2 + 1$ .

#### RTS Control (D1)

Bit D1 controls the RTS pin. Setting bit D1 to 0 causes RTS to be high; setting it to 1 causes it to go low.

If Auto Enable mode is selected in asynchronous mode,  $\overline{RTS}$  operates differently. If bit D1 remains at 0 from the start of transmission through to the end,  $\overline{RTS}$  will stay high. If it is set to 1 from the start of a transmission,  $\overline{RTS}$  remains low. If it starts set to 1 and is then set to 0 while transmitting,  $\overline{RTS}$  will not go high until all data is transferred out of the Tx shift register (All Sent bit D2 of SR1 = 1).

## Transmit CRC Calculator Enable (D0)

Valid only in the COP or BOP mode, bit D0 determines whether transmitted data is included in the CRC calculation. If bit D0 is set when the byte is transferred into the Tx shift register, the byte is included in the Tx CRC calculation. Bit D0 should be set or reset before loading a data byte into the AMPSC.

In BOP mode, since all transmit data is included in the CRC calculation, this bit should remain set to 1.

#### **CONTROL REGISTER CR6**

Valid only in the COP or BOP mode, this byte (bits D7-D0) specifies the SYNC character pattern or address value.

In Monosync or External Sync mode, D7-D0 holds the Tx SYNC character. In Bisync mode, the low-order byte of the SYNC character is set in D7-D0.

In Monosync or External Sync mode with the SYNC character length selected as 6 bits (CR10 bit D0 = 1), bits D1 and D0 are repeated in bit positions D7 and D6 of CR6.

In BOP mode with the Address Search Enable mode set (CR3 bit D2 = 1), this byte is the secondary address. With the Multicast bit set (CR3 bit D1 = 1), only the 4 most significant bits are used.

#### **CONTROL REGISTER CR7**

Valid only in the COP or BOP mode, these bits specify the SYNC character or Flag.

In Monosync mode, D7-D0 hold the Rx SYNC character. In Bisync mode, the high-order byte of the SYNC character is set in D7-D0. These bits are not used in External Sync mode.

In Monosync mode with the SYNC character length selected as 6 bits, the 6 uppermost bits of CR7 contain the Rx SYNC character.

In BOP mode, the flag pattern (01111110) is set in bits D7-D0.

#### **CONTROL REGISTER CR8**

Valid only in the BOP mode, CR8 bits D7-D0 hold the low byte (bits 7-0) of the transmit data length. Register pair CR8 and CR9 must be loaded before the Tx Data Length Counter Enable bit (CR13 bit D1) and Tx Enable bit (CR5 bit D3) are set. The transmit data length register (TxDLR) is used to automate the sending of HDLC frames. See the description of CR13 bit D1 for detailed information.

#### **CONTROL REGISTER CR9**

Valid only in the BOP mode, CR9 bits D7-D0 hold the high byte (bits 15-8) of the transmit data length. Register CR9 is paired with CR8.

#### **CONTROL REGISTER CR10**

#### Initial CRC State (D7)

Valid only in the COP or BOP mode, bit D7 specifies the initial state of the CRC calculator. Setting this bit to 0 causes the CRC to be initialized to 0 when the Initialize Tx/Rx CRC command (CR0 bits D7-D6) is performed. Setting this bit to 1 causes the CRC to be set to all 1s.

## Data Format (D6-D5)

These bits specify the serial data format and enable the corresponding encoder/decoder.

| Bits D6-D5 | <b>Format</b> |

|------------|---------------|

| 00         | NRZ           |

| 01         | NRZI          |

| 10         | FM1           |

| 11         | FMO           |

With NRZ format, it is possible to decode Manchester encoded data by setting the DPLL mode to FM (CR14 bits D7-D5 = 110).

## Auto Tx on Sync/Tx on Loop (D4)

Bit D4 is valid only in the COP or BOP mode. In COP mode, bit D4 provides the Auto Tx on Sync function to synchronize receiver and transmitter operation as follows.

- (1) D4 = 0. The Auto Tx on Sync function (CR10 bit D1 = 1) is disabled.

- (2) D4 = 1. If CR10 bit D1 is also set to 1, the transmitter is disabled and the receiver enters the Hunt Phase. When the SYNC character is detected, character synchronization is established, the transmitter is enabled, and data transmission can

begin. The state of character synchronization can be determined from the state of the Tx Sync/On Loop bit (SR10 bit D1).

Once synchronization is established after D4 is set to 1, resetting the bit to 0 does not affect synchronization.

In BOP mode, bit D4 controls SDLC Loop operation. This bit is valid only when CR10 bit D1 (Auto Tx/Loop Enable) is set to 1. Bit D4 should be set before the transmitter or receiver is enabled.

The Tx on Loop function is used for data transmission during SDLC Loop operations. Bit D4 set to 0 (1) disables (enables) the function.

- (1) D4 = 0. The Tx on Loop function is disabled (CR10 bit D1 = 1). In SDLC Loop mode of operation, once the AMPSC forms a loop (and starts transmission), bit D4 must be reset to 0. This allows the CRC and flag to be automatically transmitted if a Tx Underrun/EOM condition occurs and allows the AMPSC to be subsequently placed in Loop mode with a 1-bit delay. Bit D4 must be reset before the CRC transmission is completed.

- (2) D4 = 1. SDLC Loop operation is selected (CR10 bit D1 = 1). In SDLC Loop mode, the RxD input is connected to the TxD output within the AMPSC to form a loop. GA (Go Ahead) pattern detection is initiated. If the GA pattern (11111110 = FEH) is detected, 1-bit delay is inserted between RxD and TxD and the GA pattern detection is continued. At this point the transmitter remains disabled, but the receiver can be enabled. Subsequently, if the GA pattern is detected, the transmitter is enabled; the GA pattern is automatically transformed into a flag so that any data in the Tx buffer may be transmitted following the flag. Once transmission is started, bit D4 must be reset before the CRC transmission is completed.

#### Idle Condition (D3)

Valid only in BOP mode, bit D3 determines the type of information to be transmitted following a closing flag or completion of the Send Abort command. If bit D3 is 0, flags will be sent; if it is a 1, continuous marks (1s) will be sent.

#### Transmit Condition on Underrun (D2)

Valid only in the BOP mode, bit D2 determines transmitter action when a Tx Underrun condition occurs. If bit D2 is reset, either the CRC followed by a flag or just a flag is transmitted depending on the state of the Tx Underrun/EOM bit (SR1 bit D6) and the Tx CRC Enable

**■ 6427525 0087066 867 ■**

bit (CR5 bit D0). If the CRC is disabled or the Tx Underrun bit is a 1, only flags are sent. Otherwise, the CRC is sent followed by flags. If bit D2 is set, the Abort message is sent followed by flags regardless of the state of the Tx Underrun/EOM bit or the Tx CRC Enable bit.

## Auto Tx/Loop Enable (D1)

Valid only in the COP or BOP mode, bit D1 enables the operation that is set with bit D4. This bit should be set before the transmitter or receiver is enabled.

In COP mode, if D1 is set to 0, the Auto Tx on Sync function is disabled; if D1 is set to 1, the Auto Tx on Sync function is enabled.

In BOP mode, bit D1 controls SDLC Loop operation. If D1 is set to 0, Loop operation is disabled. If this bit is set to 0 after the AMPSC has entered loop operation, the RxD pin is disconnected from the TxD output in the AMPSC as soon as the GA pattern has been received, disabling SDLC Loop mode. If bit D1 is set to 1, Loop operation is enabled.

## SYNC Character Length (D0)

Valid only in the COP mode, bit D0 determines the number of bits per SYNC character. Setting bit D0 to 0 gives a character length of 8 bits in Monosync and 16 bits in Bisync. With bit D0 = 1, the character length is 6 bits for Monosync mode. Bit D0 must not be set to 1 in Bisync mode.

#### **CONTROL REGISTER CR11**

Each bit of CR11 controls E/S interrupt request generation by the AMPSC due to the E/S interrupt sources. An interrupt is generated if the E/S interrupts are enabled (CR1 bit D0 = 1). For the causes of interrupts assigned to each, refer to the description of SR1. Setting each bit to 1 enables it as a source of interrupts.

## Break/Abort/Go Ahead Interrupt Enable (D7)

In Asynchronous and COP modes, bit D7 enables interrupts at the beginning and end of each detected break condition (a null character plus a framing error).

In BOP mode, when not in SDLC loop, bit D7 enables interrupts at the beginning and end of each received abort condition (7 or more consecutive 1-bits). In SDLC loop mode, bit D7 also enables interrupts for detecting the GA pattern (11111110 = FEH).

# Transmitter Underrun/End of Message Interrupt Enable (D6)

Valid only in the COP or BOP mode, bit D6 enables interrupts caused by Tx Underrun and Tx End of Message detection.

#### Clear to Send Interrupt Enable (D5)

Bit D5 enables interrupts caused by a change of state on the CTS pin.

#### SYNC/Hunt Interrupt Enable (D4)

Bit D4 enables interrupts caused by a change in the SYNC/Hunt state.

#### Data Carrier Detect Interrupt Enable (D3)

Bit D3 enables interrupts caused by a change of state on the  $\overline{\text{DCD}}$  pin.

## All Sent Interrupt Enable (D2)

Valid only in the Asynchronous or BOP mode, bit D2 enables interrupts generated by the All Sent condition.

# Idle Detect Interrupt Enable (D1)

Valid only in the BOP mode, bit D1 enables interrupts caused by a change in the Idle Detection condition.

## **BRG** Interrupt Enable (D0)

Bit D0 enables interrupts caused by one of the baud rate generator/timers (BRG) counting down from 1 to 0. Also, each of the BRGs must be enabled (CR12 bits D3-D2).

#### **CONTROL REGISTER CR12**

## **BRG Select for TRxC (D7)**

When BRG is selected as the source of the clock at the  $\overline{TRxC}$  pin (CR15 bits D1-D0 = 10), and the  $\overline{TRxC}$  pin is set to output (CR15 bit D2 = 1), bit D7 selects TxBRG (D7 = 1) or RxBRG (D7 = 0).

#### **BRG Select for DPLL (D6)**

Bit D6 selects the source (TxBRG or RxBRG) for the DPLL. It is valid when the BRG is selected as the source for the DPLL circuit (CR14 bits D7-D5 = 100). Setting bit D6 to 1 selects TxBRG and setting it to 0 selects RxBRG.

#### Transmit BRG Interrupt Enable (D3)

Bit D3 enables an E/S interrupt when the TxBRG counts down from 1 to 0. It is valid only when the BRG IE bit is set (CR11 bit D0 = 1).

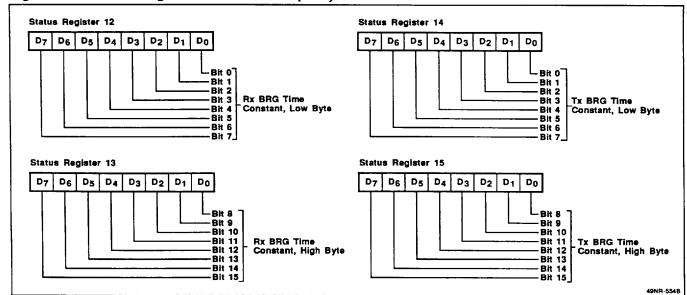

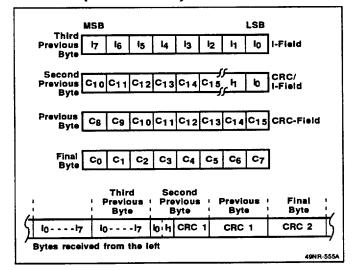

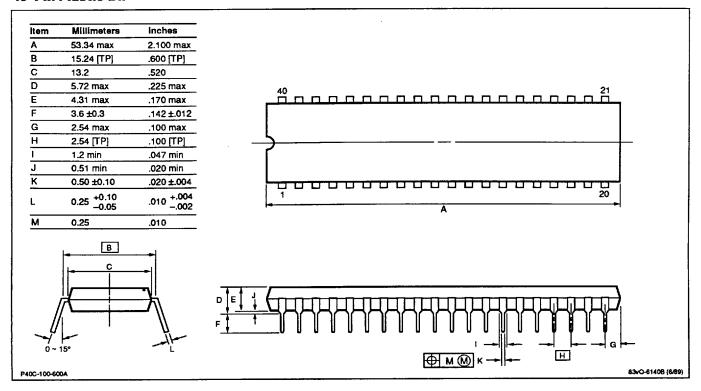

27