#### CMOS 4-BIT MICROCONTROLLER

# **TMP47C440BN** TMP47C440BF

The 47C440B is high speed and high performance 4-bit single chip micro computers, integrating the 8-bit A/D converter and watchdog timer based on the TLCS-47 series.

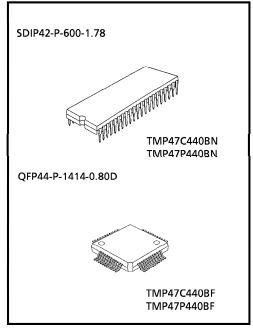

| PART No.    | ROM          | RAM         | PACKAGE            | OTP version |

|-------------|--------------|-------------|--------------------|-------------|

| TMP47C440BN | 4006 0 bit   | 256 4 bit   | SDIP42-P-600-1.78  | TMP47P440VN |

| TMP47C440BF | 4096 × 8-bit | 256 × 4-bit | QFP44-P-1414-0.80D | TMP47P440VF |

#### **FEATURES**

◆4-bit single chip microcomputer

$\blacklozenge$ Instruction execution time : 1.9  $\mu$ s (at 4.2 MHz)

♦90 basic instructions

Table look-up instructions

5-bit to 8-bit data conversion instruction

◆Subroutine nesting : 15 levels max.

♦6 interrupt sources (External: 2, Internal: 4)

All sources have independent latches each, and multiple interrupt control is available

◆I/O port (34 pins)

Input 2 ports 5 pins Output 2 ports 8 pins 6 ports 1/0 21 pins

◆Interval timer

◆Two 12-bit Timer/Counters

Timer, event counter, and pulse width measurement mode

◆Watchdog Timer

◆Serial Interface with 4-bit buffer

External/internal clock, leading/trailing edge shift mode

- ◆8-bit successive approximate type A/D converter

- With sample and hold

- 8 analog inputs

- Converting time : 48 μs (4 MHz)

◆High current outputs

LED direct drive capability (typ. 20 mA × 8 bits)

♦ Hold function

Battery/Capacitor back-up

◆Real Time Emulator: BM47214A

980901EBP1

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to foreign exchange and foreign trade laws.

The information contained herein is presented only as a quide for the applications of our products. No responsibility

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

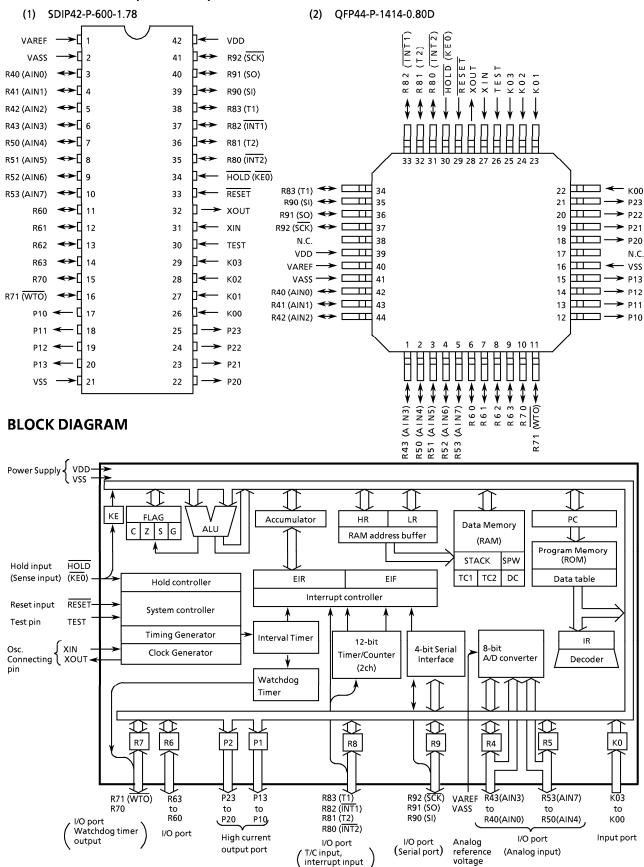

## **PIN ASSIGNMENTS (TOP VIEW)**

# **PIN FUNCTION**

| PIN NAME                                                         | Input / Output | FUNCTIONS                                                                                                            |                                        |  |  |  |

|------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------|--|--|--|

| K03 to K00                                                       | Input          | 4-bit input port                                                                                                     |                                        |  |  |  |

| P13 to P10                                                       |                | 4-bit output port with latch.                                                                                        |                                        |  |  |  |

| P23 to P20                                                       | Output         | 8-bit data are output by the 5-bit to 8-bit dat                                                                      | a conversion instruction [OUTB @HL].   |  |  |  |

| R43 (AIN3)<br>to<br>R40 (AIN0)<br>R53 (AIN7)<br>to<br>R50 (AIN4) | I/O (Input)    | 4-bit I/O port with latch.  When used as input port or analog input, the latch must be set to "1".                   | A / D converter analog input           |  |  |  |

| R63 to R60                                                       | I/O            | 4-bit I/O port with latch                                                                                            |                                        |  |  |  |

| R71 (WTO)                                                        | I/O (Output)   | 2-bit I/O port with latch. When used as input port or watchdog                                                       | Watchdog timer output                  |  |  |  |

| R70                                                              | I/O            | timer output, the latch must be set to "1".                                                                          |                                        |  |  |  |

| R83 (T1)                                                         |                | 4-bit I/O port with latch.                                                                                           | Timer/Counter 1 external input         |  |  |  |

| R82 (ĪNT1)                                                       | 1/0 (1         | When used as input port, external interrupt input pin, or timer/counter external input pin, the latch must be set to | External interrupt 1 input             |  |  |  |

| R81 (T2)                                                         | I/O (Input)    |                                                                                                                      | Timer/Counter 2 external input         |  |  |  |

| R80 (ĪNT2)                                                       |                | "1".                                                                                                                 | External interrupt 2 input             |  |  |  |

| R92 ( <del>SCK</del> )                                           | I/O(I/O)       | 3-bit I/O port with latch.                                                                                           | Serial clock I/O                       |  |  |  |

| R91 (SO)                                                         | I/O (Output)   | When used as input port or serial port, the                                                                          | Serial data output                     |  |  |  |

| R90 (SI)                                                         | I/O (Input)    | latch must be set to "1".                                                                                            | Serial data input                      |  |  |  |

| XIN                                                              | Input          | Resonator connecting pins.                                                                                           |                                        |  |  |  |

| хоит                                                             | Output         | For inputting external clock, XIN is used and 2                                                                      | XOUT is opened.                        |  |  |  |

| RESET                                                            | Input          | Reset signal input                                                                                                   |                                        |  |  |  |

| HOLD (KEO)                                                       | Input (Input)  | HOLD request/release signal input                                                                                    | Sense input                            |  |  |  |

| TEST                                                             | Input          | Test pin for out-going test. Be opened or fixe                                                                       | ed to low level.                       |  |  |  |

| VDD                                                              |                | + 5V                                                                                                                 |                                        |  |  |  |

| VSS                                                              |                | 0V (GND)                                                                                                             |                                        |  |  |  |

| VAREF                                                            | Power supply   | A/D converter analog reference voltage (High                                                                         | h)                                     |  |  |  |

| VASS                                                             |                | A/D converter analog reference voltage (Low                                                                          | ······································ |  |  |  |

#### **OPERATIONAL DESCRIPTION**

Conserning the 47C440B, the hardware configuration and operation of hardwares are described. As the description is porvided with priority on those parts deffering from the 47C400B, the technical data sheets for the 47C400B shall also be referred to.

#### 1. SYSTEM CONFIGURATION

**◆INTERNAL CPU FUNCTION**

They are the same as those of the 47C440B.

- **◆**PERIPHERAL HARDWARE FUNCTION

- ① I/O Port

- 2 Interval Timer

- 3 Timer/Counters (TC1, TC2)

- 4 A/D Converter

- **⑤** Wachdog Timer

- 6 Serial Interface

The description has been provided with priority on functions (①, ④ and ⑤) added to and changed from the 47C400B.

## 2. PERIPHERAL HARDWARE FUNCTION

#### 2.1 Ports

The 47C440B has 10 I/O ports (34 pins) each as follows:

① KO ; 4-bit input ② P1, P2 ; 4-bit output

3 R4, R5 ; 4-bit input/output (shared with the A/D converter analog inputs)

4 R6 ; 4-bit input/output

⑤ R7 ; 2-bit input/output (shared with the watchdog timer output)

6 R8 ; 4-bit input/output(shared with external interrupt request input and

timer/counter input)

⑦ R9 ; 3-bit input/output (shared with serial port)

This section describes ports of ③ and ⑤ which are changed from the 47C400B.

Table 2-1 lists the port address assignments and the I/O instructions that can access the ports.

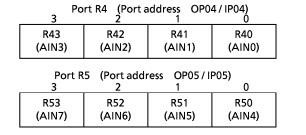

#### (1) Ports R4 (R43-R40), R5 (R53-R50)

Ports R4 and R5 are 4-bit I/O ports with latch shared by the analog inputs for A/D converter. When used as an input ports or analog inputs, the latch should be set to "1". If other port is used as an output, be careful not to execute the output instruction for any port during A/D conversion in order to keep accuracy of conversion. The latch is initialized to "1" and analog input is selected R40 (AINO) pin during reset.

Figure 2-1. Port R4 and R5

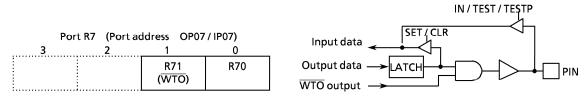

# (2) Port R7 (R71, R70)

Port R7 is 2-bits I/O port with latch. R71 pin is shared by the watchdog timer output. To use R71 pin for the watchdog timer output, the latch should be set to "1". The latch is initialized to "1" during reset. R70 pin is normal I/O pin. R72 and R73 pins do not exist actually but "1" is read when an input instruction is executed.

Figure 2-2. Port R7

Table 2-1. Port Address Assignments and Available I/O Instructions

| Port            |                              | Port                            |           |            | andul      | Input Undundandul | lion      |             | - 1   |

|-----------------|------------------------------|---------------------------------|-----------|------------|------------|-------------------|-----------|-------------|-------|

| Address         |                              |                                 | IN %p, A  | OUT A,%p   | Ė          | į                 | SET %p, b | TEST %p, b  | SET @ |

| (**)            | Input (IP**)                 | Output (OP**)                   | IN %p,@HL | ООТ @НГ,%р | UUI #K, %p | OU IB WHL         | CLR %p, b | теѕтР %р, b |       |

| H00             | K0 input port                |                                 | 0         | 1 (        | Ι(         | ۱ (               | 1 (       | 0(          | i     |

| -0              | P1 output latch              | P1 output port                  | )<br>     | )<br>'C    | )<br>(     | (Note 2)          | -         | ) (         | I     |

| 05              | P2 output latch              | P2 output port                  | 0         | 0          | 0          | C                 | •         | Э           | l     |

| 03              | -                            | ſ                               | 1 (       | Ι(         | 1 (        | ı                 | ۱ (       | ۱ (         | ۱(    |

| 04              | R4 input port (Analog input) | R4 output port                  | )(        | )(         | ) C        | 1                 | )(        | )(          | )(    |

| 02              | R5 input port (Analog input) | R5 output port                  | 0         | 0(         | )<br>(     | ı                 | )(        | )(          | )(    |

| 90              | R6 input port                | R6 output port                  | )(        | )(         | Э(         | ı                 | )(        | )(          | )(    |

| 02              | R7 input port                | R7 output port                  | )(        | )(         | Э(         | 1                 | Э(        | )(          | O     |

| 80              | R8 input port                | R8 output port                  | 0         | Ċ          | ) (        | 1                 | Э(        | )(          | I     |

| 60              | R9 input port                | R9 output port                  | 0         | 0          | 0          | ı                 | C         | O .         | ı     |

| ₹0              |                              |                                 | ı         | ı          | ı          | 1                 | ı         | ı           | ı     |

| 08              |                              |                                 | 1         | ı          | ı          | ı                 | ı         | 1 (         | ı     |

| S               | A/D status input             |                                 | 0         | ı          | 1          | ı                 | ı         | 0           | ı     |

| 00              | A / D converted value        | 1                               | 0         | 1          | ı          | ı                 | ı         | 1 (         | ı     |

| 90              | SIO, Hold status             |                                 | 0         | 1          | 1 (        | ı                 | Į         | )           | I     |

| 0F              | Serial recieve buffer        | Serial transmit buffer          | 0         | 0          | 0          | 1                 | 1         | 1           | 1     |

| 10 <sub>H</sub> | Undefined                    | Hold operating mode control     | ı         | 0          | ı          | 1                 | İ         | 1           | ı     |

| =               | Undefined                    |                                 | 1         | l          | ı          | ı                 | ı         | ı           | ı     |

| 12              | Undefined                    | A / Danalog input selector      | ı         | 0          | •          | ı                 | ı         | 1           | ı     |

| 13              | Undefined                    | A/D start register              | 1         | 0          | 1          | ı                 | ı         | ı           | ı     |

| 14              | Undefined                    |                                 | 1         | 1 (        | ı          | ı                 | ı         | ı           | l     |

| 15              | Undefined                    | Watchdog Timer control          | ı         | 0          | 1          | ı                 | 1         | ı           | ı     |

| 16              | Undefined                    |                                 | 1         | ١          | 1          | ı                 | ı         | ı           | i     |

| 17              | Undefined                    |                                 | 1         | ı          | 1          | 1                 | ı         | ı           | I     |

| 18              | Undefined                    |                                 | I         | 1          | ı          | ı                 | ı         | 1           | ı     |

| 19              | Undefined                    | Interval Timer intrrupt control | 1         | 0          | ı          | ı                 | ļ         | ı           | İ     |

| 4               | Undefined                    |                                 | 1         | ı          | 1          | ı                 | l         | 1           | ı     |

| 8               | Undefined                    |                                 | 1         | 1          | ı          | ı                 | ı         | ı           | ı     |

| 7               | Undefined                    | Timer/Counter 1 control         | ١         | 0          | ı          | 1                 | ı         | ı           | ı     |

| ₽               | Undefined                    | Timer/Counter 2 control         | 1         | 0          | ı          | ı                 | ı         | ı           | ı     |

| #               | Undefined                    |                                 | 1         | 1 (        | ı          | 1                 | 1         | 1           | I     |

| #               | Undefined                    | Serial interface control        | 1         |            | -          | 1                 | 1         |             |       |

"---" means the reserved state. Unavailable for the user programs. Note 1. Note 2.

The 5-bit to 8-bit data conversion instruction [OUTB @HL], automatic access to ports P1 and P2.

#### 2.2 A/D Converter

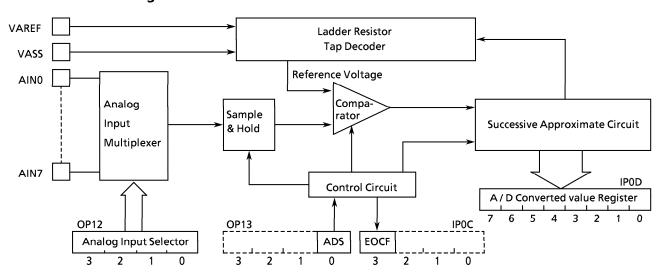

The 47C440B has a 8-bit successive approximate type A/D converter and is capable of processing 8 analog inputs.

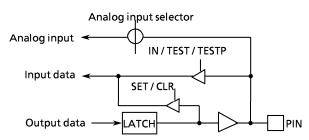

# 2.2.1 Circuit configuration

Figure 2-3. Block Diagram of A/D Converter

#### 2.2.2 Control of A/D converter

The operation of A/D converter is controlled by a command register (OP12, OP13, IP0C, IP0D).

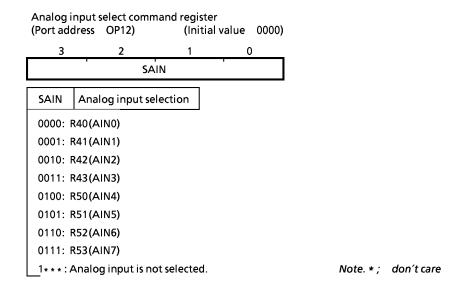

(1) Analog input selector (OP12)

Analog inputs (AIN0 through AIN7) are selected by values of this register.

Figure 2-4. Analog input selector

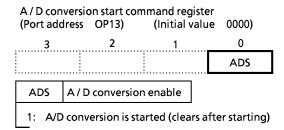

### (2) Start of A/D conversion (OP13)

A/D conversion is started when ADS is set to "1". After the conversion is started, ADS is cleared by hardware. If the restart is requested during the conversion, the conversion is started again at the time. Analog input voltage is hold by the sample hold circuit.

Figure 2-5. A/D conversion start register

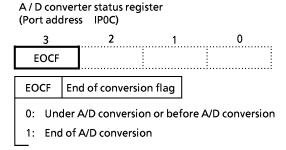

#### (3) A/D converter and frag (IPOC)

End of Conversion Flag (EOCF) is a single bit flag showing the end of conversion and is set to "1" when conversion ended. When both upper 4 bits and lower 4 bits of a converted value are read or A/D conversion is started, EOCF is cleared to "0".

Figure 2-6. A/D converter status register

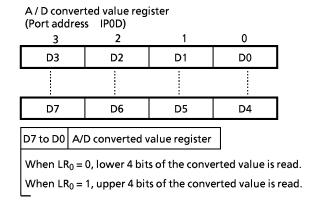

## (4) A/D converted value register (IP0D)

An A/D converted value is read by accessing port address IPOD. An A/D converted value is read by splitting into upper 4 bits and lower 4 bits by a value of  $LR_0$  (LSB of the L registers).

Figure 2-7. A/D converted value register

#### 2.2.3 How to use A/D converter

Apply positive of analog reference voltage to the VAREF pin and negative to the VASS pin. The A/D conversion is carried out by splitting reference voltage between VAREF and VASS to bit corresponding voltage by a ladder resistor and making a judgement by comparing it with analog input voltage.

#### (1) Start of A / D conversion

Prior to conversion, select one of the analog input AIN0 through AIN7 by the analog input selector. Place output of the analog input, which is to be A/D converted, in the high impedance state by setting "1". If other port is used as an output, be careful not to execute the output instruction for any port during conversion in order to keep accuracy of conversion.

A/D conversion is started by setting ADS (bit 1 of the A/D conversion start register). When conversion ends after 24 instruction cycles, EOCF showing the end of conversion is set to "1". Analog input voltage is sampled during the following 2 instruction cycles after setting conversion enable.

Note. The sample and hold circuit has capacitor ( $C_A = 12 \text{ pF typ.}$ ) with resister ( $RA = 5 \text{ k}\Omega$  typ.). See I/O circuitry table. This capacitor should be charged or discharged within 2 instruction cycles.

#### (2) Reading of an A/D converted value

After the end of conversion, read an A/D converted value is read by splitting into lower 4 bits and upper 4 bits by the A/D converted value register (IPOD).

Lower 4 bits of the A/D converted value can be read when  $LR_0 = 0$  and upper 4 bits when  $LR_0 = 1$ . Usually an A/D converted value is stored in RAM by an instruction [IN %p, @HL]. Further, if an A/D converted value is read during the conversion, it becomes an indefinite value.

# (3) A / D conversion with HOLD operation

When the HOLD operation is started during the conversion, the conversion is terminated and an A/D converted value becomes indefinite. Therefore, EOCF is kept clear to "0" after release from the HOLD operation. However, if the HOLD operation is started after the end of A/D conversion (after EOCF has been set), A/D converted value and status of EOCF are held.

Example: Selecting analog input (AIN3), starting A/D conversion, monitoring EOCF and storing lower 4 bits and upper 4 bits of a converted value to RAM [10<sub>H</sub>] and RAM [11<sub>H</sub>] respectively.

|        | LD   | A, #3H     | ; | Selects analog input (AIN3)          |

|--------|------|------------|---|--------------------------------------|

|        | OUT  | A, %OP12   |   |                                      |

|        | LD   | A, #1H     | ; | Start of A/D conversion              |

|        | OUT  | A, %OP13   |   |                                      |

| SLOOP: | TEST | %IPOC, 3   | ; | To wait until EOCF goes to "1"       |

|        | В    | SL00P      |   |                                      |

|        | LD   | HL, #10H   | ; | HL ← 10 <sub>H</sub>                 |

|        | IN   | %IPOD, @HL | ; | RAM $[10_H] \leftarrow Lower 4 bits$ |

|        | INC  | L          | ; | Increment of L registers             |

|        | IN   | %IPOD, @HL | ; | RAM $[11_H] \leftarrow Upper 4 bits$ |

|        |      |            |   |                                      |

# 2.3 Watchdog Timer (WDT)

The purpose of the watchdog timer is to detect the malfunction (ranaway) of program due to external noise or other causes and return the operation to the normal condition.

The watchdog timer output is output to R71 must be set to "1". Further, during reset, the output latch of R71 is set to "1", and the watchdog timer becomes disable state.

The initialization at time of runaway will become possible when the  $\overline{\text{WTO}}$  pin and  $\overline{\text{RESET}}$  pin are connected each other.

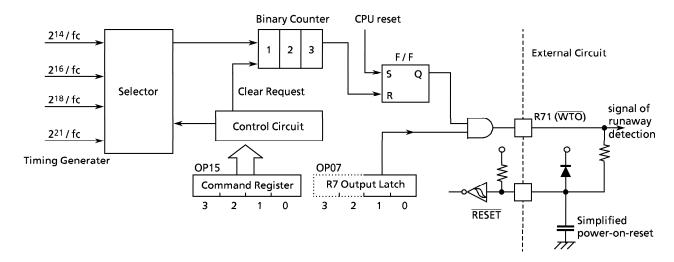

## 2.3.1 Configuration of Watchdog Timer

The watchdog timer consists of 3-stage binary counter, flip-flop (F/F), and its control circuit. The F/F is set to "1" during reset, and cleared to "0" at the rising edge of the binary counter output.

Figure 2-8. Watchdog Timer

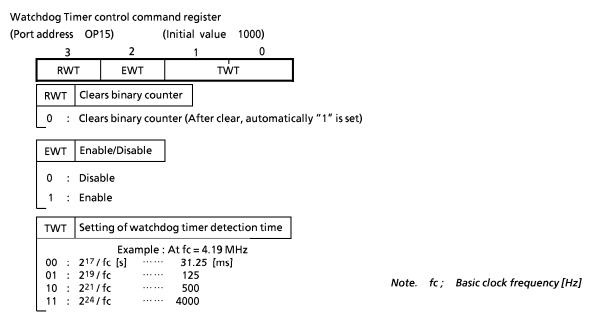

## 2.3.2 Control of watchdog timer

The watchdog timer is controlled by the command register (OP15). This command register is initialized to " $0000_B$ " during reset. The following are procedure to detect the malfunction (runaway) of CPU by the watchdog timer.

- ① At first, detection time of the watchdog timer should be set and binary counter should be cleared.

- ② The watchdog timer should be become enable.

- ③ Binary counter must be cleared before the detection time of the watchdog timer. When the runaway of CPU is taken place for some reason and binary counter is not cleared, the F/F is cleared to "0" at the rising edge of the binary counter and signal of runaway detection is become active (WTO output is "L").

Figure 2-9. Command Register

Example: To set the watchdog detection time (221 / fc[s]). And to enable the watchdog timer.

```

LD

A, #0010B

; OP15 \leftarrow 0010<sub>B</sub>

(Sets WDT detection time. Clears binary counter)

OUT

A, %OP15

A, #0110B

LD

; OP15 ← 0110<sub>B</sub> (Enables WDT)

OUT

A, %OP15

Within WDT

detection time

; OP15 ← 0110<sub>B</sub> (Clears binary counter)

LD

A, #0110B

OUT

A, %OP15

```

Note. RWT can be operated only by clearing to "0". Note that both EWT (Enable Watchdog Timer) and RWT should not be set to "1" at the same time.

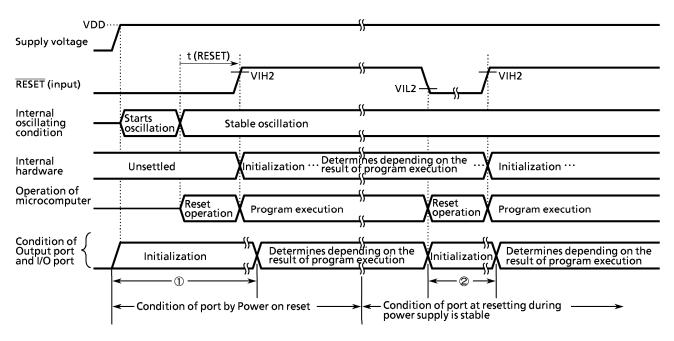

# **Port Condition by RESET Operation**

The transition of Port condition by RESET operation is shown as below.

Figure 2-10. Port condition by Reset operation

Note 1: t(RESET) > 24/fc

Note 2: VIL2: Stands for low level input voltage of RESET pin.

VIH2: Stands for high level input voltage of RESET pin.

Note 3: The term from power on reset to the time program is executed (above ①) and also the term starting from reset operation during power supply is stable to the program is executed (above ②), the port is on the initial condition. The initial condition of Port differs from I/O circuit by each port, refer to the section of "INPUT/OUTPUT CIRCUITRY". Thus, when using Port as an output pin, in the term of the above ① and ②, the voltage level on the signal that connects with the output pin of Port to the input pin of external application circuit should be determined by the external circuitry such as pull-up resistor and / or pull-down resistor.

# **INPUT/OUTPUT CIRCUITRY**

- (1) Control pins

- The input/output circuitries of the 47C440B control pins are similar to that of the 47C400B.

- (2) I/O Ports

The input/output circuitries of the 47C440B I/O ports are shown below, any one of the circuitries can be chosen by a code (SA-SC) as a mask option.

| PORT                 | I/O    | INPL                                                | JT/OUTPUT CIRC    | CUITRY and CC     | DDE                                                                                                                     | REMARKS                                                                                                                                         |

|----------------------|--------|-----------------------------------------------------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                      |        | SA                                                  | SE                |                   | sc                                                                                                                      |                                                                                                                                                 |

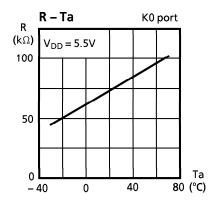

| К0                   | Input  | <\-\                                                | R <sub>IN</sub> W | R <sub>IN</sub> & | Pull-up / pull-down resistor $R_{\text{IN}} = 70 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$ |                                                                                                                                                 |

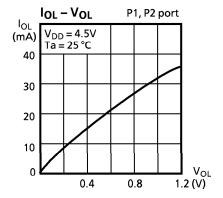

| P1<br>P2             | Output |                                                     |                   | VDD               |                                                                                                                         | Sink open drain output Initial "Hi-Z" High current I <sub>OL</sub> = 20 mA (typ.)                                                               |

| R4<br>R5<br>R6<br>R7 | 1/0    | R4, R5  AIN selector  C <sub>A</sub> R <sub>A</sub> | <b>■</b>          | R6, R7            | VDD O                                                                                                                   | Sink open drain output Initial "Hi-Z" $R = 1 k\Omega \text{ (typ.)}$ Analog input $R_A = 5 k\Omega \text{ (typ.)}$ $C_A = 12 \text{ pF (typ.)}$ |

| R8<br>R9             | 1/0    |                                                     | VDD O             | <b>R</b> R        |                                                                                                                         | Sink open drain output Initial "Hi-Z"  Hysteresis input  R = 1 kΩ (typ.)                                                                        |

# **ELECTRICAL CHARACTERISTICS**

ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0V)$

| PARAMETER                                   | SYMBOL            | PINS         | RATING                         | UNIT |

|---------------------------------------------|-------------------|--------------|--------------------------------|------|

| Supply Voltage                              | V <sub>DD</sub>   |              | – 0.3 to 6.5                   | V    |

| Input Voltage                               | V <sub>IN</sub>   |              | - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |

| Output Voltage                              | V <sub>OUT</sub>  |              | - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |

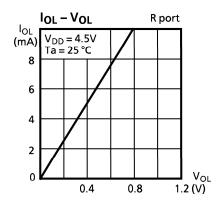

|                                             | I <sub>OUT1</sub> | Ports R      | 3.2                            |      |

| Output Current (Per 1 pin)                  | lOUT2             | Ports P1, P2 | 30                             | mA   |

| Output Current (Total)                      | Σl <sub>OUT</sub> | Ports P1, P2 | 120                            | mA   |

| Power Dissipation $[T_{opr} = 70^{\circ}C]$ | PD                |              | 600                            | mW   |

| Soldering Temperature (time)                | Tsld              |              | 260 (10 s)                     | °C   |

| Storage Temperature                         | Tstg              |              | – 55 to 125                    | °C   |

| Operating Temperature                       | Topr              |              | – 30 to 70                     | °C   |

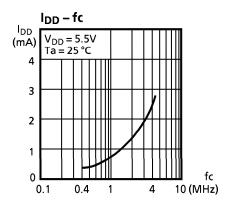

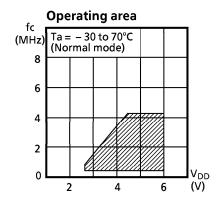

RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

| PARAMETER          | SYMBOL           | PINS                    | CONDITIONS              | Min.                | Max.                                                                  | UNIT |

|--------------------|------------------|-------------------------|-------------------------|---------------------|-----------------------------------------------------------------------|------|

|                    |                  |                         | fc = 6.0 MHz            | 4.5                 |                                                                       |      |

| Supply Voltage     | $V_{DD}$         |                         | fc = 4.2 MHz            | 2.7                 | 5.5                                                                   | v    |

|                    |                  |                         | In the HOLD mode        | 2.0                 |                                                                       |      |

|                    | V <sub>IH1</sub> | Except Hysteresis Input |                         | $V_{DD} \times 0.7$ |                                                                       |      |

| Input High Voltage | V <sub>IH2</sub> | V <sub>DD</sub> ≧ 4.5 V | V <sub>DD</sub>         | v                   |                                                                       |      |

|                    | V <sub>IH3</sub> |                         | V <sub>DD</sub> <4.5 V  | $V_{DD} \times 0.9$ | $V_{DD}$ $V_{DD} \times 0.3$ $V_{DD} \times 0.25$ $V_{DD} \times 0.1$ |      |

|                    | V <sub>IL1</sub> | Except Hysteresis Input |                         |                     |                                                                       |      |

| Input Low Voltage  | $V_{IL2}$        | Hysteresis Input        | V <sub>DD</sub> ≧ 4.5 V | 0                   | V <sub>DD</sub> × 0.25                                                | v    |

|                    | V <sub>IL3</sub> |                         | V <sub>DD</sub> <4.5 V  |                     | V <sub>DD</sub> × 0.1                                                 |      |

| Clock Frequency    | fc               | XIN, XOUT               |                         | 0.4                 | 6.0                                                                   | MHz  |

Note. Input voltage  $V_{IH3}$ ,  $V_{IL3}$ : in the HOLD mode

D.C. CHARACTERISTICS

$(V_{SS} = 0V, T_{opr} = -30 \text{ to } 70 \text{ °C})$

| PARAMETER                              | SYMBOL           | PINS                           | CONDITIONS                                     | Min. | Тур. | Max. | UNIT |

|----------------------------------------|------------------|--------------------------------|------------------------------------------------|------|------|------|------|

| Hysteresis Voltage                     | V <sub>HS</sub>  | Hysteresis Input               |                                                | -    | 0.7  | _    | V    |

| Input Current                          | I <sub>IN1</sub> | Port K0, TEST, RESET, HOLD     | V <sub>DD</sub> = 5.5V,                        |      |      |      |      |

| Imput current                          | I <sub>IN2</sub> | Ports R (open drain)           | V <sub>IN</sub> = 5.5V / 0V                    |      | _    | ± 2  | μΑ   |

| Low Input Current                      | I <sub>IL</sub>  | Ports R (push-pull)            | $V_{DD} = 5.5V, \ V_{IN} = 0.4V$               | _    | _    | -2   | mA   |

| 1                                      | R <sub>IN1</sub> | Port K0 with pull-up/pull-down |                                                | 30   | 70   | 150  | kΩ   |

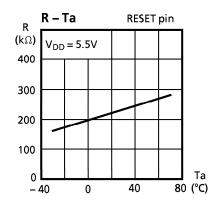

| Input Resistance                       | R <sub>IN2</sub> | RESET                          |                                                | 100  | 220  | 450  | K42  |

| Output Leakage Current                 | I <sub>LO</sub>  | Ports R (open drain)           | $V_{DD} = 5.5V, \ V_{OUT} = 5.5V$              |      | _    | 2    | μA   |

| Output Low Voltage                     | V <sub>OL2</sub> | Except XOUT, ports P           | $V_{DD} = 4.5V$ , $I_{OL} = 1.6 \text{ mA}$    | _    | _    | 0.4  | ٧    |

| Low output Current                     | I <sub>OL1</sub> | Ports P1, P2                   | V <sub>DD</sub> = 4.5V, V <sub>OL</sub> = 1.0V | 1    | 20   | _    | mA   |

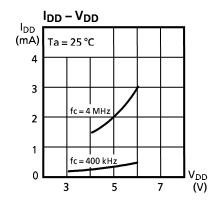

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>  |                                | V <sub>DD</sub> = 5.5V, fc = 4 MHz             | _    | 3    | 6    | mA   |

| Supply Current<br>(in the HOLD mode)   | I <sub>DDH</sub> |                                | V <sub>DD</sub> = 5.5V                         | _    | 0.5  | 10   | μΑ   |

- Note 1. Typ. values show those at  $T_{opr} = 25 \,^{\circ}\text{C}$ ,  $V_{DD} = 5V$ .

- Note 2. Input Current  $I_{IN1}$ ; The current through resistor is not included, when the input resistor (pull-up/pull-down) is contained.

- Note 3. Supply Current  $I_{DD}$ ,  $I_{DDH}$ ;  $V_{IN} = 5.3V/0.2V$ The K0 port is open when the input resistor is contained. The voltage applied to the R port is within the valid range.

A / D CONVERSION CHARACTERISTICS

$(T_{opr} = -30 \text{ to } 70 \,^{\circ}\text{C})$

| PARAMETER                      | SYMBOL             | CONDITIONS                           | Min.                  | Тур. | Max.              | UNIT |

|--------------------------------|--------------------|--------------------------------------|-----------------------|------|-------------------|------|

| Analog Reference Voltage       | V <sub>AREF</sub>  |                                      | V <sub>DD</sub> – 1.5 | _    | V <sub>DD</sub>   | .,   |

| Analog Reference voltage       | V <sub>ASS</sub>   |                                      | V <sub>SS</sub>       | _    | 1.5               | V    |

| Analog Reference Voltage Range | △V <sub>AREF</sub> | V <sub>AREF</sub> - V <sub>ASS</sub> | 2.5                   | _    | _                 | >    |

| Analog Input Voltage           | V <sub>AIN</sub>   |                                      | V <sub>ASS</sub>      | _    | V <sub>AREF</sub> | <    |

| Analog Supply Current          | I <sub>REF</sub>   |                                      | _                     | 0.5  | 1.0               | mA   |

| Nonlinearity Error             |                    | 504.44                               | _                     | _    | ± 1               |      |

| Zero Point Error               |                    | $V_{DD} = 5.0V, V_{SS} = 0.0V$       | _                     | _    | ± 1               |      |

| Full Scale Error               |                    | V <sub>AREF</sub> = 5.000V           | _                     | _    | ± 1               | LSB  |

| Total Error                    |                    | $V_{ASS} = 0.000V$                   | _                     | _    | ± 2               |      |

TOSHIBA

A. C. CHARACTERISTICS

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 5.5V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

| PARAMETER                    | SYMBOL           | CONDITIONS          | Min.                      | Тур. | Max. | UNIT |

|------------------------------|------------------|---------------------|---------------------------|------|------|------|

| Instruction Cycle Time       | t <sub>cy</sub>  |                     | 1.9                       | _    | 20   | μs   |

| High level Clock pulse Width | t <sub>WCH</sub> | Estamal dedumenda   |                           |      |      |      |

| Low level Clock pulse Width  | t <sub>WCL</sub> | External clock mode | 80                        | _    | _    | ns   |

| A/D Sampling Time            | t <sub>AIN</sub> | fc = 4 MHz          | _                         | 4    | _    | μs   |

| Shift Data Hold Time         | t <sub>SDH</sub> |                     | 0.5 t <sub>cy</sub> – 300 | _    | _    | ns   |

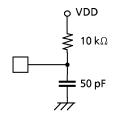

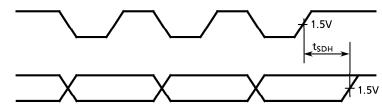

Note. Shift Data Hold Time

External circuit for SCK pin and SO pin

Serial port (completion of transmission)

SCK SO

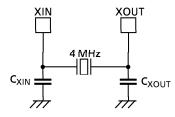

**RECOMMENDED OSCILLATING CONDITIONS**

$(V_{SS} = 0V, V_{DD} = 4.5 \text{ to } 5.5V, T_{opr} = -30 \text{ to } 70^{\circ}\text{C})$

(1) 4MHz

**Ceramic Resonator**

CSA4. 00MG (MURATA)

$C_{XIN} = C_{XOUT} = 30 \text{ pF}$

KBR-4. 00MS (KYOCERA)

$C_{XIN} = C_{XOUT} = 30 pF$

**Crystal Oscillator**

204B-6F 4. 0000 (TOYOCOM)  $C_{XIN} = C_{XOUT} = 20 pF$

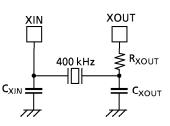

(2) 400kHz

**Ceramic Resonator**

CSB400B (MURATA)

KBR-400B (KYOCERA)

$C_{XIN} = C_{XOUT} = 220 \text{ pF}, R_{XOUT} = 6.8 \text{ k}\Omega$

$C_{XIN} = C_{XOUT} = 100 \text{ pF, } R_{XOUT} = 10 \text{ k}\Omega$

## **TYPICAL CHARACTERISTICS**