#### **Features**

- IBM PowerPC<sup>®</sup> 405 32-bit RISC processor core operating up to 266 MHz

- Memory Management Unit

- 16KB instruction and 8KB data caches

- Multiply-Accumulate (MAC) function, including fast multiply unit

- Programmable Timers

- Synchronous DRAM (SDRAM) interface operating up to 133MHz

- 32-bit interface for non-ECC applications

- 40-bit interface serves 32 bits of data plus 8 check bits for ECC applications

- · External Peripheral Bus

- Flash ROM/Boot ROM interface

- Direct support for 8-, 16-, or 32-bit SRAM and external peripherals

- Up to eight devices

- External Mastering supported

- DMA support for external peripherals, internal UART and memory

- Scatter-gather chaining supported

- Four channels

- Programmable Interrupt Controller supports interrupts from a variety of sources

- Supports 7 external and 10 internal interrupts

- Edge triggered or level-sensitive

- Positive or negative active

- Non-critical or critical interrupt to processor core

- Programmable critical interrupt priority ordering

- Two serial ports (16550 compatible UART)

- One IIC interface

- · General Purpose I/O (GPIO) available

- · Supports JTAG for board level testing

- Internal Processor Local Bus (PLB) runs at SDRAM interface frequency

### Description

The IBM PowerPC 405CR (PPC405CR) is a 32-bit RISC embedded controller. High performance, peripheral integration, and low cost make the device ideal for wired communications, network printers, and other computing applications.

This device is an easy upgrade for systems based on PowerPC 403xx embedded processors, while providing a base for custom chip designs.

The controller is powered by a PPC405 embedded core. This core tightly couples a 266 MHz CPU, MMU, instruction and data caches, and debug logic. Fine-tuning of the core reduces data transfer overhead, minimizes pipeline stalls, and improves performance.

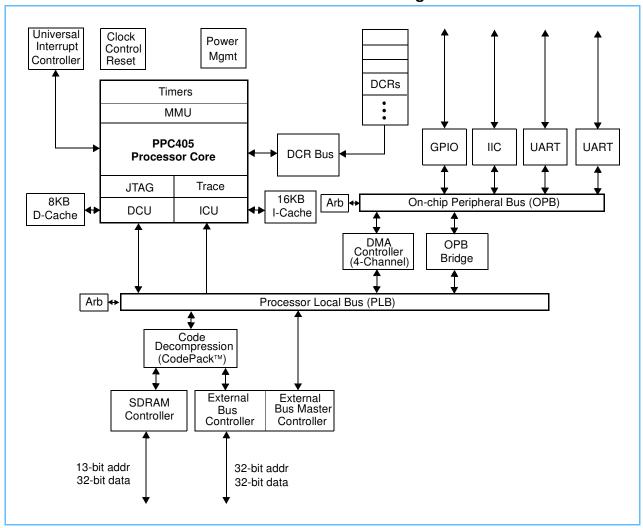

The PPC405CR employs the IBM CoreConnect<sup>™</sup> bus architecture. This architecture, as implemented on the PPC405CR, consists of a 64-bit, 133-MHz Processor Local Bus (PLB) and a 32-bit, 66-MHz On-Chip Peripheral Bus (OPB). High-performance peripherals attach to the PLB and less performance-critical peripherals attach to the OPB.

Technology: IBM CMOS SA-12E 0.25  $\mu$ m (0.18  $\mu$ m L<sub>eff</sub>)

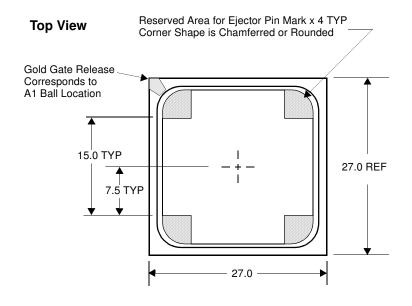

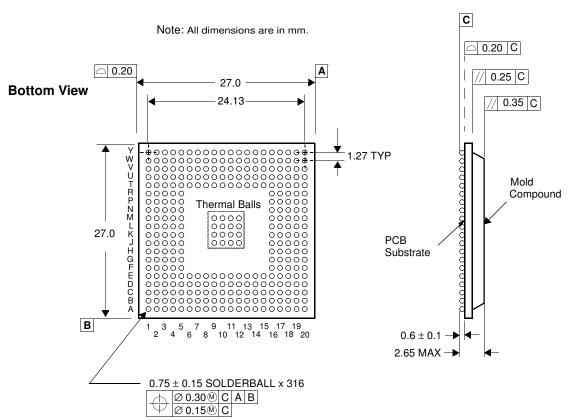

Package: 27mm, 316-ball enhanced plastic ball grid array (E-PBGA)

Power (estimated): Typical 0.9W, Maximum 2.0W at 200MHz.

| Contents                                              |   |

|-------------------------------------------------------|---|

| Ordering, PVR, and JTAG Information                   | 1 |

| Address Map Support                                   | 3 |

| SDRAM Memory Controller                               | 7 |

| External Peripheral Bus Controller (EBC)              | 7 |

| DMA Controller                                        | 3 |

| UART                                                  | 3 |

| IIC Bus Interface                                     | 3 |

| General Purpose IO (GPIO) Controller                  | ) |

| Universal Interrupt Controller (UIC)                  | ) |

| JTAG                                                  | ) |

| Pin Lists1                                            | l |

| Signal Descriptions                                   | l |

| Spread Spectrum Clocking                              | 1 |

| Strapping                                             | ) |

| Figures                                               |   |

| PPC405CR Embedded Controller Functional Block Diagram | 5 |

| 27mm, 316-Ball E-PBGA Package                         | ) |

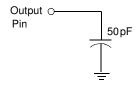

| Timing Waveform                                       | 3 |

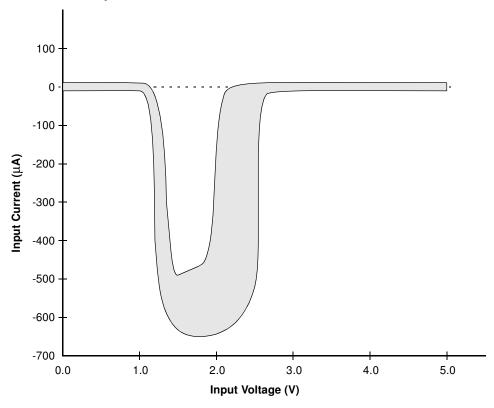

| 5V-Tolerant I/O Input Current                         | ļ |

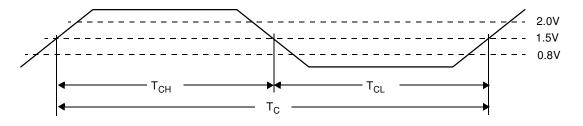

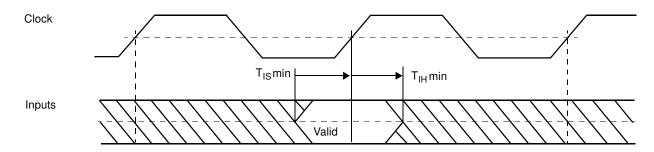

| Input Setup and Hold Waveform                         | 3 |

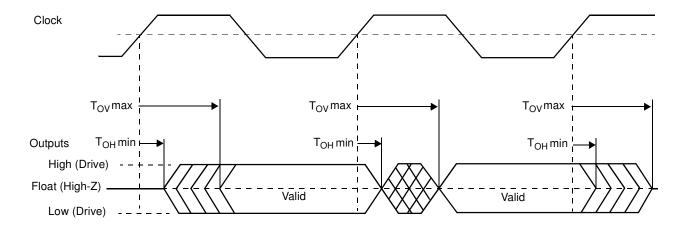

| Output Delay and Float Timing Waveform                | 3 |

|                                                       |   |

# **Tables**

| System Memory Address Map           | 6  |

|-------------------------------------|----|

| DCR Address Map                     | 6  |

| Signals Listed Alphabetically       |    |

| Signals Listed by Ball Assignment   |    |

| Pin Summary                         | 21 |

| Signal Functional Description       | 23 |

| Absolute Maximum Ratings            | 29 |

| Package Thermal Specifications      | 29 |

| Recommended DC Operating Conditions |    |

| Input Capacitance                   |    |

| DC Electrical Characteristics       |    |

| Clocking Specifications             |    |

| Peripheral Interface Clock Timings  |    |

| I/O Specifications—All speeds       |    |

| I/O Specifications—133 and 200MHz   |    |

| I/O Specifications—266MHz           |    |

| Stranning Pin Assignments           | 40 |

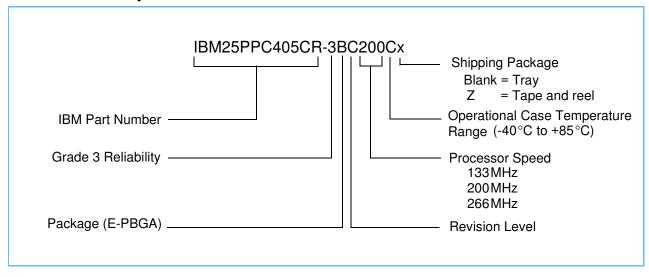

### Ordering, PVR, and JTAG Information

| Product Name | Order Part Number <sup>1</sup> | Processor<br>Frequency | Package          | Rev<br>Level | PVR Value  | JTAG ID    |

|--------------|--------------------------------|------------------------|------------------|--------------|------------|------------|

| PPC405CR     | IBM25PPC405CR-3BC133C          | 133MHz                 | 27mm, 316 E-PBGA | С            | 0x40110145 | 0x42051049 |

| PPC405CR     | IBM25PPC405CR-3BC133CZ         | 133MHz                 | 27mm, 316 E-PBGA | С            | 0x40110145 | 0x42051049 |

| PPC405CR     | IBM25PPC405CR-3BC200C          | 200MHz                 | 27mm, 316 E-PBGA | С            | 0x40110145 | 0x42051049 |

| PPC405CR     | IBM25PPC405CR-3BC200CZ         | 200MHz                 | 27mm, 316 E-PBGA | С            | 0x40110145 | 0x42051049 |

| PPC405CR     | IBM25PPC405CR-3BC266C          | 266MHz                 | 27mm, 316 E-PBGA | С            | 0x40110145 | 0x42051049 |

| PPC405CR     | IBM25PPC405CR-3BC266CZ         | 266MHz                 | 27mm, 316 E-PBGA | С            | 0x40110145 | 0x42051049 |

Note 1: Z at the end of the Order Part Number indicates a tape and reel shipping package. Otherwise, the chips are shipped in a tray.

This section provides the part numbering nomenclature for the PPC405CR. For availability, contact your local IBM sales office.

Each part number contains a revision code. This refers to the die mask revision number and is specified in the part numbering scheme for identification purposes only.

The PVR (Processor Version Register) is software accessible and contains additional information about the revision level of the part. Refer to the *PPC405CR Embedded Processor User's Manual* for details on the register content.

#### **IBM Part Number Key**

### **PPC405CR Embedded Controller Functional Block Diagram**

The PPC405CR is designed using the IBM Microelectronics Blue Logic<sup>®</sup> methodology in which major functional blocks are integrated together to create an application-specific ASIC product. This approach provides a consistent way to create complex ASICs using IBM CoreConnect<sup>™</sup> Bus Architecture.

### **Address Map Support**

The PPC405CR incorporates two simple and separate address maps. The first address map defines the possible use of address regions that the processor can access. The second address map is for Device Configuration Registers (DCRs). The DCRs are accessed by software running on the PPC405CR processor through the use of **mtdcr** and **mfdcr** instructions.

#### System Memory Address Map 4GB System Memory

| Function             | Subfunction                                                                                       | Start Address | End Address | Size   |

|----------------------|---------------------------------------------------------------------------------------------------|---------------|-------------|--------|

|                      | SDRAM and External Peripherals                                                                    | 0x00000000    | 0xEF5FFFF   | 3830MB |

| General Use          | <b>Note:</b> Any of the address ranges listed at right may be use for any of the above functions. | 0xF0000000    | 0xFFFFFFF   | 256 MB |

| Boot-up              | Peripheral Bus Boot <sup>1</sup>                                                                  | 0xFFE00000    | 0xFFFFFFF   | 2MB    |

| Internal Peripherals | UART0                                                                                             | 0xEF600300    | 0xEF600307  | 8B     |

|                      | UART1                                                                                             | 0xEF600400    | 0xEF600407  | 8B     |

|                      | IIC0                                                                                              | 0xEF600500    | 0xEF60051F  | 32B    |

|                      | OPB Arbiter                                                                                       | 0xEF600600    | 0xEF60063F  | 64B    |

|                      | GPIO Controller Registers                                                                         | 0xEF600700    | 0xEF60077F  | 128B   |

#### Notes:

- 1. When peripheral bus boot is selected, Peripheral bank 0 is automatically configured at reset to the address range listed above.

- 2. After the boot process, software may reassign the boot memory region for other uses.

- 3. All address ranges not listed above are reserved.

#### DCR Address Map 4KB Device Configuration Register

| Function                             | Start Address | End Address | Size                   |

|--------------------------------------|---------------|-------------|------------------------|

| Total DCR Address Space <sup>1</sup> | 0x000         | 0x3FF       | 1KW (4KB) <sup>1</sup> |

|                                      |               |             |                        |

| Reserved                             | 0x000         | 0x00F       | 16W                    |

| Memory Controller Registers          | 0x010         | 0x011       | 2W                     |

| External Bus Controller Registers    | 0x012         | 0x013       | 2W                     |

| Decompression Controller Registers   | 0x014         | 0x015       | 2W                     |

| Reserved                             | 0x016         | 0x07F       | 106W                   |

| PLB Registers                        | 0x080         | 0x08F       | 16W                    |

| Reserved                             | 0x090         | 0x09F       | 16W                    |

| OPB Bridge Out Registers             | 0x0A0         | 0x0A7       | 8W                     |

| Reserved                             | 0x0A8         | 0x0AF       | 8W                     |

| Clock, Control, and Reset            | 0x0B0         | 0x0B7       | 8W                     |

| Power Management                     | 0x0B8         | 0x0BF       | 8W                     |

| Interrupt Controller                 | 0x0C0         | 0x0CF       | 16W                    |

| Reserved                             | 0x0D0         | 0x0FF       | 48W                    |

| DMA Controller Registers             | 0x100         | 0x13F       | 64W                    |

| Reserved                             | 0x140         | 0x3FF       | 704W                   |

#### Notes:

<sup>1.</sup> DCR address space is addressable with up to 10 bits (1024 or 1K unique addresses). Each unique address represents a single 32-bit (word) register, or 1 kiloword (KW) (which equals 4 KB).

### **SDRAM Memory Controller**

The PPC405CR Memory Controller core provides a low latency access path to SDRAM memory. A variety of system memory configurations are supported. The memory controller supports up to four logical banks. Up to 256MB per bank are supported, up to a maximum of 1 GB. Memory timings, address and bank sizes, and memory addressing modes are programmable.

#### Features include:

- 11x8 to 13x11 addressing for SDRAM (2- and 4-bank)

- · 32-bit memory interface support

- · Programmable address compare for each bank of memory

- Industry standard 168-pin DIMMS are supported (some configurations)

- 4MB to 256MB per bank

- · Programmable address mapping and timing

- · Auto refresh

- · Page mode accesses with up to 4 open pages

- Power Management (self-refresh)

- Error Checking and Correction (ECC) support

- Standard SEC/DED coverage

- Aligned nibble error detect

- Address error logging

### **External Peripheral Bus Controller (EBC)**

- Supports eight banks of ROM, EPROM, SRAM, Flash memory, or slave peripheral I/O

- · Up to 66 MHz operation

- · Burst and non-burst devices

- 8-, 16-, 32-bit byte-addressable data bus width support

- Programmable 2K clock time-out counter with disable for Ready

- · Programmable access timing per device

- 0-255 wait states for non-burst devices

- 0-31 burst wait states for first access and up to 7 wait states for subsequent accesses

- Programmable CSon, CSoff relative to address

- Programmable OEon, WEon, WEoff (0 to 3 clock cycles) relative to CS

- · Programmable address mapping

- · Peripheral device pacing with external "Ready"

- · External master interface

- Write posting from external master

- Read prefetching on PLB for external master reads

- Bursting capable from external master

- Allows external master access to all non-EBC PLB slaves

- External master can control EBC slaves for own access and control

#### **DMA Controller**

- · Supports the following transfers:

- Memory-to-memory transfers

- Buffered peripheral to memory transfers

- Buffered memory to peripheral transfers

- · Four channels

- · Scatter/Gather capability for programming multiple DMA operations

- 8-, 16-, 32-bit peripheral support (OPB and external)

- · 32-bit addressing

- · Address increment or decrement

- · Internal 32-byte data buffering capability

- · Supports internal and external peripherals

- · Support for memory mapped peripherals

- · Support for peripherals running on slower frequency buses

#### **UART**

- · One 8-pin UART and one 4-pin UART interface provided

- · Selectable internal or external serial clock to allow wide range of baud rates

- · Register compatibility with NS16550 register set

- · Complete status reporting capability

- Transmitter and receiver are each buffered with 16-byte FIFOs when in FIFO mode

- · Fully programmable serial-interface characteristics

- · Supports DMA using internal DMA engine

#### **IIC Bus Interface**

- Compliant with Phillips® Semiconductors I<sup>2</sup>C Specification, dated 1995

- · Operation at 100kHz or 400kHz

- 8-bit data

- 10- or 7-bit address

- · Slave transmitter and receiver

- · Master transmitter and receiver

- · Multiple bus masters

- Supports fixed V<sub>DD</sub> IIC interface

- Two independent 4 x 1 byte data buffers

- · Twelve memory-mapped, fully programmable configuration registers

- One programmable interrupt request signal

- · Provides full management of all IIC bus protocol

- · Programmable error recovery

### **General Purpose IO (GPIO) Controller**

- Controller functions and GPIO registers are programmed and accessed via memory-mapped OPB bus master accesses.

- All GPIOs are pin-shared with other functions. DCRs control whether a particular pin that has GPIO

capabilities acts as a GPIO or is used for another purpose. The 23 GPIOs are multiplexed with:

- 7 of 8 chip selects.

- All seven external interrupts.

- All nine instruction trace pins.

- Each GPIO output is separately programmable to emulate an open-drain driver (two states, drive to zero or open circuit).

#### **Universal Interrupt Controller (UIC)**

The Universal Interrupt Controller (UIC) provides the control, status, and communications necessary between the various sources of interrupts and the local PowerPC processor.

#### Features include:

- Supports 7 external and 10 internal interrupts

- · Edge triggered or level-sensitive

- · Positive or negative active

- Non-critical or critical interrupt to PPC405 processor core

- · Programmable critical interrupt priority ordering

- Programmable critical interrupt vector for faster vector processing

#### **JTAG**

- IEEE 1149.1 test access port

- IBM RISCWatch debugger support

- JTAG Boundary Scan Description Language (BSDL)

### 27mm, 316-Ball E-PBGA Package

#### **Pin Lists**

In this section there are two tables that correlate the external signals to the physical package pin (ball) on which they appear.

The following table lists all the external signals in alphabetical order and shows the ball number on which the signal appears. Multiplexed signals are shown with the default signal (following reset) *not* in brackets and the alternate signal in brackets. The page number listed gives the page in "Signal Functional Description" on page 23 where the signals in the indicated interface group begin.

### Signals Listed Alphabetically (Part 1 of 7)

| Signal Name          | Ball       | Interface Group            | Page |

|----------------------|------------|----------------------------|------|

| AV <sub>DD</sub>     | E20        | Power                      | 28   |

| BA0                  | J17        | opp.u.                     | 00   |

| BA1                  | H18        | SDRAM                      | 23   |

| BankSel0             | L19        |                            |      |

| BankSel1             | N17        | SDRAM                      | 23   |

| BankSel2             | P17        | ODITAIN                    | 23   |

| BankSel3             | U19        |                            |      |

| BusReq               | P2         | External Master Peripheral | 25   |

| CAS                  | K17        | SDRAM                      | 23   |

| ClkEn0               | J19        | SDRAM                      | 23   |

| ClkEn1               | G20        | ODITAW                     | 20   |

| DMAAck0              | C16        |                            |      |

| DMAAck1              | B17        | External Slave Peripheral  | 23   |

| DMAAck2              | B16        | External olavor oriphoral  |      |

| DMAAck3              | A14        |                            |      |

| DMAReq0              | A19        |                            |      |

| DMAReq1              | C15        | External Slave Peripheral  | 23   |

| DMAReq2              | B15        |                            | _    |

| DMAReq3              | A8         |                            |      |

| DQM0                 | U18        |                            |      |

| DQM1                 | W14        | SDRAM                      | 23   |

| DQM2<br>DQM3         | Y10<br>U8  |                            |      |

| DQMCB                | V19        | SDRAM                      | 23   |

|                      | F17        | SDRAW                      | 23   |

| Drvrlnh1<br>Drvrlnh2 | C19        | System                     | 27   |

| ECC0                 | V17        |                            |      |

| ECC0                 | V17<br>Y18 |                            |      |

| ECC2                 | U14        |                            |      |

| ECC3                 | V13        |                            |      |

| ECC4                 | Y13        | SDRAM                      | 23   |

| ECC5                 | V12        |                            |      |

| ECC6                 | W11        |                            |      |

| ECC7                 | V11        |                            |      |

| EOT0/TC0             | G4         |                            |      |

| EOT1/TC1             | F2         | External Clave Deviabage   | 23   |

| EOT2/TC2             | W1         | External Slave Peripheral  | 23   |

| EOT3/TC3             | Y2         |                            |      |

# Signals Listed Alphabetically (Part 2 of 7)

| Signal Name | Ball       | Interface Group                                                  | Page |

|-------------|------------|------------------------------------------------------------------|------|

| ExtAck      | U5         |                                                                  |      |

| ExtReq      | Y3         | External Master Peripheral                                       | 25   |

| ExtReset    | P4         |                                                                  |      |

|             | A1         |                                                                  |      |

|             | A6         |                                                                  |      |

|             | A10        |                                                                  |      |

|             | A15        |                                                                  |      |

|             | A20        |                                                                  |      |

|             | B2         |                                                                  |      |

|             | B19        |                                                                  |      |

|             | C3         |                                                                  |      |

|             | C18        |                                                                  |      |

|             | D4         |                                                                  |      |

|             | D17        |                                                                  |      |

|             | E5         |                                                                  |      |

|             | E10        |                                                                  |      |

|             | E11        |                                                                  |      |

|             | E16        |                                                                  |      |

|             | F1         |                                                                  |      |

|             | F20        |                                                                  |      |

|             | J9         |                                                                  |      |

|             | J10        |                                                                  |      |

|             | J11        | Power                                                            |      |

| GND         | J12        | Note: J9–J12, K9–K12, L9–L12, and M9–M12 are also thermal balls. | 28   |

|             | K5         |                                                                  |      |

|             | K9         |                                                                  |      |

|             | K10        |                                                                  |      |

|             | K11<br>K12 |                                                                  |      |

|             | K12<br>K16 |                                                                  |      |

|             | K20        |                                                                  |      |

|             | L1         |                                                                  |      |

|             | L5         |                                                                  |      |

|             | L9         |                                                                  |      |

|             | L10        |                                                                  |      |

|             | L11        |                                                                  |      |

|             | L12        |                                                                  |      |

|             | L16        |                                                                  |      |

|             | M9         |                                                                  |      |

|             | M10        |                                                                  |      |

|             | M11        |                                                                  |      |

|             | M12        |                                                                  |      |

|             | R1         |                                                                  |      |

|             | R20        |                                                                  |      |

Signals Listed Alphabetically (Part 3 of 7)

| Signal Name   | Ball | Interface Group                                                         | Page |

|---------------|------|-------------------------------------------------------------------------|------|

|               | T5   |                                                                         |      |

|               | T10  |                                                                         |      |

|               | T11  |                                                                         |      |

|               | T16  |                                                                         |      |

|               | U4   |                                                                         |      |

|               | U17  |                                                                         |      |

|               | V3   |                                                                         |      |

| GND (cont)    | V18  | Power                                                                   | 28   |

|               | W2   |                                                                         |      |

|               | W19  |                                                                         |      |

|               | Y1   |                                                                         |      |

|               | Y6   |                                                                         |      |

|               | Y11  |                                                                         |      |

|               | Y15  |                                                                         |      |

|               | Y20  |                                                                         |      |

| GPIO1[TS1E]   | B18  |                                                                         |      |

| GPIO2[TS2E]   | D16  |                                                                         |      |

| GPI03[TS10]   | C17  |                                                                         |      |

| GPIO4[TS2O]   | P18  |                                                                         |      |

| GPIO5[TS3]    | T17  | System                                                                  | 27   |

| GPIO6[TS4]    | W18  |                                                                         |      |

| GPIO7[TS5]    | Y19  |                                                                         |      |

| GPIO8[TS6]    | W13  |                                                                         |      |

| GPIO9[TrcClk] | V6   |                                                                         |      |

| Halt          | E19  | System                                                                  | 27   |

| HoldAck       | T4   |                                                                         |      |

| HoldPri       | T3   | External Master Peripheral                                              | 25   |

| HoldReq       | V2   |                                                                         |      |

| IICSCL        | U15  | Internal Peripheral                                                     | 25   |

| IICSDA        | W17  | Internal Peripheral                                                     | 25   |

| IRQ0[GPIO17]  | D18  |                                                                         |      |

| IRQ1[GPIO18]  | C20  |                                                                         |      |

| IRQ2[GPIO19]  | E18  |                                                                         |      |

| IRQ3[GPIO20]  | D20  | Interrupts                                                              | 26   |

| IRQ4[GPIO21]  | G17  |                                                                         |      |

| IRQ5[GPIO22]  | F18  |                                                                         |      |

| IRQ6[GPIO23]  | W20  |                                                                         |      |

| MemAddr0      | Y7   |                                                                         |      |

| MemAddr1      | W7   |                                                                         |      |

| MemAddr2      | V8   |                                                                         |      |

| MemAddr3      | U7   |                                                                         |      |

| MemAddr4      | Y4   |                                                                         |      |

| MemAddr5      | U6   | SDRAM                                                                   | 66   |

| MemAddr6      | W4   | Note: During a CAS cycle MemAddr0 is the least significant bit (lsb) on | 23   |

| MemAddr7      | V5   | this bus.                                                               |      |

| MemAddr8      | W3   |                                                                         |      |

| MemAddr9      | V4   |                                                                         |      |

| MemAddr10     | U3   |                                                                         |      |

| MemAddr11     | V1   |                                                                         |      |

| MemAddr12     | T2   |                                                                         |      |

Signals Listed Alphabetically (Part 4 of 7)

| Signal Name            | Ball       | Interface Group                                                      | Page |

|------------------------|------------|----------------------------------------------------------------------|------|

| MemClkOut0             | H20        |                                                                      |      |

| MemClkOut1             | G18        | SDRAM                                                                | 23   |

| MemData0               | J18        |                                                                      |      |

| MemData1               | K19        |                                                                      |      |

| MemData2               | L20        |                                                                      |      |

| MemData3               | M20        |                                                                      |      |

| MemData4               | M19        |                                                                      |      |

| MemData5               | L18        |                                                                      |      |

| MemData6               | L17        |                                                                      |      |

| MemData7               | N20        |                                                                      |      |

| MemData8               | N19        |                                                                      |      |

| MemData9               | M18        |                                                                      |      |

| MemData10              | M17        |                                                                      |      |

| MemData11              | P20        |                                                                      |      |

| MemData12              | P19        |                                                                      |      |

| MemData13              | N18        |                                                                      |      |

| MemData14              | U20        | SDRAM                                                                |      |

| MemData15              | T18        | <b>Note:</b> MemData0 is the most significant bit (msb) on this bus. | 23   |

| MemData16              | W16        | The transfer of the most signment sit (most) on the sact             |      |

| MemData17              | Y17        |                                                                      |      |

| MemData18              | Y16        |                                                                      |      |

| MemData19              | V14        |                                                                      |      |

| MemData20              | Y14        |                                                                      |      |

| MemData21              | U12        |                                                                      |      |

| MemData22              | W12        |                                                                      |      |

| MemData23              | Y12<br>Y9  |                                                                      |      |

| MemData24              | W9         |                                                                      |      |

| MemData25<br>MemData26 | VV9<br>V10 |                                                                      |      |

| MemData27              | U10        |                                                                      |      |

| MemData28              | Y8         |                                                                      |      |

| MemData29              | W8         |                                                                      |      |

| MemData30              | V9         |                                                                      |      |

| MemData31              | U9         |                                                                      |      |

|                        | F5         |                                                                      |      |

|                        | G5         |                                                                      |      |

|                        | P5         |                                                                      |      |

|                        | R5         |                                                                      |      |

|                        | T6         |                                                                      |      |

|                        | T7         |                                                                      |      |

|                        | T14        |                                                                      |      |

|                        | T15        |                                                                      |      |

| OV <sub>DD</sub>       | F16        | Power                                                                | 28   |

|                        | G16        |                                                                      |      |

|                        | P16        |                                                                      |      |

|                        | R16        |                                                                      |      |

|                        | E6         |                                                                      |      |

|                        | E7         |                                                                      |      |

|                        | E14        |                                                                      |      |

|                        | E15        |                                                                      |      |

Signals Listed Alphabetically (Part 5 of 7)

| Signal Name    | Ball | Interface Group                                               | Page |

|----------------|------|---------------------------------------------------------------|------|

| PerAddr0       | A3   |                                                               |      |

| PerAddr1       | A4   |                                                               |      |

| PerAddr2       | B6   |                                                               |      |

| PerAddr3       | D7   |                                                               |      |

| PerAddr4       | C6   |                                                               |      |

| PerAddr5       | B7   |                                                               |      |

| PerAddr6       | D8   |                                                               |      |

| PerAddr7       | C7   |                                                               |      |

| PerAddr8       | B8   |                                                               |      |

| PerAddr9       | A7   |                                                               |      |

| PerAddr10      | D9   |                                                               |      |

| PerAddr11      | C8   |                                                               |      |

| PerAddr12      | B9   |                                                               |      |

| PerAddr13      | D10  |                                                               |      |

| PerAddr14      | C9   |                                                               |      |

| PerAddr15      | A9   | External Slave Peripheral                                     |      |

| PerAddr16      | B11  | Note: PerAddr0 is the most significant bit (msb) on this bus. | 23   |

| PerAddr17      | A11  | , ,                                                           |      |

| PerAddr18      | B12  |                                                               |      |

| PerAddr19      | D11  |                                                               |      |

| PerAddr20      | A13  |                                                               |      |

| PerAddr21      | B13  |                                                               |      |

| PerAddr22      | C12  |                                                               |      |

| PerAddr23      | D12  |                                                               |      |

| PerAddr24      | B14  |                                                               |      |

| PerAddr25      | C13  |                                                               |      |

| PerAddr26      | D13  |                                                               |      |

| PerAddr27      | A16  |                                                               |      |

| PerAddr28      | C14  |                                                               |      |

| PerAddr29      | D14  |                                                               |      |

| PerAddr30      | A17  |                                                               |      |

| PerAddr31      | D15  |                                                               |      |

| PerBLast       | E2   | External Slave Peripheral                                     | 23   |

| PerClk         | D3   | External Master Peripheral                                    | 25   |

| PerCS0         | D6   |                                                               |      |

| PerCS1[GPIO10] | B5   |                                                               |      |

| PerCS2[GPIO11] | C5   |                                                               |      |

| PerCS3[GPIO12] | A5   | External Slave Peripheral                                     | 00   |

| PerCS4[GPIO13] | B10  | External Slave Peripheral                                     | 23   |

| PerCS5[GPIO14] | C10  |                                                               |      |

| PerCS6[GPIO15] | A12  |                                                               |      |

| PerCS7[GPIO16] | C11  |                                                               |      |

# Signals Listed Alphabetically (Part 6 of 7)

| Signal Name | Ball | Interface Group                                               | Page |

|-------------|------|---------------------------------------------------------------|------|

| PerData0    | U2   |                                                               |      |

| PerData1    | R4   |                                                               |      |

| PerData2    | U1   |                                                               |      |

| PerData3    | R2   |                                                               |      |

| PerData4    | R3   |                                                               |      |

| PerData5    | T1   |                                                               |      |

| PerData6    | N4   |                                                               |      |

| PerData7    | P3   |                                                               |      |

| PerData8    | N2   |                                                               |      |

| PerData9    | P1   |                                                               |      |

| PerData10   | M4   |                                                               |      |

| PerData11   | N3   |                                                               |      |

| PerData12   | M2   |                                                               |      |

| PerData13   | N1   |                                                               |      |

| PerData14   | L4   |                                                               |      |

| PerData15   | МЗ   | External Slave Peripheral                                     | 00   |

| PerData16   | L2   | Note: PerData0 is the most significant bit (msb) on this bus. | 23   |

| PerData17   | M1   | • , ,                                                         |      |

| PerData18   | K2   |                                                               |      |

| PerData19   | L3   |                                                               |      |

| PerData20   | K1   |                                                               |      |

| PerData21   | J1   |                                                               |      |

| PerData22   | J2   |                                                               |      |

| PerData23   | K3   |                                                               |      |

| PerData24   | K4   |                                                               |      |

| PerData25   | H1   |                                                               |      |

| PerData26   | H2   |                                                               |      |

| PerData27   | J3   |                                                               |      |

| PerData28   | J4   |                                                               |      |

| PerData29   | G1   |                                                               |      |

| PerData30   | G2   |                                                               |      |

| PerData31   | H3   |                                                               |      |

| PerErr      | B1   | External Master Peripheral                                    | 25   |

| PerOE       | E4   | External Slave Peripheral                                     | 23   |

| PerPar0     | C2   |                                                               |      |

| PerPar1     | G3   | External Slave Peripheral                                     | 23   |

| PerPar2     | E1   | Ελίστιαι Οιάνε Γετιμπειαι                                     | 23   |

| PerPar3     | H4   |                                                               |      |

| PerReady    | E3   | External Slave Peripheral                                     | 23   |

| PerR/W      | C1   | External Slave Peripheral                                     | 23   |

| PerWBE0     | D2   |                                                               |      |

| PerWBE1     | F4   | Estant Oliver Buildham                                        | 22   |

| PerWBE2     | F3   | External Slave Peripheral                                     | 23   |

| PerWBE3     | D1   |                                                               |      |

| PerWE       | C4   | External Slave Peripheral                                     | 23   |

| RAS         | K18  | SDRAM                                                         | 23   |

| Rcvrlnh     | E17  | System                                                        | 27   |

Signals Listed Alphabetically (Part 7 of 7)

| Signal Name                                                                            | Ball                                                                                                 | Interface Group                                                                                                                                                                     | Page |

|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Reserved                                                                               | J20<br>G19<br>R17<br>T20<br>V16                                                                      | Other pins  Notes:  1. Connect G19 to ground.  2. Other reserved pins are not connected internally within the chip and should not have signals, voltage, or ground applied to them. | 28   |

| SysClk<br>SysErr<br>SysReset                                                           | H17<br>A18<br>D19                                                                                    | System                                                                                                                                                                              | 27   |

| TCK<br>TDI<br>TDO                                                                      | B4<br>A2<br>D5                                                                                       | JTAG                                                                                                                                                                                | 26   |

| TestEn                                                                                 | F19                                                                                                  | System                                                                                                                                                                              | 27   |

| TmrClk                                                                                 | B20                                                                                                  | System                                                                                                                                                                              | 27   |

| TMS                                                                                    | В3                                                                                                   | JTAG                                                                                                                                                                                | 26   |

| TRST                                                                                   | H19                                                                                                  | JTAG                                                                                                                                                                                | 26   |

| UARTO_CTS UARTO_DCD UARTO_DSR UARTO_DTR UARTO_RI UARTO_RIS UARTO_RTS UARTO_RX UARTO_TX | W10<br>R18<br>U16<br>U13<br>V15<br>V20<br>T19<br>W15                                                 | Internal Peripheral                                                                                                                                                                 | 25   |

| UART1_DSR[UART1_CTS] UART1_RTS[UART1_DTR] UART1_Rx UART1_Tx                            | V7<br>W6<br>W5<br>Y5                                                                                 | Internal Peripheral                                                                                                                                                                 | 25   |

| UARTSerClk                                                                             | R19                                                                                                  | Internal Peripheral                                                                                                                                                                 | 25   |

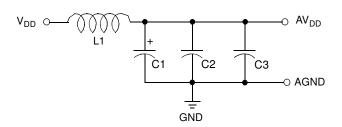

| V <sub>DD</sub>                                                                        | E8<br>E9<br>E12<br>E13<br>H5<br>H16<br>J5<br>J16<br>M5<br>M16<br>N5<br>N16<br>T8<br>T9<br>T12<br>T13 | Power                                                                                                                                                                               | 28   |

| WE                                                                                     | U11                                                                                                  | SDRAM                                                                                                                                                                               | 23   |

# Signals Listed by Ball Assignment (Part 1 of 3)

| Ball       | Signal Name    | Ball | Signal Name    | Ball | Signal Name      | Ball | Signal Name      |

|------------|----------------|------|----------------|------|------------------|------|------------------|

| A1         | GND            | B10  | PerCS4[GPIO13] | C19  | DrvrInh2         | E8   | V <sub>DD</sub>  |

| A2         | TDI            | B11  | PerAddr16      | C20  | IRQ1[GPIO18]     | E9   | V <sub>DD</sub>  |

| А3         | PerAddr0       | B12  | PerAddr18      | D1   | PerWBE3          | E10  | GND              |

| A4         | PerAddr1       | B13  | PerAddr21      | D2   | PerWBE0          | E11  | GND              |

| <b>A</b> 5 | PerCS3[GPIO12] | B14  | PerAddr24      | D3   | PerClk           | E12  | V <sub>DD</sub>  |

| A6         | Gnd            | B15  | DMAReq2        | D4   | GND              | E13  | V <sub>DD</sub>  |

| <b>A</b> 7 | PerAddr9       | B16  | DMAAck2        | D5   | TDO              | E14  | OV <sub>DD</sub> |

| A8         | DMAReq3        | B17  | DMAAck1        | D6   | PerCS0           | E15  | OV <sub>DD</sub> |

| A9         | PerAddr15      | B18  | GPIO1[TS1E]    | D7   | PerAddr3         | E16  | GND              |

| A10        | GND            | B19  | GND            | D8   | PerAddr6         | E17  | Rcrvinh          |

| A11        | PerAddr17      | B20  | TmrClk         | D9   | PerAddr10        | E18  | IRQ2[GPIO19]     |

| A12        | PerCS6[GPIO15] | C1   | PerR/W         | D10  | PerAddr13        | E19  | Halt             |

| A13        | PerAddr20      | C2   | PerPar0        | D11  | PerAddr19        | E20  | AV <sub>DD</sub> |

| A14        | DMAAck3        | C3   | GND            | D12  | PerAddr23        | F1   | GND              |

| A15        | GND            | C4   | PerWE          | D13  | PerAdd26         | F2   | EOT1/TC1         |

| A16        | PerAddr27      | C5   | PerCS2[GPIO11] | D14  | PerAddr29        | F3   | PerWBE2          |

| A17        | PerAddr30      | C6   | PerAddr4       | D15  | PerAddr31        | F4   | PerWBE1          |

| A18        | SysErr         | C7   | PerAddr7       | D16  | GPIO2[TS2E]      | F5   | OV <sub>DD</sub> |

| A19        | DMAReq0        | C8   | PerAddr11      | D17  | GND              | F16  | OV <sub>DD</sub> |

| A20        | GND            | C9   | PerAddr14      | D18  | IRQ0[GPIO17]     | F17  | Drvrlnh1         |

| B1         | PerErr         | C10  | PerCS5[GPIO14] | D19  | SysReset         | F18  | IRQ5[GPIO22]     |

| B2         | GND            | C11  | PerCS7[GPIO16] | D20  | IRQ3[GPIO20]     | F19  | TestEn           |

| В3         | TMS            | C12  | PerAddr22      | E1   | PerPar2          | F20  | GND              |

| B4         | тск            | C13  | PerAddr25      | E2   | PerBLast         | G1   | PerData29        |

| B5         | PerCS1[GPIO10] | C14  | PerAddr28      | E3   | PerReady         | G2   | PerData30        |

| В6         | PerAddr2       | C15  | DMAReq1        | E4   | PerOE            | G3   | PerPar1          |

| В7         | PerAddr5       | C16  | DMAAck0        | E5   | GND              | G4   | EOT0/TC0         |

| B8         | PerAddr8       | C17  | GPI03[TS10]    | E6   | OV <sub>DD</sub> | G5   | OV <sub>DD</sub> |

| В9         | PerAddr12      | C18  | GND            | E7   | OV <sub>DD</sub> | G16  | OV <sub>DD</sub> |

Signals Listed by Ball Assignment (Part 2 of 3)

| Ball | Signal Name     | Ball | Signal Name  | Ball | Signal Name      | Ball | Signal Name      |

|------|-----------------|------|--------------|------|------------------|------|------------------|

| G17  | IRQ4[GPIO21]    | K2   | PerData18    | МЗ   | PerData15        | P18  | GPIO4[TS2O]      |

| G18  | MemClkOut1      | K3   | PerData23    | M4   | PerData10        | P19  | MemData12        |

| G19  | Reserved        | K4   | PerData24    | M5   | V <sub>DD</sub>  | P20  | MemData11        |

| G20  | ClkEn1          | K5   | GND          | М9   | Thermal Ball     | R1   | GND              |

| H1   | PerData25       | K9   | Thermal Ball | M10  | Thermal Ball     | R2   | PerData3         |

| H2   | PerData26       | K10  | Thermal Ball | M11  | Thermal Ball     | R3   | PerData4         |

| НЗ   | PerData31       | K11  | Thermal Ball | M12  | Thermal Ball     | R4   | PerData1         |

| H4   | PerPar3         | K12  | Thermal Ball | M16  | V <sub>DD</sub>  | R5   | OV <sub>DD</sub> |

| H5   | V <sub>DD</sub> | K16  | GND          | M17  | MemData10        | R16  | OV <sub>DD</sub> |

| H16  | V <sub>DD</sub> | K17  | CAS          | M18  | MemData9         | R17  | Reserved         |

| H17  | SysClk          | K18  | RAS          | M19  | MemData4         | R18  | UART0_DCD        |

| H18  | BA1             | K19  | MemData1     | M20  | MemData3         | R19  | UARTSerClk       |

| H19  | TRST            | K20  | GND          | N1   | PerData13        | R20  | GND              |

| H20  | MemClkOut0      | L1   | GND          | N2   | PerData8         | T1   | PerData5         |

| J1   | PerData21       | L2   | PerData16    | N3   | PerData11        | T2   | MemAddr12        |

| J2   | PerData22       | L3   | PerData19    | N4   | PerData6         | Т3   | HoldPri          |

| J3   | PerData27       | L4   | PerData14    | N5   | V <sub>DD</sub>  | T4   | HoldAck          |

| J4   | PerData28       | L5   | GND          | N16  | V <sub>DD</sub>  | T5   | GND              |

| J5   | V <sub>DD</sub> | L9   | Thermal Ball | N17  | BankSel1         | T6   | OV <sub>DD</sub> |

| J9   | Thermal Ball    | L10  | Thermal Ball | N18  | MemData13        | T7   | OV <sub>DD</sub> |

| J10  | Thermal Ball    | L11  | Thermal Ball | N19  | MemData8         | T8   | V <sub>DD</sub>  |

| J11  | Thermal Ball    | L12  | Thermal Ball | N20  | MemData7         | Т9   | V <sub>DD</sub>  |

| J12  | Thermal Ball    | L16  | GND          | P1   | PerData9         | T10  | GND              |

| J16  | V <sub>DD</sub> | L17  | MemData6     | P2   | BusReq           | T11  | GND              |

| J17  | BA0             | L18  | MemData5     | P3   | PerData7         | T12  | V <sub>DD</sub>  |

| J18  | MemData0        | L19  | BankSel0     | P4   | ExtReset         | T13  | V <sub>DD</sub>  |

| J19  | ClkEn0          | L20  | MemData2     | P5   | OV <sub>DD</sub> | T14  | $OV_{DD}$        |

| J20  | Reserved        | M1   | PerData17    | P16  | OV <sub>DD</sub> | T15  | $OV_{DD}$        |

| K1   | PerData20       | M2   | PerData12    | P17  | BankSel2         | T16  | GND              |

|      |                 |      |              |      |                  |      |                  |

# Signals Listed by Ball Assignment (Part 3 of 3)

| Ball | Signal Name | Ball | Signal Name              | Ball | Signal Name              | Ball       | Signal Name  |

|------|-------------|------|--------------------------|------|--------------------------|------------|--------------|

| T17  | GPIO5[TS3]  | U18  | DQM0                     | V19  | DQMCB                    | W20        | IRQ6[GPIO23] |

| T18  | MemData15   | U19  | BankSel3                 | V20  | UARTO_RTS                | Y1         | GND          |

| T19  | UART0_RX    | U20  | MemData14                | W1   | EOT2/TC2                 | Y2         | EOT3/TC3     |

| T20  | Reserved    | V1   | MemAddr11                | W2   | GND                      | Y3         | ExtReq       |

| U1   | PerData2    | V2   | HoldReq                  | W3   | MemAddr8                 | Y4         | MemAddr4     |

| U2   | PerData0    | V3   | GND                      | W4   | MemAddr6                 | Y5         | UART1_TX     |

| U3   | MemAddr10   | V4   | MemAddr9                 | W5   | UART1_RX                 | Y6         | GND          |

| U4   | GND         | V5   | MemAddr7                 | W6   | UART1_RTS<br>[UART1_DTR] | <b>Y</b> 7 | MemAddr0     |

| U5   | ExtAck      | V6   | GPIO9[TrcClk]            | W7   | MemAddr1                 | Y8         | MemData28    |

| U6   | MemAddr5    | V7   | UART1_DSR<br>[UART1_CTS] | W8   | MemData29                | <b>Y</b> 9 | MemData24    |

| U7   | MemAddr3    | V8   | MemAddr2                 | W9   | MemData25                | Y10        | DQM2         |

| U8   | DQM3        | V9   | MemData30                | W10  | UARTO_CTS                | Y11        | GND          |

| U9   | MemData31   | V10  | MemData26                | W11  | ECC6                     | Y12        | MemData23    |

| U10  | MemData27   | V11  | ECC7                     | W12  | MemData22                | Y13        | ECC4         |

| U11  | WE          | V12  | ECC5                     | W13  | GPIO8[TS6]               | Y14        | MemData20    |

| U12  | MemData21   | V13  | ECC3                     | W14  | DQM1                     | Y15        | GND          |

| U13  | UART0_DTR   | V14  | MemData19                | W15  | UART0_TX                 | Y16        | MemData18    |

| U14  | ECC2        | V15  | UART0_RI                 | W16  | MemData16                | Y17        | MemData17    |

| U15  | IICSCL      | V16  | Reserved                 | W17  | IICSDA                   | Y18        | ECC1         |

| U16  | UARTO_DSR   | V17  | ECC0                     | W18  | GPIO6[TS4]               | Y19        | GPIO7[TS5]   |

| U17  | GND         | V18  | GND                      | W19  | GND                      | Y20        | GND          |

### **Signal Descriptions**

The PPC405CR embedded controller is packaged in a 316-ball enhanced plastic ball grid array (E-PBGA). The following table provides a summary of the number of package pins associated with each functional interface group.

#### **Pin Summary**

| Group               | No. of Pins |

|---------------------|-------------|

| SDRAM               | 71          |

| External Peripheral | 97          |

| External Master     | 9           |

| Internal Peripheral | 15          |

| Interrupts          | 7           |

| JTAG                | 5           |

| System              | 18          |

| Total Signal Pins   | 222         |

| $AV_DD$             | 1           |

| OV <sub>DD</sub>    | 16          |

| $V_{DD}$            | 16          |

| Gnd                 | 40          |

| Thermal (and Gnd)   | 16          |

| Reserved            | 5           |

| Total Pins          | 316         |

#### **Multiplexed Pins**

In the table "Signal Functional Description" on page 23, each I/O signal is listed along with a short description of the signal function. Some signals are multiplexed onto the same package pin (ball) so that the pin can be used for different functions. Multiplexed signals are shown as a default signal with a secondary signal in square brackets (for example, GPIO1[TS1E]). Active-low signals (for example, RAS) are marked with an overline.

It is expected that in any single application a particular pin will always be programmed to serve the same function. The flexibility of multiplexing allows a single chip to offer a richer pin selection than would otherwise be possible.

In addition to multiplexing, many pins are also multi-purpose. For example, the EBC peripheral controller address pins are used as outputs by the PPC405CR to broadcast an address to external slave devices when the PPC405CR has control of the external bus. When during the course of normal chip operation an external master gains ownership of the external bus, these same pins are used as inputs which are driven by the external master and received by the EBC in the PPC405CR.

#### **Intialization Strapping**

One group of pins is used as strapped inputs during system reset. These pins function as strapped inputs only during reset and are used for other functions during normal operation (see "Strapping" on page 40). Note that these are *not multiplexed* pins since the function of the pins is not programmable.

#### **Pull-Up and Pull-Down Resistors**

Pull-up and pull-down resistors are used for strapping during reset and to retain unused or undriven inputs in an appropriate state. The recommended pull-up value of  $3k\Omega$  to +3.3V ( $10k\Omega$  to +5V can be used on 5V tolerant I/Os) and pull-down value of  $1k\Omega$  to GND, applies only to individually terminated signals. To prevent possible damage to the device, I/Os capable of becoming outputs *must never* be tied together and terminated through a common resistor.

If your system-level test methodology permits, input-only signals can be connected together and terminated through either a common resistor or directly to +3.3V or GND. When a resistor is used, its value must ensure that the grouped I/Os reach a valid logic zero or logic one state when accounting for the total input current into the PPC405CR.

#### Unused I/Os

Strapping of some pins may be necessary when they are unused. Although the PPC405CR requires only the pull-up and pull-down terminations as specified in the "Signal Functional Description" on page 23, good design practice is to terminate all unused inputs or to configure I/Os such that they always drive. If unused, the peripheral and SDRAM buses should be configured and terminated as follows:

- Peripheral interface—PerAddr0:31, PerData0:31, and all of the control signals are driven by default.

Terminate PerReady high and PerError low.

- SDRAM—Program SDRAM0\_CFG[EMDULR]=1 and SDRAM0\_CFG[DCE]=1. This causes the PPC405CR to actively drive all of the SDRAM address, data, and control signals.

#### **External Bus Control Signals**

All peripheral bus control signals (PerCS0:7, PerR/W, PerWBE0:3, PerOE, PerWE, PerBLast, HoldAck, ExtAck) are set to the high-impedance state when ExtReset=0. In addition, as detailed in the *PowerPC 405CR Embedded Processor User's Manual*, the peripheral bus controller can be programmed via EBC0\_CFG to float some of these control signals between transactions and/or when an external master owns the peripheral bus. As a result, a pull-up resistor should be added to those control signals where an undriven state may affect any devices receiving that particular signal.

The following table lists all of the I/O signals provided by the PPC405CR. Please refer to "Signals Listed Alphabetically" on page 11 for the pin number to which each signal is assigned.

### Signal Functional Description (Part 1 of 6)

Multiplexed signals are shown in brackets following the first signal name assigned to each multiplexed ball. **Notes:**

- 1. Receiver input has hysteresis.

- 2. Must pull up. See "Pull-Up and Pull-Down Resistors" on page 22 for recommended termination values.

- 3. Must pull down. See "Pull-Up and Pull-Down Resistors" on page 22 for recommended termination values.

- 4. If not used, must pull up.

- 5. If not used, must pull down.

- 6. Strapping input during reset; pull-up or pull-down required.

- 7. Pull-up may be required. See "External Bus Control Signals" on page 22.

| Signal Name          | Description                                                                                                                                                                 | I/O | Туре                      | Notes |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-------|--|--|--|

| SDRAM Interface      |                                                                                                                                                                             |     |                           |       |  |  |  |

| MemData0:31          | Memory Data bus.  Notes:  1. MemData0 is the most significant bit (msb).  2. MemData31 is the least significant bit (lsb).                                                  | I/O | 3.3V LVTTL                |       |  |  |  |

| MemAddr12:0          | Memory Address bus.  Notes:  1. MemAddr12 is the most significant bit (msb).  2. MemAddr0 is the least significant bit (lsb).                                               | 0   | 3.3V LVTTL                |       |  |  |  |

| BA0:1                | Bank Address supporting up to four internal banks.                                                                                                                          | 0   | 3.3V LVTTL                |       |  |  |  |

| RAS                  | Row Address Strobe.                                                                                                                                                         | 0   | 3.3V LVTTL                |       |  |  |  |

| CAS                  | Column Address Strobe.                                                                                                                                                      | 0   | 3.3V LVTTL                |       |  |  |  |

| DQM0:3               | DQM for byte lanes 0 (MemData0:7),<br>1 (MemData8:15),<br>2 (MemData16:23), and<br>3 (MemData24:31).                                                                        | 0   | 3.3V LVTTL                |       |  |  |  |

| DQMCB                | DQM for ECC check bits.                                                                                                                                                     | 0   | 3.3V LVTTL                |       |  |  |  |

| ECC0:7               | ECC check bits 0:7.                                                                                                                                                         | I/O | 3.3V LVTTL                |       |  |  |  |

| BankSel0:3           | Select up to four external SDRAM banks.                                                                                                                                     | 0   | 3.3V LVTTL                |       |  |  |  |

| WE                   | Write Enable.                                                                                                                                                               | 0   | 3.3V LVTTL                |       |  |  |  |

| ClkEn0:1             | SDRAM Clock Enable.                                                                                                                                                         | 0   | 3.3V LVTTL                |       |  |  |  |

| MemClkOut0:1         | Two copies of an SDRAM clock allows, in some cases, glueless SDRAM attach without requiring this signal to be repowered by a PLL or zero-delay buffer.                      | 0   | 3.3V LVTTL                |       |  |  |  |

| External Slave Perip | heral Interface                                                                                                                                                             |     |                           |       |  |  |  |

| PerData0:31          | Peripheral data bus used by PPC405CR when not in external master mode, otherwise used by external master.  Note: PerData0 is the most significant bit (msb) on this bus.    | I/O | 5V tolerant<br>3.3V LVTTL | 1     |  |  |  |

| PerAddr0:31          | Peripheral address bus used by PPC405CR when not in external master mode, otherwise used by external master.  Note: PerAddr0 is the most significant bit (msb) on this bus. | I/O | 5V tolerant<br>3.3V LVTTL | 1     |  |  |  |

| PerPar0:3            | Peripheral byte parity signals.                                                                                                                                             | I/O | 5V tolerant<br>3.3V LVTTL | 1     |  |  |  |

#### Signal Functional Description (Part 2 of 6)

Multiplexed signals are shown in brackets following the first signal name assigned to each multiplexed ball. **Notes:**

- 1. Receiver input has hysteresis.

- 2. Must pull up. See "Pull-Up and Pull-Down Resistors" on page 22 for recommended termination values.

- 3. Must pull down. See "Pull-Up and Pull-Down Resistors" on page 22 for recommended termination values.

- 4. If not used, must pull up.

- 5. If not used, must pull down.

- 6. Strapping input during reset; pull-up or pull-down required.

- 7. Pull-up may be required. See "External Bus Control Signals" on page 22.

| Signal Name         | Description                                                                                                                                                                                                                                                                                                                                                                                             | I/O    | Туре                      | Notes |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------------------|-------|

| PerWBE0:3           | As outputs, these pins can act as byte-enables which are valid for an entire cycle or as write-byte-enables which are valid for each byte on each data transfer, allowing partial word transactions. As outputs, pins are used by either peripheral controller or the DMA controller depending upon the type of transfer involved. Used as inputs when external bus master owns the external interface. | I/O    | 5V tolerant<br>3.3V LVTTL | 1,7   |

| PerWE               | Peripheral write enable. Active when any of the four PerWBE0:3 signals are active.                                                                                                                                                                                                                                                                                                                      | 0      | 5V tolerant<br>3.3V LVTTL |       |

| PerCS0              | Peripheral chip select bank 0.                                                                                                                                                                                                                                                                                                                                                                          | 0      | 5V tolerant<br>3.3V LVTTL | 7     |

| PerCS1:7[GPIO10:16] | Seven additional peripheral chip selects or General Purpose I/O. To access this function, software must toggle a DCR register bit.                                                                                                                                                                                                                                                                      | O[I/O] | 5V tolerant<br>3.3V LVTTL | 1,7   |

| PerOE               | Used by either peripheral controller or DMA controller depending upon the type of transfer involved. When the PPC405CR is the bus master, it enables the selected device to drive the bus.                                                                                                                                                                                                              | 0      | 5V tolerant<br>3.3V LVTTL | 7     |

| PerR/W              | Used by the PPC405CR when not in external master mode, as output by either the peripheral controller or DMA controller depending upon the type of transfer involved. High indicates a read from memory, low indicates a write to memory. Otherwise it used by the external master as an input to indicate the direction of transfer.                                                                    | I/O    | 5V tolerant<br>3.3V LVTTL | 1     |

| PerReady            | Used by a peripheral slave to indicate it is ready to transfer data.                                                                                                                                                                                                                                                                                                                                    | I      | 5V tolerant<br>3.3V LVTTL | 1     |

| PerBLast            | Used by the PPC405CR when not in external master mode, otherwise used by external master. Indicates the last transfer of a memory access.                                                                                                                                                                                                                                                               | I/O    | 5V tolerant<br>3.3V LVTTL | 1, 7  |

| DMAReq0:3           | DMAReq0:3 are used by slave peripherals to indicate they are prepared to transfer data.                                                                                                                                                                                                                                                                                                                 | I      | 5V tolerant<br>3.3V LVTTL | 1     |