### **Dual Output 150/300-mA Low Dropout Regulator**

### **DESCRIPTION**

SiP2210 is a dual output low dropout regulator capable of supplying 150 mA from output 1 and 300 mA from output 2. The SiP2210 has the outputs independently enabled. In addition to the LDOs, an open drain output has been included, which is capable of sinking 150 mA. SiP2210 offers a low dropout, low ground current and extremely low noise with the addition of a bypass capacitor.

Protection features include ERR, undervoltage lockout, output current limit, and thermal shutdown.

The fixed output version of SiP2210 is available in a lead (Pb)-free MLP33-10 PowerPAK package and the adjustable version is available in a lead (Pb)-free MLP44-16 PowerPAK package. Both packages ares specified to operate over the range of - 40 °C to 85 °C.

### **FEATURES**

- 2.25 V to 5.5 V input voltage range

- Two outputs 150 mA and 300 mA

- Low ground current of 48 µA

- Open drain driver output sinking 150 mA

- Low dropout voltage of 65 mV at 100 mA

- ERR

- Current limit

- Thermal shutdown

- MLP33-10 PowerPAK<sup>®</sup> package (fixed output)

MLP44-16 PowerPAK<sup>®</sup> package (adjustable output)

- MIC2210 pin-for-pin replacement

### **APPLICATIONS**

- Cellular phones

- Wireless modems

- **PDAs**

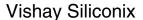

### TYPICAL APPLICATION CIRCUIT

### SiP2210

### Vishay Siliconix

| ABSOLUTE MAXIMUM RATINGS                             |                                |             |       |  |

|------------------------------------------------------|--------------------------------|-------------|-------|--|

| Parameter V <sub>IN</sub> , V <sub>EN</sub> , to GND |                                | Limit       | Unit  |  |

|                                                      |                                | - 0.3 to 7  | V     |  |

| Power Dissipation                                    | MLP33-10 PowerPAK <sup>b</sup> | 1600        | mW    |  |

|                                                      | MLP44-16 PowerPAK <sup>c</sup> | 1880        | 11100 |  |

| Storage Temperature                                  |                                | - 55 to 150 | °C    |  |

| Thermal Resistance (MLP10 PowerPAK)                  |                                | 50          | °C/W  |  |

#### Notes:

- a. Device mounted with all leads soldered or welded to PC board.

b. Derate 20 mW/°C above 70 °C.

- c. Derate 23.5 mW/°C above 70 °C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE                |             |      |

|--------------------------------------------|-------------|------|

| Parameter                                  | Limit       | Unit |

| Input Voltage Range                        | 2.25 to 5.5 | V    |

| Enable Voltage Range                       | 0 to 5.5    | V    |

| Operating Temperature Range T <sub>A</sub> | - 40 to 85  | °C   |

| Operating Temperature Range T <sub>J</sub> | - 40 to 125 | C    |

| SPECIFICATIONS                            |                       |                                                                                          |        |       |        |       |        |

|-------------------------------------------|-----------------------|------------------------------------------------------------------------------------------|--------|-------|--------|-------|--------|

|                                           |                       | Test Conditions Unless Specified                                                         |        |       | Limits |       |        |

| Parameter                                 | Symbol                | $V_{IN} = V_{OUT} + 1 V^{e}, C_{OUT} = 1 \mu F, I_{OUT} = 100 \mu A,$<br>$T_{A} = 25 °C$ | Temp.a | Min.b | Typ.c  | Max.b | Unit   |

| Regulators                                |                       |                                                                                          |        |       |        | ı     |        |

| Outside Mallagrand Agreement              |                       | From Nominal V <sub>OUT</sub>                                                            | Room   | - 1   |        | 1     | 0/     |

| Output Voltage Accuracy                   |                       |                                                                                          | Full   | - 2   |        | 2     | %      |

| Output Voltage<br>Temperature Coefficient |                       |                                                                                          | Room   |       | 40     |       | ppm/°C |

| Line Deculation®                          |                       | V <sub>IN</sub> = V <sub>OLIT</sub> + 1 V to 5.5 V                                       | Room   | - 0.3 | 0.2    | 0.3   |        |

| Line Regulation <sup>e</sup>              |                       | VIN = VOUT + 1 V to 5.5 V                                                                | Full   | - 0.6 |        | 0.6   | %      |

| Load Regulation                           |                       | I <sub>OUT</sub> = 100 μA to 150 mA (LDO 1 and 2)                                        | Room   |       | 0.2    | 1.0   | /0     |

| Load Hegulation                           |                       | $I_{OUT} = 100 \mu A \text{ to } 300 \text{ mA (LDO 2)}$                                 | Room   |       |        | 1.5   |        |

|                                           |                       | I <sub>OUT</sub> = 150 mA (LDO 1 and 2)                                                  | Room   |       | 120    | 190   | - mV   |

| Dropout Voltage <sup>f</sup>              | $V_{DROP}$            | ,                                                                                        | Full   |       |        | 250   |        |

|                                           | * DROP                | I <sub>OUT</sub> = 300 mA (LDO 2)                                                        | Room   |       | 240    | 340   |        |

|                                           |                       | 1001 = 000 HIA (EDO 2)                                                                   | Full   |       |        | 420   |        |

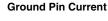

|                                           |                       | $I_{OUT1} = I_{OUT2} = 0 \mu A$                                                          | Room   |       | 48     | 65    |        |

| Ground Pin Current                        | l <sub>G</sub>        | $I_{OUT1} = I_{OUT2} = 0 \mu A$                                                          | Full   |       |        | 80    | μΑ     |

| Ground I III Guirent                      | ·G                    | I <sub>OUT1</sub> = 150 mA, I <sub>OUT2</sub> = 300 mA                                   | Room   |       | 60     |       |        |

|                                           |                       | V <sub>EN</sub> < 0.4 V                                                                  | Full   |       |        | 2.0   |        |

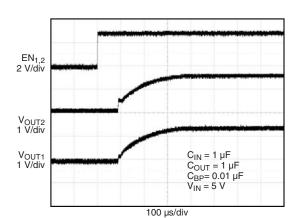

| Sequence Time Delay <sup>d</sup>          | t <sub>SEQ</sub>      |                                                                                          | Room   |       | 70     |       | μs     |

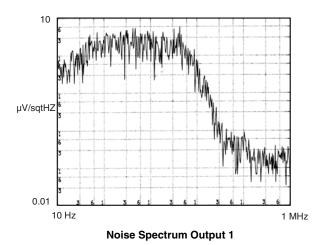

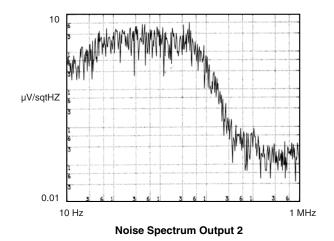

| Output Voltage Noise                      |                       | $C_{BP} = 0.01 \mu F$                                                                    |        |       | 30     |       | μVrms  |

| Ripple Rejection                          |                       | $f = 1 \text{ kHz}, C_{OUT} = 1 \mu F, C_{BP} = 10 \text{ nF}$                           | Room   |       | 60     |       | dB     |

| Tupple Hejection                          |                       | $f = 20 \text{ kHz}, C_{OUT} = 1 \mu\text{F}, C_{BP} = 10 \text{ nF}$                    | Room   |       | 40     |       | uБ     |

| Inputs                                    |                       |                                                                                          |        |       |        |       |        |

| EN, SW Input Voltage                      | $V_{IL}$              | Logic Low                                                                                | Full   |       |        | 0.6   | V      |

| Err, err input voltage                    | V <sub>IH</sub>       | Logic High                                                                               | Full   | 1.8   |        |       | •      |

| EN, SW Input Current                      | I <sub>IL</sub>       | V <sub>IL</sub> < 0.6 V                                                                  | Room   | - 1   | 0.01   | 1     | μΑ     |

| = 1, 517 input Gairoin                    | I <sub>IH</sub>       | V <sub>IH</sub> > 1.8 V                                                                  | Room   | - 1   | 0.01   | 1     |        |

| SET Pin Threshold Voltage                 | V <sub>TH</sub> (set) | POR = High                                                                               | Room   |       | 1.25   |       | V      |

| SET Pin Current Source                    |                       | V <sub>SET</sub> = 0 V                                                                   | Room   | 0.75  | 1.25   | 1.75  | μΑ     |

| SPECIFICATIONS               |                  |                                                                       |        |       |        |       |      |

|------------------------------|------------------|-----------------------------------------------------------------------|--------|-------|--------|-------|------|

|                              |                  | Test Conditions Unless Specified                                      |        |       | Limits |       |      |

|                              |                  | $V_{IN} = V_{OUT} + 1 V^{e}, C_{OUT} = 1 \mu F, I_{OUT} = 100 \mu A,$ |        |       |        |       |      |

| Parameter                    | Symbol           | T <sub>A</sub> = 25 °C                                                | Temp.a | Min.b | Typ.c  | Max.b | Unit |

| Error Flag Output (ERR)      |                  |                                                                       |        |       |        |       |      |

| Threshold                    | $V_{THL}$        | % of Nominal V <sub>OUT2</sub>                                        | Room   | 90    |        |       | %    |

| Threshold                    | V <sub>THH</sub> | 76 OF NOTHINAL VOUT2                                                  | Room   |       |        | 96    | %    |

| Output Voltage               | V <sub>OL</sub>  | I <sub>L</sub> = 250 μA                                               | Room   |       | 0.02   | 0.1   | V    |

| Leakage Current              | I <sub>ERR</sub> | ERR = High                                                            | Room   | - 1   | 0.01   | 1     | μΑ   |

| Driver (DRV) Output          |                  |                                                                       |        |       |        |       |      |

| Output Voltage               | V <sub>OL</sub>  | I <sub>L</sub> = 150 mA                                               | Full   |       | 0.2    | 0.6   | V    |

| Leakage Current              |                  | I <sub>DRV</sub> = 0 mA, V <sub>DRV</sub> = 5.5 V, SW = 0 V           | Room   | - 1   | 0.01   | 1     | μΑ   |

| Protection                   |                  |                                                                       |        |       |        |       |      |

| Current Limit                | 1                | V <sub>OUT1</sub> = 0 V                                               | Room   | 150   | 280    | 460   | mA   |

|                              | IIL              | V <sub>OUT1</sub> = 0 V                                               | Room   | 300   | 450    | 700   | IIIA |

| Thermal Shutdown Temperature |                  | · ·                                                                   |        |       | 165    |       | °C   |

| Thermal Hysteresis           |                  |                                                                       | Room   |       | 25     |       | C    |

#### Notes:

- a. Room = 25 °C, Full = 40 °C to 85 °C.

- b. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum.

- c. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

- d. Timing is measured from 90 % of LDO #1's final value to 90 % of LDO #2's final value.

- e. For higher output of the regulator pair.

- f. Dropout voltage is defined as the input to output differential voltage at which the output voltage drops 2 % below the output voltage measured with a 1 V differential, provided that V<sub>IN</sub> does not drop below 2.25 V. When V<sub>OUT(nom)</sub> is less than 2.25 V, the output will be in regulation when 2.25 V V<sub>OUT(nom)</sub> is greater than the dropout voltage specified.

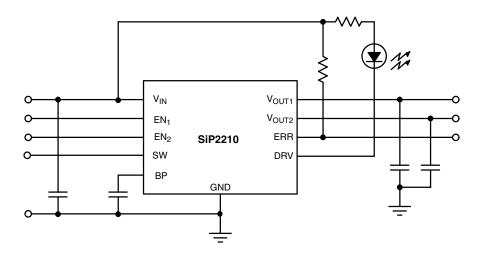

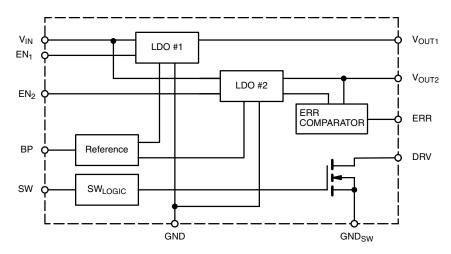

### **FUNCTIONAL BLOCK DIAGRAM**

Fixed Voltage Version

Adjustable Voltage Version

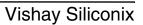

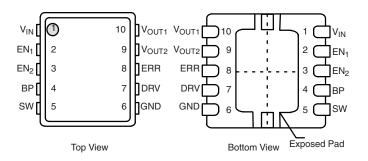

### PIN CONFIGURATION AND ORDERING INFORMATION

### PowerPAK MLP33-10 with Large Pad

### PowerPAK MLP44-16

| VOLTAGE OPTIONS |             |

|-----------------|-------------|

| Voltage         | Code (x, z) |

| Adj             | A           |

| 1.5             | F           |

| 1.6             | W           |

| 1.8             | G           |

| 1.85            | D           |

| 1.9             | Y           |

| 2.0             | Н           |

| 2.1             | E           |

| 2.5             | J           |

| 2.6             | К           |

| 2.7             | L           |

| 2.8             | M           |

| 2.85            | N           |

| 2.9             | 0           |

| 3.0             | Р           |

| 3.1             | Q           |

| 3.2             | R           |

| 3.3             | S           |

| 3.4             | Т           |

| 3.5             | U           |

| 3.6             | V           |

| ORDERING INFORMATION |                    |                      |         |  |

|----------------------|--------------------|----------------------|---------|--|

| Part Number          | Temp. Range        | Package              | Marking |  |

| SiP2210DMP-XZ-E3     | - 40 °C to 85 °C - | PowerPAK<br>MLP33-10 | 10XZ    |  |

| SiP2210DLP-AA-E3     | - 40 0 10 83 0     | PowerPAK<br>MLP44-16 | 10AA    |  |

X: Output 1 voltage code.

Z: Output 2 voltage code.

| Pin Number | Nama     | Franklan          |                                                          |          |  |

|------------|----------|-------------------|----------------------------------------------------------|----------|--|

| MLP33-10   | MLP44-16 | Name              | Function                                                 | Function |  |

| 1          | 15, 16   | V <sub>IN</sub>   | Input voltage for the power MOSFETs and their gate drive |          |  |

| 2          | 1        | EN <sub>1</sub>   | Enables LDO #1 output.                                   |          |  |

|            | 6        | NC                | No Connect                                               |          |  |

| 3          | 2        | EN <sub>2</sub>   | Enables LDO #2 output.                                   |          |  |

| 4          | 3        | BP                | Bypass for noise reduction                               |          |  |

|            | 4        | ADJ <sub>1</sub>  | Feedback connection for LDO #1                           |          |  |

| 5          | 5        | SW                | Control for open drain output                            |          |  |

| 6          | 7, 8     | GND               | Ground                                                   |          |  |

|            | 9        | GND <sub>SW</sub> | Ground for the internal N-channel MOSFET switch          |          |  |

|            | 10       | ADJ <sub>2</sub>  | Feedback connection for LDO #2                           |          |  |

| 7          | 11       | DRV               | Open drain output                                        |          |  |

| 8          | 12       | ERR               | ERROR flag output                                        |          |  |

| 9          | 13       | V <sub>OUT2</sub> | Output of LDO #2 - 300 mA                                |          |  |

| 10         | 14       | V <sub>OUT1</sub> | Output of LDO #1 - 150 mA                                |          |  |

The exposed pad on both packages must be connected externally to the GND pin.

# VISHAY.

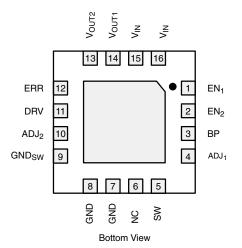

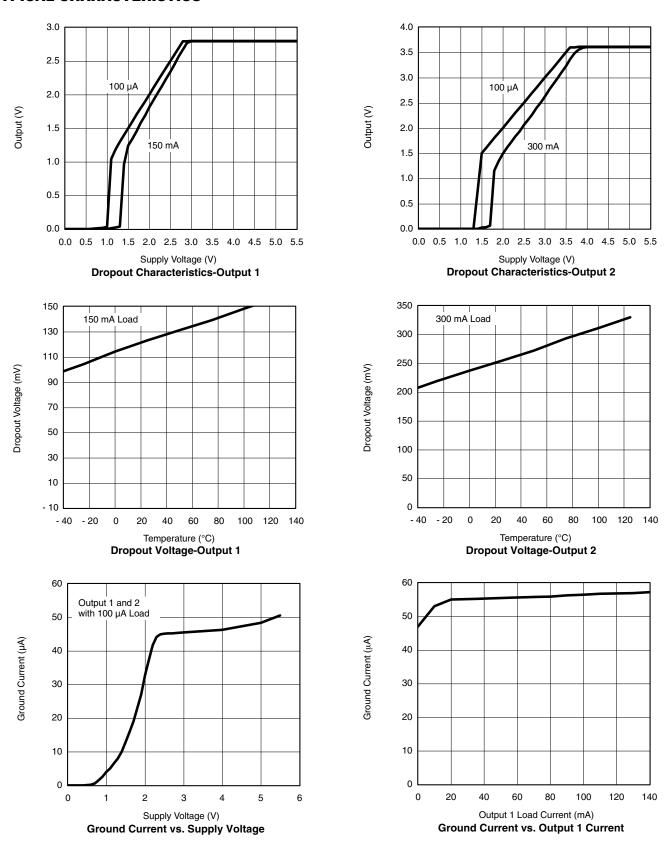

### **TYPICAL CHARACTERISTICS**

### **TYPICAL CHARACTERISTICS**

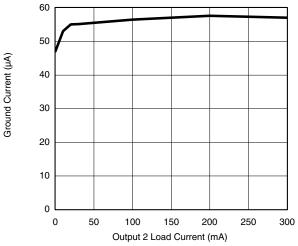

### **Ground Current vs. Output 2 Current**

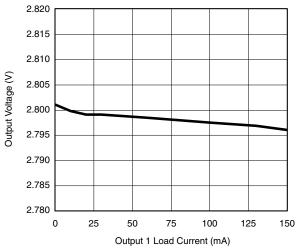

Output Voltage vs. Load Current-Output 1

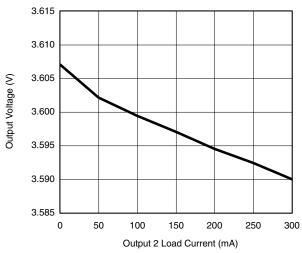

Output Voltage vs. Load Current-Output 2

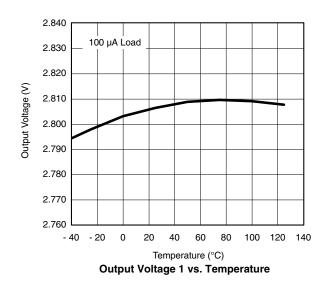

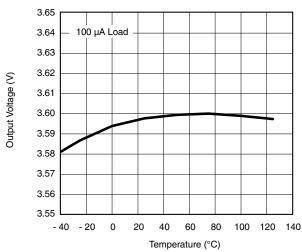

Output Voltage 2 vs. Temperature

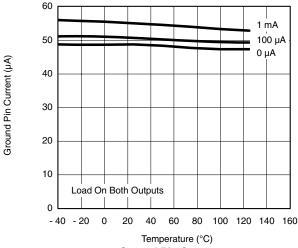

### TYPICAL CHARACTERISTICS

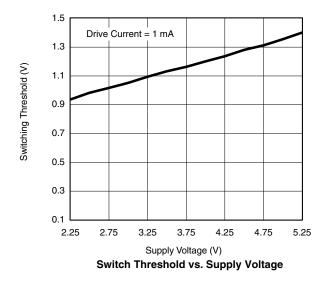

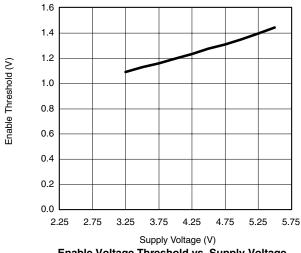

Enable Voltage Threshold vs. Supply Voltage

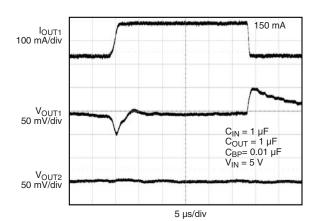

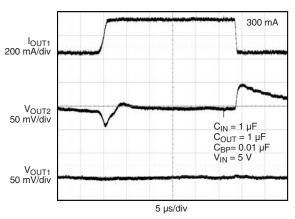

### **TYPICAL WAVEFORMS**

**Enable Sequence**

**Load Transient Response LDO1**

**Load Transient Response LDO2**

#### **DETAILED OPERATION**

The SiP2210 is a low dropout, low quiescent current monolithic dual linear regulator, with power-on reset and open drain driver output features. With output voltage range from 1.25 V to 5 V, the first regulator can source 150 mA and the second regulator can source 300 mA. The open drain driver has the capability to drive LED's for backlighting applications.

### $V_{IN}$

$V_{IN}$  is the input supply pin for both LDO's. The bypass capacitor for this pin is not critical as long as the input supply has low enough source impedance. For practical circuits, a 1.0  $\mu$ F or larger ceramic capacitor is recommended. When the source impedance is not low enough and/or the source is several inches from the SiP2210, then a larger input bypass capacitor is needed. When the source impedance, wire and trace impedance are unknown, it is recommended that an input bypass capacitor be used of a value that is equal to or greater than the output capacitor.

### V<sub>OUT1,2</sub> (LDO Outputs)

The  $V_{OUT}$  is the output voltage of the regulator. Connect a bypass capacitor from  $V_{OUTx}$  to ground. The output capacitor can be any value from 1.0  $\mu$ F to 10.0  $\mu$ F. A ceramic capacitor with X5R or X7R dielectric type is recommended for best output noise, line transient, and load transient performance.

#### **Enable**

The EN1 and EN2 pins control the turning on and off of their respective regulators in the SiP2210.  $V_{OUT}$  of both outputs are guaranteed to be on when the Enable pin voltage is equal or greater than 1.8 V.  $V_{OUT}$  is guaranteed to be off when the Enable pin voltage equals or is less than 0.6 V. To automatically turn on  $V_{OUT}$  whenever the input is applied, tie the Enable pin to  $V_{IN}$ .

### **ERROR Flag Output (ERR)**

The ERR is an open drain output that goes low when  $V_{OUT2}$  is less than 5 % of its nominal value. As with any open drain output, an external pull up resistor is needed. The ERR pin is disconnected if not used.

#### **OPEN-Drain Driver (DRV)**

The SW pin a logic level input put that controls the DRV pin. The switch pin is an active high input and should not be left floating. The drive pin is an open drain output able to sink 150 mA of current.

### **Bypass Capacitor**

For low noise application and/or increase in power supply rejection ration (PSRR) connect a high frequency ceramic capacitor from BP to ground. A 0.01  $\mu\text{F}$  X5R or X7R ceramic capacitor is recommended.

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppg?73441">www.vishay.com/ppg?73441</a>.

Vishay

### **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Document Number: 91000 Revision: 18-Jul-08