# CMOS SYNCHRONOUS RAM 64K (64K x 1-BIT)

# PRELIMINARY IDT71501S

#### **FEATURES:**

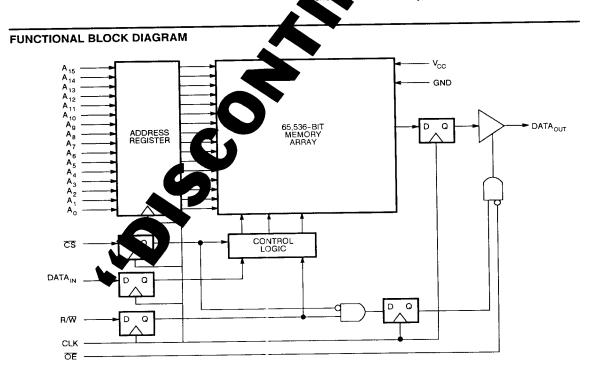

- Internal pipeline registers on Address, Data and control lines

- · Very fast write cycle time

- High-speed

- Military: 45ns (max.)

- Commercial: 35/45ns (max.)

- Low power consumption: 385mW (typ.)

- All inputs/outputs TTL-compatible ( $V_{OL} = 0.4V @ I_{OL} = 8mA$ )

- Separate, latched data input and output

- Three-state output

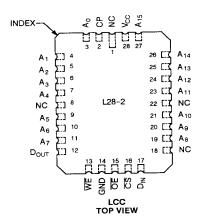

- Available in JEDEC standard 24-pin, 300 mil Sidebraze and Plastic DIP, 24-pin, 300 mil SOIC and 28-pin LCC

- Produced with advanced CEMOS<sup>™</sup> high-performance technology

- Military product compliant to MIL-STD-883, Class B

### **DESCRIPTION:**

The IDT71501 is a high-speed 64K x 1 static RAM synchronized with pipeline registers on the Address, Data, Chip Select ( $\overline{CS}$ ) and Write Enable ( $\overline{WE}$ ) pins. This product is designed to assist in the design of pipelined processif, yetems by removing the need for external pipeline registers. The internal registers offer speed improvements through high

Read cycle times are stass. 35ns, with higher speed Output Enable (OE) and Clock wild had Output functions to enable the high-speed system begin an aximum throughput possible in an efficient large errory pipelined system. Write cycles are as fast as 25ns. Fig. 1. The second of the property of of the prop

The IDT7150 packaged in industry standard 24-pin, 300 mil plastic a pram DIPs, as well as a 28-pin leadless chip carrier (LCC) and discounting the control of the control o

Mh. grade product is manufactured in compliance with the of MIL-STD-883, Class B, making it ideally suited to comperature applications demanding the highest level of perfections and reliability.

CEMOS is a trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**DECEMBER 1987**

© 1987 Integrated Device Technology, Inc.

4-215

DSC-1038/-

# PIN CONFIGURATIONS

### ABSOLUTE MAXIMUM RATINGS (1)

| SYMBOL            | RATING                                     | COMMERCIAL   | MILITARY      | UNIT |

|-------------------|--------------------------------------------|--------------|---------------|------|

| V <sub>TERM</sub> | Terminal Voltage<br>with Respect to<br>GND | -0.5 to +7.0 | -0.5 to + 7.0 | ٧    |

| TA                | Operating<br>Temperature                   | 0 to +70     | -55 to + 125  | °C   |

| T <sub>BIAS</sub> | Temperature<br>Under Bias                  | -55 to +125  | -65 to + 135  | °C   |

| T <sub>STG</sub>  | Storage<br>Temperature                     | -55 to +125  | -65 to + 150  | °C   |

| P <sub>T</sub>    | Power Dissipation                          | 1.0          | 1.0           | W    |

| lout              | DC Output Current                          | 50           | 50            | mA   |

### NOTE:

### CAPACITANCE (TA = +25°C, f = 1.0MHz)

| SYMBOL           | PARAMETER(1)       | CONDITIONS            | TYP. | UNIT |  |

|------------------|--------------------|-----------------------|------|------|--|

| C <sub>IN</sub>  | Input Capacitance  | V <sub>IN</sub> = 0V  | 8    | pF   |  |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0V | 8    | pF   |  |

### NOTE:

# RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| GRADE      | AMBIENT<br>TEMPERATURE | GND | V <sub>cc</sub> |

|------------|------------------------|-----|-----------------|

| Military   | -55°C to +125°C        | 0V  | 5.0V ± 10%      |

| Commercial | 0°C to +70°C           | ov  | 5.0V ± 10%      |

# RECOMMENDED DC OPERATING CONDITIONS

| SYMBOL          | PARAMETER          | MIN.                | TYP. | MAX. | UNIT |

|-----------------|--------------------|---------------------|------|------|------|

| V <sub>CC</sub> | Supply Voltage     | 4.5                 | 5.0  | 5.5  | ٧    |

| GND             | Supply Voltage     | 0                   | 0    | 0    | ٧    |

| V <sub>IH</sub> | Input High Voltage | 2.2                 | _    | 6.0  | ٧    |

| VIL             | Input Low Voltage  | -0.5 <sup>(1)</sup> | -    | 8.0  | ٧    |

#### NOTE:

1.  $V_{\rm IL} = -3.0V$  for pulse width less than 20ns.

Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress raiing only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

This parameter is determined by device characterization but is not production tested.

# DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE RANGE (V<sub>CC</sub> = 5.0V ±10%)

| SYMBOL                             | PARAMETER TEST CONDITIONS      |                                                                               | 18             | S IDT71501S<br>MIN. MAX. |            | UNIT |  |

|------------------------------------|--------------------------------|-------------------------------------------------------------------------------|----------------|--------------------------|------------|------|--|

| iiul                               | Input Leakage Current          | $V_{CC} = 5.5V$ , $V_{IN} = 0V$ to $V_{CC}$                                   | MIL.<br>COM'L. | _                        | 10<br>5    | μΑ   |  |

| II <sub>LO</sub> I                 | Output Leakage Current         | $\overline{CS} = V_{IH}, V_{O\cup T} = 0V \text{ to } V_{CC}$ $V_{CC} = Max.$ | MIL.<br>COM'L. | -                        | 10<br>5    | μА   |  |

| I <sub>CC1</sub>                   | Operating Power Supply Current | CS = V <sub>IL</sub> , Output Open<br>V <sub>CC</sub> = Max.                  | MIL.<br>COM'L. | _                        | 140<br>125 | mA   |  |

| l <sub>CC2</sub>                   | Dynamic Operating Current      | Min. Duty Cycle = 100% MIL. V <sub>CC</sub> = Max., Output Open COM'L.        |                | _                        | 140<br>125 | mA   |  |

|                                    |                                | I <sub>OL</sub> = 8mA, V <sub>CC</sub> = Min.                                 |                | _                        | 0.4        | v    |  |

| V <sub>OL</sub> Output Low Voltage |                                | I <sub>OL</sub> = 10mA, V <sub>CC</sub> = Min.                                |                | - "-                     | 0.5        |      |  |

| V <sub>OH</sub>                    | Output High Voltage            | I <sub>OL</sub> = -4mA, V <sub>CC</sub> = Min.                                |                | 2.4                      |            | V    |  |

# 4

### **ACTEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V       |

|-------------------------------|-------------------|

| Input Rise/Fall Times         | 5ns               |

| Input Timing Reference Levels | 1.5V              |

| Output Reference Levels       | 1.5V              |

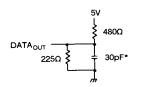

| Output Load                   | See Figures 1 & 2 |

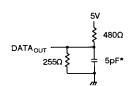

Figure 1. Output Load

Figure 2. Output Load (for tolz, tohz)

\*Including scope and jig.

# AC ELECTRICAL CHARACTERISTICS OVER THE **OPERATING TEMPERATURE AND SUPPLY VOLTAGE**

|                  |                                    | IDT71501\$35 |      | IDT71501S45<br>MIN. MAX. |              | UNIT |

|------------------|------------------------------------|--------------|------|--------------------------|--------------|------|

| SYMBOL           | PARAMETER                          | MIN.         | MAX. | MIN.                     | max.         | L    |

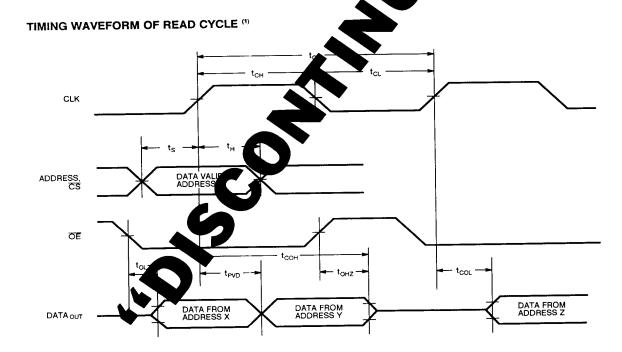

| READ CY          | CLE                                |              |      | <del> </del>             |              |      |

| t <sub>CP</sub>  | Clock Period (Read Cycle Time)     | 35           |      | 45                       |              | ns   |

| t <sub>CH</sub>  | Clock High Time                    | 7            |      | 7                        |              | ns   |

| t <sub>CL</sub>  | Clock Low Time                     | 7            |      | 7                        |              | ns   |

| ts               | Data, Address, WE, CS Set-up Time  | 5            |      | 5                        | <del>_</del> | ns   |

| t <sub>H</sub>   | Data, Address, WE, CS Hold Time    | 5            |      | 5                        |              | ns   |

| toLZ             | Output Low Z Time (1, 2)           | 0            |      | 0                        | _            | ns   |

| t <sub>OHZ</sub> | Output High Z Time (1, 2)          | _            | 15   |                          | 20           | ns   |

| t <sub>PVD</sub> | Prop. Delay, CLK to Valid Data Out | 13           |      | 1                        |              | ns   |

| t <sub>COL</sub> | Clock to Output in Low Z (2)       | 0            |      |                          |              | ns   |

| t <sub>GOH</sub> | Clock to Output in High Z (2)      | _            | 20   |                          | 25           | ns   |

### NOTES:

- 1. Transition is measured ±200mV from low or high impedance voltage with load (Figures 1 a

- 2. This parameter is guaranteed but not tested.

### NOTE:

1. The device must be selected by a CS level for the conditions above to take place.

# AC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE AND SUPPLY VOLTAGE

|                 |                                   | IDT71501S35 |      | IDT71501S45 |      | UNIT |  |  |

|-----------------|-----------------------------------|-------------|------|-------------|------|------|--|--|

| SYMBOL          | PARAMETER                         | MIN.        | MAX. | MIN.        | MAX. | UNIT |  |  |

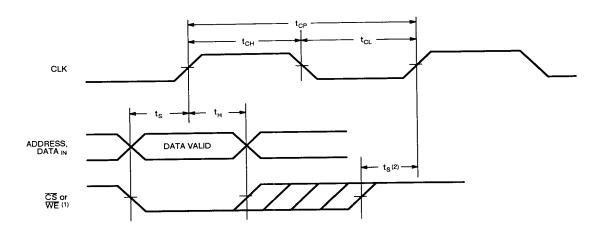

| WRITE CYCLE     |                                   |             |      |             |      |      |  |  |

| t <sub>CP</sub> | Clock Period (Write Cycle Time)   | 25          | _    | 35          |      | ns   |  |  |

| t <sub>CH</sub> | Clock High Time                   | 7           | _    | 7           |      | ns   |  |  |

| t <sub>CL</sub> | Clock Low Time                    | 7           |      | 7           |      | ns   |  |  |

| ts              | Data, Address, WE, CS Set-up Time | 5           |      | 5           |      | ns   |  |  |

| tu              | Data, Address, WE, CS Hold Time   | 5           | -    | 5           |      | ns   |  |  |

### TIMING WAVEFORM OF WRITE CYCLE

#### NOTES:

- 1. Either CS or WE can be used to trigger a write cycle, provided that the other signal is low at the same time.

- 2. When a write is terminated, either CS or WE must become high at least one ts before the next rising edge of CLK.

# TRUTH TABLE

|          | INPUT BEFORE CLK  |    |      |    |    | AFTER CLK_ |

|----------|-------------------|----|------|----|----|------------|

| MODE     | A <sub>0-15</sub> | cs | DIN  | WE | ŌĒ | Dout       |

| Read     | ADDR              | L  | X    | Н  | L  | Data       |

| Write    | ADDR              | L  | Data | L  | Х  | High Z     |

| Deselect | X                 | н  | х    | Х  | Х  | High Z     |

| Disable  | ×                 | Х  | ×    | Х  | Н  | High Z     |

4-219

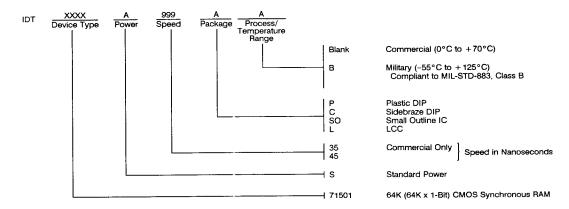

### **ORDERING INFORMATION**