# High Performance CMOS 5 x 7 Alphanumeric Displays

# Technical Data

#### **HCMS-29xx Series**

#### **Features**

- Easy to Use

- Interfaces Directly with Microprocessors

- 0.15" Character Height in 4, 8, and 16 (2x8) Character Packages

- 0.20" Character Height in 4 and 8 Character Packages

- Rugged X- and Y-Stackable Package

- Serial Input

- Convenient Brightness Controls

- Wave Solderable

- Offered in Five Colors

- Low Power CMOS Technology

- TTL Compatible

# **Description**

The HCMS-29xx series are high performance, easy to use dot matrix displays driven by on-board CMOS ICs. Each display can be directly interfaced with a microprocessor, thus eliminating the need for cumbersome interface components. The serial IC interface allows higher character count information displays with a minimum of data lines. A variety of colors, font heights, and character counts gives designers a wide range of product choices for their specific applications and the easy to read 5 x 7 pixel format allows the display of uppercase, lower case, Katakana, and custom userdefined characters. These displays are stackable in the x- and ydirections, making them ideal for high character count displays.

### **Applications**

- Telecommunications Equipment

- Portable Data Entry Devices

- Computer Peripherals

- Medical Equipment

- Test Equipment

- Business Machines

- Avionics

- Industrial Controls

#### **Device Selection Guide**

| Description           | AlGaAs<br>HCMS- | HER<br>HCMS- | Orange<br>HCMS- | Yellow<br>HCMS- | Green<br>HCMS- | Package<br>Drawing |

|-----------------------|-----------------|--------------|-----------------|-----------------|----------------|--------------------|

| 1 x 4 0.15" Character | 2905            | 2902         | 2904            | 2901            | 2903           | A                  |

| 1 x 8 0.15" Character | 2915            | 2912         | 2914            | 2911            | 2913           | В                  |

| 2 x 8 0.15" Character | 2925            | 2922         | 2924            | 2921            | 2923           | C                  |

| 1 x 4 0.20" Character | 2965            | 2962         | 2964            | 2961            | 2963           | D                  |

| 1 x 8 0.20" Character | 2975            | 2972         | 2974            | 2971            | 2973           | Е                  |

ESD WARNING: STANDARD CMOS HANDLING PRECAUTIONS SHOULD BE OBSERVED TO AVOID STATIC DISCHARGE.

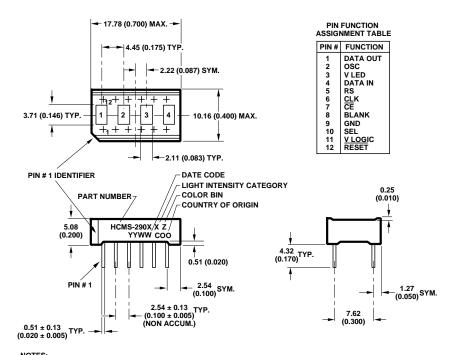

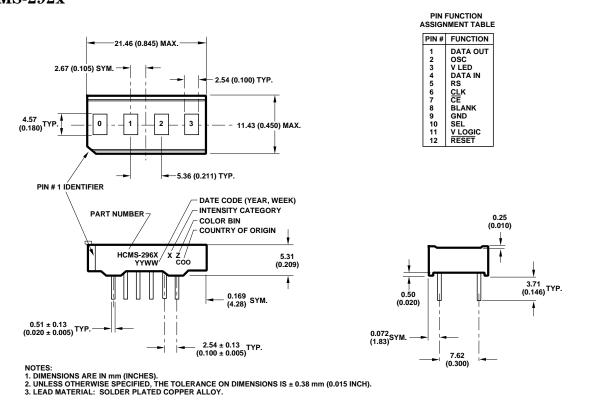

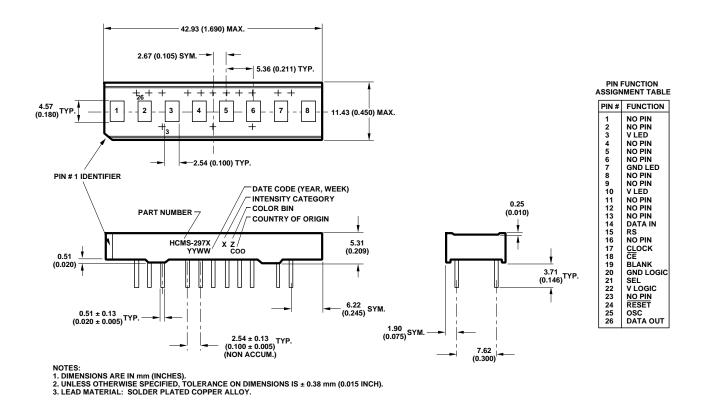

- NOTES: 1. DIMENSIONS ARE IN mm (INCHES). 2. UNLESS OTHERWISE SPECIFIED, TOLERANCE ON DIMENSIONS IS  $\pm$  0.38 mm (0.015 INCH). 3. LEAD MATERIAL: SOLDER PLATED COPPER ALLOY.

## HCMS-290x

PIN FUNCTION ASSIGNMENT TABLE

| SSIGNWENT TABLE                                                                                                                                                                                                                                                                  |                                                                                                                                                                                            |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIN#                                                                                                                                                                                                                                                                             | FUNCTION                                                                                                                                                                                   |  |  |  |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>110<br>111<br>122<br>133<br>14<br>155<br>166<br>177<br>181<br>192<br>20<br>21<br>22<br>22<br>23<br>24<br>25<br>26<br>26<br>26<br>27<br>28<br>29<br>29<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20<br>20 | NO PIN NO PIN V LED NO PIN ED ATA IN RS NO PIN CLOCK CE BLANK GND LOGIC SEL V LOGIC NO PIN RESET OSC DATA OUT |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                            |  |  |  |  |  |

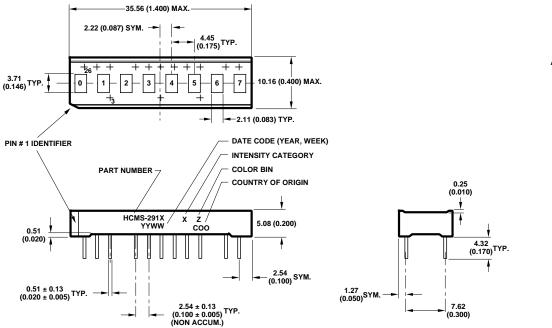

- NOTES: 1. DIMENSIONS ARE IN mm (INCHES). 2. UNLESS OTHERWISE SPECIFIED, TOLERANCE ON DIMENSIONS IS  $\pm$  0.38 mm (0.015 INCH). 3. LEAD MATERIAL: SOLDER PLATED COPPER ALLOY.

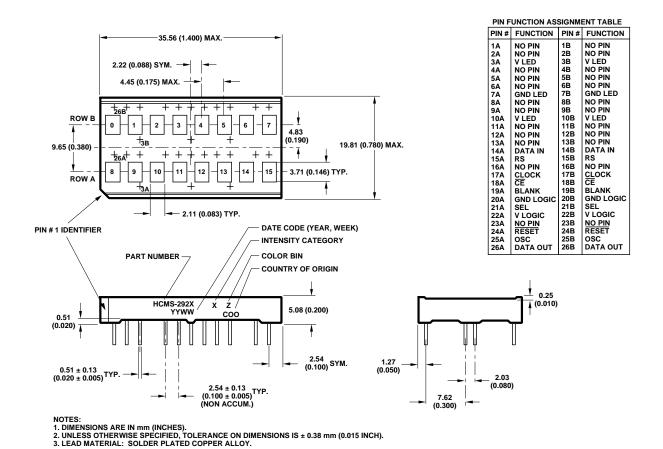

## HCMS-292x

HCMS-296x

## **HCMS-297x**

# **Absolute Maximum Ratings**

| Logic Supply Voltage, V <sub>LOGIC</sub> to GND <sub>LOGIC</sub>     |

|----------------------------------------------------------------------|

| LED Supply Voltage, $V_{LED}$ to $GND_{LED}$                         |

| Input Voltage, Any Pin to GND0.3 V to $V_{LOGIC} + 0.3 \text{ V}$    |

| Free Air Operating Temperature Range $T_A^{[1]}$ 40°C to +85°C       |

| Relative Humidity (non-condensing)                                   |

| Storage Temperature, $T_S$ 55°C to 100°C                             |

| Maximum Solder Temperature                                           |

| 1.59 mm (0.063 in.) Below Seating Plane, t < 5 sec260°C              |

| ESD Protection @ $1.5 \text{ k}\Omega$ , $100 \text{ pF}$ (each pin) |

| TOTAL Package Power Dissipation at $T_A = 25^{\circ}C^{[2]}$         |

| 4 character 1.2 W                                                    |

| 8 character                                                          |

| 16 character                                                         |

|                                                                      |

#### Notes:

1. For operation in high ambient temperatures, see Appendix A, Thermal Considerations.

# Recommended Operating Conditions Over Temperature Range (-40°C to +85°C)

| Parameter                                                        | Symbol         | Min. | Тур. | Max. | Units |

|------------------------------------------------------------------|----------------|------|------|------|-------|

| Logic Supply Voltage                                             | $V_{ m LOGIC}$ | 3.0  | 5.0  | 5.5  | V     |

| LED Supply Voltage                                               | $ m V_{LED}$   | 4.0  | 5.0  | 5.5  | V     |

| $\mathrm{GND}_{\mathrm{LED}}$ to $\mathrm{GND}_{\mathrm{LOGIC}}$ | _              | -0.3 | 0    | +0.3 | V     |

# Electrical Characteristics Over Operating Temperature Range (-40 $^{\circ}\text{C}$ to +85 $^{\circ}\text{C})$

|                                                                                                             |                          | T <sub>A</sub> =   | 25℃                | -40°C < T <sub>A</sub> < 85°C |                        |          |                                                                          |

|-------------------------------------------------------------------------------------------------------------|--------------------------|--------------------|--------------------|-------------------------------|------------------------|----------|--------------------------------------------------------------------------|

|                                                                                                             |                          | V <sub>LOGIC</sub> | = 5.0 V            |                               | $_{\rm OGIC}$ < 5.5 V  |          |                                                                          |

| Parameter                                                                                                   | Symbol                   | Typ.               | Max.               | Min.                          | Max.                   | Units    | Test Conditions                                                          |

| Input Leakage Current HCMS-290X/296X (4 char) HCMS-291X/297X (8 char) HCMS-292X (16 char)                   | II                       |                    | +7.5<br>+15<br>+15 | -2.5<br>-5.0<br>-5.0          | +50<br>+100<br>+100    | μА       | $V_{IN} = 0 \text{ V to } V_{LOGIC}$                                     |

| I <sub>LOGIC</sub> OPERATING<br>HCMS-290X/296X (4 char)<br>HCMS-291X/297X (8 char)<br>HCMS-292X (16 char)   | I <sub>LOGIC</sub> (OPT) | 0.4<br>0.8<br>0.8  | 2.5<br>5<br>5      |                               | 5<br>10<br>10          | mA       | $V_{\rm IN} = V_{ m LOGIC}$                                              |

| I <sub>LOGIC</sub> SLEEP <sup>[1]</sup> HCMS-290X/296X (4 char) HCMS-291X/297X (8 char) HCMS-292X (16 char) | I <sub>LOGIC</sub> (SLP) | 5<br>10<br>10      | 15<br>30<br>30     |                               | 25<br>50<br>50         | μА       | $V_{\rm IN} = V_{ m LOGIC}$                                              |

| I <sub>LED</sub> BLANK<br>HMCS-290X/296X (4 char)<br>HCMS-291X/297X (8 char)<br>HCMS-292X (16 char)         | I <sub>LED</sub> (BL)    | 2.0<br>4.0<br>4.0  | 4<br>8<br>8        |                               | 4.0<br>8<br>8          | mA       | BL = 0 V                                                                 |

| I <sub>LED</sub> SLEEP <sup>[1]</sup> HCMS-290X/296X (4 char) HCMS 291X/297X (8 char) HCMS-292X (16 char)   | I <sub>LED</sub> (SLP)   | 1<br>2<br>2        | 3<br>6<br>6        |                               | 50<br>100<br>100       | μА       |                                                                          |

| Peak Pixel Current <sup>[2]</sup> HCMS-29X5 (AlGaAs) HCMS-29XX (Other Colors)                               | $I_{PIXEL}$              | 15.4<br>14.0       | 17.1<br>15.9       |                               | 18.7<br>17.1           | mA<br>mA | V <sub>LED</sub> = 5.5 V<br>All pixels ON,<br>Average value per<br>pixel |

| HIGH level input voltage                                                                                    | V <sub>ih</sub>          |                    |                    | 2.0                           |                        | V        | $4.5 \text{ V} < \text{V}_{\text{LOGIC}} < 5.5 \text{ V}$                |

|                                                                                                             |                          |                    |                    | $0.8~V_{ m LOGIC}$            |                        | V        | $3.0 \text{ V} < V_{\text{LOGIC}} < 4.5 \text{ V}$                       |

| LOW level input voltage                                                                                     | V <sub>il</sub>          |                    |                    |                               | 0.8                    | V        | $4.5 \text{ V} < \text{V}_{\text{LOGIC}} < 5.5 \text{ V}$                |

|                                                                                                             |                          |                    |                    |                               | 0.2 V <sub>LOGIC</sub> | V        | $3.0 \text{ V} < V_{\text{LOGIC}} < 4.5 \text{ V}$                       |

| HIGH level output voltage                                                                                   | $V_{ m oh}$              |                    |                    | 2.0                           |                        | V        | $V_{LOGIC} = 4.5 \text{ V},$ $I_{oh} = -40 \mu\text{A}$                  |

|                                                                                                             |                          |                    |                    | $0.8~V_{LOGIC}$               |                        | V        | $3.0 \text{ V} < V_{\text{LOGIC}} < 4.5 \text{ V}$                       |

| LOW level output voltage                                                                                    | V <sub>ol</sub>          |                    |                    |                               | 0.4                    | V        | $V_{LOGIC} = 5.5 \text{ V},$<br>$I_{ol} = 1.6 \text{ mA}^{[3]}$          |

|                                                                                                             |                          |                    |                    |                               | $0.2~V_{LOGIC}$        | V        | $3.0 \text{ V} < V_{\text{LOGIC}} < 4.5 \text{ V}$                       |

| Thermal Resistance                                                                                          | $R\theta_{J-P}$          | 70                 |                    |                               |                        | °C/W     | IC junction to pin                                                       |

#### Notes

- 1. In SLEEP mode, the internal oscillator and reference current for LED drivers are off.

- 2. Average peak pixel current is measured at the maximum drive current set by Control Register 0. Individual pixels may exceed this value.

- 3. For the Oscillator Output,  $I_{\rm ol}$  = 40  $\mu A.$

# Optical Characteristics at $25^{\circ}C^{[1]}$

$\rm V_{\rm LED} = 5.0$  V, 50% Peak Current, 100% Pulse Width

|                     |             | Luminous Intensity<br>per LED <sup>[2]</sup><br>Character Average (µcd) |      | Peak<br>Wavelength<br>λ <sub>Peak</sub> (nm) | Dominant Wavelength $\lambda_d^{[3]}$ (nm) |

|---------------------|-------------|-------------------------------------------------------------------------|------|----------------------------------------------|--------------------------------------------|

| Display Color       | Part Number | Min.                                                                    | Typ. | Typ.                                         | Typ.                                       |

| AlGaAs Red          | HCMS-29X5   | 95                                                                      | 230  | 645                                          | 637                                        |

| High Efficiency Red | HCMS-29X2   | 29                                                                      | 64   | 635                                          | 626                                        |

| Orange              | HCMS-29X4   | 29                                                                      | 64   | 600                                          | 602                                        |

| Yellow              | HCMS-29X1   | 29                                                                      | 64   | 583                                          | 585                                        |

| Green               | HCMS-29X3   | 57                                                                      | 114  | 568                                          | 574                                        |

#### Notes:

- 1. Refers to the initial case temperature of the device immediately prior to measurement.

- 2. Measured with all LEDs illuminated.

- 3. Dominant wavelength,  $\lambda_d$ , is derived from the CIE chromaticity diagram and represents the single wavelength which defines the perceived LED color.

# **Electrical Description**

| Pin Function                    | Description                                                                                                                                                                                                                                  |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET (RST)                     | Sets Control Register bits to logic low. The Dot Register contents are unaffected by the Reset pin. (logic low = reset; logic high = normal operation).                                                                                      |

| DATA IN $(D_{IN})$              | Serial Data input for Dot or Control Register data. Data is entered on the rising edge of the Clock input.                                                                                                                                   |

| DATA OUT ( $D_{OUT}$ )          | Serial Data output for Dot or Control Register data. This pin is used for cascading multiple displays.                                                                                                                                       |

| CLOCK (CLK)                     | Clock input for writing Dot or Control Register data. When Chip Enable is logic low, data is entered on the rising Clock edge.                                                                                                               |

| REGISTER SELECT (RS)            | Selects Dot Register (RS = logic low) or Control Register (RS = logic high) as the destination for serial data entry. The logic level of RS is latched on the falling edge of the $\overline{\text{Chip}}$ $\overline{\text{Enable}}$ input. |

| CHIP ENABLE (CE)                | This input must be a logic low to write data to the display. When $\overline{\text{CE}}$ returns to logic high and CLK is logic low, data is latched to either the LED output drivers or a Control Register.                                 |

| OSCILLATOR SELECT (SEL)         | Selects either an internal or external display oscillator source.<br>(logic low = External Display Oscillator; logic high = Internal Display Oscillator).                                                                                    |

| OSCILLATOR (OSC)                | Output for the Internal Display Oscillator (SEL = logic high) or input for an External Display Oscillator (SEL = logic low).                                                                                                                 |

| BLANK (BL)                      | Blanks the display when logic high. May be modulated for brightness control.                                                                                                                                                                 |

| $\mathrm{GND}_{\mathrm{LED}}$   | Ground for LED drivers.                                                                                                                                                                                                                      |

| $\mathrm{GND}_{\mathrm{LOGIC}}$ | Ground for logic.                                                                                                                                                                                                                            |

| $V_{ m LED}$                    | Positive supply for LED drivers.                                                                                                                                                                                                             |

| $V_{ m LOGIC}$                  | Positive supply for logic.                                                                                                                                                                                                                   |

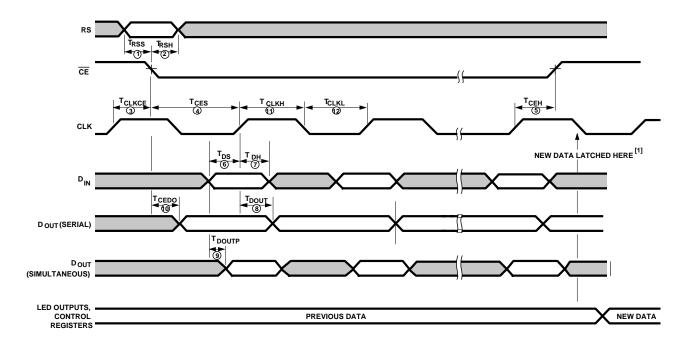

# AC Timing Characteristics Over Temperature Range (-40°C to +85°C)

| Timing<br>Diagram<br>Ref.<br>Number | Description                                                                          | Symbol             | 4.5 V < V <sub>L0</sub> | <sub>OGIC</sub> <5.5 V<br>  Max. | V <sub>LOGIO</sub><br>Min. | g = 3 V<br>Max. | Units |

|-------------------------------------|--------------------------------------------------------------------------------------|--------------------|-------------------------|----------------------------------|----------------------------|-----------------|-------|

| 1                                   | Register Select Setup Time to Chip Enable                                            | t <sub>rss</sub>   | 10                      | Mux                              | 10                         | www.            | ns    |

| 2                                   | Register Select Hold Time to Chip Enable                                             | $t_{ m rsh}$       | 10                      |                                  | 10                         |                 | ns    |

| 3                                   | Rising Clock Edge to Falling<br>Chip Enable Edge                                     | ${ m t_{clkce}}$   | 20                      |                                  | 20                         |                 | ns    |

| 4                                   | Chip Enable Setup Time to<br>Rising Clock Edge                                       | $t_{ces}$          | 35                      |                                  | 55                         |                 | ns    |

| 5                                   | Chip Enable Hold Time to<br>Rising Clock Edge                                        | $t_{\rm ceh}$      | 20                      |                                  | 20                         |                 | ns    |

| 6                                   | Data Setup Time to Rising<br>Clock Edge                                              | $t_{ m ds}$        | 10                      |                                  | 10                         |                 | ns    |

| 7                                   | Data Hold Time after Rising<br>Clock Edge                                            | t <sub>dh</sub>    | 10                      |                                  | 10                         |                 | ns    |

| 8                                   | Rising Clock Edge to D <sub>OUT</sub> [1]                                            | $t_{ m dout}$      | 10                      | 40                               | 10                         | 65              | ns    |

| 9                                   | Propagation Delay $D_{IN}$ to $D_{OUT}$<br>Simultaneous Mode for<br>one $IC^{[1,2]}$ | $t_{ m doutp}$     |                         | 18                               |                            | 30              | ns    |

| 10                                  | CE Falling Edge to D <sub>OUT</sub> Valid                                            | $t_{ m cedo}$      |                         | 25                               |                            | 45              | ns    |

| 11                                  | Clock High Time                                                                      | ${ m t_{clkh}}$    | 80                      |                                  | 100                        |                 | ns    |

| 12                                  | Clock Low Time                                                                       | ${ m t_{clkl}}$    | 80                      |                                  | 100                        |                 | ns    |

|                                     | Reset Low Time                                                                       | t <sub>rstl</sub>  | 50                      |                                  | 50                         |                 | ns    |

|                                     | Clock Frequency                                                                      | F <sub>cyc</sub>   |                         | 5                                |                            | 4               | MHz   |

|                                     | Internal Display Oscillator<br>Frequency                                             | F <sub>inosc</sub> | 80                      | 210                              | 80                         | 210             | KHz   |

|                                     | Internal Refresh Frequency                                                           | $F_{rf}$           | 150                     | 410                              | 150                        | 400             | Hz    |

|                                     | External Display Oscillator Frequency Prescaler = 1                                  | F <sub>exosc</sub> | 51.2                    | 1000                             | 51.2                       | 1000            | KHz   |

|                                     | Prescaler = 8                                                                        |                    | 410                     | 8000                             | 410                        | 8000            | KHz   |

### **Notes:**

<sup>1.</sup> Timing specifications increase  $0.3\ \mathrm{ns}$  per pf of capacitive loading above  $15\ \mathrm{pF}.$

<sup>2.</sup> This parameter is valid for Simultaneous Mode data entry of the Control Register.

# **Display Overview**

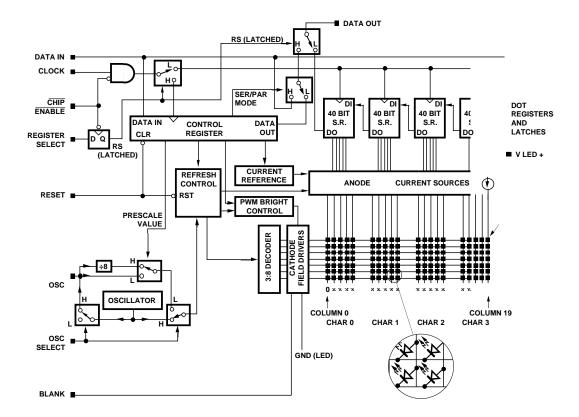

The HCMS-29xx series is a family of LED displays driven by on-board CMOS ICs. The LEDs are configured as 5 x 7 font characters and are driven in groups of 4 characters per IC. Each IC consists of a 160-bit shift register (the Dot Register), two 7-bit Control Words, and refresh circuitry. The Dot Register contents are mapped on a one-to-one basis to the display. Thus, an individual Dot Register bit uniquely controls a single LED.

8-character displays have two ICs that are cascaded. The Data Out line of the first IC is internally connected to the Data In line of the second IC forming a 320-bit Dot Register. The display's other control and power lines are connected directly to both ICs. In 16-character displays, each row functions as an independent 8-character display with its own 320-bit Dot Register.

#### Reset

Reset initializes the Control Registers (sets all Control Register bits to logic low) and places the display in the sleep mode. The Reset pin should be connected to the system power-on reset circuit. The Dot Registers are not cleared upon power-on or by Reset. After power-on, the Dot Register contents are random; however, Reset will put the display in sleep mode, thereby blanking the LEDs. The Control Register and the Control Words are cleared to all zeros by Reset.

To operate the display after being Reset, load the Dot Register with logic lows. Then load Control Word 0 with the desired brightness level and set the sleep mode bit to logic high.

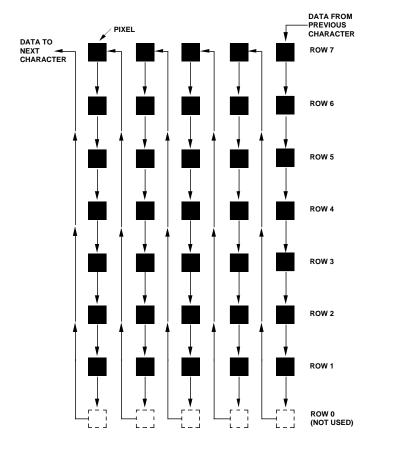

## **Dot Register**

The Dot Register holds the pattern to be displayed by the

LEDs. Data is loaded into the Dot Register according to the procedure shown in Table 1 and the Write Cycle Timing Diagram.

First RS is brought low, then  $\overline{\text{CE}}$  is brought low. Next, each successive rising CLK edge will shift in the data at the  $D_{\text{IN}}$  pin. Loading a logic high will turn the corresponding LED on; a logic low turns the LED off. When all 160 bits have been loaded (or 320 bits in an 8-digit display),  $\overline{\text{CE}}$  is brought to logic high.

When CLK is next brought to logic low, new data is latched into the display dot drivers. Loading data into the Dot Register takes place while the previous data is displayed and eliminates the need to blank the display while loading data.

#### Pixel Map

In a 4-character display, the 160-bits are arranged as 20

| Table 1. | Register | Truth | <b>Table</b> |

|----------|----------|-------|--------------|

|----------|----------|-------|--------------|

| Function                                  | CLK        | CE           | RS |

|-------------------------------------------|------------|--------------|----|

| Select Dot Register                       | Not Rising | $\downarrow$ | L  |

|                                           | 1          | L            | X  |

| Copy Data from Dot Register to Dot Latch  | L          | Н            | X  |

| Select Control Register                   | Not Rising | <b>\</b>     | Н  |

| Load Control Register <sup>[1][3]</sup>   | 1          | L            | X  |

| Latch Data to Control Word <sup>[2]</sup> | L          | 1            | X  |

#### Notes:

- 1. BIT D<sub>0</sub> of Control Word 1 must have been previously set to Low for serial mode or High for simultaneous mode.

- 2. Selection of Control Word 1 or Control Word 0 is set by  $D_7$  of the Control Shift Register. The unselected control word retains its previous value.

- 3. Control Word data is loaded Most Significant Bit  $(D_7)$  first.

NOTE:

1. DATA IS COPIED TO THE CONTROL REGISTER OR THE DOT LATCH AND LED OUTPUTS WHEN CE IS HIGH AND CLK IS LOW.

# **HCMS-29xx Write Cycle Diagram**

columns by 8 rows. This array can be conceptualized as four 5 x 8 dot matrix character locations, but only 7 of the 8 rows have LEDs (see Figures 1 & 2). The bottom row (row 0) is not used. Thus, latch location 0 is never displayed. Column 0 controls the left-most column. Data from Dot Latch locations 0-7 determine whether or not pixels in Column 0 are turned-on or turned-off. Therefore, the lower left pixel is turned-on when a logic high is stored in Dot Latch location 1. Characters are loaded in serially, with the left-most character being loaded first and the right-most character being loaded last. By loading one character at a time and latching the data before loading the next character, the figures will appear to scroll from right to left.

# **Control Register**

The Control Register allows software modification of the IC's operation and consists of two independent 7-bit control words. Bit  $D_7$  in the shift register selects one of the two 7-bit control words. Control Word 0 performs pulse width modulation brightness control, peak pixel current brightness control, and sleep mode. Control Word 1 sets serial/simultaneous data out mode, and external oscillator prescaler. Each function is independent of the others.

# **Control Register Data Loading**

Data is loaded into the Control Register, MSB first, according to the procedure shown in Table 1 and the Write Cycle Timing Diagram. First, RS is brought to logic high and then  $\overline{\text{CE}}$  is brought to logic low. Next, each successive rising CLK edge will shift in the data on the  $D_{\text{IN}}$  pin. Finally, when 8 bits have been loaded, the CE line is brought to logic high. When CLK goes to logic low, new data is copied into the selected control word. Loading data into the Control Register takes place while the previous control word configures the display.

#### **Control Word 0**

Loading the Control Register with  $D_7$  = Logic low selects Control Word 0 (see Table 2). Bits  $D_0$ - $D_3$  adjust the display brightness by pulse width modulating the LED on-time, while Bits  $D_4$ - $D_5$  adjust the display brightness by changing the peak pixel current. Bit  $D_6$  selects normal operation or sleep mode.

Figure 1.

Figure 2.

Sleep mode (Control Word 0, bit  $D_6 = Low$ ) turns off the Internal Display Oscillator and the LED pixel drivers. This mode is used when the IC needs to be powered up, but does not need to be active. Current draw in sleep mode is nearly zero. Data in the Dot Register and Control Words are retained during sleep mode.

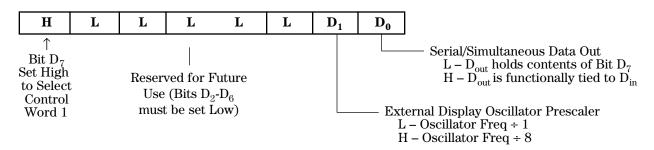

### **Control Word 1**

Loading the Control Register with  $D_7$  = logic high selects Control Word 1. This Control Word performs two functions: serial/simultaneous data out mode and external oscillator prescale select (see Table 2).

# Serial/Simultaneous Data Output D<sub>0</sub>

Bit  $D_0$  of control word 1 is used to switch the mode of  $D_{OUT}$  between serial and simultaneous data entry during Control Register writes. The default mode (logic low) is the serial  $D_{OUT}$  mode. In serial mode,  $D_{OUT}$  is connected to the last bit ( $D_7$ ) of the Control Shift Register.

Storing a logic high to bit  $D_0$  changes  $D_{OUT}$  to simultaneous mode which affects the Control Register only. In simultaneous mode,  $D_{OUT}$  is logically connected to  $D_{IN}$ . This arrangement allows multiple ICs to have their Control Registers written to simultaneously. For example, for N ICs in the serial mode, N \* 8 clock pulses are needed to load the

same data in all Control Registers. In the simultaneous mode, N ICs only need 8 clock pulses to load the same data in all Control Registers. The propagation delay from the first IC to the last is N \*  $t_{\rm DOUTP}$ .

# External Oscillator Prescaler Bit D<sub>1</sub>

Bit D<sub>1</sub> of Control Word 1 is used to scale the frequency of an external Display Oscillator. When this bit is logic low, the external Display Oscillator directly sets the internal display clock rate. When this bit is a logic high, the external oscillator is divided by 8. This scaled frequency then sets the internal display clock rate. It takes 512 cycles of the display clock (or  $8 \times 512 = 4096$  cycles of an external clock with the divide by 8 prescaler) to completely refresh the display once. Using the prescaler bit allows the designer to use a higher external oscillator frequency without extra circuitry.

This bit has no affect on the internal Display Oscillator Frequency.

# Bits D<sub>2</sub>-D<sub>6</sub>

These bits must always be programmed to logic low.

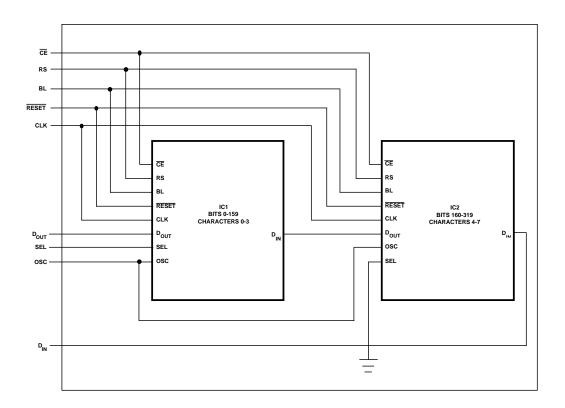

#### Cascaded ICs

Figure 3 shows how two ICs are connected within an HCMS-29XX display. The first IC controls the four left-most characters and the second IC controls the four

right-most characters. The Dot Registers are connected in series to form a 320-bit dot shift register. The location of pixel 0 has not changed. However, Dot Shift Register bit 0 of IC2 becomes bit 160 of the 320-bit dot shift register.

The Control Registers of the two ICs are independent of each other. This means that to adjust the display brightness the same control word must be entered into both ICs, unless the Control Registers are set to simultaneous mode.

Longer character string systems can be built by cascading multiple displays together. This is accomplished by creating a five line bus. This bus consists of  $\overline{CE}$ , RS, BL, Reset, and CLK. The display pins are connected to the corresponding bus line. Thus, all  $\overline{\text{CE}}$  pins are connected to the  $\overline{\text{CE}}$ bus line. Similarly, bus lines for RS, BL, Reset, and CLK are created. Then  $D_{IN}$  is connected to the right-most display. D<sub>OUT</sub> from this display is connected to the next display. The left-most display receives its  $\boldsymbol{D}_{IN}$  from the  $\boldsymbol{D}_{OUT}$  of the display to its right. D<sub>OUT</sub> from the left-most display is not used.

Each display may be set to use its internal oscillator, or the displays may be synchronized by setting up one display as the master and the others as slaves. The slaves are set to receive their oscillator input from the master's oscillator output.

**Table 2. Control Shift Register**

## CONTROL WORD 0

| L                                                                                                                 | $\mathbf{D_6}$ | $\mathbf{D_5}$   | $\mathbf{D_4}$           | $\mathbf{D}_3$                                      | $\mathbf{D_2}$                                           | $\mathbf{D_1}$                                                     | $\mathbf{D_0}$                                           |                                                                                      |                                                                                                             |                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------|----------------|------------------|--------------------------|-----------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| $\begin{array}{c} \uparrow \\ \text{Bit D}_7 \\ \text{Set Low} \\ \text{to Select} \\ \text{Control} \end{array}$ |                |                  |                          | ]                                                   | PWM Br<br>Con                                            | <br>rightnes<br>itrol                                              | 6S                                                       | On-Time<br>Oscillator<br>Cycles                                                      | Duty<br>Factor<br>(%)                                                                                       | Relative<br>Brightness<br>(%)                                                                       |

| Word 0                                                                                                            |                |                  |                          | L<br>L<br>L<br>L<br>L<br>H<br>H<br>H<br>H<br>H<br>H | L<br>L<br>L<br>H<br>H<br>H<br>L<br>L<br>L<br>H<br>H<br>H | L<br>H<br>H<br>L<br>L<br>H<br>H<br>L<br>L<br>H<br>H<br>H<br>L<br>H | L<br>H<br>L<br>H<br>L<br>H<br>L<br>H<br>L<br>H<br>L<br>H | 0<br>1<br>2<br>3<br>4<br>5<br>7<br>9<br>11<br>14<br>18<br>22<br>28<br>36<br>48<br>60 | 0<br>0.2<br>0.4<br>0.6<br>0.8<br>1.0<br>1.4<br>1.8<br>2.1<br>2.7<br>3.5<br>4.3<br>5.5<br>7.0<br>9.4<br>11.7 | 0<br>1.7<br>3.3<br>5.0<br>6.7<br>8.3<br>11.7<br>15<br>18<br>23<br>30<br>37<br>47<br>60<br>80<br>100 |

|                                                                                                                   |                | Brigh            | Current<br>tness<br>trol | Typ<br>Pix                                          | pical Pea<br>el Curre<br>(mA)                            | ent                                                                | Sca                                                      | lative Full<br>lle Current<br>e Brightness, %)                                       |                                                                                                             |                                                                                                     |

|                                                                                                                   |                | H<br>L<br>L<br>H | L<br>H<br>L<br>H         |                                                     | 4.0<br>6.4<br>9.3<br>12.8                                |                                                                    |                                                          | 31<br>50<br>73 (Default at 1<br>100                                                  | Power Up)                                                                                                   | )                                                                                                   |

| SLE                                                                                                               | EP MO          | DE               | L – DIS                  | SABLES                                              | INTERN                                                   | NAL OSC                                                            | CILLATO                                                  | R-DISPLAY BLANI                                                                      | K                                                                                                           |                                                                                                     |

## CONTROL WORD 1

H - NORMAL OPERATION

Figure 3. Cascaded ICs.

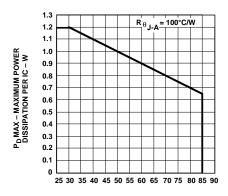

# Appendix A. Thermal Considerations

The display IC has a maximum junction temperature of  $150^{\circ}$ C. The IC junction temperature can be calculated with Equation 1 below.

A typical value for  $R\theta_{JA}$  is  $100^{\circ}\text{C/W}$ . This value is typical for a display mounted in a socket and covered with a plastic filter. The socket is soldered to a .062 in. thick PCB with .020 inch wide, one ounce copper traces.

$P_{\rm D}$  can be calculated as Equation 2 below.

Figure 4 shows how to derate the power of one IC versus ambient temperature. Operation at high ambient temperatures may require the power per IC to be reduced. The power consumption can be reduced by changing either the N,  $I_{PIXEL}$ , Osc cyc or  $V_{LED}$ . Changing  $V_{LOGIC}$  has very little impact on the power consumption.

TA - AMBIENT TEMPERATURE - °C

Figure 4.

### **Equation 1:**

$T_{J}MAX = T_{A} + P_{D} * R\theta_{JA}$

Where:

$T_{I}MAX = maximum IC junction temperature$

$T_A$  = ambient temperature surrounding the display

$R\theta_{JA}$  = thermal resistance from the IC junction to ambient

$P_D$  = power dissipated by the IC

#### **Equation 2:**

$P_{D} = (N * I_{PIXEL} * Duty Factor * V_{LED}) + I_{LOGIC} * V_{LOGIC}$

Where:

$P_D$  = total power dissipation

N = number of pixels on (maximum 4 char \* 5 \* 7 = 140)

$I_{PIXEL}$  = peak pixel current.

Duty Factor = 1/8 \* Osccyc/64

Osc cyc = number of ON oscillator cycles per row

$I_{LOGIC} = IC logic current$

$V_{LOGIC}$  = logic supply voltage

#### **Equation 3:**

$I_{\rm PEAK} = M * 20 * I_{\rm PIXEL}$

Where:

$I_{PEAK}$  = maximum instantaneous peak current for the display

M = number of ICs in the system

20 = maximum number of LEDs on per IC

$I_{PIXEL}$  = peak current for one LED

#### **Equation 4:**

$I_{LED}(AVG) = N * I_{PIXEL} * 1/8 * (oscillator cycles)/64$

(see Variable Definitions above)

# Appendix B. Electrical Considerations

#### **Current Calculations**

The peak and average display current requirements have a significant impact on power supply selection. The maximum peak current is calculated with Equation 3 below.

The average current required by the display can be calculated with Equation 4 below.

The power supply has to be able to supply  $I_{PEAK}$  transients and supply  $I_{LED}(AVG)$  continuously. The range on  $V_{LED}$  allows noise on this supply without significantly changing the display brightness.

# **V<sub>LOGIC</sub>** and **V<sub>LED</sub>** Considerations

The display uses two independent electrical systems. One system is used to power the display's logic and the other to power the display's LEDs. These two systems keep the logic supply clean.

Separate electrical systems allow the voltage applied to  $V_{LED}$  and  $V_{LOGIC}$  to be varied independently. Thus,  $V_{LED}$  can vary from 0 to 5.5 V without affecting either the Dot or the Control Registers.  $V_{LED}$  can

be varied between 4.0 to 5.5 V without any noticeable variation in light output. However, operating  $V_{\rm LED}$  below 4.0 V may cause objectionable mismatch between the pixels and is not recommended. Dimming the display by pulse width modulating  $V_{\rm LED}$  is also not recommended.

V<sub>LOGIC</sub> can vary from 3.0 to 5.5 V without affecting either the displayed message or the display intensity. However, operation below 4.5 V will change the timing and logic levels and operation below 3 V may cause the Dot and Control Registers to be altered.

The logic ground is internally connected to the LED ground by a substrate diode. This diode becomes forward biased and conducts when the logic ground is 0.4 V greater then the LED ground. The LED ground and the logic ground should be connected to a common ground which can withstand the current introduced by the switching LED drivers. When separate ground connections are used, the LED ground can vary from -0.3 V to +0.3 V with respect to the logic ground. Voltages below -0.3 V can cause all the dots to be ON. Voltage above +0.3 V can cause dimming and dot mismatch. The LED ground for the LED drivers can be routed separately from the logic ground until an appropriate ground plane is available. On long interconnections between the display and the host system, voltage drops on the analog ground can be kept from affecting the display logic levels by isolating the two grounds.

#### **Electrostatic Discharge**

The inputs to the ICs are protected against static discharge and input current latchup. However, for best results, standard CMOS handling precautions should be used. Before use, the HCMS-29XX should be stored in antistatic tubes or in conductive material. During assembly, a grounded conductive work area should be used and assembly personnel should wear conductive wrist straps. Lab coats made of synthetic material should be avoided since they are prone to static buildup. Input current latchup is caused when the CMOS inputs are subjected to either a voltage below ground ( $V_{IN}$  < ground) or to a voltage higher then  $V_{\rm LOGIC} \ (V_{\rm IN} > V_{\rm LOGIC})$  and when a high current is forced into the input. To prevent input current latchup and ESD damage, unused inputs should be connected to either ground or V<sub>LOGIC</sub>. Voltages should not be applied to the inputs until V<sub>LOGIC</sub> has been applied to the display.

#### Appendix C. Oscillator

The oscillator provides the internal refresh circuitry with a signal that is used to synchronize the columns and rows. This ensures that the right data is in the dot drivers for that row. This signal can be supplied from either an external source or the internal source.

A display refresh rate of  $100~\mathrm{Hz}$  or faster ensures flicker-free operation. Thus for an external oscillator the frequency should be greater than or equal to  $512~\mathrm{x}$   $100~\mathrm{Hz} = 51.2~\mathrm{kHz}$ . Operation above  $1~\mathrm{MHz}$  without the

prescaler or 8 MHz with the prescaler may cause noticeable pixel to pixel mismatch.

# Appendix D. Refresh Circuitry

This display driver consists of 20 one-of-eight column decoders and 20 constant current sources, 1 one-of-eight row decoder and eight row sinks, a pulse width modulation control block, a peak current control block, and the circuit to refresh the LEDs. The refresh counters and oscillator are used to synchronize the columns and rows.

The 160 bits are organized as 20 columns by 8 rows. The IC illuminates the display by sequentially turning ON each of the 8 row-drivers. To refresh the display once takes 512 oscillator cycles. Because there are eight row drivers, each row driver is selected for 64 (512/8) oscillator cycles. Four cycles are used to briefly blank the display before the following row is switched on. Thus, each row is ON for 60 oscillator cycles out of a possible 64. This corresponds to the maximum LED on time.

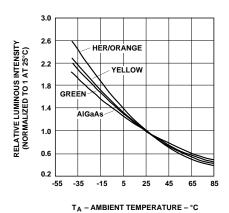

# Appendix E. Display Brightness

Two ways have been shown to control the brightness of this LED display: setting the peak current and setting the duty factor. Both values are set in Control Word 0. To compute the resulting display brightness when both PWM and peak current control are used, simply multiply the two relative brightness factors. For example, if Control Register 0 holds the word 1001101, the peak current

Figure 5.

is 73% of full scale (BIT  $D_5 = L$ , BIT  $D_4 = L$ ) and the PWM is set to 60% duty factor (BIT  $D_3 = H$ , BIT  $D_2 = H$ , BIT  $D_1 = L$ , BIT  $D_0 = H$ ). The resulting brightness is 44% (.73 x .60 = .44) of full scale.

The temperature of the display will also affect the LED brightness as shown in Figure 5.

## Appendix F. Reference Material

Application Note 1027: Soldering  $LED\ Components$

Application Note 1015: Contrast Enhancement Techniques for LED Displays