# Reprogrammable 16K x 16 Processor-Intelligent PROM

#### **Features**

- 0.8-micron CMOS for optimum speed/power

- High speed (for commercial and military)

- -25-ns single access time

- 11-ns burst access time

- 16-bit-wide words

- Input address registered, latched, or transparent

- On-chip programmable burst logic

- Programmable compatibility with many common microprocessors

- Three programmable chip selects

- Programmable output enable

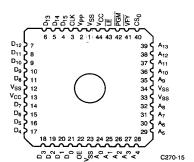

- 44-pin PLCC and 44-pin LCC packages

- 100% reprogrammable in windowed packages

- TTL-compatible I/O

- Capable of withstanding greater than 2001V static discharge

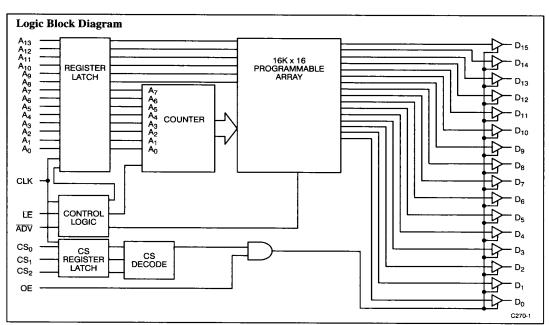

#### **Functional Description**

The CY7C270 is a 16K-word by 16-bit PROM designed to support a number of popular microprocessors with little or no "glue" logic. This PROM is packaged in a 44-pin PLCC package and a 44-pin LCC package. The CY7C270 is available in windowed packages for 100% reprogrammability. The memory cells utilize proven EPROM floating-gate technology.

The CY7C270 offers a number of programmable features that allow the user to configure the PROM for use with their

chosen microprocessor. The programmable features include a choice between registered and latched modes of operation. The CY7C270 also has an on-board programmable counter for burst reads. The user may select a 2-bit, 4-bit, or 8-bit linear counter, or program the PROM to use the Intel 80486 burst pattern (*Table* 2). A separate control input (ADV) is used to choose between single reads and bursts. In addition, the burst counter and latch may be bypassed for asynchronous operation to be used with DSP processors.

The CY7C270 allows the user to independently program the polarity of each chip select (CS<sub>2</sub> – CS<sub>0</sub>). This provides on-chip decoding of up to eight banks of PROM. The polarity of the asynchronous output enable pin (OE) is also programmable.

#### Selection Guide

|                           |            | CY7C270-15 | CY7C270-20 | CY7C270-30 |

|---------------------------|------------|------------|------------|------------|

| Minimum Clock Period (ns) | "-         | 15         | 20         | 30         |

| Maximum Operating         | Commercial | 175        | 175        | 175        |

| Current (mA)              | Military   | 200        | 200        | 200        |

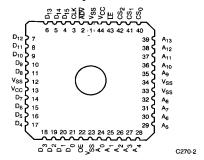

### Pin Configuration

#### LCC/PLCC (Opaque Only) Top View

# **Operating Modes**

The CY7C270 can be specifically configured for use with many popular microprocessors. The PROM configuration for some of these processors is detailed in *Table 1*. Note that many of the processors can use either registered or latched mode depending on their speed.

Table 1. Processor-Intelligent PROM Configuration

| Processor      | Registered/Latched | Burst Counter              |

|----------------|--------------------|----------------------------|

| SPARC          | Registered         |                            |

| Intel 486      | Latched            | Table Logic <sup>[1]</sup> |

| 80386          | Latched            | _                          |

| Motorola 68040 | Latched            | 2-Bit Counter              |

| Motorola 68030 | Latched            | 2-Bit Counter              |

| Intel 80960KB  | Registered         | 2-Bit Counter              |

| Intel 80960CA  | Latched            | 2-Bit Counter              |

| AMD 29000      | Latched            | 8-Bit Counter              |

| MIPS R3000     | Registered         | _                          |

| MIPS R2000     | Registered         | _                          |

| Motorola 88000 | Registered         | _                          |

#### Note:

The Intel 486 uses a non-sequential burst. The CY7C270 is equipped with a look-up table (described in Table 2) for use with this processor.

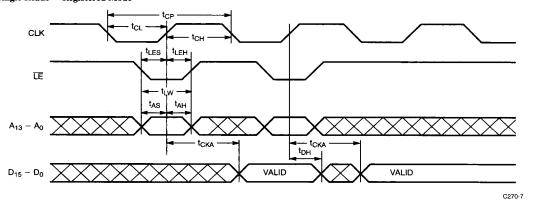

### Single Read Access in Registered Mode

A read access is initiated in registered mode on the rising edge of CLK if all three chip selects are asserted and  $\overline{LE}$  is sampled LOW. The address applied to the input is stored in a register and is delivered to both the PROM core and the counter. The contents of the memory location accessed by the original address are delivered to the outputs. When  $\overline{LE}$  is asserted the system ignores the advance enable  $(\overline{ADV})$  input.

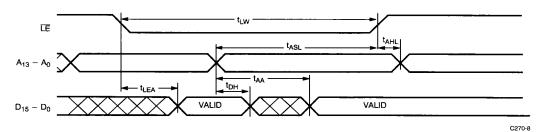

### Single Read Access in Latched Mode

In latched mode, the CY7C270 can take advantage of situations where the address is available well before the rising edge of CLK. A read is initiated when the latch is opened (on the falling edge of  $\overline{\rm LE}$ ). The address is sent directly to the PROM core and to the counter. The contents of the memory location addressed by the original address are delivered to the outputs. The latch is closed when  $\overline{\rm LE}$  is deasserted.

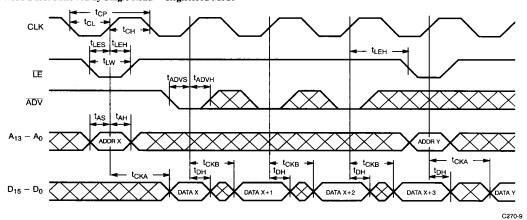

#### **Burst Sequence**

During a burst, the first read is initiated as a single access read. After the initial read, the  $\overline{LE}$  input is held inactive. The advance enable input  $(\overline{ADV})$  controls the address sequencing starting with the second read.  $\overline{ADV}$  is sampled on the rising edge of the CLK input. If  $\overline{ADV}$  is sampled LOW, the address is incremented to the next location. The number of address bits incremented by the counter is programmed by the user. The counter wraps around after reaching the maximum count without affecting other bits in the address.

Special burst advancement logic is included in the CY7C270 to support the Intel 80486 burst operation. The 80486 bursts in the non-sequential pattern shown in *Table 2*.

Some processors have the capability to suspend a burst. In order to suspend a burst in the CY7C270 the processor must simply deasert the ADV input. When the ADV input is reasserted the burst will continue from where it left off. It is not necessary for the processor to send a new address to the PROM.

Table 2. Look-Up Table for Use with Intel 486

| Fir<br>Addı |                | Seco<br>Addi |                |           | Third<br>Address |           | rth            |

|-------------|----------------|--------------|----------------|-----------|------------------|-----------|----------------|

| $A_{x+1}$   | A <sub>x</sub> | $A_{x+1}$    | A <sub>x</sub> | $A_{x+1}$ | A <sub>x</sub>   | $A_{x+1}$ | A <sub>x</sub> |

| 0           | 0              | 0            | 1              | 1         | 0                | 1         | 1              |

| 0           | 1              | 0            | 0              | 1         | 1                | 1         | 0              |

| 1           | 0              | 1            | 1              | 0         | 0                | 0         | 1              |

| 1           | 1              | 1            | 0              | 0         | 1                | 0         | 0              |

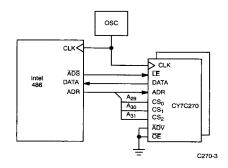

#### **Application Example 1**

80486 Instruction Memory Using Two CY7C270s

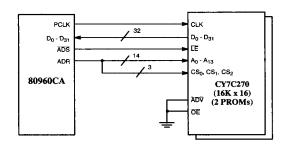

### **Application Example 2**

Intel 80960CA Using Two CY7C270s

#### **Pin Descriptions**

### Input Signals

$A_{13}-A_0$  (Address lines). The address inputs are stored in a register at the rising edge of CLK if the device is programmed in registered mode. If the device is programmed in latched mode, the address inputs flow into the PROM while  $\overline{LE}$  is active and are captured at the rising edge of  $\overline{LE}$ . For asynchronous operation, the device should be programmed in the latch mode with  $\overline{LE}$  tied LOW.

**CLK** (Clock line). The clock is used to sample the  $\overline{ADV}$  input. In registered mode, the clock is also used to sample  $\overline{LE}$ ,  $CS_2 - CS_0$ , and the address.

**LE** (Latch Enable). In registered mode, this input is sampled on the rising edge of CLK. If it is active, the address and chip selects are stored in a register. In latched mode, the address and chip selects are latched on the rising edge of this signal.

$\overline{ADV}$  (Advance Enable). This signal is used for burst reads. If  $\overline{LE}$  is inactive,  $\overline{ADV}$  is sampled on the rising edge of CLK. If  $\overline{ADV}$  is

### **Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

| Storage Temperature 65°C to +150°C                            |

|---------------------------------------------------------------|

| Ambient Temperature with                                      |

| Power Applied – 55°C to +125°C                                |

| Supply Voltage to Ground Potential 0.5V to +7.0V              |

| DC Voltage Applied to Outputs                                 |

| in High Z State $\dots -0.5V$ to $+7.0V$                      |

| DC Input Voltage                                              |

| DC Program Voltage                                            |

| UV Erasure                                                    |

| Static Discharge Voltage>2001V (per MIL-STD-883, Method 3015) |

| (per MIL-STD-883, Method 3015)                                |

| Latch-Up Current >200 mA                                      |

|                                                               |

#### **Pin Definitions**

| Signal Name     | I/O | Description                |

|-----------------|-----|----------------------------|

| $A_{13} - A_0$  | I   | Address Inputs             |

| CLK             | I   | Clock                      |

| <u>LE</u>       | I   | Latch Enable               |

| ADV             | I   | Advance Enable             |

| $CS_2 - CS_0$   | I   | Programmable Chip Selects  |

| OE              | I   | Programmable Output Enable |

| $D_{15} - D_0$  | 0   | Data Outputs               |

| V <sub>CC</sub> | -   | Power Supply               |

| V <sub>SS</sub> | -   | Ground                     |

LOW, the counter will be incremented and the next address will be delivered to the PROM core. ADV should be tied HIGH, and in the programming mode, the burst enable (BE) should be disabled for asynchronous operation.

$CS_2 - CS_0$  (Synchronous Chip Selects). The polarity of each chip select is programmed by the user. The inputs from these pins are stored in a register on the rising edge of CLK in registered mode. In latched mode, the inputs are latched on the rising edge of  $\overline{LE}$ . All three chip selects must be active in order to select the device.

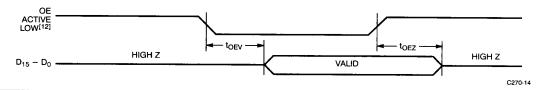

OE (Asynchronous Output Enable). The polarity of this pin is programmable. The outputs are active when OE is asserted and tristated when OE is deasserted.

#### **Output Signals**

$D_{15}-D_0$  (Data Outputs). Data from the array location addressed on inputs  $A_{13}-A_0$  will appear on these pins. The outputs will be tri-stated if OE is deasserted or if the chip is not selected.

### **Operating Range**

| Range                     | Ambient<br>Temperature | v <sub>cc</sub> |

|---------------------------|------------------------|-----------------|

| Commercial                | 0°C to +70°C           | 5V ±10%         |

| Industrial <sup>[2]</sup> | - 40°C to +85°C        | 5V ±10%         |

| Military <sup>[3]</sup>   | - 55°C to +125°C       | 5V ±10%         |

#### Notes:

- Contact a Cypress representative for industrial temperature range specifications.

- 3. TA is the "instant on" case temperature.

### Electrical Characteristics[4, 5]

| Parameter       | Description                     | Test Conditions                                                    |            | Min. | Max.     | Unit |

|-----------------|---------------------------------|--------------------------------------------------------------------|------------|------|----------|------|

| V <sub>OH</sub> | Output HIGH Voltage             | $V_{CC}$ = Min., $I_{OH}$ = $-2.0$ mA                              |            | 2.4  |          | V    |

| V <sub>OL</sub> | Output LOW Voltage              | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8.0 mA (6.0 mA Mil)      |            |      | 0.4      | v    |

| V <sub>IH</sub> | Input HIGH Level                | Guaranteed Input Logical HIGH Voltage for                          | All Inputs | 2.0  | $V_{CC}$ | V    |

| $V_{IL}$        | Input LOW Level                 | Guaranteed Input Logical LOW Voltage for A                         | all Inputs | -3.0 | 0.8      | V    |

| I <sub>IX</sub> | Input Leakage Current           | $GND \le V_{IN} \le V_{CC}$                                        | - 10       | +10  | μА       |      |

| $V_{CD}$        | Input Clamp Diode<br>Voltage    | Note 4                                                             |            |      | μА       |      |

| I <sub>OZ</sub> | Output Leakage<br>Current       | $V_{CC} = Max., V_{OL} \le V_{OUT} \le V_{OH},$<br>Output Disabled |            | - 40 | +40      | μA   |

| I <sub>OS</sub> | Output Short Circuit<br>Current | $V_{CC} = Max., V_{OUT} = 0.0V^{[6]}$                              |            | - 20 | -90      | mA   |

| $I_{CC}$        | Power Supply Current            | $V_{CC} = Max., I_{OUT} = 0.0 \text{ mA}$                          | om'l       |      | 175      | mA   |

|                 |                                 | M                                                                  | lilitary   |      | 200      | mA   |

# Capacitance<sup>[4]</sup>

| Parameter        | Description        | Test Conditions                         | Max. | Unit |

|------------------|--------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                         | 10   | pF   |

### Notes:

- See Introduction to CMOS PROMs in this Data Book for general information on testing.

See the last page of this specification for Group A subgroup testing in-

- formation.

- For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

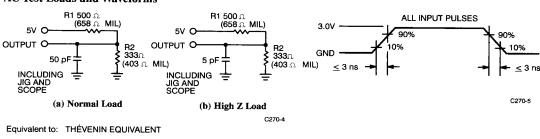

# **AC Test Loads and Waveforms**

# Switching Characteristics Over the Operating Range<sup>[5]</sup>

|                   |                                      | Commercial and Military |        |       |        |       |       |      |

|-------------------|--------------------------------------|-------------------------|--------|-------|--------|-------|-------|------|

|                   |                                      | CY7C2                   | 270-15 | CY7C2 | 270-20 | CY7C2 | 70-30 | l    |

| Parameter         | Description                          | Min.                    | Max.   | Min.  | Max.   | Min.  | Max.  | Unit |

| t <sub>CP</sub>   | Clock Period                         | 15                      |        | 20    |        | 30    |       | ns   |

| t <sub>CH</sub>   | Clock HIGH Pulse Width               | 6                       |        | 8     |        | 13    |       | ns   |

| t <sub>CL</sub>   | Clock LOW Pulse Width                | 6                       |        | 8     |        | 13    |       | ns   |

| t <sub>AS</sub>   | Address Set-Up to CLK Rise           | 3                       |        | 4     |        | 4     |       | ns   |

| t <sub>AH</sub>   | Address Hold from CLK Rise           | 2                       |        | 3     |        | 4     |       | ns   |

| t <sub>LES</sub>  | LE Set-Up to CLK Rise                | 3                       |        | 4     |        | 4     |       | ns   |

| t <sub>LEH</sub>  | LE Hold from CLK Rise                | 2                       |        | 3     |        | 4     |       | ns   |

| t <sub>LW</sub>   | Latch Pulse Width                    | 7                       |        | 10    |        | 12    |       | ns   |

| t <sub>ADVS</sub> | ADV Set-Up to CLK Rise               | 3                       |        | 4     |        | 4     |       | ns   |

| t <sub>ADVH</sub> | ADV Hold from CLK Rise               | 2                       |        | 3     |        | 4     |       | ns   |

| t <sub>ASL</sub>  | Address Set-Up to Latch Close        | 3                       |        | 4     |        | 4     |       | ns   |

| t <sub>AHL</sub>  | Address Hold from Latch Close        | 2                       |        | 3     |        | 4     |       | ns   |

| t <sub>DH</sub>   | Data Hold                            | 3                       | 1      | 3     |        | 3     |       | ns   |

| t <sub>AA</sub>   | Address to Data for Single Read      |                         | 25     |       | 28     | 1     | 35    | ns   |

| t <sub>LEA</sub>  | LE Low to Data Valid for Single Read |                         | 25     |       | 28     |       | 35    | ns   |

| t <sub>CKA</sub>  | Clock to Data for Single Read        |                         | 25     |       | 28     |       | 35    | ns   |

| t <sub>CKB</sub>  | CLK Rise to Data for Burst Read      |                         | 11     |       | 12     |       | 15    | ns   |

| t <sub>CSS</sub>  | CS Set-Up to CLK Rise                | 3                       |        | 4     |        | 4     |       | ns   |

| t <sub>CSH</sub>  | CS Hold from CLK Rise                | 2                       |        | 3     |        | 4     |       | ns   |

| t <sub>COV</sub>  | CLK Rise to Output Valid             |                         | 11     |       | 12     |       | 15    | ns   |

| t <sub>COZ</sub>  | CLK Rise to High Z Output            |                         | 11     |       | 12     |       | 15    | ns   |

| t <sub>CSOV</sub> | CS Asserted to Output Valid          |                         | 13     |       | 15     | 1     | 18    | ns   |

| t <sub>CSOZ</sub> | CS Deasserted to High Z Output       |                         | 13     |       | 15     |       | 18    | ns   |

| t <sub>CSSL</sub> | CS Set-Up to Latch Close             | 3                       |        | 4     |        | 4     |       | ns   |

| t <sub>CSHL</sub> | CS Hold from Latch Close             | 2                       |        | 3     |        | 4     |       | ns   |

| t <sub>LOV</sub>  | Latch Open to Output Valid           |                         | 13     |       | 15     |       | 18    | ns   |

| t <sub>LOZ</sub>  | Latch Open to High Z Output          |                         | 13     | ŀ     | 15     |       | 18    | ns   |

| t <sub>OEV</sub>  | OE Asserted to Output Valid          |                         | 11     |       | 12     |       | 15    | ns   |

| t <sub>OEZ</sub>  | OE Deasserted to High Z Output       |                         | 11     |       | 12     |       | 15    | ns   |

# **Switching Waveforms**

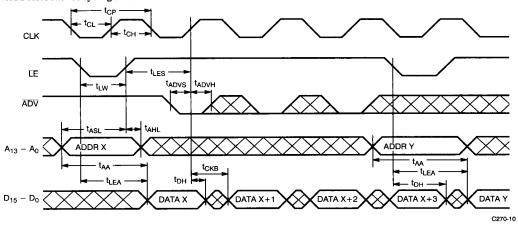

# Single Reads - Registered Mode<sup>[7, 8]</sup>

# Single Reads - Latched Mode<sup>[8]</sup>

# 4-Word Burst Followed by Single Read - Registered Mode [8]

Notes: 7. ADV is assumed HIGH.

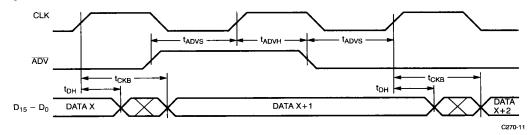

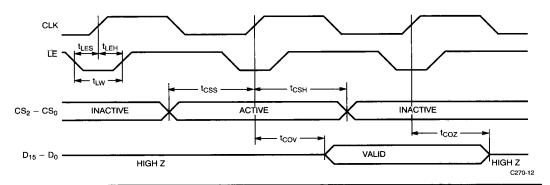

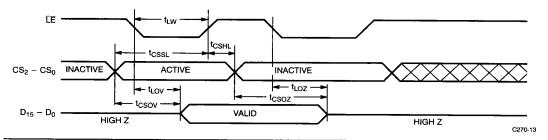

8.  $CS_2 - CS_0$ , OE are assumed active.

# Switching Waveforms (continued)

# $\textbf{4-Word Burst Followed by Single Read-Latched Mode}^{[8]} \\$

# Suspended Burst<sup>[8, 9]</sup>

# Output Controlled by CS and CLK — Registered Mode $\ensuremath{^{[10]}}$

Notes: 9. Burst in progress.

10. OE assumed active.

# Switching Waveforms (continued)

# Outputs Controlled by CS and $\overline{\text{LE}}$ - Latched Mode

### Outputs Controlled by OE[11]

#### Notes:

11. CS2 - CS0 are assumed active.

### **Erasure Characteristics**

Wavelengths of light less than 4000 Angstroms begin to erase the CY7C270. For this reason, an opaque label should be placed over the window if the PROM is exposed to sunlight or fluorescent lighting for extended periods of time.

The recommended dose for erasure of ultraviolet light is a wavelength of 2537 Angstroms for a minimum dose (UV intensity multiplied by exposure time) of 25 Wsec/cm². For an ultraviolet lamp with a 12  $\rm mW/cm^2$  power rating the exposure time would be approximately 35 minutes. The 7C270 needs to be within 1 inch of the lamp during erasure. Permanent damage may result if the PROM

### 12. OE active HIGH is a programmable option.

is exposed to high intensity UV light for an extended period of time. 7258 Wsec/cm<sup>2</sup> is the recommended maximum dosage.

### **Architecture Configuration Bits**

The CY7C270 is configured by programming the Control Word located at the end of the programmable array (4000H). *Table 3* gives the specific information for configuring the architecture.

To use the CY7C270 as a purely asynchronous PROM, tie the  $\overline{ADV}$  signal to  $V_{CC}$ , the CLK and  $\overline{LE}$  signal to  $V_{SS}$ , and program the control word for No Burst and Latched mode of operation  $(D_3=1,D_{15}=0)$ .

Table 3. Control Word for Architecture Configuration

|                                                          |                               | Control Word                                                          |                                                                                           |

|----------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Control Option                                           | Bit                           | Programmed Level                                                      | Function                                                                                  |

| OE                                                       | $D_0$                         | 0 = Default                                                           | OE Active LOW                                                                             |

| Output Enable                                            |                               | 1 = Programmed                                                        | OE Active HIGH                                                                            |

| C <sub>1</sub> C <sub>0</sub><br>(Counter Configuration) | D <sub>2</sub> D <sub>1</sub> | 00 = Default<br>01 = Programmed<br>10 = Programmed<br>11 = Programmed | 486 2-Bit Counter<br>Linear 2-Bit Counter<br>Linear 4-Bit Counter<br>Linear 8-Bit Counter |

| R/L                                                      | D <sub>3</sub>                | 0 = Default                                                           | Registered Mode                                                                           |

| Registered/Latched                                       |                               | 1 = Programmed                                                        | Latched Mode                                                                              |

| CS <sub>0</sub>                                          | D <sub>12</sub>               | 0 = Default                                                           | CS <sub>0</sub> Active LOW                                                                |

| Chip Select 0                                            |                               | 1 = Programmed                                                        | CS <sub>0</sub> Active HIGH                                                               |

| CS <sub>1</sub>                                          | D <sub>13</sub>               | 0 = Default                                                           | CS <sub>1</sub> Active LOW                                                                |

| Chip Select 1                                            |                               | 1 = Programmed                                                        | CS <sub>1</sub> Active HIGH                                                               |

| CS <sub>2</sub>                                          | D <sub>14</sub>               | 0 = Default                                                           | CS <sub>2</sub> Active LOW                                                                |

| Chip Select 2                                            |                               | 1 = Programmed                                                        | CS <sub>2</sub> Active HIGH                                                               |

| BE                                                       | D <sub>15</sub>               | 0 = Default                                                           | No Burst                                                                                  |

| (Burst Enable)                                           |                               | 1 = Programmed                                                        | Burst (follow C <sub>1</sub> C <sub>0</sub> )                                             |

# Bit Map

| Programmer Address (Hex) | RAM Data     |

|--------------------------|--------------|

| 0000                     | Data         |

|                          |              |

| •                        |              |

| •                        | · .          |

| 3FFF                     | Data         |

| 4000                     | Control Word |

Control Word (4000H - default state is 00H)  $D_{15}$   $D_0$  BE CS $_2$  CS $_1$  CS $_0$  X X X X X X X X X R/L  $C_1$   $C_0$  OE

# **Programming Information**

Programming support is available from Cypress as well as from a number of third-party software vendors. For detailed programming information, including a listing of software packages, please see the PROM Programming Information located at the end of this section. Programming algorithms can be obtained from any Cypress representative.

Table 4. Program Mode Table

| Mode            | V <sub>PP</sub> | PGM           | VFY              | $D_0 - D_{15}$ |

|-----------------|-----------------|---------------|------------------|----------------|

| Program Inhibit | V <sub>PP</sub> | $V_{IHP}$     | V <sub>IHP</sub> | High Z         |

| Program Enable  | V <sub>PP</sub> | $V_{\rm ILP}$ | $V_{IHP}$        | Data           |

| Program Verify  | $V_{PP}$        | $V_{IHP}$     | V <sub>ILP</sub> | Data           |

**Table 5. Configuration Mode Table**

| Mode                    | V <sub>PP</sub> | PGM       | VFY              | A <sub>2</sub>  | $D_0 - D_{15}$ |

|-------------------------|-----------------|-----------|------------------|-----------------|----------------|

| Program Inhibit         | V <sub>PP</sub> | $V_{IHP}$ | $V_{IHP}$        | $V_{PP}$        | High Z         |

| Program Control<br>Word | V <sub>PP</sub> | $V_{ILP}$ | $V_{IHP}$        | V <sub>PP</sub> | Control Word   |

| Verify Control<br>Word  | V <sub>PP</sub> | $V_{IHP}$ | V <sub>ILP</sub> | V <sub>PP</sub> | Control Word   |

Table 6. Signature Mode Table

| Signature Mode | A <sub>0</sub>   | A9              | $D_0 - D_{15}$ |

|----------------|------------------|-----------------|----------------|

| Cypress Code   | V <sub>ILP</sub> | $V_{PP}$        | 0034H          |

| Device Code    | $V_{IHP}$        | V <sub>PP</sub> | 0013H          |

Figure 1. Programming Pinout

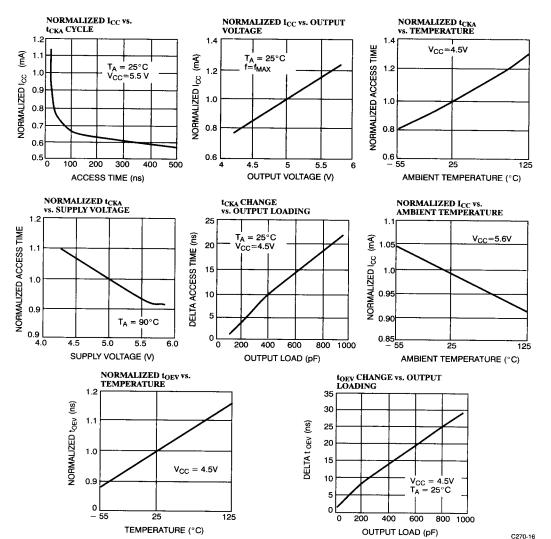

# Typical DC and AC Characteristics

# Ordering Information<sup>[13]</sup>

| Speed<br>(ns) | Ordering Code   | Package<br>Name | Package Type                          | Operating<br>Range |  |

|---------------|-----------------|-----------------|---------------------------------------|--------------------|--|

| 15            | 15 CY7C270-15HC |                 | 44-Pin Windowed Leaded Chip Carrier   | Commercial         |  |

|               | CY7C270-15JC    | J67             | 44-Lead Plastic Leaded Chip Carrier   |                    |  |

|               | CY7C270-15HMB   | H67             | 44-Pin Windowed Leaded Chip Carrier   | Military           |  |

|               | CY7C270-15QMB   | Q67             | 44-Pin Windowed Leadless Chip Carrier | 1                  |  |

| 20            | CY7C270-20HC    | H67             | 44-Pin Windowed Leaded Chip Carrier   | Commercial         |  |

|               | CY7C270-20JC    | J67             | 44-Lead Plastic Leaded Chip Carrier   | 1                  |  |

|               | CY7C270-20HMB   | H67             | 44-Pin Windowed Leaded Chip Carrier   | Military           |  |

|               | CY7C270-20QMB   | Q67             | 44-Pin Windowed Leadless Chip Carrier | 1                  |  |

| 30            | CY7C270-30HC    | H67             | 44-Pin Windowed Leaded Chip Carrier   | Commercial         |  |

|               | CY7C270-30JC    | J67             | 44-Lead Plastic Leaded Chip Carrier   |                    |  |

|               | CY7C270-30HMB   | H67             | 44-Pin Windowed Leaded Chip Carrier   | Military           |  |

|               | CY7C270-30QMB   | Q67             | 44-Pin Windowed Leadless Chip Carrier | 1                  |  |

# MILITARY SPECIFICATIONS Group A Subgroup Testing DC Characteristics

| Parameter       | Subgroups |

|-----------------|-----------|

| V <sub>OH</sub> | 1, 2, 3   |

| $V_{OL}$        | 1, 2, 3   |

| $V_{IH}$        | 1, 2, 3   |

| V <sub>IL</sub> | 1, 2, 3   |

| I <sub>IX</sub> | 1, 2, 3   |

| I <sub>OZ</sub> | 1, 2, 3   |

| $I_{CC}$        | 1, 2, 3   |

# Note:

Most of the above products are available in industrial temperature range. Contact a Cypress representative for specifications and product availability.

# **Switching Characteristics**

| Parameter         | Subgroups       |

|-------------------|-----------------|

| t <sub>AS</sub>   | 7, 8, 9, 10, 11 |

| t <sub>AH</sub>   | 7, 8, 9, 10, 11 |

| t <sub>LES</sub>  | 7, 8, 9, 10, 11 |

| t <sub>LEH</sub>  | 7, 8, 9, 10, 11 |

| t <sub>ADVS</sub> | 7, 8, 9, 10, 11 |

| t <sub>ADVH</sub> | 7, 8, 9, 10, 11 |

| t <sub>DH</sub>   | 7, 8, 9, 10, 11 |

| t <sub>CKA</sub>  | 7, 8, 9, 10, 11 |

| t <sub>CSS</sub>  | 7, 8, 9, 10, 11 |

| t <sub>CSH</sub>  | 7, 8, 9, 10, 11 |

| t <sub>AA</sub>   | 7, 8, 9, 10, 11 |

| t <sub>CKB</sub>  | 7, 8, 9, 10, 11 |

| t <sub>LEA</sub>  | 7, 8, 9, 10, 11 |

| t <sub>OEV</sub>  | 7, 8, 9, 10, 11 |

| t <sub>LW</sub>   | 7, 8, 9, 10, 11 |

| t <sub>ASL</sub>  | 7, 8, 9, 10, 11 |

| t <sub>CSSL</sub> | 7, 8, 9, 10, 11 |

| t <sub>AHL</sub>  | 7, 8, 9, 10, 11 |

| t <sub>CSHL</sub> | 7, 8, 9, 10, 11 |

| t <sub>CSOV</sub> | 7, 8, 9, 10, 11 |

| t <sub>LOV</sub>  | 7, 8, 9, 10, 11 |

| t <sub>COV</sub>  | 7, 8, 9, 10, 11 |

Document #: 38-00179-E